## HETEROGENEOUS SYSTEM DESIGN AND OPTIMISATION FOR EMBEDDED VISION SYSTEMS

A THESIS SUBMITTED TO THE UNIVERSITY OF MANCHESTER

FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

IN THE FACULTY OF SCIENCE AND ENGINEERING

2020

By

Chao Jiang

School of Electrical and Electronic Engineering

| Li       | st of        | Figur             | es                                | 7  |

|----------|--------------|-------------------|-----------------------------------|----|

| Li       | st of        | Table             | $\mathbf{s}$                      | 9  |

| Li       | st of        | Abbr              | eviations                         | 13 |

| 1        | Intr         | $\mathbf{coduct}$ | ion                               | 27 |

|          | 1.1          | Challe            | enges of heterogeneous systems    | 28 |

|          |              | 1.1.1             | Design                            | 29 |

|          |              | 1.1.2             | Programming                       | 29 |

|          | 1.2          | Objec             | tives of the research             | 30 |

|          | 1.3          | Resea             | rch outcomes                      | 30 |

|          | 1.4          | Origin            | nal contributions of the research | 31 |

|          | 1.5          | Disser            | rtation Overview                  | 31 |

| <b>2</b> | $Th\epsilon$ | Inter             | face Technologies                 | 33 |

|          | 2.1          | Peripl            | neral Interface                   | 33 |

|          |              | 2.1.1             | PCIe                              | 34 |

|          |              | 2.1.2             | RapidIO                           | 36 |

|          |              | 2.1.3             | Gigabit Ethernet                  | 37 |

|          |              | 2.1.4             | USB                               | 38 |

|          |              | 2.1.5             | The Simple Serial Protocols       | 40 |

|          |              | 2.1.6             | Custom memory interface           | 41 |

|          |              | 2.1.7             | Communication in the SoC FPGA     | 42 |

|          |              | 2.1.8             | Summary                           | 43 |

|          | 2.2          | Syster            | m Interface                       | 44 |

|   |     | 2.2.1  | AMBA                                        |

|---|-----|--------|---------------------------------------------|

|   |     | 2.2.2  | WISHBONE                                    |

|   |     | 2.2.3  | AVMM interface                              |

|   |     | 2.2.4  | Summary                                     |

| 3 | The | Platf  | orm                                         |

| • | 3.1 |        | flash overview                              |

|   | 0.1 | 3.1.1  | ARM SoC                                     |

|   |     | 3.1.2  | FPGA                                        |

|   |     | 3.1.3  | Applications                                |

|   | 3.2 |        | ides of the bridge                          |

|   | J   | 3.2.1  | GPMC                                        |

|   |     | 3.2.2  | AVM                                         |

|   | 3.3 | 91-1-  | ous work                                    |

|   | 3.4 |        | nary                                        |

|   | 5.1 | Sami   |                                             |

| 4 | The | Desig  | gn of GPMC-to-FPGA Bridge                   |

|   | 4.1 | Issues | with the two interfaces                     |

|   | 4.2 | The L  | ightweight Bridge                           |

|   |     | 4.2.1  | Composition of the memory-mapped sub-bridge |

|   |     | 4.2.2  | Translation of the write transaction        |

|   |     | 4.2.3  | Translation of the read transaction         |

|   | 4.3 | The E  | Iigh-Performance Bridge                     |

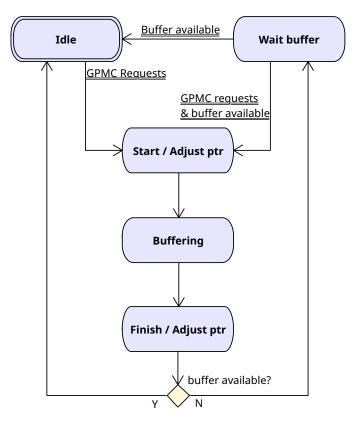

|   |     | 4.3.1  | The Stream buffer and its customisation     |

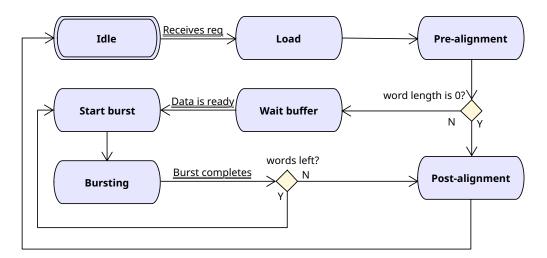

|   |     | 4.3.2  | SRAM interface read slave controller        |

|   |     | 4.3.3  | AVM read controller                         |

|   |     | 4.3.4  | SRAM interface slave write controller       |

|   |     | 4.3.5  | AVM write controller                        |

|   |     | 4.3.6  | Transmuxer and operation mode               |

|   |     | 4.3.7  | Control/status registers                    |

|   |     |        |                                             |

| 5 | Ben | ıchmaı | rk for the GPMC-to-FPGA bridge                   | 89  |

|---|-----|--------|--------------------------------------------------|-----|

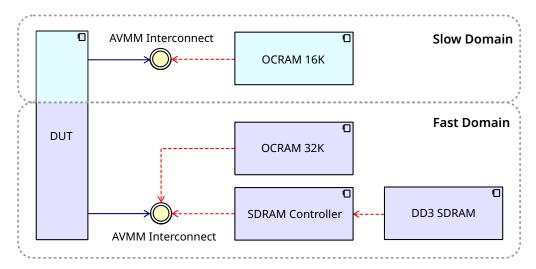

|   | 5.1 | Test I | Environment                                      | 89  |

|   |     | 5.1.1  | FPGA                                             | 89  |

|   |     | 5.1.2  | Software                                         | 91  |

|   | 5.2 | Tests  | and Results                                      | 94  |

|   | 5.3 | Discus | ssion                                            | 99  |

|   |     | 5.3.1  | Hardware limitations                             | 99  |

|   |     | 5.3.2  | Bandwidth                                        | 100 |

| 6 | Sup | port o | of the OpenCL framework on the ARMflash platform | 103 |

|   | 6.1 | Requi  | irements for implementation                      | 104 |

|   |     | 6.1.1  | The memory model in OpenCL                       | 105 |

|   |     | 6.1.2  | Reference Implementations in the AOCL            | 106 |

|   |     | 6.1.3  | Design requirements                              | 107 |

|   | 6.2 | Design | n                                                | 109 |

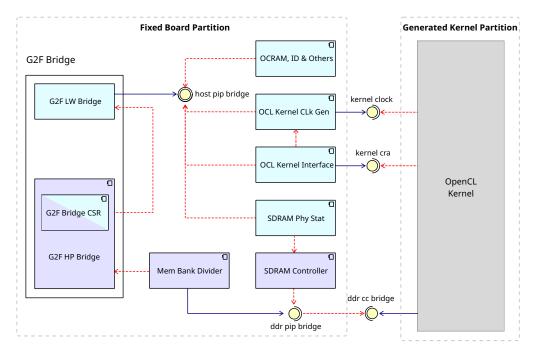

|   |     | 6.2.1  | FPGA partition                                   | 109 |

|   |     | 6.2.2  | Software                                         | 111 |

|   | 6.3 | Resul  | ts                                               | 114 |

|   |     | 6.3.1  | FPGA partition                                   | 114 |

|   |     | 6.3.2  | Applications                                     | 115 |

|   | 6.4 | Discus | ssion                                            | 116 |

|   |     | 6.4.1  | Advantages                                       | 117 |

|   |     | 6.4.2  | Platform limitation                              | 117 |

|   |     | 6.4.3  | Interface limitation                             | 118 |

| 7 | Bac | kgrou  | nd for Program Optimisation                      | 121 |

|   | 7.1 | Progr  | am analysis and optimisation                     | 121 |

|   |     | 7.1.1  | Polyhedral analysis                              | 121 |

|   |     | 7.1.2  | DAG-based analysis                               | 124 |

|   |     | 7.1.3  | Tile size generation                             | 124 |

|   | 7.2 | The H  | Halide Language                                  | 126 |

|   |       | 7.2.1  | Algorithm                                  | . 126 |

|---|-------|--------|--------------------------------------------|-------|

|   |       | 7.2.2  | Schedule                                   | . 127 |

|   |       | 7.2.3  | Portability                                | . 128 |

|   |       | 7.2.4  | The Halide auto-scheduler                  | . 129 |

| 8 | An    | Altern | native Auto-Optimiser                      | 131   |

|   | 8.1   | The A  | auto-optimiser                             | . 131 |

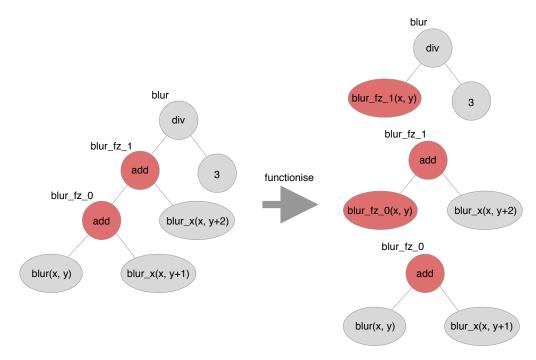

|   |       | 8.1.1  | Source transformation                      | . 132 |

|   |       | 8.1.2  | Partition                                  | . 138 |

|   |       | 8.1.3  | Intra-partition analysis                   | . 139 |

|   |       | 8.1.4  | Intra-partition optimisation               | . 142 |

|   | 8.2   | Exper  | iment                                      | . 146 |

|   | 8.3   | Discus | ssion                                      | . 146 |

| 9 | Cor   | clusio | n and Future Work                          | 149   |

|   | 9.1   | Conclu | usion                                      | . 149 |

|   | 9.2   | Future | e Work                                     | . 150 |

|   |       | 9.2.1  | The GPMC-to-FPGA bridge                    | . 151 |

|   |       | 9.2.2  | AOCL support for custom embedded systems   | . 151 |

|   |       | 9.2.3  | Automatic optimisation for Halide programs | . 151 |

| R | efere | nces   |                                            | 153   |

## List of Figures

| 2.1  | Communication model for USB [25]                                    | 36 |

|------|---------------------------------------------------------------------|----|

| 2.2  | Bridges available on a Intel SoC FPGA [29]                          | 42 |

| 3.1  | The ARMflash platform                                               | 48 |

| 3.2  | AM3358 L3 Topology [28]                                             | 49 |

| 3.3  | ARMflash as part of a smart camera system                           | 51 |

| 3.4  | Waveform for NAND read operation                                    | 52 |

| 3.5  | Waveform for accessing NOR flash                                    | 54 |

| 3.6  | The address phase waveforms of the GPMC NOR protocol configured     |    |

|      | in (a) AD-multiplexing (b) AAD-multiplexing mode                    | 55 |

| 3.7  | The relationship between GPMC data access and write-enable          | 56 |

| 3.8  | The behaviour of the GPMC wait signal                               | 57 |

| 3.9  | Waveform for burst AVM write [37]                                   | 58 |

| 3.10 | Waveform for burst AVM read [37]                                    | 59 |

| 3.11 | AVM and generated AVMM interconnect                                 | 60 |

| 3.12 | EVS-MUX with two bridge modules attached used as part of a smart    |    |

|      | camera system                                                       | 61 |

| 3.13 | Use of the address bus of the memory interface in the EVS-MUX. $$ . | 62 |

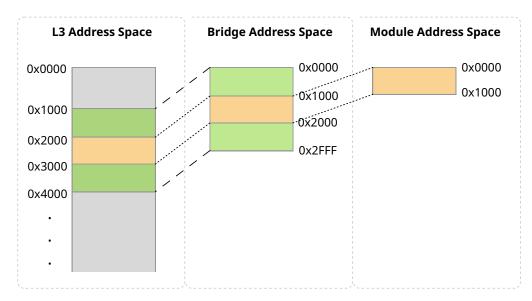

| 4.1  | Memory mapping of an FPGA module into SoC's L3                      | 66 |

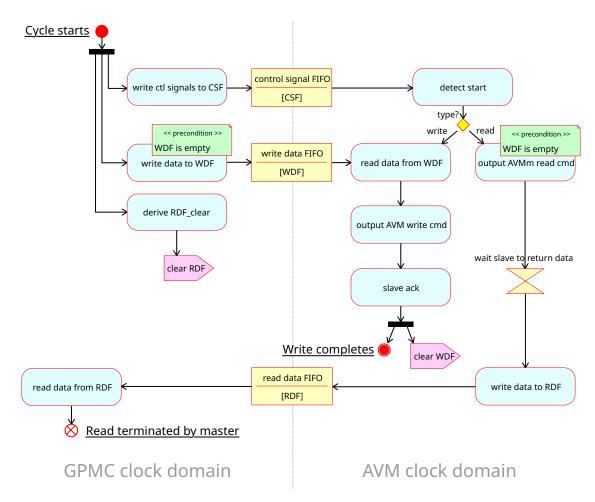

| 4.2  | Transaction translation in the lightweight bridge                   | 69 |

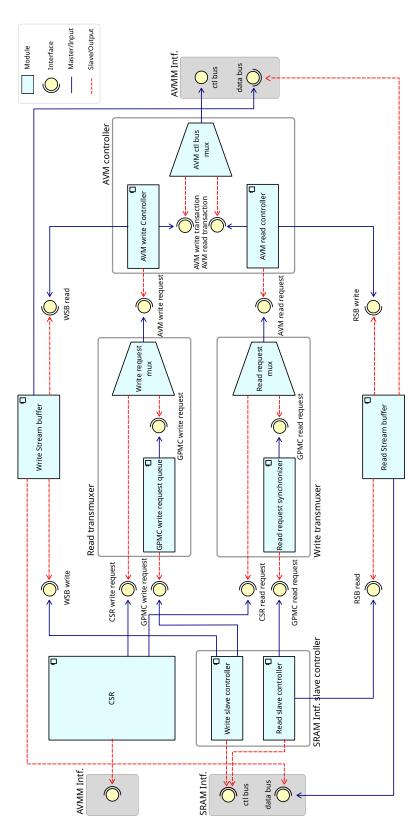

| 4.3  | Composition of the high-performance bridge                          | 71 |

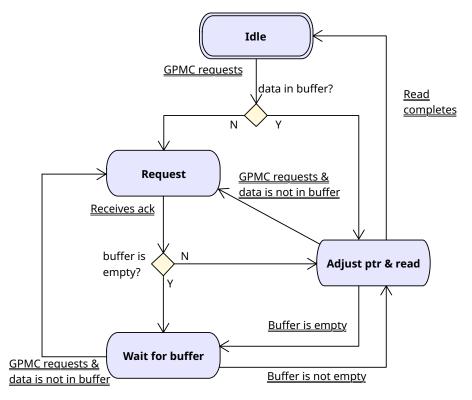

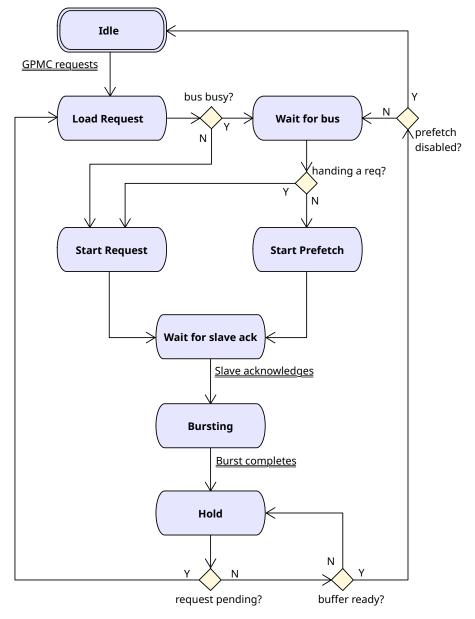

| 4.4  | Finite-state machine for the SRAM interface read slave controller   | 75 |

| 4.5  | Finite-state machine for AVM read controller                        | 77 |

| 4.6  | Finite-state machine for SRAM interface write slave controller      | 79 |

8 List of Figures

| 4.7 | Finite-state machine for AVM write controller                             |

|-----|---------------------------------------------------------------------------|

| 4.8 | Reconfigurable mapping                                                    |

| 5.1 | FPGA benchmark environment for the GPMC-to-FPGA bridge and                |

|     | EVS-MUX                                                                   |

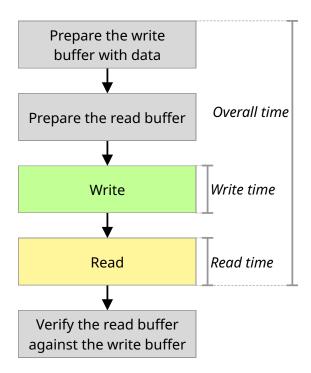

| 5.2 | Flow diagram for the test programs                                        |

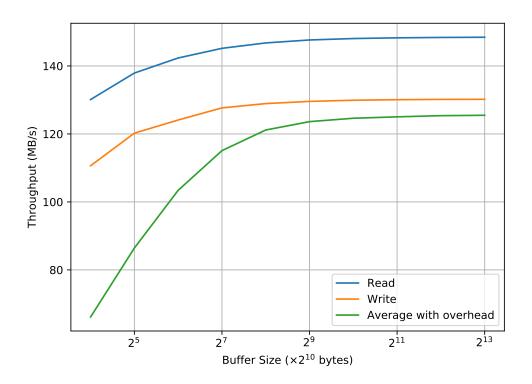

| 5.3 | The relationship between test buffer size and throughput in Con-          |

|     | fig 24 (f = 125 MHz, DW = 32 bit, BS = 64 bytes) 96                       |

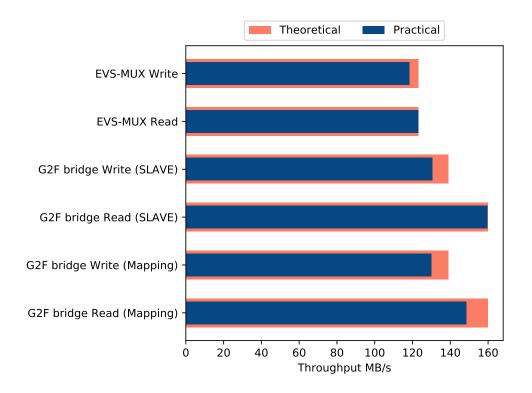

| 5.4 | Throughput (practical and theoretical limit) comparison between the       |

|     | GPMC-to-FPGA bridge in Config 24 (f = 125 MHz, DW = 32 bit,               |

|     | BS = 64  bytes)                                                           |

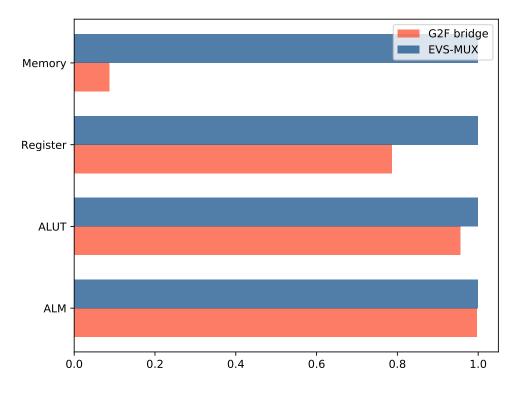

| 5.5 | Resource usage (normalised to the usage of the EVS-MUX) com-              |

|     | parison between the GPMC-to-FPGA bridge and the EVS-MUX in                |

|     | Config 24 (f = 125 MHz, DW = 32 bit, BS = 64 bytes)                       |

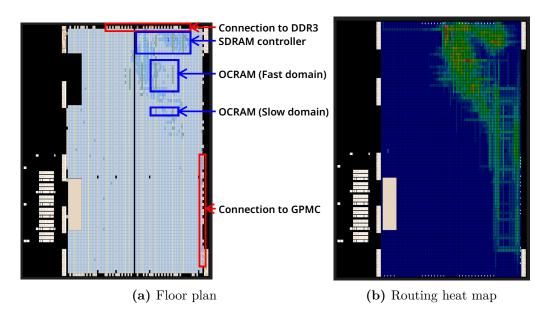

| 5.6 | FPGA floor plan for Configuration 22 (DW = 32 bits, BS = 32 bytes). $100$ |

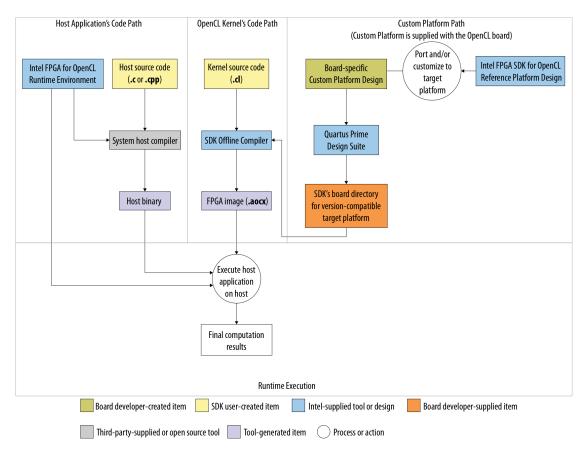

| 6.1 | Programming flow in Intel FPGA OpenCL framework [41] 104                  |

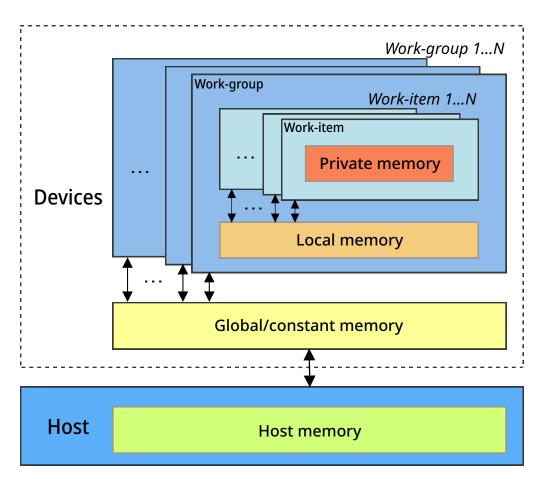

| 6.2 | OpenCL memory model [42]                                                  |

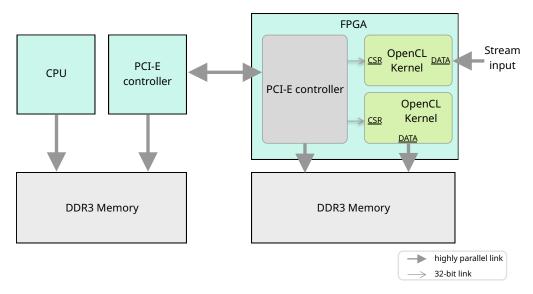

| 6.3 | Host-kernel communication in the PCI-E based platform 106                 |

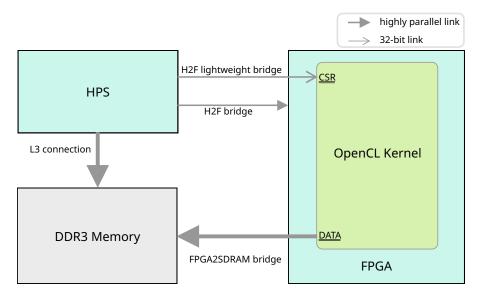

| 6.4 | Host-kernel communication in the SoC FPGA platform 107                    |

| 6.5 | FPGA design for AOCL support on ARMflash                                  |

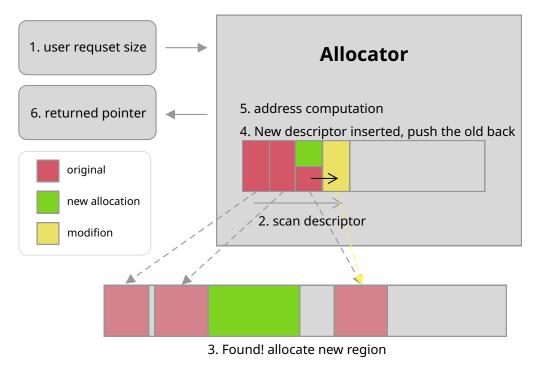

| 6.6 | Memory allocation by the simple memory allocator                          |

| 7.1 | An example for loop (a) and its iteration domain (b)                      |

| 8.1 | Functionisation of blur in List 8.1a                                      |

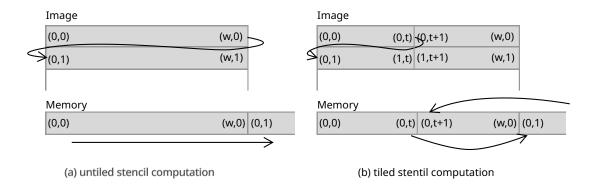

| 8.2 | Memory access pattern in untiled (a) and tile (b) stencil computation.144 |

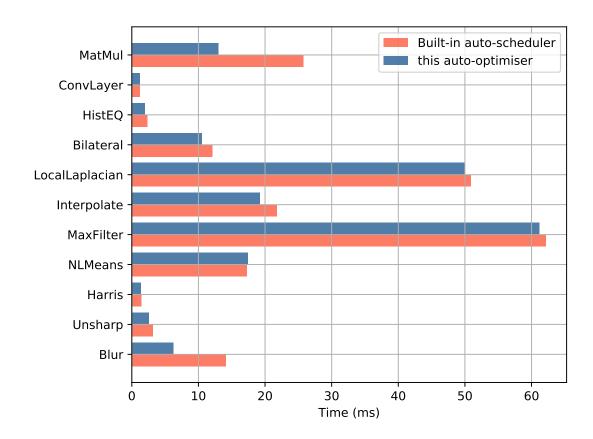

| 8.3 | Execution time comparison for the auto-optimiser of this work (blue       |

|     | bars) and Halide's built-in auto-scheduler (red bars)                     |

## List of Tables

| 2.1 | Resource usage of Avalon-MM Hard IP for PCI Express for Cyclone                        |     |

|-----|----------------------------------------------------------------------------------------|-----|

|     | V, in terms of the number of adaptive logic modules (ALM), the                         |     |

|     | number of bits of memory and the number of combinatory logic. [11]                     | 35  |

| 2.2 | Triple speed Ethernet IP resource usage on Cyclone V GX in terms                       |     |

|     | of logic elements (LE), logic registers (LR) and memory blocks [20].                   | 38  |

| 2.3 | Comparison between interfacing options for SoC with an external                        |     |

|     | FPGA                                                                                   | 43  |

| 3.1 | Comparison between interfacing options available in AM3358 for                         |     |

|     | connecting an external FPGA                                                            | 50  |

| 4.1 | High-performance bridge register map                                                   | 85  |

| 4.2 | Bit map for the Control/Status register (Word Offset = $0x 0$ )                        | 86  |

| 5.1 | Comparison of maximum transaction size and equivalent GPMC                             |     |

|     | burst length between different methods                                                 | 94  |

| 5.2 | Maximum throughput for different FPGA configurations                                   | 95  |

| 5.3 | FPGA fitter resource usage of GPMC-to-FPGA bridge in Config 24                         |     |

|     | $(f = 125 \text{ MHz}, DW = 32 \text{ bit}, BS = 64 \text{ bytes}). \dots \dots \dots$ | 98  |

| 5.4 | $f_{\rm MAX}$ measurement of the clock domains in the GPMC-to-FPGA                     |     |

|     | bridge for Config 24 (f = 125 MHz, DW = 32 bit, BS = 64 bytes)                         | 99  |

| 6.1 | Resource usage for the infrastructure partition                                        | 114 |

## List of Algorithms

| 1 | Pseudo code for refactoring step                    | 13. |

|---|-----------------------------------------------------|-----|

| 2 | Refactor matching functions to the pattern function | 130 |

| 3 | Remove a trivially schedulable function             | 13' |

| 4 | Intra-partition computation reorder and split       | 14  |

#### List of Abbreviations

1-D, 2-D, n-D One- or two-dimensional or n dimensional

$\mathbf{ALM}$  . . . . . . Adaptive logic module

**ALUT** . . . . . Adaptive loop-up table

AOCL . . . . Intel FPGA OpenCL

**API** . . . . . Application programming interface

**AST** . . . . . Abstract syntax tree

AVM . . . . . Avalon memory-mapped master

**AVMM** . . . . Avalon memory-mapped

DAG . . . . . Directed acyclic graph

CPU . . . . . . Central processing unit

CSF . . . . . . Control signal FIFO

**DSL** . . . . . Domain specific language

**DMA** . . . . Direct memory access

**DSP** . . . . . . Digital signal processor/processing

EDMA . . . . Enhanced direct memory access

**FIFO** . . . . . First-in-first-out

**FPGA** . . . . . Field programmable gate array

**FPS** . . . . . . Frame per second

$\mathbf{Gb}$  . . . . . . . Gigabit

**GB** . . . . . . . Gigabyte

**GPMC** . . . . General purpose memory controller

GPU . . . . . Graphics processing unit

**GT** . . . . . . . Gigatransfers

HDL . . . . . . Hardware description language

**HPS** . . . . . . Hard processor system

I2C . . . . . . Inter-integrated circuit

**IP** . . . . . . Intellectual property

**JIT** . . . . . . Just-in-time

KB . . . . . . Kilobyte

LE . . . . . . Logic element

LR . . . . . . Logic register

**L1, L2, L3, L4** Level 1, level 2, level 3, level 4

MB . . . . . . Megabyte

MM . . . . . Memory-mapped

MMD . . . . . Memory-mapped device

OCRAM . . . On-chip random-access memory

**OSI** . . . . . Open System Interconnect

**PC** . . . . . . Personal Computer

PCB . . . . . Printed circuit board

PCIe . . . . . Peripheral component interconnect express

PHY . . . . . External physical layer

RDF . . . . . . Read data FIFO

SIMD . . . . . Single instruction multiple data

SoC . . . . . System on a chip

SPI . . . . . . . Serial peripheral interface

**SRAM** . . . . . Static random-access memory

$\mathbf{TLP}$  . . . . . Transaction layer packet

**USB** . . . . . . Universal serial bus

**UDP** . . . . . . User Datagram Protocol

$\mathbf{UART}$  . . . . Universal asynchronous receiver-transmitter

$\mathbf{WDF}$  . . . . . Write data FIFO

#### Abstract

Heterogeneous computing is becoming a common approach to speed up processing, especially for embedded systems which require minimum power consumption. Dedicated processors like graphics processing units (GPU), digital signal processors (DSP) and field programmable gate arrays (FPGA) are often used besides the traditional central processing units (CPU) in order to meet real time processing needs whilst staying within a restricted power usage. When using such systems, the communication between the various processors and the management of tasks across them are important challenges that need to be tackled.

This work studied the possible interfacing options between a traditional CPU and an FPGA device such that a high transfer rate could be obtained. A memory-based custom bridge with configurable transaction translation was designed to interface a CPU and an FPGA. The bridge makes use of a flash memory controller that is widely available in embedded systems, enabling the addition of a re-configurable hardware accelerator without dedicated interfaces like the Peripheral Component Interconnect Express (PCIe). The bridge consists of two sub-interfaces to handle all communication scenarios; one of them allows access to non-prefetchable memory, and the other provides prefetching to improve bandwidth for sequential access via stream buffers, achieving up to 148.45 MB/s, an improvement of about 20% when compared to existing designs.

The developed bridge was incorporated into the Intel FPGA OpenCL framework to enable OpenCL-based FPGA acceleration for embedded systems. This includes the development of an FPGA design with the developed bridge as the part of the fixed elements, and software required for the configuration of the fixed elements and the communication between the CPU and the FPGA, including direct memory access (DMA) between the two. It demonstrates the possibility to have OpenCL in low-cost embedded platforms, lowering the entry point for FPGA accelerated computing.

The work also looks to provide an automatic optimiser to generate CPU schedules for Halide which is a domain specific language that separates the algorithm and the schedule of a conventional program. The optimiser avoids the loss of optimisation opportunities from the way a function is expressed and presents a new way of analysing the pipeline to generate schedules for optimal performance, and improves the performance up to 50% when compared to Halide's built-in auto-scheduler.

## Declaration

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

## Copyright

- i. The author of this thesis (including any appendices and/or schedules to this thesis) owns certain copyright or related rights in it (the "Copyright") and s/he has given The University of Manchester certain rights to use such Copyright, including for administrative purposes.

- ii. Copies of this thesis, either in full or in extracts and whether in hard or electronic copy, may be made **only** in accordance with the Copyright, Designs and Patents Act 1988 (as amended) and regulations issued under it or, where appropriate, in accordance with licensing agreements which the University has from time to time. This page must form part of any such copies made.

- iii. The ownership of certain Copyright, patents, designs, trademark and other intellectual property (the "Intellectual Property") and any reproductions of copyright works in the thesis, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property and/or Reproductions.

- iv. Further information on the conditions under which disclosure, publication and commercialisation of this thesis, the Copyright and any Intellectual Property and/or Reproductions described in it may take place is available in the University IP Policy (see http://documents.manchester.ac.uk/DocuInfo.aspx?DocID=487), in any relevant Thesis restriction declarations deposited in the University Library, The University Library's regulations (see http://www.manchester.ac.uk/library/aboutus/regulations) and in The University's policy on presentation of Theses.

## Acknowledgements

I would like to thank everyone at the University of Manchester who supported me throughout the course of this PhD, especially my supervisor.

## List of Publications

- T.B. Garcia-Nathan, A. Kachatkou, C. Jiang, D. Omar, J. Marchal, H. Chagani, N. Tartoni and R.G. van Silfhout, Compact and portable X-ray imager system using Medipix3RX, Journal of Instrumentation, October 2017

- H. Chagani, T.B. Garcia-Nathan, C. Jiang, A. Kachatkou, J. Marchal, D. Omar, N. Tartoni, R.G. van Silfhout and S. Williams, Performance of the Lancelot Beam Po-sition Monitor at the Diamond Light Source, Journal of Instrumentation, December 2017

# Introduction

Heterogeneous systems are commonly used in different computing scenarios, ranging from high-performance computer systems used in various scientific research to embedded systems such as the smart phone. The heterogeneity of the systems can be generally classified into three categories:

- Machine level

- Board level

- Chip level

At machine level, different types of computers could be interconnected to form a system or a computing network; heterogeneous cloud computation with OpenStack Compute [1] allows machines with different architectures, operating systems, and other specifications to provide high-performance computing as well as power efficiency.

At board level, one of the examples is the personal computer (PC); when external peripheral processors, such as the graphics processing units (GPU) and the digital signal processors (DSP), are attached to the motherboard, the machine becomes a heterogeneous system which allows faster computation in applications utilising the dedicated processors.

At chip level, the heterogeneous system on a chip (SoC) found in, for example, the smart phones and the smart cameras could have various types of processing cores, such as a general-purpose central processing unit (CPU) and a GPU, fused in a single chip. Such designs provide not only performance and power benefits similarly as the previous systems, but are also extremely compact.

#### 1.1 Challenges of heterogeneous systems

Due to the involvement of different kinds of computing machines or units, the design and the use of heterogeneous systems could face difficulties in the following aspects [2]:

- 1. Algorithm design

- 2. Code-type profiling

- 3. Analytical benchmarking

- 4. Partitioning and mapping

- 5. Machine selection

- 6. Scheduling

- 7. Synchronisation

- 8. Interconnect requirement

- 9. Programming environment

- 10. Performance evaluation

In general, a heterogeneous system must be designed so that the interconnection between the heterogeneous components can efficiently communicate with each other in order to meet the bandwidth requirements. The input program to the system would need to be written to utilise the different processors efficiently, and the program's executor needs to have sufficient knowledge about the program and the system so that it can divide the tasks to run on the most suitable processor. This research focuses on the design of the heterogeneous system and the programs' execution on individual processors, and the following sections provide background for the work.

1. Introduction 29

#### 1.1.1 Design

Processor selection and interconnection are two key topics in designing a heterogeneous system. When designing a low-cost system, board level heterogeneity is the most cost effective among the categories mentioned previously and the size of the system could also be relatively small. The LancelotRX smart camera system [3], for example, uses such an approach to integrate a field programmable gate array (FPGA) device and an ARM SoC on the same printed circuit board (PCB) board called the ARMflash. Additionally, as a second example, the RedCape is designed as a stackable expansion board for the open-source single-board computer, the Beaglebone, upgrading a CPU-only board with an FPGA. The inter-processor interface often requires a high bandwidth to remove any potential bottlenecks; for example, in image processing applications, for real-time video processing found in a smart camera system, the bandwidth required would be around 187 MB/s<sup>1</sup> when 24bit high definition video (1080p) is streamed at 30 frames per second (FPS). Such a bandwidth can usually only be met with dedicated hardware interfaces, such as Peripheral Component Interconnect Express (PCIe) and USB 3.0, which may have limited availability in low-cost SoCs, and thus, alternative solutions need to be developed. In the ARMflash platform inside the Lancelot RX, a custom memory interface is used to link the two processors. However, limited performance of the interface module on the FPGA side still leaves the inter-processor interface the bottleneck of the whole system. Hence, it becomes necessary to improve the memory interface bridge on the ARMflash platform.

#### 1.1.2 Programming

On the other hand, programming of the different processors in a heterogeneous system is challenging. The use of meta-programming is one of the methods to tackle this issue; code for different processors is written in similar syntax, so it could be more easily maintained. For image processing applications, Halide [4] is one of the meta-programming languages which can be compiled into binaries for different

$<sup>^{1}\</sup>mathrm{In}$  this thesis, KB, MB, and GB denotes  $10^{3},\,10^{6},\,$ and  $10^{9}$  bytes respectively.

processor architectures or back-ends, for example, ARM, x86, CUDA and OpenGL. Besides providing a unified language for programming a heterogeneous system, Halide also decouples algorithms' definitions and schedules so that the algorithms computation can be more easily optimised. The schedules of an algorithm are the order of evaluation of the algorithm on a particular processor. These schedules can be easily applied as parametric function calls in a program, although it is still challenging to choose the right schedule with its parameters. Halide provides a built-in auto-scheduler for tackling the issue, but it is realised the schedules generated by it are still far from optimal sometimes. Hence, it becomes necessary to improve the heuristics for schedule generation.

#### 1.2 Objectives of the research

The research aims to create a low-cost heterogeneous embedded system with supporting software packages. The research is mainly focused on the ARMflash platform in order to meet the high bandwidth requirements of smart camera systems for relevant applications for which the platform is used. Finally, the supporting software should ease the difficulty of using such a system.

#### 1.3 Research outcomes

The research has achieved the following:

Designed a new memory-interface-based inter-processor bridge for the ARMflash platform The new interface bridge, consisting of a lightweight subbridge and a high-performance sub-bridge, fully utilises the hardware capability available. Through benchmarking and comparing with the original design, the new design shows considerable performance improvement.

1. Introduction 31

Implemented OpenCL for the FPGA on the ARMFlash platform By having OpenCL enabled for the platform, it allows the use of the low-cost embedded system as a hardware-accelerated computing device. It also improves code reusability and maintenances by converting existing hardware-description-language-based (HDL-based) processing code to OpenCL programs.

Provided a better automatic scheduling heuristic for Halide for schedule generation The alternative auto-optimiser has shown improvement in most test cases when comparing to Halide's built-in auto-scheduler, although it is still limited in generating the best schedule.

#### 1.4 Original contributions of the research

The incorporation of the stream buffer, which is one of the techniques to realise hardware prefetching, into the high-performance sub-bridge of the GPMC-to-FPGA bridge separates the design from the other commonly found solutions for similar embedded systems. Although stream buffer has been widely used in cache design, it has not been part of a custom FPGA interface.

The board support packages for the ARMflash system could also provide a ready-to-use extension to Beaglebone board with similar configurations. It lowers the entry point for OpenCL acceleration on FPGA, and due to the board level heterogeneity, it is more flexible for board designer to choose the configuration for their targeted application.

The alternative auto-optimizer for Halide on the other hand improves the heuristic for CPU scheduling, which could be served as a basis for scheduling on other processors.

#### 1.5 Dissertation Overview

The rest of this thesis is structured as the following:

- Chapter 2 gives the overview of options for interfacing a CPU and an FPGA and a comparison of several options.

- Chapter 3 describes the target platform (ARMflash) and resource available.

- Chapter 4 outlines the design of the GPMC-to-FPGA bridge.

- Chapter 5 evaluates the designed bridge with a benchmark system.

- Chapter 6 proposes one use case of the designed bridge: the integration with Intel OpenCL framework for FPGA.

- Chapter 7 discusses existing work on programming optimisation.

- Chapter 8 presents an auto-optimiser for the Halide programming language.

- Chapter 9 concludes the work and suggest future improvement and directions.

## 2

## The Interface Technologies

When designing a heterogeneous system with commodity ARM application SoC and FPGA devices, two interfaces are particularly important: the peripheral interface between the SoC and FPGA, and the system interface in the FPGA design. The former handles the communication between the SoC and the FPGA, allowing the two devices interacting with each other, while the latter links up various system-level components in the FPGA design. This Chapter overviews the two types of interface, considering the performance and complexity for potential choices.

#### 2.1 Peripheral Interface

The peripheral interface provides a solution for connecting external devices to a SoC. In the case of an ARM SoC and an FPGA, this interface often becomes the bottleneck when there is a large data flow between the two devices. Hence, it is important to choose a suitable technology to meet the requirements of the most demanding application. The following sections give an overview of potential options for the interface with particular emphasis on bandwidth, supporting circuitry, FPGA resource usage and driver software complexity.

#### 2.1.1 PCIe

PCIe is a high-performance peripheral interconnect protocol widely used in PC for connecting various devices, such as the GPU, Ethernet controller and non-volatile memory device, to the main system. It is also one of the more commonly used options for interfacing an FPGA with a PC system. Research has been published with efforts to improve bus mastering in PCIe for the FPGA in particular to ensure the best performance [5, 6], and various FPGA vendors provide complete solutions to enable the FPGA to function as a PCIe device [7, 8].

Common PCIe interconnects consist of the root complex, the switch and endpoints. The root complex links the processor and memory subsystem to the PCIe network and sends out packets on behalf of the processor. The PCIe switch works similarly as a network switch commonly found in a local Ethernet network; it connects multiple devices and routes the packets to their destinations. An endpoint, which represents the peripheral device in the PCIe network, generates or receives a transaction packet. All the PCIe devices are connected to the network via the PCIe link; which can consist of up to 32 lanes. Each lane is constituted of one differential pair of signals, of which one is used for sending data and the other for receiving. Whereas version 1.0 of the protocol can deliver 2.5 GT/s per lane, the most recent version 4.0 features 16.0 GT/s of bandwidth [9]. This rate multiplies by the number of lanes used in the link to give a throughput that is rarely achievable via other protocols. However, the calculation of the effective data rate needs to take account of the encoding scheme; for example, the version 1.0 uses 8b/10b encoding that results in a throughput of 250 MB/s per lane. Besides, more overhead is introduced when wrapping the user data in a packet; a typical memory write of 256 bytes using 32-bit addressing has a total packet size of 278 bytes, as a result the effective transfer rate of user data reduces to 230 MB/s [10].

At the device level, the PCIe is divided into three layers; the transaction layer which converts application requests into transaction layer packets (TLP), the data link layer which handles the flow controls via a request-acknowledge mechanism, and the physical layer which consists of the digital and analogue

| Data Rate or<br>Interface Width      | ALMs | Memory<br>(M10K) | Logic<br>Registers |  |  |  |  |

|--------------------------------------|------|------------------|--------------------|--|--|--|--|

| Avalon-MM Bridge                     |      |                  |                    |  |  |  |  |

| Gen1 ×4                              | 1250 | 27               | 1700               |  |  |  |  |

| Avalon-MM InterfaceCompleter Only    |      |                  |                    |  |  |  |  |

| 64                                   | 600  | 11               | 900                |  |  |  |  |

| 128                                  | 1350 | 22               | 2300               |  |  |  |  |

| Avalon-MMCompleter Only Single DWord |      |                  |                    |  |  |  |  |

| 64                                   | 160  | 0                | 230                |  |  |  |  |

**Table 2.1:** Resource usage of Avalon-MM Hard IP for PCI Express for Cyclone V, in terms of the number of adaptive logic modules (ALM), the number of bits of memory and the number of combinatory logic. [11]

circuitry for passing the electrical signals over the serial link. When deploying PCIe in the FPGA, the design and integration could be simplified with vendor provided intellectual property (IP), which implements all the above layers and an application interface. Such IP could provide a performance close to the theoretical limit; it is possible to have 222 MB/s and 225 MB/s respectively when performing read and write transaction using a direct memory access (DMA) engine for a single lane configuration using version 1.0 [8]. Hence, the throughput requirement for a simple video streaming application could be met with the minimum setup. Also, as shown in Table 2.1, the inclusion of the PCIe controller only consumes limited logic for the performance it can deliver; due to most of the IP using logic with fixed configuration blocks in hardware, the usage is mainly for the translation between the application interface and the transaction layer. As a result, the rest of an FPGA design could be more flexible in terms of routing and resource usage.

When adding a PCIe device to an embedded system, the primary concerns are the availability of a PCIe controller in the SoC and the required software and driver to interact with a custom-built device. A recent high-end SoC is more likely to be equipped with such a controller due to its popularity, leaving the software the only issue on the SoC side. Besides, the availability of a PCIe controller on the FPGA is often restricted to mid to high-end devices.

#### 2.1.2 RapidIO

RapidIO is another high-performance packet-based interconnect protocol designed to link up various devices in a system. Initially being one of the best interconnect options for embedded systems [12], the protocol has evolved to become a general way to link up devices at the chip and board level and is commonly used in high-performance computer designs where bandwidth and latency is crucial [13].

A RapidIO network is constructed from connected devices called the endpoints and the switches. The physical connection between the device and the network is defined as the link, and the version 1 of RapidIO offers 1.25 GT/s across each lane present in the link which could consist of up to four lanes [12]. Communication is carried out on a point-to-point basis that is similar to a local Ethernet network, and the transaction packet is sized 268 bytes of which 256 bytes make up the user payload [10]. Considering that the serial communication uses 8b/10b encoding, the resultant minimum throughput is about 119 MB/s. Similar to the PCIe interface, newer versions of RapidIO also offer improvements in bandwidth.

At the device level, RapidIO is structured similarly to the PCIe; the controller is divided into three layers of abstraction, the logic layer, the data link layer and the physical layer. The logic layer converts application requests and responses into standardised RapidIO packets. The data link layers handle the acknowledgement-based communication with the target device in the network. Lastly, the physical layer realises the transaction in the forms of electrical signals over the links.

Many mid-range and high-end FPGA devices are RapidIO ready when they are equipped with the essential transceivers, and vendors also offer complete solutions with all layers mentioned above and an application interface to allow RapidIO to be integrated with user logic. However, the RapidIO solutions are usually resource hungry; for example, the instantiation of such IP would require more than 10000 adaptive logic modules (ALM) and 10000 dedicated registers on Intel Cyclone V FPGA which is about 10% of the total available logic for the highest density device in the Cyclone V series [14]. Hence, the implementation of the RapidIO interface would practically only make sense for the high-density devices which are usually

no economical choice for embedded system. Also, commercial SoCs for embedded systems usually do not contain a RapidIO controller, and thus the incorporation of RapidIO requires external physical layer (PHY) chips that are usually attached to the PCIe port of the SoC [14]. Such an approach generally complicates the system and adds more cost.

#### 2.1.3 Gigabit Ethernet

Ethernet is the most widely used interconnect technology to link up multiple computing systems, especially with the introduction of Gigabit Ethernet which by definition provides 1 Gb/s bandwidth. For video streaming applications, this bandwidth is often sufficient, and many camera devices uses Ethernet as the external interface [15].

According to the Open System Interconnect (OSI) model, the Ethernet defined by IEEE 802.3 covers the functions in layer 1 and layer 2 of the model; the physical layer and the data link layer. The third layer, the network layer, handles the routing of the packet in the network, and layer 4, the transport layer is responsible for host-to-host communication [16]. As each layer adds its header to the data packet coming from a higher layer in the hierarchy, the overhead increases. For a typical User Datagram Protocol (UDP) packet with priority tagging at the link level, there is 66-byte packet overhead; when the data payload is 256 bytes, it results in an effective bandwidth of about 99 MB/s. This means that the communication efficiency of Ethernet is less than that of PCIe or RapidIO, also considering there is no multi-lane configuration for a single Ethernet connection. Moreover, as only the first and second layers are implemented in hardware, the actual bandwidth in the application could be reduced further as the software adds significant delays to the data path. In the worst case, the real bandwidth could be only 30% of the theoretical 125 MB/s [10].

Due to its wide availability, Ethernet, especially the Gigabit Ethernet variant has been used extensively to enable communication with an FPGA [17–19]. The IP for the Ethernet media access controller is also available from several vendors [20]. Table 2.2 summaries the resource usage of such IP in the Intel Cyclone V FPGA.

| IP Core                          | Settings                          | FIFO<br>Depth<br>(bits) | LE   | LR   | Memory<br>(M10K) |

|----------------------------------|-----------------------------------|-------------------------|------|------|------------------|

| 10/100/1000 Mbps<br>Ethernet MAC | MII/GMII Full-<br>and half-duplex | 2048×32                 | 3644 | 5340 | 27               |

| 10/100 Mbps<br>Small MAC         | MII Full- and<br>half-duplex      | $2048 \times 32$        | 1539 | 2295 | 21               |

| 1000 Mbps<br>Small MAC           | RGMII<br>Full-duplex only         | $2048 \times 32$        | 1265 | 2060 | 20               |

**Table 2.2:** Triple speed Ethernet IP resource usage on Cyclone V GX in terms of logic elements (LE), logic registers (LR) and memory blocks [20].

Notably, as the IP only covers up to layer 2 in the OSI model, user logic has to implement the protocols used in the other layers [21, 22]. This could pose a design challenges on the FPGA side, whereas on the ARM side, a complete software stack is often implemented in the operating system. Moreover, because Ethernet is widely used and often an essential part of a computer system, the software development could be eased by various verified libraries.

Externally, PHY chips are required to transmit the packets over electrical links, and considerable space on and off the PCB has to be allocated to them and related passives for both ends of an Ethernet connection. Moreover, because the Ethernet usually concerns a chassis level connection that is made by an electrical cable to link up components residing in separated chassis using two RJ45 type plugs and sockets, an onboard connection would result in non-standard setup and create other hardware design challenges.

#### 2.1.4 USB

The Universal Serial Bus (USB) is commonly used for connecting peripheral devices to a PC. From the initial support of the link speeds of 1.5 Mb/s and 12 Mb/s, the bus has been developed to support up to 20 Gb/s in the double lane configuration of USB 3.2 Gen 2. Its usage as an interface between the FPGA and SoC has proven to be viable in many cases [23, 24].

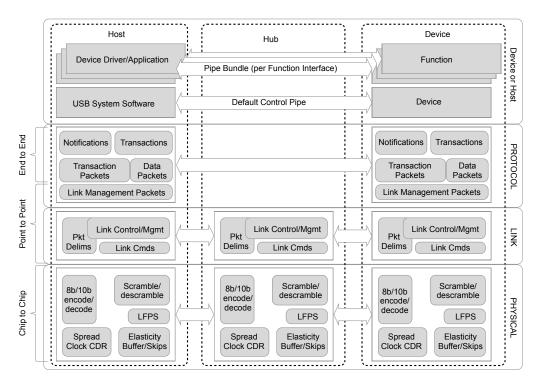

Figure 2.1: Communication model for USB [25].

Unlike previously mentioned interconnects, there can be only one host or master controller within a USB network at a time, and all communication is initiated by the host controller. As shown in Figure 2.1, the communication protocol is divided into four layers. While the application and system software work with USB pipe at the topmost layer, the packet management is handled by the protocol layer. USB packets can have the following types:

- Link Management Packet

- Transaction Packet

- Data Packets

- Isochronous Timestamp Packets

Apart from the Data Packet which is constructed from the user data and a 16-byte header, all other types of packets provide control and status information between the host and the device. A transaction has to be initiated by a Transaction Packet before any data goes onto the bus.

Since the USB bus must be driven by a PHY, it is necessary to include an external chip to enable the FPGA to access the USB. Such a chip often provides a

first-in-first-out (FIFO) interface which can be connected to regular I/O ports on an FPGA, and user logic is required to implement the control logic and interface it with the application. As a result, the throughput is very much limited by the FIFO interface of the chip assuming ideal implementation of FPGA logic, but such restrictions does not pose any bottleneck for applications like video streaming. For example, the FTDI FT601, a USB 3.0 to FIFO interface bridge chip, is measured to provide a maximum data rate of 363 MB/s [24], which is more than enough bandwidth for full HD video streaming according to the calculation in Chapter 1.

Most embedded SoCs are equipped with a version of USB host controllers, however, only the newer ones will be equipped with a USB 3 which can provide the sufficient bandwidth mentioned before. Generally, if a USB 2, which offers about ten times less throughput compared to USB 3, is used, it is necessary to reduce the frame size and frame rate to produce a satisfactory stream [26].

#### 2.1.5 The Simple Serial Protocols

Besides the protocols mentioned above, it is possible to use a simple serial protocol, such as the Inter-integrated circuit (I2C), communication protocol of the Universal asynchronous receiver-transmitter (UART) and Serial peripheral interface (SPI), to interface an FPGA device. While these protocols are commonly used in embedded systems to connect external sensors, memory and other devices, the throughput offered is significantly less than that from the previous three protocols. The maximum throughput of I2C is rated at 5 Mb/s [27]. On the other hand, there is no restraint in the maximum interface clock frequency for UART and SPI theoretically, but their transfer rate is restricted by where the controllers are placed in the system. Protocol-wise, in UART communication, every byte is wrapped with a start bit, a stop bit and an optional parity before sent over an asynchronous bus, and for SPI communication, at every configured edge of the SPI clock, a data bit could be transmitted from the master to the slave as well as from the slave to the master. Hence, potentially both protocols could yield a very high bandwidth when the controller uses a high frequency clock. However, in most implementations of the

controller, the controller's clock is divided down from that of the interconnect to which the controller is attached. Practically, the controllers are usually parts of the slow peripheral domains which results in their limited throughput. For example, in the AM3358 SoC, both the SPI and UART controllers are in the domain whose clock frequency is 48 MHz, resulting in a maximum UART rate of 3.69 Mbps and an SPI rate of 48 Mbps when acting as a master device [28]. Therefore, when video streams are delivered through these interfaces, significant reduction in frame size is needed for a reasonable frame rate.

#### 2.1.6 Custom memory interface

A custom memory interface is often built from simple interfaces consisting of a parallel data/address bus and some control signals; for example, the flash memory interface and the static random-access memory (SRAM) interface. Unlike the previous options, due to the lack of standardization, it is left to the designer to establish the communication with appropriate timing settings. Due to its parallel nature, such a memory interface can be established as a low-cost and low-complex solution since it often only needs direct electrical links between devices. Similar to all other parallel interfaces, the throughput of such an interface is determined by the width of the data bus and the frequency of the clock that synchronises the data transfer. As an example, for 16-bit data bus clocked at 100 MHz, it is possible to achieve 200 MB/s maximum in theory, which is comparable to all previous interface options. Often dedicated parallel memory bus interfaces are available on microprocessors. For example, a flash memory controller features on many ARM SoC, and accessing the attached memory devices by memory instructions, and thus requiring a minimal or no software driver. The main challenge of a parallel bus solution lies the in the design of the FPGA bridge module, which translates between the memory interface and the FPGA system interface signals. The quality of this translation affects the performance of the solution, and is subjected to the hardware and corresponding designs.

#### 2.1.7 Communication in the SoC FPGA

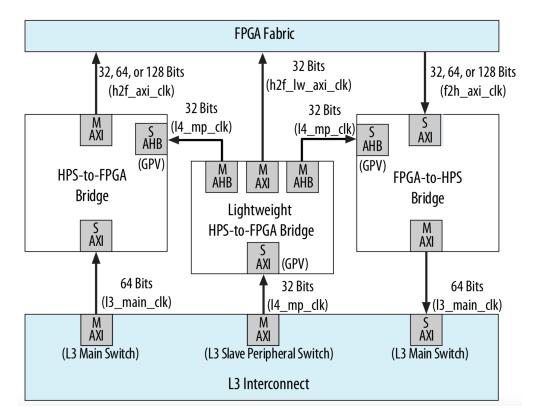

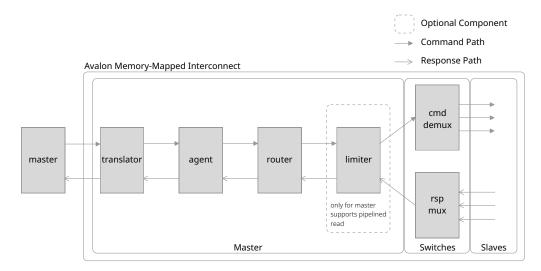

While the above interfacing options could be used to link up a processor with an external FPGA, FPGA devices exist with an integrated hard processor system (HPS); such an FPGA device has a portion of its logic hard-coded to create a typical SoC. The HPS communicates with the rest of the configurable logic via dedicated bridges. For the Intel SoC FPGA devices, four types of bridges are available to meet different communication requirements. As shown in Figure 2.2, both the HPS-to-FPGA and FPGA-to-HPS bridge are connected to the HPS's system interconnect via a 64-bit data port and runs at a maximum frequency of 400 MHz, while the lightweight HPS-to-FPGA bridge connects to the 32-bit data port of L4 interconnect which runs at 100 MHz maximum. The bandwidth offered by the former eliminates the potential bottleneck at the interface between a conventional SoC and FPGA, whereas the latter ensures side-effect-free transactions.

Moreover, in a SoC FPGA system, an SDRAM controller is shared between

Figure 2.2: Bridges available on a Intel SoC FPGA [29].

the HPS and the reconfigurable fabric. The controller can be accessed via a 64-bit data bus using a CPU, and a data bus of width up to 256 bits using the FPGA fabric. The shared memory can be used to exchange information without actually moving the data, thus providing an efficient way of communication.

#### 2.1.8 Summary

The SoC FPGA is an excellent choice to provide a direct solution to the problem of introducing an FPGA device to embedded systems but generally suffers from limited FPGA resources and the lack of advanced components in the HPS. For example, a GPU; which is commonly found in a commercial SoC; is not present in a SoC FPGA device, and the maximum density of the reconfigurable logic is about one third compared to regular models. When considering interfacing an external FPGA device with an ARM SoC, the following technologies are viable if high bandwidth is demanded: the PCIe, RapidIO, Gigabit Ethernet, USB 3 and possibly a custom interface via a memory controller. As Table 2.3 compares them qualitatively based on the discussion presented previously in the chapter, it could be seen although the use of a custom interface is heavily dependent on the available memory controller and its interface, the solution is feasible with a good implementation. Through the following chapters, the thesis will prove the use of a custom interface via flash

| Technology                 | Supporting<br>Circuitry | FPGA<br>Resource<br>Usage | Max<br>Throughput | SoC<br>Driver<br>Effort |

|----------------------------|-------------------------|---------------------------|-------------------|-------------------------|

| PCIe                       | None if linked directly | Minimum                   | Medium            | High                    |

| RapidIO                    | External PHY            | Maximum                   | Fastest           | High                    |

| Ethernet                   | External PHY            | Medium                    | Slowest           | Low                     |

| USB 3                      | External bridging chip  | Minimum                   | Medium            | Low                     |

| Custom Memory<br>Interface | None                    | Minimum                   | Medium            | None                    |

**Table 2.3:** Comparison between interfacing options for SoC with an external FPGA.

memory controller although may not be the fastest, but is one of the most efficient way for interfacing because of its ease to use and the bandwidth provided.

# 2.2 System Interface

For complicated FPGA designs, components are often connected at system level via memory-mapped protocols, so each component can be accessed via its assigned address. For such purpose popular memory-mapped protocols often provide an open specification. Examples are the ARM Advanced Microcontroller Bus Architecture (AMBA) and WISHBONE, and vendor specific interfaces such as the Intel Avalon memory-mapped (AVMM) protocol. This section summarises these system interfaces in terms of their capability, complexity and configurability.

#### 2.2.1 AMBA

The ARM AMBA specification includes several on-chip interconnect protocols for connecting various system components in an embedded SoC, some of which are also implementable in FPGA system designs. Each protocol offers different benefits to cover a wide range of applications. Some protocols which are relevant to a system interface in an FPGA are the following:

Coherent Hub Interface (CHI) is the latest protocol from ARM to provide the best performance with coherency support. It uses a layered model; similar to PCIe and RapidIO; to offer more flexible topologies. It also includes a mechanism of Quality of Service to better access the interaction of components. [30]

Advanced eXtensible Interface (AXI) is one of the more widely used buses in embedded application SoCs. It is a multi-channel generic interface with burst transaction. Major FPGA vendors such as Intel and Xilinx offer IPs with the AXI interfaces to create a system-level connection. [31, 32]

- **AXI Coherency Extension (ACE)** is the AXI protocol with additional coherency support. It offers a way for connecting coherent processors with memory controllers before the development of the CHI. [31]

- Advanced High-Performance Bus (AHB) is one of the main system-level interfaces used in micro-controllers. Unlike the AXI interface, the AHB is a shared interface with burst transaction support. The main advantages of the bus over the AXI are its lower power consumption and latency. [31]

- Advanced Peripheral Bus (APB) offers a way for connecting peripheral components with low or no demand in bandwidth. It is a non-burst interface with very low complexity and power consumption. [33]

While there is no implementation for the CHI at current stage, it is possible to meet any performance demands with AXI and AHB. In terms of configuration, the AHB can have a data bus up to 1024 bits and a maximum burst size of 16 words, while the AXI allows more words in a burst transaction with the same data bus configuration. [31]

#### 2.2.2 WISHBONE

The WISHBONE [34] is an interconnect specification from OpenCores, aiming to provide a standardised data exchange protocol for custom systems. It focuses on simplicity and low resource usage, with a reasonable performance. Similar to AHB, it supports the connection of multiple masters and slaves to a shared bus. Transaction wise, it supports burst and pipelined transaction for improved throughput. However, it only supports a configuration of data bus up to 64 bits, which is rarely sufficient in system with a large amount of data flow.

#### 2.2.3 AVMM interface

The AVMM interface [35] is proprietary protocol from Intel featuring an interface built around a shared bus with configurations for both pipelined and burst transactions. Its data bus width is configurable up to 1024 bits with a burst size of up to 1024 words. The AVMM interface also uses a slave-side arbitration scheme to allow multiple masters to perform transactions at the same time.

## 2.2.4 Summary

In constructing a high-performance system featuring an FPGA, it is obvious that the AXI, AHB or AVMM interfaces are better options compared to the rest. Within the setting of embedded vision systems that put limits on the complexity and power budget whilst working with restraints set by both hardware and software availability, the work focuses on the Avalon memory-mapped protocol, because the target device is from Intel and most existing IPs are only compatible with the AVMM interface.

From the comparison made in Chapter 2, it could be seen that a custom memory interface would be an efficient way to interface an ARM SoC and FPGA, potentially providing both simplicity and performance. One of the aims of the research is to implement such an interface on an in-house platform, named the ARMflash. This chapter will firstly give an overview of this particular platform, including available options for SoC-FPGA interfacing. Secondly, the details of the protocols on both sides of a custom interface are highlighted, and the work on the bridge is discussed.

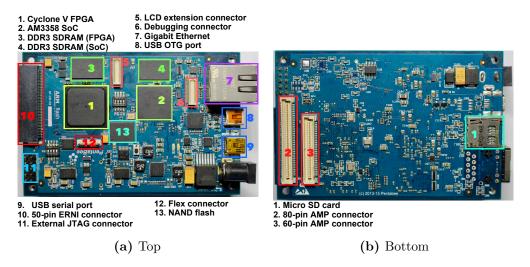

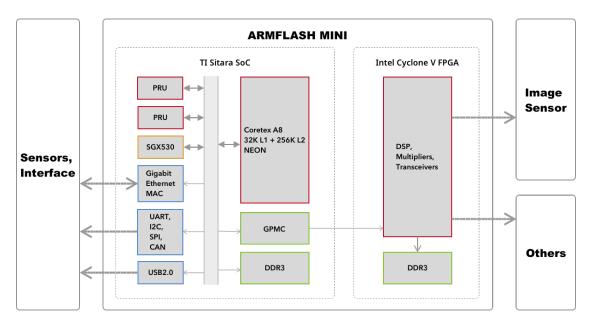

# 3.1 ARMflash overview

The ARMflash is a platform developed in-house, modelling the popular BeagleBone series. As shown in Figure 3.1, at its core, the ARMflash has a Texas Instrument's AM3358 SoC, and an Intel Cyclone V FPGA (5CGXFC7C6U19C6N). Both processors have dedicated 512 MB DDR3 SDRAM attached, providing storage for large data sets in computation. In terms of connectivity, the platform exposes most of the FPGA I/O via AMP and ERNI connectors, coupled with the communication and debug interfaces from the SoC; such as the Gigabit Ethernet, USB, serial ports. The platform provides both SDMMC and NAND flash as persistent storage options.

**Figure 3.1:** The ARMflash platform.

#### 3.1.1 ARM SoC

The main processors in the AM3358 SoC consist of a Cortex A8 ARM processor, a PowerVR SGX530 GPU, and two Programmable Real-time Units (PRUs). The Cortex A8 CPU is a dual issue super scalar processor, which means it can execute two instructions simultaneously most of the time. It is also equipped with an Advanced Single instruction multiple data (SIMD) Extension (NEON), which can handle a combined maximum data width of 128 bits. The processor performs computation with a 13-stage integer pipeline and a 10-stage NEON pipeline. It is configured with  $32 \times 2^{10}$  bytes (32.8 KB) 4-way set associative level 1 (L1) cache and  $256 \times 2^{20}$  bytes (268.4 KB) 8-way set associative level 2 (L2) cache for efficient data fetching from memory. On the other hand, the PowerVR SGX530 is a 3D hardware accelerator supporting OpenGL ES 2.0, it has a computation capability of 1.6 Giga FLOPS (floating-point operation per second) when running at 200 MHz. Lastly, there are two PRU subsystems providing substantial DSP capability due to their support of the multiply-accumulation instruction.

Supporting the processors, the AM3358 SoC has an enhanced DMA engine to enable offloading the CPU from large memory transactions. It also consists of many peripheral modules including Gigabit Ethernet MAC, USB 2, general-purpose memory controller (GPMC) and various serial interfaces such as the UART and SPI.

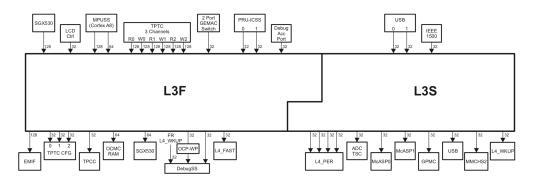

**Figure 3.2:** AM3358 L3 Topology [28].

Memory-mapped system components of the SoC form the level 3 (L3) and level 4 (L4) memory systems, although components are accessed like a memory device, L3 and L4 are not physical memories but referred as an interconnect. As shown in Figure 3.2, the L3 interconnect in the AM3358 runs at two different speeds; the fast domain operates at 200 MHz whereas the slow domain runs at 100 MHz maximum. All processors that are connected to the fast domain with a substantial bus width, and notably the more demanding ones; for example, the CPU and GPU; have a connection data width of 128 bits to ensure their performance. On the other hand, all peripheral components are connected to the slow domain and some slower ones are attached to the more distanced level 4 (L4) interconnect. As discussed in Chapter 2, the components that could be utilised to interface an external FPGA device are the Ethernet, USB, and the GPMC; the serial interfaces at L4 are excluded since they are clearly inferior in terms of performance in large data transfer. As shown in Table 3.1, the GPMC has great potential for being a part of a high-performance bridging solution between the SoC and the FPGA, which also resonates with previous discussions.

#### 3.1.2 FPGA

The Cyclone V GX chip is equipped with hard-logic 3.125 Gbps transceivers and external memory controller for adding additional DDR memory devices, together with PLL, DSP, multipliers and memory blocks. The FPGA is configured using the JTAG interface, both externally and via the ARM SoC. The latter is implemented

|                        | USB 2.0                       | Gigabit<br>Ethernet                | Memory<br>Controller<br>(GPMC) |

|------------------------|-------------------------------|------------------------------------|--------------------------------|

| Bandwidth              | 480 Mbps                      | 1000 Mbps                          | 1600 Mbps                      |

| Additional<br>Hardware | USB FIFO chip                 | Ethernet PHY                       | None                           |

| Access Method          | Packet based,<br>USB protocol | Packet based,<br>Ethernet protocol | Memory instructions            |

**Table 3.1:** Comparison between interfacing options available in AM3358 for connecting an external FPGA.

using general-purpose I/O lines of the SoC, and these lines are multiplexed with the external JTAG interface to give flexibility in configuring the FPGA. The FPGA's I/O is exposed via two major connectors, a 50-pin ERNI connector and 80-pin AMP connector, which allows daughter boards to be attached for extended functionalities and connection to a range of image sensors.

# 3.1.3 Applications

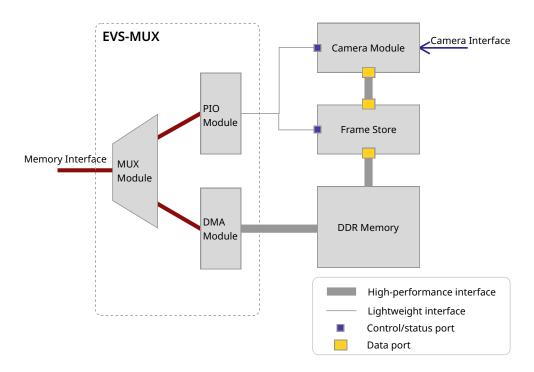

The ARMflash is a powerful embedded system, and has been part of both commercial product and research prototypes, particularly in image processing applications. For example, the FMB Oxford's BPM Nano unit uses the platform as its core to perform calculations for X-ray beams, and the Lancelot smart camera system is built around the platform with the Medipix image sensor from CERN. As shown in Figure 3.3, when building such smart camera systems with the platform, the image sensor usually feeds the digitised output data directly to the FPGA via the expansion connectors, and stream processing is performed before storing the data in the memory. The other processors in the SoC could then retrieve the data and carry out further processing before sending the result via the Ethernet. Due to this heterogeneous platform, the system designed is compact while also sophisticated and powerful.

Figure 3.3: ARMflash as part of a smart camera system.

# 3.2 Two sides of the bridge

Having overviewed the platform, this section looks at the relevant components and protocols in detail in preparation for developing a bridge solution between the ARM SoC and the FPGA via custom memory interface using the GPMC in the AM3358 and the protocols it supports, with the AVMM protocol for the FPGA.

#### 3.2.1 GPMC

Within the SoC, the GPMC is connected to the L3 slow interconnect, which operates at 100MHz, via a 32-bit data port and has direct connections to the DMA engine and the interrupt controller. Externally, the GPMC exposes a simple memory interface consisting of address and data buses with various control signals. It is capable of interfacing to non-volatile memory; such as the NAND and NOR flash; and volatile memory like the SRAM. It can address up to  $256 \times 2^{20}$  bytes (268.4 MB) per individual chip-select (3 available) and perform burst access of up to 32 bytes with a parallel data bus up to 16 bits wide.

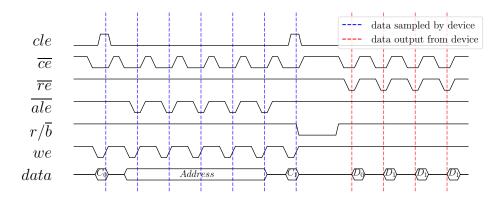

Figure 3.4: Waveform for NAND read operation.

#### Memory protocols

The memory access protocols the GPMC supports can be generally categorised into the following two; the NAND protocol and the NOR protocol.

**NAND protocol** The GPMC follows the protocol to access a NAND flash. The NAND flash is a page-oriented storage device; which means to access a memory location, the entire page which the location belongs to needs to be fetched. As shown in Figure 3.4, a typical read operation for NAND memory involves multiple cycles. Firstly, a command cycle is issued at the beginning to initiate the operation, and it is followed by address cycles which select the internal page and a second command cycle that sets the sub-command and starts the execution of the operation. Lastly, when the data is ready, all data in the selected page could be read out in sequence. Each transaction cycle, which is defined by the assertion of the chipenable signal, can communicate data of only one word whose size is determined by the interface data bus width. Hence, to exchange multiple bytes of data, multiple transactions are required. However, after the initial data, a shorter access time can also be used to obtain data more quickly. The write or program operation is carried out similarly to the read, with the exception that the data cycles happen immediately after the address cycles, and the second command cycle is issued after the data cycle to start the write process.

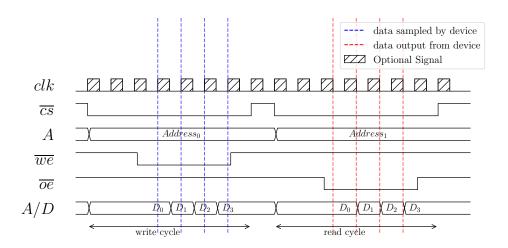

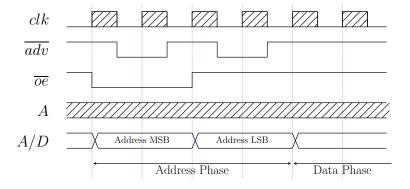

NOR protocol Different from the above NAND protocol, the NOR protocol delivers the address and data in the same cycle as shown in Figure 3.5. It supports both the NOR flash and SRAM-like devices; the two only differs by the ability to perform burst read or page read. Although the required electrical links increases due to the inclusion of the address bus, the cycle efficiency; which is defined by the ratio between the time used to deliver data and the total operating time in a transaction; increases significantly. Moreover, when accessing 16-bit devices, the ability to access multiple words in the same transaction further boost this efficiency. The protocol offers two schemes for address configuration for the memory device; the AD-multiplexing scheme and the AAD-multiplexing scheme; to reduce the number of electrical links for connection. Both schemes multiplex the address bits into the data bus, dividing a transaction cycle into two phases; an address phase when a segment of the address is delivered on the data bus, and a data phase in which data access is carried out. In the AD-multiplexing scheme, only the 16 least significant bits (LSB) are transmitted over the data bus, and the rest of the bits would still require to be sent over the address bus which is now 16 lines narrower. On the other hand, the address bus is entirely assimilated into the data bus in the AAD scheme; the address is divided into two segments, the 16 LSB and the remaining bits, and sent out in big-endian order; the most significant part is transmitted first.

When considering using the above protocols to communicate with an FPGA, the NOR protocol outperforms the NAND protocol in the following aspects:

- 1. Unlike the entirely asynchronous NAND protocol, the support of synchronous transactions in the NOR protocol fits better into FPGA design practice.

- 2. The NOR protocol provides better support for random access which is essential for accessing modules registers and memory mapped I/O in the FPGA system.

- 3. Due to its high cycle efficiency, the NOR protocol offers a higher overall throughput compared to the NAND protocol, which can also be confirmed by NOR flash's higher data rate [36].

Figure 3.5: Waveform for accessing NOR flash.

When the GPMC is configured for NAND devices access, the enabling of the prefetch and post-write engine offers significant reduction in the data delay experienced by the SoC. However, due to the inefficiency of the protocol itself, the NAND protocol is stilled considered to be inferior. Also, when using the NOR protocol, it is possible to implement similar functionalities in the FPGA if required.

#### Signals and configurations

Due to the NOR protocol's superiority mentioned earlier, it is chosen to be used for interfacing the FPGA on the ARMflash platform. After studying the GPMC's configuration and behaviour for the NOR protocol, it is found that there are challenges to interface the GPMC to an FPGA, despite being a straight-forward protocol. Since the GPMC is originally intended for the flash memory devices, it requires a bespoke IP at the FPGA side to handle all issues arisen from using it as a general-purpose communication controller. The following sections summarise the essential configurations of the GPMC for use with an FPGA and also concerns which cause design difficulties.

**Data Bus Width** Although the GPMC supports both 8-bit and 16-bit devices in the NOR protocol, it only supports burst access for the 16-bit devices [28].

Considering that the FPGA modules would often have 32-bit registers, to access such registers, the GPMC needs to be able to access at least four bytes in one transaction for efficient communication; otherwise, the access to a single register would require multiple transactions which results in significantly longer access time. Such access which demands more than one GPMC word (16-bit) makes burst transfer essential. Besides, when configured to support 16-bit device, the GPMC can also enable address-data multiplexing to spare some address lines and thus reduce PCB area usage. Strictly speaking, due to the intention of supporting both read and write, the device which the FPGA will emulate is the SRAM device as NOR flash devices does not support burst write although they share a similar waveform.

#### (a) AD-multiplexing mode

(b) AAD-multiplexing mode

**Figure 3.6:** The address phase waveforms of the GPMC NOR protocol configured in (a) AD-multiplexing (b) AAD-multiplexing mode.

Addressing mode As mentioned before, both the AD-multiplexing and AAD-multiplexing schemes provide a solution to reduce board area usage for routing the address signals. However, it is achieved at the cost of the reduction in cycle efficiency. As shown in Figure 3.6a and 3.6b, the use of AD-multiplexing scheme would require at least one clock cycle for the address phase, and at least three clock cycles are needed for the AAD-multiplexing scheme due to the toggling of the control signal. However, as the sampling of the address bus has to take one clock cycle, it is possible to align this sampling to the same cycle used by the address phase in the AD-multiplexing scheme, making the scheme produce no extra overhead. Hence, the GPMC is configured to use such scheme to provide the maximal addressable space when communicating with the FPGA.

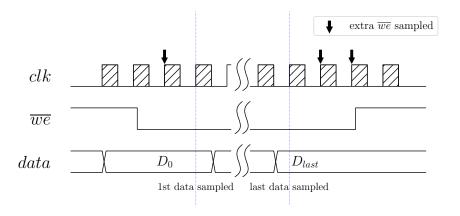

Behaviour of the enable signals The GPMC uses the write-enable and outputenable signals to control the direction of the data in the NOR protocol. As for conventional flash memory devices, the transaction length is limited by its page size, and thus, the duration of these signals' assertion does not have to correspond to the length of data. For example, in synchronous mode, assuming data is sampled or captured at each rising edge, a controller does not require to assert the control signals for four clock cycles to access four words of data. As a result, there is no way to ensure that the control signals and the data have the same duration in a

Figure 3.7: The relationship between GPMC data access and write-enable.

transaction. As shown in Figure 3.7, it is possible for the GPMC to assert the control signals before the start of the access and also after all data has been accessed. It is possible to end the transaction immediately after the last data so that due to the gated clock the last assertion of the control signal would not be observed, but it requires the device not to register any of them which is not a good practice for FPGA designs. This behaviour creates difficulty when these GPMC signals control the sampling and output of data especially at the end of the cycle. When using the write-enable to sample the incoming data, the expectation that the signals are de-asserted at the edge the last data is captured cannot be met. As the transaction length is dynamically controlled by request to the controller, it is also not the best practice to assume when data is valid in the cycle. Therefore, it requires the bridge on the FPGA side to correct the alignment between the control signals and the data.

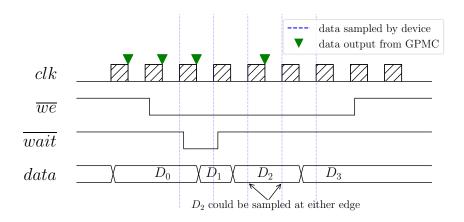

Behaviour of the wait-request The GPMC includes a wait signal which can be used by the device to dynamically delay the sampling and output of data by the controller. The use of the signal could potentially increase the throughput and allow better flow control; it allows the device to return the data faster when condition allows by defining a short access time, and it could stall the GPMC when the device could not cope with either the read or write. The wait signal can be interpreted as a valid signal asserted only during valid output for a read transaction, but for

Figure 3.8: The behaviour of the GPMC wait signal.

write transactions, the effect of the wait can only be seen one data cycle later. As shown in Figure 3.8, due to the data output delay of approximately one clock cycle when configuring to use the fastest clock [28], the wait has to be asserted at least two cycles earlier by the device before it can no longer accept more data. Although such behaviour could be handled trivially by conventional memory devices, when designing a bridge between the FPGA and the GPMC, additional synchronisation is necessary for translating the behaviour of the FPGA into the correct wait signal for the GPMC. Moreover, it is observed the wait signal also controls the end of a write transaction, at the edge when the last data is sampled by the device, GPMC samples the wait to ensure that the device correctly acknowledges the last data so that it can finish the transaction.

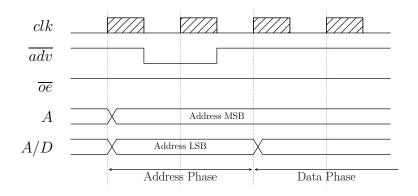

#### 3.2.2 AVM

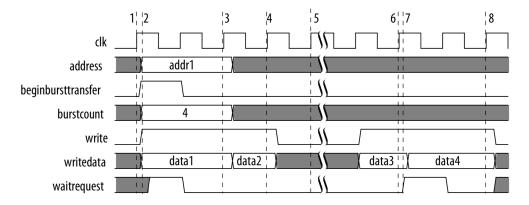

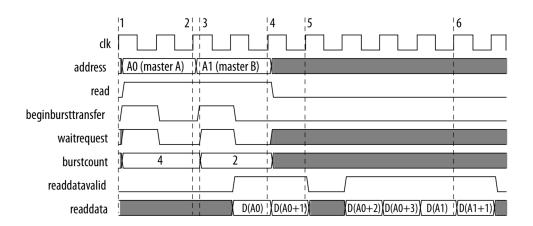

On the FPGA side, the designed bridge interacts with the rest of the system via AVMM interface. In order for the bridge to send out transactions to the FPGA interconnect, it is required to behave as an Avalon Memory-mapped Master (AVM). Figures 3.9 and 3.10 show typical waveforms for burst transactions of read and write from such a master. For a burst read transaction, the timing could be divided into two phases; the command phase and the data phase, and the read data could be asynchronously returned by the slave; the time between the read command and the first data is variable, and multiple read command could be queued before

Figure 3.9: Waveform for burst AVM write [37].

Figure 3.10: Waveform for burst AVM read [37].

the completion of the previous ones. Hence, the throughput of the connection could be significantly improved as a result of the pipelined transfer. Besides, the AVM also supports none-burst pipelined transaction and simple fixed-wait-time transaction, and they are generally less capable in term of performance, but the equipping master can be implemented in much simpler logic due to the reduction in electrical links and control logic.

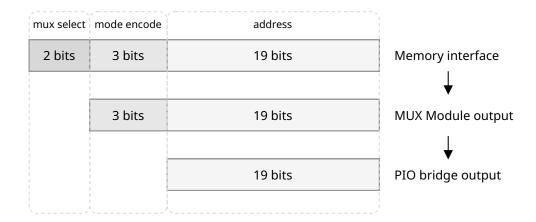

Interface-wise, the command and data buses use separated links for read and write transactions, but it is possible to merge the parameter bus which generally consists of the address, burst-count and byte-enable. As a result of the merging, a unified master with less logic could be designed to handle both read and write serially. Although in this case the concurrency between read and write is sacrificed, the actual loss in performance is considered negligible due to the short read command phase and the separation of data channels. Besides, the system interconnect is usually generated automatically by software tools, and the AVM is connected accordingly to the generated logic depending on its capability as shown in 3.11. As the interconnect master logic is generated for each master connected to the interconnect, the merging could result in the reduction of logic and the number of switches. Similar to the memory interface of the GPMC, the AVMM interconnect uses word-based addressing internally; although the master and slave could be configured to use byte address, transactions are converted via truncation. As a result, unaligned access which the address is not divisible by the length needs to be

3.3. Previous work

Figure 3.11: AVM and generated AVMM interconnect.

handled by manipulating the byte enable, and this is not performed by the generated interconnect; the user-designed controller has to handle the alignment when required.

#### 3.3 Previous work