# 3D MODELING AND INTEGRATION OF CURRENT AND FUTURE INTERCONNECT

## TECHNOLOGIES

## A DISSERTATION IN Electrical and Computer Engineering and Physics

## Presented to the Faculty of the University of Missouri-Kansas City in partial fulfillment of the requirements for the degree

# DOCTOR OF PHILOSOPHY

## by ABDUL HAMID BIN YOUSUF

B.Sc. University of Dhaka, 2010 M.S. University of Dhaka, 2012

> Kansas City, Missouri 2021

© 2021

# ABDUL HAMID BIN YOUSUF

ALL RIGHTS RESERVED

# 3D MODELING AND INTEGRATION OF CURRENT AND FUTURE INTERCONNECT TECHNOLOGIES

Abdul Hamid Bin Yousuf, Candidate for the Doctor of Philosophy Degree University of Missouri-Kansas City, 2021

#### ABSTRACT

To ensure maximum circuit reliability it is very important to estimate the circuit performance and signal integrity in the circuit design phase. A full phase simulation for performance estimation of a large-scale circuit not only require a massive computational resource but also need a lot of time to produce acceptable results. The estimation of performance/signal integrity of sub-nanometer circuits mostly depends on the interconnect capacitance. So, an accurate model for interconnect capacitance can be used in the circuit CAD (computer-aided design) tools for circuit performance estimation before circuit fabrication which reduces the computational resource requirement as well as the time constraints. We propose a new capacitance models for interconnect lines in multilevel interconnect structures by geometrically modeling the electrical flux lines of the interconnect lines. Closed-form equations have been derived analytically for ground and coupling capacitance. First, the capacitance model for a single line is developed, and then the new model is used to derive expressions for the capacitance of a line surrounded by neighboring lines in the same and the adjacent layers above and below. These expressions are simple, and the calculated results are within 10% of Ansys Q3D extracted values.

Through silicon via (TSV) is one of the key components of the emerging 3D ICs. However, increasing number of TSVs in smaller silicon area leads to some severe negative impacts on the performance of the 3D IC. Growing signal integrity issues in TSVs is one of the major challenges of 3D integration. In this paper, different materials for the cores of the vias and the interposers are investigated to find the best possible combination that can reduce crosstalk and other losses like return loss and insertion loss in the TSVs. We have explored glass and silicon as interposer materials. The simulation results indicate that glass is the best option as interposer material although silicon interposer has some distinct advantages. For via cores three materials - copper (Cu), tungsten (W) and Cu-W bimetal are considered. From the analysis it can concluded that W would be better for high frequency applications due to lower transmission coefficient. Cu offers higher conductivity, but it has larger thermal expansion coefficient mismatch with silicon. The performance of Cu-W bimetal via would be in between Cu and W. However, W has a thermal expansion coefficient close to silicon. Therefore, bimetal Cu-W based TSV with W as the outer layer would be a suitable option for high frequency 3D IC. Here, we performed the analysis in terms of return loss, transmission coefficient and crosstalk in the vias.

Signal speed in current digital systems depends mainly on the delay of interconnects. To overcome this delay problem and keep up with Moore's law, 3D integrated circuit (vertical integration of multiple dies) with through-silicon via (TSV) has been introduced to ensure much smaller interconnect lengths, and lower delay and power consumption compared to conventional 2D IC technology. Like 2D circuit, the estimation of 3D circuit performance depends on different electrical parameters (capacitance, resistance, inductance) of the TSV. So, accurate modeling of the electrical parameters of the TSV is essential for the

design and analysis of 3D ICs. We propose a set of new models to estimate the capacitance, resistance, and inductance of a Cu-filled TSV. The proposed analytical models are derived from the physical shape and the size of the TSV. The modeling approach is comprehensive and includes both the cylindrical and tapered TSVs as well as the bumps.

On-chip integration of inductors has always been very challenging. However, for sub-14nm on-chip applications, large area overhead imposed by the on-chip capacitors and inductors has become a more severe concern. To overcome this issue and ensure power integrity, a novel 3D Through-Silicon-Via (TSV) based inductor design is presented. The proposed TSV based inductor has the potential to achieve both high density and high performance. A new design of a Voltage Controlled Oscillator (VCO) utilizing the TSV based inductor is also presented. The implementation of the VCO is intended to study the feasibility, performance, and real-world application of the proposed TSV based inductor.

#### APPROVAL PAGE

The faculty listed below, appointed by the Dean of the School of Graduate Studies, have examined a thesis titled "3D Modeling and Integration of Current and Future Interconnect Technologies," presented by Abdul Hamid Bin Yousuf, candidate for the Doctor of Philosophy degree, and certify that in their opinion it is worth of acceptance.

### Supervisory Committee

Masud H. Chowdhury, Ph.D., Committee Chair Department of Electrical and Computer Engineering

> Paul Rulis, Ph.D. Department of Physics

Ghulam Chaudhry, Ph.D. Department of Electrical and Computer Engineering

Deb Chatterjee, Ph.D. Department of Electrical and Computer Engineering

Baek-Young Choi, Ph.D. Department of Computing and Engineering

# CONTENTS

| ABSTRACT              | iii  |

|-----------------------|------|

| LIST OF ILLUSTRATIONS | .xi  |

| LIST OF TABLES        | .xix |

| CHAPTER 1 INTRODUCTION                                                             |

|------------------------------------------------------------------------------------|

| 1.1 Interconnect Modeling1                                                         |

| 1.2 3D Integration                                                                 |

| 1.3 Organization                                                                   |

| 1.4 Dissertation Objective                                                         |

| CHAPTER 2 BACKGROUND OF CAPACITANCE MODELING OF ON-CHIP                            |

| INTERCONNECT7                                                                      |

| 2.1 Introduction                                                                   |

| 2.2 Interconnect Geometry                                                          |

| 2.3 Interconnect Model 10                                                          |

| 2.4 Resistance Model 11                                                            |

| 2.5 Capacitance Model 12                                                           |

| CHAPTER 3 ACCURATE MODELING OF INTERCONNECT CAPACITANCE IN                         |

| MULTILEVEL INTERCONNECT STRUCTURES FOR SUB 22NM TECHNOLOGY 17                      |

| 3.1 Introduction 17                                                                |

| 3.2 Analyzing Electric Field Distribution in Multi-Layer Interconnect Structure 17 |

| 3.2.1 Single Interconnect Line Over A Ground Plane 17                              |

| 3.2.2 Capacitance Model for A Single Interconnect Line Over the Ground Plane 18    |

| 3.2.3 Three Interconnect Lines Between Two Ground Planes                        |

|---------------------------------------------------------------------------------|

| 3.2.4 Capacitance Model of Multiple Lines Between Two Ground Planes             |

| 3.2.5 When the Spacing Between The Interconnect Is Greater Than The Oxide       |

| Thickness $(S > \frac{3}{2}T)$                                                  |

| 3.2.6 When The Spacing Between The Interconnect Is Less Than The Oxide          |

| Thickness $(S < \frac{3}{2}T)$                                                  |

| 3.2.7 Capacitance Model of Multiple Lines Over a Ground Plane (Special Case) 36 |

| 3.3 Model Validation                                                            |

| 3.4 Summary                                                                     |

| CHAPTER 4 ANALYSIS OF DIFFERENT MATERIALS AND STRUCTURES FOR                    |

| THROUGH SILICON VIA AND THROUGH GLASS VIA IN 3D INTEGRATED                      |

| CIRCUITS                                                                        |

| 4.1 Introduction                                                                |

| 4.2 Result and Analysis                                                         |

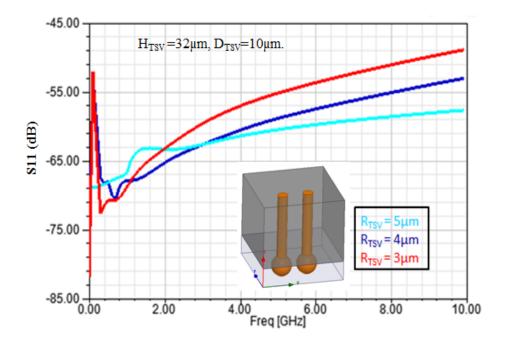

| 4.2.1 Return Loss in TSV For Different Materials 48                             |

| 4.2.2 TSV Transmission Coefficient or Insertion Loss for Different Materials 52 |

| 4.2.3 Near End and Far End Crosstalk                                            |

| 4.2.4 Radius Variation                                                          |

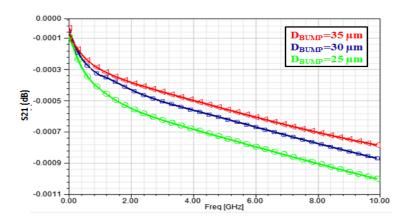

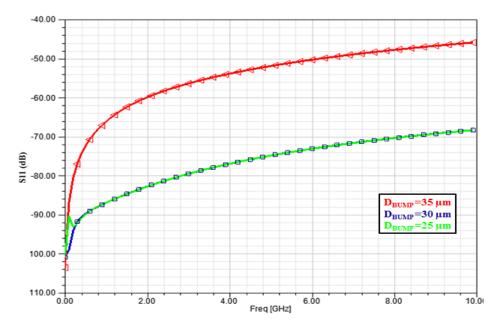

| 4.2.5 Bump Dimension Variation                                                  |

| 4.2.6 Effects of Multiple Layers of TSVs                                        |

| 4.3 Summary                                                                     |

| CHAPTER 5 IMPACTS OF DIFFERENT SHAPES OF THROUGH-SILICON-VIA                    |

| CORE ON 3D IC PERFORMANCE                                                       |

| 5.1 Introduction                                                              |

|-------------------------------------------------------------------------------|

| 5.2 Simulation Setup                                                          |

| 5.3 Result and Analysis                                                       |

| 5.3.1 Measurement of Return Loss for Different Shapes of TSVs                 |

| 5.3.2 Measurement of Transmission Coefficient for Different Shapes of TSVs 74 |

| 5.3.3 E-Field and H-Field Distribution                                        |

| 5.4 Summary                                                                   |

| CHAPTER 6 ACCURATE ELECTRICAL MODELING OF CU-FILLED THROUGH-                  |

| SILICON VIA (TSV)                                                             |

| 6.1 Introduction                                                              |

| 6.2 Modeling of TSV Capacitance                                               |

| 6.2.1 The Capacitive Model of The Bumps                                       |

| 6.2.2 The Capacitive Model of the Landing Pads of the TSVs                    |

| 6.2.3 The Capacitive Model of TSV Core                                        |

| 6.3 Modeling of TSV & Bump Resistance                                         |

| 6.4 Modeling of TSV Inductance                                                |

| 6.5 Equivalent Circuit and S-parameter for TSV Pair                           |

| 6.6 Results and Analysis                                                      |

| 6.7 Summary 104                                                               |

| CHAPTER 7 DESIGN AND CHARACTERIZE TSV BASED INDUCTOR FOR HIGH                 |

| FREQUENCY VOLTAGE-CONTROLLED OSCILLATOR DESIGN 106                            |

| 7.1 Introduction                                                              |

| 7.2 Background                                                                |

| 7.3 Optimization of TSV Inductor Performance for VCO Design       | 113 |

|-------------------------------------------------------------------|-----|

| 7.4 Voltage Controlled Oscillator Design Using TSV based inductor | 123 |

| 7.5 Analysis                                                      | 125 |

| 7.6 Summary                                                       | 127 |

| CONCLUSION AND FUTURE WORK                                        | 129 |

| REFERENCES                                                        | 133 |

| VITA                                                              | 139 |

# ILLUSTRATIONS

| FigurePage                                                                                 |

|--------------------------------------------------------------------------------------------|

| 1.1.1: IRDS prediction of (a) device scaling down (b) increasing interconnect length       |

| and (c) increasing interconnect delay [2, 3]2                                              |

| 1.1.2: Prediction for interconnect aspect ratio and pitch                                  |

| 1.2.1: 3D Integrated Circuit with TSVs, bumps and micro-bumps [2]5                         |

| 2.2.1: Geometry of Interconnect                                                            |

| 2.2.2: Metal stack of Intel's (a) 90nm and (b) 45nm process [6] 10                         |

| 2.3.1: Lumped approximation of distributed RC circuit [6] 11                               |

| 3.2.1: (a) Single interconnect line over a ground plane. The interconnect line is          |

| surrounded SiO <sub>2</sub> . (b) Electric potential (Contour) and Electric filed          |

| distribution for a single interconnect line over a ground plane                            |

| 3.2.2: (a) Fringing field lines originating from the sidewall of the interconnect line (b) |

| approximate fringing field lines originating from the top wall of the                      |

| interconnect line                                                                          |

| 3.2.3: Approximated electric field lines originating from the corner of the                |

| interconnect                                                                               |

| 3.2.4: (a) Three interconnect lines sandwiched between two ground planes. The              |

| interconnect lines are surrounded by $SiO_2$ . (b) Electric potential (Contour) and        |

| Electric filed distribution for three parallel interconnect lines between two              |

| ground planes. Here insulator thickness (T) = $0.1\mu m$ and separation (S)                |

| between adjacent interconnect is 0.1µm25                                                   |

| 3.2.5: Electric field distribution of two parallel interconnect lines over a ground plane |

|-------------------------------------------------------------------------------------------|

| for various combination of insulator thickness (T) and separation (S). (a) T =            |

| $0.1\mu m, S = 0.025\mu m, (b) T = 0.025\mu m, S = 0.1\mu m$                              |

| 3.2.6: Approximated electric field lines originating from a portion of the sidewall of    |

| the interconnect                                                                          |

| 3.2.7: Approximated electric field lines originating from a portion of the sidewall of    |

| the interconnect that ends up on the bottom portion of neighboring                        |

| interconnect                                                                              |

| 3.2.8: Approximated electric field lines originating from the bottom of the               |

| interconnect. A portion of the electric field lines ends up on the ground and             |

| the remaining part ends up on the bottom of the neighboring interconnect 33               |

| 3.2.9: Electric field generates from the corner of interconnect                           |

| 3.2.10: Electric field distribution of multiple interconnect line over a single ground    |

| plane                                                                                     |

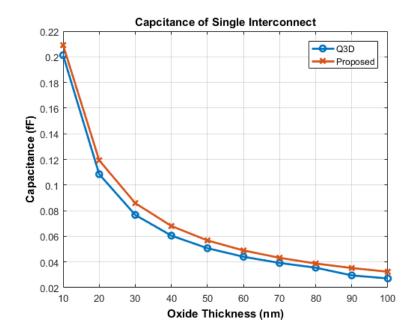

| 3.3.1: Total capacitance of single interconnect over a ground plane                       |

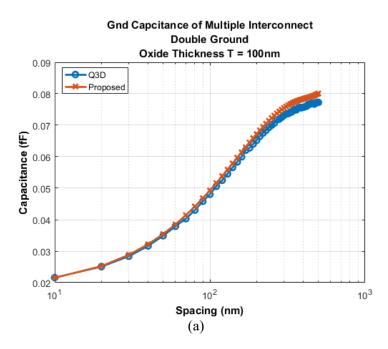

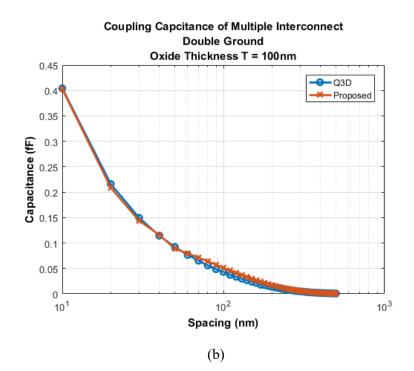

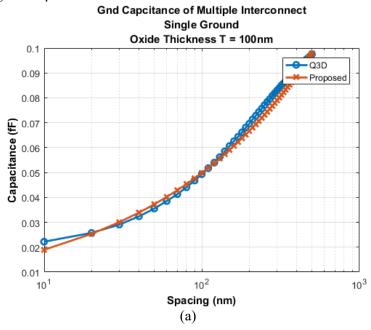

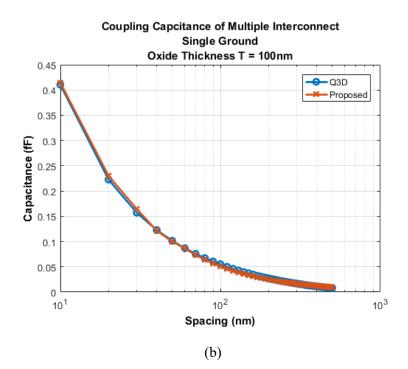

| 3.3.2: (a) Ground capacitance and (b) coupling capacitance of multiple interconnect       |

| line between two ground planes                                                            |

| 3.3.3: (a) Ground capacitance and (b) coupling capacitance of multiple interconnect       |

| line over a ground plane                                                                  |

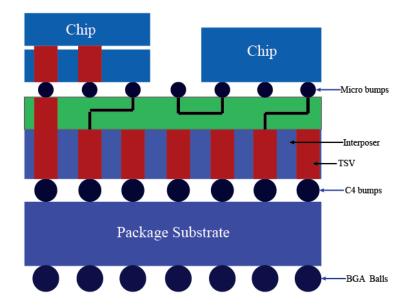

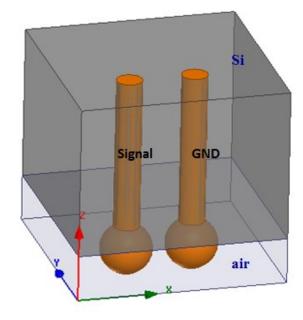

| 4.1.1: 3D IC with package substrate, TSVs and different bumps                             |

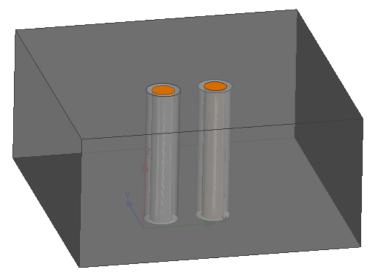

| 4.1.2: Simulation setup to measure return loss, transmission coefficient, near-end        |

| crosstalk (NEXT) and far-end crosstalk (FEXT). The distance between the                   |

| signal TSV and the ground TSV is 10µm (pitch)                                             |

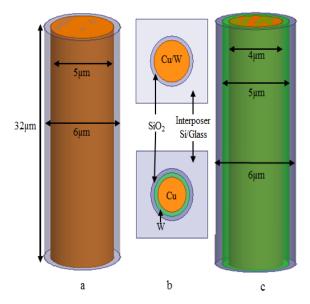

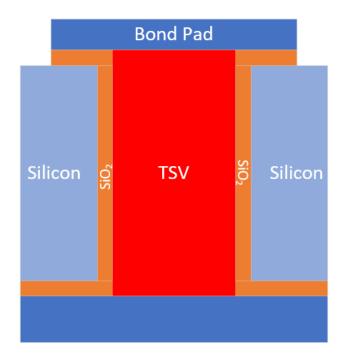

| 4.1.3: a. TSV of height 32 $\mu$ m and diameter 5 $\mu$ m with 6 $\mu$ m of SiO <sub>2</sub> layer (thickness |

|---------------------------------------------------------------------------------------------------------------|

| $0.5 \mu m)$ b. cross sectional view of Cu/W TSV (top) and bimetal (Cu-W) TSV                                 |

| (bottom) as the core surrounded by $SiO_2$ insulating layer and Si/Glass                                      |

| interposer c. TSV of height 32 $\mu$ m, Cu core with diameter 4 $\mu$ m and W layer                           |

| with thickness 0.5µm                                                                                          |

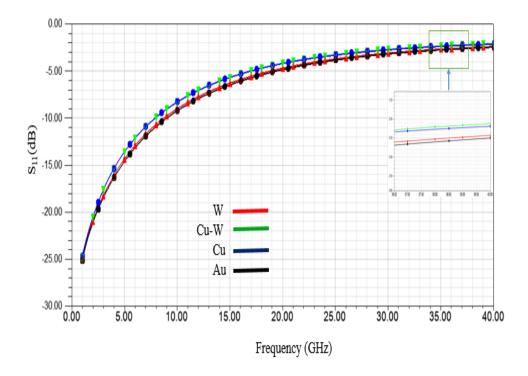

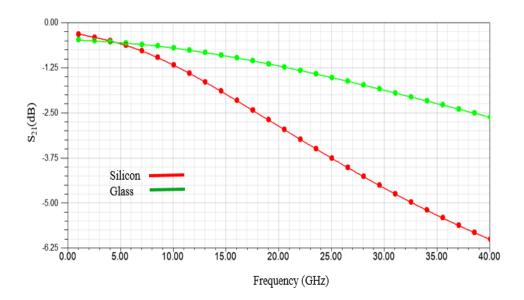

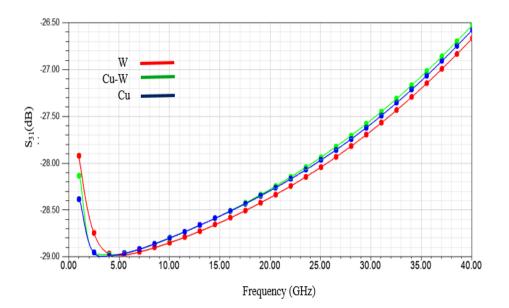

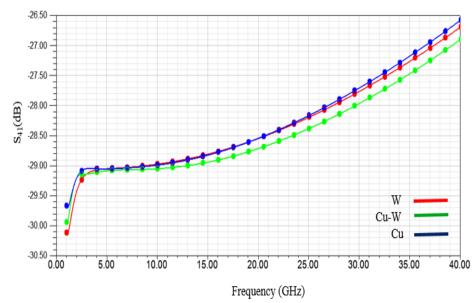

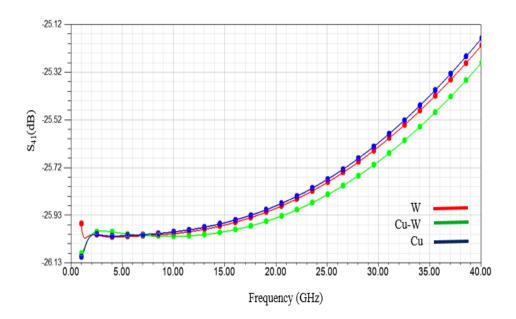

| 4.2.1: HFSS simulation for reflection coefficient $(S_{11})$ . Blue curve shows $S_{11}$ values               |

| for Cu TSV. Green curve is for Cu-W bimetal (overlapping in main figure                                       |

| with Cu TSV), Red is for W TSV. Silicon is used as an interposer material in                                  |

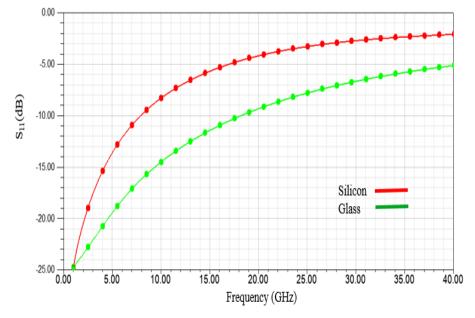

| the simulation                                                                                                |

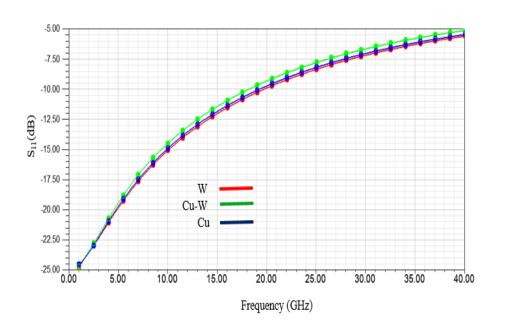

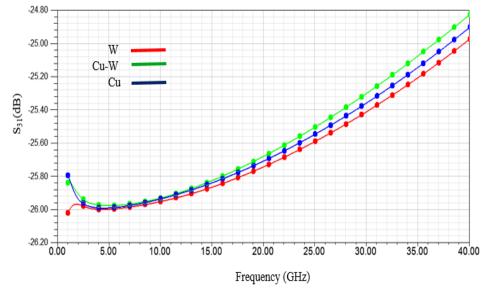

| 4.2.2: HFSS simulation for reflection coefficient $(S_{11})$ with Glass as an interposer                      |

| (TGV). (Red curve is for W via, Green curve is for Cu-W via and Blue curve                                    |

| is for Cu via)                                                                                                |

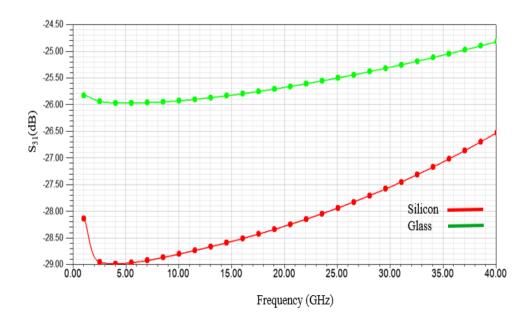

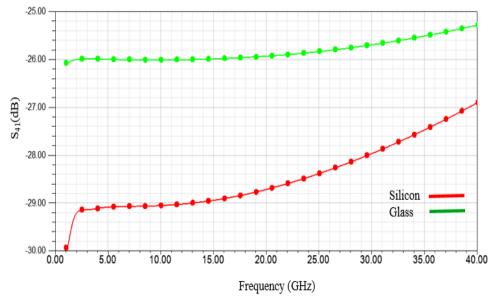

| 4.2.3: Comparison between the reflection coefficients $(S_{11})$ of Cu-W bimetal vias                         |

| when glass is used as an interposer (Green) and silicon is used as interposer                                 |

| (Red)                                                                                                         |

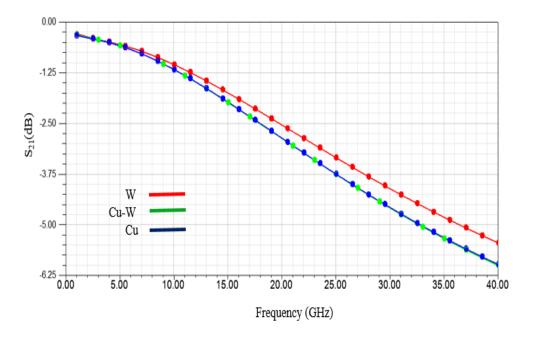

| 4.2.4: HFSS simulation for transmission coefficient ( $S_{21}$ ). Red curve shows $S_{21}$                    |

| values for W TSV. Green is for Cu-W bimetal TSV and Blue is for Cu TSV.                                       |

| Silicon is used as an interposer material in the simulation                                                   |

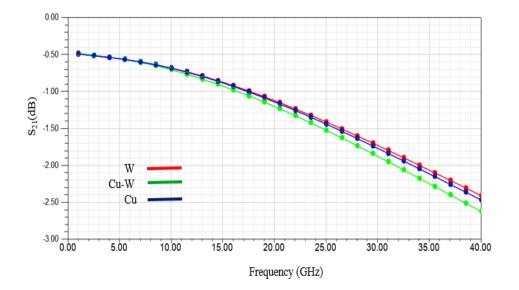

| 4.2.5: HFSS simulation for transmission coefficient $(S_{21})$ with Glass as an interposer.                   |

| (Red curve is for W TGV, Green curve is for Cu-W TGV and Blue curve is                                        |

| for W TGV)                                                                                                    |

| 4.2.6: Comparison between the transmission coefficients $(S_{21})$ of Cu-W vias when  |

|---------------------------------------------------------------------------------------|

| glass is used as an interposer (Green) and silicon is used as interposer (Red).       |

|                                                                                       |

| 4.2.7: Near-end crosstalk (NEXT) simulation for different via cores in silicon        |

| interposer (TSVs). Red curve is for W TSV, Green curve is for Cu-W TSV                |

| and Blue curve is for Cu TSV56                                                        |

| 4.2.8: Near end crosstalk (NEXT) simulation for different vias in glass interposer    |

| (TGVs). Red curve is for W TGV, Green curve is for Cu-W TGV and Blue                  |

| curve is for Cu TGV                                                                   |

| 4.2.9: NEXT in Cu via with silicon (RED) and glass (GREEN) interposers                |

| 4.2.10: Far-end crosstalk (FEXT) simulation for different vias in silicon interposer. |

| (Red curve is for W TSV, Green curve is for Cu-W TSV and Blue curve is for            |

| Cu TSV)                                                                               |

| 4.2.11: Far-end crosstalk (FEXT) simulation for different vias in glass interposer.   |

| (Red curve is for W TGV, Green curve is for Cu-W TGV and Blue curve is                |

| for Cu TGV)                                                                           |

| 4.2.12: FEXT in Cu TSV with Silicon interposer (Red) and Glass interposer (Green).    |

|                                                                                       |

| 4.2.13: Basic HFSS model used to measure the performance of TSVs with different       |

| TSV diameter and relative spacing                                                     |

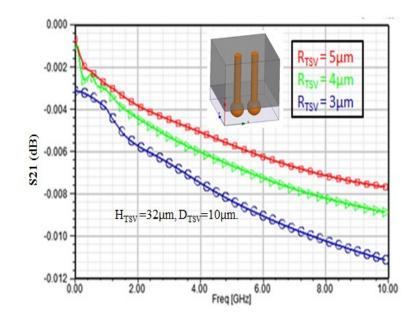

| 4.2.14: Transmission coefficient measurement of Cu TSV for three different radii 60   |

| 4.2.15: Return Loss measurement of Cu TSV for different radii                         |

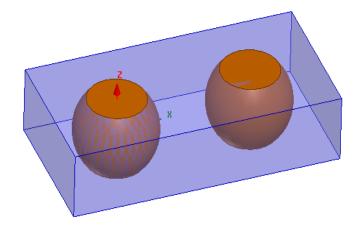

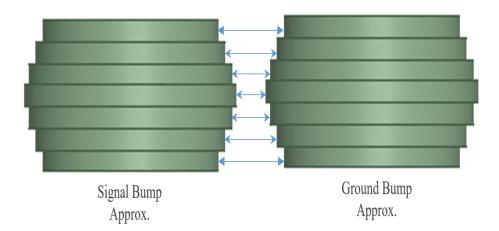

| 4.2.16: Typical signal and ground bump with Bump height of $18\mu m$ and radius of       |

|------------------------------------------------------------------------------------------|

| 12.5μm                                                                                   |

| 4.2.17: Transmission coefficient between bumps at different frequencies                  |

| 4.2.18: Return loss $(S_{11})$ measured between two bumps for different bump diameters.  |

|                                                                                          |

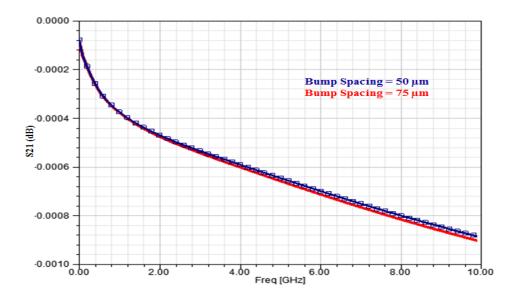

| 4.2.19: Transmission coefficient $(S_{21})$ between two bumps when the relative spacing  |

| between them is 50µm (blue) and 75µm (red)                                               |

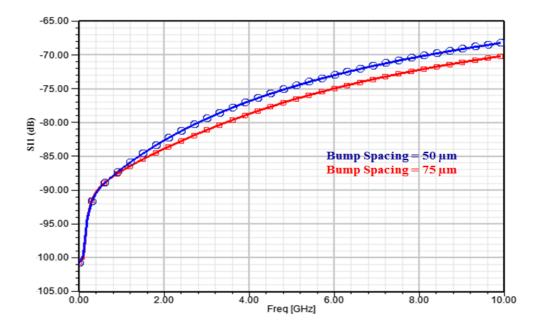

| 4.2.20: Return loss comparison between two bumps when they are placed $50\mu m$ and      |

| 75μm apart                                                                               |

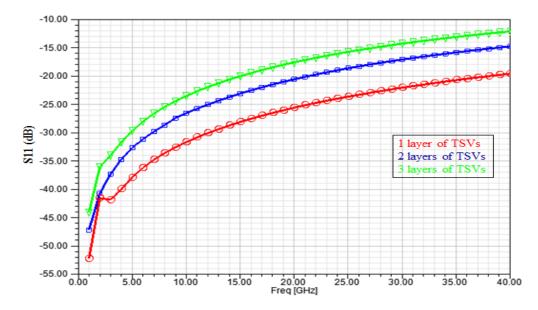

| 4.2.21: Return loss measurement for stacked TSV layers with diameter of the TSV is       |

| $20\mu m$ , height of the TSV is $60\mu m$ and pitch is $25\mu m$                        |

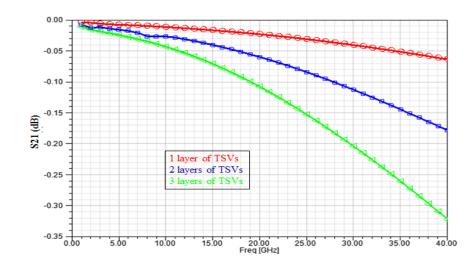

| 4.2.22: Comparison of transmission coefficient between TSVs with different layers.       |

|                                                                                          |

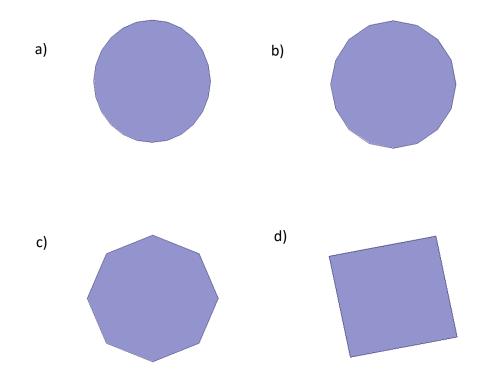

| 5.2.1: Different shapes of TSVs used for simulation. a. circular TSV b.                  |

| Hexadecagonal TSV c. Octagonal TSV d. Rectangular TSV71                                  |

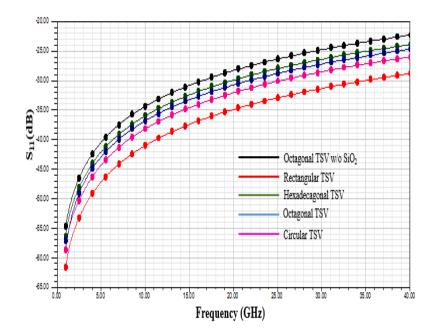

| 5.3.1: HFSS simulation for reflection coefficient (S11). Pink curve shows S11 values     |

| for circular TSV. Green curve is for hexadecagonal TSV, Red is for                       |

| rectangular TSV, Blue curve is for octagonal TSV and Black curve is for                  |

| octagonal TSV without the insulating layer73                                             |

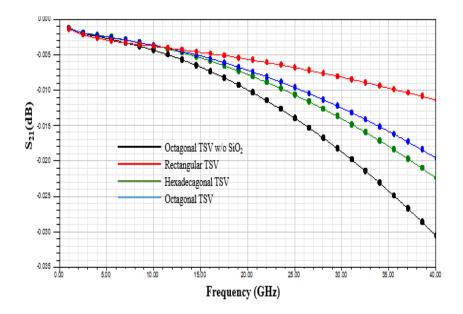

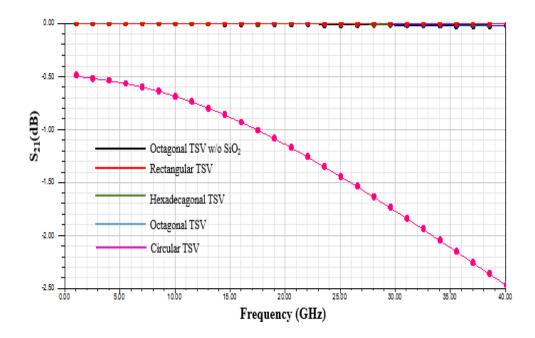

| 5.3.2: HFSS simulation for insertion loss $(S_{21})$ for different shapes of TSVs. Green |

| curve shows S21 values for hexadecagonal TSV, Red is for rectangular TSV,                |

| Blue curve is for octagonal TSV and Black curve is for octagonal TSV                     |

| without the insulating layer74                                                           |

| 5.3.3: Comparison between the insertion loss (S21) of circular TSV (pink) with other                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| polygonal TSVs (Overlapping)75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

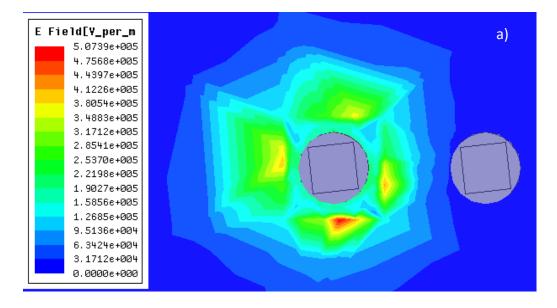

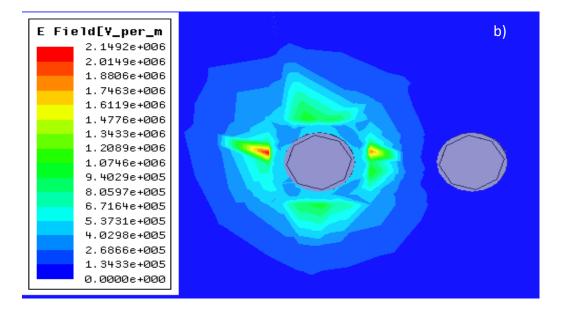

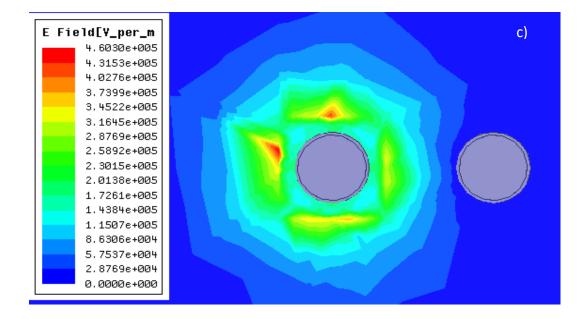

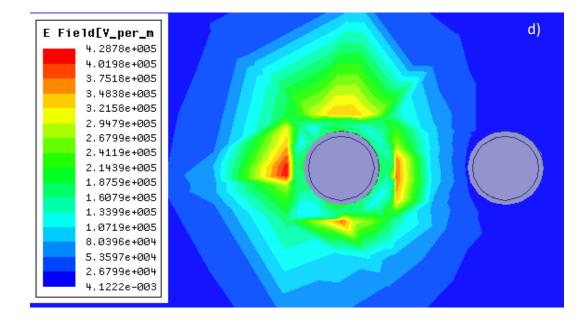

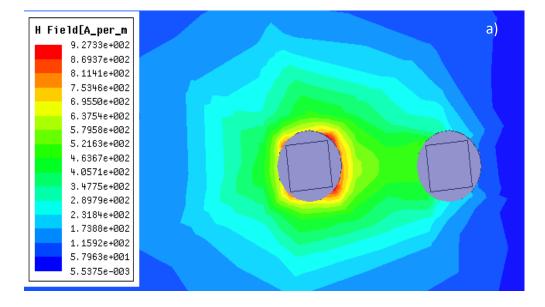

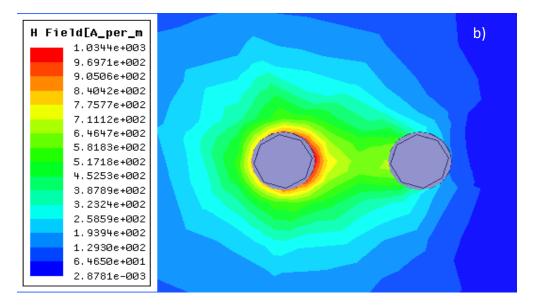

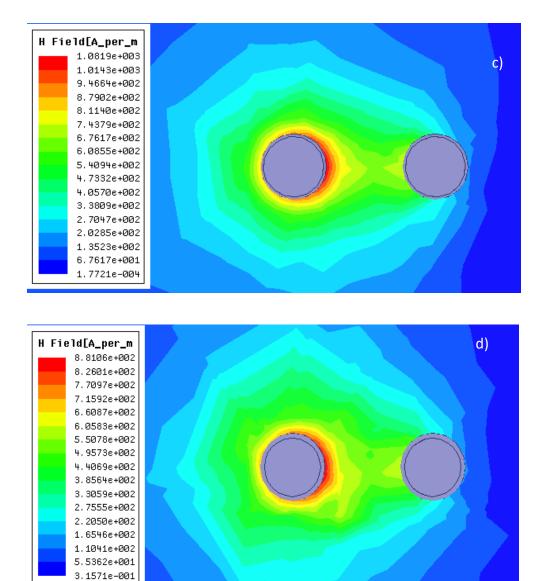

| 5.3.4: HFSS simulation of E-field distribution of a. rectangular, b. octagonal, c.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| hexadecagonal and d. circular TSVs78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.3.5: HFSS simulation of H-field distribution of a. rectangular, b. octagonal, c.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| hexadecagonal and d. circular TSVs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

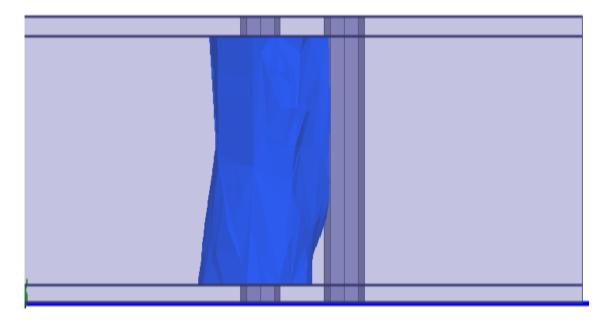

| 5.3.6: Side view of electric field distribution of an octagonal TSV when no insulating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| layer is used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6.2.1: Through-Silicon Via (TSV) structure with the core (copper pathway),                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| surrounding dielectric layer and landing pads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

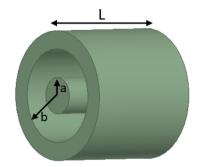

| 6.2.2: A cylindrical capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

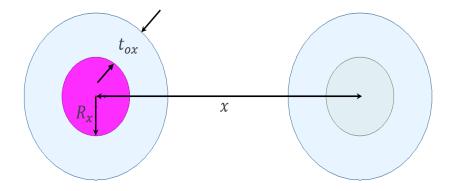

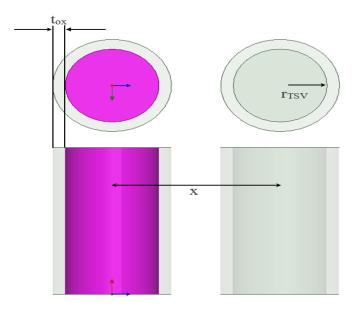

| 6.2.3: Two cylindrical segments at a distance x, with a radius of the cylinder $R_x$ and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6.2.3: Two cylindrical segments at a distance x, with a radius of the cylinder $R_x$ and thickness of the insulating layer $t_{ox}$ . This diagram is used to derive cylindrical                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| thickness of the insulating layer $t_{ox}$ . This diagram is used to derive cylindrical                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| thickness of the insulating layer t <sub>ox</sub> . This diagram is used to derive cylindrical capacitive formulae                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <ul> <li>thickness of the insulating layer t<sub>ox</sub>. This diagram is used to derive cylindrical capacitive formulae</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <ul> <li>thickness of the insulating layer t<sub>ox</sub>. This diagram is used to derive cylindrical capacitive formulae</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <ul> <li>thickness of the insulating layer t<sub>ox</sub>. This diagram is used to derive cylindrical capacitive formulae.</li> <li>6.2.4: A spherical segment is divided into small cylindrical segments, where the radius of each segment is Δr higher or lower than the previous one.</li> <li>89</li> <li>6.2.5: Electric filed lines between two segmented bumps.</li> </ul>                                                                                                                                                                                                   |

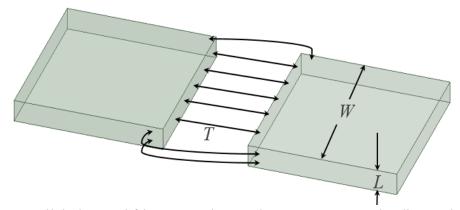

| <ul> <li>thickness of the insulating layer t<sub>ox</sub>. This diagram is used to derive cylindrical capacitive formulae.</li> <li>88</li> <li>6.2.4: A spherical segment is divided into small cylindrical segments, where the radius of each segment is Δr higher or lower than the previous one.</li> <li>89</li> <li>6.2.5: Electric filed lines between two segmented bumps.</li> <li>89</li> <li>6.2.6:Parallel plate and fringe capacitances between two TSV landing pads. Here, L is</li> </ul>                                                                            |

| <ul> <li>thickness of the insulating layer t<sub>ox</sub>. This diagram is used to derive cylindrical capacitive formulae.</li> <li>88</li> <li>6.2.4: A spherical segment is divided into small cylindrical segments, where the radius of each segment is Δr higher or lower than the previous one.</li> <li>89</li> <li>6.2.5: Electric filed lines between two segmented bumps.</li> <li>89</li> <li>6.2.6:Parallel plate and fringe capacitances between two TSV landing pads. Here, L is the thickness, W is the height and width of the pad, and T is the distance</li> </ul> |

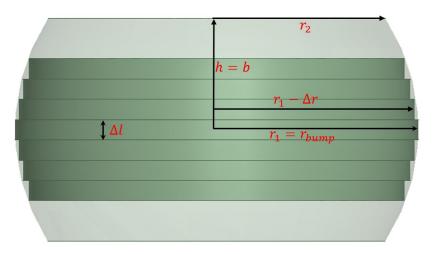

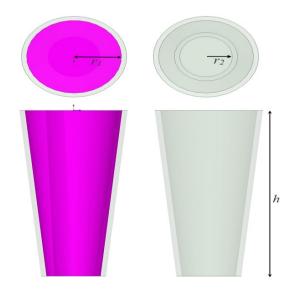

| 6.2.8: Tapered TSV with radius $r_1$ and $r_2$ , where $r_1 > r_2$ , and h is the height of the |

|-------------------------------------------------------------------------------------------------|

| TSV                                                                                             |

| 6.2.9: Tapered TSV divided into cylindrical segments with each step the radius of the           |

| cylindrical segments is decreased by an amount $\Delta \mathbf{r}$ and the height of each step  |

| is Δ <b>l</b> 95                                                                                |

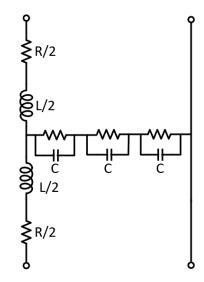

| 6.5.1: T-element equivalent circuit                                                             |

| 6.6.1: Comparison of Q3D field solver capacitance and the proposed model when the               |

| radius ( $r_1$ ) is decreased from 16µm to 11µm                                                 |

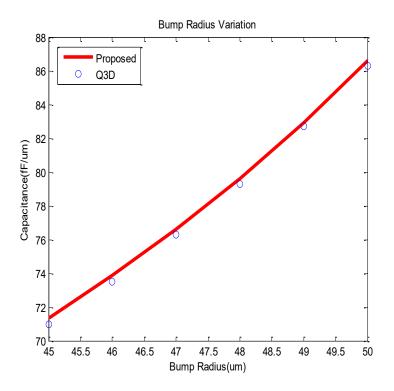

| 6.6.2: Comparison of Q3D field solver capacitance and the proposed model when the               |

| bump radius ( $r_{bump} = r_1$ ) is varied from 45µm to 50µm                                    |

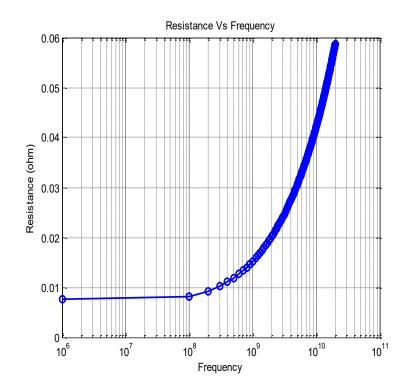

| 6.6.3: Change of TSV resistance with frequency due to the skin effect                           |

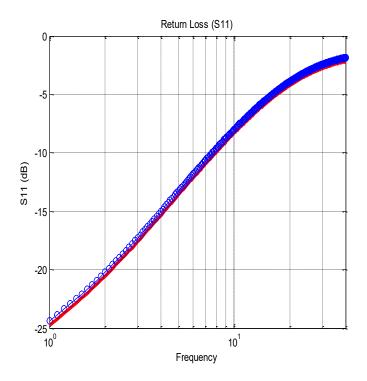

| 6.6.4: Return loss of differential TSV                                                          |

| 7.2.1: TSV based 3D inductor (top view)                                                         |

| 7.2.2: (a) Inductance and (b) Quality Factor of 3D TSV inductor when the radius of              |

| the TSV changes from $0.5\mu m - 4.0\mu m$                                                      |

| 7.2.3: The series resistance of a 3D TSV inductor when the radius of the TSV                    |

| changes from $1.0\mu m - 4.0\mu m$                                                              |

| 7.3.1: 3D TSV based inductor in a single layer with 10 turns                                    |

| 7.3.2: (a) Inductance and (b) Quality Factor of 3D TSV inductor when Cu (Green)                 |

| and W (Blue) are used as the core material 117                                                  |

| 7.3.3: (a) Inductance and (b) Quality Factor of 3D TSV inductor when Si (Green) and             |

| Glass (Blue) are used as the substrate118                                                       |

| 7.3.4: (a) Inductance and (b) Quality Factor of 3D TSV inductor for different 'Oxide |

|--------------------------------------------------------------------------------------|

| thickness119                                                                         |

| 7.3.5: (a) Inductance and (b) Quality Factor of 3D TSV inductor for SiO2/Air         |

| insulation layer120                                                                  |

| 7.3.6: (a) 3D TSV based inductor (b) Cross-sectional view of 3D TSV inductor 121     |

| 7.3.7: (a) Inductance and (b) Quality Factor of 3D TSV inductor for Single layer and |

| two-layer approach122                                                                |

| 7.4.1: LC VCO with Cross coupled NMOS/PMOS with varactor Capacitor for               |

| voltage tuning124                                                                    |

| 7.5.1: Frequency of oscillation 6GHz126                                              |

| 7.5.2: Frequency of oscillation 5.2GHz                                               |

# TABLES

| Fable   Page                                                         | ge  |

|----------------------------------------------------------------------|-----|

| 1. Dimensions of different metal layers in Intel 45nm technology [6] | . 9 |

| 2. TSV parameters and their values                                   | 49  |

| 3. TSV parameters and their values                                   | 71  |

| 4. TSV parameters and their values 1                                 | 00  |

| 5. TSV Design Parameters                                             | 16  |

| 6. Inductor Performance Comparison 1                                 | 23  |

| 7. Inductor parameters for VCO Design 1                              | 24  |

| 8. Core parameters for VCO Design 1                                  | 25  |

| 9. VCO Performance                                                   | 27  |

#### CHAPTER 1

#### **INTRODUCTION**

#### **1.1 Interconnect Modeling**

To keep up with Moore's law [1], the number of transistors is increasing to accommodate more functionality into a fixed size chip. Only way to achieve that is to scale down the physical dimensions of devices and wires that connects the devices in a chip. In the deep sub nanometer technology, the wire connecting the devices (also known as interconnect) plays a vital role of the chip's overall performance. With scaling down, the devices are becoming faster in every new generation, but the interconnects are getting narrower, so the performance of the interconnects getting worse. We now reach such a point where the interconnect delay is more prominent compared to gate delay and interconnect delay determines the chip performance.

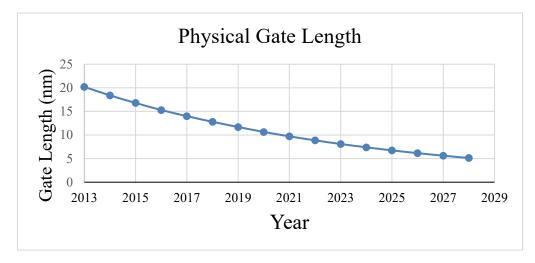

(c) *Figure 1.1.1:* IRDS prediction of (a) device scaling down (b) increasing interconnect length and (c) increasing interconnect delay [2, 3].

Figure 1.1.1 shows the roadmap for device scaling and path to overall interconnect performance [2, 3]. With aggressive scaling down of the device, more interconnect is

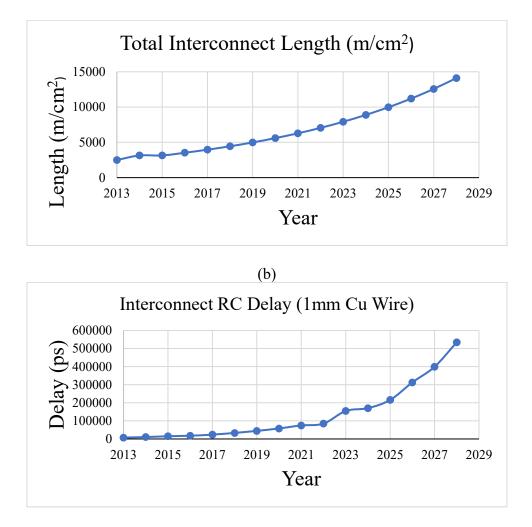

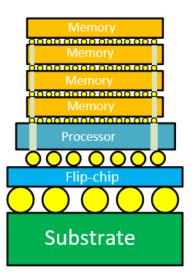

required to tie them all. Thus, the interconnects are placed very compactly, reducing their pitch (spacing between neighboring interconnect). As the width of interconnect also scaled down with device sizes, to keep up with device performance and reducing the overall resistance of the interconnect, height of the interconnect is increasing with every successive generation increasing their aspect ratio (height/width) as shown in Figure 1.1.2.

Figure 1.1.2: Prediction for interconnect aspect ratio and pitch.

As the interconnect performance becoming dominant, it is very important to predict the effect of the interconnect performance before chip fabrication. The interconnect performance depends on the resistance and the capacitance of the interconnect. Predicting the resistance of an interconnect is straight forward and depends on the dimension and material of interconnect. Contrary to that predicting the capacitance of an interconnect is very

3

complex procedure and often depends on different factors. So, it is very important to have an accurate model of interconnect capacitance to correctly predict the interconnect performance.

#### **1.2 3D Integration**

The demand for integrating more functionality into a single chip leads to technology scaling so that the number of transistors in a chip can be increased without increasing the chip area. But according to International Roadmap for Devices and Systems (IRDS) technology scaling may not be possible for 2D technology after 2024 [4]. Several leading chip manufacturing labs also known as foundries namely 'GlobalFoundries', halted their production below 7nm as the cost of building and maintaining new manufacturing facilities are beyond anticipation [5]. 3D integration can be a possible solution of this problem as 3D integration promises more functionality and better performance on a similar 2D chip area. It is a step towards 'more than Moore' era.

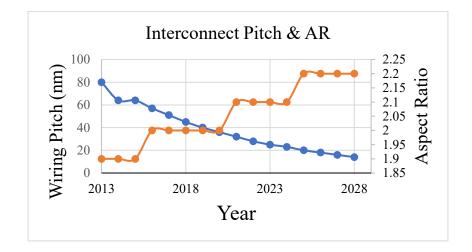

In general 3D integration means stacking up two or more 2D integrated chip vertically with the through-silicon vias (TSV), interposers, bumps, and micro bumps as shown in Figure 1.2.1. 3D integration promises improve performance, low power, smaller chip area, and reduced manufacturing cost compared to 2D integration. 3D integration comprises technologies such as 'system in package (SiP)', TSV based 3D integrated circuits, monolithic 3D integration etc.

Figure 1.2.1: 3D Integrated Circuit with TSVs, bumps and micro-bumps [2]

TSV based 3D integrated circuits solve one of the biggest problems of 2D integrated circuits currently face – ever increasing interconnect length. Through-silicon via (TSV) is a potential solution to the long interconnect problem as they are connected vertically and much shorter in length. Though shorter in length but their other dimension is large compared to nano scale interconnect, often having radius in ' $\mu m$ ' range. This large structure of TSVs introduces several other problems. So, when one uses TSV based 3D ICs it is important to make sure about the material of the core, material of the insulation layer that surrounds the TSV and characteristics of the interposer through with the TSV goes from one layer to the

next. As TSVs are responsible for supplying the power and signal, knowledge about their electrical and thermal characteristics are also very important.

#### 1.3 Organization

This dissertation consists of seven chapters. Chapter 1 provides a general introduction and overview also layout of the dissertation. Chapter 2 provides the background of current state of interconnect capacitive modeling. Chapter 3 discuss about the capacitance modeling of multi-level interconnect structure. Chapter 4 introduces the performance of TSVs based on the material composition and Chapter 5 tackles with the performance of TSV based on its shape and size. In Chapter 6 electrical characterization of TSVs are discussed and finally Chapter 7 presents the optimization of TSV based inductor for VCO design.

#### **1.4 Dissertation Objective**

The main objectives of the dissertation are summarized as follows:

- To provide an accurate capacitance model for sub 22nm technology node.

- Investigate the performance dependence of TSV on its material composition and structure.

- To develop an RLC model of the TSV for the electrical characterization.

- Optimize TSV based inductor for high frequency application.

- 6

#### CHAPTER 2

#### BACKGROUND OF CAPACITANCE MODELING OF ON-CHIP INTERCONNECT

#### **2.1** Introduction

In the CMOS integrated circuit technology, the wires that connects all the transistors in a system are known as interconnect. In the modern system interconnect plays a very important role and every so often interconnect performance determines the performance of the whole system. In the early ages of VLSI (very large-scale integration), the performance of On-Chip interconnect is mostly overlooked because the performance of the overall integrated system mostly depended on the performance of the transistors. The transistors are very slow compared to modern VLSI technology and the interconnect used to connect all those transistors are wide and thick thus results in very low resistance and they are placed moderately far apart from one another. So, the interconnects were treated as ideal equipotential nodes with lumped capacitance [6].

In the modern deep sub-micron technology, the interconnects are narrower and densely populated. So, the resistance goes high and introduce other parasitic effects such as coupling capacitance between neighboring interconnects which leads to a point where the RC delay of the interconnect line exceeds the gate delay of the transistors. Therefore, when designing a system with modern sub-micron technology node it is very important to have knowledge about the characteristics of the interconnect and their behavior and impact on the performance of the system.

#### 2.2 Interconnect Geometry

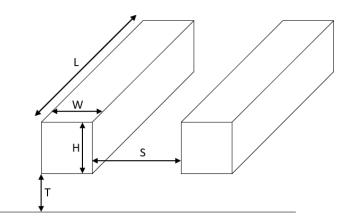

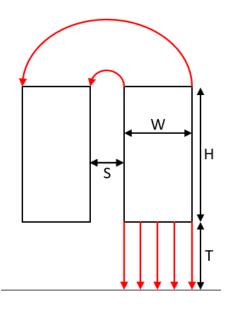

Figure 2.2.1 shows two interconnects are placed side by side over a ground plane as in modern CMOS technology. The width of the interconnect is W, height H, length L, the distance from the ground to the interconnect (also known as oxide thickness) T and distance between two interconnects (spacing) S. The term 'pitch' is known as the sum of width and spacing and the height to width  $\left(\frac{H}{W}\right)$  ratio is known as 'aspect ratio'.

Figure 2.2.1: Geometry of Interconnect

In early VLSI technology only a single layer of interconnect was used to connect all the transistors. Up until 1990s a maximum of two to three metal layers can be found on a system. But modern VLSI systems uses nine (9) or more metal layers because of the number of transistors in the system to connect and the advancement of chemical-mechanical polishing to fabricate several metal layers.

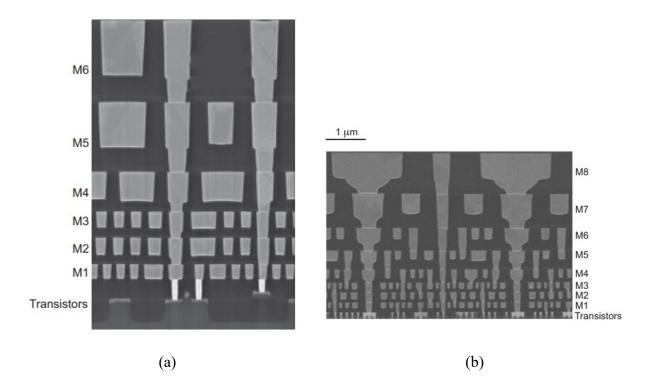

Figure 2.2.2 shows Intel 90 and 45 nm process, where the 90 nm process has six (6) metal layers and 45 nm process has nine (9) metal layers. The metal layers those are closed to the transistors (layer M1, M2) are densely packed and narrow in dimension (high pitch). The upper metal layers wider and offer great pitch. Table 1 shows different dimensions of intel 45nm process.

S(nm)Pitch (nm) Layer H(nm)W(nm)M9 17.5 μm 13 µm 30.5 μm 7 μm M8 M7 M6 M5 M4 M3 M2 M1

Table 1Dimensions of different metal layers in Intel 45nm technology [6]

Figure 2.2.2: Metal stack of Intel's (a) 90nm and (b) 45nm process [6]

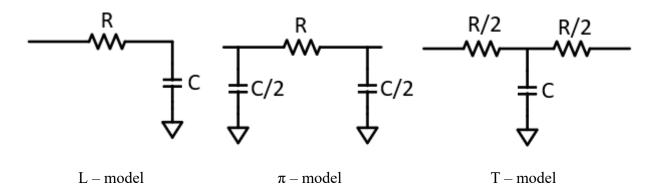

#### 2.3 Interconnect Model

An interconnect can be treated as a distributed circuit with resistance and capacitance per unit length [6]. The behavior of interconnect can be approximated by the number of lumped elements. L - model,  $\pi$  - model and T - model are the three standard approximations. Among the three approximation the performance of L – model is worst because to achieve accurate result numerous lumped elements are required. In case of  $\pi$  – model, only three segments are sufficient to achieve 97% accuracy. The accuracy of T – model is like  $\pi$  – model but it is much slower compared to  $\pi$  – model. So, to use any of the standard model first the model for resistance and capacitance are required.

Figure 2.3.1: Lumped approximation of distributed RC circuit [6]

#### 2.4 Resistance Model

The model for the resistance of an interconnect is more straight forward compared to capacitance. The resistance of a uniform rectangular interconnect can be formulated as Eq. (1).

$$R = \frac{\rho L}{WH} \tag{1}$$

Where  $\rho$  is the resistivity of the interconnect material, *L* is the length of the interconnect, *W* is the width of the interconnect and *H* is the thickness of the interconnect.

Eq. (1) can also be expressed as Eq. (2).

$$R = R_{\circ} \frac{L}{W}$$

(2)

In Eq. (2)  $R_{\circ}(=\rho/H)$  is the sheet resistance and has the unit  $\Omega$ /square.

#### 2.5 Capacitance Model

The classical formula for calculating the capacitance of a rectangular interconnect over a ground plane is expressed as Eq. (3) also known as parallel plate capacitance.

$$C = \frac{\varepsilon_{ox}WL}{T} \tag{3}$$

Where  $\varepsilon_{ox}$  is the dielectric constant of the oxide material used between the interconnect and the ground plane. Considering only the capacitance in Eq. (3) for the interconnect model is not sufficient for sub-micron technology as the aspect ratio of the interconnect is higher than previous generations and the interconnect are densely packed. The higher aspect ratio introduces fringing capacitance and the reducing spacing between interconnects produces coupling capacitances become dominant over parallel plate capacitance [3], [2], [7]. The fringing capacitance is very complicated to compute and to get an accurate result a numerical field solver is required. Over the decades, there have been numerous models proposed in the literature to capture interconnect capacitances of high-speed integrated circuits based on empirical, numerical, and analytical methods.

A method is proposed in [8] based on 'sub-area' method. In this method the calculation error was eliminated by divide the system into sub-aera. By using this method, the capacitance of a single interconnect over a ground plane is expressed as Eq. (4).

$$\frac{C_1}{\varepsilon_{ox}L} = 1.15 \left(\frac{W}{T}\right) + 2.80 \left(\frac{H}{T}\right)^{0.222}$$

(4)

Capacitance of three interconnect over a ground plane is expressed as Eq. (5).

$$\frac{C_3}{\varepsilon_{ox}L} = C_1 + 2\left[0.03\left(\frac{W}{T}\right) + 0.83\left(\frac{H}{T}\right) - 0.07\left(\frac{H}{T}\right)^{0.222}\right] \left(\frac{S}{T}\right)^{-1.34}$$

(5)

The relative error of this model is less than 10% when  $0.3 < \frac{W}{T} < 10$ ,  $0.3 < \frac{H}{T} < 10$ and  $0.5 < \frac{S}{T} < 10$ .

The model proposed in [9] where a conductor with a rectangular middle part and two hemispherical end section was placed over a ground plane. Eq. (6) shows the expression for the capacitance when  $W \ge \frac{H}{2}$  and in Eq. (7) when  $W < \frac{H}{2}$ .

$$\frac{C}{\varepsilon_{ox}L} = \left[\frac{\left(W - \frac{H}{2}\right)}{T} + \frac{2\pi}{\ln\left(1 + \frac{2T}{H} + \sqrt{\frac{2T}{H}\left(\frac{2T}{H} + 2\right)}\right)}\right]$$

(6)

$$\frac{C}{\varepsilon_{ox}L} = \left[\frac{W}{T} + \frac{\pi \left(1 - 0.0543 \frac{H}{2T}\right)}{\ln \left(1 + \frac{2T}{H} + \sqrt{\frac{2T}{H} \left(\frac{2T}{H} + 2\right)}\right)} + 1.47\right]$$

(7)

The model is accurate within 10% when the aspect ratio is less than 2 and T = H.

A computationally efficient model was proposed in [10] which is accurate within 6% for aspect ratio less than 3.3. The proposed capacitance model is shown in Eq. (8).

$$\frac{C}{\varepsilon_{ox}L} \left[ \frac{W}{T} + 0.77 + 1.06 \left( \frac{W}{T} \right)^{0.25} + 1.06 \left( \frac{H}{T} \right)^{0.5} \right]$$

(8)

Although those models discussed above are still extensively used, but they don't take into account the aspect ratio of modern interconnect technology (where the height is greater than the width), as a result lacking the accuracy required for current VLSI interconnect capacitance calculation [3]. A two-dimensional numerical solution by Green's function is used in [11] to calculate the capacitance of a single interconnect in a homogeneous medium. Boundary-element method (BEM) [12] [13] [14] [15] [16], finite element method [17], finite difference method [18], and semi-analytical approaches [19], [20] are also used in the

literature for capacitance modeling of complex interconnect structures. Still, these approaches are computationally expensive, and not suitable to implement in CAD tools. A number of empirical models are proposed in [21] [22] [8] [23] for a specific set of interconnects geometries but these models are complicated and strictly limited to a small number of interconnect configurations. The model proposed in [23] considers fringing capacitance originate from top-wall to ground plane, parallel plate approximation is used to estimate the side-wall fringing capacitance. These models are simple and works well for a conductor with aspect ratio less than 1, the accuracy is not acceptable in the current VLSI technology nodes. Analytical expressions are given in [24] and [9] by modifying the thickness of a rectangular interconnect to a circular cross-section. Expressions in [9] closely follow two-dimensional simulation results, but model is only valid for aspect ratio less than half. The capacitance model discussed in [24] is based on the approximation that the heigh of a interconnect is equal to a diameter of circular interconnect cross-section. It reduces the effective width by half of its thickness. The model is not valid when the aspect ratio of the interconnect is equal to 1, in that case model doesn't converge. Both models in [24] and [9] do not take into account the fringing electric field coming from the top surface of the interconnect. A fringing capacitance model is proposed in [25], which considers the nonlinearities of second-order effects of field interactions. Although the model provides a closed-form solution with good accuracy, the expression is complex to be used in regular circuit analysis. A number of experimental models for capacitance calculation have been

proposed in [26] [27] [28] [29] that estimate on-chip wiring capacitances. The models are based on "charge based capacitance measurements". Although these methods provide higher accuracy compared to empirical or analytical models, they are useful only for post-manufacturing stages.

#### CHAPTER 3

# ACCURATE MODELING OF INTERCONNECT CAPACITANCE IN MULTILEVEL INTERCONNECT STRUCTURES FOR SUB 22NM TECHNOLOGY

#### 3.1 Introduction

The increasing demand for higher performance and multiple functions lead to smaller devices and increasing chip density, which makes the interconnect role dominant over device performance in nanoscale integrated circuits. Therefore, it is essential to accurately model different capacitive components of interconnect lines to estimate delay and crosstalk noise in early design phases. With continuous scaling, the aspect ratio (height/width) of interconnect has become more than unity. As a consequence, the fringing and the coupling capacitances are becoming dominant over parallel-plate ground capacitance [3], [2], [7]. Moreover, the total overlap capacitance between interconnect lines in the adjacent layers are also getting stronger due to a higher number of metal layers [30].

#### 3.2 Analyzing Electric Field Distribution in Multi-Layer Interconnect Structure

#### 3.2.1 Single Interconnect Line Over A Ground Plane

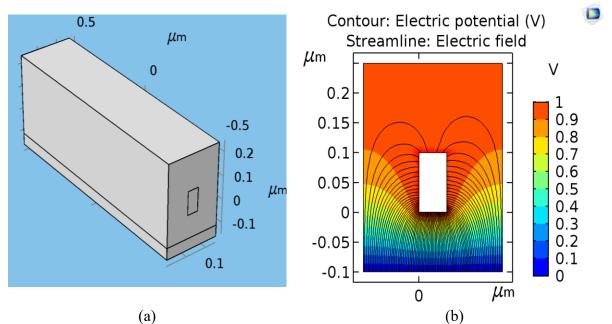

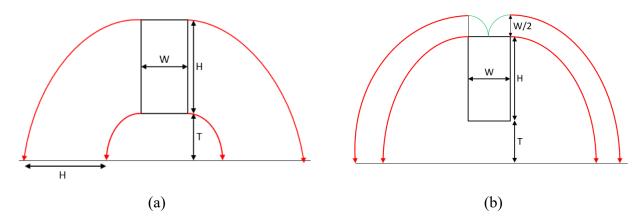

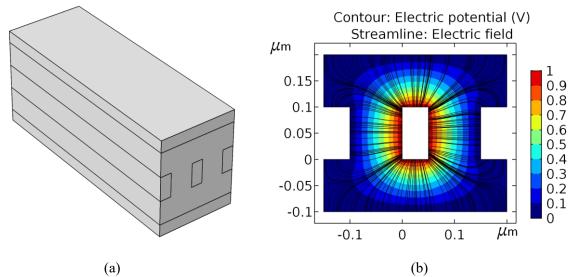

We have analyzed the electric field distribution of interconnects over the ground plane. We started with a simple structure where there is one interconnect line placed on the ground plane. We observed how electric fields originate from the interconnect and ends up on the ground plane. Figure 3.2.1(a) shows an interconnect line over a ground plane where

the interconnect line is surrounded by an insulating material  $(SiO_2)$ . In the figure the height (H) of the interconnect is  $0.1\mu m$ , width (W) is  $0.05\mu m$ , length of the interconnect is  $1\mu m$ , and the thickness (T) of the oxide layer (distance between the bottom of the interconnect line and the top of the ground plane) is  $0.1\mu m$ . Figure 3.2.1(b) shows the electric field distribution in xz-plane for the structure shown Figure 3.2.1(a). The applied voltage is 1V. It is observed from Figure 3.2.1(b) that electric field lines are coming not only from the bottom wall to the ground plane but also from the sidewall as well as from the top to the ground plane. The electric field tends to bend close to the corner of the interconnect line. The electric field line those are originated at the bottom plate and terminate to the ground plane in a straight line are less compared to the lines those are bend at the corner.

#### **3.2.2** Capacitance Model for A Single Interconnect Line Over the Ground Plane

The basic idea behind the self-capacitance model of a single interconnect is effectively analyzing electrical flux lines coming out of that line. From a quick observation of the electric field distribution shown in Figure 3.2.1(b), it is concluded that self-capacitance has mainly three components:

- a. Capacitance due to line to ground field.

- b. Capacitance due to side wall and top wall fringing field.

- c. Capacitance due to corner fringing field.

Figure 3.2.1: (a) Single interconnect line over a ground plane. The interconnect line is surrounded  $SiO_2$ . (b) Electric potential (Contour) and Electric filed distribution for a single interconnect line over a ground plane.

#### **3.2.2.1** Capacitance Due to Line to Ground Field.

The capacitance due to line to the ground field can be easily modeled by the parallelplate capacitance approximation and can be expressed as Eq. (1) where W is the width of the interconnect, T is the distance between the interconnect and the ground plane (also known as the dielectric thickness), L is the length of the interconnect (not shown in the figures) and  $\varepsilon$  is dielectric constant.

$$\frac{C_{PP}}{\varepsilon L} = \frac{W}{T} \tag{1}$$

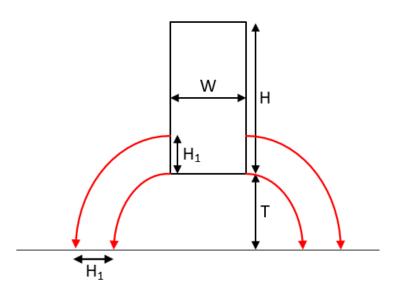

#### 3.2.2.2 Capacitance Due To Side Wall And Top Wall Fringing Field

The capacitance due to the fringing field between the sidewall of the interconnect and the ground plane can be approximated by assuming that the electric field originating from the sidewall of the interconnect follows a circular path to the ground. The electric field lines are originating from T (at the bottom of the interconnect) to H + T (at the top of the interconnect). If the length (distance) of the electric field that originates from the bottom of the interconnect to the ground is  $\frac{\pi r}{2}$  (assuming the radius is r), we can approximate the capacitance due to the fringing fields using Eq. (2).

$$\frac{C_{fringe}}{\varepsilon L} = \int \frac{width}{distance}$$

(2)

$$C_{fringe,sidewall} = \int_{T}^{H+T} \frac{dr}{\pi r/2} = \frac{2}{\pi} \ln\left(1 + \frac{H}{T}\right)$$

(3)

*Figure 3.2.2:* (a) Fringing field lines originating from the sidewall of the interconnect line (b) approximate fringing field lines originating from the top wall of the interconnect line.

The capacitance due to the fringing field originating from the top of interconnect can be formulated the same way as we formulate sidewall fringing field capacitance. For simplicity, a portion of the fringing field is not considered (indicated by the green line in Figure 3.2.2(b)) so that the electric field approximated to have a circular path starting from the top of the interconnect (T + H) to the ground, extending to height  $(T + H + \frac{W}{2})$ . Using Eq. (2) to approximate the top wall fringing capacitance,  $C_{fringe,topwall}$  can be expressed as Eq. (4).

$$C_{fringe,topwall} = \int_{H+T}^{H+T+W/2} \frac{dr}{\pi r/2} = \frac{2}{\pi} \ln\left(1 + \frac{W}{2(H+T)}\right)$$

(4)

## 3.2.2.3 Capacitance Due to Corner Fringing Field

Finally,  $C_{cornerfringe}$  is the capacitance due to the point charge located at the corner of the bottom of the interconnect. Unlike  $C_{fringe,topwall}$  or  $C_{fringe,sidewall}$  the electric field lines for  $C_{cornerfringe}$  are originated from a single point. So instead of circular electric field approximation, we have to use elliptical field line approximation (as shown in Figure 3.2.3). Assuming the first electric field is very close to the origin ( $x \approx 0$ ), we can approximate the capacitance due to the corner fringing filed as Eq. (5).

*Figure 3.2.3:* Approximated electric field lines originating from the corner of the interconnect.

$$C_{cornerfringe} \approx \int_{0}^{T} \frac{dx}{\frac{\pi}{2}\sqrt{\frac{(x^2+T^2)}{2}}} = \frac{3\sqrt{2}}{\pi} \ln(1+\sqrt{2})$$

(5)

From Eq. (5) we observe that  $C_{cornerfringe}$  is constant, but observation from the simulation data indicate that it should increase with decreasing the oxide thickness (*T*). So  $C_{cornerfringe}$  can be expressed as Eq. (6).

$$C_{cornerfringe} = \alpha_1 \frac{3\sqrt{2}}{\pi} \ln(1 + \sqrt{2})$$

(6)

Where  $\alpha_1 = \left(\frac{W}{T}\right)$ . As the top corners of the interconnect are far away from the ground plane, they are not considered for the capacitance calculation.

So, the total capacitance between the interconnect and the ground plane is the summation of parallel plate capacitance ( $C_{PP}$ ), two side-wall capacitance ( $C_{fringe,sidewall}$ ), top-wall capacitance ( $C_{fringe,topwall}$ ) and two bottom corner capacitance ( $C_{cornerfringe}$ ).

$$\frac{C_{total,single}}{\varepsilon L} = C_{PP} + 2C_{fringe,sidewall} + 2C_{fringe,topwall} + 2C_{cornerfringe}$$

(7)

$$\frac{C_{total,single}}{\varepsilon L} = \frac{W}{T} + \frac{4}{\pi} \ln\left(1 + \frac{H}{T}\right) + \frac{4}{\pi} \ln\left(1 + \frac{W}{2(H+T)}\right) + \alpha_1 \frac{6\sqrt{2}}{\pi} \ln\left(1 + \sqrt{2}\right) \tag{8}$$

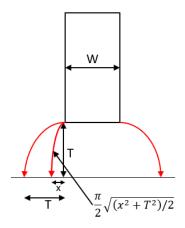

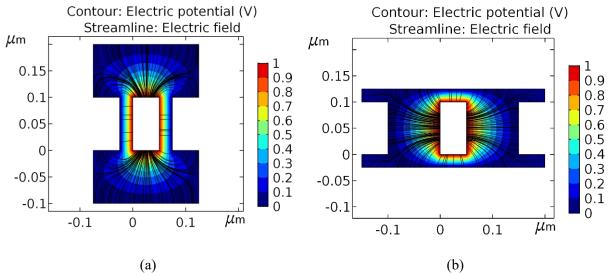

#### 3.2.3 Three Interconnect Lines Between Two Ground Planes

Figure 3.2.4(a) shows three parallel interconnect lines between two ground planes. In the figure the height (*H*) of the interconnect is  $0.1\mu m$ , width (*W*) is  $0.05\mu m$ , length of the interconnect is  $1\mu m$ , the distance between the bottom of the interconnect line and the top of the ground plane (*T*) is  $0.1\mu m$ , and the separation (*S*) between two interconnect lines is  $0.1\mu m$ .

To capture the influence of the distance between the bottom plate to the ground plane (insulator thickness T) and separation between neighboring interconnect lines (*S*), we analyze the different combinations of '*S*' and '*T*.' Figure 3.2.5 shows two such combinations where (a)  $T = 0.1\mu m$ ,  $S = 0.025\mu m$ , (b)  $T = 0.025\mu m$ ,  $S = 0.1\mu m$ . It has observed that when '*S*' is smaller than '*T*'(S < T), the field originating from the sidewall of the interconnect no longer ended up on the ground plane. Still, some of the electric field lines that originate from the bottom plate end up on the neighboring bottom plate, as shown in Figure 3.2.5(a). The electric field lines from the sidewall end up on the ground plane occurs when insulator thickness is greater than interconnect separation (T > S), as shown in Figure 3.2.5(b). So, there is a transition point when this transition occurs. We varied '*T*' and '*S*' from  $0.01\mu m$  to  $0.5\mu m$  and analyzed each combination and found that electric field lines from the sidewall end up in ground plane when S > 1.5T and electric field lines from the bottom plate of one interconnect lines to the bottom plate of the neighboring interconnect line happens when S < 1.5T.

*Figure 3.2.4:* (a) Three interconnect lines sandwiched between two ground planes. The interconnect lines are surrounded by SiO<sub>2</sub>. (b) Electric potential (Contour) and Electric filed distribution for three parallel interconnect lines between two ground planes. Here insulator thickness  $(T) = 0.1 \mu m$  and separation (S) between adjacent interconnect is  $0.1 \mu m$

#### 3.2.4 Capacitance Model of Multiple Lines Between Two Ground Planes

In this subsection, we formulate the expressions of capacitance for multiple lines running in parallel between two ground planes by using the concept developed in the previous subsection. We consider only three lines between ground planes, as shown in Figure 3.2.4(a), where the middle line (the line of interest) is sandwiched between two neighboring lines.

*Figure 3.2.5:* Electric field distribution of two parallel interconnect lines over a ground plane for various combination of insulator thickness (T) and separation (S). (a)  $T = 0.1 \mu m$ ,  $S = 0.025 \mu m$ , (b)  $T = 0.025 \mu m$ ,  $S = 0.1 \mu m$ .

Since capacitive coupling is a short-range phenomenon, we do not consider the next order neighboring lines beyond the immediate left and then immediately right neighbors while calculating the coupling capacitance of the middle line. We assume that two neighboring lines are grounded to ignore electric flux originating from them since it simplifies the flux distribution of the structure. However, if these two neighboring lines also carry signals (driven by a driver), the effective coupling capacitance will be multiple of that when connected to ground depending on the switching activities of the coupled lined, as discussed in the subsequent section.

Based on the electric field distribution observed in Figure 3.2.5(a),(b), depending on oxide thickness (T) and spacing between neighboring interconnect (S) we can separate the capacitance formulation into two part, a. when  $S > \frac{3}{2}T$  and b. when  $S < \frac{3}{2}T$ .

# **3.2.5** When the Spacing Between the Interconnect Is Greater Than the Oxide

Thickness  $(S > \frac{3}{2}T)$

#### 3.2.5.1 Capacitance Due to Line to Ground Field

Bottom side field lines form a parallel-plate capacitance ( $C_{PP}$ ) with the ground plane like the single line.

$$\frac{C_{PP}}{\varepsilon L} = \frac{W}{T} \tag{9}$$

#### 3.2.5.2 Capacitance Due to Corner Fringing Field

There will be fringing capacitance between the corners of the neighboring interconnect. The corner fringing capacitance will contribute to the total capacitance depending on the insulator thickness and separation between two neighboring interconnects. The  $C_{fringe,corner}$  can be evaluated as same procedure as Eq. (6). Eq. (10) shows the resulting formula for  $C_{fringe,corner}$ .

$$C_{fringe,corner} = \alpha_2 \frac{3\sqrt{2}}{\pi} \ln(1 + \sqrt{2})$$

(10)

Where  $\alpha_2 = \left(\frac{W+S}{T}\right)$ .

#### 3.2.5.3 Capacitance Due to Side Wall to Ground Fringing Field

Fringing fields from the smaller segment  $H_1$  form capacitance with the ground. We model this component ( $C_{fringe,sidewall}$ ) like what we have done for the single interconnect case. Unlike the single interconnect case not all the side wall electric field contribute to the sidewall to ground fringing capacitance. A smaller portion of the side wall ( $H_1$ ), the value of which depends on the separation between interconnect (S) and the oxide thickness (T). The electric field lines at the edge of parallel plates are not precisely straight lines. Figure 3.2.6 shows the electric field lines originated from the segment  $H_1$  of the side wall. The electric field approximated to have a circular path starting from the bottom of the interconnect (T) to the ground, extending to height ( $T + H_1$ ).  $C_{fringe,sidewall}$  can be expressed as Eq. (11).

$$C_{fringe,sidewall} = \int_{T}^{T+H_1} \frac{dr}{\pi r/2} = \frac{2}{\pi} \ln\left(1 + \frac{H_1}{T}\right)$$

(11)

*Figure 3.2.6:* Approximated electric field lines originating from a portion of the sidewall of the interconnect.

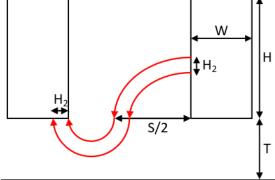

#### 3.2.5.4 Capacitance Due to Side Wall to Bottom Plate Fringing Field

A small portion of electric field from the side of the interconnect ends up on the bottom of the neighboring interconnect. We assume that the segment of the electric field originating from the sidewall that ends on the bottom of the neighboring interconnect is not more than 10%. Figure 3.2.7 shows the electric field that originated from the segment  $H_2$  (= 0.1 $H_1$ ). To formulate this capacitance, we divide the electric field into two parts. The first section of the electric filed that originate from the sidewall and ends in between the two interconnects (at S/2). The electric filed in this section assume to have elliptical shape. Eq. (12) shows the capacitance due to the elliptical portion of the electric field.

$$C_{fringe,side-bottomwall_{e}} = \int_{H_{1}}^{H_{1}+H_{2}} \frac{dr}{\frac{1}{\pi^{2}\sqrt{2}}}$$

$$C_{fringe,side-bottomwall_{e}} = \frac{3\sqrt{2}}{\pi} \ln\left(\frac{(H_{1}+H_{2}) + \sqrt{(H_{1}+H_{2})^{2} + \left(\frac{S}{2}\right)^{2}}}{(H_{1}) + \sqrt{(H_{1})^{2} + \left(\frac{S}{2}\right)^{2}}}\right)$$

(12)

*Figure 3.2.7:* Approximated electric field lines originating from a portion of the sidewall of the interconnect that ends up on the bottom portion of neighboring interconnect.

In the second section we have a circular electric field pattern. The inner circle assumes to have a diameter  $\left(\frac{s}{2}\right)$ . Eq. (13) shows the capacitance due to the circular portion of the electric field.

$$C_{fringe,side-bottomwall_c} = \int_{\frac{S}{2}}^{\frac{S}{2}+H_2} \frac{dr}{\pi r} = \frac{1}{\pi} \ln\left(1 + \frac{2H_2}{S}\right)$$

(13)

So, the total capacitance due to the circular and elliptical field can be represented as Eq. (14).

$C_{fringe,side-bottomwall} = series(C_{fringe,side-bottomwall_{c'}}, C_{fringe,side-bottomwall_{e}})$

$C_{fringe,side-bottomwall}$

$$= series\left(\frac{1}{\pi}\ln\left(1 + \frac{2H_2}{S}\right), \frac{3\sqrt{2}}{\pi}\ln\left(\frac{(H_1 + H_2) + \sqrt{(H_1 + H_2)^2 + \left(\frac{S}{2}\right)^2}}{(H_1) + \sqrt{(H_1)^2 + \left(\frac{S}{2}\right)^2}}\right)\right)$$

(14)

# 3.2.5.5 Capacitance Due to Side Wall Parallel Plate Field

The remaining electric field that originates from the sidewall ends up on the sidewall of the neighboring interconnect, creating a parallel plate equivalent capacitance as shown in Eq. (15).

$$\frac{C_{PP,sidewall}}{\varepsilon L} = \frac{H - 2H_1 - 2H_2}{S}$$

(15)

In summary, the total capacitance of an interconnect line between two neighboring interconnect line and between two grounds can be formulated as Eq. (16), when the separation between the interconnects is greater than the oxide thickness  $(S > \frac{3}{2}T)$ .

$C_{total} = 2C_{PP} + 4C_{fringe,corner} + 4C_{fringe,sidewall} + 4C_{fringe,side-bottomwall} + 2C_{PP,sidewall} (16)$

$$\frac{C_{total}}{\varepsilon L} = 2\frac{W}{T} + 4\alpha_2 \frac{3\sqrt{2}}{\pi} \ln(1+\sqrt{2}) + 4\frac{2}{\pi} \ln\left(1+\frac{H_1}{T}\right) + 2\frac{H-2H_1-2H_2}{S} + 4series\left(\frac{1}{\pi} \ln\left(1+\frac{2H_2}{S}\right), \frac{3\sqrt{2}}{\pi} \ln\left(\frac{(H_1+H_2)+\sqrt{(H_1+H_2)^2+\left(\frac{S}{2}\right)^2}}{(H_1)+\sqrt{(H_1)^2+\left(\frac{S}{2}\right)^2}}\right)\right)$$

(17)

# 3.2.6 When the Spacing Between the Interconnect Is Less Than The Oxide Thickness $(S < \frac{3}{2}T)$

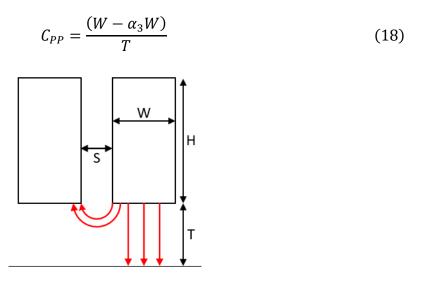

#### 3.2.6.1 Capacitance Due to Line to Ground Field

When the oxide thickness (T) is greater than the spacing between the interconnect (S), not all the electric fields originating from the bottom of the interconnect ends on the ground plane. A portion of the electric field also ends up on the bottom of the neighboring interconnect as shown in Figure 3.2.5(a) and Figure 3.2.8. We assume the electric field lines

originate from the portion  $(W - \alpha_3 W)$  terminate on the ground. The value of  $\alpha_3$  depends on the oxide thickness (T) and the separation (S).  $\alpha_3$  increases if the spacing between neighboring interconnect decreases or the oxide thickness (T) decreases. So, we can express the capacitance due to the line to ground field as Eq. (18).

*Figure 3.2.8:* Approximated electric field lines originating from the bottom of the interconnect. A portion of the electric field lines ends up on the ground and the remaining part ends up on the bottom of the neighboring interconnect.

#### 3.2.6.2 Capacitance Due to Bottom Plate to Bottom Plate Fringing Field

The remaining section of the electric field originates from the middle interconnect ends up in the neighboring interconnect creating a circular path. Eq. (19) shows the capacitance formula for  $C_{fringe,bottom-bottom}$ .

$$C_{fringe,bottom-bottom} = \int_{S}^{S+\alpha_{3}W} \frac{dr}{\pi r} = \frac{1}{\pi} \ln\left(1 + \frac{\alpha_{3}W}{S}\right)$$

(19)

# 3.2.6.3 Capacitance Due to Corner Fringing Field

When corners of the neighboring interconnect come close they generates capacitance depending on how close the corners are. Eq. (20) shows the  $C_{fringe,corner}$  model.

*Figure 3.2.9:* Electric field generates from the corner of interconnect.

$$C_{fringe,corner} \approx \int_{0}^{S} \frac{dr}{\pi \sqrt{\frac{(r^2 + S^2)}{2}}} = \frac{\sqrt{2}}{\pi} \ln(1 + \sqrt{2})$$

(20)

$C_{fringe,corner}$  depends on the spacing between two interconnects but the model does not reflect that. So, we add a depending variable  $\alpha_4$  whose value depends on the interconnect spacing (S).

#### 3.2.6.4 Capacitance Due to Sidewall-to-Sidewall parallel Field

Capacitance due to sidewall-to-sidewall electric field is basically the parallel plate capacitance where the width equivalent is H (height of the interconnect) and oxide thickness equivalent is spacing (S)

$$C_{PP,sidewall} = \frac{H}{S} \tag{21}$$

In summary, the total capacitance of an interconnect line between two neighboring interconnect line and between two grounds can be formulated as Eq. (16), when the separation between the interconnects is smaller than the oxide thickness  $(S < \frac{3}{2}T)$ .

$$C_{total} = 2C_{PP} + 4C_{fringe,corner} + 2C_{PP,sidewall} + 4C_{fringe,bottom-bottom}$$

(22)

$$\frac{C_{total}}{\varepsilon L} = 2\frac{(W - \alpha_3 W)}{T} + 4\frac{\sqrt{2}}{\pi}\ln(1 + \sqrt{2}) + 2\frac{H}{S} + 4\frac{1}{\pi}\ln\left(1 + \frac{\alpha_3 W}{S}\right)$$

(23)

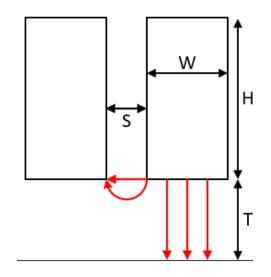

#### 3.2.7 Capacitance Model of Multiple Lines Over a Ground Plane (Special Case)

A special case of the previous section is when multiple interconnect lines placed over a single ground plane. The electric field distribution on the bottom half of the interconnect is exactly same as the previous section, but on the top section as there is no ground plane, we only have corner fringing capacitance and topwall-to-topwall fringing capacitance as shown in Figure 3.2.10.

*Figure 3.2.10:* Electric field distribution of multiple interconnect line over a single ground plane.

The corner fringing field and the topwall-to-topwall fringing field can be formulated as Eq. (24) and Eq. (25).

$$C_{fringe,corner-top} \approx \int_{0}^{S} \frac{dr}{\pi \sqrt{\frac{(r^2 + S^2)}{2}}} = \frac{\sqrt{2}}{\pi} \ln(1 + \sqrt{2}) \times \alpha_5$$

(24)

$$C_{fringe,topwall-topwall} = \int_{S}^{S+W} \frac{dr}{\pi r} = \frac{1}{\pi} \ln\left(1 + \frac{W}{S}\right)$$

(25)

So the total capacitance when  $S > \frac{3}{2}T$  is the summation of  $C_{PP}$ ,  $C_{fringe,corner}$ ,  $C_{fringe,topwall-topwall}$ ,  $C_{fringe,corner-top}$ ,  $C_{fringe,sidewall}$ , and  $C_{fringe,side-bottomwall}$  as shown in Eq. (26).

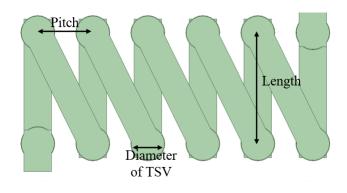

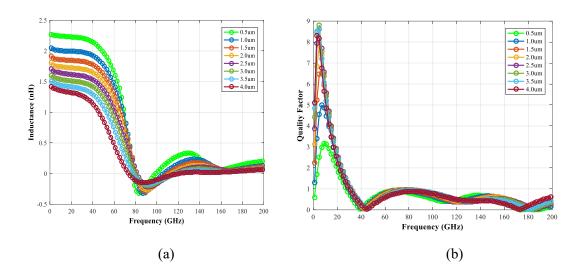

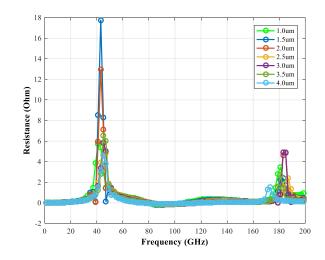

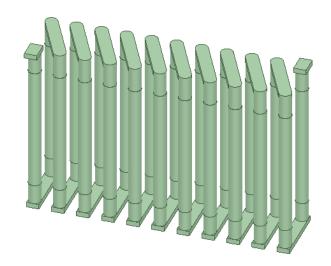

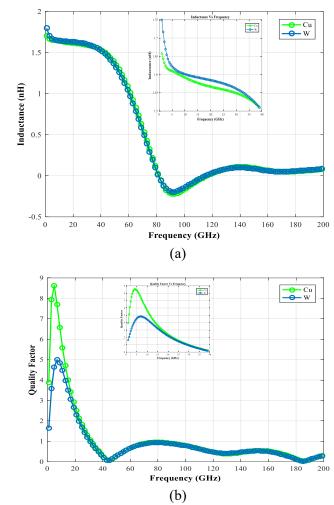

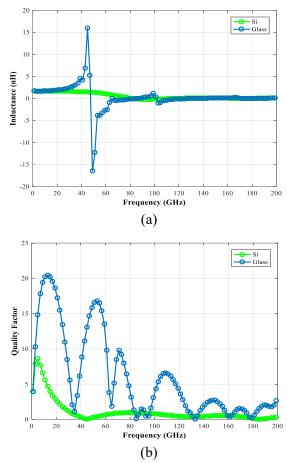

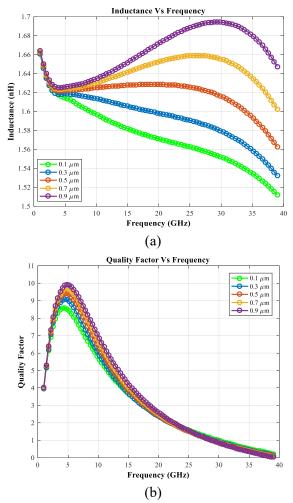

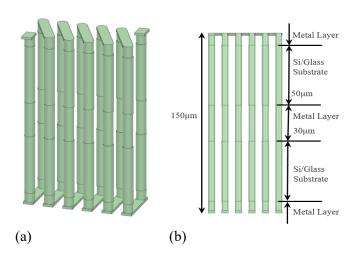

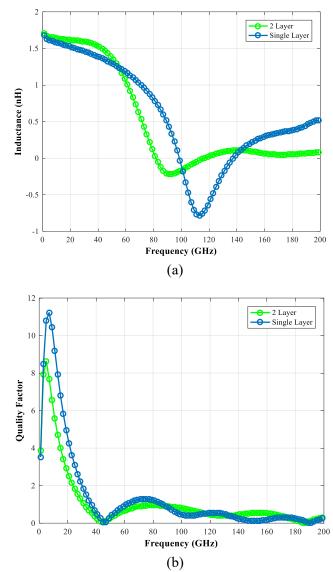

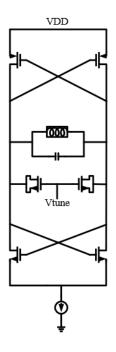

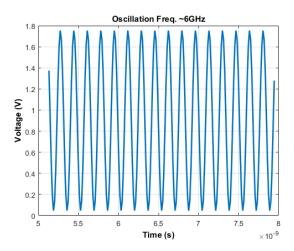

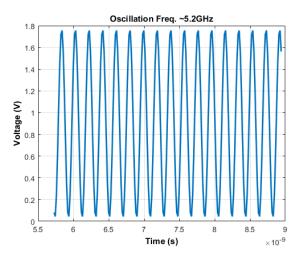

$C_{total} = C_{PP} + 2C_{fringe,corner} + 2C_{fringe,sidewall} + 2C_{fringe,side-bottomwall} + 2C_{PP,sidewall} + 2C_{fringe,corner-top} + C_{fringe,topwall-topwall}$