# ON-CHIP VOLTAGE REGULATOR- CIRCUIT DESIGN AND AUTOMATION

# A Dissertation in Electrical and Computer Engineering and Computer Science

Presented to the Faculty of the University of Missouri–Kansas City in partial fulfillment of the requirements for the degree

# DOCTOR OF PHILOSOPHY

by

## FARID UDDIN AHMED

Master of Science (M.Sc) in Electrical and Computer Engineering, University of Missouri-Kansas City, Missouri, USA, 2020

> Kansas City, Missouri 2021

© 2021 FARID UDDIN AHMED ALL RIGHTS RESERVED

## ON-CHIP VOLTAGE REGULATOR- CIRCUIT DESIGN AND AUTOMATION

Farid Uddin Ahmed, Candidate for the Doctor of Philosophy Degree

University of Missouri-Kansas City, 2021

## ABSTRACT

With the increase of density and complexity of high-performance integrated circuits and systems, including many-core chips and system-on-chip (SoC), it is becoming difficult to meet the power delivery and regulation requirements with off-chip regulators. The off-chip regulators become a less attractive choice because of the higher overheads and complexity imposed by the additional wires, pins, and pads. The increased I2R loss makes it challenging to maintain the integrity of different voltage domains under a lower supply voltage environment in the smaller technology nodes. Fully integrated on-chip voltage regulators have proven to be an effective solution to mitigate power delivery and integrity issues. Two types of regulators are considered as most promising for on-chip implementation: (i) the low-drop-out (LDO) regulator and (ii) the switched-capacitor (SC) regulator. The first part of our research mainly focused on the LDO regulator. Inspired by the recent surge of interest for capless voltage regulators, we presented two fully on-chip external capacitor-less low-dropout voltage regulator design.

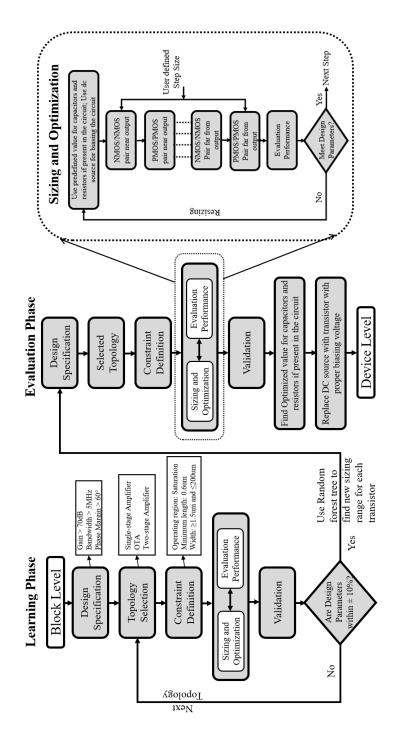

The second part of this proposal explores the complexity of designing each block of the regulator/analog circuit and proposed a design methodology for analog circuit synthesis using simulation and learning-based approach. As the complexity is increasing day-by-day in an analog circuit, hierarchical flow mostly uses for design automation. In this work, we focused mainly on Circuit-level, one of the significant steps in the flow. We presented a novel, efficient circuit synthesis flow based on simulation and learning-based optimization methods. The proposed methodology has two phases: the learning phase and the evaluation phase. Random forest, a supervised learning is used to reduce the sample points in the design space and iteration number during the learning phase. Additionally, symmetric constraints are used further to reduce the iteration number during the sizing process. We introduced a three-step circuit synthesis flow to automate the analog circuit design. We used Hspice as a simulation tool during the evaluation phase of the proposed methodology. The three most common analog circuits are chosen: single-stage differential amplifier, operational transconductance amplifier, and two-stage differential amplifier to verify the algorithm. The tool is developed in Python, and the technology we used is 0.6um. We also verified the optimized result in Cadence Virtuoso.

### APPROVAL PAGE

The faculty listed below, appointed by the Dean of the School of Graduate Studies, have examined a dissertation titled "On-chip Voltage Regulator– Circuit Design and Automation," presented by Farid Uddin Ahmed, candidate for the Doctor of Philosophy degree, and hereby certify that in their opinion it is worthy of acceptance.

# Supervisory Committee

Masud H Chowdhury, Ph.D., Committee Chair Department of Computer Science Electrical Engineering

Yugyung Lee, Ph.D., Co-discipline Advisor Department of Computer Science Electrical Engineering

Ghulam Chaudhry, Ph.D., Committee Member Department of Computer Science Electrical Engineering

Ahmed Hassan, Ph.D., Committee Member Department of Computer Science Electrical Engineering

Cory Beard, Ph.D., Committee Member Department of Computer Science Electrical Engineering

# CONTENTS

| A              | BSTR                  | ACT                                                | iii  |  |  |  |  |  |  |

|----------------|-----------------------|----------------------------------------------------|------|--|--|--|--|--|--|

| LI             | LIST OF ILLUSTRATIONS |                                                    |      |  |  |  |  |  |  |

| LIST OF TABLES |                       |                                                    |      |  |  |  |  |  |  |

| A              | CKNC                  | WLEDGEMENTS                                        | xiii |  |  |  |  |  |  |

| Cł             | napter                |                                                    |      |  |  |  |  |  |  |

| 1              | INTF                  | RODUCTION                                          | 1    |  |  |  |  |  |  |

|                | 1.1                   | Motivation                                         | 1    |  |  |  |  |  |  |

|                | 1.2                   | Thesis Objective                                   | 3    |  |  |  |  |  |  |

| 2              | ON-0                  | CHIP POWER DELIVERY SYSTEM                         | 7    |  |  |  |  |  |  |

|                | 2.1                   | Background                                         | 7    |  |  |  |  |  |  |

|                | 2.2                   | Voltage Regulator Classification                   | 11   |  |  |  |  |  |  |

| 3              | FUN                   | DAMENTALS OF ON-CHIP VOLTAGE REGULATOR             | 21   |  |  |  |  |  |  |

|                | 3.1                   | Low-dropout Voltage Regulator (LDO)                | 21   |  |  |  |  |  |  |

|                | 3.2                   | Switched Capacitor Voltage Regulator               | 24   |  |  |  |  |  |  |

| 4              | LDO                   | DESIGN IN 45NM TECHNOLOGY                          | 30   |  |  |  |  |  |  |

|                | 4.1                   | Proposed LDO Design                                | 30   |  |  |  |  |  |  |

|                | 4.2                   | Modeling Frequency Response of The Proposed Design | 37   |  |  |  |  |  |  |

|                | 4.3                   | Simulation and Result Analysis                     | 40   |  |  |  |  |  |  |

|                | 4.4                   | Comparison with Prior Works                        | 46   |  |  |  |  |  |  |

| 5 | LDO | DESIGN IN 180NM TECHNOLOGY                                  | 52  |

|---|-----|-------------------------------------------------------------|-----|

|   | 5.1 | Proposed LDO Design                                         | 52  |

|   | 5.2 | Modeling Frequency Response of The Proposed Design          | 57  |

|   | 5.3 | Simulation and Result Analysis                              | 59  |

|   | 5.4 | Comparison with Prior Works                                 | 62  |

|   | 5.5 | Application                                                 | 63  |

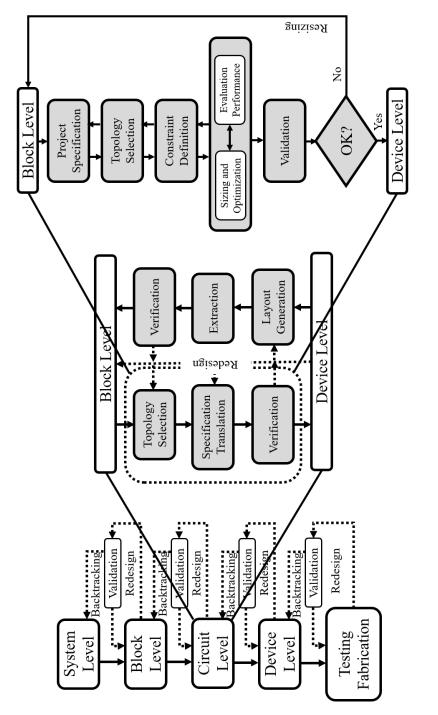

| 6 | ANA | LOG DESIGN AUTOMATION                                       | 66  |

|   | 6.1 | Background                                                  | 66  |

|   | 6.2 | Analog design Flow                                          | 68  |

| 7 | PRO | POSED ANALOG DESIGN METHODOLOGY                             | 75  |

|   | 7.1 | Methodology                                                 | 75  |

|   | 7.2 | Implementation of the proposed methodology                  | 82  |

|   | 7.3 | Result and Analysis                                         | 89  |

| 8 | ENE | RGY EFFICIENT FDSOI AND FINFET BASED POWER GATING CIR-      |     |

|   | CUL | Γ USING DATA RETENTION TRANSISTOR                           | 93  |

|   | 8.1 | Background                                                  | 93  |

|   | 8.2 | Characteristics of Devices                                  | 95  |

|   | 8.3 | Working Principle of Proposed Design                        | 98  |

|   | 8.4 | Benchmarking between FDSOI and FinFET based NAND logic gate | 100 |

| 9 | CON | ICLUSIONS & FUTURE WORK                                     | 103 |

|   | 9.1 | Summary                                                     | 103 |

|   | 9.2 | Future Work                                                 | 104 |

| REFE | RENCE | LIS | Τ. | • | • |  | • | • | • | • | • | • | • | • | • | • | • | • | <br>• | • | • | • | • | • | • | • | • | • | • | • | • | • | 106 |

|------|-------|-----|----|---|---|--|---|---|---|---|---|---|---|---|---|---|---|---|-------|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|

| VITA |       |     |    | • | • |  |   |   | • |   |   |   | • | • |   |   |   | • |       | • |   | • |   |   |   |   |   | • | • | • | • |   | 121 |

# LIST OF ILLUSTRATIONS

| Figure | F                                                                            | age |

|--------|------------------------------------------------------------------------------|-----|

| 1      | Different distributed power delivery system (a) off-chip implementation      |     |

|        | (b) having on-chip linear regulators with external on/off-chip switching     |     |

|        | regulators (c) having on-chip switching regulators with only one external    |     |

|        | on/off-chip switching regulator.                                             | 9   |

| 2      | Block diagram of (a) series Linear Regulator and (b) shunt Linear Regulator. | 14  |

| 3      | Example of step-down (a) switched-inductor converter and (b) switched-       |     |

|        | capacitor converter.                                                         | 15  |

| 4      | Different Switched-capacitor regulator topology                              | 17  |

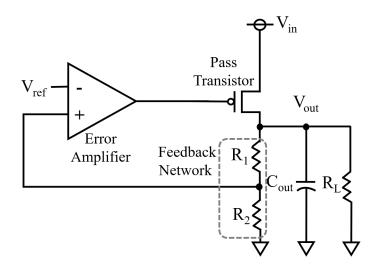

| 5      | Basic structure of an LDO                                                    | 22  |

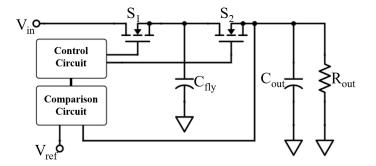

| 6      | Basic structure of an SC regulator                                           | 25  |

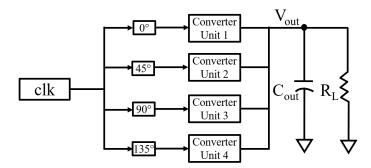

| 7      | A simple 4-phase interleaved SC converter                                    | 26  |

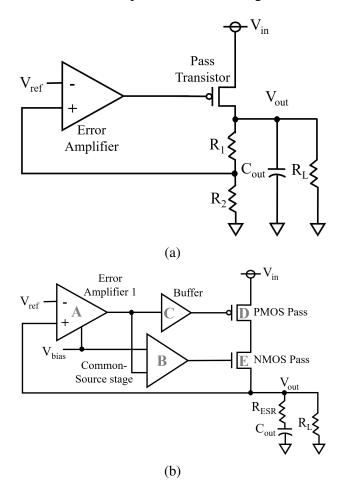

| 8      | Block diagram of (a) traditional LDO and (b) proposed design                 | 31  |

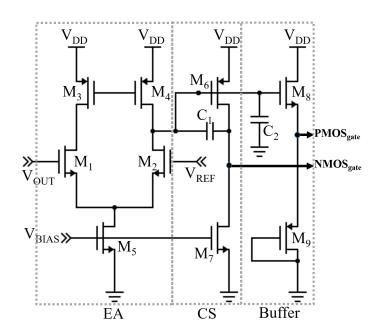

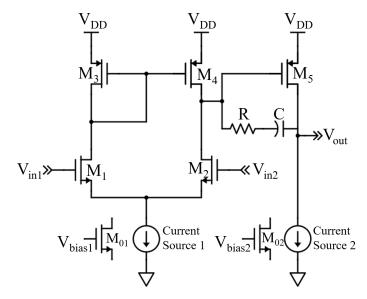

| 9      | Schematic diagram of EA, CS and buffer.                                      | 32  |

| 10     | Schematic diagram of supply independent biasing network                      | 34  |

| 11     | Output current of the supply independent biasing network                     | 35  |

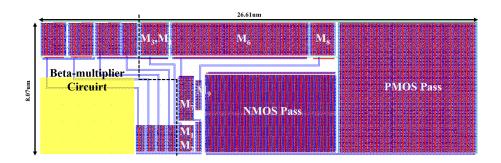

| 12     | Transistor level layout of the proposed design                               | 37  |

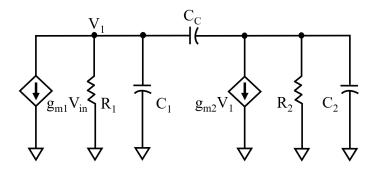

| 13     | Small signal equivalent circuit of the EA and CS stage                       | 38  |

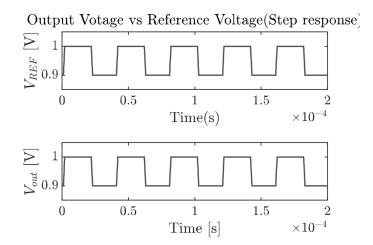

| 14 | Reference tracking response of the regulator with a step in the input ref- |    |

|----|----------------------------------------------------------------------------|----|

|    | erence voltage from 900mV to 1.0V                                          | 41 |

| 15 | Load transient response of the proposed regulator with a step of load cur- |    |

|    | rent from 0 to 15mA                                                        | 42 |

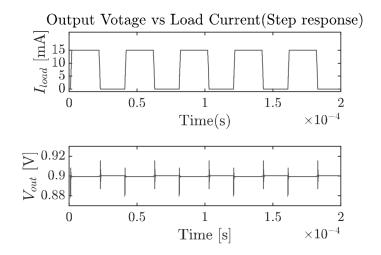

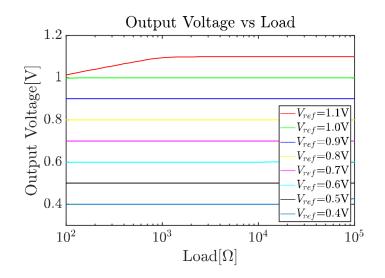

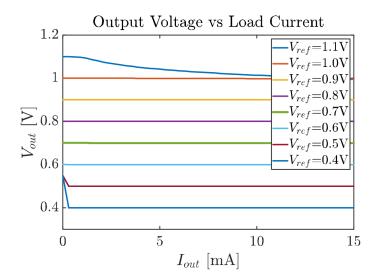

| 16 | Output voltage regulation for various reference voltages and loads         | 43 |

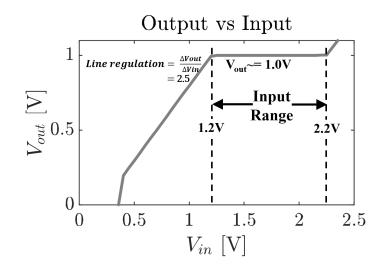

| 17 | Line regulation of the proposed design.                                    | 44 |

| 18 | Output voltage with respect to load current. Output starts to distort for  |    |

|    | $V_{ref} > 1.0$ V                                                          | 44 |

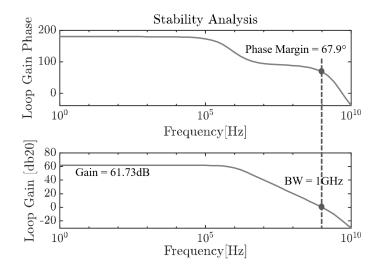

| 19 | Frequency response of the loop consists of EA and CS stage                 | 45 |

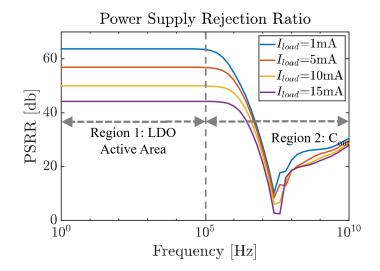

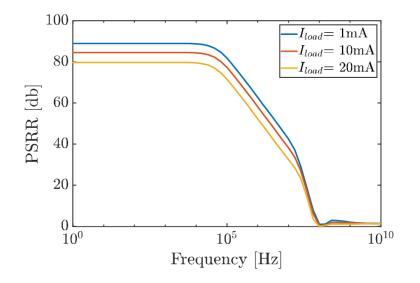

| 20 | PSRR plot of the Proposed LDO Design                                       | 46 |

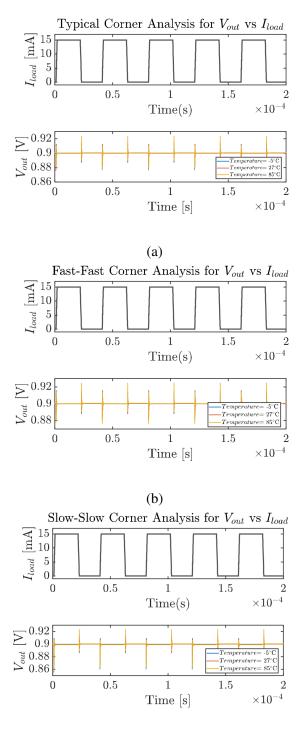

| 21 | Corner Analysis of the Proposed design with step load for (a) typical (b)  |    |

|    | fast-fast and (c) slow-slow.                                               | 48 |

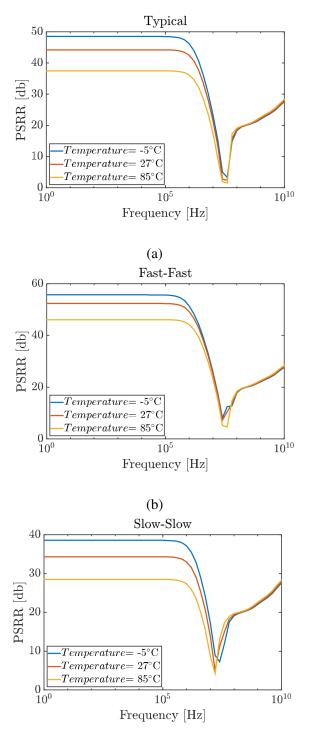

| 22 | Corner Analysis of Proposed design for PSRR (a) typical (b) fast-fast and  |    |

|    | (c) slow-slow                                                              | 49 |

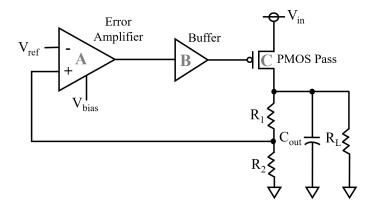

| 23 | Block Diagram of proposed design in 180nm                                  | 52 |

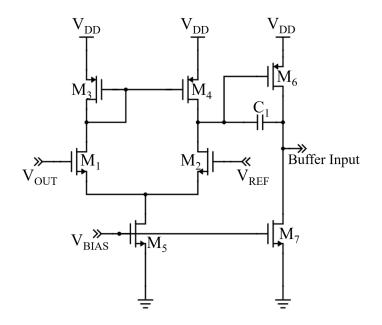

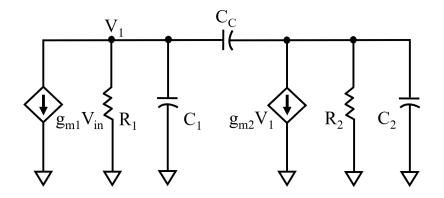

| 24 | Schematic of Error Amplifier Circuit                                       | 53 |

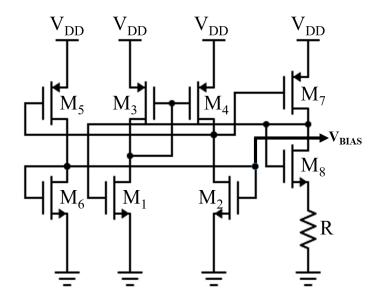

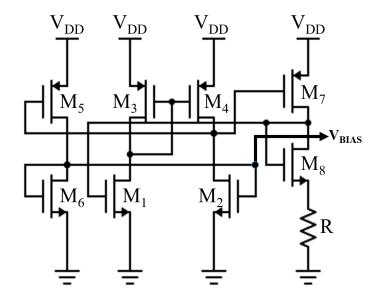

| 25 | Schematic diagram of supply independent biasing network                    | 54 |

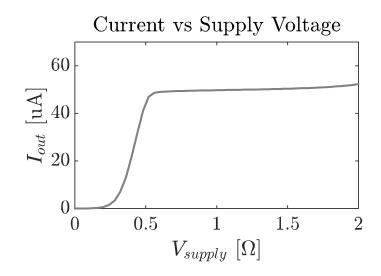

| 26 | Output current of the supply independent biasing network                   | 54 |

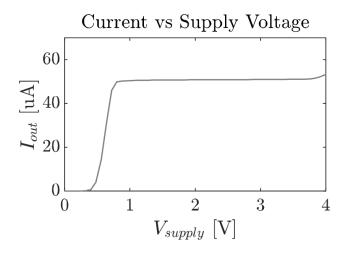

| 27 | Schematic of Voltage follower/Buffer Circuit                               | 56 |

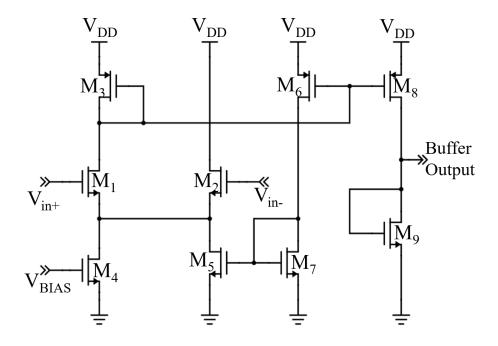

| 28 | Transistor level layout of the proposed design with capacitors             | 58 |

| 29 | Small signal equivalent circuit of two stage Error Amplifier               | 58 |

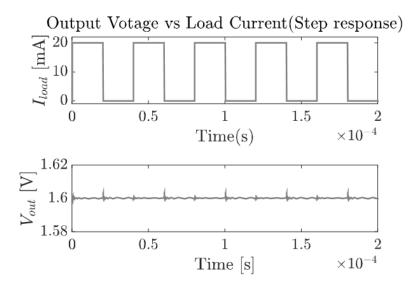

| 30 | Load transient response of the proposed regulator with a step of load cur-  |     |

|----|-----------------------------------------------------------------------------|-----|

|    | rent from 0 to 20mA                                                         | 60  |

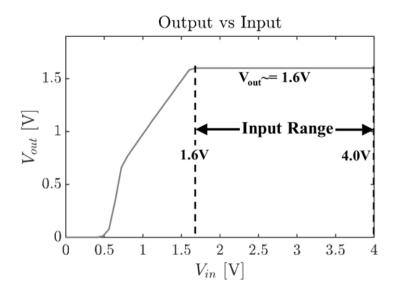

| 31 | Line regulation of the proposed design.                                     | 61  |

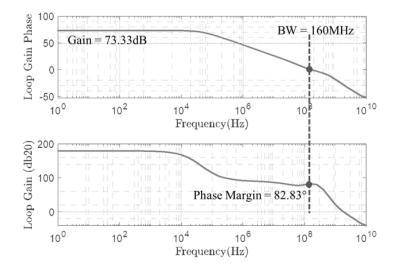

| 32 | Frequency response of the two stage error amplifier                         | 62  |

| 33 | PSRR plot of the Proposed LDO Design                                        | 63  |

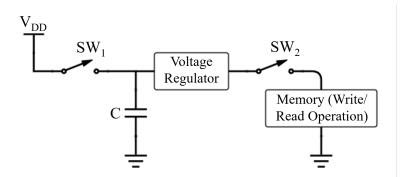

| 34 | Setup Configuration of the proposed memory security                         | 65  |

| 35 | Analog Design flow highlighting top-down circuit-level design flow [1] [2]  | 70  |

| 36 | Proposed circuit synthesis methodology flow                                 | 76  |

| 37 | Relation between iteration number and a) transistor step size b) transistor |     |

|    | count                                                                       | 80  |

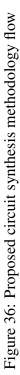

| 38 | Circuit diagram of a Single-stage Differential Amplifier                    | 84  |

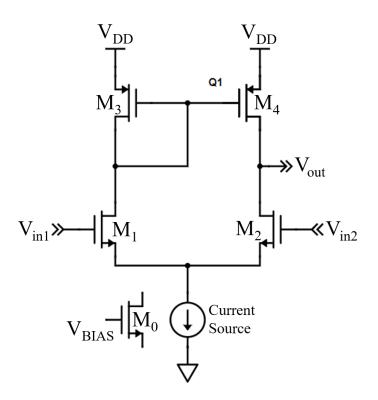

| 39 | Circuit diagram of an Operational Transconductance Amplifier                | 85  |

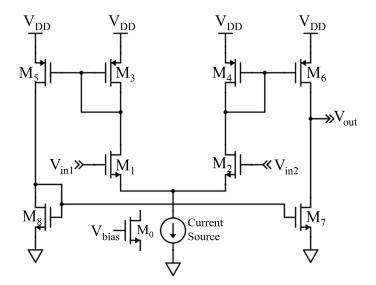

| 40 | Circuit diagram of a Two-stage Differential Amplifier                       | 85  |

| 41 | Implementation of Random decision forest for Single-stage Amplifier         |     |

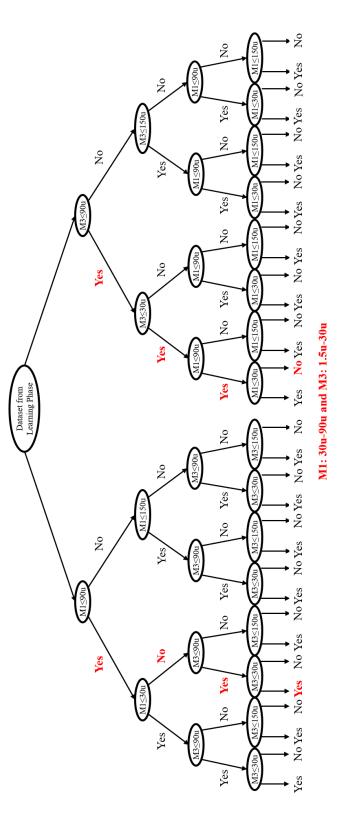

|    | transistor Sizing                                                           | 88  |

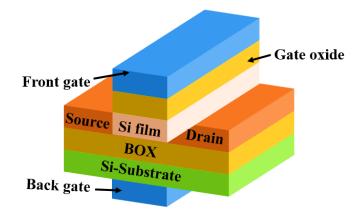

| 42 | Double gate FDSOI device                                                    | 95  |

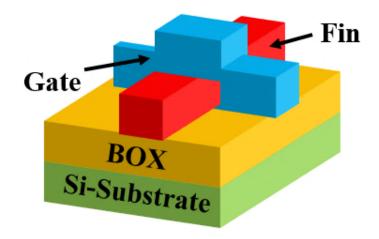

| 43 | FinFET device on a SOI structure                                            | 96  |

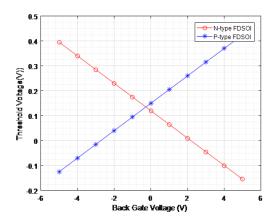

| 44 | Threshold Voltage Dependence upon back gate bias for FDSOI                  | 97  |

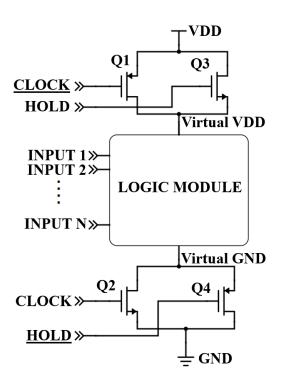

| 45 | Power gating technique using sleep transistor and data retention transistor |     |

|    | for any Logic Module.                                                       | 99  |

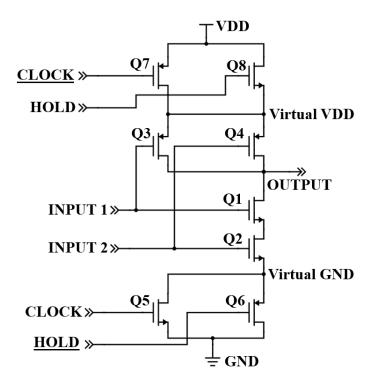

| 46 | Power gating technique using sleep transistor with data retention transis-  |     |

|    | tor for 2-input NAND gate                                                   | 101 |

# LIST OF TABLES

| Tables |                                                                       | Page |

|--------|-----------------------------------------------------------------------|------|

| 1      | Summary of differences between Linear and switching regulator         | 20   |

| 2      | Design Parameters of Fig. 9                                           | 33   |

| 3      | Specifications of the Proposed LDO                                    | 36   |

| 4      | Corner analysis value for PMOS and NMOS pass transistor               | 47   |

| 5      | Corner analysis value of the step response at different temperature   | 47   |

| 6      | Comparison with Prior Work                                            | 51   |

| 7      | Specifications of the Proposed LDO                                    | 57   |

| 8      | Comparison with Prior Work                                            | 64   |

| 9      | Three set of Design Specifications                                    | 83   |

| 10     | Accuracy of three different classification algorithm                  | 89   |

| 11     | Iteration number and execution time of the proposed methodology for   |      |

|        | three diferent topology                                               | 90   |

| 12     | Result comparison between specifications achieved from Hspice and Ca- |      |

|        | dence Simulation                                                      | 91   |

| 13     | Modes of operation depending on control signal.                       | 100  |

| 14     | Performance summary of FDSOI and SOI-FINFET based NAND gate           | 102  |

#### ACKNOWLEDGEMENTS

Foremost, I would like to express my sincere gratitude to my advisor Prof. Masud H Chowdhury for the continuous support of my Ph.D study and research, for his patience, motivation, enthusiasm, and immense knowledge. His guidance helped me in all the time of research and writing of this thesis. I could not have imagined having a better advisor and mentor for my Ph.D study.

Besides my advisor, I would like to thank the rest of my thesis committee: Prof. Yugyung Lee, Prof. Ghulam Chaudhry, Prof. Ahmed Hassan, and Prof. Cory Beard, for their encouragement and insightful comments.

I thank my fellow labmates in Micro & Nano-electronics Lab Group: Abdul Hamid B. Yousuf, Marouf Khan, Moqbull Hossain, Mahmood Uddin Mahood, Liaquat Ali, Hemanshu Shishupal, Athiya Nizam and Zarin Tasnim Sandhie, for the stimulating discussions, for the long days we were working together before deadlines, and for all the fun we have had in the last four years.

I would also like to thank my family: my parents Late Abu Taher Sarker and Farida Akhter, for giving birth to me at the first place and supporting me spiritually throughout my life. Last but not the least, I would like to thank my wife, Zarin Tasnim Sandhie and my daughter, Amayah Fareeza Ahmed for giving me strength and meaning to successfully complete my PhD.

## CHAPTER 1

#### INTRODUCTION

#### **1.1 Motivation**

According to the VLSI industry's demand to minimize the power dissipation and meet the current demand for high-performance microprocessors, the dual-VDD microprocessor was proposed [3,4]. Later, to maximize the utilization of chip area and low power consumption, system-on-chip was introduced. The basic idea is to integrate all computer or other electronic system components into a single chip. As different components require different voltage to operate on-chip, voltage regulation becomes one of VLSI's promising fields. Moreover, due to the dynamic switching power's quadratic dependence and the more than linear dependence of the gate oxide and sub-threshold leakage on the supply voltage, power dissipation is significantly diminished when parts of a microprocessor operating at a lower voltage level. Different approaches are made and proposed for voltage regulation.

Voltage regulators, which are the integral parts of the power delivery systems of all microelectronic circuits and systems, are traditionally off-chip devices placed on the motherboard to deliver regulated voltage to different integrated circuits and components of the systems. Typically, these off-chip regulators are made of power transistors and large passive components like inductors and capacitors with significant footprints, which are not as scalable as the on-chip logic transistors and interconnects. With the introduction of multi-/many-core chips and system-on-a-chip (SoC), dynamic voltage and frequency scaling (DVFS) has become the standard approach to achieve optimum performance with the minimum number of voltage sources [5]. Different components/cores of the high-performance and high-density chips require different voltages. These voltages often need to be adjusted quickly. Slow off-chip regulators limit the scope of performance energy efficiency improvement. Nowadays, a complex integrated circuit requires an increasing number of voltage domains to increase computational resources by utilizing parallelism within a strict thermal and power budget. Because of this requirement, the extent of the power supply's scalability has become further limited. Slow off-chip voltage regulators would not be able to modify the supply voltages in response to varying on-chip load and activity at nano/picosecond timescale.

The number of cores and on-chip functional blocks are increasing in Soc. There are an increasing need and an inherent benefit to utilizing an individual power supply for each core/functional block to optimize the total chip power and performance. These additional off-chip regulators will increase the power supply impedance due to a separate package power plan and a limited number of pins, which will degrade performance and power efficiency. Additional off-chip regulators also lead to additional costs due to the increased motherboard size and package complexity. The power and performance constrained applications like sensors, and biomedical devices need to overcome these problems. Thus, on-chip voltage regulators have become an indispensable part of the traditional microprocessors' power management scheme. One of the primary objectives of the on-chip voltage regulator is to lower the supply voltages whenever possible. Lower

voltage level leads to a quadratic reduction of dynamic switching power and more than the linear reduction of the sub-threshold and gate leakage power. On-chip regulators can provide fast voltage scaling, and multiple on-chip power domains with various voltage and current specifications [6]. The key motivations to integrate voltage regulators on the chip are: (i) minimizing the conduction and parasitic losses in the power delivery system by reducing the interconnect length between the regulator and the processor, and (ii) reduction of the response time of the feedback control.

For on-chip implementation, two different types of VRs are mostly explored in the recent literature; Switching VR and linear VR. Whereas switching VR offers the highest efficiency, linear VR is free from any switching noise, possesses ripple rejection capacity, low voltage noise, and is less complicated [7]. The linear regulators have the advantages of low output noise, fast response time, and smaller area overhead, but their efficiency is lower compared to the switching regulator.

#### **1.2** Thesis Objective

Due to the exponentially increasing demand for portable and mobile devices, the design complexity in the field of System-on-Chip (SoC) is increasing considerably. The industrial need is concentrated towards high-performance circuit design, which requires very low power but enables high-speed operation [8–10]. In addition to that, the need for a self-regulating power supply or Voltage Regulator (VR) for every functional block is also increasing because it optimizes the total power and performance of the chip by

turning it off during the idle period. Incorporating an off-chip VR lowers the powerefficiency and performance as the power-supply impedance substantially rises owing to the split-package power planes and limited PINs. On the other hand, an on-chip VR saves area and enables power-efficient, high-speed, and secure localized voltage regulation [6]. Due to these reasons mentioned above, on-chip VRs have become a vital portion of a conventional microprocessor circuit's power management scheme along with the power and performance constrained applications like sensors and biomedical devices as it can provide noise and ripple-free supply voltage throughout the complete chip [11] [12].

Two different types of VRs are mostly investigated in the previous literatures, such as: Switch-Cap [13] [14] [15] and linear VR [11] [12] [16] [17]. Whereas switch-cap VR offers the highest efficiency, linear VR is free from any switching noise, possesses ripple rejection capacity, low voltage noise, and is less complicated [7]. Hence, linear voltage regulators are preferable to other types of voltage regulators. Low- DropOut (LDO) is a type of linear VR which can provide output voltage close to the input voltage (the difference between the output voltage and input voltage <1V).

Two types of LDO can be found in the literature: analog and digital. Usually, lower technology nodes are used to design digital LDO, whereas higher is preferable for analog [18] [19] [20]. Analog LDO is preferred for on-chip implementation because digital LDO consumes more area and are more complex to design. In this work, we consider only analog LDO, and henceforth the term *LDO* denotes *analog LDO*.

Several researches on Fully integrated LDO VRs are available where the scope of design is mostly confined to technology nodes above 90nm [16] [17] [21] [22] [23] [24].

A limited number of literatures are available for less than 90nm technology nodes as analog blocks' power supply rails become more noise-prone in lower nodes. The lowfrequency noise in a MOSFET increases gradually with decreasing gate area. As a result, for a specific W/L ratio, a larger L means a larger W, which results in more gate area and lower noise. Few other drawbacks of working with lower technology nodes are the electromigration process, higher leakage current, quantum effects, etc. To maintain minimal noise and alleviate the issues mentioned above, higher technology node is preferred in analog circuits. Few designs of LDO VR are proposed with 65nm node [21] [25] [26] and some are in 45nm and beyond where mostly Silicon-On-Insulator (SOI) structure are used [27] [28] [29] [30] [31]. Generally, a large capacitor is used at the LDO's output to enhance the Power Supply Rejection Ratio (PSRR). This large capacitor consumes a large area in case of an on-chip implementation and generates a large area-overhead. To alleviate the issue, occasionally, off-chip capacitors are utilized. For the fabrication of a VR block along with the SoC or functional blocks receiving power supply from VR, two different technology processes are needed by the industry, which makes the fabrication process more complicated as SoC is generally implemented in the sub-nm region. In our paper, we propose an external capacitor-less LDO design in 45nm CMOS bulk technology, which offers low power and high PSRR and includes a small on-chip output capacitor. For fabrication, we designed another capless LDO in TSMC 180nm using traditional LDO design concept. The main contributions of this work is as follows:

1. Proposed fully on-chip LDO designs in 45nm and 180nm CMOS technology;

2. Introduced an additional feedback loop in the traditional LDO to improve transient

response and PSRR

- 3. Designed the LDO with very small active area and wide output range;

- 4. Presented DC, transient and stability analysis of the proposed design;

- Presented corner analysis and the effect of temperature variation on the proposed design;

- 6. Compared proposed designs with the state-of-the-art prior works.

There is an extensive manual work and time involved to design each block of an analog circuit like LDO regulator. To investigate this issue, we explored the analog design flow and proposed a methodology for analog circuit synthesis. We took error amplifier from LDO as an example to implement our methodology. We also developed a tool in python to control the flow of the methodology. The main contributions of this work is as follows:

- 1. Proposed a fully design methodology for analog circuit synthesis;

- 2. Introduced two phase optimization for topology selection and transistor sizing

- 3. Introduced three abstraction level to synthesize analog circuit correctly;

- 4. Used random forest tree and symmetric constraints to reduce the iteration and find optimize sizing which will eventually reduce flow completion time;

- 5. Developed a tool to run the proposed methodology in Hspice.

## CHAPTER 2

#### **ON-CHIP POWER DELIVERY SYSTEM**

#### 2.1 Background

On-chip power management is usually limited to power gating for digital circuits and linear regulators for analog circuits. Power gating can minimize the leakage current while the primary circuit is off. Most of the power gating schemes need additional circuitry to maintain the state of the logic elements during the off state, leading to the extra area and power overheads because of the additional circuitry's switching losses and IR drop. Besides, power gating techniques cannot support dynamic voltage and frequency scaling (DVFS). Linear regulator technology such as the low-drop-out regulator (LDO) mostly able to satisfy these objectives of DVFS for low-noise implementation. However, the linear regulators have low efficiency due to their limited voltage conversion ratio (VCR). Therefore, LDOs are not commonly used for the DVFS scheme and power domains requiring high currents (in SoCs and high-performance microprocessors). LDOs are usually used for analog circuits that require good supply noise rejection, and efficiency is relatively less critical. In these applications, the regulator power consumption is insignificant compared to the whole chip's total power. For applications where higher efficiency and a more comprehensive range of output voltages are critical, the switching regulators are the only alternative. The linear regulators have the advantages of low output noise, fast response time, and smaller area overhead, but their efficiency is lower compared to the switching regulator. Switching regulators are widely used in power constraint systems due to their higher efficiency and performance [32].

In 2003, on-chip integration of a switching regulator (a high-efficiency monolithic buck-converter [3]) was demonstrated on the same die as a dual-VDD microprocessor. Both the inductive and capacitive components were used in that design. However, onchip integration of the traditional switching regulators (mostly buck converters) is very challenging due to large inductors in these circuits. Integrating physical inductors inside the chip is very inefficient and costly. Therefore, there has been a growing interest in designing inductor-less or emulated inductor-based switching regulators for on-chip implementation [33]. The active filter-based circuit topology is proposed in 2005 [34] to improve the switching voltage regulator circuit in size and cost perspective. It is theoretically shown that with active filters, it is possible to obtain transfer functions nearly the same as the LC low pass filters with much less area. In 2010, a fully integrated SC converter with different step-down ratios was presented to spread the output voltage range [35]. The primary purpose of this design was to achieve high-power efficiency across a wide range of output voltages. However, the on-chip voltage regulators induce additional problems like added power loss, area consumption, and increased susceptibility to the load current steps. A detailed system-level analysis of fast and per-core DVFS using on-chip switching regulators has been done in [5] to explore the potential benefits of on-chip regulators. The analysis also shows how the overall system power consumption can be reduced, providing fine-grained power management and fast voltage scaling with an on-chip regulator [5].

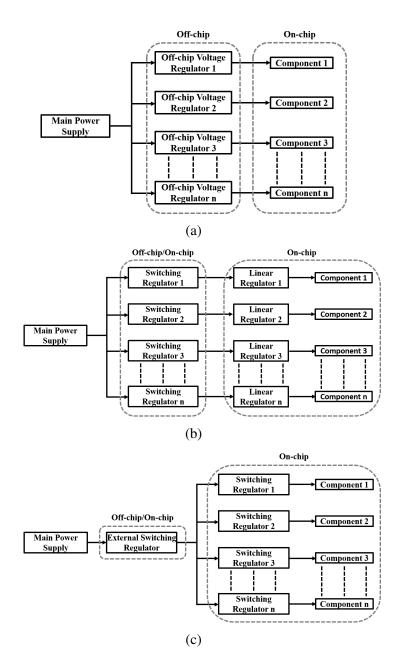

Some hybrid implementations explored the possibility of integrating the switching

Figure 1: Different distributed power delivery system (a) off-chip implementation (b) having on-chip linear regulators with external on/off-chip switching regulators (c) having on-chip switching regulators with only one external on/off-chip switching regulator.

and the linear regulators to take advantage of both [36–39]. In [38], a hybrid two-stage power delivery system with off-chip buck converters and a tree of on-chip linear regulators has been proposed. These hybrid regulation schemes are expected to be efficient and straightforward in design and achieve higher power efficiency and lower noise, area, and voltage overheads. The regulators generate the desired supply voltage from a higher input voltage, thereby becoming an independent supply source for each voltage domain. As a larger conversion ratio leads to lower efficiency, a power management scheme may have several stages of voltage regulators to step-down the primary supply voltage to some intermediate voltages step-by-step. These intermediate stages may consist of either both linear and switching regulators or only switching regulators. In using both types of regulators, switching regulators should be the first stage to achieve higher efficiency with different conversion ratios. In the last stage, linear regulators supply low noise core voltage to the microprocessors and SoCs' components/cores.

Fig. 1 illustrates how regulators can be implemented to provide distributed power delivery with both on-chip and off-chip implementation using linear and switching regulators. The typical all off-chip regulator implementation is shown in Fig. 1a. Distributed on-/off-chip regulators based power delivery scheme is shown in Fig. 1b, where four external switching regulators are used to supply each independent on-chip LDO regulators designated for one specific voltage domain. Each external regulator has different output voltage and current requirements and supplies to each SoC component through the linear regulator. Fig. 1c shows the distributed delivery system consists of only one switching regulator in the first stage and an array of switching regulators in the second stage. Here,

one switching regulator would step down the primary supply voltage to an intermediate value, and each second-stage switching regulator then supplies the core voltage to each component. The original concept of the on-/off-chip hybrid regulation scheme was presented in [?]. It is proposed that the second stage regulators delivering supply voltage to individual core/component should be linear regulators, which would be controlled by the external or internal switching regulators. For the schemes like Fig. 1b and Fig. 1c, the implementation of the first-stage voltage regulators can be either off-chip or on-chip. In the scheme presented in Fig. 1c and [38], with only one single external switching voltage regulator, the motherboard area and circuit overheads used for the power delivery network can be considerably reduced, leading to the improvement of the efficiency of the voltage regulation by  $3\hat{a}4\%$  [5]. However, the active filter based on-chip switching regulators have many functional blocks and very complex circuitry. To reduce the on-chip footprint of these switching regulators, researchers are continually looking for new ways.

### 2.2 Voltage Regulator Classification

Voltage Regulator (VR) is the most essential component of a power management integrated circuit (PMIC). The main objective of a VR is to provide a fixed DC voltage irrespective of input voltage or load condition. There are three essential components of a Voltage Regulator stage in PMIC; pass elements, a feedback circuit, and a stable reference voltage. The feedback circuit senses the output variations and does the error correction by amplifying the error signal. Then generates a control signal which drives the pass element to minimize the output's error/variation based on the reference voltage. Voltage regulators can be categorized into Linear Voltage Regulators, Switching Voltage Regulators [32, 40]. In this survey, the transistor is the pass element in all the state-of-the-art works discussed here. Transistors can be operated in three regions to regulate the voltage at the output. These regions are saturation or active, ohmic or linear, and cut-off region. In linear voltage regulators, the pass transistor works in the linear region of its operation during voltage regulation. When the pass transistor operates and switches in-between the cut-off and saturation state, the regulator is called a Switching Voltage regulator.

# 2.2.1 Linear Voltage Regulator

Linear Voltage Regulators are the original form of regulators in regulating power supplies to the desired output voltage. In a linear voltage regulator, the active pass element (usually a BJT or a MOSFET) is responsible for regulating the output voltage. When a load is connected, the input or load changes will result in a current variation flowing through the transistor so that a fixed voltage is maintained at the output. For the transistor to vary it's current, it must be operated in a linear or ohmic region. A significant amount of wasted power is realized in linear VR, which can be calculated from the difference of input and output voltage. This voltage difference is dropped in the pass element and wasted through heat dissipation. In linear VR, a minimum voltage is needed to get the desired output within the specifications. Often the difference between this minimum input voltage and the output voltage is referred to as dropout voltage. Earlier, linear voltage regulators were sorted into five categories; Positive Adjustable Regulators, Negative Adjustable Regulators, Fixed Output Regulators, Tracking Regulators, Floating Regulators [32, 40]. In all of these categories, they needed several volts to get the desired output voltage. For a well-established linear VR like LM7805, the value was about 2.5V. Since the output is 5V, at least 7.5V is needed at the input. There is a significant increase in the demand for efficient power supplies in today's world, where designers are trying to minimize the wasted power dissipated as heat. The manufacturers are considering to minimize the dropout voltage to as low as 100mV sometimes. As a result, a new type of linear regulator emerges called a low-dropout (LDO) voltage regulator. Nowadays, if the dropout voltage is less than 1V, it is essentially called LDO. For the rest of the paper, we are considering LDO as linear VR.

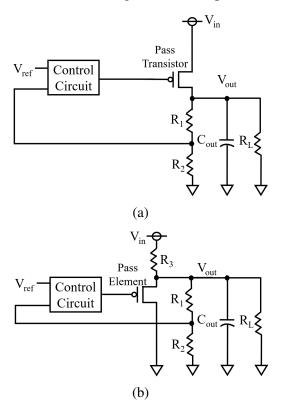

Linear Voltage regulators can be categorized based on how the load is connected to the output. They are Series Voltage Regulators; Shunt Voltage Regulators [40].

#### 2.2.1.1 Series Voltage Regulator

In series voltage regulators, the active pass element (transistor) is connected in series with the load. Fig. 2a shows the basic circuit diagram of the series voltage regulator. The load  $R_L$  is in series with the pass element. In this circuit, the regulator's output voltage is sensed through the voltage divider network  $R_1$  and  $R_2$  and feedback to the control circuit's input. The control circuit then compares this voltage with a reference voltage. The resulting error signal controls the conduction of the pass element. Irrespective of the load, the output voltage will be maintained by changing the pass element's conduction.

# 2.2.1.2 Shunt Voltage Regulator

A Shunt voltage regulator is just the opposite of a Series voltage regulator. The pass transistor here is connected in parallel to the load. Along with the voltage divider network, a voltage limiting resistor,  $R_3$ , is connected in series with the load. Fig. 2b shows a typical shunt voltage regulator. The transistor's conduction is controlled based on the feedback and reference voltage such that the current through the series resistor remains constant. Though the transistor's current varies with varying loads, the voltage across the load should remain constant. When compared to series regulators, shunt regulators are slightly less efficient but have a more straightforward implementation.

Figure 2: Block diagram of (a) series Linear Regulator and (b) shunt Linear Regulator.

# 2.2.2 Switching Voltage Regulators

A switching regulator's operation is different from the Linear Regulator because the pass transistor acts as a switch. The pass transistor switches between off state (cut-off region) and on state (saturation region). The output voltage is maintained at a fixed value by controlling the on-time of the pass transistor.

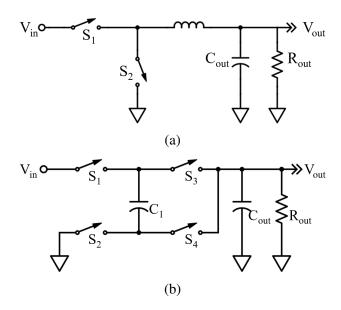

Figure 3: Example of step-down (a) switched-inductor converter and (b) switched-capacitor converter.

Switching regulators are the most promising VR to provide a wide range of output voltages with higher efficiency. In switching regulators, the charge is drawn from the input and stored in one step, and then transferred to the output in the next step. Depending on the storage element, Switching regulators can be classified into two categories based on the energy element [41]; Switched-inductor converter and Switched-Capacitor Converter. Fig. 3 shows two common examples of step-down switching converters using an inductor

and a switched-capacitor (SC) converter. There is no fundamental limit on these switching converters' efficiency in an ideal state with lossless inductors and capacitors. Between these two types, the switched-capacitor converter is our main focus in this paper.

A capacitor has three operation states; charging, discharging, and idle. A capacitor can get charge from a voltage source or other capacitor connected in the circuit. Similarly, the capacitor can discharge to a load or another capacitor in the circuit. The capacitors which are getting charged from or discharged to another capacitor are called intermediate capacitors. These intermediate capacitors increase the level of energy transfer and conduction loss in the circuit. When the capacitor is not transferring or receiving any charge, it is called an idle state. Depending on the way of charge transfer from source to load, SC converter can be divided into two categories; direct-charging-based converters [42].

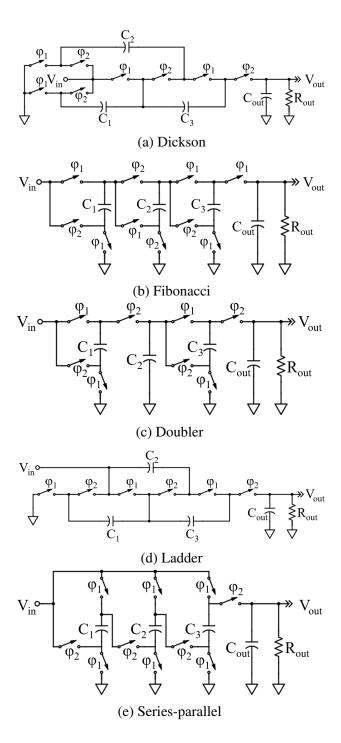

SC-based DC-DC converters typically use five common topologies, including Dickson, Fibonacci, Doubler, Ladder, and Series-Parallel. The first three are considered the up-converter (boost) because the Voltage Conversion Ratio (VCR) of these converters is more than one. The other two topologies (Ladder and Series-Parallel) are downconverter (similar to buck converter) with VCR less than one. Sometimes, Fibonacci and Doubler topologies are called exponential converters because their VCR is exponentially related to the number of capacitors. These implementations support a range of different voltages, but most of the switches are not ground referenced, making them difficult to implement. Ladder and Dickson topologies provide regularity to the power switches and their drivers. In contrast, the Series-Parallel topology has the best capacitor utilization,

Figure 4: Different Switched-capacitor regulator topology

which means it requires the smallest total capacitance for the same performance compared to other topologies. There are two other metrics named Slow-Switching-Limit (SSL) and Fast-Switching-Limit (FSL) to evaluate and compare different converter topologies' performance [43–46].

The SSL impedance is calculated assuming that the switches, capacitors, and interconnect lines are ideal and have very negligible finite resistance. The FSL occurs when the resistances associated with the switches, capacitors, and the interconnect lines dominate, and the capacitors act effectively as fixed voltage sources. In the FSL, current flow occurs in a frequency-independent piece-wise constant pattern, while the SSL impedance is inversely proportional to switching frequency. A set of charge multiplier vectors are associated with these metrics. The performance of a converter is related to the square of the sum of these charge multiplier coefficients. Topologies with a small sum of these coefficients perform better for a given switch conductance than a topology with a large sum of coefficients. These metrics also depend on the conversion ratios of the regulators. For a conversion factor of 2, all the topologies perform almost equal.

In contrast, for higher conversion ratios, in SSL comparison, Series-Parallel topology performs better than others due to lower output impedance. Moreover, Series-Parallel topologies ensure the best utilization of the capacitors and SSL comparison solely dependent on the elements' capacitance values rather than resistance values. In general, no one topology can perform well in terms of both of these metrics. In SSL and FSL comparison, Series-Parallel topology and Ladder topology performs better than other topologies, respectively [43]. Some topologies use switches efficiently, and others use capacitors efficiently, but none of the topologies are superior in both aspects. In the CMOS processes, fully integrated SC converter implementations are typically dominated by the capacitor area and performance. Therefore, Series-Parallel topology is the best topology because it is more efficient in capacitor implementation.

The differences between linear and switching voltage regulators are summarized in Table 1.

|              | Linear Voltage Regulator                                                                                                                                                                                                                                                                                                                | Switching Regulator                                                                                                                                                                                                          |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Working      | Pass element works in the linear re-                                                                                                                                                                                                                                                                                                    | Pass element works in the cut-                                                                                                                                                                                               |

| Principle    | gion. By controlling the conduction                                                                                                                                                                                                                                                                                                     | off or saturation region. By con-                                                                                                                                                                                            |

|              | of the pass element, the output volt-                                                                                                                                                                                                                                                                                                   | trolling the on-off period of the                                                                                                                                                                                            |

|              | age is maintained.                                                                                                                                                                                                                                                                                                                      | pass element, the output voltage is achieved.                                                                                                                                                                                |

| Circuit ele- | Do not need any storage elements                                                                                                                                                                                                                                                                                                        | Need storage element like inductor                                                                                                                                                                                           |

| ment         | for energy transfer.                                                                                                                                                                                                                                                                                                                    | or capacitor for energy transfer in                                                                                                                                                                                          |

| Advantages   | Ease of use, simple design, low<br>cost, free of switching noise, and<br>smaller device size. Robust in over<br>current protection and thermal pro-<br>tection.                                                                                                                                                                         | one or multiple steps<br>Higher efficiency, both step-up or<br>step-down operation is possible. As<br>less power is wasted, less heat emit.                                                                                  |

| Drawbacks    | Low efficiency, only steps down op-                                                                                                                                                                                                                                                                                                     | Higher switching noise, bottom                                                                                                                                                                                               |

|              | eration is possible. Power is wasted                                                                                                                                                                                                                                                                                                    | plate capacitance loss, complex ar-                                                                                                                                                                                          |

|              | through heat dissipation.                                                                                                                                                                                                                                                                                                               | chitecture. Takes more on-chip area than a linear regulator.                                                                                                                                                                 |

| Application  | <ol> <li>Suitable for low power applications with low output current where power requirement is not critical.</li> <li>For noise-sensitive applications, especially for radio devices and communications.</li> <li>Time-sensitive applications.</li> <li>Applications, require output voltage is close to the input voltage.</li> </ol> | <ol> <li>Because of the higher efficiency, suitable for applications where power requirement is critical.</li> <li>Thermal sensitive applications.</li> <li>Suitable for both step-up and step-down applications.</li> </ol> |

Table 1: Summary of differences between Linear and switching regulator

## CHAPTER 3

#### FUNDAMENTALS OF ON-CHIP VOLTAGE REGULATOR

# 3.1 Low-dropout Voltage Regulator (LDO)

PMIC systems are divided into multiple power domains to improve power efficiency, noise isolation and fulfill the purpose of power gating in SoCs. Hence, the required number of voltage regulators are increasing. LDO is used in SoC to provide a stable, noise-free, and accurate output voltage to the components. LDO can be fully integrated into SoCs or work as a standalone PMIC.

#### 3.1.1 LDO Voltage Regulator Architecture

An LDO voltage regulator's basic architecture comprises a voltage reference, an error amplifier, a pass transistor, and a resistor feedback network. LDO has a closed-loop architecture as the system's output is fed back to one of the error amplifier's inputs. So to ensure a stable operation, loop stability analysis should be done. The two necessary stability analysis parameters, gain and phase margin, show if the loop has a stable operating condition in a specific range. An unstable feedback loop can produce ringing, continuous oscillations at the output, which results in a poorly designed voltage regulator.

A traditional LDO VR requires an external capacitor to have an acceptable power supply rejection ratio (PSRR), good transient response, and to ensure the LDO regulator's stability. Along with these advantages mentioned, there are some drawbacks to have an

Figure 5: Basic structure of an LDO

external capacitor. The external capacitor usually has higher values, which takes a large area for on-chip implementation. Most of the time, the external capacitor is used as an off-chip element, which decreases the system's long-term reliability and consumes valuable pins in SoC devices. Some external capacitor free design found in literature where the LDO architecture does not require an external load capacitance. These designs are mentioned as "capacitor less" or "capless" LDO VR. The absence of the external capacitor makes fully on-chip implementation possible for LDO VR. Economically it is a tremendous advantage of capless LDO. Nevertheless, transient performance and PSRR become notably degrade in capless architecture. As a result, designers need to overcome significant design challenges to improve the overall performance of LDO.

## 3.1.2 LDO Voltage Regulator with External Load Capacitor

The off-chip capacitor value can be in the range of a few uF in a typical LDO design. Because of the capacitor's high value, one dominant pole resides at the output, which gives good stability in the overall system. Off-chip capacitors also offer good line and load regulation as well as good power-supply noise rejection. Nonetheless, several practical concerns must be considered when selecting external output capacitors for specific applications. External capacitors are usually bulk and have non-idealities, which can be critical. Two parasitics parameters Effective Series Inductance (ESL) and Effective Series Resistance (ESR), affect the capacitor's performance badly at high frequency.

A capacitor usually has four impedances; ESR, ESL, a large leakage resistor, and the ideal capacitor connected parallel leakage resistor. An ideal capacitor's reactance decreases with increasing frequency. Hence, a minimum ESR is needed so that the total impedance does not go to zero at high frequencies. The total impedance of the output capacitor is calculated from the capacitance and ESR reactance. The dynamic response degrades because of low impedance during the loop stability analysis as the dominant pole reduces phase margin. On the contrary, a large ESR creates a zero that stretches the closed-loop's unity gain frequency, critically worsening the phase margin and making the system unstable.

For stability purposes, the ESR of the output capacitance should be restricted within a particular range of minimum and maximum values. An external load capacitor's wrong selection might cause unnecessary power dissipation, noise, and overall stability problems, which hamper battery and device longevity.

## 3.1.3 Capless LDO Voltage Regulator

For SoC integrated and discrete applications, the capless LDO VR is an intriguing choice for the designers. Without the external load capacitor, fully on-chip implementation will be possible. Moreover, this can translate into a small digital footprint in the printed circuit board (PCB) area, and lower Bill-of-Materials (BOM) costs.

By not having any external capacitor at the output also brings several advantages for capless LDOs. There will be a reduced number of metal paths, bond wires, external pins and pads, package connections, and a decrease in the cost associated with them. In modern complex systems like SoC, several LDO VRs are typically needed. Therefore, eliminating external output capacitors gives a multiplier effect over these benefits. As there is no external capacitor at the output, there is no dominant pole at the output but a dominant internal pole changing with the load current. So it will be a challenging design problem to provide a stable output voltage across a wide range of load current and load capacitors for capless LDOs.

### 3.2 Switched Capacitor Voltage Regulator

Switched capacitor regulators are becoming a popular choice in PMIC for their on chip-implementation. Moreover, they offer a reconfigurable output voltage from a single input voltage with higher power conversion efficiency and design flexibility.

Figure 6: Basic structure of an SC regulator

## 3.2.1 Switched Capacitor Voltage Regulator architecture

A switch capacitor regulator's basic structure consists of switches, capacitors as storage elements, a comparison circuit, and control circuitry (Fig. 6). By controlling the on/off-time of the switches, capacitors transfers charge from input to output. Depending on the condition of the switches, capacitors will be charged or discharged.

The switches' on-off time is controlled by a pulse-width-modulation(PWM) operation, which is usually controlled by the control circuit. The output of the regulator is fed back to the comparison circuit to compare with a reference voltage. The resultant output then feeds to the control circuit to generate a pulse, which eventually controls the switches to charge and discharge the switches. When output falls below the reference level, on-time increases, and more charges are transmitted from the input side or intermediate capacitor to increase the output level. The on-time reduces when the output voltage reaches the reference level to prevent overshoot at the output.

Interleaving is a widespread technique usually used in SC VR design to minimize the ripple at the output [46]. In this technique, the SC regulator is divided into multiple smaller units, and clock signals deliver to each unit with a phase shift in between each unit. A simple 4-phase interleaved SC converter is presented in Fig. 7. This technique benefits in multiple ways. It reduces the input current and the output voltage ripples without redundant input and output decoupling capacitors. To minimize the output ripple, typically, there is a need for a large decoupling capacitor in single phase implementation, which incurs a significant on-chip area. Considering N-phase interleaving implementation, whenever an SC regulator's fly capacitor changes state between charging and discharging, fly capacitors in the remaining N-1 phases efficiently act to minimize the decoupling effect so that the output ripple will be less.

Figure 7: A simple 4-phase interleaved SC converter

The interleaving units' operation is controlled by a single-bound hysteretic control scheme implemented in the feedback loop. The scheme is beneficial for its simple and inherently stable operation and its high bandwidth control. The switches' switching frequency is modulated by this scheme to control the SC converters' equivalent output resistance, which ensures the desired voltage at the output. Switching frequency modulation is a popular regulation technique for on-chip SC converters [44, 45]. The scheme's basic concept is to generate a trigger signal whenever the output voltage is less than the reference voltage at the clock rising edge. The trigger signal causes the shifted clock signal to change the switches' state in the next unit to provide enough charge to make a rise at the output voltage. If the output is less than the reference voltage, no trigger signal is generated, and all the switches will be in the same state.

# 3.2.2 Different types of capacitor used in SC Regulator

The SC regulators would be able to take full advantage of monolithic integration [33, 44, 45, 47]. It is anticipated that the SC regulators can provide higher efficiency and minimize interconnect lengths and losses. SC converters consist only of transistors and capacitors, and it is easy to integrate these components inside the chip [45]. However, the SC regulators have some issues like the bottom plate capacitance of the fly capacitors, the conduction and switching losses in the transistors, the transistors' parasitic capacitances, and the Voltage Conversion Ratio (VCR). These factors negatively affect the SC regulators' performance and make it challenging to obtain the desired voltage level, efficiency, power density, and load currents. The bottom plate parasitic capacitance losses of the on-chip capacitors usually limit the peak efficiency of the converter. These losses occur when the SC converters supply the load by charging and discharging the fly capacitors. The charging and discharging of the bottom plate parasitic capacitance in every clock cycle is a non-desirable impact that imposes the losses. Several designs have been proposed to overcome these limitations and achieve higher efficiency and power density. These design approaches include different capacitors to minimize the parasitic and bottom plate capacitance losses used novel feed-forward control, hysteretic control, and other approaches.

The performance of the SC converters is mostly dependent on the capacitor technology. The most commonly used capacitor technologies are Metal-Oxide-Metal (MOM), Metal-Oxide-Semiconductor (MOS), Metal-Insulator-Metal (MIM), and Deep-Trench capacitors. The fundamental differences among these technologies are in the structure and construction procedure. One of the most crucial factors to design an SC regulator is the fly capacitors' capacitance density. The deep-Trench capacitor is the most suitable one from this perspective because of its inherent 3-D nature that helps achieve larger capacitance using a significantly smaller silicon footprint than the other technologies like MOM, MOS, or MIM. The capacitances obtained from the Deep-Trench technology are more than 100 times denser than the MOS capacitors and thus show a significant improvement in the SC regulators' power density.

The MOM capacitor's capacitance density is 0.2-1fF per  $\mu m^2$  depending on the number of the metal layers and the pitch between the layers. The MIM capacitor has a capacitance density of 1-3fF per  $\mu m^2$ . However, the Deep-Trench capacitor suffers from large series resistance and poor frequency response and exhibits a slower transient response than the equivalent MOS capacitor. The MOM and MIM structures have relatively low series resistance due to the full metal connections and show linearity, making these two technologies suitable for SC regulators' implementation. For the lower-node technologies, the MOS structure is not suitable for low supply voltage [46]. Some literature

uses another kind of capacitor called ferroelectric capacitor in SC VR for their extremely low bottom plate capacitance and high-density [48]. One of the primary sources of losses in the SC regulator is the parasitic capacitors associated with the technological features and on-chip capacitors' manufacturing process. For the MOS and MIM capacitors, parasitic capacitance from the bottom plate to the substrate can reach several percent of the minimal capacity, which may diminish the regulator's efficiency by 10â15% for some ranges of the operating voltages and currents [46]. Different capacitor technologies can be used for the proposed SC voltage regulator depending on a particular application's specifications and requirements.

## CHAPTER 4

#### LDO DESIGN IN 45NM TECHNOLOGY

In this section, we describe the basic blocks of the proposed LDO along with the design specification.

#### 4.1 Proposed LDO Design

The traditional LDO comprises an Error Amplifier (EA), a pass transistor, and a resistive feedback network, as shown in Fig. 8a [49]. In the proposed design, we replace the resistive network with an extra NMOS pass transistor driven by a commonsource (CS) stage. The proposed circuit is shown in Fig 8b. The desired output voltage is achieved by controlling the gate voltage of the two-pass transistors (NMOS and PMOS). A Equivalent Series Resistance (ESR), value of 1 is used here in series of output capacitor for proper modeling.

The purpose of the additional NMOS pass transistor here to get better control of the output voltage regulation and improve the transient response and PSRR. CS stage drives the NMOS based on the amplified output of EA. The NMOS is driven with feedback from the output node with higher amplification leveraging both EA and CS stage, and it is biased in the saturation region.

Note that the reference voltage,  $V_{ref}$  is an input to the LDO and is connected to the negative terminal of EA, which comes from a bandgap reference voltage circuit. We have skipped discussion on the bandgap circuit since that out of the scope of this paper. Details regarding EA, CS, buffer, and pass transistors are given below:

Figure 8: Block diagram of (a) traditional LDO and (b) proposed design.

# 4.1.1 Error Amplifier (EA) and Common-Source (CS) Stage

The EA (Block A in Fig. 8b) is a differential amplifier having one input as a reference voltage and other input coming from the output node as feedback. The output of the EA stage is connected to  $M_6$  of the common-source (CS) stage (Block B in Fig.

8b). In the first stage, the output is compared with the reference voltage and then feeds to the second stage. CS consists of two transistors. The output of EA also goes through the buffer (Block C) and controls the PMOS transistor. The output of CS is fed to the NMOS pass transistor. As the cascaded structure of EA and CS create a two-pole system, one compensator capacitor ( $C_1$  in Fig. 9) of 18fF value is used for the stability purpose. The  $M_5$  and  $M_8$  are biased with a biasing voltage from a supply independent biasing network. (Fig.10).

Figure 9: Schematic diagram of EA, CS and buffer.

# 4.1.2 Biasing Circuit

The biasing network is designed in such a way that it will deliver fixed current irrespective of a range of supply voltage shown in Fig.11. It is a beta-multiplier circuit

| Parameter Name                 | Value          |

|--------------------------------|----------------|

| (W/L) of $M_1, M_2$            | 16/2           |

| $(W/L)$ of $M_3, M_4$          | 40/2           |

| (W/L) of $M_5$                 | 9/2            |

| (W/L) of $M_6$                 | 500/2          |

| (W/L) of <i>M</i> <sub>7</sub> | 53/2           |

| (W/L) of $M_8$                 | 9/2            |

| (W/L) of $M_9$                 | 66/2           |

| (W/L) of NMOS Pass             | 250000/2       |

| (W/L) of PMOS Pass             | 125000/2       |

| $C_1$                          | 18fF (on-chip) |

| $C_2$                          | 10fF (on-chip) |

Table 2: Design Parameters of Fig. 9

with a differential pair in between the current mirrors to reduce the sensitivity over supply voltage. A resistor R is having a value of 720 used in the source of  $M_8$  (Fig. 10) to accurately set the output current.

## 4.1.3 Buffer

A common source follower is used in the proposed design as a buffer stage (Block C in Fig. 8b), which controls the gate voltage of the PMOS pass transistor. The output of the EA drives the buffer stage. A 10fF capacitor ( $C_2$  in Fig. 9) used here as a compensator capacitor between the gate of NMOS ( $M_9$ ) and ground to reduce the effect of noise.

#### 4.1.4 Pass Transistors

The PMOS pass transistor (Block D in Fig. 8b) is the primary driver switch of the proposed design, and the NMOS pass transistor (Block E in Fig. 8b) is used instead of

Figure 10: Schematic diagram of supply independent biasing network.

the resistive feedback network. Pass transistors are chosen with considerable sizing value to provide a sufficient amount of current to the load. Depending on the reference voltage, the output voltage is regulated by controlling two pass transistors' gate voltage. The body of the NMOS pass transistor is tied to the source to reduce the body effect.

#### 4.1.5 Simulation Environment

The LDO in this work is designed using 45nm NCSU PDK [50] bulk CMOS technology in Cadence Virtuoso. All the design parameters, such as (W/L) values of all MOSFETs and capacitor values of Fig. 9, are summarized in Table 2.

Figure 11: Output current of the supply independent biasing network.

# 4.1.6 Design Specification

In lower technology nodes, voltage headroom is a critical issue for the analog circuit as the supply voltage is scaling. Therefore, the LDO is designed for minimum output voltage. The proposed design's input voltage range is 1.2V to 2.2V, and it can generate a range of output voltage from 0.4V to 1.0V depending on the reference voltage (output voltage follows the reference voltage). The proposed LDO achieves a minimum dropout voltage of 200mV. The overall specification of the proposed design is summarized in Table 3.

In the proposed design, there are two feedback loops:

**Loop-1:** Through EA, CS stage, and NMOS. It maintains the DC value of  $V_{out}$ . EA sensed the change in output and delivered the amplified feedback to NMOS through the CS stage. If  $V_{out}$  suddenly drops, NMOS immediately increases the current through

| Parameter            | Specification      |

|----------------------|--------------------|

| Input/Output Voltage | 1.2V-2.2V/0.4-1.0V |

| Voltage Overhead     | <10mV              |

| Line Regulation      | 2.5 (mv/V)         |

| Load Regulation      | 0.0089 (mV/mA)     |

| Load Current         | 15mA (max)         |

| Quiescent Current    | 309uA              |

| $C_{out}$            | 10pF (on-chip)     |

| $\Delta V_{out}$     | 35mV               |

| Area                 | $0.0052mm^{2}$     |

| PSRR                 | max 65dB @100KHz   |

Table 3: Specifications of the Proposed LDO

it by getting the amplified correction form CS. Therefore, the NMOS contributes to the transient response of LDO.

**Loop-2:** Through EA, buffer, and PMOS. It improves the transient response of LDO by changing  $I_{load}$  rapidly for changes in the load. EA senses any changes in  $V_{out}$ . The output of EA changes and delivers feedback to PMOS via the buffer, which corrects the  $V_{out}$  by changing the current.

Advantages of additional loop: Threefold improvement we achieved because of the additional loop (Loop-1).

- 1. The voltage overhead of the output is minimized as output is more controlled by both PMOS and NMOS pass transistors.

- The noise in the supply is now filtered through the series of PMOS and NMOS pass Transistor. Because of that, PSRR is improved in the proposed design.

3. The NMOS pass transistor in an additional loop improved the transient response of the proposed design.

## 4.1.7 Layout of the Proposed Design

The layout of the proposed design is implemented in Cadence Virtuoso (Fig. 12). DRC and LVS checks are done with the Caliber tool [51]. The total active area of the design is  $214.75um^2$ . This does not include area for  $C_1$ ,  $C_2$  and  $C_{out}$ . With all on-chip capacitors, the total calculated area is  $0.0052mm^2$ . In Fig. 12, all the transistors and the inputs are annotated. Metal 1, Metal 2, and Poly are used here for all cell level layout. Parasitic extractions are not possible due to the limitation of the NCSU PDK (usage is limited to academic purposes only).

Figure 12: Transistor level layout of the proposed design.

### 4.2 Modeling Frequency Response of The Proposed Design

In this section, we present the modeling of the proposed design's frequency response using its small-signal equivalent model.

Figure 13: Small signal equivalent circuit of the EA and CS stage

# 4.2.1 Modeling of Loop 1

The cascaded structure of the EA and CS constructs a second-order two-pole system, leading to instability of the design [52]. Therefore, a compensating capacitor is needed. We have considered a capacitor of 18fF as a miller capacitor between the EA and CS stage in this work. This capacitor creates a large separation between the dominant and non-dominant pole and ensures better stability. The small-signal equivalent model is represented in Fig. 13. The gain and poles equations are presented by 4.1 to 4.7. Here, the dominant pole resides on the output of the EA.

$$R_1 = r_{ds4} \| r_{ds2} \tag{4.1}$$

$$R_2 = r_{ds6} \| r_{ds7} \tag{4.2}$$

$$C_1 = C_{db4} + C_{db4} + C_{qs7} \tag{4.3}$$

$$C_2 = C_{db7} + C_{db6} \tag{4.4}$$

$$A_{v} = \frac{V_{out}}{V_{in}} = \frac{g_{m1}g_{m2}R_{1}R_{2}(1 - \frac{sC_{c}}{g_{m2}})}{(1 + \frac{s}{\omega_{p1}})(1 + \frac{s}{\omega_{p2}})}$$

(4.5)

$$\omega_{p1}(Dominant) \cong \frac{1}{g_{m2}R_1R_2C_C} \tag{4.6}$$

$$\omega_{p2}(Non - dominant) \cong \frac{g_{m2}}{C_1 + C_2} \tag{4.7}$$

## 4.2.2 Modeling of Loop 2

There is no need for a miller capacitor for Loop-2 as there is no gain in this configuration. Note that the output impedance of buffer (=  $1/g_{m8}$ ) is lower than that of the compensating and gate capacitor of the PMOS pass transistor since the PMOS is designed with large size. Therefore, the pole moves into the unit-gain frequency of LDO and does not create any stability issue. The buffer's gain is near to unity gain, so the circuit will always be in stable condition.

# 4.2.3 Effect of output capacitor on Power Supply Retection Ratio

This section explains the effect of output capacitor on power supply rejection ratio (PSRR) and how PSRR changes over frequency. The ratio of the change in input to the output voltage it produces is called PSRR. It quantifies LDO's capability to suppress

ripple on the input voltage. The following equation can specify the PSRR of an LDO:

$$PSRR = 20log \frac{V_{input}}{V_{output}} (dB)$$

(4.8)

In our proposed design, the input ripple voltage is divided into output resistance of PMOS and NMOS devices and the output impedance of the LDO. So, equation 4.8 can be written as,

$$PSRR = 20log \frac{r_{dsp} + r_{dsn} + Z_{out}}{Z_{out}} (dB)$$

(4.9)

Here,  $Z_{out}$  = output impedance,  $r_{dsp}$  = output resistance of PMOS Pass and  $r_{dsn}$  = output resistance of NMOS Pass. Output impedance is coming from the output capacitor which can be modeled as capacitance value and Equivalent Series Resistance (ESR).

$$Z_{out} = R_{ESR} + \frac{1}{sC_{out}} \tag{4.10}$$

In low frequency, the capacitance value itself is dominant, but in ultra high frequency, ESR is responsible for LDO's PSRR. For low and ultra high frequency, following equations can be derived from equation 4.9 and 4.10 respectively.

$$PSRR = 20log(1 + sC_{out}(r_{dsp} + r_{dsn}))(dB)$$

(4.11)

$$PSRR = 20log(1 + \frac{r_{dsp} + r_{dsn}}{R_{ESR}})(dB)$$

(4.12)

## 4.3 Simulation and Result Analysis

In this section, we present the transient, DC, and AC analysis of the proposed design. The corner analysis and effect of temperature variation is also discussed here.

#### 4.3.1 Transient Analysis

Transient response is a metric to evaluate an LDO's performance for the change in the input reference voltage and load current variation (i.e., change in the load impedance).

Fig. 14 shows the load transient performance of the LDO for a step in the reference voltage from 900mV to 1.0V. Note that the output voltage is closely following the reference voltage. The voltage overhead (the difference between the reference voltage and output voltage) for the 900mV-1.0V range is below 10mV.

To evaluate the LDO's load transient response to change in the load current, we consider a step in the load current of 15mA with 10ns for both rise and fall time with the desired regulated  $V_{out} = 1.0$  V. Fig. 15 shows the corresponding result. A change in the  $V_{out}$  of 24mV is observed when the load current incurs the step of 15mA.

Figure 14: Reference tracking response of the regulator with a step in the input reference voltage from 900mV to 1.0V.

Figure 15: Load transient response of the proposed regulator with a step of load current from 0 to 15mA.

## 4.3.2 DC Analysis

DC analysis is a metric which evaluates the operating region, line regulation etc. of a LDO. Fig. 16 shows the output voltage regulation for various reference voltages with respect to load current. The output voltage maintains stable irrespective of the load  $> 10^2\Omega$ .

To evaluate LDO's line regulation, we perform a DC analysis to observe output voltage variation by varying the input supply voltage. Fig. 17 shows the corresponding result. We calculate the line regulation as  $\Delta V_{out}/\Delta V_{in} = 2.5$ . The simulation result indicates that the quiescent current of the proposed design is 309uA.

Fig. 18 shows the output voltage with respect to load current for various reference voltages. We observe performance degradation (unregulated output) at a high output load current for the reference voltage = 1.1V. Therefore, the LDO operates accurately within

Figure 16: Output voltage regulation for various reference voltages and loads.

the 0.4V-1.0V output range. There is also a slight deviation observed for 0.4V and 0.5V when the load current is below 100uA. The load regulation of the proposed design is measured at 0.0089 (mV/mA).

#### 4.3.3 AC and Stability Analysis