#### **Lakehead University**

#### Knowledge Commons, http://knowledgecommons.lakeheadu.ca

**Electronic Theses and Dissertations**

Electronic Theses and Dissertations from 2009

2021

# Gallium nitride on low temperature cofired ceramic templates for Schottky junctions

Tot, Jonny

https://knowledgecommons.lakeheadu.ca/handle/2453/4821 Downloaded from Lakehead University, KnowledgeCommons

# Gallium Nitride on Low Temperature Cofired Ceramic Templates for Schottky Junctions

**Jonny Tot**

Presented to the faculty of Electrical and Computer Engineering in partial fulfillment for a Ph.D. degree

Lakehead University Thunder Bay, Ontario April 2021

#### Acknowledgments

I would like to acknowledge the help I received throughout my research by my lab partners, supervisor, friends, and family. My time spent in the semiconductor lab was a great period of learning and growth that could not have been done without the people there. Each of them is not just a colleague but a friend who helped this research progress through meaningful discussion and debate. I would like to thank Dr. Dimiter Alexandrov for giving me the opportunity to join the lab and for the endless encouragement I received to try new ideas from him. He truly helped me understand that even undesirable results are still results and are meaningful in forming a complete understanding. I would also like to thank my family for putting up with my seemingly endless journey through academia from kindergarten to now. They have always believed in me and supported my ambitions, even when I may have felt aimless. I wish to dedicate this work to my father who could not be with me to see its completion, I know he would be proud and is sorely missed.

#### Abstract

In this work aluminum, silicon and zinc oxide were used as intermediate layers for thin film growth on cofired glass ceramic substrates. The motivation behind this work is a direct deposition of nitride thin films on the surface of the ceramic substrate, eliminating the die and attach techniques. Ceramics have unique applications due too the nature of their mechanical processing, and their physical resilience and chemical inertness. The low melting of the glass ceramics from a device processing perspective and their rough, inhomogeneous surface presents a challenge for device fabrication. Oxide materials can be applied by a variety of techniques compatible with large device areas and arbitrary shapes to apply a surface texture to improve thin film properties for device fabrication. Ideally these techniques could be applied to any substrate that meets the thermal budget of the thin film process.

Solution coating was found to be a good candidate for applying coatings since it can deposit many different oxide materials over large areas, for relatively low cost, and surface tension of the liquid phase helps to planarize the surface. Several (>7) microns of coating materials were found to be needed to reduce the appearance of the ceramic surface features.

Deposition of GaN on the surface of the oxide coatings was performed using a Flow Modulation Epitaxy (FME) style deposition in conjunction with a unique hollow cathode plasma source. These features are designed to lower the overall temperature requirements for GaN growth by providing additional Ga migration time during growth and by using nitrogen plasma as an alternative to thermal decomposition of ammonia. Ni/Au Schottky junctions fabricated on sapphire using ceramic compatible temperatures and FME show leaky characteristics with high ideality factors, indicating tunneling is a significant contributor to carrier transport through the junction.

The same Ni/Au GaN devices fabricated on ZnO coated ceramics was found to produce ohmic junctions. The density of surface states is a likely candidate for this behaviour.

## Contents

| Acknowledgments                                                | ii  |

|----------------------------------------------------------------|-----|

| Abstract                                                       | i   |

| List of Figures                                                | v   |

| List of Tables                                                 | xi  |

| List of Publications                                           | xii |

| Posters Presented                                              | xii |

| Oral presentations                                             | xii |

| 1. Background Information                                      | 1   |

| 1.1 Nitride History                                            | 1   |

| 1.2 Motivation                                                 | 4   |

| 2. Materials                                                   | 5   |

| 2.1 III-V Nitride Semiconductors                               | 5   |

| 2.2 Oxide Materials                                            | 11  |

| 2.2.1 Zinc Oxide                                               | 11  |

| 2.2.1.1 Zinc Contamination                                     | 14  |

| 2.2.2 Silicon Oxide                                            | 15  |

| 2.2.3 Anodized Alumina (AAO)                                   | 15  |

| 2.3 Cofired Ceramics                                           | 18  |

| 3. Applications                                                | 23  |

| 3.1. Schottky Diode                                            | 23  |

| 3.1.1 Surface States                                           | 28  |

| 3.1.2. Thermionic Field Emission (TFE) and Field Emission (FE) | 28  |

| 3.1.3 IV Curves                                                | 29  |

| 3.2 High Temperature Materials                                 | 30  |

| 3.3 Device Packaging                                           | 33  |

| 4. Deposition Technology                                       | 37  |

| 4.1 Dip Coating                                                | 37  |

| 4.2 Sol-Gel                                                    | 43  |

| 4.2.1 ZnO Sol Chemistry                                        | 44  |

| 4.3 Chemical Vapour Deposition (CVD)                           | 53  |

| 4.3.2 Amorphous Deposition                                     | 64  |

| 4.3.3 Surface Roughness                    | 66  |

|--------------------------------------------|-----|

| 5. Defects In III-Nitrides                 | 70  |

| 5.1 Extended Defects                       | 70  |

| 5.2 Point Defects                          | 75  |

| 5.2.1 Vacancies                            | 75  |

| 5.2.2 Impurities                           | 76  |

| 5.3 Conclusions                            | 81  |

| 6. Instrumentation                         | 82  |

| 6.1 X-ray Diffraction (XRD)                | 82  |

| 6.1.1 XRD Analysis                         | 85  |

| 6.2 Scanning Electron Microscope (SEM)     | 86  |

| 6.3 Atomic Force Mircoscopy (AFM)          | 89  |

| 6.3.1 AFM Analysis                         | 91  |

| 6.4 X-ray Photoelectron Spectroscopy (XPS) | 92  |

| 7. Experiments                             | 94  |

| 7.1 Sapphire Growth                        | 94  |

| 7.1.1 Temperature                          | 95  |

| 7.1.2 Pressure                             | 95  |

| 7.1.3 Precursor Flow Rate                  | 97  |

| 7.1.4 Conclusions                          | 100 |

| 7.2 Ceramic Properties                     | 100 |

| 7.2.1 Ceramic Composition                  | 101 |

| 7.3 Oxide Properties                       | 103 |

| 7.3.1 Surface Texture                      | 103 |

| 7.3.2 Surface Roughness                    | 104 |

| 7.4 GaN Growth                             | 115 |

| 7.4.1 Anodic Alumina                       | 115 |

| 7.4.1. ZnO                                 | 120 |

| 7.4.2. IV Curves                           |     |

| 8.0 Conclusions                            | 136 |

| Bibliography                               | 138 |

|                                            |     |

# List of Figures

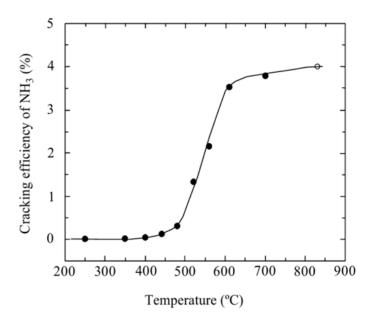

| Figure 1:Decomposition efficiency of ammonia as a function of temperature. The lower limit of atomic nitrogen production using ammonia is shown to be 600 °C from the characteristics of this curve [5]                                                                                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

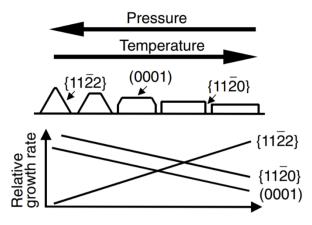

| Figure 2: The effect of temperature and pressure on controlling the relative growth rate of different hexagonal planes [5].                                                                                                                                                                                                                                                                        |

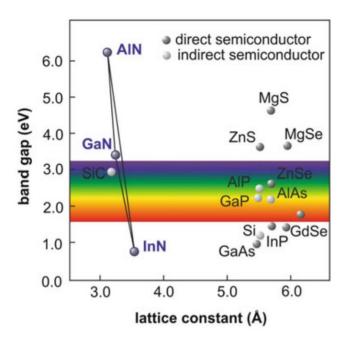

| Figure 3: Bandgap and lattice constant of many common semiconductors [29]6                                                                                                                                                                                                                                                                                                                         |

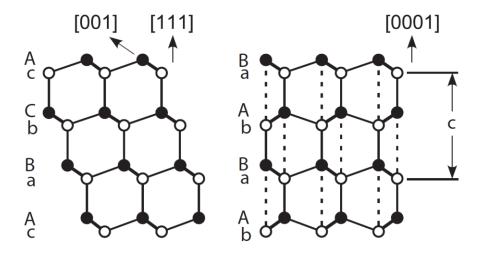

| Figure 4: ZB structure (left) with AaBbCc ordering along the [111] crystal direction. The WZ crystal (right) with AaBb stacking along the [0001] direction [33]                                                                                                                                                                                                                                    |

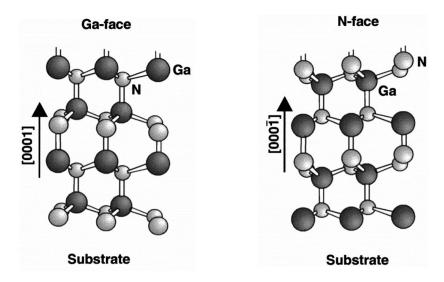

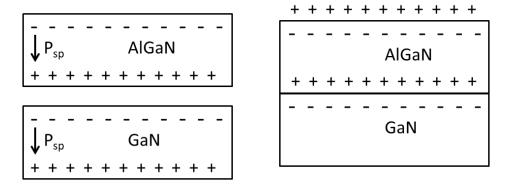

| Figure 5: Two possible stacking orders in III-Nitrides that lead to polarization facing the substrate (left) and facing the surface (right). The magnitude of the spontaneous (P <sub>sp</sub> ) and piezoelectric (P <sub>z</sub> ) polarization is the same, but the direction is opposite [37].                                                                                                 |

| Figure 6: High electron mobility channel formation from spontaneous polarization vectors in a Ga facing GaN/AlGaN heterostructure. The Ga facing crystal has P <sub>sp</sub> facing the surface while N facing crystal has it facing the substrate.                                                                                                                                                |

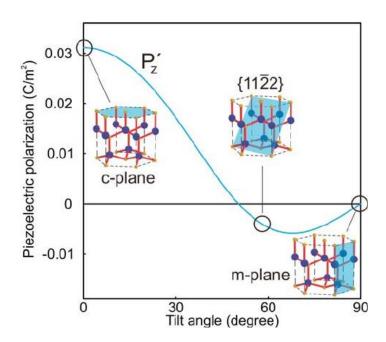

| Figure 7: Change in piezoelectric polarization constant between from the c, r and m planes in GaN [39]                                                                                                                                                                                                                                                                                             |

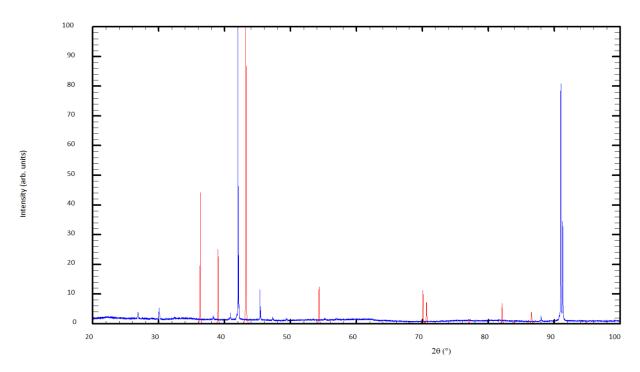

| Figure 8: Normalized Θ-2Θ XRD plot of the sapphire wafer after ZnO contamination (blue). A theoretical spectrum from Zn metal (red) is included, calculated from the HCP structure with a=2.6648 Å and c=4.9467 Å [66]. Major peaks related to the (0006) and (00012) peaks of sapphire (blue) are at 42.01° and 91.00° respectively. All other peaks in blue correspond to reactor contamination. |

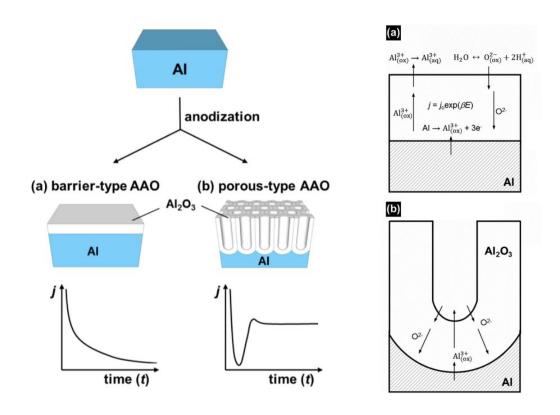

| Figure 9: Anodized alumina production for a) low pH electrolytes resulting in a self-limiting barrier type and b) high pH resulting in a continuous pore etching or porous type material [73].16                                                                                                                                                                                                   |

| Figure 10: Two stage AAO template showing the initial random pore initiation and the dimpled template for the second anodization [73].                                                                                                                                                                                                                                                             |

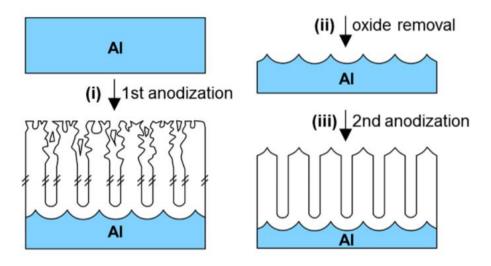

| Figure 11: LTCC production flow diagram from initial slurry mixture to a final laminated multilayer stack [90].                                                                                                                                                                                                                                                                                    |

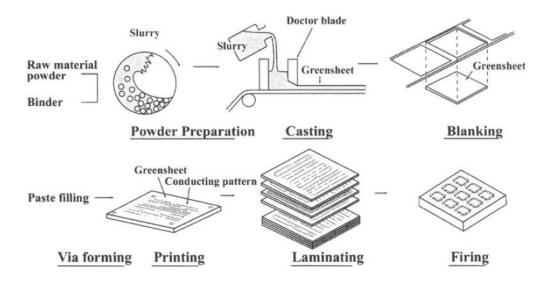

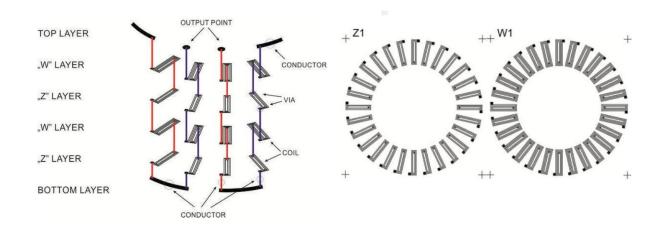

| Figure 12: 2 coils from a 28-coil structure using in an LTCC micro generator device fabricated at Wrocław University of Technology. The linewidths shown are 200 µm with up to 12 layers laminated in a single 50 mm diameter disc [99]                                                                                                                                                            |

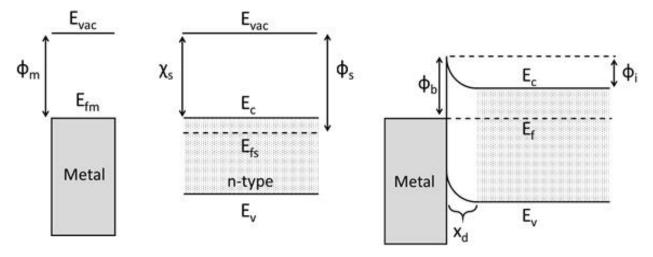

| Figure 13: Energy levels in two isolated metal and n-type semiconductor materials and after contact with electron diffusion.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 14: Band diagrams of the Schottky junction in forward (left) and reverse (right) bias. In forward bias the barrier shrinks, and the fermi level slowly returns to its isolated position. Once $Va = \phi i$ we return the isolated material scenario seen in Figure 13 (right) and the diffusion current is free to flow. In the reverse bias the applied voltage $Va$ is the same direction as the built-in potential $\phi i$ and only adds to the current blocking field, depleting more carriers from the surface and extending the depletion region. Only carriers with enough energy to jump the barrier $(\phi b)$ and thermally/optically generated currents can flow. |

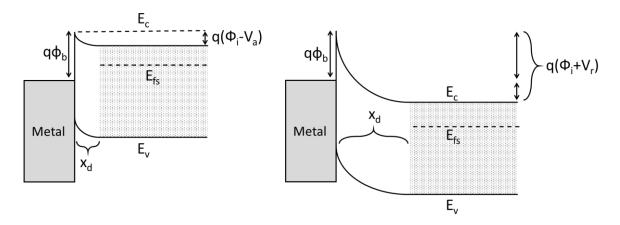

| Figure 15: Film thickness vs withdrawal speed from the bath. The drainage and capillary region are comminated by different mechanisms [133]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

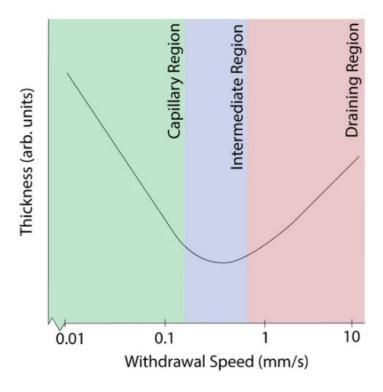

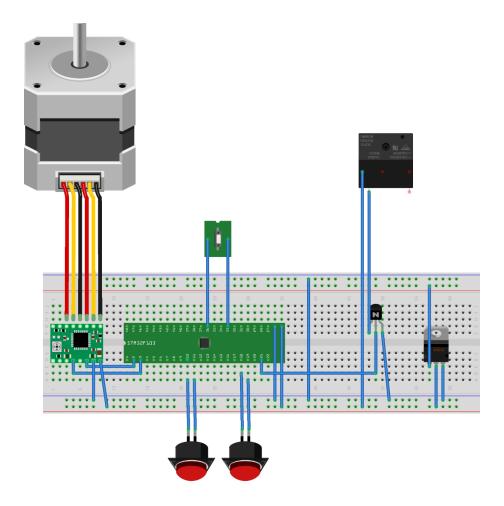

| Figure 16: Basic schematic of dip coater                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

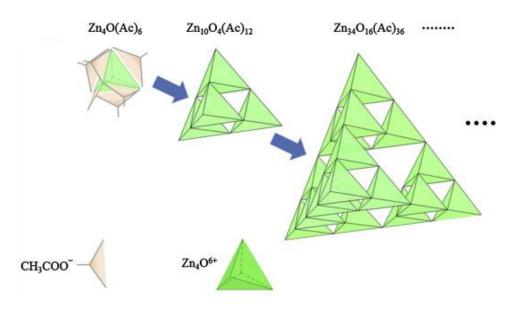

| Figure 17: Zinc oxo-acetato species formed from the zinc salt in the sol-gel process. The Zn <sub>4</sub> C clusters are charge balanced by accommodating an acetate ion on each external edge of the tetrahedra [139]                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

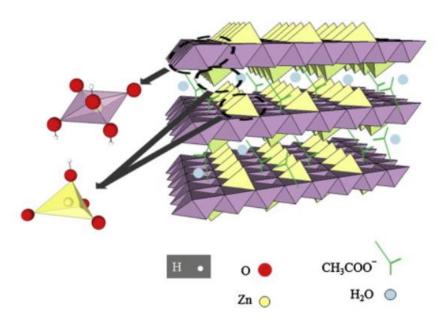

| Figure 18: Layered hydroxide zinc acetate (LHZA) or zinc double salt seen in sol-gel zinc oxide synthesis [139]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

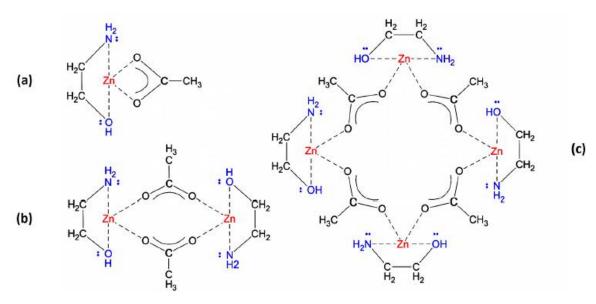

| Figure 19: The proposed stabilized complexes formed from Monoethanolamine (MEA) stabilized ZAD. The a) monomer structure b) dimer and c) tetramer all increase the solubility of ZAD in nonpolar solvents [135]                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

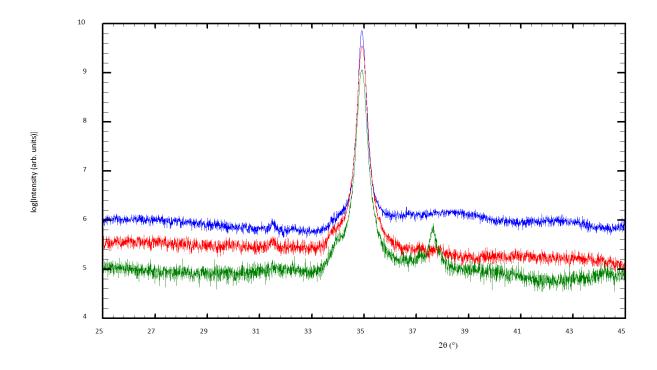

| Figure 20: Semilog plot of XRD peaks in the range of 2Θ=25° to 45° for increasing Al content in the film. Each sample is 15 dips on a glass slide. The highest peak (blue) is 0% doping, next (red) is 0.5% and green is 1%.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

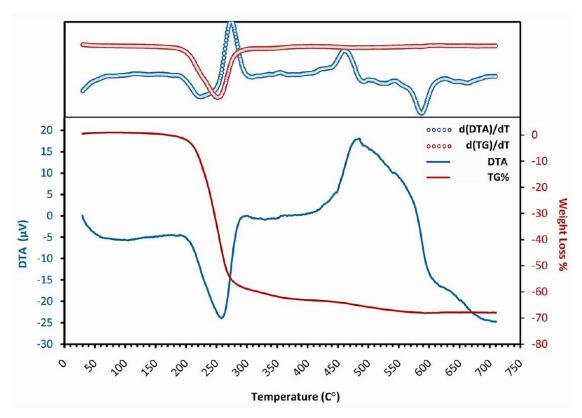

| Figure 21: TG-DTA analysis of the baking process for ZAD sol-gel showing weight loss beginning at 275 °C [135]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Figure 22: Growth rate curve showing three distinct deposition regimes. At low temperatures, the growth is limited by the precursor breakdown and at high temperatures decomposition and evaporation occurs. In between these two regimes the transport from the gas phase is diffusion limited, the growth rate is high and stable [150].                                                                                                                                                                                                                                                                                                                                            |

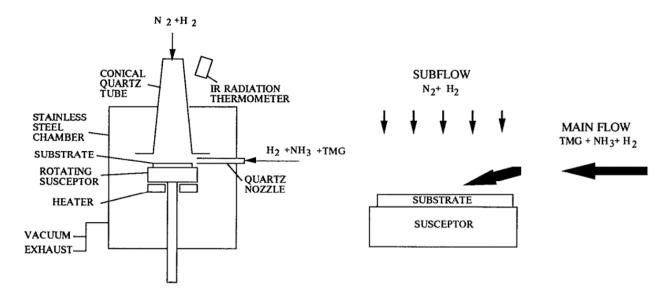

| Figure 23: Basic dual flow system used in nitride epitaxy proposed in the early 90's [129]57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

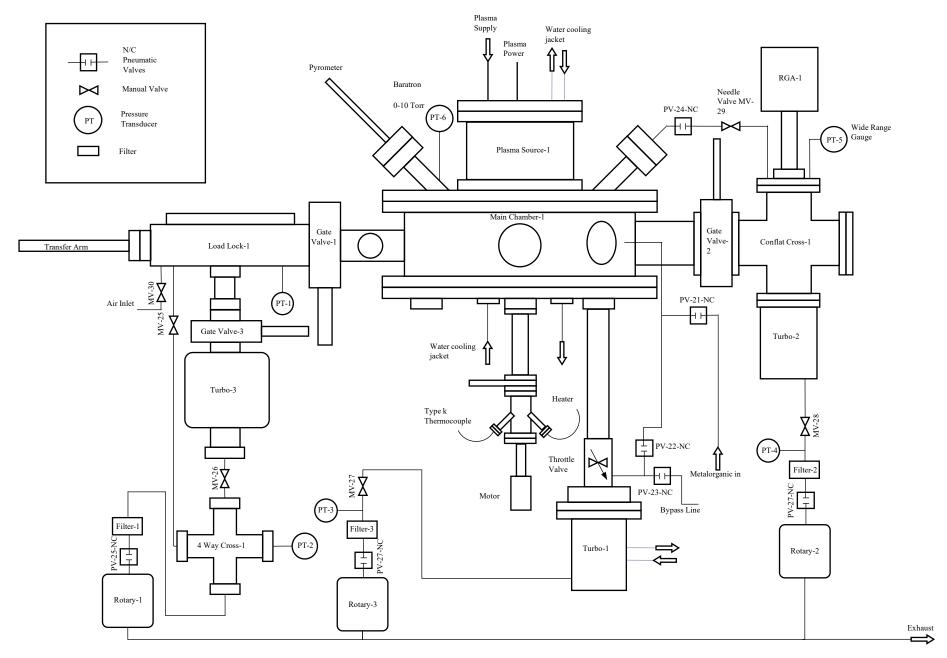

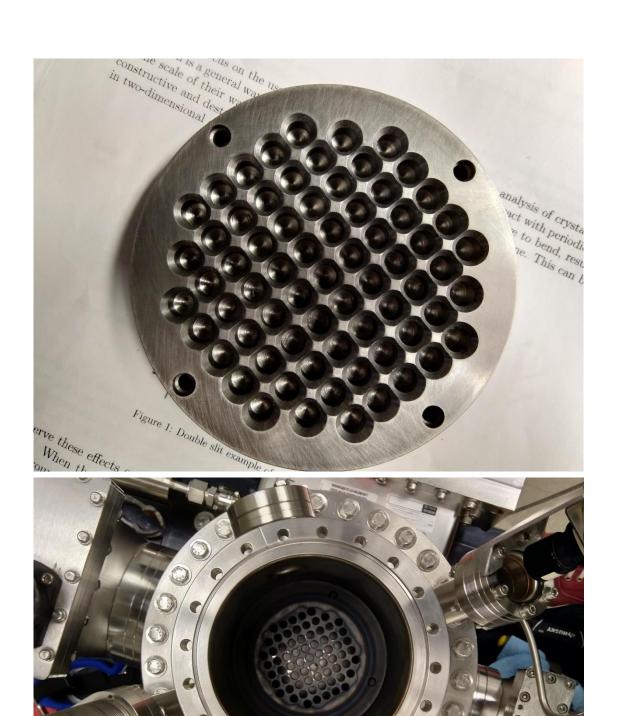

| Figure 24: Low pressure remote plasma MOCVD system used in this work60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

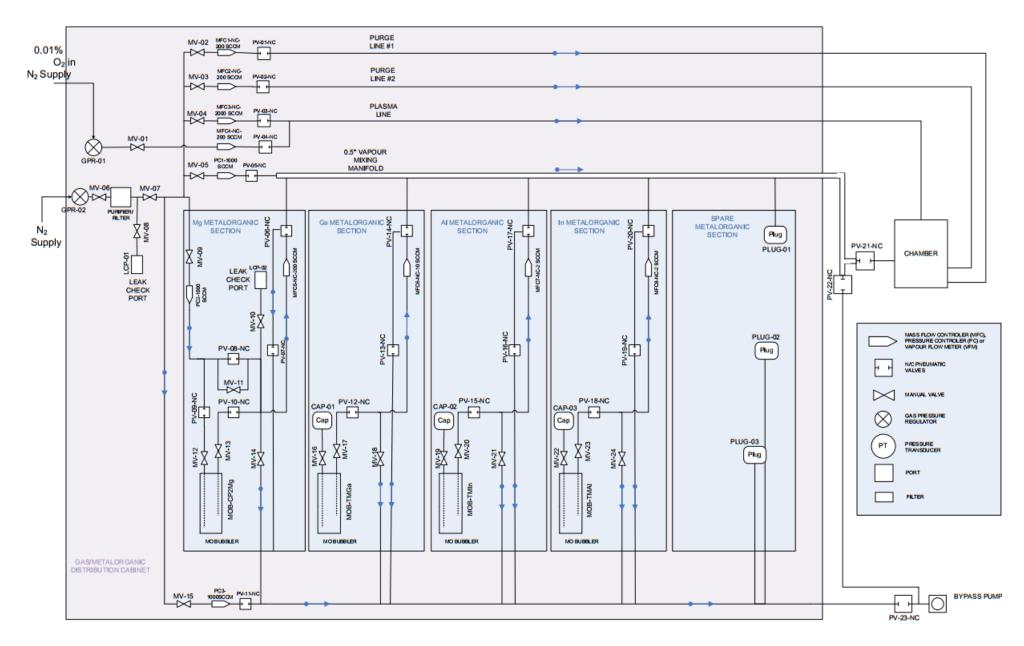

| Figure 25: Gas delivery system used to supply the MOCVD system seen in Figure 2461                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 26: Top-down view of the hollow cathode (lower) and the patterned anode (upper)63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

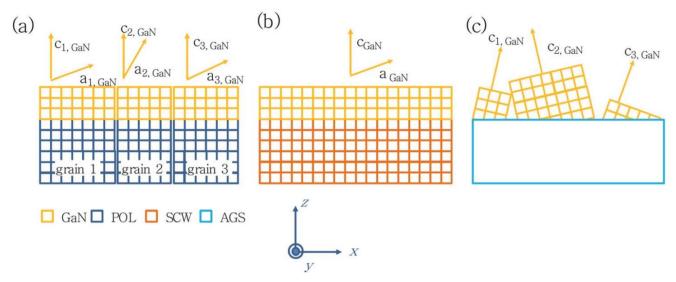

| Figure 27: Nucleation behaviour of GaN nucleation on polycrystalline (a), single crystal (b) and amorphous substrates (c) [160]                                                                                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

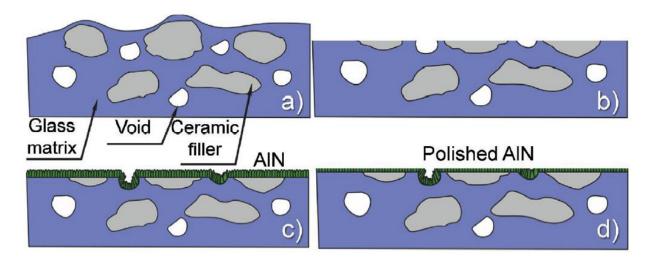

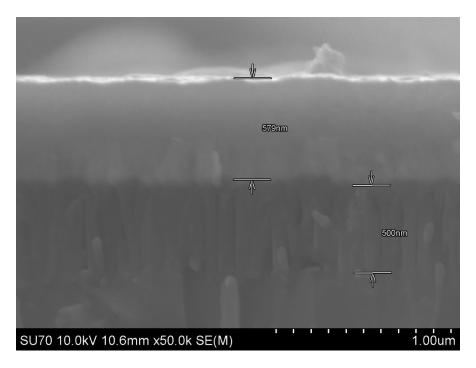

| Figure 28: AlN sputtering treatment of the bare LTCC (a). The initial surface polishing (b) levels the waviness and opens surface voids, decreasing the initial rms roughness to 120 nm. The sputtered AlN (c) reduced the roughness again to 42 nm and a final polishing (d) reduced the roughness to 5.6 nm measured on a 5x5 μm AFM scan [188] |

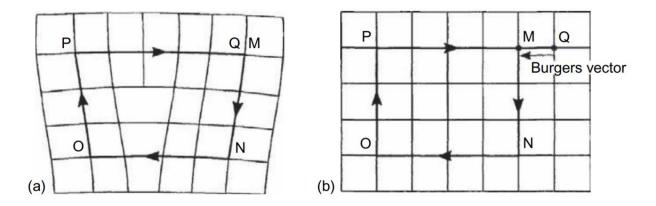

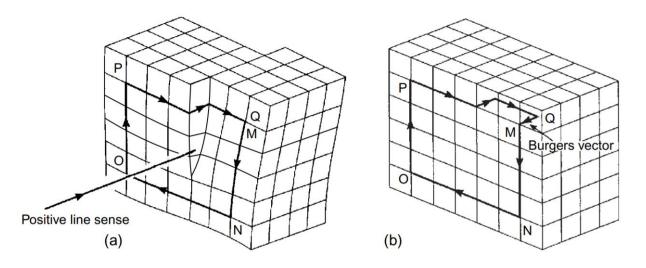

| Figure 29: a) Edge dislocation resulting from the insertion of and extra half plane and b) normal lattice with burgers circuit overlay to show the burgers vector [208]                                                                                                                                                                           |

| Figure 30: Screw dislocation and b) normal lattice with burgers circuit overlay to show the burgers vector [208]                                                                                                                                                                                                                                  |

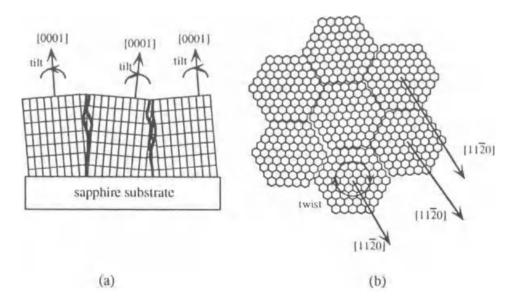

| Figure 31: the effect of grain tilt (a) and grain twist (b). Tilt (a) causes slight variations in heights of the coalescing nuclei leading to screw type dislocations. Twist (b) introduces edge type dislocations [109]                                                                                                                          |

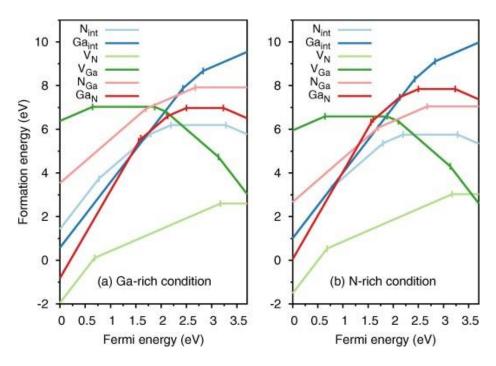

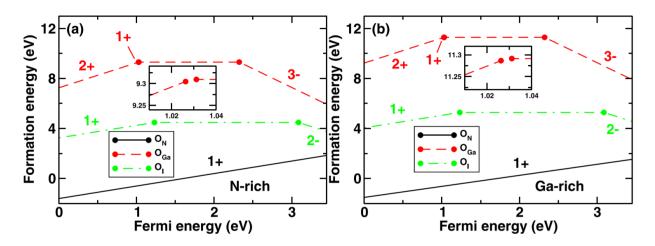

| Figure 32: Formation energy for native point defects in GaN under a) Ga rich conditions and b) N rich conditions [222].                                                                                                                                                                                                                           |

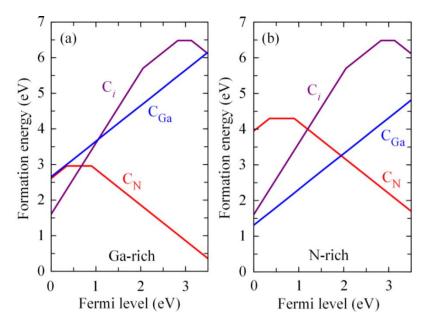

| Figure 33: HSE-DFT calculations of the formation energies of gallium substitution (C <sub>Ga</sub> ), nitroger substitution (C <sub>N</sub> ) and interstitial carbon (C <sub>i</sub> ) for carbon impurities. Gallium rich (a) and nitroger rich (b) stoichiometries are considered [225]                                                        |

| Figure 34: HSE-DFT calculations for oxygen with various positions and charge states in wurtzite GaN. In both a) nitrogen rich and b) gallium rich conditions the most stable position for oxygen is a nitrogen substitution (O <sub>N</sub> ) where it forms a single donor [233]                                                                 |

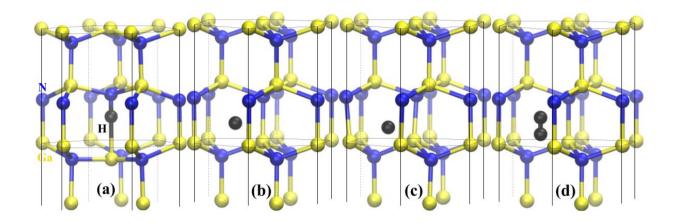

| Figure 35: Stable positions of hydrogen in the GaN wurtzite lattice for the a) +1 donor state where it is in line with the Ga-N bond b) the octahedral neutral charge state c) the octahedral acceptor charge state and d) the H <sub>2</sub> molecule [233]                                                                                      |

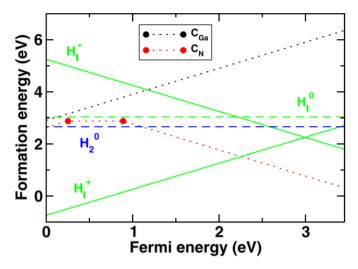

| Figure 36: Hydrogen interstitial formation energy for different charge states of hydrogen [233]                                                                                                                                                                                                                                                   |

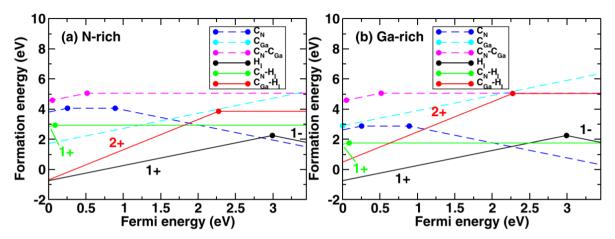

| Figure 37: Interstitial hydrogen charge states and complex formation energy in a) nitrogen rich and b) gallium rich conditions [233]                                                                                                                                                                                                              |

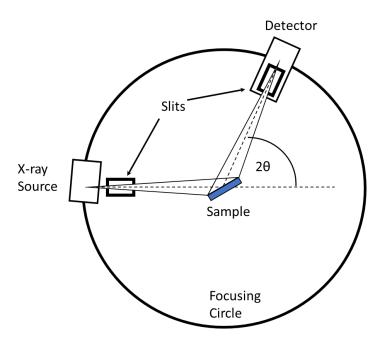

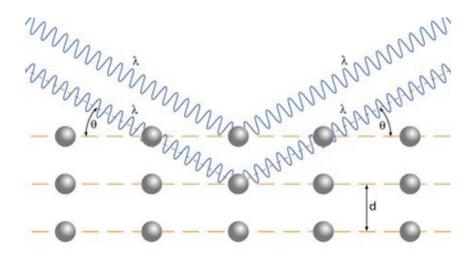

| Figure 38: Bragg-Brentano goniometer experimentally used for XRD. Measurement of planes parallel to the surface are performed using a $\Theta$ -2 $\Theta$ scan where the sample remains flat with the source and detector moving at the same constant rate.                                                                                      |

| Figure 39: Bragg condition for x-ray diffraction [234]84                                                                                                                                                                                                                                                                                          |

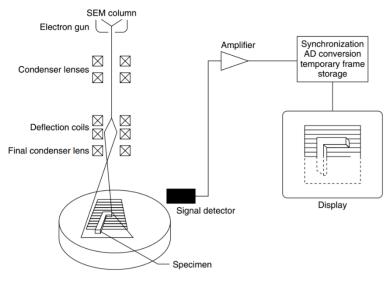

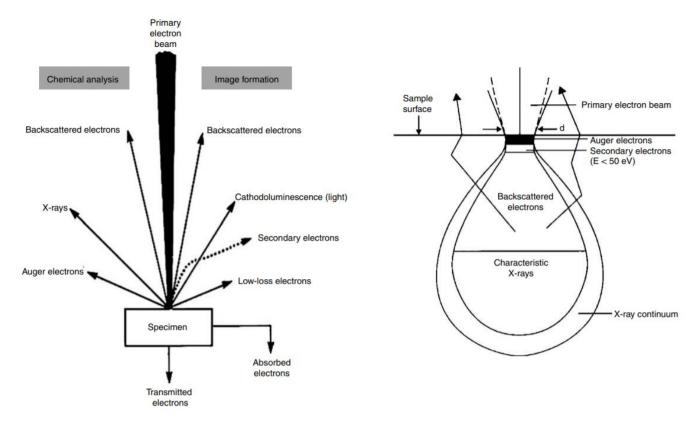

| Figure 40: Schematic diagram of SEM operation [239]                                                                                                                                                                                                                                                                                               |

| Figure 41: Primary electron beam interaction within the SEM. The electron beam can penetrate um of material releasing secondary particles along its path [239]                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

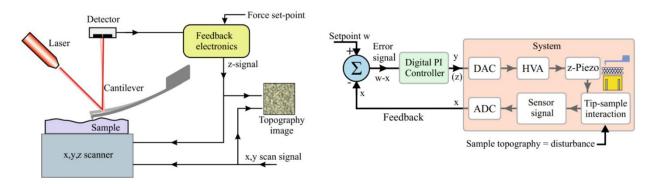

| Figure 42: Overview of AFM system (left) and the feedback system (right). The error signal used determine height is generated by monitoring the tip sample interaction with a laser and maintaining the setpoint through the high voltage amplifier (HVA) and piezo element [240] |

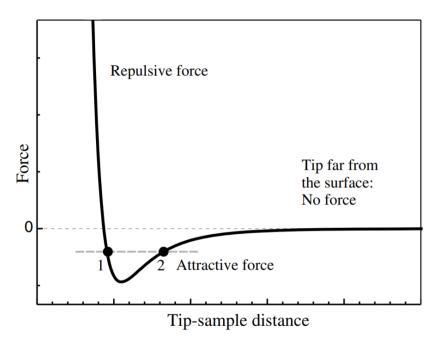

| Figure 43: Force-distance curve showing the operating regimes of (1) contact mode and (2) noncontact mode. In both cases the force is attractive towards the energy minimum, but the slope of the curve is drastically different [240].                                           |

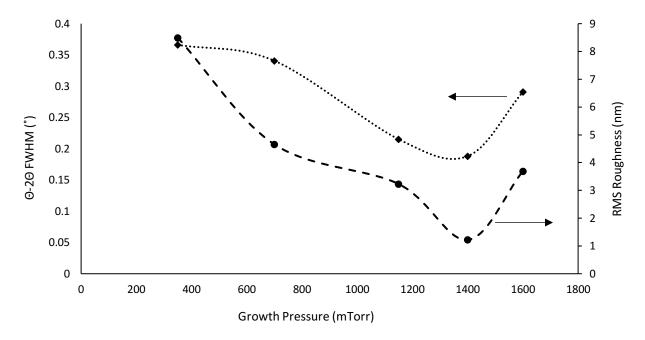

| Figure 44: (0002) GaN Θ-2Θ FWHM and surface roughness as a function of growth pressure in our system96                                                                                                                                                                            |

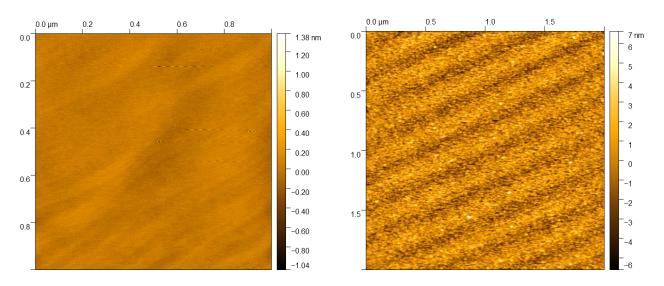

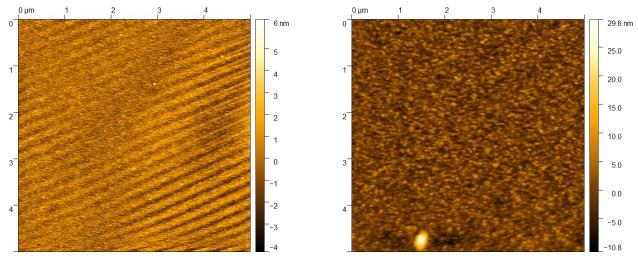

| Figure 45: AFM surface image for the bare sapphire wafer (1x1 μm, left) and 700 °C post growth surface (2x2 μm, right). The measured RMS roughness changed from 57.83 pm (left) to 1.219 nm (right)                                                                               |

| Figure 46: AFM surface image for the 700 °C sapphire deposition (5x5 μm, left) and 650 °C pos growth surface (5x5 μm, right). The measured RMS surface modifying the roughness from 1.219 nm (left) to 2.891 nm (right)                                                           |

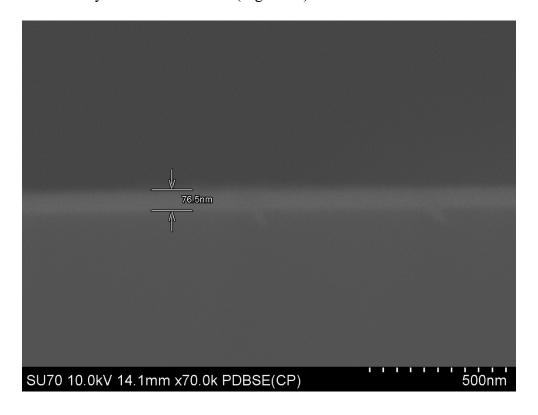

| Figure 47: BSE Image of GaN sapphire growth at 700 °C, 1400 mTorr, 0.5 sccm flow rate98                                                                                                                                                                                           |

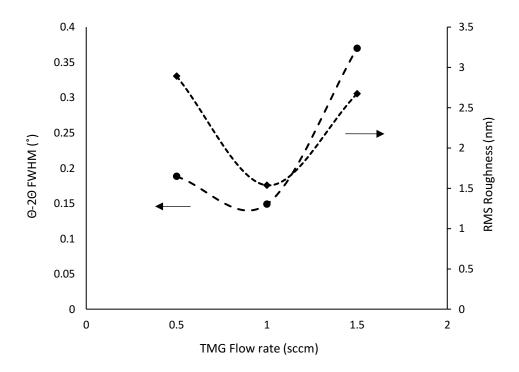

| Figure 48: Effect of varying the TMGa flow rate on the Θ-2Θ FWHM and RMS roughness99                                                                                                                                                                                              |

| Figure 49: A decrease in plasma duration is observed to decrease the XRD peak quality and introduce additional polycrystalline peaks.                                                                                                                                             |

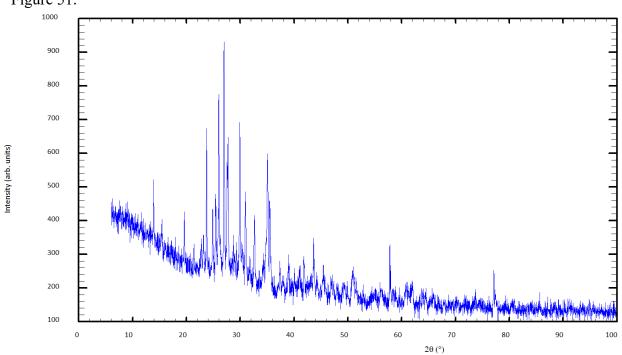

| Figure 50: XRD spectra of bare ceramic substrate. The significant number and sharp distribution of peaks indicates a non oriented multiphase mixture is present                                                                                                                   |

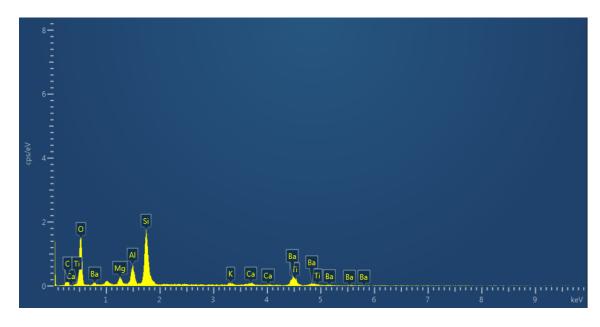

| Figure 51: EDX spectra of the bare ceramic. The EDX gives an elemental analysis of the sample based off characteristics X-ray energies                                                                                                                                            |

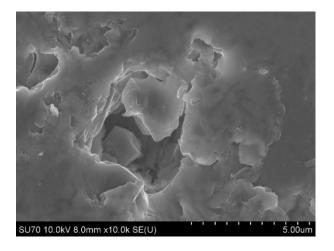

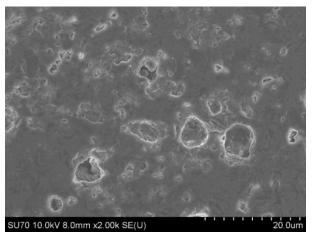

| Figure 52: SEM surface image of the bare ceramic. Two distinct pit sizes are visible in each scan originating from different processing in the ceramic                                                                                                                            |

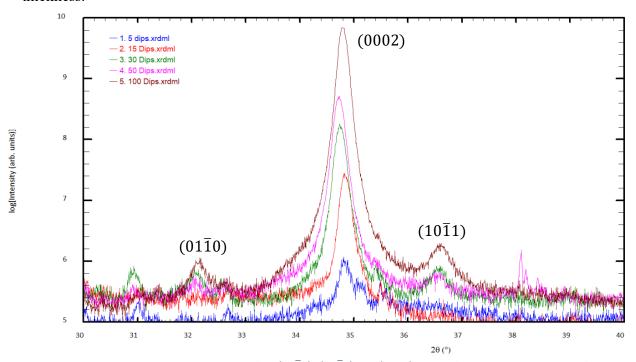

| Figure 53: Semilog plot showing the evolution of the 1010, 1011 and 0002 peaks of ZnO or LTCC. The strain free positions of these peaks are 31.7768°, 36.2638° and 34.433° respectively with a=3.249 Å and c=5.205 Å                                                              |

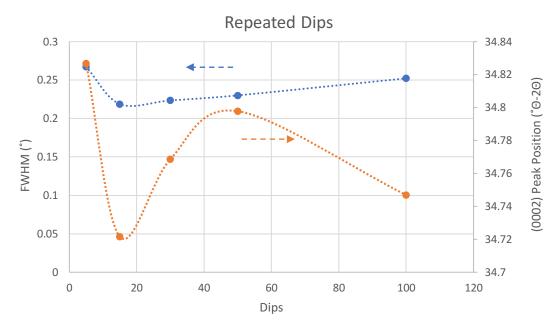

| Figure 54: Plot showing number of the effect of subsequent dips on the 0002 peak position to observe lattice strain and FWHM to observe the change in ordering along the c-axis                                                                                                   |

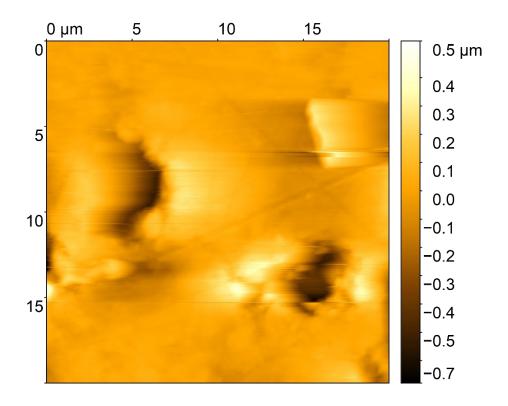

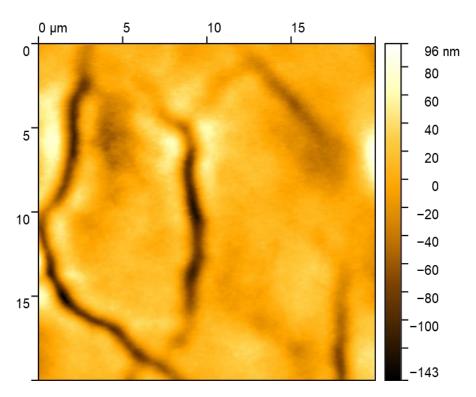

| Figure 55: 20x20 µm² AFM scan of the bare ceramic. The measured surface roughness including the pores is 116.2 nm                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

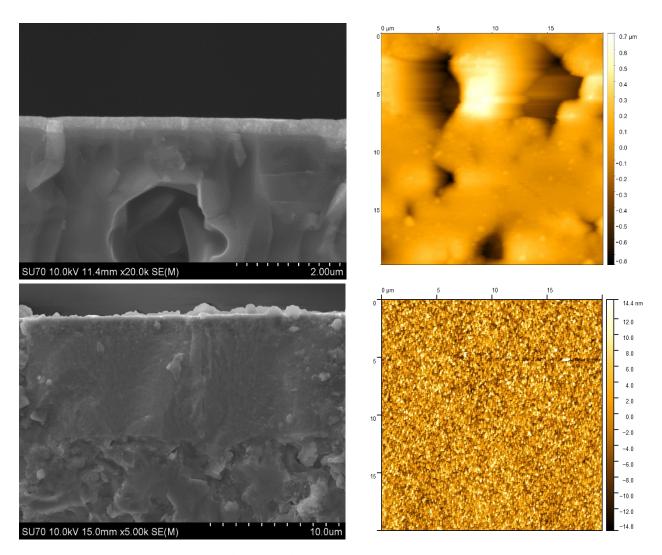

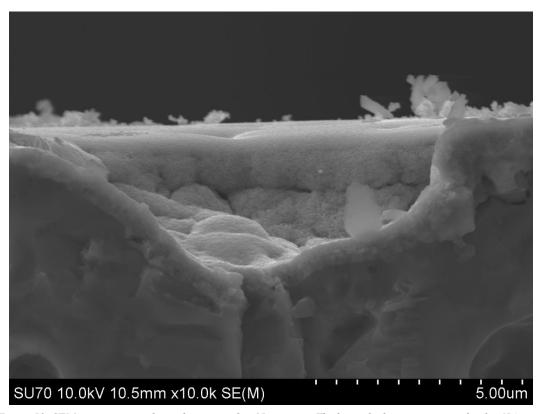

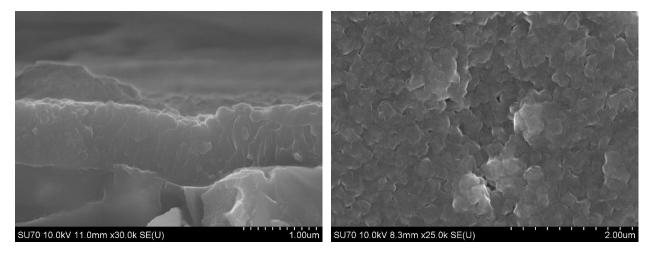

| Figure 56: SEM cross section and AFM surface scans of ZnO dip coated samples. The upper two images represent 5 dips, while the bottom is 100                                                                                                                                                                                                                                         |

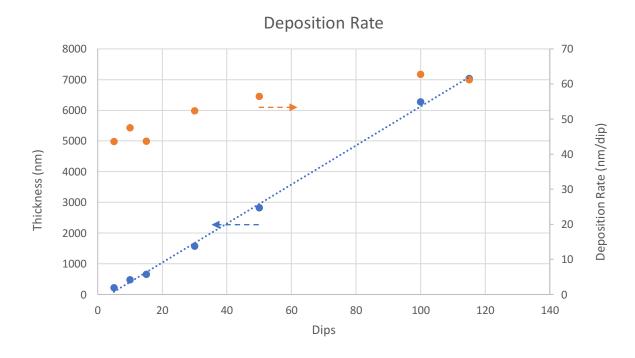

| Figure 57: Dip coating thickness and deposition rate based on total number of dips. The average per dip is seen increase with a greater number of dips                                                                                                                                                                                                                               |

| Figure 58: SEM cross section of a surface pore after 15 coatings. The layer thickness is measured to be 654 nm                                                                                                                                                                                                                                                                       |

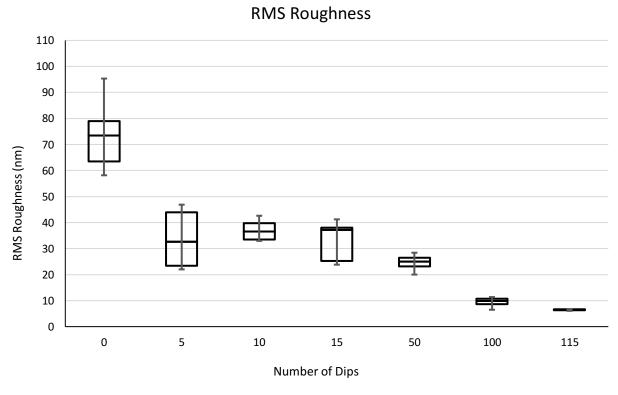

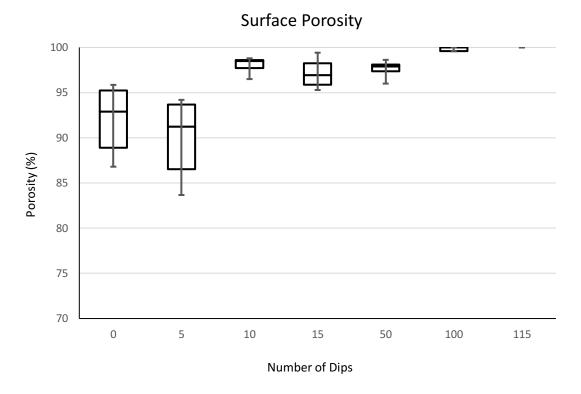

| Figure 59: Box plot of the surface roughness as a function of dip counts. Each of the boxes is determined from 5 measurements of randomly chosen spots on the surface                                                                                                                                                                                                                |

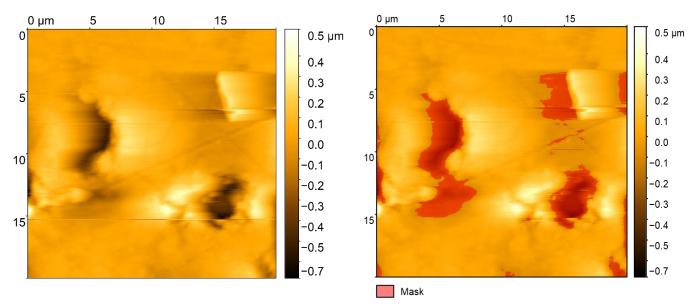

| Figure 60: Masking of the AFM data to determine porosity and reduce pit induced errors in the data                                                                                                                                                                                                                                                                                   |

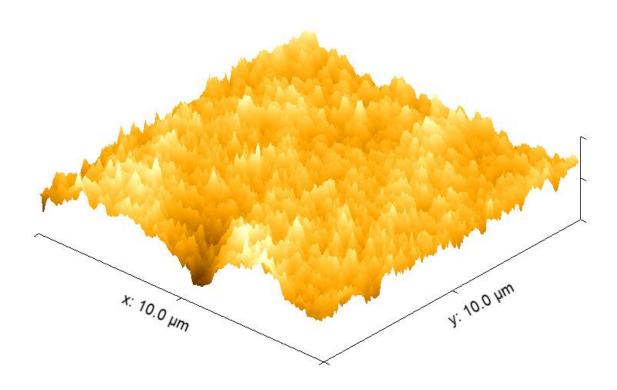

| Figure 61: 3D AFM plot of 115 dips of ZAD sol gel solution. The micron scale pits on the surface of the ceramic can still be seen to influence the roughness of the layers despite a thickness of 7.1 μm                                                                                                                                                                             |

| Figure 62: box plot of porosity determined form the arbitrary threshold masking done on the AFM samples. Surface features greater than 150 nm from the mean plane are taken as pit features111                                                                                                                                                                                       |

| Figure 63: Silica sol gel samples annealed at 500 °C. Cracking can be observed in these layers due too thermal expansion of the substrate being higher than the silica layer112                                                                                                                                                                                                      |

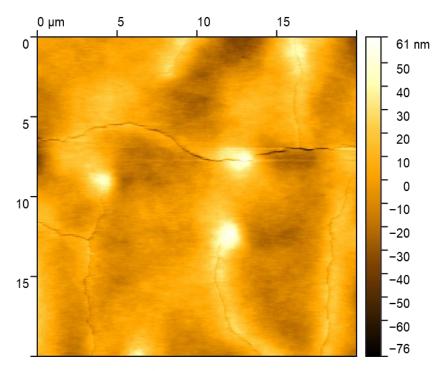

| Figure 64: AFM scan silica coated LTCC. The RMS surface roughness over 5 different samples was found to be 28.58 nm                                                                                                                                                                                                                                                                  |

| Figure 65: 1.5 µm thick dip coating layer on the silica sol gel                                                                                                                                                                                                                                                                                                                      |

| Figure 66: Anodized alumina film on LTCC cross section (left) and surface view (right)114                                                                                                                                                                                                                                                                                            |

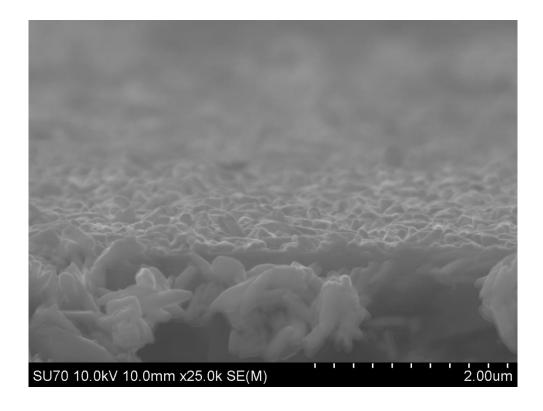

| Figure 67: Oblique view of GaN growth on LTCC substrate with no layer in between, resulting in a dense network of misoriented crystallites                                                                                                                                                                                                                                           |

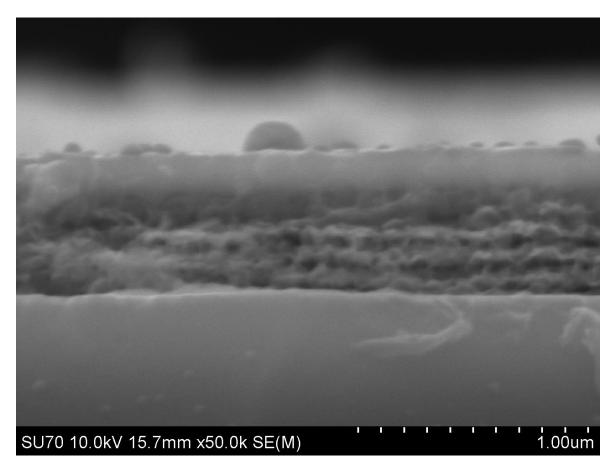

| Figure 68: SEM cross section of 1500 cycles of growth on the anodized alumina/ceramic templates. The amorphous alumina homogenizes the composition of the surface, leading to a more uniform nucleation than the bare ceramic seen in Figure Figure 67                                                                                                                               |

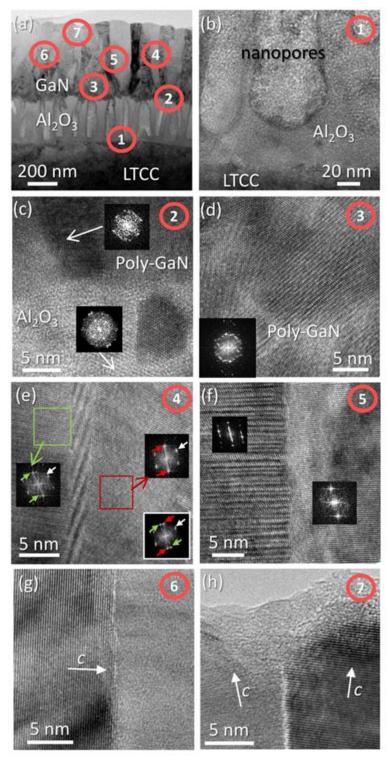

| Figure 69: Bright Field Diffraction Contrast TEM (BF-DCTEM) cross section of GaN on AAO growth illustrating several structural features of GaN. a) Overview of areas examined. b) The interface between the LTCC and AAO, show an abrupt and well adhered interface. c-d) the GaN AAO interface is seen to be mostly polycrystalline for the first 100-200 nm. e) a mixture of cubic |

| and hexagonal phases. f)-h) show the grains visible have a relative twist and tilt to one another.                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

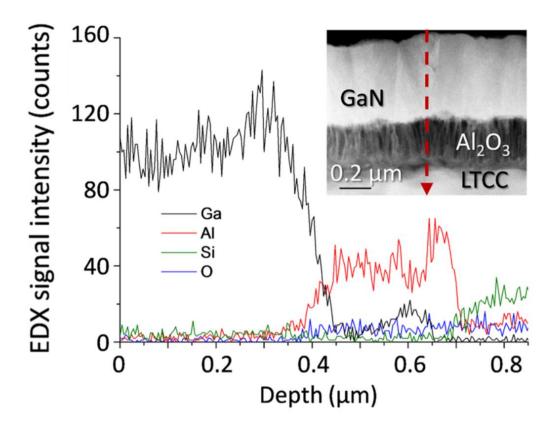

| Figure 70: EDX line profile of the GaN/AAO/LTCC structure                                                                                                                                                                |

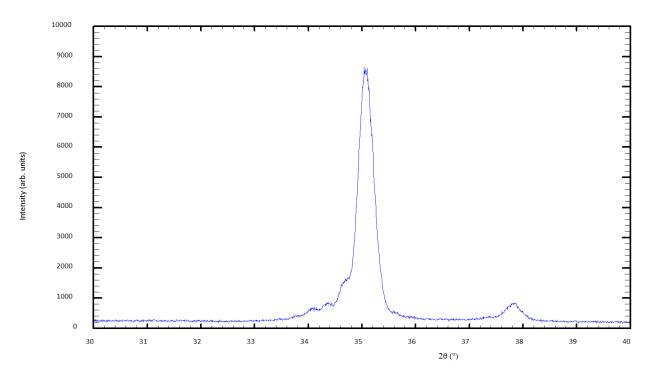

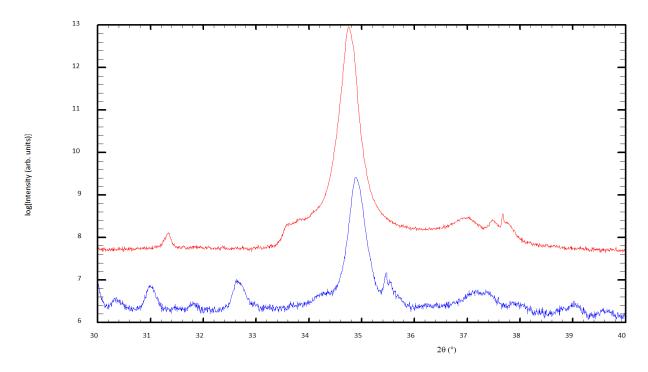

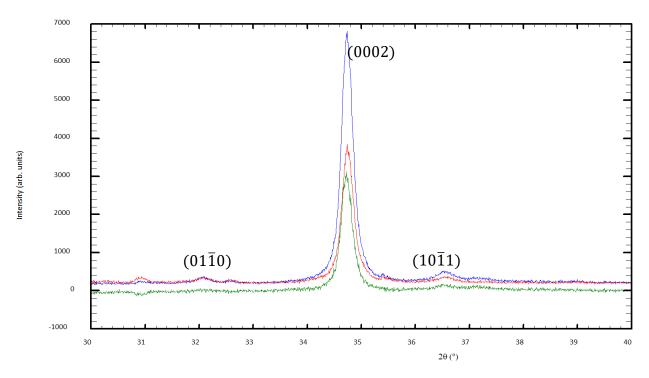

| Figure 71: XRD results from 3000 cycles on the AAO ceramic (blue) and sapphire (red) 120                                                                                                                                 |

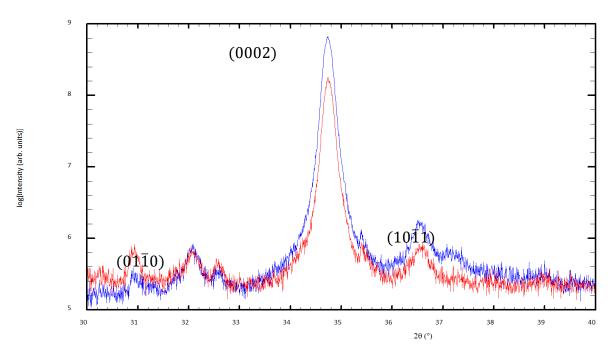

| Figure 72: XRD of GaN on ZnO coated ceramic. The red scan represents the pre deposition ZnO surface, while the blue is post growth GaN                                                                                   |

| Figure 73: GaN growth on ZnO coated LTCC. The initial curve can be seen in red and post deposition can be seen in blue. The difference between the two curves (green) is a result of the GaN deposition.                 |

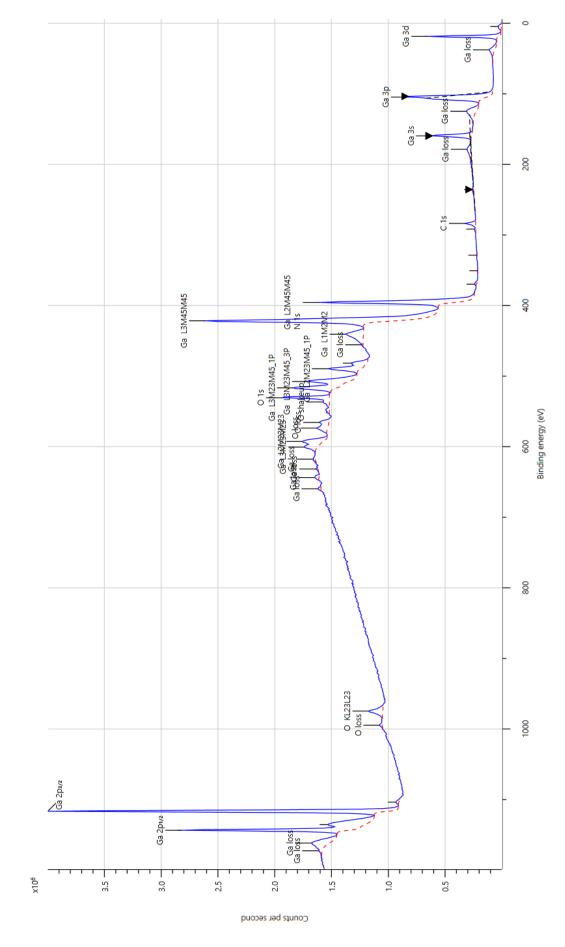

| Figure 74: XPS surface analysis of GaN on ZnO ceramic. No zinc peaks can be seen in the analysis indicating diffusion through the sample did not occur                                                                   |

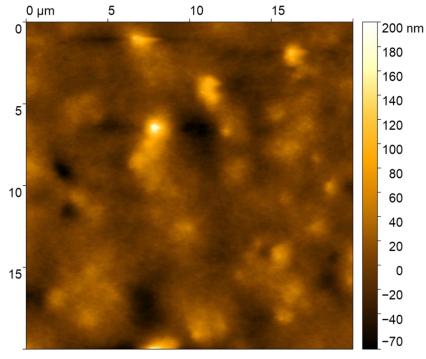

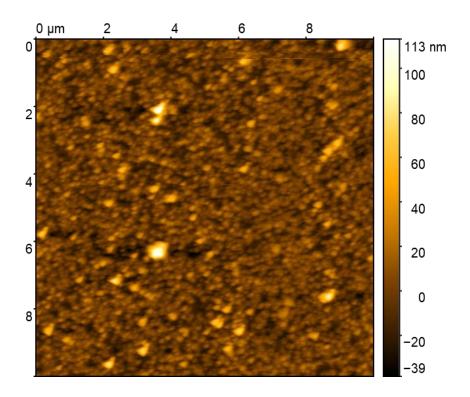

| Figure 75: AFM Scan of GaN on ZnO LTCC. The surface roughness was observed to increase with GaN deposition                                                                                                               |

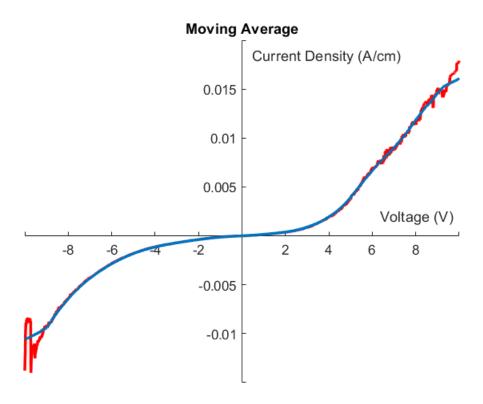

| Figure 76: 5 dip ZnO on LTCC sample etched in 1:1 HCL for 1 min. The yellowish hue of the GaN layer is visibly removed from the edges of the sample. In the cross section the layering of the ZnO structure can be seen. |

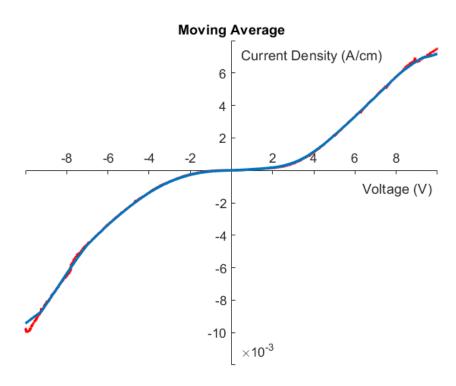

| Figure 77: GaN sapphire IV curves for 650 °C growths                                                                                                                                                                     |

| Figure 78: GaN sapphire IV curves for 700 °C growths                                                                                                                                                                     |

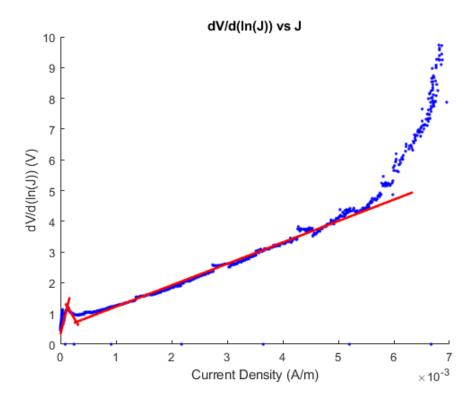

| Figure 79: dV/d(ln(J)) curve for 700 °C sapphire growths                                                                                                                                                                 |

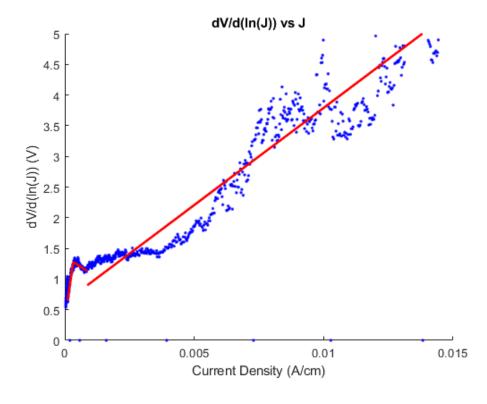

| Figure 80: dV/d(ln(J)) curve for 650 °C sapphire growths                                                                                                                                                                 |

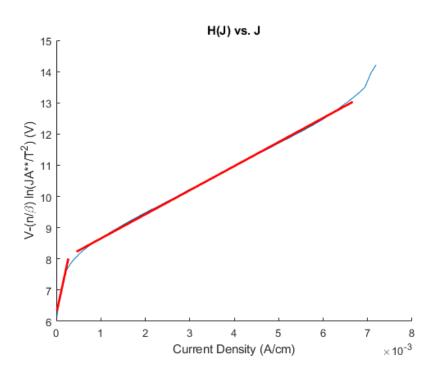

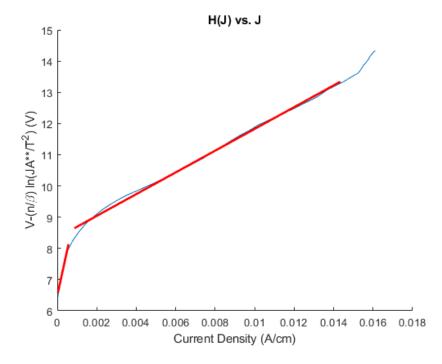

| Figure 81: Plot of auxiliary function H(J) vs. the current density J for the 650 °C130                                                                                                                                   |

| Figure 82: Plot of auxiliary function H(J) vs. the current density J for the 700 °C131                                                                                                                                   |

| Figure 83: GaN/ZnO/LTCC IV curves for the samples from 7.4.1. ZnO The curves exhibit ohmic behaviour in all cases. In the case of 115 dips some nonlinearity can be seen but no rectification can be observed            |

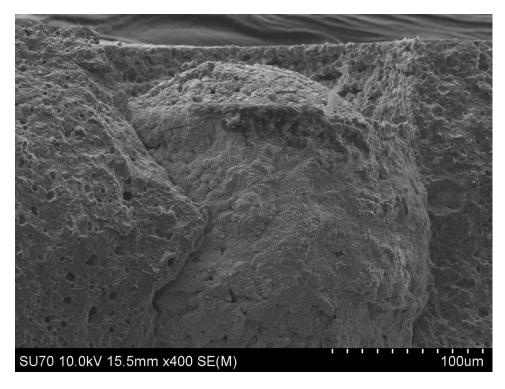

| Figure 84: ZnO coated silver via in the LTCC structure. 115 coatings (~7 μm) of material has been dip coated on the surface                                                                                              |

## List of Tables

| Table 1: Comparison of some III-V materials properties and silicon [1], [2]                                          | 1   |

|----------------------------------------------------------------------------------------------------------------------|-----|

| Table 2: Unit cell properties of silicon, nitrides, and various oxide materials                                      | 12  |

| Table 3: Melting point of various conductors used in ceramic technology [90]                                         | 20  |

| Table 4: Varshni parameters for several semiconducting materials.                                                    | 31  |

| Table 5: Coefficient of Thermal Expansion (CTE) for several materials related to electro packaging [90], [125]–[127] |     |

| Table 6: Various alcohols used in sol-gel ZnO synthesis [137].                                                       | 45  |

| Table 7: Stabilizing agents examined for their impact on crystal orientation in ZnO dip c films [139].               |     |

| Table 8: XPS peak quantification of GaN deposition on ZnO coated LTCC.                                               | 123 |

| Table 9: XPS peak quantification of GaN on sapphire at 700 °C                                                        | 123 |

| Table 10: Calculated diode parameters from Ni/Au Schottky diodes on Sapphire                                         | 132 |

| Table 11: Summary of resistance values from Figure 84                                                                | 134 |

#### List of Publications

- 1. Tot, J., R. Dubreuil, B. Kadikoff, M. Nagorski, and D. Alexandrov. "Energy Bandgap of InN," In Press.

- 2. J. M. Mánuel, J. J. Jiménez, F. M. Morales, B. Lacroix, A. J. Santos, R. García, E. Blanco, M. Domínguez, M. Ramírez, A. M. Beltrán, D. Alexandrov, J. Tot, R. Dubreuil, V. Videkov, S. Andreev, B. Tzaneva, H. Bartsch, J. Breiling, J. Pezoldt, M. Fischer, and J. Müller, "Engineering of III-Nitride Semiconductors on Low Temperature Co-fired Ceramics," Sci. Rep., vol. 8, no. 1, p. 6879, May 2018, https://doi.org/10.1038/s41598-018-25416-6.

- 3. D. Alexandrov, J. Tot, R. Dubreuil, F. M. Morales, J. M. Mánuel, J. J. Jiménez, B. Lacroix, R. García, V. Videkov, S. Andreev, B. Tzaneva, H. Bartsch, J. Pezoldt, M. Fischer, and J. Mueller, "Low Temperature Epitaxial Deposition of GaN on LTCC Substrates," in 2017 IEEE 5th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Oct. 2017, pp. 48–54, https://doi.org/10.1109/WiPDA.2017.8170501.

- 4. Kadikoff, B., R. Dubreuil, J. Tot, and D. Alexandrov. "Investigation into the Characteristics of DC Nitrogen Plasma Used for Group III-N Semiconductor Thin-Film Growths." In 2018 41st International Spring Seminar on Electronics Technology (ISSE), 1–5, 2018. <a href="https://doi.org/10.1109/ISSE.2018.8443696">https://doi.org/10.1109/ISSE.2018.8443696</a>.

- 5. Tot, J., R. Dubreuil, and D. Alexandrov. "Low Temperature Growth of InAlN on Epitaxially Grown SiC/Si (111) Wafers." In 2017 40th International Spring Seminar on Electronics Technology (ISSE), 1–5, 2017. <a href="https://doi.org/10.1109/ISSE.2017.8000892">https://doi.org/10.1109/ISSE.2017.8000892</a>.

#### Posters Presented

- R. Dubreuil, J. Tot, and D. Alexandrov, "GaN Growth on ceramics by Low Temperature RP-MOCVD", poster presented at the 13<sup>th</sup> annual International Conference on Nitride Semiconductors (ICNS-13), July 9, 2019.

- J. Tot, A. Kakanakova-Georgieva, and D. Alexandrov, "Low-temperature deposition of InN layers on high-temperature MOCVD grown AlN layers", poster presented at the International Workshop on Nitride Semiconductors (IWN) 2016.

#### Oral presentations

"Low Temperature Growth of InAlN on Epitaxially Grown SiC/Si (111) Wafers." In 2017 40th International Spring Seminar on Electronics Technology (ISSE)

#### 1. Background Information

#### 1.1 Nitride History

Group III-V semiconductors are binary semiconductor compounds used in many electrooptic and high frequency applications within electronics used as alternatives to silicon. This is often due to a direct bandgap, meaning they can efficiently absorb or emit radiation at or above their bandgap energy, or they exhibit improved electron mobility and or breakdown characteristics compared to silicon.

Table 1: Comparison of some III-V materials properties and silicon [1], [2]

| Material | Mobility (cm <sup>2</sup> /Vs) | Critical field<br>(V/cm) | Bandgap<br>(eV) | Туре     |

|----------|--------------------------------|--------------------------|-----------------|----------|

| Si       | 1400                           | 300000                   | 1.12            | indirect |

| GaAs     | 8500                           | 500000                   | 1.424           | direct   |

| GaP      | 250                            | 100000                   | 2.26            | indirect |

| GaSb     | 3000                           | 50000                    | 0.726           | direct   |

| InAs     | 44000                          | 40000                    | 0.354           | direct   |

| InP      | 5400                           | 500000                   | 1.344           | direct   |

| InSb     | 77000                          | 1000                     | 0.17            | direct   |

| GaN      | 1400                           | $3.0-5.0 \times 10^6$    | 3.42            | direct   |

Historically the group III materials have consisted of aluminum, gallium, and indium, while the group V materials have been phosphorus, arsenic, and antimony. Binary (GaAs, InP), ternary (e.g. Al<sub>x</sub>Ga<sub>1-x</sub>As) and even quaternary (In<sub>x</sub>Al<sub>y</sub>Ga<sub>1-x-y</sub>As) alloys have been studied for several decades due too the ability to produce closely matched bulk wafers through a liquid phase growth process such as Czochralski or Bridgman processes. This allows for relatively cheap substrates to be produced with low defect densities (<10<sup>5</sup> cm<sup>-3</sup>) and high purity.

Group III (Al, Ga, In) -Nitride based materials however were hindered because they cannot be grown with these techniques due to the high vapour pressure of nitrogen and high melting point

of nitrides, leading to dissociation of nitrogen from the material well before melting. Without the ability to produce wafers through liquid melt techniques, native substrates relied on vapour deposition techniques which are comparatively slow and expensive, causing wafers greater than 2" to be unavailable at a commercial scale. While bulk production of GaN wafers offers the highest quality materials for devices, it is not at a point to commercially compete with crystal growth of nitrides on foreign substrates (heteroepitaxy on Al<sub>2</sub>O<sub>3</sub>, 6H-SiC and more recently Si). Heteroepitaxy has seen commercial success since the 90's with the blue LED, however heteroepitaxial growth inevitably leads to a high degree of threading defects (>10<sup>9</sup> cm<sup>-2</sup>) extending from the interface of the two materials due too the mismatches involved. A variety of techniques such as AlN interface buffer layers [3], low temperature nucleation layers [4], and selective area growth [5] techniques have lowered dislocation densities in device epilayers to <10<sup>7</sup> cm<sup>-2</sup> [6].

Many different growth techniques have been developed for GaN epitaxy specifically, since most devices only use low alloy content AlGaN or InGaN for junctions/quantum wells. Most techniques rely on the thermal decomposition of ammonia (NH<sub>3</sub>) as a source of nitrogen for the growth, requiring temperatures of at least 600 °C to begin efficient production of atomic ammonia (Figure 2) and high V/III ratios to help prevent nitrogen desorption [2].

Figure 1:Decomposition efficiency of ammonia as a function of temperature. The lower limit of atomic nitrogen production using ammonia is shown to be 600 °C from the characteristics of this curve [5].

Temperatures higher than 600 °C are used to enhance surface migration of the metal species during growth, a typical growth temperature is 1050 °C using chemical vapour deposition (CVD) [7]. In the absence of additional energy input (plasma, laser excitation), the thermal energy largely determines the surface morphology by limiting the migration of deposition species on the surface, controlling the grain size and growth rate of different crystal planes. Figure 2 illustrates how the relative growth rate of the crystal planes changes with temperature and pressure [5].

Figure 2: The effect of temperature and pressure on controlling the relative growth rate of different hexagonal planes [5].

In the interest of transparent and flexible illumination/display technology more advanced processing technologies have been used to deposit crystalline InN, GaN, AlN and ternary alloys at temperatures well below 1050 °C [8]–[12]. Plasma based techniques are effective in lowering the overall thermal budget, with crystalline GaN being deposited between 400 °C and 500 °C on a range of substrates including glasses [13]–[16]. Much of the underlying defects are still largely unavoidable however due too the lattice and thermal mismatch with the substrate material and dislocations are still prone to appear in these low temperature techniques.

#### 1.2 Motivation

A growing field of research in nitride materials is their application to extreme environment electronics. These include exposure to corrosive environments, various forms of radiation, and high temperatures [17]. The high temperature stability of wide bandgap semiconductors an attractive feature for aerospace and space exploration, engine monitoring, flame detection and deep well drilling where bulk silicon technologies face fundamental material challenges [18]. In many of these applications the use of passive or active cooling is not feasible or may add unwanted cost and weight to designs. While wide bandgap materials enable device operation, there are many other challenges associated with device level design in these environments that extend past the active material. Contact metallization, die attach mechanisms and device packaging are also significant challenges to consider.

The die packaging is critical to device reliability and in extreme environments. Conventional FR4 PCB's have a glass transition of 130-170 °C and should not be operated close to this temperature. At temperatures beyond this, inorganic ceramics or metals are used due too their thermal stability and high thermal conductivity compared to organic materials. Low

temperature cofired ceramics (LTCC) or glass-ceramic composites, are low-cost materials that are resilient enough for these applications with a wide range of electrical/physical properties available by their composition [19]–[22]. The nature of ceramic processing also allows these materials to be shaped, cut, and folded much like a plastic prior to firing. Embedded cavities and conductors can also be created for a wide range of novel applications, such as fluidics, that extend beyond a mechanically rigid planar substrate material [23]–[25].

Die attach solutions currently involve using metals and organic materials as intermediates between the ceramic and the semiconductor die. Die attach and contact metals are points of failure in high temperature operation where their thermal mismatch can cause lift off. The motivation of this work is to use oxide materials to coat the surface of the LTCC for direct CVD film growth, eliminating the die attach process by a direct growth on the ceramic. The benefit of this would be a higher thermal stability of the attaching layer compared to metals and organics, along with removing the size and shape limitations associated with the attaching substrate. Oxide materials have the added benefit of being readily deposited by solution at room temperature with melting points <1000 °C. In this work Plasma Enhanced Chemical Vapour Deposition (PECVD) and solution processed silicon, zinc and aluminum oxides were used to enable low temperature crystalline films to be deposited on LTCC substrates. The surface characteristics of the oxide buffer and the PECVD films are characterized using X-ray and electron microscopy/spectroscopy techniques. The electronic properties of the LTCC/ZnO/GaN structure are tested by attempting to fabricate a Schottky diode structure on a deposited thin film.

#### 2. Materials

#### 2.1 III-V Nitride Semiconductors

One of the fundamental challenges of heteroepitaxy of III-N semiconductors comes from their crystal structure. All group IV elemental (Si, Ge) semiconductors and non-nitride group III-V materials have a cubic zincblende (ZB) structure, while the most stable phase of the III-Nitrides is hexagonal wurtzite (WZ). Figure 3 shows the relationship between bandgap and lattice constant for many different semiconductors. All materials seen on the right-hand side of Figure 3 share a ZB structure whereas the left hand side shows the WZ structure of the nitride family. The bandgap of InN is typically given as 0.7-0.8 eV, which has been strongly debated over the last 20 years. The value of ~0.7 eV is accepted based on strong room temperature photoluminescence peaks, however this is debatably due too Mie resonance with metallic In clusters [26]. On the contrary, a larger bandgap (>1.5 eV) has been shown to be strongly dependent on oxygen content [27]. Recent work in the Lakehead semiconductor research lab in conjunction with the Canadian Light Source (CLS) at the University of Saskatchewan has demonstrated a bandgap of ~1.8 eV through X-ray absorption/emission spectra to directly probe the band structure of different InN samples of varying morphologies [28].

Figure 3: Bandgap and lattice constant of many common semiconductors [29].

Although significant research on their cubic structures has been performed since it can be grown metastably on cubic substrates such as (100) GaAs, more mismatch exists on cubic templates than with existing hexagonal systems and it has proved challenging to avoid hexagonal inclusions in the metastable cubic structure. Motivation in this field stems from several advantages of the cubic system due too the additional crystal symmetry, such as the lack of polarization fields, increased carrier mobilities, and lower dopant activation energies [30]–[32].

While both WZ and ZB structures share a tetrahedral unit cell due too the sp<sup>3</sup> hybrid bond shape they differ in how these unit cells stack. As seen in Figure 4, a ZB structure (left) will have an AaBbCc ordering along the [111] crystal direction, while the WZ crystal (right) has an AaBb order along to [0001] direction where A and a represent the cation (positive species) and anion (negative species) respectively. The difference in the stable structure comes from the ionicity of the bond III- N, where electrostatic attraction between III-N dipoles makes alignment along the c-axis more favorable (dotted lines in Figure 4).

Figure 4: ZB structure (left) with AaBbCc ordering along the [111] crystal direction. The WZ crystal (right) with AaBb stacking along the [0001] direction [33].

This attraction is relatively weak and can be overcome by depositing these materials on cubic templates. The wurtzite (WZ) structure does not have complete charge symmetry, due too the alignment of the bonds along the c-axis. This induces a spontaneous  $(P_{sp})$  and piezoelectric  $(P_z)$  polarization effect in the crystal, which are both aligned either into or away from the (0001) surface along the c-axis depending on the stacking order (cation to anion AaBb, or vice versa, aAbB). Piezoelectric polarization induces a voltage on the c-axis of the crystal as a restoring force in response to strain in the crystal along that direction, whereas spontaneous polarization comes from the charge difference between the Ga and N in the crystal.

The direction of the polarization is determined by the substrate material, with the ordering being continued from the substrate into the nitride. Since III-Nitrides are usually grown on sapphire or (111) silicon, both of which have no polarization, the polarity is determined by the nitridation process. Epitaxy begins in both cases by depositing a thin interface layer of AlN to minimize lattice mismatch with the substrate and avoid Ga diffusion [34]. The growth conditions during this phase will dictate the polarity of all subsequent epilayers, with two possibilities seen in Figure 5 [35], [36]. Ga facing surfaces have triple co-ordinated gallium facing the surface and are generally found to be smoother than N facing surfaces. In Ga-facing surfaces the polarization vector is pointing up from the surface, while surfaces ending with triple co-ordinated nitrogen will be the opposite.

Figure 5: Two possible stacking orders in III-Nitrides that lead to polarization facing the substrate (left) and facing the surface (right). The magnitude of the spontaneous ( $P_{sp}$ ) and piezoelectric ( $P_{z}$ ) polarization is the same, but the direction is opposite [37].

The direction of this vector is useful in the polarization engineering of nitride structures, where charge accumulation can occur without doping and independent of temperature. From Gauss' law  $\left(\rho = \nabla \cdot \left(P_{sp} + P_z\right)\right)$ , a charge density  $(\rho)$  will appear due to changes in polarization, such as in heterojunctions, and will generate a bound charge at the surface as illustrated in Figure 6.

Figure 6: High electron mobility channel formation from spontaneous polarization vectors in a Ga facing GaN/AlGaN heterostructure. The Ga facing crystal has  $P_{sp}$  facing the surface while N facing crystal has it facing the substrate.

This effect can be desirable such as in the case of electron channel accumulation in high electron mobility transistors (HEMTs). High electron sheet densities (>10<sup>13</sup> cm<sup>-2</sup>) can be achieved without introducing donor dopant materials in the barrier layers that act as ionized scattering centres, degrading channel mobility. These channels are localized to the interface and can be well modelled by a triangular quantum in the device band structure [38]. This same polarization effect can also be detrimental, biasing quantum well structures in the well known quantum confined stark effect (QCSE). Polarization works separates holes and electrons in quantum well structures, thereby causing a reduction in the overlap of their wavefunctions and reduces recombination efficiency. Since the dipoles face along the c-axis in the wurtzite structure, the effects of polarization depend on the degree of c-axis orientation to the surface. shows how the degree of piezoelectric polarization changes between from the c, r, and m planes in GaN.

Figure 7: Change in piezoelectric polarization constant between from the c, r and m planes in GaN [39].

Polarization effects are useful in nitride-based sensors since they are not induced by ionized dopants or significantly dependant on the bandgap and are therefore stable over a wide range of

temperatures. The electron density at the GaN surface in is however dependant on the positive charges induced on the upper surface of the AlGaN for charge neutrality, therefore any source of negative charge on the surface will deplete the charge density in the buried AlGaN-GaN interface. Transistors based on these junctions are typically passivated for device stability, but a wide range of sensors operate by functionalizing this surface to selectively supply negative charges [40]–[43].

The piezoelectric polarization can also be utilized to measure mechanical strain. Changes in the strain state of the upper AlGaN layer will either reduce or enhance the channel carrier density depending on direction of the strain. This reverse effect can be used in nanogenerator structures, where paired with a rectifying junction, can produce nanoscale direct current generators [44]. The polarization coefficients are relatively independent of temperature, however internal strain created by mismatch can affect charge accumulation and tends to increase with temperature. In lattice matched structures the high temperature stability of nitrides makes them valuable for high temperature sensor design [45].

#### 2.2 Oxide Materials

The choice of oxides to coat LTCC comes from the composition of the ceramics themselves. To form a good bond with the substrate, a component oxide is desirable, which will easily bond into the glass network. Three oxide materials were chosen as buffers, silicon dioxide deposited through spin coating, alumina deposited by anodization of metallic aluminum and zinc oxide deposited through dip coating.

#### 2.2.1 Zinc Oxide

ZnO is a group II-VI semiconductor with many similar properties to GaN. As in the III-N, the ionicity of the bonding gives rise to the WZ crystal structure as the most stable phase. ZnO itself has been the subject of a significant amount of research owing too its wide energy bandgap

(3.437 eV [33]) allocating it many of the advantages associated with a large bandgap such as high temperature and high-power operation, low noise generation, and high breakdown voltage.

The relatively close size of the zinc/gallium atoms and oxygen/nitrogen atoms gives ZnO a closely sized crystal lattice to GaN. Similar to the III-N system, bandgap engineering is possible by alloying. This is typically done with MgO and BeO for larger bandgap alloys and CdO for lower bandgaps, although a full compositional range is not possible due too the cubic rocksalt structure of MgO and CdO [46].

Table 2: Unit cell properties of silicon, nitrides, and various oxide materials

| Material       | Lattice constant (Å) |        |  |

|----------------|----------------------|--------|--|

|                | a-axis               | c-axis |  |

| InN [47]       | 3.537                | 5.703  |  |

| GaN [47]       | 3.189                | 5.185  |  |

| AlN [47]       | 3.110                | 4.980  |  |

| ZnO [48]       | 3.249                | 5.205  |  |

| CdO [48]       | 4.689                | -      |  |

| MgO [48]       | 4.216                | -      |  |

| BeO [49]       | 2.718                | 4.409  |  |

| $Al_2O_3$ [50] | 4.765                | 12.982 |  |

| Si [50]        | 5.431                | _      |  |

The hexagonal shape of the ZnO crystal introduces similar challenges as seen in III-Nitride materials. Heteroepitaxy on substrates such as sapphire produce large lattice mismatches (18.4%) resulting in similar densities of threading dislocations on the surface  $(10^{-7} - 10^{-9} \text{ cm}^{-2})$ .

Metal oxides such as ZnO, SiO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> can uniquely produced in chemical solution using the sol-gel technique. Sol-gel relies on hydrolysis and condensation reactions to exchange alkyl ligands on the metal with bridging oxygen atoms to produce metal oxide colloids at room temperature. Using this technique, oxide materials can be produced as nano scale particles in

solution and thin films can be applied using wet chemical deposition techniques such as dip coating and spray coating. These versatile techniques can apply these coatings to many organic and nonplanar substrates. The relatively high surface area of nanoparticles lowers sintering temperatures and dense crystalline films can be produced at temperatures <600 °C. Compared to other oxide deposition techniques such as sputtering, it is simpler and more flexible in the choice of substrates. Solution chemistry can be controlled to introduce dopants [51]–[53], and controlling nanoparticle morphology is also possible with a variety of shapes with crystalline structure demonstrated [54]–[57].

The relative ease at which oxides can be wet etched compared to nitrides makes chemical wet etching highly selective in a III-Nitride/ZnO structure. Several reports of wet etching of ZnO have shown that a variety of acids including dilute mixtures of hydrochloric acid [58], [59] can etch ZnO at rates of 120 nm/min at 0.25%, increasing linearly with concentration [60]. The reported etch rates in this case are for RF sputtered layers, therefore even higher rates can be expected in sol-gel produced layers due too the increased porosity. This however may be a disadvantage in this work since wet cleaning processes for contact preparation can be destructive on the ZnO buffer.

A lack of reliable p-type doping of ZnO has been its most significant drawback to commercial device production. ZnO is normally found to be n-type because interstitial donor states from Zn (Zn<sub>i</sub>) and O vacancies (Vo) are the most stable point defects [61], as well as unintentional hydrogen donor incorporation from the growth process [62]. The low formation energies of these defects tends to lead to high background electron concentrations in grown layers. The ability to easily produce highly n-type ZnO and its wide bandgap make it an attractive alternative to ITO as a transparent conductive oxide (TCO), but limits its application in homojunction structures [63].

The general strategy in choosing a p-type dopant is a substitutional group IA element on a zinc site, codoping of donors and acceptors, or substitution of group VA elements on an oxygen site. The main issues that are usually encountered are the long-term stability of the p-type dopant, the activation energy required and its solubility.

#### 2.2.1.1 Zinc Contamination

While ZnO has a high melting temperature of 1,975 °C [64], in vacuum conditions the direct sublimation of ZnO to Zn and O gas is known to occur at temperatures as low as 700 °C [65]. Zinc and zinc containing alloys such as brass are avoided in vacuum technology due too the high vapour pressure of zinc, causing sublimation at low temperatures which can coat the reactor interior. Figure 8 shows the  $\Theta$ -2 $\Theta$  X-ray diffraction (XRD) results of a single crystal sapphire wafer heated in the contaminated system. Peaks at 42.01° and 91.00° are expected from the sapphire wafer, while all other are re-evaporated metal from the contaminant in the system.

Figure 8: Normalized  $\Theta$ -2 $\Theta$  XRD plot of the sapphire wafer after ZnO contamination (blue). A theoretical spectrum from Zn metal (red) is included, calculated from the HCP structure with a=2.6648  $\mathring{A}$  and c=4.9467  $\mathring{A}$  [66]. Major peaks related to the (0006) and (00012) peaks of sapphire (blue) are at 42.01° and 91.00° respectively. All other peaks in blue correspond to reactor contamination.

The contamination appeared on all subsequent growths and drastically reduced the quality of the epitaxial layers. In our system we found the temperature limit to be 650 °C, depositing GaN at 700 °C and a pressure of 1400 mTorr resulted in the characteristic peaks in Figure 8 (blue) on all samples. This is indicative of a deposition from the reactor walls, which could likely be a zinc contamination, however a comparison of the contaminated sapphire and the HCP zinc structure in Figure 8 shows the contaminant does not match the XRD pattern of pure zinc metal and were only found to present after heating ZnO samples in vacuum. A mechanical cleaning of the system was required to remove it. The exact nature of the contaminants is unclear, but regardless it sets a limit on the temperatures used in the ZnO experiments at 650 °C.

#### 2.2.2 Silicon Oxide

Sol-gel SiO<sub>2</sub> (or spin-on glass) has been used as insulating passivation layers, optical waveguides, a precursor to doped silica nanoparticles and has been used to produce several novel products such as Aero/Xero gels [67]–[70]. For LTCC it has been demonstrated as a planarization layer and a low cost planar optical waveguides [71], [72]. A hybrid sol-gel approach has been demonstrated as effective in reducing cracking by applying a mixture of silica nanoparticles with the coating solution to increase the volume fraction of silica in the drying solution, thus lowering shrinkage and strain in the layer. These layers did not demonstrate cracking even as thicknesses >1 µm were deposited and baked at 500 °C for 1hr. Samples used in this work were prepared by partners at TU-Ilmenau using the methods outlined in [72].

#### 2.2.3 Anodized Alumina (AAO)

Alumina is the non-crystalline version of sapphire, which is normally used in nitride growth, and is a large constituent of many ceramic mixtures. It can be produced through the anodic oxidation of metallic aluminum at room temperature. This process is used in many industrial

applications where the oxide material serves as a productive coating on the relatively soft metal. The structure of the produced film depends on the acid used as an electrolyte in the process and is the result of a balance between oxide dissolution at the acid-oxide interface and production of new alumina at the metal-oxide interface.

Figure 9: Anodized alumina production for a) low pH electrolytes resulting in a self-limiting barrier type and b) high pH resulting in a continuous pore etching or porous type material [73].

For weakly acidic solutions (pH 5-7) the oxide anodization current will quickly drop as the barrier becomes thick, as the field driven oxidation decays exponentially with thickness. The produced oxide is insoluble in these solutions so the process self limits and the oxide production will essentially go to zero at a thickness dependant on the applied voltage.

In low pH (<5) solutions the anodization will initially generate an oxide layer, however upon reaching a critical thickness (the minima in the anodization current in Figure 9b), random

stress fractures will occur in the oxide due too the large volume difference between aluminum and its oxide. This may also occur in weakly acidic solution if the thickness is too high but is undesirable in a protective coating. The fracture sites allow the oxidation to continue at the aluminum-oxide interface and the anodization current increases as the pores are created. Once the pore formation begins the volume expansion of the metal to oxide transition cause a mutual stress between adjacent pores and will help align them. The pore production can continue in the high field region at the bottom of the pore and thick, well aligned porous arrays can be produced from metal films at constant anodization current. This is done in a two-step process where an initial random pore array is allowed to reach steady state and removed, leaving a well aligned, dimpled template for a second anodization [73].

Figure 10: Two stage AAO template showing the initial random pore initiation and the dimpled template for the second anodization [73].

The pore structure can be controlled through the pH value of the electrolyte, which mainly defines the pore radius and the applied voltage, which controls the interpore distance. The lower the pH value of the solution, the smaller the pore and the higher the applied voltage the larger the interpore distance. It has been empirically found that in order to maintain an ordered array the porosity should be approximately 10% [74]. It is proposed that any interpore distance and size is

possible, so long as this 10% rule is obeyed the mutual interpore stress maintains order. Attempts to use the well ordered arrays in research have been as low cost, large area alternatives to lithographic patterning [75]–[77], templates for plasmonics and metamaterials [78]–[80], and templates for high aspect ratio nanorods [81]–[83].

A common experimental setup seen is 0.3 M oxalic acid (H<sub>2</sub>C<sub>2</sub>O<sub>4</sub>) solution and constant DC voltage of 40 V. The pore structure reported in these conditions varies based on the exact experimental conditions such as temperature and purity of the aluminum used, but using these values we can expect a pore diameter on the order of 30 nm and a spacing of 100 nm [74], [78], [84]–[87]. Given the stable nature of alumina, no oxygen contamination from the layer was observed in the experiments. The onset of glass vitrification in the ceramics therefore sets the temperature limit for the entire process [88]. The limiting temperature in this work using AAO/Heratape CT700 was determined to be 700 °C by observed rounding of edges at >700 °C.

#### 2.3 Cofired Ceramics

The application of ceramics in electronics dates to the 1950's where it was realized that ceramic processing techniques combined with screen printed conductors could not only significantly miniaturize circuit technology, but also integrate passive components in a durable monolithic structure suitable for mass production [89]. They posed several advantages over FRx organic circuit boards in applications where heat, environmental chemistry or dielectric loss is too high for reliable operation. They can be roughly divided into two major categories, high and low temperature cofired (HTCC and LTCC respectively), depending on the temperature used in the

final sintering process in the ceramic production. A typical ceramic production process can be seen in Figure 11.

Figure 11: LTCC production flow diagram from initial slurry mixture to a final laminated multilayer stack [90].

The slurry is a mixture of oxide particles of representing the final composition of the sintered ceramic, with the addition of an organic binder, solvent, and plasticizers. For LTCC most of these oxides are a mixture of silica (SiO<sub>2</sub>) and alumina (Al<sub>2</sub>O<sub>3</sub>) with differing amounts of modifier oxides (B<sub>2</sub>O<sub>3</sub>, PbO, Na<sub>2</sub>O, CaO, BaO, ZnO, Li<sub>2</sub>O). The mixture is designed to change various parameters of the ceramic, such as melting point, thermal conductivity/expansion, and dielectric loss by introducing mobile/non-mobile ionic species and non-bridging oxides in the silica-alumina amorphous network. LTCC and HTCC differ in that HTCC ceramics are least 96% alumina.

The layers are processed on a continuous reel poured from the slurry, shaped by a doctor blade, and prebaked to remove solvents. The green (pre-fired) paper-like ceramics are cast on mylar reels and patterned using laser and micromachining processes. Via holes can be formed either by punching or laser machining of the substrate to diameters as low as 150 µm [91], reaching

as low as 30  $\mu$ m in current research and trace widths as narrow as 20  $\mu$ m [92]. These features are filled with metallic frit paste by screen printing that bonds to the ceramic on firing, allowing for strong adhesion to the surface. Surface passives such as thick film resistors can be tested prior to final lamination and trimmed for high accuracy (+/- 2%). Much of this processing can be done in parallel with high volume, allowing for low cost with fine features. The final sintered thickness of the layers can be anywhere from 100  $\mu$ m to 200  $\mu$ m in thickness with as many as 30 layers [93].

The temperature of the final firing limits the materials used for conductors in these substrates. Since the highest conductivity metals have melting points below 1000 °C, processing temperatures are typically limited to 900 °C at the risk of deforming embedded line structures.

Table 3: Melting point of various conductors used in ceramic technology [90].

| Material | Electrical Resistance<br>(μΩ·cm) | Melting Point<br>(°C) |

|----------|----------------------------------|-----------------------|

| Cu       | 1.7                              | 1083                  |

| Au       | 2.3                              | 1063                  |

| Ag       | 1.6                              | 960                   |

| Pd       | 10.3                             | 1552                  |

| Pt       | 10.6                             | 1769                  |

| Ni       | 6.9                              | 1455                  |

| W        | 5.5                              | 3410                  |

| Mo       | 5.8                              | 2610                  |