## The End of The Intel Age

by

**Robert Swope Fleming**

B.S.E. Electrical Engineering (2001)

**Princeton University**

Submitted to the System Design and Management Program in Partial Fulfillment of the Requirements for the Degree of

## Master of Science in Engineering and Management

at the

Massachusetts Institute of Technology

May 2011 [Jvne 2011] © 2011 Robert Swope Fleming All rights reserved

The author hereby grants to MIT permission to reproduce and to distribute publicly paper and electronic copies of this thesis document in whole or in part in any medium now known or hereafter created.

~

/

| Signature of Author | 17-                    |            | <i>V</i><br>Design and | Robert Swope Fleming<br>d Management Program                   |

|---------------------|------------------------|------------|------------------------|----------------------------------------------------------------|

|                     | $\wedge \wedge \frown$ | Λ          |                        | January 2010                                                   |

| Certified by        | - Wy                   | Senior Lec | 7                      | Michael Davies<br>Thesis Supervisor<br>gineer Systems Division |

|                     |                        |            |                        | د ∩ ∩                                                          |

| Accepted by         |                        | System     | Design a               | Patrick Hale<br>Director<br>& Management Program               |

| MASSACHUSETTS INSTITUTE<br>OF TECHNOLOGY |               |  |  |  |

|------------------------------------------|---------------|--|--|--|

|                                          | JUL. 2 0 2011 |  |  |  |

|                                          | LIBRARIES     |  |  |  |

ARCHIVES

## **Table of Contents**

| Executive Summary - The End of the Intel Era                   | 4  |

|----------------------------------------------------------------|----|

| Chapter 1 - Why Intel Must Change                              | 7  |

| Chapter 2 - Motivation and Terminology                         | 17 |

| Categorization and Terminology                                 | 18 |

| PART I                                                         |    |

| Chapter 3 - Dvnamics of Innovation                             | 23 |

| The Abernathy-Utterback Model and Dominant Design              | 23 |

| Christensen's Attack-From-Below Disruption                     |    |

| Chapter 4 - Architecture. Modularity. and Innovation           |    |

| Architectural Innovation                                       | 29 |

| Design Rules & Modularity                                      | 32 |

| <u>Chapter 5 - Survival of the Incumbent</u>                   |    |

| PART II                                                        |    |

| Chapter 6 - A Brief History of Innovation and the PC           |    |

| The IBM 5150                                                   | 41 |

| The Importance of Instruction Set Architectures                |    |

| RISC Versus CISC                                               |    |

| The Self-Fulfilling Prophecy of Moore's Law                    |    |

| Chapter 7 - A PC on Every Desk                                 |    |

| The Beginnings of the PC Revolution                            |    |

| The PC Onslaught                                               | 49 |

| The Commoditization of the PC                                  |    |

| <u> Chapter 8 - The Semiconductor Ecosystem in the PC Era</u>  | 53 |

| From Vertical to Horizontal                                    | 53 |

| Increasing Performance, Decreasing Costs                       | 54 |

| The Advent of Multi-core                                       | 57 |

| The Power-Wall                                                 |    |

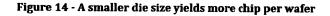

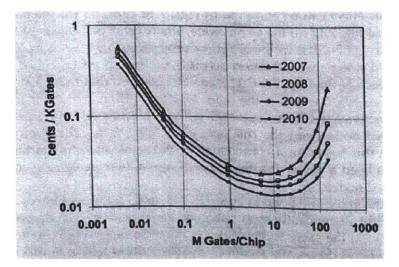

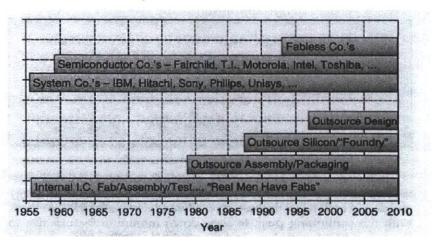

| The Economics of Semiconductor Costs                           |    |

| The Economic Exhaustion of Intel's Business Model              |    |

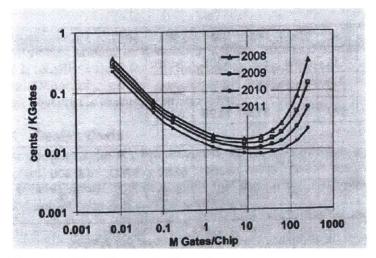

| The Rise of the Independent Wafer Foundries                    | 67 |

| The System on a Chip                                           | 68 |

| The Advanced RISC Machine                                      | 71 |

| PART III                                                       | 75 |

| Chapter 9 - Computing Diversity                                |    |

| A Myriad of Devices                                            | 76 |

| Servers, Cloud Computing and Data Centers                      |    |

| Macro Level Forces Shaping Micro Level Architecture            | 81 |

| After the Wall                                                 | 82 |

| Chapter 10 - Where the Battle is Being Fought                  |    |

| Smartphones                                                    |    |

| Data Centers and Servers                                       |    |

| Chapter 11 - ARM and Intel In the New Microprocessor Ecosystem | 91 |

| The Challenges In Microprocessors                              |    |

| The Challenge In Modular Design       |  |

|---------------------------------------|--|

| The Challenge With the Business Model |  |

| Conclusion                            |  |

| Bibliography                          |  |

### Executive Summary - The End of the Intel Era

Today, Intel is nearly synonymous with computers. In the past thirty years nearly all personal computers and the great majority of servers have shipped with a processor based on Intel's x86 architecture, of which Intel is the dominant vendor. Yet the past few years have seen a subtle yet remarkable convergence of different industry trends that very well may topple the semiconductor giant.

For the past three decades, computers have largely assumed the same shape and form, regardless of their task. Laptops, desktops, and servers have all been based on the same open modular architecture established by IBM. Yet this is not likely to be the case going forward. The past decade has seen the rise of embedded computing, perhaps best epitomized by smartphones and tablet computers.

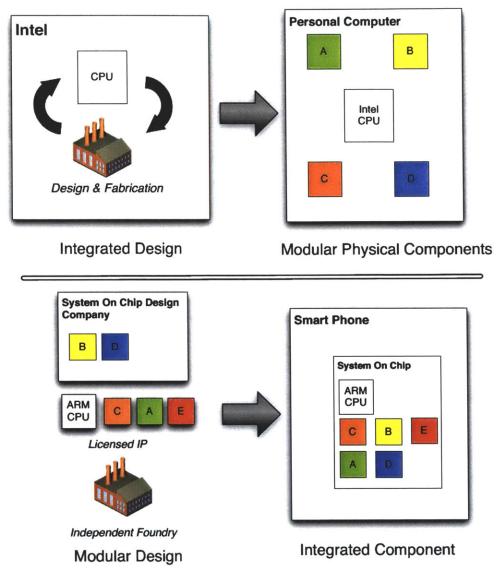

Instead of the standard PC architecture where individual components can be easily exchanged, embedded devices are typically modular *designs* with highly integrated physical components. Independent functional units, all designed by independent companies, are integrated onto the same piece of silicon to achieve system cost and performance targets. Instead of a standard x86 processor, each device category likely has a chip optimized for its specific application.

At the same time that the form of computing is changing, we are witnessing a redistribution of where computing power resides with Cloud Computing and data centers. These have ordinarily been the province of Intel based machines, but data centers have moved from using standard off-the-shelf PCs to custom designed motherboards. Again, we are seeing a shift from the modular personal computer architecture to one that is customized for the task at hand. Another concern for Intel is that the standard metrics by which products compete are in flux. For both embedded systems and data centers, the operational costs and constraints are starting to outweigh the initial outlay costs. An example is the industry shift from overall performance to system power efficiency. Intel has been a relentless driver of processor performance, and this is a significant change of focus for its R&D divisions.

Of all Intel's competitors, ARM best represents the magnitude of these challenges for Intel, and is well positioned to take advantage of all these trends. Their business model of licensing their design is well suited for a world with customized architectures, and their extensive experience in low power embedded devices has given them an advantage over Intel in processor power efficiency.

Intel is heavily invested in its existing vision of the market. They have always maintained a manufacturing process advantage through tremendous investments in new foundries, and have long championed the open PC modular architecture. Time will ultimately show if Intel is capable of meeting these growing challenges. Yet it is clear that in order to do so, it must make radical changes to itself. One may ask if it is even the same company that emerges.

### Acknowledgements

.

As I come to the end of writing this thesis, it is clear to me that I am indebted to several people. First and foremost, my entire grad-school experiment would not have been possible without the love and support of my wife Dana. It is a testament to her support of me that she spent the afternoon proofreading this document on her very first Mother's Day as a Mother. I would also like to thank my son Benjamin. The first nine months of his life coincided with the writing of this thesis, and we spent many mornings discussing over breakfast why ARM is giving Intel fits.

I would like to thank my thesis advisor, Michael Davies, for his invaluable guidance. Michael's input was essential in helping me give structure to the jumble of ideas bouncing around in my head, and helping me to avoid unproductive dead ends. And I would not have been able to get this thesis across the goal line without his help these last few weeks. Finally, I would like Pat Hale, Professor James Utterback, my classmates, and everyone who is involved in making it such an excellent program.

### Chapter 1 - Why Intel Must Change

Intel's dominance can be traced back to 1981, when IBM first introduced the personal computer. Since then Intel has dominated the processor segment of personal computing and achieved a success that few other companies have matched. In the past thirty years nearly all personal computers and the great majority of servers have shipped with a processor based on Intel's x86 architecture, of which Intel is the dominant vendor.

Yet the past few years have seen a subtle yet remarkable convergence of different industry trends that very well may topple the semiconductor giant. Not only does Intel find itself technologically behind an unexpected competitor, its very business model is threatened.

The challenges to Intel are threefold. First, the metric of competition has shifted from CPU performance to power efficiency, which is something Intel has not had to have as its primary focus in the past. Second, the *design* of chips is becoming more *modular* while the chips themselves are integrating a wider variety of functionality. This is an inversion of Intel's tradition of designing an integrated CPU and selling it into a modular system. Finally, Intel is at a significant disadvantage in a business ecosystem of licensed modular design and the commoditization of semiconductor fabrication, as its organizational structure and size is predicated on the sizable profit margins it makes from high performance processors and the co-specialization of design and manufacturing.

In order to survive, Intel will likely need to shape itself into a fundamentally different company. In November 2010, Intel announced that it would allow Achronix to use its foundries<sup>1</sup>. This marks the first time Intel has produced chips for another company, and is perhaps a sign that Intel recognizes that radical change is

<sup>&</sup>lt;sup>1</sup> <u>http://www.eetimes.com/electronics-news/4210263/Intel-to-fab-FPGAs-for-startup-Achronix</u>, observed on March 7, 2010.

necessary. There are now also rumors afoot that it will compete to manufacture some high volume ARM chips for Apple<sup>2</sup>.

Despite the myriad of tasks that computers are used for, the number of different form factors is remarkably small. Client and consumer devices can broadly be thought of as desktops and laptops (and arguably net-books as well). Servers can generally be categorized by processing power into small, medium, and large, determined by the number of processor sockets they have (Gillett, 2010).

Furthermore, these different form factors all have nearly identical internal system architectures, based on an open, modular design championed by Intel. The physical components of the system are interchangeable, and a PC firm can replace one vendor with another without significantly changing the design of their system. The only constant is an x86 processor and the Windows operating system, hence the term "Wintel." In essence, we have a massive industry served by a handful of different product lines, all based on the same open modular system architecture.

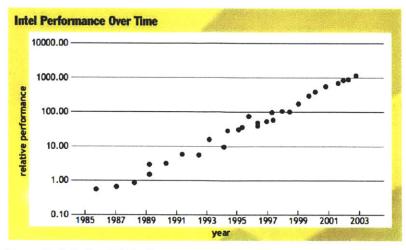

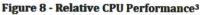

This has resulted in Intel being able to serve an enormous market with only a handful of different processors. Instead of product diversity, they have focused on manufacturing excellence and the inherent performance advantages that can be found in smaller and smaller process geometries. If we measure CPU performance against cost (MIPS / \$), Intel has relentlessly improved this metric year over year, directing all their resources and innovation towards it. This is a strategy that has served them well and is perhaps best epitomized by Moore's Law, the famous observation made by Intel co-founder Gordon Moore that the number of transistors on a chip doubles every two years.

<sup>&</sup>lt;sup>2</sup> Barak, Slyvie. "Could Intel Churn out ARM chips for Apple?" *RCR Wireless*. May 4 2011 < <u>http://www.rcrwireless.com/article/20110504/CHIPS/110509966/0</u> > Observed May 6, 2011.

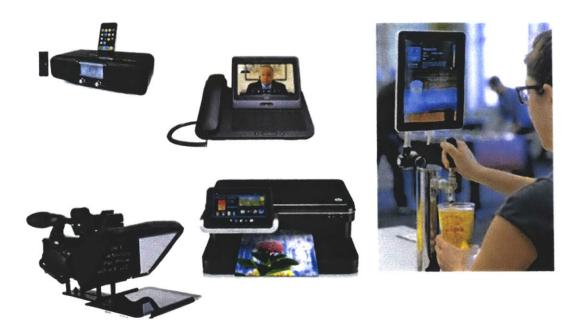

Yet the landscape of computing is changing. Instead of laptops, desktops, and servers we see the advent and ascent of smartphones and now tablet computers. Few will argue that these types of devices are not poised to grow significantly. The market research firm IDC estimates that smartphones outsold PCs for the first time in Q4 2010.<sup>3</sup> But the change extends beyond just smartphones and tablets. Everyday devices are beginning to come equipped with significant processing power. The list is long and varied: automobiles, televisions, printers, routers, handheld gaming devices, e-books, cell-phones, digital cameras, etc . . .

While the personal computer and server market has a well-established and inherently modular architecture that has benefited Intel, the embedded devices market is populated by a myriad of different architectures. Each application has its own set of size, weight, and cost-performance constraints and challenges, which in turn impose tough tradeoffs between performance and other features. This has given rise to System on a Chip (SoC) based solutions, which allow embedded devices manufacturers to both reduce system costs and have a solution highly customized to their use-case.

These SoC designs pull multiple functions onto the same piece of silicon. Instead of reserving the entire die for the processor, SoCs incorporate other system support functions, such as a memory controller, as well as application specific logic, such as a wireless modem or an ink-jet print head controller. In essence, we have a trend of *modular designs* but highly integrated physical components.

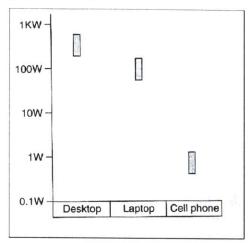

Embedded devices also have different power considerations than traditional PCs. Many of these devices are portable, mobile devices that are disconnected from the power grid and have to run off a battery. Unfortunately, there is no Moore's Law for

<sup>&</sup>lt;sup>3</sup> 100.9M - 92.1M;

http://www.idc.com/about/viewpressrelease.jsp?containerId=prUS22689111&sec tionId=null&elementId=null&pageType=SYNOPSIS and http://www.idc.com/about/viewpressrelease.jsp?containerId=prUS22653511&sec tionId=null&elementId=null&pageType=SYNOPSIS; Observed on February 9.

batteries, and adding more processing power to a smartphone can come at the cost of a shortened operational period. While the processing power of a smartphone is certainly an important design parameter, the mobility requirements far outweigh it. Few people would use a mobile device that had to be recharged every hour. Across a wide variety of market segments, we can see the focus shifting from CPU performance to CPU energy efficiency.

At the same time that the form of computing is changing, we are witnessing a redistribution of where computing power resides with Cloud Computing. Cloud-based services can bring new functionality to consumers without requiring them to purchase new devices. Cloud computing has the potential to aggregate our computing power requirements and ultimately reduce the need for raw CPU horsepower in individual devices. Instead of a PC for every desktop, the future will likely be a smartphone or a tablet paired with cloud-based services for every person.

These changes also reinforce the aforementioned shift to CPU energy efficiency. Cloud computing is aggregating the processing needs of countless people into large data centers and server farms. And despite the role of data centers as providers of computing cycles, the cost of processor computing cycles has fallen to where these data centers are more concerned with the operating costs associated with processing, namely cooling and electricity requirements, than with the capital investment required to add more processing power.

Cloud computing has been around longer than the personal computer, but it is only recently that it has reached mass-market adoption as a result of better connectivity. Nearly every tablet computer sold has a network connection of some kind, and network connectivity is one of the defining features of smartphones. This has the dual effect of emphasizing the importance of network connectivity in devices while also deflating the need for processing power for the individual. In short, macro-

level changes in consumer behavior are inflicting change onto the micro-level architecture of devices.

Perhaps the company that best embodies this convergence of threats to Intel is ARM Holdings. ARM Holdings is the developer of the ARM architecture, which is the dominant processor in the embedded devices market. If the future of computing devices truly stems from embedded devices, then ARM stands to benefit simply because of its market share. But this is a threat that runs deeper that simple market positioning.

There are three reasons why ARM is of particular concern to Intel.

First is the rising concern with operational costs of a system over the upfront costs. This manifests itself as an industry shift from a performance-cost tradeoff (MIPS/\$), to a performance-*energy efficiency* tradeoff (MIPS/Watt). For several decades, Intel has created processors with higher and higher performance, and all the while driving down costs lower. Yet now that customers care about MIPS per Watt, it is ARM who has the advantage. In many ways, this is a classic Christensen disruption from below.

The second concern is the aforementioned trend of modular design but integrated physical components. Intel has made its fortune off serving the PC and server market with a handful of products. In a market where we have a plethora of customized and integrated components, Intel can no longer rely on its manufacturing volume. Moreover, when the design is modular, ARM's business model of licensing its processors to SoC designers allows it to be a critical part of any design, regardless of how customized or integrated it is. Firms can design the portion of their system that needs to be customized themselves, and then simply license an ARM processor to complete the system. Intel is not an option, because they neither offer a product that can address a particular niche, nor can they license their x86 processors into that design.

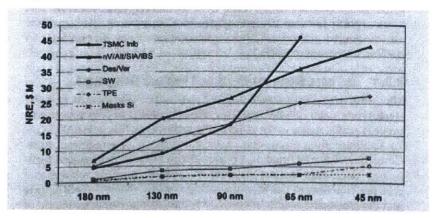

The Non-Recurring Engineering (NRE) costs associated with chip design have steadily risen year after year. For companies that would seek to make a custom chip for their product, it would at first appear that the NRE would be prohibitively high. There puts tremendous pressure on design teams to only to focus their engineering efforts on areas where they can cost effectively differentiate themselves from their competitors. In crude terms, there is good NRE, which is the creation of unique designs with value that attract customers, and there is bad NRE, which is engineering effort that creates something that is redundant in the market but is necessary. A modular design ecosystem allows companies to simply license IP for what would otherwise be 'bad' NRE. A modular design ecosystem, with ARM as the dominant processor core vendor, enables companies to entertain using customized chips.

Finally, we must question if the market of the future can support an integrated company of Intel's size. Intel is a company of \$100 Billion market cap because it has created a tremendous amount of value with its manufacturing capabilities. Intel's business model is predicated on processor design being tightly coupled with fabrication processes, which requires tremendous investments in process research and development and massive capital expenditures in fabrication equipment. Intel's business model is size. This is largely responsible for the performance improvements we have seen over the last three decades. Yet companies like TSMC are commoditizing the manufacturing of semiconductors and are willing to live off thinner margins. They generally lag behind Intel in process size, but it is not clear that this will continue to segment the market. While smaller process geometries have brought lower power consumption in the past, we are reaching a point where increased leakage current will attenuate these gains. If manufacturing excellence is no longer a competitive advantage, can Intel capture the requisite value to justify its size? Even if Intel is successful in matching ARM on energy efficiency and device integration, it may need to radically change itself in order to survive.

The differences between Intel and ARM Holdings go beyond simple market position. These are companies with two fundamentally different business models. Intel has 82,500 full-time employees and a Market Cap of \$119.66 Billion<sup>4</sup> while ARM Holdings has 1,861 employees and a Market Cap of \$11.08 Billion.<sup>5</sup> In 2009, Intel had revenues of approximately \$35.1 Billion and an operating income of \$5.7 Billion<sup>6</sup>. In the same year, ARM reported revenues of \$463.8 Million and an operating income of \$73.8 Million<sup>7</sup>. In engineering terms, Intel's x86 architecture is a CISC-based architecture (Complex Instruction Set Computer) while the ARM architecture is RISC-based (Reduced Instruction Set Computer). And finally the business models are radically different. Intel fabricates its own semiconductors, and is heavily invested in its operations. In contrast, ARM Holdings manufactures nothing and instead licenses its design out to other semiconductor companies.

This thesis will strive to answer the question – what will happen to Intel? - and is divided into three sections. Part I, spanning chapters 3, 4, and 5, is a survey of the academic frameworks used when writing this thesis. Chapter 3 covers the topics of radical innovation, dominant design, and disruptive innovation. In broad terms, it explores how industries have patterns of innovation that evolve as an industry matures, and the phenomenon of disruptions, where high performance technologies are disrupted by lower performing alternatives. These are useful frameworks to help dissect the conflict between Intel, an industry stalwart who played a crucial role in the birth of the PC industry, and ARM, whose expertise is in cell phones and the embedded space.

The nature of the differences between Intel and ARM are largely architectural differences. This is not the difference between cars and horse-drawn carts. Both companies are in the process of designing integrated circuits. Architectural

<sup>&</sup>lt;sup>4</sup> <u>http://finance.vahoo.com/g?s=INTC</u>, observed on January 25, 2011.

<sup>&</sup>lt;sup>5</sup> http://finance.yahoo.com/q?s=ARMH, observed on January 25, 2011.

<sup>&</sup>lt;sup>6</sup> Intel 2009 Annual Report.

<sup>&</sup>lt;sup>7</sup> ARM 2009 Annual Report, converted to dollars using historical exchange rate on December 31, 2009.

innovations have their own characteristics and can depart from much of the conventional wisdom. Chapter 4 investigates the concept of architectural innovation and the role of modularity in enabling rapid change.

Finally, after understanding the nature of the challenge to Intel, the logical extension is to explore the managerial consequences. The stakes are frighteningly high for companies faced with technological transitions, and history is littered with examples of organizations that failed to navigate the challenge. Chapter 5 is about the survival of incumbent firms when faced with dramatic change, and focuses on the highly opposite stories of IBM and the Polaroid Corporation.

Part II is a retrospective of the computing industry since the advent of the PC. I begin with the PC because the arrival of the PC was the last major revolution in the computing industry, and is responsible for much of the industry structure that have today. Chapter 6 begins Part II with a narrow focus and covers technological trajectories and significant innovations in processor architecture and design. In Chapter 7 the focus broadens to the PC market and traces the drivers behind the PC's spectacular success and its growth into new market after new market. The PC's success has been absolute, and what began as a hobbyists' toy now dominates nearly all forms of computing.

In Chapter 8, I look at the semiconductor industry ecosystem as a whole. This chapter touches on a variety of topics, including the industry structure, the dominant cost-performance metrics of the PC era. I spend some time exploring the massive challenge presented by the Power Wall, the escalating costs associated with building a foundry, and how Intel's business model is running out of runway, even without the challenge from ARM. Finally, Chapter 8 ends with a discussion of ARM, System on a Chip designs, and the rise of independent foundries.

Part III is a prediction of future trends. Chapter 9 focuses on technology and the trajectories of computing and how they will depart from past trends. The chapter

highlights moves towards diverse product architectures, as opposed to the PC monoculture and the emergence of cloud computing as a significant force. In Chapter 10, I investigate the design constraints in two intensely important markets laid out in Chapter 9, namely smartphones and data centers. Finally in Chapter 11, I lay out the challenges Intel faces in the present and future computing ecosystem at large and why ARM is positioned to thrive.

### <u>Chapter 2 – Motivation and Terminology</u>

So why write a thesis on Intel? My fascination with processors dates back to my undergraduate education. (If we want to pinpoint when my interest with *computers* began, we would have to dig far deeper). My chosen Major was Electrical Engineering and within that my concentration was Computer Architecture. One of the benefits of my curriculum was that I emerged from college with an understanding of how a computer works from the operating system all the way down to the physics of a metal oxide transistor.

Bar none, my favorite classes were the two I took on processor design. In my junior year, my classmates and I recreated a PDP-8 processor using FPGAs. My senior year, the project was to turn a single-issue RISC core into a dual-issue superscalar processor. I was utterly taken with the simple elegance of RISC-based designs. At the time, it made a significant impression on me that something that I considered to be an example of sophisticated engineering was largely an afterthought in the general purpose computing market by the year 2000. It was my first lesson that there was more to processors than good engineering.

After I graduated college in 2001, I went to work for Sun Microsystems. I was part of a gigantic project designing an Ultra Sparc V mainframe. In particular, I was working on the chipset outside of the processor. It was my first introduction to ASICs and logic design that was tailored for specific tasks rather than running software. Unfortunately, my time at Sun coincided with the fallout from the dotcom bust, and I was introduced to another reality of life in high tech - layoffs.

In mid 2004 I joined a small fabless semiconductor company called Oasis Semiconductor, which made chips for ink-jet printers. Because Oasis was so small, I was able to see far more of the company than I was ever able to at Sun. At Oasis, I saw the power of System on a Chip designs, and the vibrancy. It was also my first

introduction to ARM processors. The realization that you could simply license a core rather than designing your own microcontroller was an epiphany for me. The elegant simplicity of ARM's business model struck me much in the same way that RISC processors did.

When I left oasis in 2010, I had an understanding that ARM was well established and would continue to do well. However, my studies at MIT have made me realize just how quickly dramatic change can sweep an industry. Violent change seems to come periodically, albeit with long periods of stability. This is similar to the evolutionary biology theory of punctuated equilibrium, where evolutionary change happens in short intense periods, followed by relative stability<sup>1</sup>. Intel and x86 had been synonymous with computing as long as I could remember. When I left college, I could not conceive of them ever being displaced. Yet as I reflected on my undergraduate and professional experience through the lens of what I have studied in the last year and a half, it has become apparent to me that we are in the midst of a change as dramatic as the introduction of the personal computer.

This thesis is my attempt to document and outline the scope of this change, and show why we are witnessing the end of the Intel Age.

### **Categorization and Terminology**

After completing my first draft of this thesis, it was pointed out to me that I use terms and phrases liberally that might be confusing to someone who does not have a background in semiconductors. Before I get too far into this thesis, I will attempt to provide some clarification for the reader. Let me begin with Semiconductors and the Semiconductor Industry. 'Semiconductors' is a shorthand way of referring to circuits, both analog and digital, integrated onto a single piece of silicon. I use 'Integrated Circuit' as a synonym for Semiconductor.

<sup>&</sup>lt;sup>1</sup> Wikipedia. < <u>http://en.wikipedia.org/wiki/Punctuated\_equilibrium</u> > Observed May 8, 2011.

Three other terms that I use interchangeably are Microprocessor, CPU (Central Processing Unit), and Processers. In the original commercial IBM mainframes, a processor was constituted of several individual components, but when Intel invented the microprocessor, the entirety of the processor was integrated onto a single piece of silicon. This is very much the norm now, so while it is technically incorrect, I use these terms interchangeably.

There is an important distinction to make between a chip and a processor. In my mind, a chip constitutes an integrated circuit, including its final packaging. Intel makes a variety of chips, which constitute nothing other than a processor. But chip and processor are not synonymous with each other. A chip can be any integrated circuit, and is not limited to processors. In addition, a processor can be integrated with other functional circuits on a single chip, which is known as a System on a Chip.

To confuse things further, I often frequently refer to processor cores. This is a term that has risen with era of multi-core designs or System on a Chip designs, where the processor is only a part of the overall design. A processor core is a stand-alone processor, but is intended to be integrated with other circuits, be it additional processor cores or other functional circuits. A multi-core chip is an integrated circuit that has two or more processors inside of it.

There are a handful of other terms that are used throughout this thesis. 'Die' is another way of referring to the physical silicon that a circuit lives on. A wafer is a circular piece of silicon that fabrication processes are built around. They vary in size, but the current standard is 300 mm in diameter. Once fabrication is complete, the dies are cut from the wafer for individual chips. After being cut, the chips are then packaged into their ceramic packaging that most people would recognize when they look at the circuit boards inside their computers.

Finally, I need to clarify what I mean by Embedded Computing. An embedded computer is a computer system that is generally crafted to a specific task, and is only

one part of an overall product rather than the product itself. While a consumer may shop for a 'computer,' they do not go to the mall with the intent to buy an 'embedded computer.' Instead, they purchase a cell phone, a car, a printer, a microwave, a router, a television, an e-book, or any other number of devices. But an embedded computer is a critical component of each and every one of these devices. Most consumers do not realize the ubiquity of embedded computers, but our daily lives are surrounded by a myriad of them.

# **PART I**

Academic Background

### Chapter 3 - Dynamics of Innovation

The next three chapters will discuss existing academic work that I found particularly helpful in my analysis of Intel and ARM. As we move to a discussion of the PC industry in the next section, the Abernathy-Utterback model helps explain the differences between the Intel of 1981 and the Intel of 2011, and Christensen Disruption helps illustrate how a relatively small company like ARM can be so dangerous. In Chapter 4, I explore the concepts of Architectural Innovation and modularity in *Design Rules*, which I feel are the appropriate lenses to examine what ARM is doing differently. Chapter 5 discusses the managerial challenges beyond selecting the correct technology and strategy to compete. In short, failing to make the requisite managerial changes in the face of technological discontinuities can mean the end of an organization.

### The Abernathy–Utterback Model and Dominant Design

The computer industry has a long history that is characterized by the rapid pace of change. It would be a daunting task to try to track and understand every single product or innovation introduced. Fortunately, there is an established body of academic work that can help us understand the inner dynamics of innovation in microprocessors.

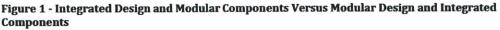

The first model to discuss is the Abernathy – Utterback model, which characterizes innovation in an industry as going through three successive phases: the fluid phase, the transitional phase, and finally the specific phase (Abernathy, Utterback 1978). As a starting point, it is helpful to map these three phases onto the traditional S-curve often associated with performance trajectories.

Figure 2 A hypothetical performance curve and the 3 phases of the Abernathy-Utterback Model

The fluid phase is characterized by the entry of both new and established firms into a market. The product category is likely new, and firms compete through product differentiation and radical innovation. A salient example would be the US automobile industry. From 1894 to 1918, 60 different firms entered the market, and the total number of firms peaked at 75 in 1923 (Utterback, 1994). This time period is populated by a number of radically different product designs, including electric cars, steam cars, as well as the internal combustion engine car.

In contrast, the transitional phase is often marked by consolidation within the industry. Using cars as the example again, between 1919 and 1941 a net of 44 firms left the automobile industry (Utterback, 1994). In addition to the declining number of competitors, the rate of product innovation typically drops off significantly. Instead, the industry begins to shift its focus from radical production innovation to *process* innovation and limits its R&D to a specific set of product features. As we can see, the shift from the fluid to the transitional phase is a dramatic change and begs the question of why does this occur?

Most often this change is attributable to the emergence of the dominant design. The dominant design is the result of all the product innovation that occurs in the fluid phase, and by definition "wins the allegiance of the marketplace." Once a dominant design begins to emerge, it becomes increasing difficult for firms to compete through product differentiation alone, as there are expectations in the marketplace of what the product should be. To use the automobile example again, it is clear that the dominant is design is the internal combustion engine car, and all the features that are standard on cars today (windshield wipers, electric starters, seatbelts, etc. ...) (Utterback, 1994)

It is important to note that the dominant design is not necessarily the product with the highest performance, or greatest amount of functionality. It is determined by a combination of technological and market forces, but can also be influenced by factors such as standards, regulation and government influence.

The final phase in the Abernathy-Utterback model is the specific phase, and in many ways extends the trends of the transitional phase. We see further consolidation, often resulting in an oligopoly of a handful of firms sharing the market. The dominant design is well defined, and the product category is heavily standardized. Whatever product innovation occurs is mostly incremental innovation, and even the manufacturing of products is fairly rigid, with well-defined supply chains and distribution channels.

It is also important to note that the Abernathy-Utterback model also recognizes that the different phases also have a strong influence on how an organization is structured. For example, entrepreneurship is common in the fluid phase, while project teams and task groups are more common in the transitional phase. Companies in the specific phase are characterized by highly structured and rigid organizational structures.

### **Christensen's Attack-From-Below Disruption**

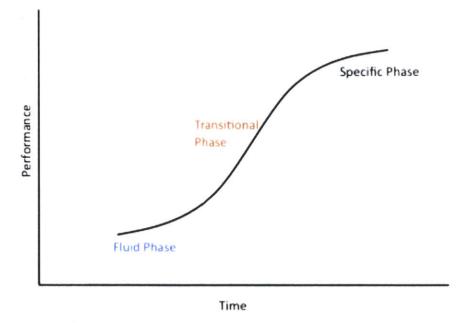

The stability of the specific phase leads directly into the next framework of interest, Clayton Christensen's attack-from-below disruptive innovation described in *The Innovator's Dilemma*. Christensen outlines a phenomenon where incumbent organizations, who are well into the specific phase, can be well run and make all the right decisions, yet still be overtaken in the market by lower performing technologies.

The concept of *disruption* is a complex and dynamic idea, but it begins with the recognition that technologies have performance trajectories. These trajectories are almost always upward over time, as products improve performance year after year. Some examples: with each generation of products hard drives add more storage, semiconductors add more transistors, printers print at faster page rates, bicycles get lighter and so on and so on.

Companies are rewarded for these trajectories when the market is segmented by performance. Increasing product performance allows companies to reach more lucrative segments of the market, and the market rewards companies that have performance advantages over their competitors. These trajectories and expectations of market behavior can embed themselves in an organization in a myriad of ways. Competitive strategies, relationships with the customers, organizational structure, market choices, and R&D capabilities are all optimized to race further ahead in the technological trajectory. Christensen uses the term *value-network* to describe this. The value-network drives companies to chase higher and higher product performance and makes it hard for a company to behave in any other way.

This sets the stage for one of the key ideas behind disruption: that the market's supply of performance can overshoot customers' demand. When a disruption occurs, a product attacks the incumbent firm "from below." That is to say that the

attacking product has lower performance on what has hitherto been the most important attribute, but still enough to satisfy the needs of a given segment. As both products meet the performance needs of a customer, the basis of competition begins to shift to other dimensions.

This leads to another central idea in a disruption: the attacking product often has superior performance in different dimension than the one along which the established technology trajectory was measured. This is a subtle concept, and is best demonstrated by the example of the hard drive industry used by Christensen. Within a generation of hard drives, the performance trajectory was for increasing storage space. Without fail, each successive market leader is disrupted by a product with smaller storage space. But each disruptive product is also *physically* smaller, allowing it to fit into smaller computers. The 14 inch hard drives were dominant in the mainframe market, but 8 inch hard drives were able to take the minicomputer market because while both technologies met the storage requires of minicomputers, the 8-inch technology offered a superior form-factor.

Time

Figure 3 - Attack from below disruption

Disruptions sometimes catch companies by surprise, but they can be difficult to avoid even if they are seen coming. The reason for this is the aforementioned valuenetwork, which establish overwhelming feedback mechanisms to keep companies focused along existing performance trajectories. It is for this reason that disruptions can be so dangerous to incumbent firms.

### Chapter 4 - Architecture, Modularity, and Innovation

### Architectural Innovation

While the previous chapter focused on dynamics of innovation, the discussion only differentiated between innovation in the product itself and innovation in the process to create the product. To be sure, innovation is a multi-dimensional phenomenon. In particular, this chapter will focus on innovations in the product *architecture* and the challenges faced by organizations when a product's architecture begins to change.

What is meant by architectural innovation? In the paper Architectural Innovation: The Reconfiguration of Existing Product Technologies and the Failure of Established Firms, Rebecca Henderson and Kim Clark define architectural innovation as "innovations that change the way in which the components of a product are linked together, while leaving the core design concepts untouched" (Henderson and Clark, 1990). As that quote alludes, in this framework innovation can occur along two dimensions: the aforementioned architectural innovations and innovations in the core concepts.

In broad terms, this leaves us four types of innovation, shown in table 1 which is a replication of Henderson and Clark's work.

|                           | Core Concepts<br>Reinforced | Core Concepts<br>Overturned |

|---------------------------|-----------------------------|-----------------------------|

| Architecture<br>Unchanged | Incremental Innovation      | Modular Innovation          |

| Architecture<br>Changed   | Architectural Innovation    | Radical Innovation          |

Table 1

Radical innovation and incremental innovation are compatible with the views of innovation discussed in the previous chapter. Radical innovation is diverse experimentation with all the aspects of a product, ultimately resulting in a dominant design. In the specific phase of an industry after a dominant design has been established the most common type of innovation is incremental innovation.

Modular Innovation is also a straightforward concept. Henderson and Clark use the example of replacing an analog phone with a digital one. The two phones are based on significantly different technologies, yet they both have keypads, antennas, speakers and microphones. In short, an analog phone and a digital phone are still both phones. A similar example would be the recent switch to HDTV. From a product standpoint, much of the technology has changed, yet the TVs all still have the same categories of components (signal inputs, a screen, speakers, a power cord, etc . . .).

Architectural innovation is more elusive concept. To recognize this type of innovation, we must realize that knowledge and expertise in a specific technology or component is altogether different than knowledge of how a technology or component interacts with other technologies and components. For example, a ceiling fan has many of the same components as a portable fan, such as an electric motor and the fan blades. Yet how these components are connected in very different ways, such as what the housing for the motor looks like. (Henderson and Clark, 1990).

The main thrust of Henderson and Clark's paper is that this type of architectural innovation presents a significant challenge to established firms. An established firm will likely have relevant expertise for the new architecture, but they may not understand how their knowledge is relevant. And in truth, their capabilities may also blind them to critical changes in the new architecture. RCA was an industry leader in transistors, radio circuits, and speakers, all critical parts of a transistor radio, yet it was Sony who was the one who achieved market dominance. (Henderson and Clark, 1990).

Why is this a challenge for established firms? In a market in the specific phase, where the dominant design has been established, firms must be highly efficient to survive. As the architecture of a product is stable, it can become "embedded" in the organization. For example, a designer of televisions will likely have a screen design team and a control electronics design team. This specialization is an effective way to execute incremental innovation, and contributes to deep domain knowledge.

The way these different groups interact is also likely to be standardized and optimized around the product design process for televisions. This creates "information filters" within an organization. The screen design team and control team will likely share information such as bandwidth and signaling requirements, but not share with each other information such as thermals or size and weight. These information filters are often necessary for high performing teams involved in incremental innovation, as it helps to block out unnecessary distractions. In summary, an organization can become like a mirror of the product it is designing, both in its physical organization and its methodologies.

However as architectural innovations change the way components are connected, they will likely be incompatible with these structures. The aforementioned information filters can cause teams to not fully understand new critical interactions in a new architecture. The internal processes that companies organizations rely on to create high performing products can become a liability in the face of a change in architecture. And even if an architectural change is fully understood by an incumbent, it still has a significant handicap as organizational structure is painful to uproot and rebuild while simultaneously trying to design a fundamentally different product.

#### **Design Rules & Modularity**

One potent form of architectural innovation is the introduction of modularity in a design. This is not to be confused with the aforementioned modular innovation. Modular innovation refers to innovation within the components of an already modular design. In *Design Rules*, Carliss Baldwin and Kim Clark discuss how introducing modularity into a design, thereby innovating in its architecture, can have profound effects on a products value and performance. These changes can be so powerful as to reshape the entire competitive landscape.

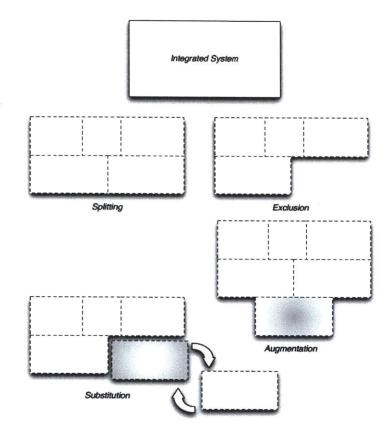

Modularity can be used to make a system more flexible and adaptable, and allow a market to rapidly find a system with the most value. Instead of a single monolithic design, a modular design consists of separate components whose interactions are defined by the systems "design rules." The core of *Design Rules* built around identification of six operators that designers could use to create and modify a modular system.

The first operator is *splitting*. Splitting is the first operation that must occur to create a modular system. It is the act of separating functions that were previously integrated together and having them both adhere to the same design rules which allows them to interact. The second operation of *substitution* is simply replacing one module with another. For example, a designer can replace a hard drive on computer with one with entirely different performance specifications without incurring significant economic costs. As long as the modules adhere to the same design. Without splitting and substitution, market choice can only act on the system as a whole.

The next operator is *augmentation*. Augmentation adds new modules to a system and introduces new functionality. *Exclusion* is the inversion of augmentation, and is the removal of a module from a system. Logically, the exclusion operator reduces

the functional range of a system. Again, all modules in a system must adhere to the same design rules. A simple example would be the Swiss-Army knife. Adding a new corkscrew or blade to the knife is augmentation, while removal of the can opener would be exclusion.

**Figure 4 Four of the Six Modular Operators**

*Inversion* can be used when several different modules end up creating solutions to the same problem repeatedly. Inversion creates a standard module to solve a problem. For example, it is common in software to create a data-structure called a linked list. Now most programming languages come with built in linked-list modules for programmers to use. The term inversion comes from the act of a designer bringing something from within a module up to a higher level for other modules to use. The final operator is *porting*, and in many ways is a logical extension *inversion*. While inversion brought solutions the inner workings of a module to a higher level, porting allows a module to be used in other systems. Using the words of Baldwin and Clark, porting lets a module "breaks free" of the system. Tesla Motors first designed its battery packs for use in the Tesla Roadster, but it ported its battery for use in the Daimler Smart ED car<sup>1</sup>.

These six operators can lead to a number of different outcomes dizzying in their variety. In complex systems, it is rare that a company understands fully how the final system will perform - let alone how a market will receive its product. A modular system allows designers to create a large number of different systems at a relatively low cost. This higher rate of "experimentation" results in a higher probability of a company will create a design that is of greater economic value.

Of particular relevance to this document is how introducing a modular design can lead to modular clusters, which is a term *Design Rules* uses to describe a type of industry structure. As a design shifts from an integrated monolithic design to a modular based design, design efforts become decentralized. This decentralization can evolve from separate design teams within a company to completely separate organizations. In this type of industry structure, the design of a system is spread over multiple independent firms, who sometimes are actively competing with each other.

Carliss Baldwin and Kim Clark explore this idea further in the working paper "Architectural Innovation and Dynamic Competition: The Smaller 'Footprint' Strategy." By leveraging modularity, companies can focus themselves on the portion of the design where they believe they can create the most value. Sun Microsystems focused their design efforts on the interface they believed to be the performance bottleneck, namely the interface between the CPU and memory and used standard

<sup>&</sup>lt;sup>1</sup> Autoblog.com. January 13, 2009 < <u>http://green.autoblog.com/2009/01/13/tesla-</u> <u>confirms-smart-ed-battery-supply-deal/</u> > Observed April 26, 2011.

modules for the rest of the design. With this approach they were able to outperform systems designed by Apollo Computer, who designed nearly all aspects of their product. Sun's smaller organizational "footprint" allowed them to not only build a better product, but also be much more capital efficient while doing so. (Baldwin and Clark, 2006) It is easy to see how modular clusters can create feedback loops and allows small, networked organizations to create powerful systems quickly and efficiently.

Modular clusters share a great deal of overlap with "business ecosystems." While a review of the relevant literature of business ecosystems is outside the scope of this thesis, a great discussion of the dynamics and powers of ecosystems can be found in the articles "Strategy as Ecology" (Iansiti and Levien, 2004) and "Predators and Prey: A New Ecology of Competition." (Moore, 1993)

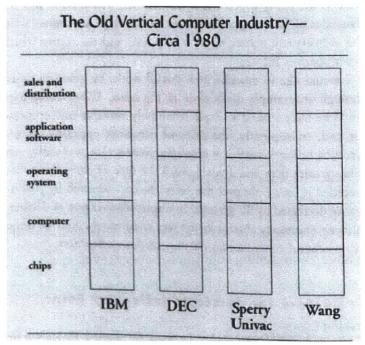

The authors of *Design Rules* posit that this evolution is beyond the control of an initial firm, and modular clusters can emerge despite the active efforts of the originating firm to maintain control of the design. The modern computer industry, itself a modular cluster, is a consequence of the decision by IBM to make System/360 a modular design. It is truly striking when engineering decisions made at the micro-architectural level can resonate to the point where a giant like IBM was knocked from their perch.

### Chapter 5 - Survival of the Incumbent

There is nothing so captivating as the fall of the giant. There is no shortage of analysis of why companies fail, and yet there is no widely accepted wisdom as to if established incumbents have long-term advantages or if they doomed to eventual failure. At this point, much of the work is anecdotal in scope, and only analyzes the success or failure of individual companies rather than developing a common framework. But if anything is clear, it is that companies can fail in a spectacular variety of ways.

In all of this analysis, by far the most common question is "Was failure avoidable?" Some of the academic work explored in chapters 3 and 4 would seem to suggest that certain types of challenges are particularly difficult for companies to overcome: architectural innovations may not be understood by the incumbent as their internal structure filters out critical information flow; Clayton Christensen's book suggest that an attack-from-below based disruption is nearly impossible for an incumbent to beat back. But perhaps we need to separate the question of a company's failure in a market from its overall failure.

The first example to investigate is perhaps the most famous turnaround story in business today: Lou Gerstner's miraculous turnaround of IBM in the 1990s. In the early 1990's, IBM's earnings were falling off a cliff. In 1991, IBM reported a loss of \$2.82 Billion, a dramatic swing from its earnings of over \$6 billion the previous year. In 1992 the losses nearly doubled to \$4.96 Billion. And in 1993, the losses ballooned to a staggering \$8.1 Billion.<sup>1</sup> While it dominated the mainframe market, IBM's market dominance was being attacked by mini-computers and PCs. At the same time, it was facing a critical technology change in its flagship product line, as

<sup>1</sup> IBM Archives: 1990s < <u>http://www-</u>

03.ibm.com/ibm/history/history/decade 1990.html > Observed on March 28, 2011.

mainframes needed tor transition from bipolar designs to CMOS based designs (Wladwasky-Berger, 2009)

A decades of avoiding layoffs, IBM cut 125,000 employees between the years of 1986 and 1993. It was at this point that the existing CEO John Akers resigned and John Gerstner was selected to be his replacement. Throughout the 1990s Gerstner transformed IBM from a hardware technology vendor to a broad-based solutions and services provider (Harreld et al., 2007). There is no shortage of books and articles on what IBM did to execute its turnaround, and Gerstner overhauled nearly aspect of the business, from its internal accounting principles, to its advertising strategies, to its product development. But it was the role of IBM's culture in its turnaround that is perhaps the most broadly applicable.

Lou Gerstner was certainly a capable executive before he came to IBM but perhaps the most notable qualification was the fact he was the first CEO to come from outside IBM. In fact, this was a critical requirement of the job. When searching for a new executive, the executive only considered candidates from outside the company as the board "felt strongly that what was wrong with IBM couldn't be fixed by an IBMer." (Garr, 1999, pg. 21) Why make this a requirement of the job? Perhaps it was a tacit acknowledgement by IBM's board that its problems ran deeper than poor strategic choices, and that the culture of the organization needed to change as well.

In his first year on the job, Gerstner had to struggle with "malicious obedience," where the existing senior and mid-level managers would agree to anything he suggested but would continue to operate in the manner they were used to. (Garr, 1999, pg. 71) To combat this, Gerstner made a series of moves and changes that sent a clear and undeniable signal to IBM that the culture had to change. He forced out senior managers who demonstrated that they were incapable of changing their ways. He wrested power from IBM's successful foreign subsidiaries, and ousted their senior executives who had long and successful track records. (Garr, 1999,

37

pg.72). Finally, he changed the bonus and incentive plan for the rank-and-file employees, all of which was Gerstner's way of saying things must change and that IBM would have standards accountability. (Garr, 1999, pg. 135)

Another potent example of the role of culture in an organizations ability to adapt is the story of Polaroid. Unlike IBM, Polaroid was unable to overcome its challenges and filed for bankruptcy in October of 2001.<sup>2</sup> Polaroid's failure is often attributed to its inability to transition from analog to digital photography. What is tragic about Polaroid is that they were an early technology leader in digital photography. Their Electronic Imaging Group was founded in 1981 and in 1992 they had a working prototype of their PDC-2000 digital camera. However, the belief that Polaroid was a film company was deeply ingrained in the management at Polaroid, and a product that did not conform to the razor & blades business model, such as a digital camera, struggled for executive support. As a result, the PDC-2000 was not released until 1996. What is remarkable is that even with the long delay, the PDC-2000 was still a best in class digital camera, but at that point there were over 40 competitors in the market and it failed to take off. (Tripsas and Gavetti, 2000)

So why did Polaroid fail while IBM was able reverse its fortunes? There are numerous differences between these companies, but perhaps it was the pace of failure that is the critical difference. That is to say, IBM's earnings had plummeted dramatically in the span of two years, which perhaps engendered a sense of crisis that may have been lacking at Polaroid, who's failure played out over a decade. The old anecdote of the frog in a boiling pot of water is an apt metaphor for this.

Finally, we must consider if failure of an organization is inevitable. The creation of new firms and the failure of existing companies is an established tenet of business today. With each challenge a company faces, it must ask if it could be the one that

<sup>&</sup>lt;sup>2</sup> CNN Money, "Polaroid files Chapter 11" <

http://money.cnn.com/2001/10/12/companies/polaroid/ > Observed on March 29, 2011.

puts them out of business. In *Organizational Ecology*, Michael Hannan and John Freeman use biological theory to explore the evolution of organizations. One consequence of their work is the realization that just like in biological populations, the death of an organization is highly correlated with its age. (Hannan and Freeman, 1989, pg. 245) There is no fountain of youth for companies. While we cannot say with any certainty which organizations will survive and which will fail, it is clear that giants like Polaroid, IBM, or even Intel must take any challenge seriously.

# **PART II**

The Past

# Chapter 6 - A Brief History of Innovation and the PC

In this second part, I begin with the IBM 5150, the machine that signified the arrival of the personal computer. Why start with the PC? In short, the advent of the PC was the last major revolution in the computing industry, and is responsible for the industry ecosystem we currently have. The revolution we are witnessing today in many ways mirrors what started in 1981. As this is a thesis about Intel, this chapter will focus in on technological trajectories and innovation in processors. In Chapter 7, I will trace the PC onslaught as it overtakes higher performing machines with frighteningly regularity, and how much of that growth is due to innovations and advances in processor performance. Chapter 8 will outline the challenges Intel faces, and the Herculean efforts it must undertake to keep Moore's Law chugging along. It will then pivot to ARM and System on a Chip semiconductor design, which sets up the final third of this thesis.

# The IBM 5150

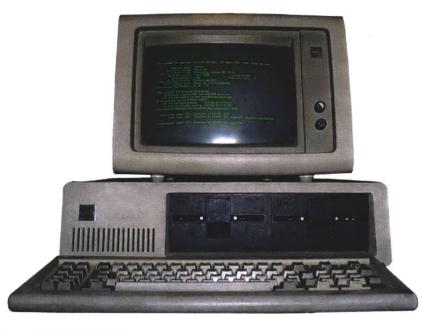

While technically not the first Personal Computer, the release of the IBM 5150 in 1981 is widely recognized as the event that kick-started the PC industry<sup>1</sup>. In a move highly atypical of IBM, the 5150 used technology developed by outside companies, shipping with the 8086 processor designed by Intel and an operating system developed by Microsoft. In a strange twist of fate, Intel may owe its place the PC business to Motorola. Before the 5150, IBM had a favored internal project that was stumbling because Motorola was late in delivering the processor. In order to satisfy a corporate deal with Sears, IBM created the 5150 as a stopgap and chose Intel to supply the processor. (Jackson, 1997, pg. 203)

The 5150 project was a crash project through and through. To save time and money, the IBM design team elected to use off the shelf parts and software rather than

<u>03.ibm.com/ibm/history/history/year 1981.html</u> > Observed on March 30, 2011.

<sup>&</sup>lt;sup>1</sup> IBM Archives: 1981. < <u>http://www-</u>

develop internally, as evidenced by the inclusion of Intel and Microsoft. ("Getting Personal", Economist 2006) In turn, the Intel 8086 chip IBM selected was itself a stopgap for Intel's iAPX432, which was a much delayed and troubled project. And Microsoft purchased MS-DOS from a third company, where it was originally named Q DOS, which stands for Quick and Dirty Operating System. (Jackson, 1997, pg 162, 205) Finally, IBM elected to make the specifications open to facilitate the development of outside software. IBM had modest sales goals for the 5150, and wanted to keep the development as low cost as possible.

# Figure 5 - The IBM 5150<sup>2</sup>

IBM's decision to build an open architecture for the PC and its "Big Blue" reputation in the market turned out to be a fateful pairing. Although there were many firms trying to grab a piece of the nascent PC market, IBM's entry was a legitimization of a market that up until that point many people considered to be merely the province of hobbyists. The founders of Compaq recognized that whenever IBM entered a market, whatever it released became the standard. (Wilcox, 1998) As the 5150's architecture was open, Compaq could simply buy the same off the shelf parts and

<sup>&</sup>lt;sup>2</sup> Image Source: Self-reliance-works.com < <u>http://www.self-reliance-works.com/wp-content/uploads/2011/01/IBM-5150-PC.jpg</u> > Observed May 8, 2011.

software and was able to create a software compatible machine within a year. After this, the history of the PC one of a steady stream of IBM PC clones and diminishing IBM fortunes. With a single product release, IBM had both defined the modern PC and gave away the keys to the kingdom.

## The Importance of Instruction Set Architectures

While much of the literature focuses on the significance of IBM outsourcing the operating system of the 5150 to Microsoft, IBM's decision to use Intel's 8086 processor was equally important. In short, it allowed Intel to define the Instruction Set Architecture (ISA) of the PC market. The ISA is a critical element of computer architecture. It defines the interface between hardware and software. An ISA defines a set of instructions and operations that a processor can interpret and execute. All software is a string of these instructions, which when executed in order create higher-level functions.

IBM first established the importance of the ISA with its System/360 mainframe. (Lee, 2011) Without a stable ISA, software is not guaranteed to continue operating correctly as it transitions from one generation of products to the next. And as the body of software written grows for a particular product, so do the costs of switching to a new product. IBM realized that a lack of software compatibility drove up costs both for itself and for its customers, making it harder to sell them new products. This is tremendously significant, and the System/360 represents the first time that software was not exclusively co-specialized with the hardware. The concept of backwards-compatibility had arrived.

The ISA frees up processor designers to introduce whatever innovations they like without fear of affecting software compatibility, as long as their innovations don't modify the ISA. An ISA is important because decouples the hardware-software interface from the implantation. It is a contract between hardware and software that all parties must adhere to.

43

When IBM selected Intel to supply the processor for the 5150, they didn't ask them to design an implementation of an IBM's ISA. They selected a processor that was an implementation of Intel's own x86 ISA. An ISA is not something chosen lightly, as it only becomes harder to make changes to it with time. But given the crash nature of the 5150, IBM's actions are understandable. But this simple choice codified the x86 ISA, which IBM neither owned nor controlled, into the standard architecture of PCs.

### **RISC Versus CISC**

Although an ISA is rarely changed, they can be discarded if the benefits outweigh the costs. While IBM dealt them an extraordinarily strong hand, Intel's dominance was hardly *fait accompli*. One of the significant challenges the x86 faced was from processors with a RISC-based ISA. RISC stands for Reduced Instruction Set Computing, and it represents a school of thought and design that was a significant departure from the existing practices. By contrast, the x86 ISA is often referred to as a CISC (Complex Instruction Set Computing) based design.

The key difference between RISC and CISC is the number of instructions included in the ISA as well as complexity of the instructions themselves. When CISC processors were first designed, the amount of memory space software occupied was critical. (Lee, 2011) By expanding the number of supported instructions, software could be written with fewer instructions. A good analogy is the different between the Chinese written-language, where a single character represents a syllable, versus the Latin alphabet, where multiple characters must be used to construct a syllable. If paper is extraordinarily valuable, writing in Chinese is preferable, as it will require less paper. CISC also allowed instructions to be variable in length (i.e. 4 bytes versus 10 bytes), which allowed the software instructions to not take up any more room than was necessary. However, as memories became larger and larger, the memory footprint of software became less and less of a concern and instruction throughput, how many instructions a processor can process in a second, became an industry focus. RISC is very much aligned with this shift. The design philosophy of RISC was to reduce and standardize the instructions in the ISA. For example, instead of a single instruction that can read data from memory, add two numbers, and write the result back to memory, a RISC processor would require a load instruction, an add instruction, and finally a write instruction. But by reducing the number of instructions supported, the circuits needed to decode the instruction became simpler. And by standardizing instructions, such as disallowing variable length instructions, designers can introduce innovations such as pipelines. Processor pipelines are analogous to assembly lines, and allow multiple instructions to be operated on simultaneously. In short, RISC designers believe a simpler ISA will enable a faster processor.

Intel faced many challenges from RISC based designs: Sun's SPARC chips, Hewlett-Packard's PA-RISC series, Motorola's PowerPC, etc ... The RISC versus CISC debate also played out in academia, with much of the literature touted the performance advantages of RISC based designs. In an industry driven by performance, this would seem to be a decisive blow to Intel.

So why do all PCs today ship with Intel processors instead of PowerPC chips? While there was much academic debate about the benefits of RISC versus CISC, it ultimately came down to a business decision. Microsoft and Intel were always careful to ensure backwards software compatibility, both in the ISA and the operating system. There was just too much industry investment in the x86 based PC to justify switching. (Lee, 2011)

In fact, Intel was able to close much of the performance gap through mimicking many of the innovations first introduced in RISC based designs. For example, without changing the x86 instruction set Intel broke up the long complicated CISC based instructions into simpler micro-ops, allowing them to pipeline their

45

processors. By the late 1990's, x86 chips were meeting or beating the performance of many of their RISC counterparts. (Mann, 1997) (Lee, 2011)

## The Self-Fulfilling Prophecy of Moore's Law

Intel's pursuit of higher performance did not stop after its victory over RISC. Gordon Moore, an Intel co-founder, famously recognized that the number of transistors in an integrated circuit was doubling roughly every two years (Moore, 1965). This observation is now referred to as Moore's Law. While Moore's Law was originally in reference to the number of transistors on a chip, it soon became interpreted as predicting that processor *performance* will double. This helped stoke a tremendous amount of focus on increasing chip performance and became something of a self-fulfilling prophecy (Lee, 2011).

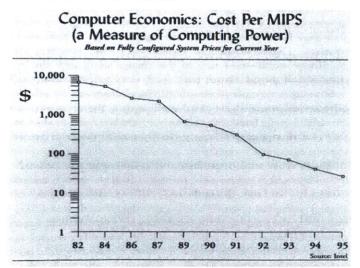

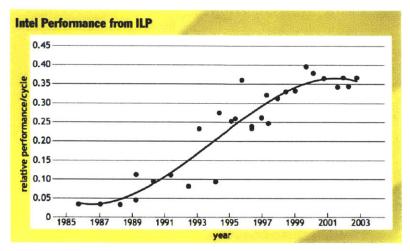

In the hunt for higher and higher performance, Intel introduced many innovations that, while they increased performance, achieved only declining incremental benefits. In turn these changes lead to highly complex, power-hungry designs. For example, the initial RISC pipelines were only 5 or 6 stages long, but Intel soon reached pipeline depths of 15 or 20 stages (Lee, 2011). This complexity comes with a cost.

Using the pipeline example again, processors sometimes have to throw away the instructions they are processing and start over. A longer pipeline means more instructions queued up in their pipeline, and hence a higher penalty if the pipeline needs to be flushed. As pipeline flushes have a higher penalty, designers will add more logic to try to detect and avoid the hazards that trigger them. This leads to bigger and bigger circuits, which consume more and more power all for incremental performance gains. But the market was demonstrating an appetite for higher performance, and this lead to tremendous pressure on engineers to keep the performance gains coming (Lee, 2011).

Around 2003, Intel hit what is known in engineering circles as the 'power-wall'. The power-wall refers to the amount of heat that a processor core can dissipate. Higher performance means more heat that must be dissipated to maintain the operating performance of the chips. As silicon circuits get hotter, their performance begins to degrade dramatically. As Intel was running out of ways to increase processor performance, it elected to begin designing chips with multiple processor cores on them. With each core below the power-wall, Intel found they could keep increasing the theoretical performance of their products (Lee, 2011) (Patterson, 2010)

Multi-core chips are predicated on the ability of software to take advantage of the parallel processing capacity. Theoretically, software should be able to break up tasks into operations that can be conducted simultaneously on different processor cores. However, effective use of parallelism has proved notoriously difficult for compilers and software writers. Parallel computing has been around for nearly 50 years, and there are countless also-rans who tried to capitalize on parallel processing. There are only a handful of success stories, where the applications map very well to parallel processing, such as the rendering of computer animated movies or weather simulations. Yet, as a whole it would seem that software developers are not prepared. (Patterson, 2010) Moore's Law marches on, but Intel may have finally surpassed software's ability to use the additional performance.

# Chapter 7 - A PC on Every Desk

## The Beginnings of the PC Revolution

While the last chapter points to the IBM 5150 as the advent of the modern PC, the roots of personal computers go back to the 1960s. On December 9<sup>th</sup>, 1968 Douglas Engelbart gave a demonstration of a project that is now known as "The Mother of All Demos."<sup>1</sup> In this demonstration, Engelbart presented a vision of what a personal computer could look like, and marked the debut of the mouse, "what you see is what you get" text editing, hyperlinks, text and graphics on the same screen, and even a program that looks remarkably like PowerPoint.

Though much of what Engelbart demonstrated looks very familiar to a modern PC user, it was radically different from what computing looked like in the 1970s. Mainframes, what IBM called "Big Iron", typically did not have interactive interfaces and would take up entire rooms. Minicomputers, such as the famous DEC PDP-8, reduced the size of machines considerably, but were still primarily used for computationally intense work, not for day-to-day office work. The closest product to Engelbart's vision would be the standalone word processors, such as the Wang 1200, but even they did not encompass the breadth of functionality envisioned in Engelbart's demonstration.

But work continued apace on the personal computer. The late 1970s is littered with kit computers, such as the Altair computer kit and the RadioShack TRS-80, which were popular with technicians and hobbyists. Apple was founded in this tradition, with Steve Wozniak and Steve Jobs building computers in and selling them out of their garage (Jackson, 1997, pg. 202).

<sup>&</sup>lt;sup>1</sup> Tweney, Dylan "Dec. 9, 1968: The Mother of All Demos." *Wired*. December 9, 2008. < <u>http://www.wired.com/science/discoveries/news/2008/12/dayintech 1209</u> >

Observed on April 4, 2011.

When IBM tiptoed into personal computers, it initially targeted sales into the consumer market. As IBM's strength otherwise lay in the B2B market, the 5150 personal computer was distributed through a deal with Sears (Jackson, 1997, pg 203). Yet precisely because IBM was known for its business products, the IBM PC found an enthusiastic market in office sales. After a sluggish start, IBM's sales took off in 1982 (Reimer, 2005).

Though PCs first found their footing in the business world, the low price point allowed a rapid expansion into the home market. IBM made a several attempts to regain control of the IBM-PC market, such as their release of the PC jr in 1984<sup>2</sup>, but by that point the PC market was clearly in control of the clone manufacturers. Much of this success was due to the popular Lotus 1-2-3 application. Compaq realized the importance of the office market, and made a strategic partnership with Lotus 1-2-3 creator Mitch Kapor to sell their machines with the famous spreadsheet program (Wilcox, 1998). By 1986, IBM and the various clone manufacturers who conformed to the X86 ISA collectively crossed the 50% market share threshold (over proprietary alternatives offered by Commodore, Amiga, and Apple) and never looked back. (Reimer, 2005)

#### The PC Onslaught

Dating back to the founding of Microsoft, Bill Gates and Paul Allen had a vision of computers becoming ubiquitous, perhaps best epitomized by their slogan "A PC on every desk."<sup>3</sup> Much of the growth PCs experienced in the early days was in this spirit, with computers finding their way into contexts and environments where computers had never been used before. Yet the PC also proved to be something of an invasive species, displacing industry incumbents such as IBM itself (which later

<sup>&</sup>lt;sup>2</sup> IBM Archives: 1980s < <u>http://www-</u>

<sup>&</sup>lt;u>03.ibm.com/ibm/history/history/decade\_1980.html</u> > Observed on March 28, 2011. <sup>3</sup> Microsoft's Tradition of Innovation <

http://www.microsoft.com/about/companyinformation/ourbusinesses/profile.ms px > Observed on April 4, 2011.

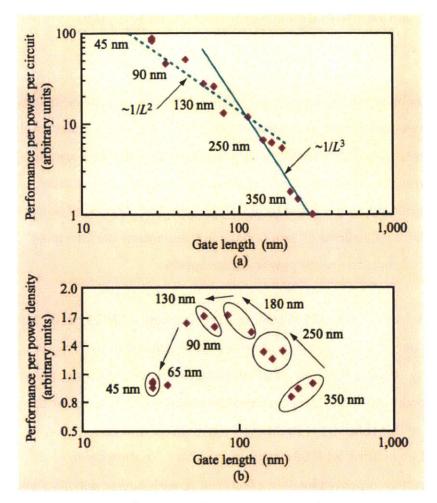

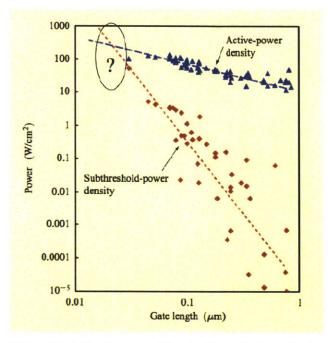

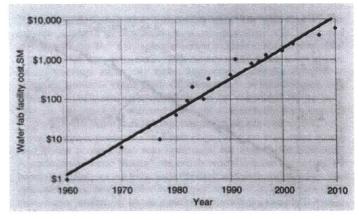

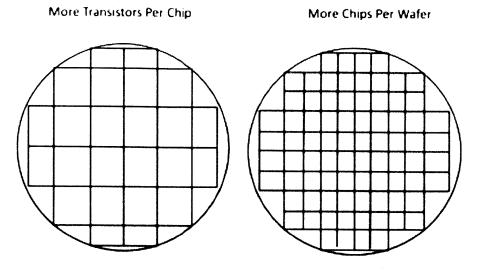

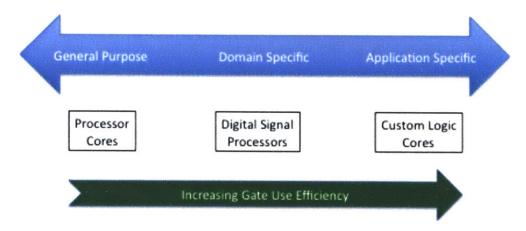

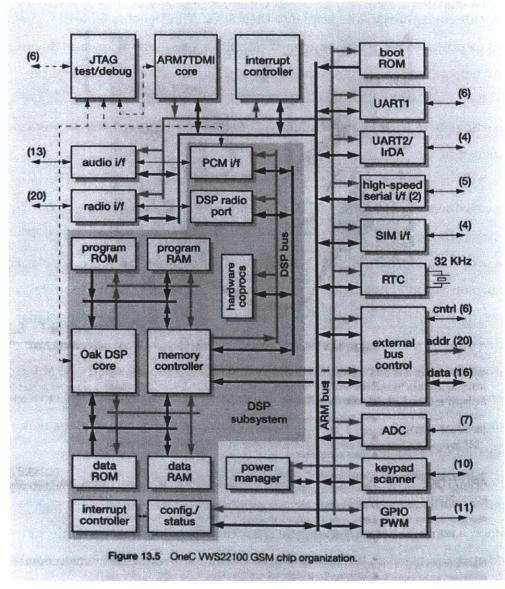

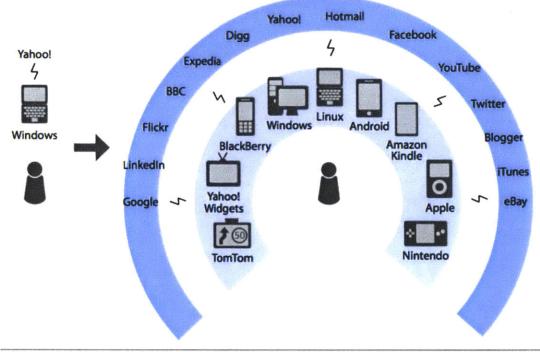

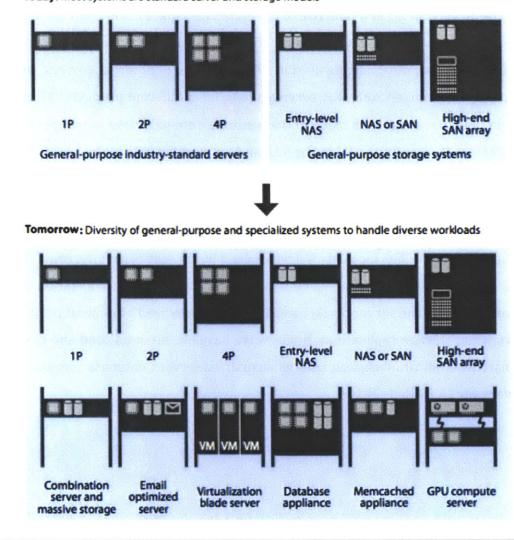

diverted this business to Lenovo), Digital Equipment Company (DEC), and Wang Laboratories. While these companies were correct that the initial personal computer could not compete with word processors, minicomputers and mainframes, they failed to recognize the rapidly growing threat. PCs were benefited from Moore's law more than any other device, and it wasn't long before the PC was in the same performance class as its beefier cousins. (Haynes, 1994)