#### A DIGITAL CONTROLLER FOR A UNITY POWER FACTOR CONVERTER

by

#### AHMED MITWALLI

#### S.B., ELECTRICAL ENGINEERING AND COMPUTER SCIENCE MASSACHUSETTS INSTITUTE OF TECHNOLOGY (June 1991)

Submitted to the Department of Electrical Engineering and Computer Science in Partial Fulfillment of the Requirements for the Degree of

MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

January 1993

©Ahmed Mitwalli 1993 All rights reserved

The author hereby grants to MIT permission to reproduce and to distribute publicly copies of this thesis document in whole or in part.

| Signature of Author |                                                       |                         |

|---------------------|-------------------------------------------------------|-------------------------|

| Ū                   | <sup>2</sup> Department of Electrical Engineering and | <b>Computer Science</b> |

|                     |                                                       | January 15, 1993        |

| Certified by |     |                        |

|--------------|-----|------------------------|

| •            | • • |                        |

|              |     | <br>George C. Verghese |

George C. Verghese Professor of Electrical Engineering Thesis Supervisor

| Certified | by | <br> | <br> |        |   |      |

|-----------|----|------|------|--------|---|------|

|           |    |      |      | Storen | P | Look |

Assistant Professor of Electrical Engineering Thesis Supervisor

| Accepted by                             |     |               | 1. 1.C.M   |             |             |           |

|-----------------------------------------|-----|---------------|------------|-------------|-------------|-----------|

| - • • • • • • • • • • • • • • • • • • • | 7/1 | $\mathcal{O}$ |            |             | Campbell    | L. Searle |

| MASSACHUSETTS INSTITUTE                 | Cha | airman, l     | Department | Committee o | on Graduate | Students  |

CHIVES

## A Digital Controller for a Unity Power Factor Converter

by

## Ahmed Mitwalli

Submitted to the Department of Electrical Engineering and Computer Science on January 15, 1993, in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering

### Abstract

Digital control is rare in the area of power converters due mainly to cost considerations. As operating requirements of power supplies become more stringent, however, their control poses difficult problems better dealt with using digital rather than analog control. With the falling prices of microcontrollers and the increase in their processing power, microprocessor-based controllers for power converters should soon become practical. In this thesis, a digital controller for a Unity Power Factor AC-DC converter is designed, based on a linear large-signal model of the power supply. A hardware implementation of the design is presented and analyzed, along with simulations of the closed-loop system. Issues in digital control of power systems, such as quantization effects and fixed-point representation of system parameters, are examined in the context of this system. An adaptive controller is then designed and implemented using the same system. The experimental results are then compared with the simulations and used to evaluate the implementation.

Thesis Supervisor: George C. Verghese Title: Professor of Electrical Engineering

Thesis Supervisor: Steven B. Leeb Title: Assistant Professor of Electrical Engineering To my wonderful parents, whose love and support have turned out to be my greatest assets. I owe you more than I can ever repay.

To my beautiful sister, Dalia, who has always stood by my side. I have never met anyone who is more unselfish.

To my loving brother, Mohammed. May you have a bright and successful future. God bless them all.

#### Acknowledgements

I had an incredibly stimulating and rewarding experience working on my Master's thesis, and I have many people to thank for it. Mainly, I had the opportunity to work with two exceptional supervisors.

Professor Verghese has to be one of the most brilliant human beings I have ever met. The knowledge and insights I have gained from interacting with him are invaluable. His excellence as a person also extends far beyond his academic achievements and intellectual abilities, and he has provided me with a role model in many aspects of life. Thank you George.

Professor Steve Leeb has the rare combination of a deep understanding of theoretical issues and knowledge of practical matters. He worked closely with me on this project, and his contributions are in every part of it. He was there on the long nights of work, always ready to help, and never out of answers. I had the great opportunity to work with him as a fellow student and friend and then as a supervising faculty member. Thank you Steve.

Professor Aleksandar Stankovic, now at Northeastern University, was yet another exceptional person I had the privilege of working with. It is hard to imagine my last year and a half without his help and encouragement (on and off the basketball court). His intelligence and good nature are of a rare magnitude.

Everyone in LEES deserves some thanks. The friendliness of the place made my experience the best it could have been. Special thanks to Derek, Kamakshi, Haatchitaba, John, Dave, Brett, Jeff, Mary, and of course, Vivian.

Thanks to family and friends. Without my parents, my sister Dalia, and my brother Mohammed, and their constant support from so far away, none of this would have been possible. I also thank my roommates and friends with all my heart.

I would like to acknowledge and thank Digital Equipment Corporation for supporting the project, and in particular Dr. Joseph Thottuvelil, who was a great help and a pleasure to work with.

4

# Contents

| 1 | Int | oduction and Background                      | 12         |  |  |  |  |  |  |

|---|-----|----------------------------------------------|------------|--|--|--|--|--|--|

|   | 1.1 | Objectives                                   | 12         |  |  |  |  |  |  |

|   | 1.2 | The Power Factor                             |            |  |  |  |  |  |  |

|   | 1.3 | High Power Factor AC-DC Converters           | 14         |  |  |  |  |  |  |

|   | 1.4 | Modeling of UPF Power Supplies               | 16         |  |  |  |  |  |  |

|   | 1.5 | Digital Control                              | 18         |  |  |  |  |  |  |

|   | 1.6 | Motivation                                   | 19         |  |  |  |  |  |  |

|   | 1.7 | Thesis Organization                          | 21         |  |  |  |  |  |  |

| 2 | Mo  | deling and Control Design                    | 23         |  |  |  |  |  |  |

|   | 2.1 | Dynamic Models of the UPF                    | 23         |  |  |  |  |  |  |

|   |     | 2.1.1 The $T_s$ -Averaged Model              | 23         |  |  |  |  |  |  |

|   |     | 2.1.2 The $T_L$ -Averaged Model              | 24         |  |  |  |  |  |  |

|   |     | 2.1.3 Sampled Data Models                    | 25         |  |  |  |  |  |  |

|   | 2.2 | Controller Design                            | 27         |  |  |  |  |  |  |

|   |     | 2.2.1 PI Control                             | 27         |  |  |  |  |  |  |

|   |     | 2.2.2 Deadbeat Control                       | 32         |  |  |  |  |  |  |

|   |     | 2.2.3 Additional Design Features             | 33         |  |  |  |  |  |  |

|   |     | 2.2.4 Integrator Windup and Startup Behavior | <b>3</b> 6 |  |  |  |  |  |  |

|   |     | 2.2.5 Overall Design                         | 37         |  |  |  |  |  |  |

| 3 | Imp | lementation                                  | 40         |  |  |  |  |  |  |

|   | 3.1 | Hardware Implementation                      | 40         |  |  |  |  |  |  |

|   |     | 3.1.1         | Digital Voltage-Loop Controller                       | 40         |

|---|-----|---------------|-------------------------------------------------------|------------|

|   |     | 3.1.2         | D/A Conversion                                        | 45         |

|   |     | 3.1.3         | Analog Current-Loop Controller                        | 45         |

|   |     | 3.1.4         | A/D Resolution Enhancement                            | 47         |

|   |     | 3.1.5         | A/D Anti-Aliasing Filter                              | 48         |

|   |     | 3.1.6         | The Complete System                                   | 50         |

|   | 3.2 | Imple         | mentation of Control Algorithm in Software            | 50         |

|   |     | 3.2.1         | Timing                                                | 52         |

|   |     | 3.2.2         | Scaling and Digital Parameters                        | 53         |

|   |     | 3.2.3         | Other Controller Characteristics                      | 57         |

|   |     | 3.2.4         | Overall Software Implementation                       | 64         |

| 4 | Des | sign an       | d Implementation of Adaptive Control                  | 65         |

| - | 4.1 | -             |                                                       | 65         |

|   | 4.2 |               | and Implementation                                    | . 05<br>66 |

|   | 1.2 | 4.2.1         |                                                       | 66         |

|   |     | 4.2.2         | Gain Tuning and Testing                               | 71         |

|   |     |               |                                                       |            |

| 5 | Exp | perime        | ntal Results                                          | 73         |

|   | 5.1 | Exper         | imental Setup                                         | 73         |

|   | 5.2 | Syster        | n Simulation and Results                              | 74         |

|   |     | <b>5.2.</b> 1 | Simulation                                            | 74         |

|   |     | 5.2.2         | Digital Controller Without Adaptive Control           | 75         |

|   |     | 5.2.3         | Adaptive Control                                      | 78         |

|   |     | 5.2.4         | Overall Results                                       | 80         |

| 6 | Mo  | re Con        | npact Implementations                                 | 85         |

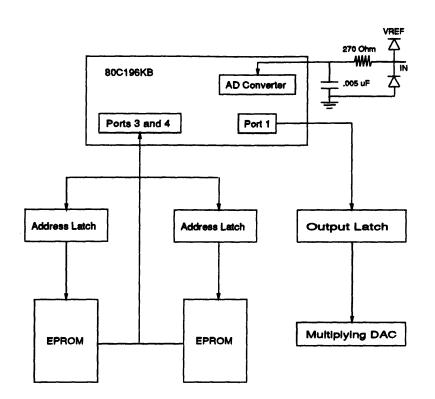

|   | 6.1 | Microp        | processor Implementation Without the Evaluation Board | 85         |

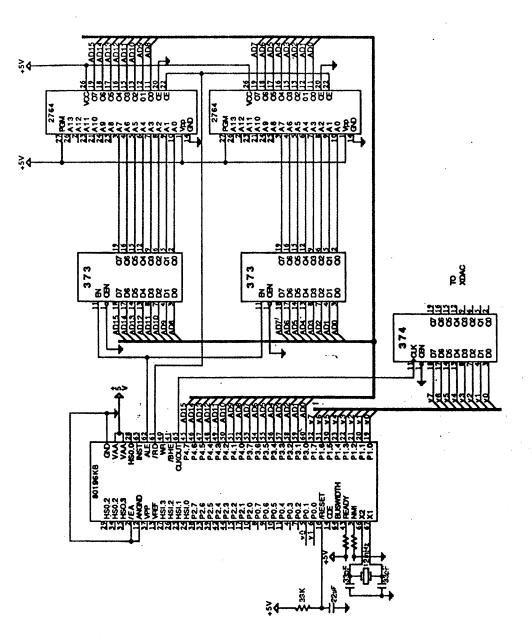

|   |     | 6.1.1         | Memory Interfacing                                    | 86         |

|   |     | 6.1.2         | A/D Interfacing                                       | 86         |

|   |     | 6.1.3         | Experimental Results and Conclusions                  | 87         |

|   | 6.2 VLSI Implementation                                             | 88  |

|---|---------------------------------------------------------------------|-----|

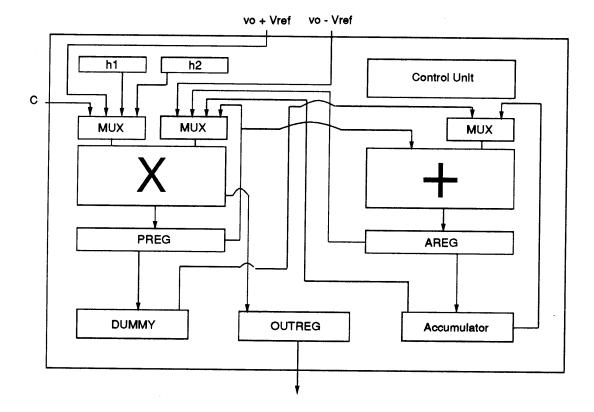

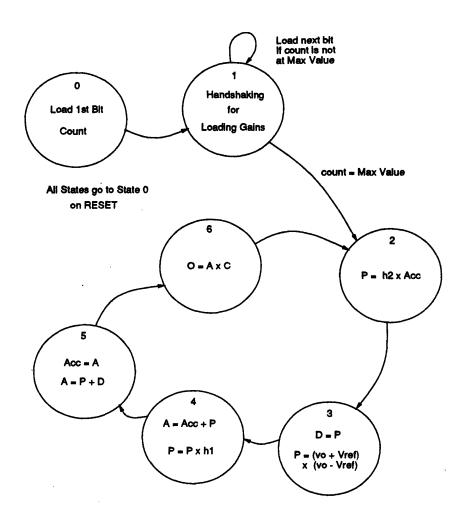

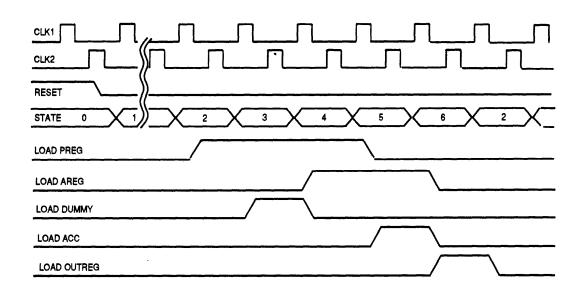

|   | 6.2.1 Overall System Layout                                         | 89  |

|   | 6.2.2 Control and Data Path                                         | 89  |

| 7 | Conclusions and Future Work                                         | 94  |

| A | Derivation of Closed-Loop Transfer Function in the z-Domain         | 97  |

| в | Comparison of Large- and Small-Signal Models                        | 101 |

| С | Passive Filters for Anti-Aliasing and Ripple Frequency Selection    | 105 |

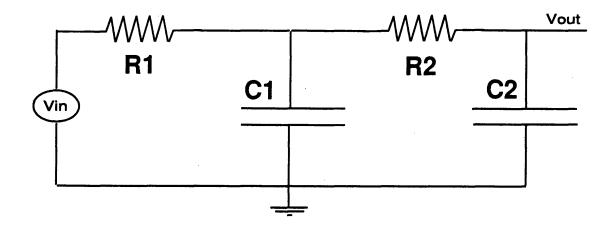

|   | C.1 Anti-Aliasing Filter                                            | 105 |

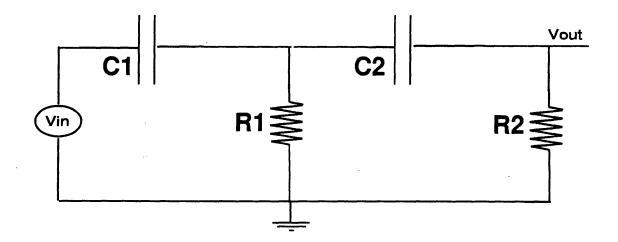

|   | C.2 Bandpass Filter for the 120Hz Ripple                            | 106 |

| D | Simulation Code                                                     | 114 |

|   | D.1 Simulations of the Discrete-Time System                         | 114 |

|   | D.2 Simulation of Digital System and Multiple Features              | 117 |

|   | D.3 Simulations of $T_s$ -Model for Capacitance Estimation          | 123 |

| E | Circuit Schematics                                                  | 128 |

| F | Controller C Code                                                   | 136 |

| G | Schematic and Timing Diagrams for Compact Microprocessor Sys        | 5-  |

|   | tem                                                                 | 147 |

| н | Transistor Level Schematics of Multiplier Cell and Block Descriptio | n   |

|   | of Multiplier Block                                                 | 150 |

|   |                                                                     |     |

|   |                                                                     |     |

# List of Figures

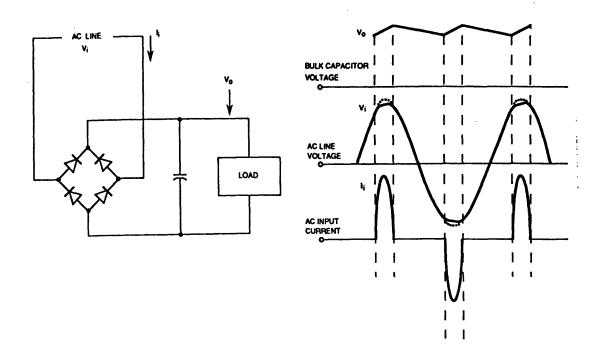

| 1-1 | Voltage and current in conventional capacitor-filtered rectifiers.[15] | 15 |

|-----|------------------------------------------------------------------------|----|

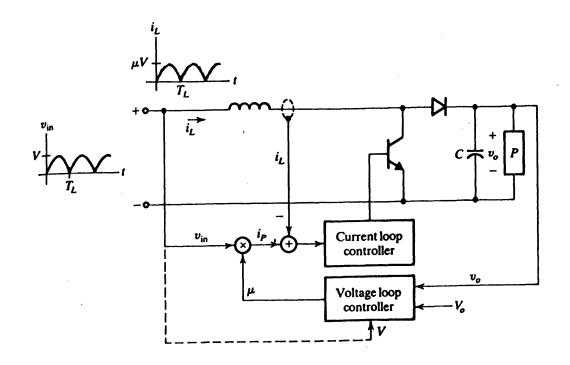

| 1-2 | A high power factor ac/dc switching preregulator [3]                   | 17 |

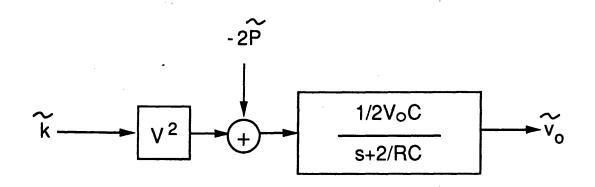

| 1-3 | Block diagram for a linearized model of a UPF                          | 17 |

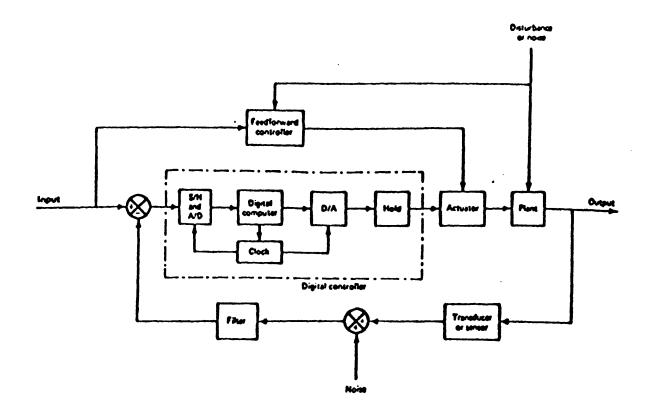

| 1-4 | A typical digital controller [6]                                       | 20 |

| 2-1 | The $T_L$ -based sampled-data-model.                                   | 26 |

| 2-2 | A discrete-time PI controller [3]                                      | 28 |

| 2-3 | Response of the closed-loop system with proportional control           | 30 |

| 2-4 | Response of the closed loop system with PI control — system poles at   |    |

|     | .5                                                                     | 31 |

| 2-5 | Deadbeat response to load disturbance                                  | 32 |

| 2-6 | A self-tuning regulator [10].                                          | 34 |

| 2-7 | Regulator with antiwindup                                              | 36 |

| 2-8 | Startup with integrator windup and no soft-start                       | 37 |

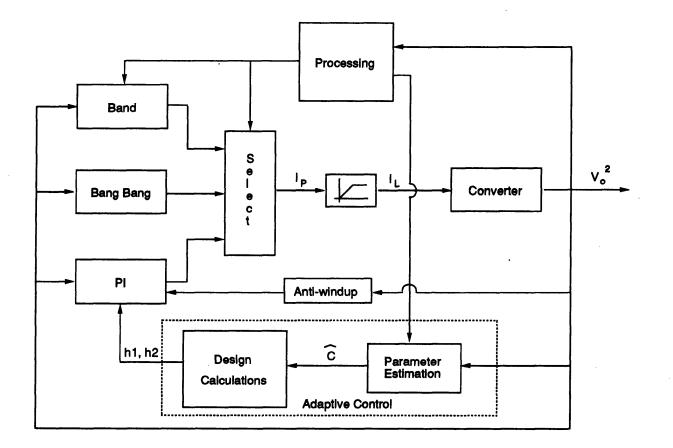

| 2-9 | Overall controller design                                              | 38 |

| 3-1 | The digital development system                                         | 42 |

| 3-2 | The 80C196 interrupt structure [13]                                    | 43 |

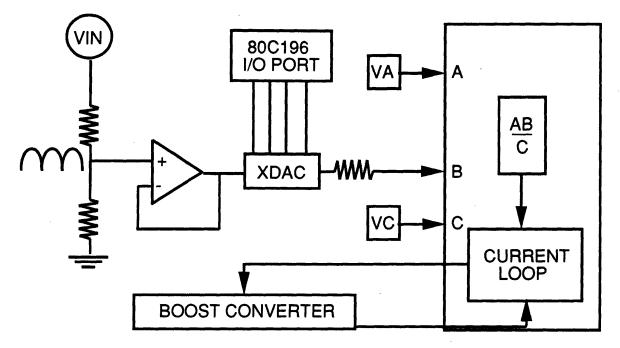

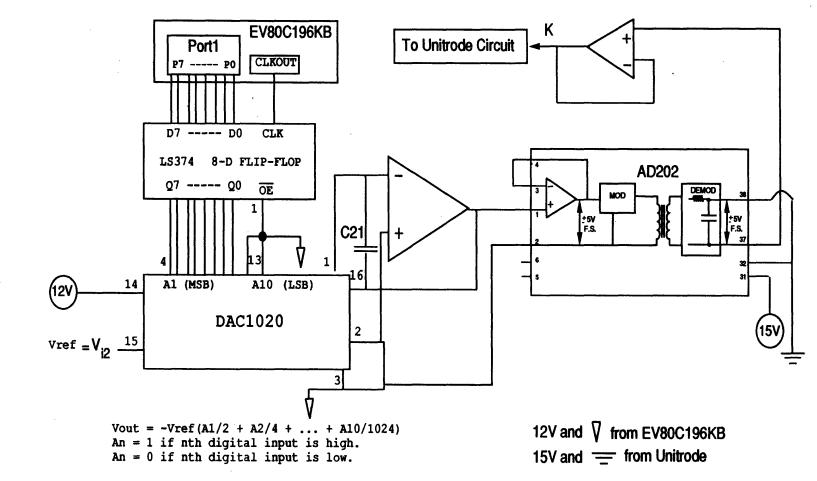

| 3-3 | Output port 1 and multiplying DAC configuration                        | 46 |

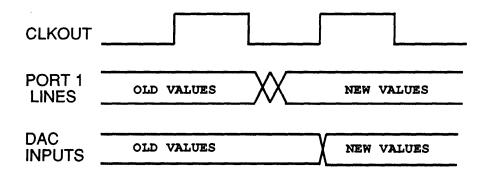

| 3-4 | Output synchronization.                                                | 46 |

| 3-5 | Implementation of the current loop                                     | 47 |

| 3-6 | Closed-loop system with 8-bit input quantization                       | 48 |

| 3-7 | Closed-loop system with 10-bit input quantization.                     | 49 |

| 3-8 | Increasing Input Resolution                                            | 49 |

| 3-9          | Overall structure of hardware system                                                | 51 |

|--------------|-------------------------------------------------------------------------------------|----|

| 3-10         | System timing.                                                                      | 53 |

| 3-11         | Transformation of $v_o$ to the digital value of $v_o^2$                             | 55 |

| 3-12         | Transformation of V to its digital value. $\ldots$ . $\ldots$ . $\ldots$ . $\ldots$ | 56 |

| <b>3</b> -13 | Startup transient with anti-windup mechanism.                                       | 58 |

| 3-14         | Startup behavior with soft-startup and initial anti-windup scheme                   | 59 |

| <b>3</b> -15 | Startup behavior with soft-startup and modified anti-windup scheme.                 | 60 |

| 3-16         | 10-bit quantized system with poles at .8                                            | 63 |

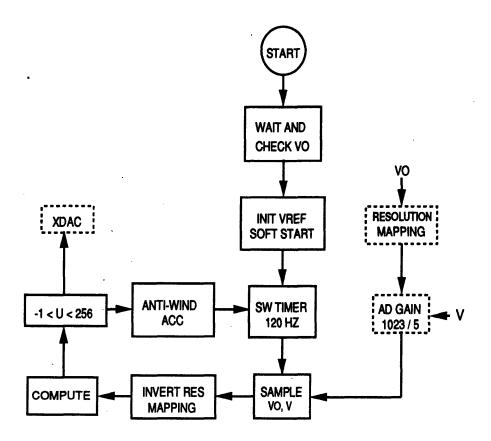

| 3-17         | Software structure                                                                  | 64 |

| 4-1          | Load transient response with $\hat{C} > C$                                          | 67 |

| 4-2          | Ripple response to capacitance doubling followed by load doubling                   | 68 |

| 4-3          | Ripple Detection                                                                    | 70 |

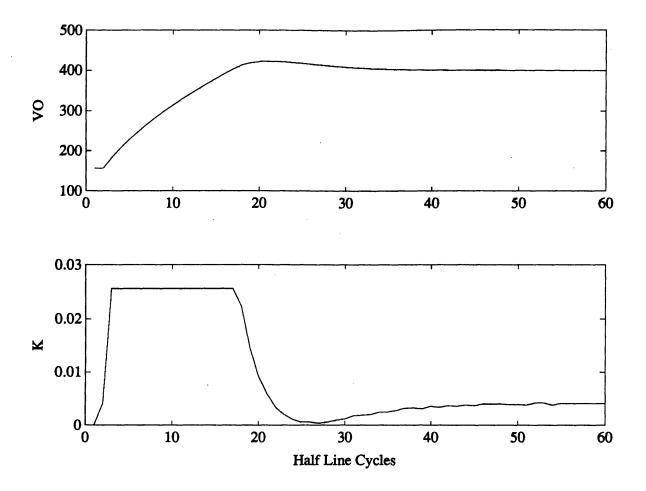

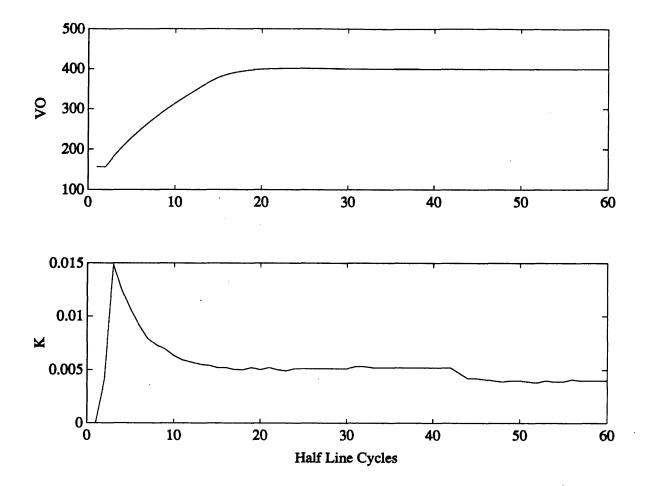

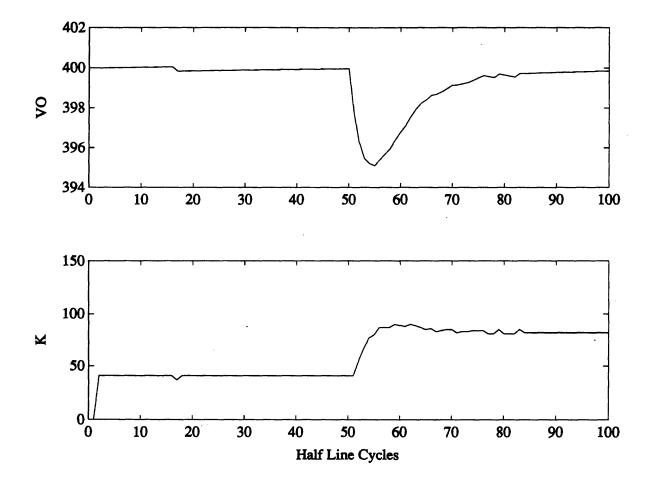

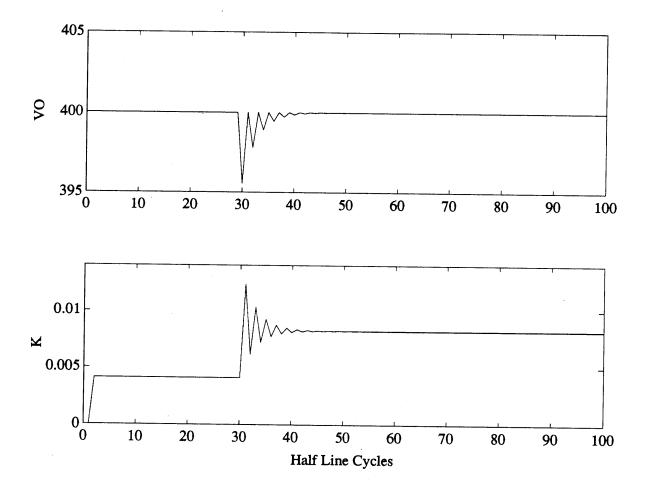

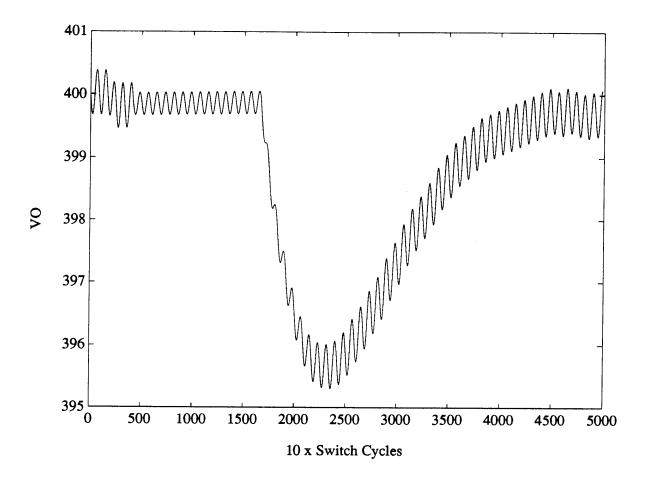

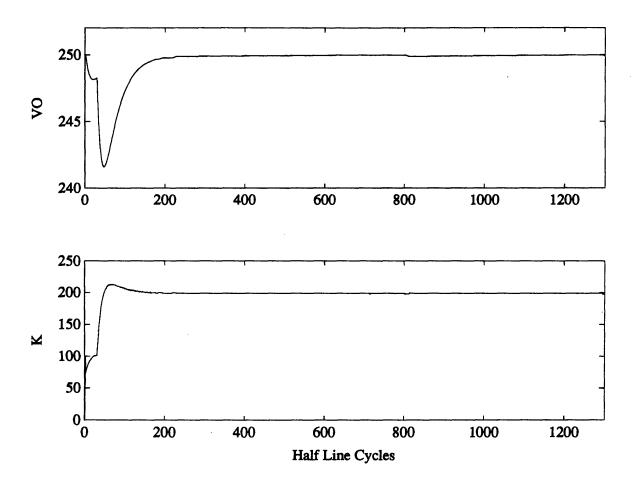

| 5-1          | Simulation of Startup in Implemented System                                         | 76 |

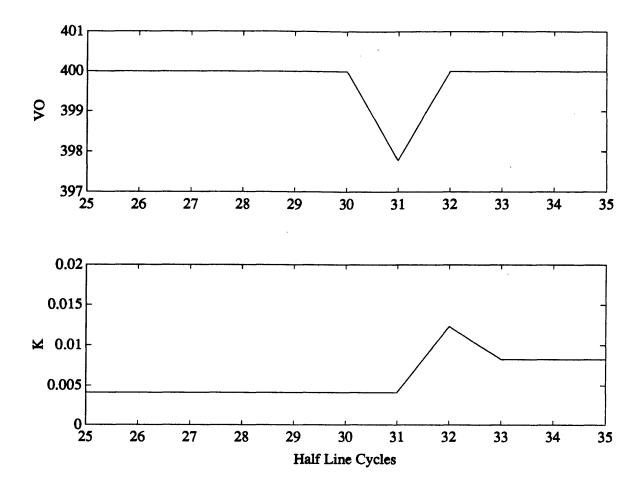

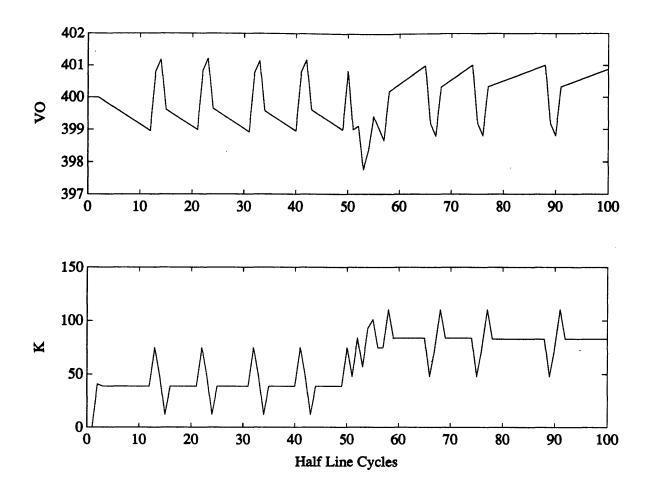

| 5-2          | Simulation of Load Transient Response in Implemented Digital System.                | 77 |

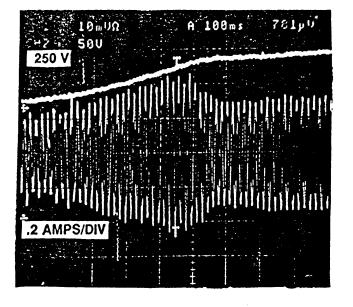

| 5-3          | Startup in Implemented System                                                       | 79 |

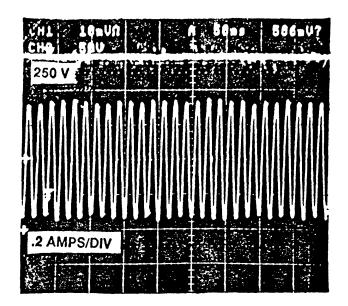

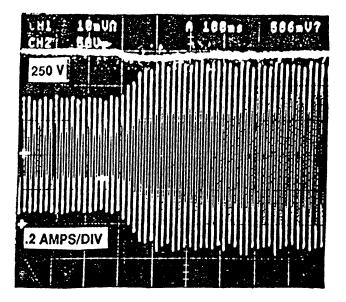

| 5-4          | Steady-State in Implemented System                                                  | 80 |

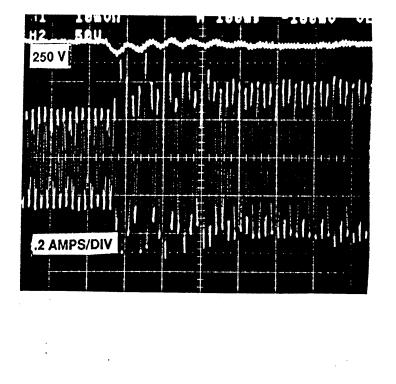

| 5-5          | Response of Implemented System to Load Transient                                    | 81 |

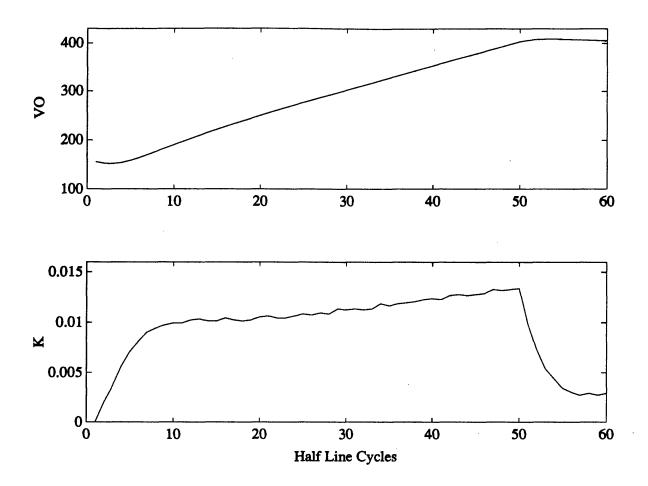

| 5-6          | Response of System with Incorrect Load Capacitor Value without Adap-                |    |

|              | tive Control                                                                        | 82 |

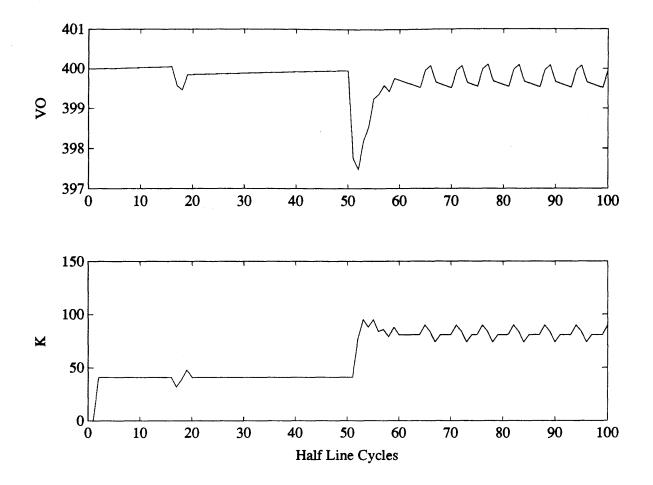

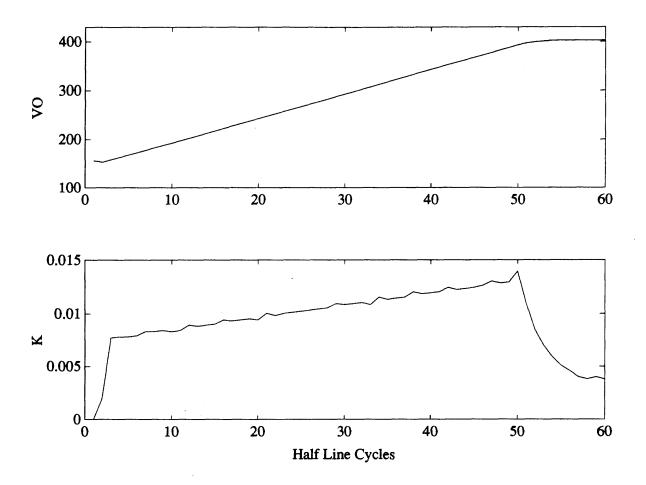

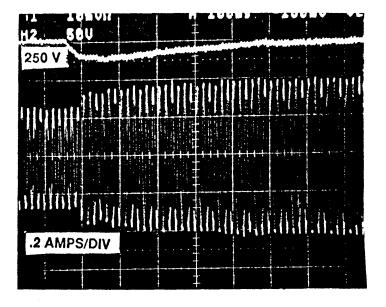

| 5-7          | Response of System with Incorrect Load Capacitor Value with Adap-                   |    |

|              | tive Control                                                                        | 83 |

| 6-1          | Block diagram of compact microprocessor implementation                              | 87 |

| 6-2          | Block diagram of VLSI implementation.                                               | 90 |

| 6-3          | Finite state machine for data path control                                          | 91 |

| 6-4          | Timing of Control Circuitry.                                                        | 93 |

| <b>A</b> -1  | The Closed-Loop System.                                                             | 98 |

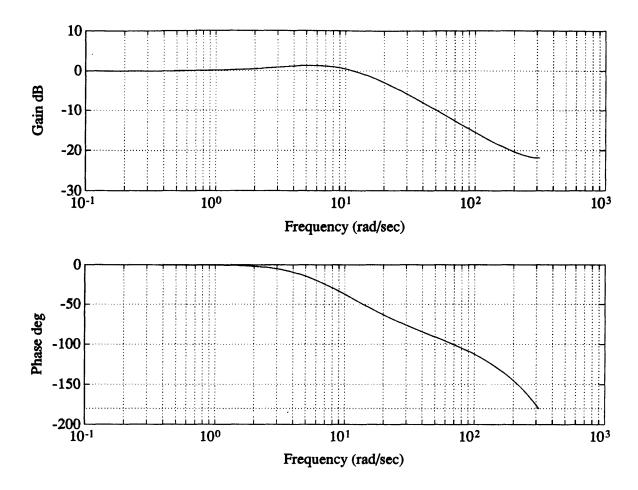

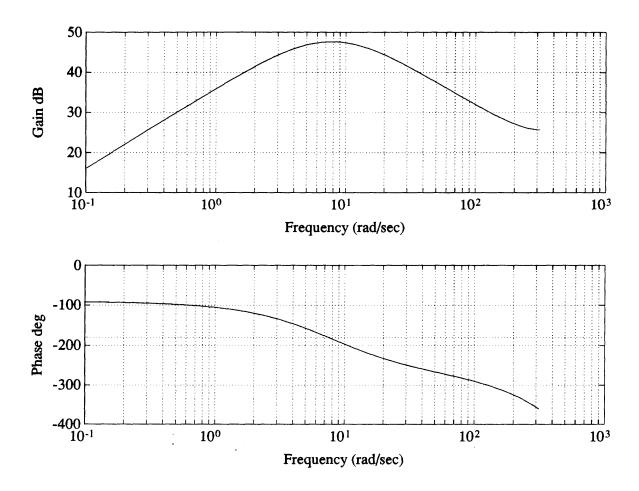

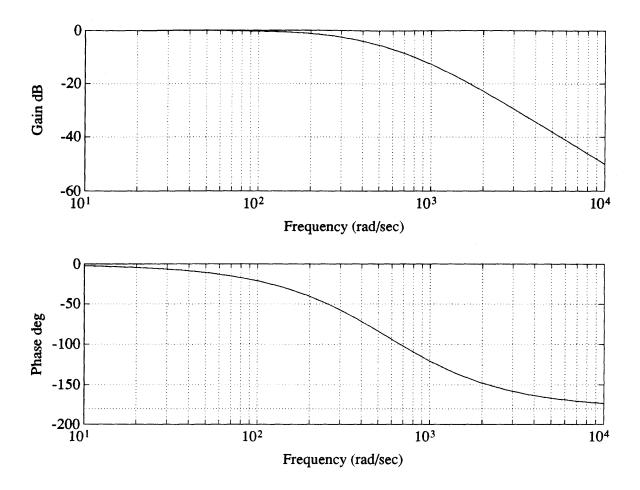

| A-2          | Bode Plot for Transfer Function Between Reference Voltage and Out-                  |    |

|              | put Voltage                                                                         | 99 |

| A-3        | Bode Plot for Transfer Function Between Reference Voltage and Out-       |     |

|------------|--------------------------------------------------------------------------|-----|

|            | put Voltage                                                              | 100 |

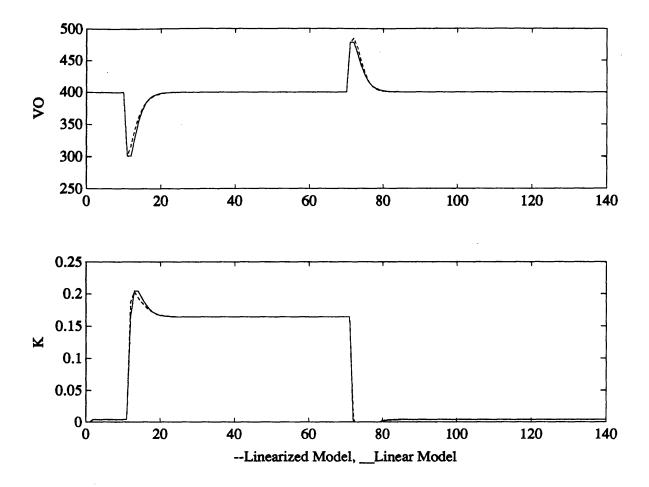

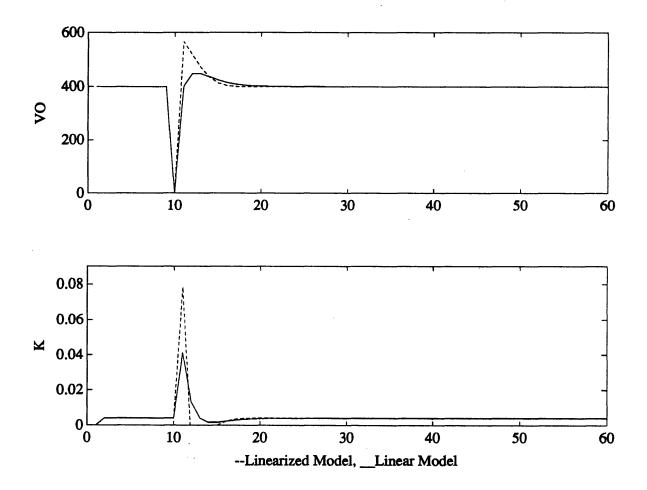

| <b>B-1</b> | Response of large-signal and small-signal controllers to load transients |     |

|            | from 50 Watts to 2000 Watts and back. With the large capacitor used,     |     |

|            | there is hardly any difference                                           | 102 |

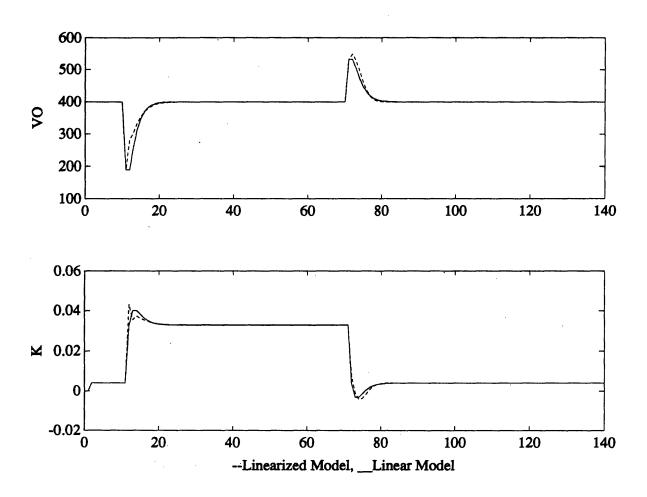

| B-2        | Response of large-signal and small-signal controllers to load transients |     |

|            | from 50 Watts to 400 Watts and back. The capacitor used is a tenth       |     |

|            | of the size of the capacitor used earlier                                | 103 |

| B-3        | Response of large-signal and small-signal controllers to large voltage   |     |

|            | transients                                                               | 104 |

| C-1        | A Second-Order Low-Pass Filter.                                          | 106 |

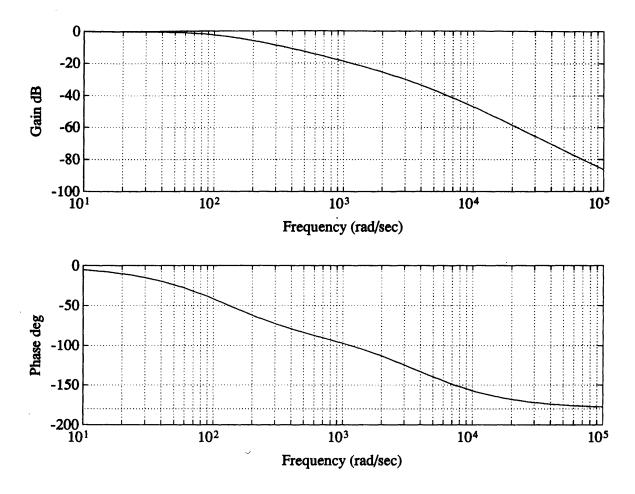

| C-2        | Bode plot for implemented anti-aliasing filter                           | 107 |

| C-3        | A Second-Order High-Pass Filter                                          | 107 |

| C-4        | Bode Plot for Low-Pass Component of Ripple Band-Pass Filter              | 108 |

| C-5        | Bode Plot for High-Pass Component of Ripple Band-Pass Filter             | 109 |

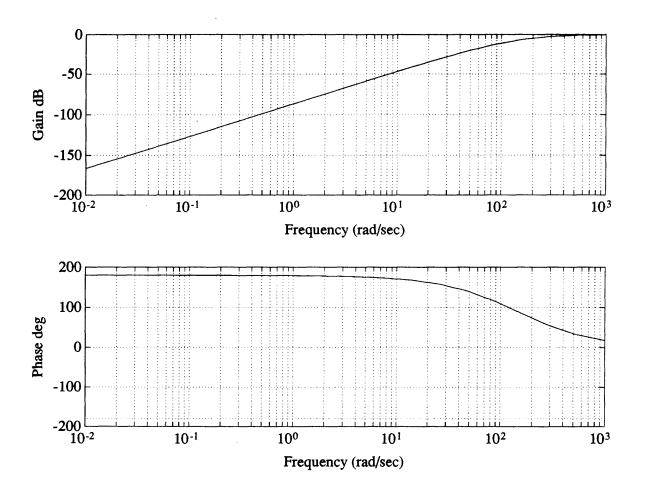

| E-1        | Unitrode Application Circuit.                                            | 131 |

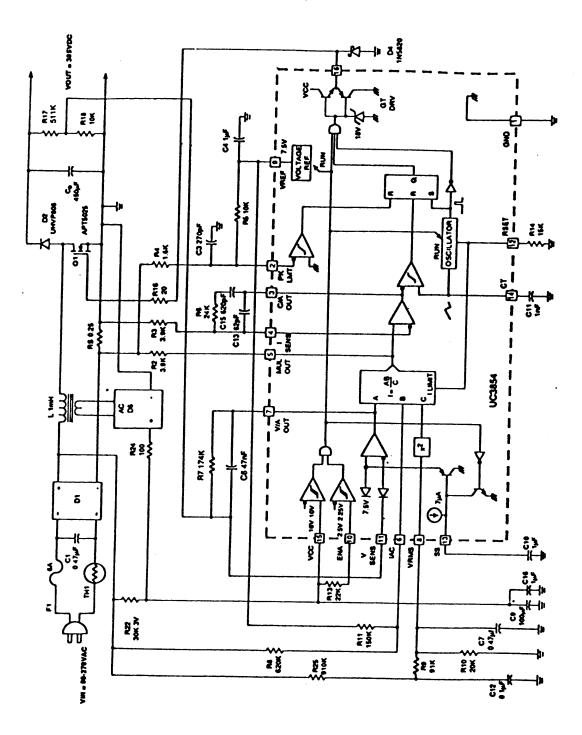

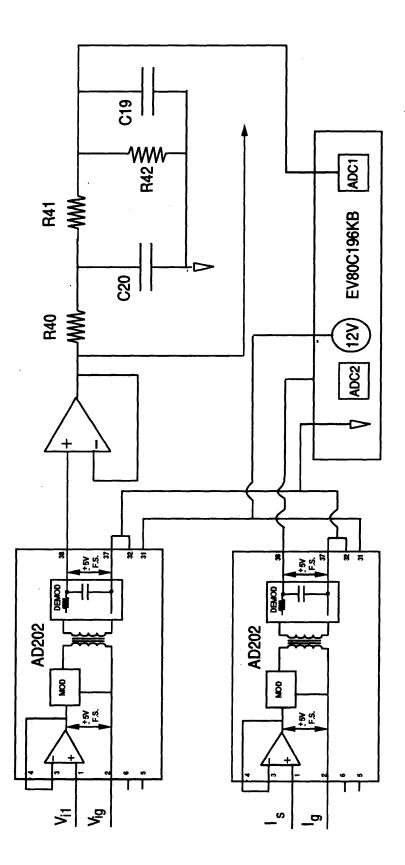

| E-2        | Boost Converter and Analog Current Loop                                  | 132 |

| E-3        | Input Circuitry for Sampling Input Voltage and Load Current              | 133 |

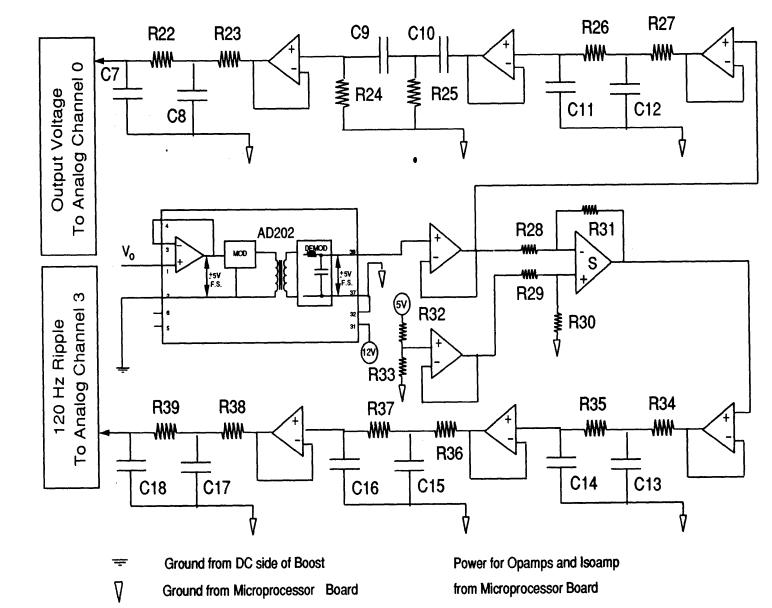

| E-4        | Input Circuitry for Sampling Output Voltage and 120Hz Ripple             | 134 |

| E-5        | Circuitry for Converting Digital Command to Analog Voltage               | 135 |

| G-1        | Schematic Digaram of Compact Digital System                              | 148 |

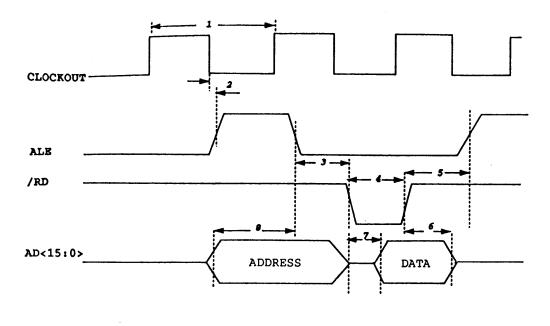

| G-2        | Timing Diagram for Memory Access Cycle.                                  | 149 |

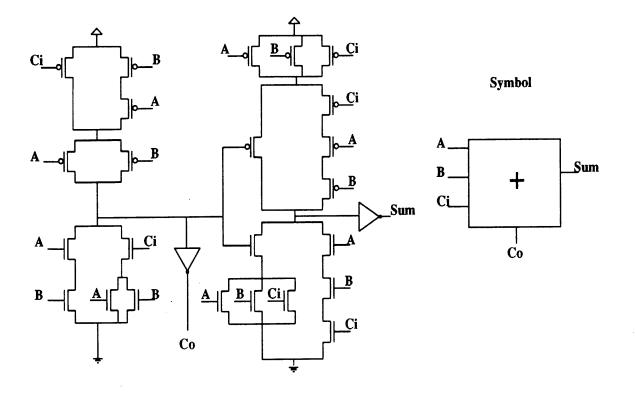

| H-1        | Circuit Schematic for Adder Cell.                                        | 151 |

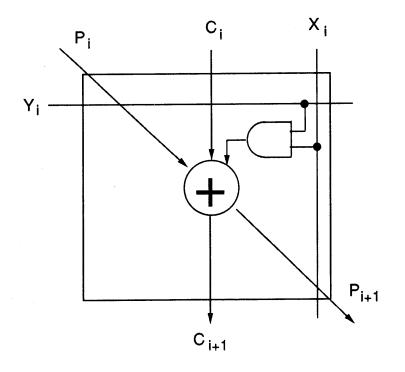

| H-2        | A Product Cell.                                                          | 151 |

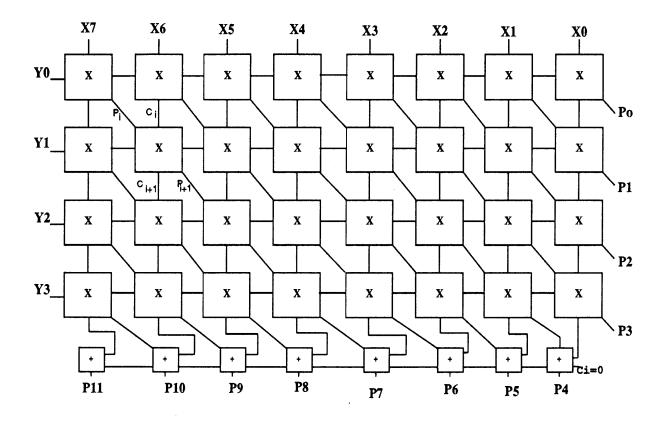

| H-3        | An 8 by 4 Parallel Multiplier                                            | 152 |

.

.

10

# List of Tables

| 6.1         | Estimated Cost for Components | 88  |

|-------------|-------------------------------|-----|

| <b>E.</b> 1 | Resistor Values               | 129 |

| E.2         | Capacitor Values              | 129 |

| E.3         | Other Components              | 130 |

.

## Chapter 1

## Introduction and Background

## 1.1 Objectives

The main goal of this thesis is to explore an implementation of a digital controller for a power electronic circuit. Although digital control techniques are widely used in the area of motor drives, they are rare in other areas of power electronics, mainly because of cost considerations. As operating requirements on power converters become more stringent, however, controlling them becomes a complex problem, better solved with digital rather than analog control. There has been some effort in researching digital control for power supplies [17] [5], but very little has been done in terms of actual implementation of such controllers. This experiment should provide insight into some of the difficulties that arise in realizing such systems as well as answers to these problems.

A Unity Power Factor (UPF) converter was chosen for the implementation. The increasing popularity of this power supply makes it a natural target for research. Moreover, as a high end product in the power supply industry, it is a prime candidate for experimenting with advanced control techniques that are conceivable with a digital controller.

In implementing this controller, several issues are examined. A large-signal sampled data model is used for control design and simulation. This model, as well as the simulation techniques used, are evaluated based on the experimental results. The discrete-time analysis methods, simulation environment, and the development system should provide a taste of what capabilities are available for achieving digital control in power electronics.

Demonstrating the availability of the necessary development tools and the real-

izability of digital controllers for power supplies is not enough to motivate choosing them in practice, however. Additional features that are not easily implemented with analog circuits, such as parameter estimation, are therefore included in the design. Potential reductions in the size and cost of such controllers as well as possible improvement in performance are explored. Overall, an evaluation of the prototype and a look at product feasibility are used to determine whether digital control of power supplies may be the direction in which we should be heading.

## **1.2** The Power Factor

The power factor,  $k_p$ , of a two-terminal network is defined in [3] as the ratio of the average power measured at the terminals to the product of the rms values of the terminal voltage and current.

$$k_p = \frac{\langle p(t) \rangle}{V_{rms} Irms} = \frac{\langle p(t) \rangle}{S}$$

(1.1)

$\langle p(t) \rangle$  is known as real power and is measured in watts, and S is known as apparent power and is measured in volt-amperes. The optimal value for this ratio is unity, indicating that the source is delivering all of its power to the load.

In an AC system, the voltage and current are typically periodic waveforms in time, and the measured power is the product of these waveforms over a cycle [18]. In order for the product of the rms values of the voltage and current to equal the measured power and yield a unity power factor, the two waveforms need to coincide in shape and phase. To understand this better, we consider as an example an ac system with a single harmonic of voltage and a distorted current. The standard utility voltage supply is nominally a sinusoidal waveform:

$$v(t) = V_s \sin \omega t \tag{1.2}$$

Assuming a port with periodic current i(t):

$$i(t) = \sum_{n=0}^{\infty} I_n \sin(n\omega t + \theta_n) = I_1 \sin(\omega t + \theta_1) + \sum_{|n|\neq 1} (I_n \sin n\omega t + \theta_n)$$

(1.3)

The average power delivered by this system is:

$$\langle P \rangle = \frac{1}{T} \int_0^T vidt = V_{srms} I_{1rms} \cos \theta_1 = Sk_d k_{\theta}$$

(1.4)

where  $k_d = \frac{I_1 rm_s}{I_{rm_s}}$  and  $k_{\theta} = \cos \theta$ ;  $k_d$  is the distortion factor and  $k_{\theta}$  is the displacement factor. The power factor is then defined as:

$$k_p = k_d k_\theta \tag{1.5}$$

If the shapes of the voltage and current waveforms coincide,  $k_d$  is unity, and if they are in phase,  $k_{\theta}$  is unity. Hence, for a unity power factor, we need two waveforms of the same harmonic content and phase [3].

In the past, low power factors were mainly due to phase displacement, or a nonunity  $k_{\theta}$ . Most of the loads that an ac power system had to provide power to were linear, drawing a sinusoidal current at the same frequency as the input voltage sine wave. These loads were usually inductive, causing the current to lag the voltage. The displacement factor was then less than unity, resulting in poor power factors. Power factor correction in such a situation can be simply achieved by adding the appropriate capacitor in shunt with the load. More recently, however, the power factor problem has taken on a different form. Today, electronic devices and power supplies present a highly non-linear load to the AC source, therefore drawing a distorted, non-sinusoidal current from the utility. An example of such a load is the basic configuration of the AC-DC power converter used to supply most computers and other electronic equipment with power, namely a simple rectifier circuit with capacitive filtering. Figure 1-1 shows a diagram of such a circuit and its waveforms.

The line rectifier adds a dc component to the input voltage, and the capacitor input filter extracts it and supplies it to the load. The capacitor is replenished by the rectifier at each half cycle with brief bursts of current at each voltage peak. The resulting current is distorted as shown. The poor power factor here is due to  $k_d$ , the distortion factor. The contribution to load power is made by a harmonic component of the current which is in phase with the input voltage, but heavily attenuated due to distortion. Power factors in such setups may be as low as 50%. Power factor correction here involves reshaping the input current waveform, and is a much more difficult problem than adding phase to correct for displacement effects.

## **1.3 High Power Factor AC-DC Converters**

Most AC-DC power converters used today are based on a design similar to the one presented above, with a rectifier and an input filter. The resulting power factor is usually around .6, and the current waveform is distorted with higher harmonics. Most computers require only a few hundred watts and this poor power factor multiplied by

Figure 1-1: Voltage and current in conventional capacitor-filtered rectifiers.[15]

the 1400 or so watts available from a standard outlet provides the necessary power. However, recent trends in computers and electronic systems have resulted in an increasing demand for power factor corrected power converters. The overall number of computers (and other electronic devices that use switch-mode power supplies) has increased dramatically as a result of cost reductions, increasing level of computer literacy, and user-friendly interfaces. This results in more power wasted due to poor power factor, which translates directly into utility losses, since the utility usually charges customers for real power consumed. Moreover, the increasing demand for computing power in workstations has led to an increase in workstation components and therefore in their electrical power requirements. As the power limits of standard electrical outlets are approached, one way to meet these new requirements is to rewire offices with nonstandard outlets. Besides incurring extra cost on the customer, this solution requires rewiring of the outlets every time the workstation is moved [1]. A more practical solution would be to increase the power factor of the power supply.

As mentioned earlier, a poor power factor in switched power converters is usually accompanied by distorted current waveforms. The higher harmonics in these waveforms may interfere with nearby instruments, often making it necessary to add extra filtering components. Higher harmonics may also resonate and interfere with the utility's circuit protection devices, causing them to malfunction. Power factor correction through current shaping would essentially eliminate many or all of these higher harmonics. In Europe, more stringent limits on the harmonic content of power supply waveforms are already being legislated. According to the tougher standards recommended by the International Electrotechnical Commission (IEC) 555-2, power supplies rated higher than 300 watts need to incorporate some form of power factor correction [18].

Responding to this increasing need for higher power factors, several systems with power factor correction have been developed. The multiple output Modular Power System with high power utilization [2] provides an 80% power factor to deliver 1200 watts to a workstation from a standard outlet. It does not, however, solve the problem with input current harmonics. More recently, power supplies with almost unity power factors (UPF) have been introduced, providing levels of power near the maximum that can be drawn from the standard outlet. A UPF uses a certain power supply topology with some control scheme that draws a current with the same frequency and shape as the input voltage.

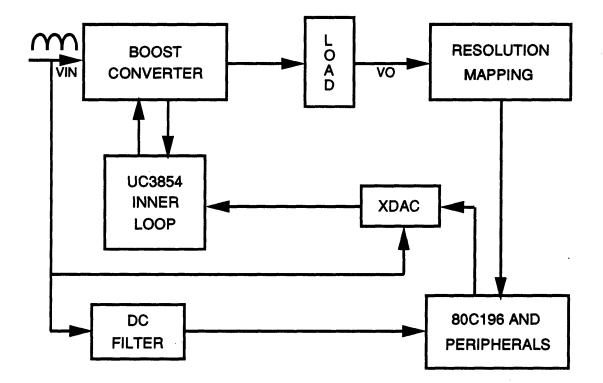

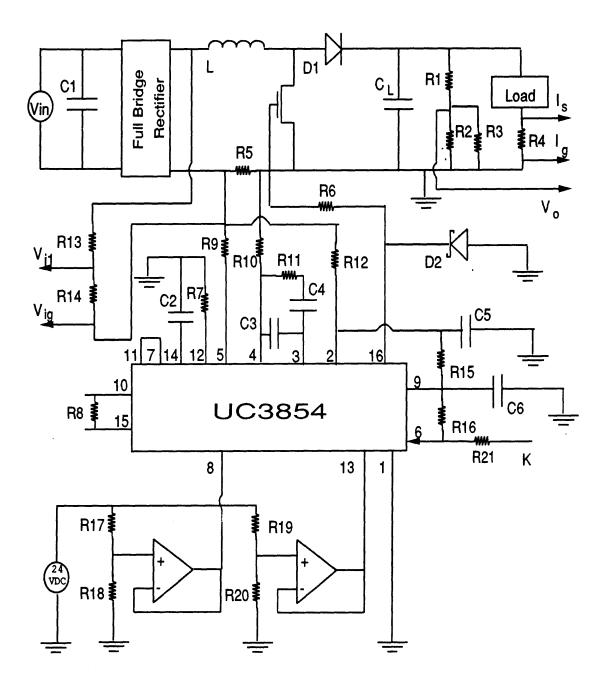

One increasingly popular scheme for achieving this sinusoidal input current uses the circuit in Figure 1-2. The boost converter in the circuit receives as its input the rectified AC waveform,  $V|sin\omega t|$ . The inner loop controls the source current to the shape and phase of the input voltage by providing a switching sequence for the transistor that forces the inductor current  $i_L(t)$  towards a desired current  $i_p(t)$ , which is in turn made proportional to the input voltage. The outer voltage loop regulates the output voltage  $v_o$  to the reference voltage  $V_o$  by adjusting the proportionality constant used to generate  $i_p(t)$  every line cycle [4]. This allows the system to correct for deviations from the nominal point in the output voltage due to disturbances in the constant load P.

## **1.4 Modeling of UPF Power Supplies**

There are different approaches to modeling UPF power supplies and designing their control loops. We focus here on the boost converter topology presented above. In [1], Williams investigates five different control circuits. They are all based on a small-signal transfer function between  $i_p(t)$  and  $v_o(t)$ . Henze and Mohan [5] use a hysteretic current controller for the inner loop and a digital PI controller for the outer voltage loop. One model presented by [4] and [17] is derived by linearizing a power balance description of the boost converter above with a load resistor in parallel with the constant power load and is shown in Figure 1-3. The linearization is done around the nominal operating point for the output voltage,  $V_o$ .

Without the load resistor, a power balance description averaged over half a line cycle yields:

$$\frac{dv_o^2(t)}{dt} = \frac{1}{C}(V^2k(t) - 2P)$$

(1.6)

Averaging techniques used to arrive at this and other models will be discussed in more detail in Chapter 2. Linearizing this about the nominal operating point, and using tildes to denote deviations from the nominal, we get the following transform

Figure 1-3: Block diagram for a linearized model of a UPF.

domain description (which is the result in Figure 1-3 for the case R = 0).

$$\tilde{v}_o = \frac{1}{2sV_oC} (V^2 \tilde{k} - 2\tilde{P}) \tag{1.7}$$

The models mentioned above and the one developed here are all derived through some form of linearization. Linearized models are valid only in the vicinity of the nominal operating point and are therefore small-signal models. In Chapter 2 we develop a large signal model that we use for the design of the digital controller. A large signal model is more accurate, and controllers based on it are potentially more robust and reliable than those based on linearized models.

## **1.5 Digital Control**

In the last decade or so there has been a rapid increase in the use of digital controllers in dynamic systems. Digital controllers have become an integral part of the operation of many industrial systems [6]. Originally, they were used as components only in large-scale control systems. However, the evolution of microprocessors and microcomputers that can rapidly perform a variety of control functions has brought digital control into small-scale systems as well.

The ability to "make decisions" (i.e. implement complex, nonlinear, time varying control laws) is one of the main strengths of digital control. Applications that utilize this capability include "intelligent" industrial robots and fuel economy optimization in automobiles. This and other advantages of digital computing over analog computing combine with the decreasing cost and size of microprocessors and microcomputers to produce the current trend toward digital controllers rather than analog controllers [6]. Some of the advantages of digital control are:

- Straightforward data processing allows for more complex calculations and the implementation of modern control schemes.

- A simple change of a program allows for a change in controller characteristics. This flexibility allows the designer to modify the controller at will, as well as implement adaptive control schemes.

- Digital controllers are superior in terms of internal noise, aging, and drift effects.

Some of the disadvantages of digital control are:

• System performance is likely to degrade as sampling and quantizing result in more errors.

- A digital controller that compensates for such degradation involves a more complex design than its analog counterpart.

- A digital controller can be slower and more expensive than an analog controller [6].

Generally, digital control of a continuous time system involves sampling of the control signals, A-D conversion, processing of the digital data using a digital computer, D-A conversion of the digital outputs, and interpolation of the resulting signal. Figure 1-4 illustrates a typical digital control system.

In power electronics, digital control of motors and motor drives has become very popular, [7], [8]. However, the use of digital control in other converter systems is not widespread. Power converter systems place high demands on digital control systems, and digital controllers that meet these high demands are often considered too costly. The systems must be able to handle fast closed-loop control processes with sampling times of 1 ms and below. They must also meet specific time requirements in generating control signals and reacting to process interrupts. A good user interface is required so that changes to the controller may be made easily during planning and testing [9]. In [9], Siebert reviews a new multicomputer control system for all types of converters. The design uses 3 80196 Intel microprocessors and provides a fairly high-level language interface. Very little has been done in terms of actual implementation of digital controllers for power converters, however. A low cost digital controller for DC - AC inverters and DC - DC PWM converters is discussed in [14].

## **1.6** Motivation

With the increasing need for high power factor converters, UPF power supplies have rapidly gained popularity. It is essential that power supplies for workstations and other computers be robust, reliable, and quick to respond to perturbations in circuit parameters. The linear large signal model introduced in the next chapter leads to a controller that promises quick and reliable correction of changes in the output voltage that result from perturbations in load power or input voltage. Simulations show transients settling down after eight line cycles, but even faster response is possible [4]. Power factors of .97 in steady state are also simulated. Large perturbations are handled well due to the linearity of the model that underlies the controller design. Prior to this project, however, only an analog controller based on the large signal model had been implemented.

Figure 1-4: A typical digital controller [6].

The cyclic nature of the UPF converter, due to its sinusoidal inputs, makes it easily and accurately described via a sampled data model. Once such a model is available, the design of discrete-time controllers using the model can be straightforward. A discrete time controller lends itself naturally to implementation in a digital setting. A digital implementation would add to the flexibility and robustness of the system. Moreover, it would allow for the on-line real time estimation of various circuit parameters that are likely to change with age or for other reasons, thereby facilitating adaptive control. One such parameter is the bus capacitance, which can be estimated from the ripple on the output voltage. The microprocessor may also be programmed to shut down under emergency conditions and at the request of the user. Considering that the cost of microprocessors is decreasing rapidly and that we could conceivably use part of the processing capability already available on a system, the cost of a digital implementation may not be significantly more than an analog one, if at all. Moreover, a digital controller need not be slower than an analog one; closed-loop bandwidths can be comparable, and digital controllers can even result in faster settling than analog controllers. This will become clear in the case of UPF converter control, as the sampled data model and controller are developed in later chapters.

Digital control theory is well-developed [10], and microprocessors are becoming

less and less expensive and more powerful. Nevertheless, the cost of digital hardware is still too high for many small-scale applications. This combines with programming complexity and time to hinder the development of digital control applications. The digital controller explored in this thesis is developed with cost as well as design time in mind. An inexpensive microprocessor is chosen, and a high-level language (C) is used for algorithmic implementation. Entry of digital controllers into a field of small-scale inexpensive products such as power electronics would be highly unlikely without attention to cost and design time. Our goal is to demonstrate that digital controllers can provide equal or better performance than their analog counterparts in controlling inexpensive power electronic circuits with little extra cost in design time or money.

## **1.7** Thesis Organization

This thesis document is organized into seven chapters. Chapter 2 develops a largesignal model for the boost converter, averaged over the time scales of both the switching period and half the line period. It then presents a sampled data model based on the averaged models, which is then used for the design of a discrete-time controller. Simulations of the resulting discrete-time system are then described.

Chapter 3 describes the implementation of the digital controller. It begins by discussing common issues in digital control, such as quantization error and sampling. Problems more specific to the system at hand are then introduced. A description of the microprocessor development system is provided, and the initial implementation is discussed. Software, digital hardware, and analog hardware used for interfacing to the power converter are described. Simulations used in the development process are also shown.

Design and implementation of adaptive control are discussed in Chapter 4. Other additional features and potential improvements are also explored. While some are simple enough to implement, others do not promise significant improvement in this system but are worth exploring for future reference.

Chapter 5 presents the results of experiments. These results are compared with simulations for verification of successful operation. They are also compared with an analog implementation of a related control scheme (to evaluate the digital implementation), and with an implementation using a commercially available circuit that utilizes a different control scheme (to evaluate our choice of controller). Chapter 6 investigates more compact implementations of this system. The first one uses the same microprocessor as in the development of the prototype, and interfaces it directly to off-chip memory and other hardware essential to this application, eliminating the need for the development board and all the extra hardware and firmware. A second uses a VLSI implementation, which would be cheaper, faster, and more compact.

Chapter 7 summarizes the pertinent conclusions of this research work, and identifies problems for future research. Matlab simulation code, C programs for testing and running the microcontroller, and hardware schematics are included in the appendices.

## Chapter 2

## Modeling and Control Design

Systems that are inherently cyclic, such as the one at hand, can be accurately described using a sampled data model (SDM). Such a model is a discrete time description useful for designing discrete time controllers. Sampled data models and discrete time control for the UPF are developed below. Simulations of the closed-loop system under various control designs are included, but omitting details such as quantization.

## 2.1 Dynamic Models of the UPF

The circuit in Figure 1-2 can be described by a power balance equation, as mentioned earlier. This power balance relationship is used to develop continuous- and discrete-time models of the circuit, averaged over both the switching period and the period of the rectified line voltage. These models are used to develop controllers and to obtain simulations in MATLAB<sup>TM</sup> for the closed-loop system with different controller designs.

## 2.1.1 The T<sub>s</sub>-Averaged Model

In [4] Mahabir develops models for the UPF using a resistive load in parallel with a constant power load. The models below are developed in the same manner, ignoring the effect of the load resistor in parallel with the constant load. Equating the power input to the system in Figure 1-2 with the power dissipated in the different components, we find:

$$\frac{1}{2}C\frac{dv_o^2}{dt} = v_{in}i_L - \frac{1}{2}L\frac{di_L^2}{dt} - P$$

(2.1)

Typically, the inner-loop, or the current loop controller, is operating at a much higher bandwidth than the outer loop. If we choose that to be the case, we can make the approximation that the inner loop is working ideally, and that the inductor current is following the current commanded by the controller:

$$i_L(t) = k(t)v_{in}(t) \tag{2.2}$$

(Note that k(t) is referred to in Figures 1-2 and 2-2 as  $\mu(t)$ .) Substituting for the inductor current above:

$$\frac{1}{2}C\frac{dv_o^2(t)}{dt} = k(t)v_{in}^2(t) - \frac{1}{2}L\frac{d[k^2(t)v_{in}^2(t)]}{dt} - P$$

(2.3)

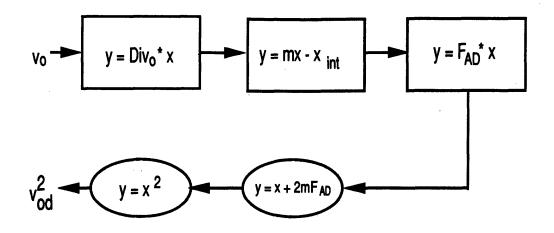

In developing this model, the switching frequency ripple in the output voltage was ignored. This result is essentially the same as that arrived at by averaging a switch model over the switching period. Hence it will be referred to as the continuous-time  $T_s$ -averaged model. It is clear that if  $v_o$  is taken as the state variable, 2.3 is a nonlinear description of the power converter. However, if  $v_o^2$  is used, the model is effectively linear [4].

## **2.1.2** The $T_L$ -Averaged Model

The  $T_s$ -averaged model may still be simplified further by averaging over a longer period. Let  $T_L$  be the period of the rectified input. Averaging 2.3 over  $T_L$  yields an averaged model on the time scale of the input period. The running average defined by

$$\bar{w}(t) = \frac{1}{T_L} \int_{t-T_L}^t w(\tau) d\tau$$

(2.4)

is used. Denote  $v_o^2(t)$  by x. If the ripple in  $v_o(t)$  is small, then  $x \approx \bar{v}_o^2$ . Assuming that k(t) varies slowly enough to be considered constant over any interval of length  $T_L$  further simplifies our analysis, as

$$\int_{t-T_{L}}^{t} k(t) v_{in}^{2}(t) \approx k(t) \frac{V^{2}}{2}$$

(2.5)

and

$$\int_{t-T_L}^t \frac{d[k^2(t)v_{in}^2(t)]}{dt} \approx 0$$

(2.6)

with our assumption that k(t) is slowly varying. The resulting  $T_L$  -averaged model is given by the *linear time-invariant (LTI) first-order* description

$$\frac{dx(t)}{dt} = \frac{1}{C}(V^2k(t) - 2P)$$

(2.7)

The  $T_L$ -averaged model is not as accurate as the  $T_s$ -averaged one, as it ignores the ripple on the output voltage. This ripple is very small, however, as the load capacitor is usually very large. The  $T_L$ -averaged model provides a much simpler description, which facilitates the straightforward design of controllers. Moreover, the assumption that k(t) is essentially constant over a rectified line period allows for the implementation of "slow" controllers that operate on that parameter. This is especially helpful in digital implementations, as will become clear shortly. The  $T_s$ -averaged model is required for simulations and in formulating an expression for the output voltage ripple, which is used in Chapter 5 to estimate the value of the output capacitor. However, controllers based on the  $T_L$ -averaged model should yield satisfactory results in regulating the output voltage in our application. Controllers based on the  $T_s$ -averaged model would need to react with the frequency of the switch. An analog implementation of such a "fast" controller is currently being investigated [15], but a digital implementation at that speed with the currently available technology would be too expensive to be practical.

#### 2.1.3 Sampled Data Models

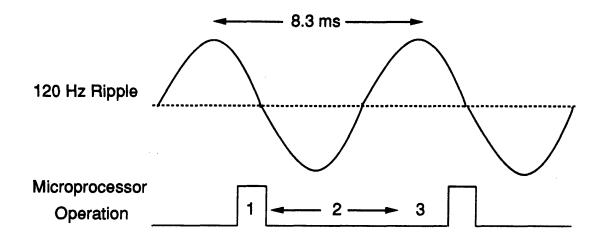

To achieve a unity power factor, the input current has to coincide in shape and phase with the input voltage. This dictates that k(t) is kept constant over each cycle. Under this condition, it is natural to investigate sampled data models (SDM) and controllers. A sampled data model on the time scale of the input period  $T_L$  is developed below and eventually used for designing a discrete-time controller for the digital controller implementation. With  $T_L = 8.3ms$  as the sampling period, there is ample processing time for most present day micro-controllers to execute significant control algorithms. A sampled data model on the time scale of the switching period  $T_s$  is also developed. It is used later in simulations and in developing adaptive control schemes, for which the " $T_L$ -SDM" proves insufficient [4].

#### $T_L$ -SDM

Assume that k(t) is essentially constant over the input period, the value of k(t) in the *n*th cycle being denoted by k[n]. Let the value of  $v_o^2$  at the beginning of the *n*th cycle equal x[n]. Integrating either the  $T_s$ -averaged model in 2.3 or the  $T_L$ -averaged model in 2.7 over  $T_L$  yields the following equation [3]:

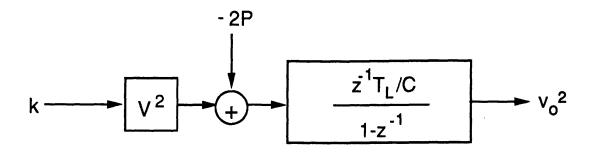

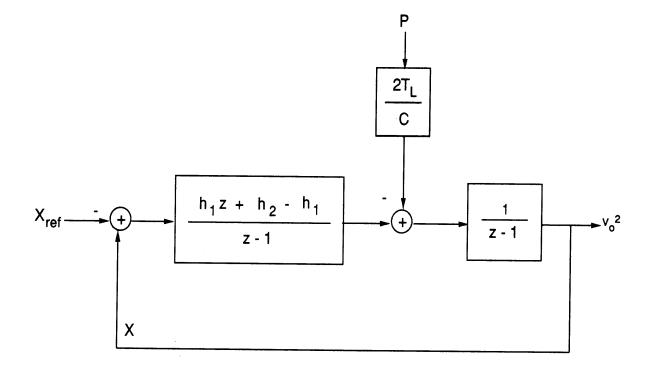

Figure 2-1: The  $T_L$ -based sampled-data-model.

$$\frac{1}{2}C(x[n+1] - x[n]) = T_L(k[n]\frac{V^2}{2} - P)$$

(2.8)

ог

$$x[n+1] = x[n] + \frac{T_L V^2}{C} k[n] - \frac{2T_L}{C} P$$

(2.9)

This  $T_L$ -SDM is a state-space representation of a first-order LTI discrete-time system, with control input k[n] and disturbance input P, as shown in Figure 2-1 (which actually represents the z-transformed version of 2.9).

### $T_s$ -SDM

The development of a sampled data model at the time scale of the switch period is similar to that of the  $T_L$ -SDM. Assume that k(t) is constant over  $T_s$ . The time index  $\eta$  is used to denote the switching period. The sampled data model is then acquired by integrating the  $T_s$ -averaged model of 2.3 over  $T_s$ . As presented in [4], the  $T_s$ -SDM is

$$x[\eta+1] = x[\eta] + b_1[\eta]k[\eta] + b_2[\eta]k^2[\eta] - \frac{2PT_s}{C}$$

(2.10)

where  $b_1[\eta]$  and  $b_2[\eta]$  are time varying input gains given by:

$$b_1[\eta] = \frac{V^2}{C} T_s - \frac{V^2}{C} \left\{ \frac{T_L}{2\pi} \left[ \sin\left(2\pi(\eta+1)T_s/T_L\right) - \sin\left(2\pi\eta T_s/T_L\right) \right] \right\}$$

(2.11)

$$b_2[\eta] = \frac{V^2 L}{C} \{ \sin^2\left(\pi(\eta+1)T_s/T_L\right) - \sin^2\left(\pi\eta T_s/T_L\right) \}$$

(2.12)

whereas the  $T_L$  -SDM ignores the ripple in the output voltage, and therefore reaches a steady state where x[n+1] = x[n], The  $T_{\bullet}$  -SDM does not ignore this ripple. It therefore reaches a cyclic steady state with a period equal to that of the output voltage ripple.

## 2.2 Controller Design

The models developed above are verified through simulation and comparison with results from a test circuit in [4]. These models are useful for designing controllers for the UPF. Controllers may be designed based on the linearized model presented earlier, or on any of the linear models of the last section. Both the  $T_s$ -Averaged and  $T_L$ -Averaged models have been used to design analog controllers for the UPF [15], [4]. To take advantage of the  $T_s$ -SDM in a digital controller would require processing speed that cannot be met today with a commercially viable digital implementation. The  $T_L$ -SDM is therefore chosen as the basis for designing a discrete-time controller to be implemented digitally.

#### 2.2.1 PI Control

A natural way to regulate the output voltage to a desired value  $V_o$  is to use a discrete time version of proportional integral, or PI, control [3]. This provides for zero steadystate error despite uncertainties in system parameters (including load power) as shown below. Proportional control by itself could not avoid load regulation in this case. To exploit the linear model of the power supply, the state variable to be controlled needs to be the square of the output voltage instead of the voltage. This variable is x, and is regulated to a desired value  $X = V_o^2$ . Note that the value of  $v_o$  at the beginning of each input cycle is what is being regulated to the reference, and not the average value of  $v_o$ . The ripple on  $v_o$  is assumed to be small enough that this is not a major concern.

To assure that in steady-state the error in the output voltage goes to zero, the error in  $v_o^2 = x$  is fed into an accumulator, i.e. a discrete-time version of an integrator. For the accumulator, a new state variable  $\sigma$  is defined:

$$\sigma[n+1] = \sigma[n] + (x[n] - X)$$

(2.13)

The input to the accumulator is the error term  $x[n] - X = v_{err}[n]$ . If a steady state is attained, x[n+1] = x[n] = X and  $v_{err}[n] = 0$  (Otherwise the accumulator would

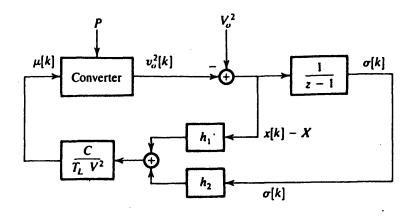

Figure 2-2: A discrete-time PI controller [3].

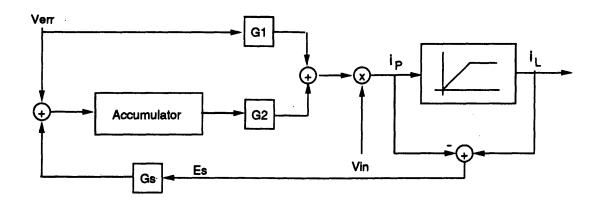

not be in steady state). To implement PI control then, the value of the accumulator is multiplied by an accumulator gain  $G_I$  and added to the product of a proportional gain  $G_P$  and  $v_{err}$ . The result is fed into the open-loop system through its control input k[n]:

$$k[n] = G_P v_{err}[n] + G_I \sigma[n]$$

(2.14)

Defining the normalized gains

$$h_1 = \frac{T_L V^2}{C} G_P \tag{2.15}$$

$$h_2 = \frac{T_L V^2}{C} G_I \tag{2.16}$$

yields the following:

$$k[n] = \frac{T_L V^2}{C} (h_1(x[n] - X) + h_2 \sigma[n])$$

(2.17)

The resulting closed-loop system is shown in Figure 2-2.

The accumulator in the figure is shown as  $\frac{1}{z-1}$ . This is the z-transform transfer function of the accumulator described above in 2.13 from its input  $v_{err}$  to its output  $\sigma$ .

The overall system is a combination of the converter and the controller, both of which are first-order subsystems. The closed-loop model is therefore second-order, and is described by the following state-space model:

$$\begin{pmatrix} \sigma[k+1]\\ x[k+1] \end{pmatrix} = \begin{pmatrix} 1 & 1\\ h_2 & 1+h_1 \end{pmatrix} \begin{pmatrix} \sigma[k]\\ x[k] \end{pmatrix} - \begin{pmatrix} 1\\ h_1 \end{pmatrix} X - \begin{pmatrix} 0\\ \frac{2T_L}{C} \end{pmatrix} P \qquad (2.18)$$

If

$$\boldsymbol{A} = \begin{pmatrix} 1 & 1 \\ h_2 & 1 + h_1 \end{pmatrix}$$

(2.19)

The characteristic polynomial for this system, obtained by finding the determinant of zI - A, is

$$z^{2} - (h_{1} + 2)z + 1 + h_{1} - h_{2}$$

(2.20)

The roots of the characteristic polynomial are the poles of the system:

$$z_1, z_2 = \frac{(h_1 + 2) \pm \sqrt{h_1^2 + 4h_2}}{2}$$

(2.21)

The transient response of any variable in the system is of the form  $c_1 z_1^k + c_2 z_2^k$  (for  $z_1 \neq z_2$ ), where  $c_1$  and  $c_2$  are constants that depend on the initial conditions (and on which variable is being considered). If  $G_I$  and  $G_P$  can be chosen such that  $z_1$  and  $z_2$  have magnitude less than 1, the system will be stable, and will reach a steady state in which  $v_{err} = 0$ .

Without the accumulator part, the state variable x would be governed by the first-order equation

$$x[n+1] = x[n] + h_1(x[n] - X) - \frac{2T_L P}{C}$$

(2.22)

which in the steady state settles down to

$$x[n+1] = x[n] = X + \frac{2T_L P}{Ch_1}.$$

(2.23)

This system exhibits load regulation and a nonzero steady-state error.

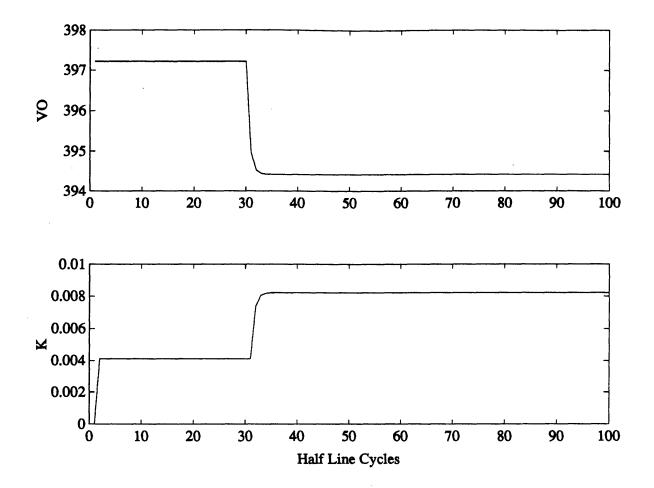

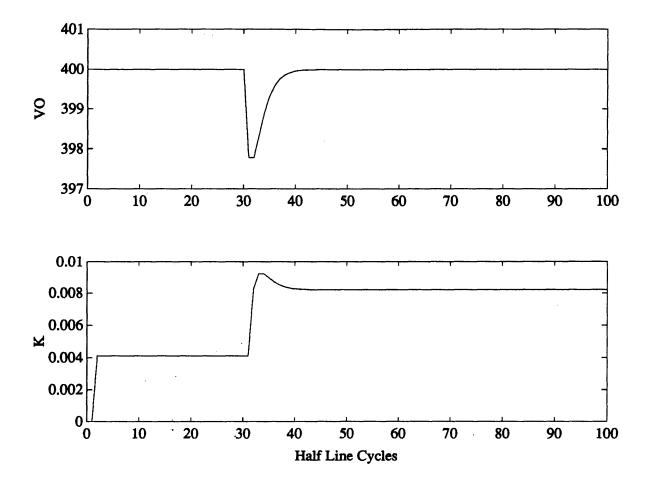

Figure 2-3 shows the response of the closed-loop system with proportional control to a doubling in the load and Figure 2-4 shows the response to the same perturbation with PI control. In these simulations, as well as in all simulations hereafter, plots of k will be used to illustrate the envelope of the input current, since from Figure 1-2,  $i_P = kv_{in}$ .

Figure 2-3: Response of the closed-loop system with proportional control.

The scheme above assumes that no knowledge of the load is available, and proceeds to compute and store in the accumulator a value that would provide zero error for any load. In most cases, however, a nominal value for it is known; if measurements of the load are available, they can be taken advantage of as well. Based on knowledge of the actual or nominal load, the control variable k[n] may be found as the sum of a nominal K[n] and a  $\tilde{k}[n]$  to be computed by a PI controller. This scheme has its advantages. In particular, the controller does not need to work as hard if the estimate for K[n] is accurate. This can translate into less computation time in a digital implementation. Moreover, outputting  $\tilde{k}[n]$  instead of K[n] could mean more resolution per unit of control variable, if, as in the case of a digital controller, the output resolution is limited. The controller developed above is more straightforward to implement however, and is better equipped to deal with the most general cases in which the load and other parameters in the circuit are not well known, and is therefore chosen for the implementation. The issues introduced here regarding the difference between the two designs are discussed further as implementation issues.

Figure 2-4: Response of the closed loop system with PI control — system poles at .5.

Figure 2-5: Deadbeat response to load disturbance.

## 2.2.2 Deadbeat Control

A stable LTI continuous-time system cannot settle down to its steady-state in finite time after a disturbance occurs, since its transients decay exponentially. In discretetime systems, however, the case is different. Transients evolve as  $A^n$ , where n is the number of time steps. By choosing A to be a nilpotent matrix, with eigenvalues at 0, this quantity will go to zero in finite time. Specifically, if A is a nilpotent matrix,  $A^n = 0$  will definitely be true for n = m, where m is the dimension of A, or for n < munder certain conditions. The result is a so-called *deadbeat* system, whose transients last only a finite number of steps.

For the UPF closed-loop system with PI control, setting  $z_1, z_2 = 0$  in 2.21 yields the values  $h_1 = -2$  and  $h_2 = -1$  for the normalized controller gains. The simulations in Figure 2-5 show the response of the deadbeat system to a doubling in the load. Steady state is recovered in 2 cycles, the order of the closed-loop system.

Clearly, deadbeat response requires very high gains and high levels of control com-

mand that may not be available to the designer. As will be shown in Chapter 3, high gains and bandwidth also result in an increase in quantization error in the digital system. . In the case of the UPF, a tremendous increase in input current (to correct for the error in the output voltage induced by the step in power) is required to achieve deadbeat behavior. Physical limitations in the actual implementations deny the system such input current levels. These limitations along with the complications due to high bandwidth in the quantized system prevent the implementation of deadbeat control.

## 2.2.3 Additional Design Features

The PI controller introduced above yields satisfactory results in analysis and simulation. However, power supply component limitations, system specifications, and other implementation difficulties require the utilization of other control techniques in conjunction with the basic controller. A digital implementation facilitates these extra features with relative ease. Most of these control techniques are developed in more detail in the implementation section, as they resulted from some implementation difficulty and many of their parameters are implementation dependent. However, their general features were part of the initial design process and are introduced below.

#### **Adaptive Control**

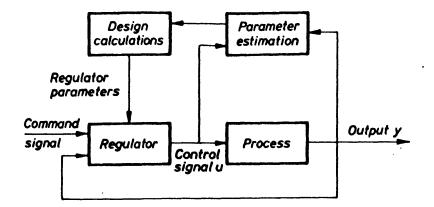

Uncertainties in modeling and circuit parameters motivate the implementation of adaptive control. An adaptive controller has the ability to "redesign" or adjust its control characteristics based on measured or estimated system parameters. Regulators that employ such methods to automatically adapt to variations in system parameters are also known as self-tuning regulators (STR). Figure 2-6 shows a block diagram of a self-tuning regulator. An outer loop in the regulator adjusts the parameters of the regulator through estimation and design calculations. The process and a feedback regulator, the PI controller in our application, make up an inner loop which is "adapted" to parameter variations using inputs from the outer loop.

The system at hand provides a good test-bed for parameter estimation and adaptive control techniques. A microprocessor based system has the ability to carry out the complex computations necessary, and uncertainty in the circuit parameters of the power supply provides a problem to tackle.

The gain block with gain value  $\frac{C}{T_L V^2}$  in Figure 2-2 provides several circuit parameters of which our knowledge is not necessarily perfect. The value of  $T_L$  depends on whether the input frequency is 50Hz or 60Hz. Adapting to variations in input frequency requires detection of the zero-crossings of the input waveform and is not

Figure 2-6: A self-tuning regulator [10].

implemented here. V, the peak input voltage, depends on whether the input is supposed to be 110voltsrms or 220voltsrms. It may also change during operation. To correct for perturbations due to disturbances in the input voltage, a DC filter is used to estimate the peak input voltage and use the updated value in place of the original estimate. This is the path shown as a dashed line in Figure 1-2. A more difficult problem is responding to changes in the value of the load capacitance. The design and implementation of a self-tuning controller which responds to variations in output capacitance are presented in Chapter 5.

#### **Bang-Bang Control**

Components in the power supply are rated for operation below certain peak values of voltage and current. For this reason, it may be necessary to apply an automatic shutoff of the system if the PI controller allows the output voltage or other variables to reach these limits for certain unlikely but possible disturbances. There may also be a specification on the lower bound the voltage is permitted to reach. A slow but robust controller may behave optimally in dealing with common disturbances but would allow excursions outside this allowed band for some extreme operating conditions.

One way to deal with this problem is to have different controllers for the different situations. A linear controller, such as the PI controller discussed earlier, may be designed and optimized for one range of voltages around the nominal operating point. A second controller detects if the circuit variables are near their specified limits and applies more extreme commands to bring them back within the safe range of operation. A controller that switches back and forth between two control commands in this manner is known as a bang-bang or an on-off controller. [19] discusses a similar a similar idea.

In a digital implementation of a controller such as the one at hand, quantization error may be a problem in the steady state, and is usually a function of the gains of the feedback loop. While reducing these gains will reduce the effects of quantization, it may result in a regulator that fails to meet the specifications of the system. An on-off controller could then be used to insure that these specifications ar met. A more detailed analysis requires more knowledge of the implementation and the system limitations, and is presented later.

#### **Band Control**

Another application of the division of the regions of operation among different controllers for optimal results should be helpful in dealing with quantization error in the digital implementation. Increasing the resolution on the input to the controller and reducing its gains can bring the control quantization error to within tolerable levels for normal operation. With the inclusion of adaptive control, in this case capacitance estimation and self-tuning based on the estimated capacitance value, measurement of the output voltage ripple is required. This ripple may be very low in amplitude, close to the size of the error due to quantization of the control. For such a measurement, therefore, it will be necessary to eliminate quantization noise, at least for the time of the measurement.

To achieve cancellation of quantization noise, the controller command cannot be allowed to fluctuate. This fluctuation is inherent in the digital implementation of the controller, however, and may only be eliminated by disabling the PI controller for some time while the output voltage is in (or near) the steady state. The general algorithm for this scheme involves averaging the control command within a certain distance from the steady-state and using the average value while measurement of the output ripple is being carried out. The converter isrunning open-loop in this regime, and care has to be taken to close the loop if significant deviation from the steady state is detected. The result is that within the band of  $\pm \epsilon$ , the voltage is allowed to settle to any value. If  $\epsilon$  is small enough, the error is insignificant, and a reasonable resolution on the AD converter and the output port should make such a value feasible. Of course, the transient response is no longer the same for certain load disturbances. The details of this algorithm and results are also discussed later.

Figure 2-7: Regulator with antiwindup

### 2.2.4 Integrator Windup and Startup Behavior

In the actual UPF system, there are upper and lower limits on the input current that the feedback controller can command. For certain load disturbances and controller gains, these limits may be reached. When that happens, the input current will saturate at its limit, regardless of how far beyond the limit the controller commands it to be. The feedback path is effectively broken. In a regulator that utilizes integral action, this results in integrator windup [10].

When the feedback path is broken, the integrator is left unconnected to the rest of the system except through its input, which is the error in this case. Being an unstable system, it may integrate to a very large value. When the error is finally reduced to the desired level, the integral may be so large that it takes considerable time until it assumes a normal value again, so the commanded current will remain stuck at its limit far longer than it should for proper recovery. One way to avoid integrator windup is through an additional feedback path that sends the error between the actual and desirable commanded currents back to the integrator through an appropriate gain, as shown in Figure 2-7. The error between the commanded and the actual currents is zero when the current is not saturated.

A more easily implemented solution is to completely isolate the integrator when the current is saturated. The integral action is disabled, and the value in the integrator is held until the current is no longer saturated.

Significant windup effects are witnessed in the UPF system simulations only during the startup transient. The load transients did not produce enough of a voltage disturbance to cause the integrator to wind up. Another problem with the startup

Figure 2-8: Startup with integrator windup and no soft-start.

transient is the shape of the current, which shoots to the saturation level due to the large error detected. This problem is dealt with using a soft-startup routine. The reference voltage is initialized to a lower voltage than the desired one. It is then stepped up to the final value over a few cycles, during which the current level rises slowly as it raises the output voltage level to the reference. Figure 2-8 demonstrates the effect of integrator windup and the sharp current transient during startup. The implementation of a soft-startup routine and an anti-windup scheme are discussed in Chapter 3.

# 2.2.5 Overall Design

Combining the PI controller, the adaptive controller for estimating and adjusting to the capacitance, the bang-bang controller, the "band" controller, and the anti-windup mechanism, the system in Figure 2-9 is obtained.

The combination of several features and control loops complicates the design be-

Figure 2-9: Overall controller design.

yond the basic PI controller. However, with a fairly cheap digital implementation, the inclusion of even more features is possible, as will be demonstrated in the next chapter.

.

,

# Chapter 3

# Implementation

A digital implementation of the controller can add to the robustness of the system by allowing a more complex and flexible design, and a highly repeatable implementation. The disadvantages, however, are higher cost, and performance degradation due to sampling and quantization [6]. In the following sections, the various hardware and software components used to implement different sections of the layout in Figures 1-2 and 2-9 are presented. The implementation discussed here excludes the adaptive control section. A general description of the development system is given, with reference to the system manuals for more details. Use of the relevant components in this specific application is then illustrated. Implementation circuits are mentioned by function and illustrated by block diagrams. The algorithms used are presented and the methods used to arrive at the design parameters are discussed. Calculations with actual values and circuit diagrams are reserved for the appendices, however.

# **3.1** Hardware Implementation

Hardware is needed to replace every component in Figure 1-2. Digital hardware is used for implementing the voltage-loop controller. The current-loop controller is implemented in analog hardware and interfaced to the boost converter. Interfacing between the digital hardware and the rest of the circuit requires some extra miscellaneous hardware as well. The implementation of these circuits is discussed below, and their construction method briefly outlined.

# 3.1.1 Digital Voltage-Loop Controller

The voltage-loop controller in 1-2 is to be implemented digitally. From the system model and control design described in Chapter 2, the output of this loop only changes

once every  $T_L$  seconds. This low-speed loop naturally lends itself to a digital implementation that is not too expensive. To implement the current-loop controller on a microprocessor would require more expensive technology. Moreover, the digital implementation of the voltage-loop controller provides most of the flexibility and robustness that one could hope to achieve in this system. The extra cost required to include the current loop controller on the microprocessor is not warranted presently.

The ROMless 16-bit 80C196KB was chosen as the microprocessor for the application. Much less expensive than 32-bit microprocessors and DSP chips, this embedded microcontroller provides ample processing power for the system at hand. A straightforward implementation of the PI controller discussed above actually should not require even as sophisticated or expensive a microprocessor as the 80C196KB. However, the difficulties and complications in design due to quantization may cause a simpler microprocessor to end up requiring a considerably more complex implementation. Moreover, to achieve high levels of performance and to explore the various control schemes and features made possible by operating in the digital domain, a reasonably powerful microprocessor is required.

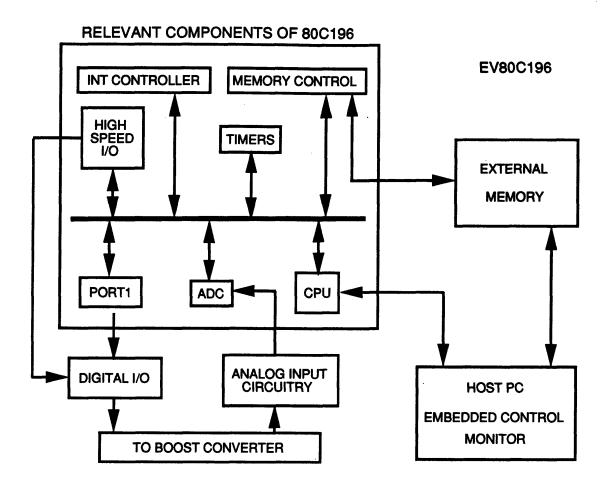

The EV80C196KB software evaluation tool for the 80C196KB microcontroller allows control and monitoring of the processor through an Embedded Controller Monitor (ECM) that supports basic debug facilities in the target system [12]. The ECM is broken into two programs, one executing in the EV80C196KB and the other in an IBM PC compatible. They communicate via an asynchronous serial channel to allow the downloading of microcontroller programs, execution of these programs, and monitoring the various processor states as the programs execute. The 80C196KB has a 16-bit CPU and 232 bytes of on-chip RAM. It is a register-to-register machine, so no accumulator is needed, and most operations can be directly performed from or to any of the registers. In addition, there are many peripherals that are directly controlled through register operations. Figure 3-1 illustrates the features of the evaluation board and the microprocessor necessary in the application. Details of this system and other features of the 80C196KB and the EV80C196KB are found in [13] and [12].

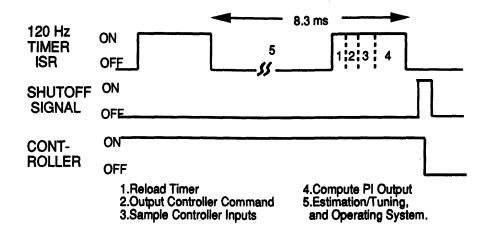

#### **Interrupt Handling**

In a digital control system, some tasks such as sampling and output generation need to be synchronized to specific points in time. Others are event generated, such as shutdown or other precautionary measures taken when a certain condition is detected. Still other tasks, such as system operation services or computations carried out during time gaps free of other processing tasks, have no time restriction. For such a system, an interrupt oriented software structure is the best choice. In the UPF controller setup, the sampling and control output need to be carried out at specific points in time (8.33 ms apart). System shut-off, whether user generated or due to failure, is

Figure 3-1: The digital development system.

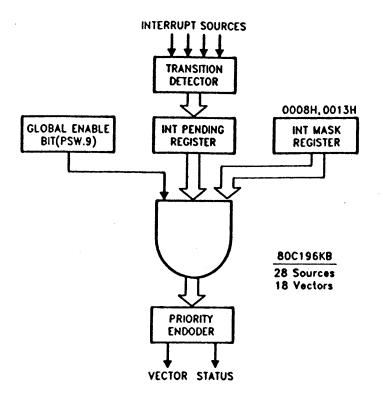

event-generated, and fine tuning of the system over several control cycles may be accomplished through estimation of circuit parameters to be computed over some time, whenever the processor is free. The event-generated tasks are carried out when an event occurs, and the time specific tasks are executed when timers on the microcontroller expire or reach a specified value. These events and timers generate interrupts, with the event-generated interrupts in this case having the higher priority. When an interrupt is generated, the CPU transfers control to the interrupt service routine (ISR) associated with the detected interrupt, as instructed by an interrupt vector. Tasks that have no timing constraints are not executed within an ISR and therefore have the lowest priority. On the 80C196KB, special function registers (SFR) and other devices handle interrupt generation, as shown in Figure 3-2.

#### The A/D Converter

The 80C196KB has an analog to digital (A/D) converter system on board. The system has an 8-channel multiplexer to allow the sampling of 8 different analog signals at

Figure 3-2: The 80C196 interrupt structure [13].

different times. The output of the multiplexer is passed through a sample and hold and then a 10-bit successive-approximation A/D converter. On the 12MHz version of the microprocessor, a conversion is completed in approximately  $26\mu s$ . As is the case with other peripherals, the A/D converter is SFR controlled. In this application, an A/D sample is acquired by writing a value to an SFR that specifies the channel to be sampled and initiates the acquistion. When the conversion is complete, an interrupt is generated. The results of the conversion (the value sampled and the number of the source channel) are found in other SFR's. This process is outlined below:

- 1. Conversions are started by loading the AD\_COMMAND register with the channel number and setting the GO bit to one to initiate conversion immediately.

- 2. The AD\_RESULT\_HI register contains the 8 most significant bits of the conversion result.

- 3. The 2 least significant bits are acquired from the AD\_RESULT\_LO rgister. This SFR is also contains information on which channel has just completed a conversion. This information is necessary as the UPF application requires the use of more than one channel.

The A/D converter generates an interrupt when conversion is completed. This method of detection is chosen over the possible polling of a status bit in AD\_RESULT\_LO, in

accordance with the interrupt driven software structure of the whole system.

#### Timers

There are two timers on the 80C196KB. Timer1 is a 16-bit free-running timer incremented every 16 clock cycles, giving it a timing resolution of  $1.33\mu s$ . Timer2 is clocked externally through an input pin. Four "software timers" may be implemented using the high speed output unit (HSO) in conjunction with one of these timers. This is accomplished by programming the HSO to generate interrupts at preset times. As each programmed time is reached by the specified timer, a Software Timer Interrupt is optionally generated. The timing of the digital controller implemented here is accomplished by writing to SFR's specifying Timer1 as the source of timing and enabling the Software Timer Interrupt. When the interrupt is generated, time-specific tasks are carried out. The source of the interrupt is identified from the contents of another register. This information is necessary when using more than one software timer (e.g. to implement a digital filter during testing, or for adaptive control which uses much faster sampling to estimate circuit parameters). The steps below describe this implementation:

- 1. The HSO\_COMMAND register is loaded with the number of the software timer to be initiated. Timer1 is specified and the Software Timer Interrupt is enabled also as part of the byte written to the HSO\_COMMAND register.

- 2. The HSO\_TIME register is loaded with the sum of the current value of Timer1 and another number. Timer1 will then increment once every 16 clock cycles until it reaches the number loaded into the HSO\_TIME register, at which time it will generate a software interrupt.

- 3. The I/O status register 1 (IOS1) contains information on which software timer expired. In our application this information is necessary when using more than one software timer (e.g.. to implement a digital filter during testing and for adaptive control, which uses much faster sampling to estimate circuit parameters).

#### **Output Ports**

Ports 3 and 4 on the 80C196KB are output ports. On the EV80C196, however, these ports are used for memory access, and may not be used for output without off-board latches and decoding [12]. Port 1 and two pins on Port 2 are "quasi-bidirectional", and may be used as output pins [13]. In our implementation, the 8 lines on Port 1 are used for the output, as it turns out that 8 bits provide sufficient resolution. However, it should be noted that in an application not constrained by the evaluation

board's use of resources, higher output resolution may be achieved, and control of more than one system on the same microcontroller is feasible. The output mechanism is discussed further in the next section.

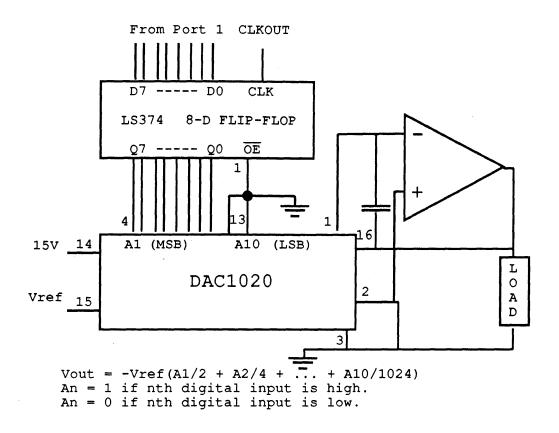

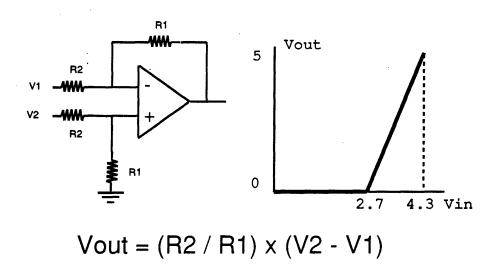

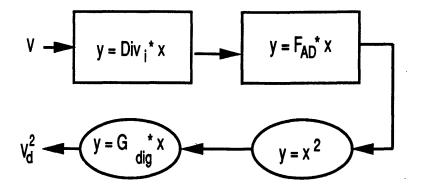

# **3.1.2** D/A Conversion

The output of the digital voltage-loop controller needs to be fed to the current-loop controller as an analog signal. A natural implementation of the system computes the commanded current  $i_P$  in Figure 1-2 inside the microprocessor and then converts it to an analog signal to send to the current loop controller. This requires, in addition to computing k[n], that the input waveform be sampled and reconstructed to provide the correct sinusoidal shape on the controller output. This extra sampling and processing is demanding in terms of microcontroller power and time. A better method utilizes a multiplying digital-to-analog converter (multiplying DAC). A multiplying DAC outputs a certain function of a digital and an analog input, usually a product. It is used to replace the multiplier in Figure 1-2 with inputs k[n] and  $v_{in}(t)$ . Figure 3-3 illustrates the multiplying DAC in the implemented circuit configuration.