### Universidad Carlos III de Madrid

**Bachelor Thesis**

**Biomedical Engineering**

Design of Operational Amplifiers with Feedforward multistage architecture in CMOS low voltage technology for biomedical instrumetation applications.

> Author: Macarena Castillo Fabregat Tutor: Enrique Prefasi Sen

> > Leganés, June 2015

# **Index of Contents**

| 1. Introduction                                                                     |    |

|-------------------------------------------------------------------------------------|----|

| 1.1 Objectives                                                                      | 7  |

| 1.2 Motivation                                                                      |    |

| 1.3 Presenting the problem                                                          | 8  |

| 1.4 Planning                                                                        | 9  |

| 1.5 Regulatory frame                                                                | 10 |

| 2. Design of an operational amplifier                                               | 11 |

| 2.1 State of the art                                                                | 11 |

| 2.1.1 Single Stage Operational Amplifier Realization                                | 11 |

| 2.1.2 Two Stage Miller Compensated Operational Amplifier                            | 14 |

| 2.1.3 Two Stage Operational Amplifier with Right Half Plane Zero Cancellation       | 21 |

| 2.1.4 Nested Miller Three Stage Operational Amplifier                               | 24 |

| 2.1.5 Two Stage Feedforward Compensated Operational Amplifier                       | 25 |

| 2.1.6 Three Stage Feedforward Compensated Operational Amplifier                     | 27 |

| 2.2 Operational Amplifier Design                                                    | 29 |

| 2.3 Alternative designs                                                             | 35 |

| 2.3.1 Two Stage Miller Compensated Operational Amplifier                            | 35 |

| 2.3.2 Two Stage Miller Compensated Operational Amplifier with Right Half Plane Zero |    |

| Cancellation                                                                        | 37 |

| 2.3.3 Nested Miller Three Stage Operational Amplifier                               | 38 |

| 2.3.4 Two Stage Feedforward Compensated Operational Amplifier                       | 39 |

| 3. Operational amplifier for integration                                            | 41 |

| 3.1 Design of the model                                                             | 41 |

| 3.2 Simulations                                                                     | 44 |

| 4. Integrating the integrator in a Sigma Delta Band Pass circuit                    | 48 |

| 4.1 Model design                                                                    | 48 |

| 4.2 Simulations                                                                     | 51 |

| 5. Conclusion                                                                       | 58 |

| 5.1 Concluding remarks                                                              | 58 |

| 5.2 Future work                                                                     | 59 |

| 5.3 Social and economic background                                                  | 59 |

# Index of Equations

| Equation 2.1-1Voltage through a capacitor                                                            | 11  |

|------------------------------------------------------------------------------------------------------|-----|

| Equation 2.1-2: Current through an inductor                                                          | 11  |

| Equation 2.1-3: Ideal integrator output voltage                                                      | 12  |

| Equation 2.1-4: Unity Gain Frequency of a real integrator                                            | 14  |

| Equation 2.1-5: Transfer function of a real integrator                                               | 14  |

| Equation 2.1-6:: Two Stage Miller compensated Operational amplifier transfer function                | 16  |

| Equation 2.1-7: DC gain of Two Stage Miller Compensated Operational Amplifier                        | 17  |

| Equation 2.1-8: Zero of Two Stage Miller Compensated Operational Amplifier                           | 17  |

| Equation 2.1-9: Solution to a quadratic equation                                                     | 17  |

| Equation 2.1-10: Solution to a quadratic equation, in terms of the poles of the transfer             | 17  |

| function                                                                                             | 17  |

| Equation 2.1-11: Approximation to find the first pole                                                | 17  |

| Equation 2.1-12: Approximation to find the second pole                                               | 17  |

| Equation 2.1-13: Value of the poles                                                                  | 17  |

| Equation 2.1-14: Scaling of the poles                                                                | 18  |

| Equation 2.1-15: DC gain of single stage operational amplifier with external load                    | 19  |

| Equation 2.1-16: DC Gain of two stage Miller compensated operational amplifier with<br>external load | 19  |

| Equation 2.1-17: Transfer function of a two stage Miller compensated operational amplif              |     |

|                                                                                                      | 20  |

| Equation 2.1-18: Phase response at unity gain frequency of a two stage Miller compensat              | ed  |

| operational amplifier                                                                                | 20  |

| Equation 2.1-19: Phase margin of a two stage Miller compensated operational amplifier                | 20  |

| Equation 2.1-20:Transfer function of the circuit                                                     | 21  |

| Equation 2.1-21Extra voltage needed to eliminate the zero                                            | 22  |

| Equation 2.1-22: Value of resistor to eliminate the zero                                             | 22  |

| Equation 2.1-23: Output voltage with effective zero elimination                                      | 23  |

| Equation 2.1-24: Value of the zero in the presence of a resistor                                     | 23  |

| Equation 2.1-25 Transfer function of two stage Miller with right half plane zero cancellat           | ion |

|                                                                                                      | 23  |

| Equation 2.1-26:DC gain of nested Miller three stage operational amplifier                           | 24  |

| Equation 2.1-27: Condition for nested Miller three stage operational amplifier to integra            |     |

| Equation 2.1-28: DC gain of two stage feedforward compensated operational amplifier                  | 26  |

| Equation 2.1-29: Transfer function of two stage feedforward compensated opensated                    |     |

| operational amplifier                                                                                | 26  |

| Equation 2.1-30: Value of the poles and zero for two stage feedforward compensated                   |     |

| operational amplifier                                                                                | 26  |

| Equation 2.1-31: Simplified expression for two stage feedforward compensated operatio                |     |

| amplifier transfer function                                                                          | 27  |

| Equation 2.1-32: Condition for stability                                                             | 27  |

| Equation 2.1-33:Transfer function of three stage feedforward compensated operational amplifier       | 28  |

| Equation 2.1-34: DC gain of three stage feedforward compensated operational amplifier                | 28  |

| Equation 2.1-35: Values of the poles for three stage feedforward compensated operation               |     |

| amplifier                                                                                            | 28  |

| Equation 2.1-36: Quadratic equation to find the values of the zeroes                                 | 28  |

| Equation 2.1-37: Values of the coefficients of the quadratic equation                                | 28  |

| Equation 2.1-38: Simplified expression of the transfer function of a three stage feedforwa           |     |

| compensated operational amplifier                                                                    | 29  |

| Equation 2.2-1DC gain for a three stage feedforward operational amplifier                            | 30  |

| Equation 2.2-2: Nyquist theorem                                                                      | 31  |

| Equation 2.2-3: Transfer function of three stage feedforward compensated operational                 |     |

| amplifier                                                                                            | 32  |

| Equation 2.2-4: DC gain at each stage of model 2                                                     | 33  |

| Equation 2.2-5: DC gain of model 3                                                                   | 34  |

| Equation 2.3-1: DC gain of two stage Miller compensated operational amplifier           | 35 |

|-----------------------------------------------------------------------------------------|----|

| Equation 2.3-2: Transfer function of two stage Miller compensated system                | 36 |

| Equation 2.3-3: Condition for left half plane zero                                      | 37 |

| Equation 2.3-4: Transfer function of two stage feedforward compensated operational      |    |

| amplifier                                                                               | 39 |

| Equation 2.3-5: DC gain of two stage feedforward compensated operational amplifier      | 39 |

| Equation 2.3-6: poles of the two stage feedforward compensated operational amplifier    | 39 |

| Equation 2.3-7: Zero of the two stage feedforward compensated operational amplifier     | 39 |

| Equation 2.3-8: Simplified transfer function of two stage feedforward compensated       |    |

| operational amplifier                                                                   | 39 |

| Equation 3.1-1:Equivalent impedance at operational amplifier entrance                   | 42 |

| Equation 3.1-2: Voltage entering through the operational amplifier                      | 42 |

| Equation 3.1-3: Transfer function of voltage entering through the operational amplifier | 42 |

| Equation 3.1-4: Equivalent resistance at the output of the operational amplifier        | 42 |

| Equation 3.1-5: Transfer function at the output of the operational amplifier            | 42 |

| Equation 3.1-6: Impedance of a capacitor                                                | 43 |

| Equation 3.1-7: Simulink box equivalent to capacitor impedance                          | 43 |

| Equation 3.1-8: Unity gain frequency of an ideal itegrator                              | 43 |

| Equation 3.1-9: Cut off frequency of a real integrator                                  | 44 |

| Equation 3.2-1: Unity gain frequency of the system                                      | 45 |

| Equation 4.2-1Calculation of capacitor value                                            | 51 |

| _                                                                                       |    |

# Index of Figures

| Figure 2.1-1: Ideal integrator                                                            | 12 |

|-------------------------------------------------------------------------------------------|----|

| Figure 2.1-2: Real integrator                                                             | 12 |

| Figure 2.1-3: Ideal integrator Bode plot                                                  | 13 |

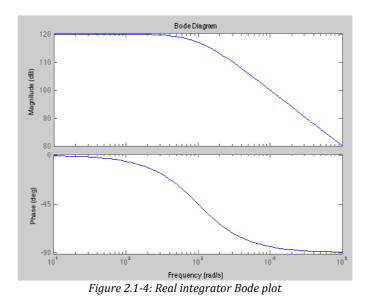

| Figure 2.1-4: Real integrator Bode plot                                                   | 13 |

| Figure 2.1-5: External load in parallel with resistor                                     | 15 |

| Figure 2.1-6: Circuit to deal with the presence of al external load                       | 15 |

| Figure 2.1-7: Two Stage Miller Compensated Operational Amplifier                          | 16 |

| Figure 2.1-8: Single stage operational amplifier with external load                       | 19 |

| Figure 2.1-9: Two stage Miller compensated operational amplifier with external load       | 19 |

| Figure 2.1-10:Circuit under study                                                         | 22 |

| Figure 2.1-11 : Circuit configuration to eliminate the zero                               | 22 |

| Figure 2.1-12: Two stage Miller with right half plane zero cancellation circuit           | 23 |

| Figure 2.1-13Nested Miller three stage operational amplifier                              | 24 |

| Figure 2.1-14: Two stage feedforward compensated operational amplifier                    | 25 |

| Figure 2.1-15Three stage feedforward compensated operational amplifier                    | 27 |

| Figure 2.2-1:Simulink model of a three stage feedforward compensated operational          |    |

| amplifier                                                                                 | 31 |

| Figure 2.2-2: Bode plot of three stage feedforward model                                  | 32 |

| Figure 2.2-3: Simulink model 2 of three stage feedforward compensated operational         |    |

| amplifier                                                                                 | 32 |

| Figure 2.2-4: Bode plot of three stage feedforward model 2                                | 33 |

| Figure 2.2-5: Simulink model 3 of three stage feedforward operational amplifier           | 34 |

| Figure 2.2-6: Bode plot of model 3 three stage feedforward system                         | 35 |

| Figure 2.3-1: Simulink model of two stage Miller compensated operational amplifier        | 36 |

| Figure 2.3-2: Bode plot of two stage Miller compensated model                             | 36 |

| Figure 2.3-3: Simulink model for two stage Miller compensated system with right half plan | ıe |

| zero cancellation                                                                         | 37 |

| Figure 2.3-4: Bode plot of two stage Miller compensated model with right half plane zero  |    |

| cancellation                                                                              | 38 |

| Figure 2.3-5: Simulink model of two stage feedforward system                              | 39 |

| Figure 2.3-6: Bode plot of thw two stage feedforward model                                | 40 |

| Figure 3.1-1: Ideal operational amplifier in integrating configuration                    | 41 |

| Figure 3.1-2: Small signal model of operational amplifier                                 | 41 |

| Figure 3.1-3: Simulink model of operational amplifier in integrating configuration        | 43 |

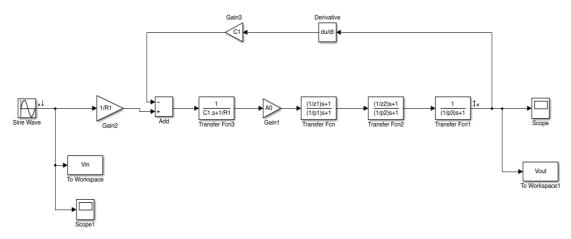

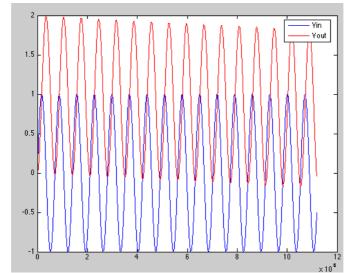

| Figure 3.2-1: Simulation of the real integrator model with the specified parameters       | 45 |

| Figure 3.2-2: Simulation 2 of the real integrator                                         | 45 |

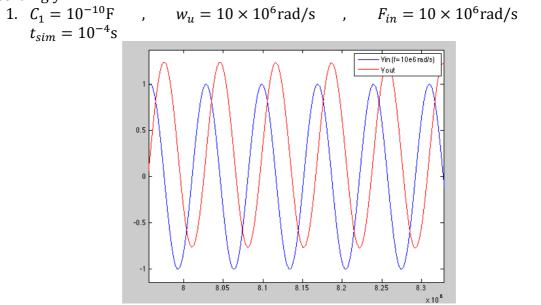

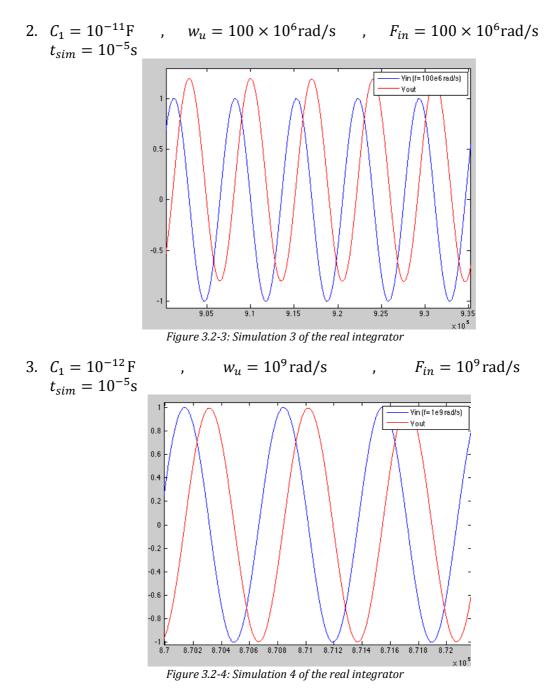

| Figure 3.2-3: Simulation 3 of the real integrator                                         | 46 |

| Figure 3.2-4: Simulation 4 of the real integrator                                         | 46 |

| Figure 3.2-5: Simulation 5 of the real integrator                                         | 47 |

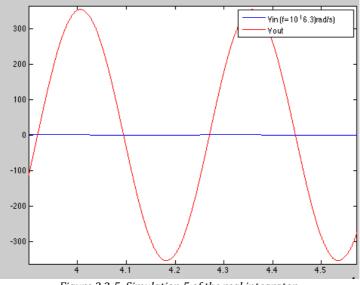

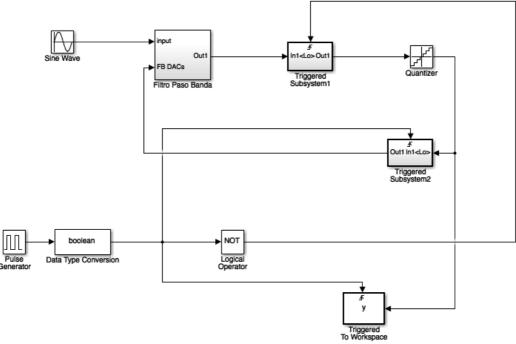

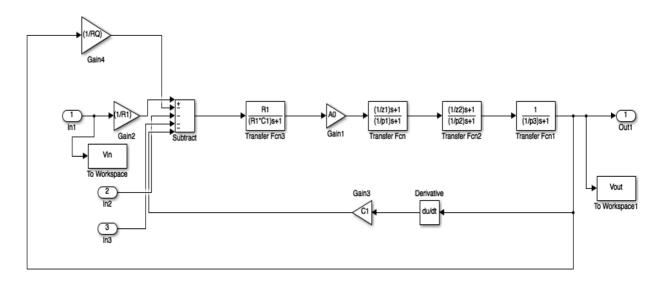

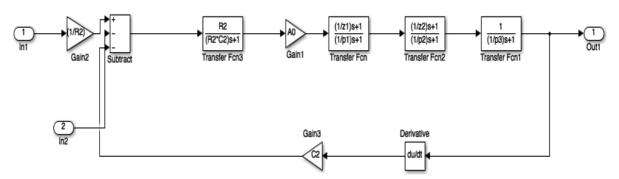

| Figure 0-1: Sigma Delta second order Band Pass Simulink model                             | 49 |

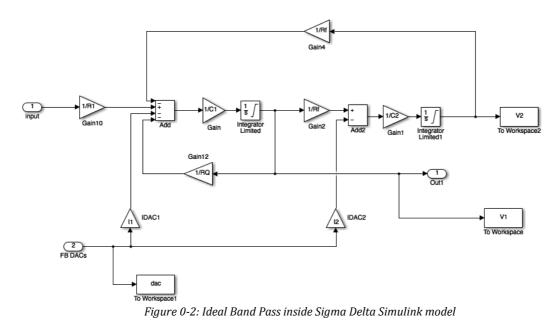

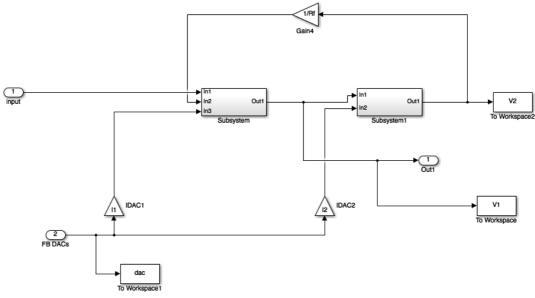

| Figure 0-2: Ideal Band Pass inside Sigma Delta Simulink model                             | 49 |

| Figure 0-3: Real band pass Sigma Delta Simulink Model                                     | 50 |

| Figure 0-4: Simulink model of first real integrator belonging to Sigma Delta              | 50 |

| Figure 0-5: Simulink model of second real integrator belonging to Sigma Delta             | 51 |

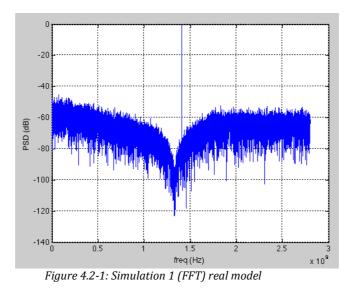

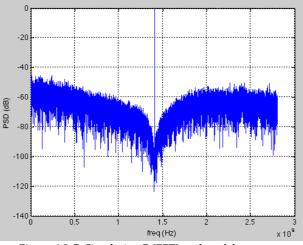

| Figure 4.2-1: Simulation 1 (FFT) real model                                               | 52 |

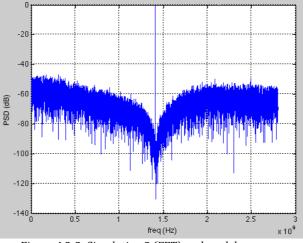

| Figure 4.2-2: Simulation 2 (FFT) real model                                               | 52 |

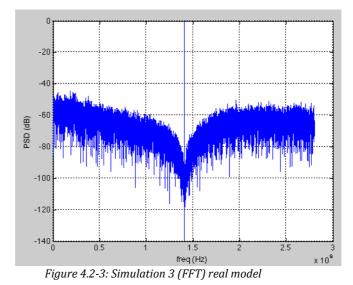

| Figure 4.2-3: Simulation 3 (FFT) real model                                               | 53 |

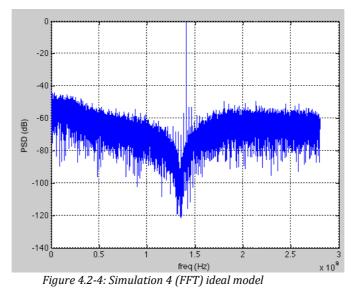

| Figure 4.2-4: Simulation 4 (FFT) ideal model                                              | 53 |

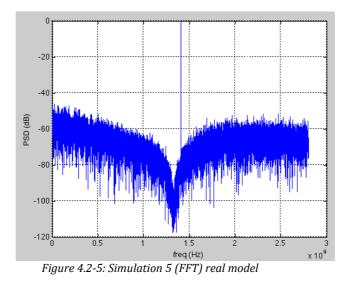

| Figure 4.2-5: Simulation 5 (FFT) real model                                               | 54 |

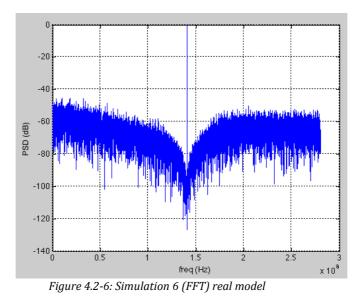

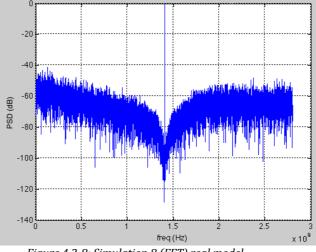

| Figure 4.2-6: Simulation 6 (FFT) real model                                               | 55 |

| Figure 4.2-7: Simulation 7 (FFT) real model                                               | 55 |

| Figure 4.2-8: Simulation 8 (FFT) real model                                               | 56 |

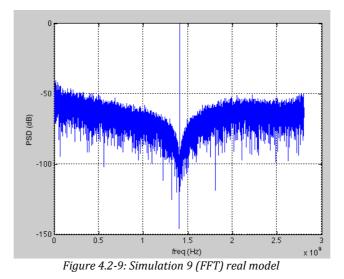

| Figure 4.2-9: Simulation 9 (FFT) real model                                               | 57 |

## **Index of Tables**

| Table 1.4-1:Planning                                                                       | 9   |

|--------------------------------------------------------------------------------------------|-----|

| Table 2.1-1: Comparison between real and ideal integrator output voltage                   | 12  |

| Table 2.1-2:Comparison of the poles in the absence and presence of a feedback capacitor    | 18  |

| Table 2.1-3: Comparison of the DC gains of single stage and two stage Miller operational   |     |

| amplifiers                                                                                 | 19  |

| Table 2.1-4: Comparison of the values of the poles originally and after the assumptions    | 21  |

| Table 2.1-5:Change in the value of the zero depending on the value of the resistor         | 24  |

| Table 2.2-1: Poles and Zeros for the Bode plot                                             | 29  |

| Table 2.2-2Values for the variables of the three stage feedforward model                   | 31  |

| Table 2.2-3: Values of the variables for model 2                                           | 33  |

| Table 2.2-4: Values of the variables for model 3 of three stage feedforward system         | 34  |

| Table 2.3-1: Values of the variables for two stage Miller compensated system               | 36  |

| Table 2.3-2: Values of the variables for two stage miller compensated model with right hal | lf  |

| plane zero cancellation                                                                    | 38  |

| Table 2.3-3: Values of the variables for the two stage feedforward model                   | 40  |

| Table 3.2-1:Values of the variables for the real integrator model                          | 44  |

| Table 4.2-1: Values of poles and zeroes for an operational amplifier with reduced bandwic  | dth |

|                                                                                            | 56  |

### **1** Introduction

Magnetic Resonance (MRI) is an imaging technique used to obtain anatomical and structural features of a patient's body. The creation of a measurable signal is based on the varying water concentration throughout the body. The atoms which participate actively in such event are the hydrogen atoms from water, which create a varying magnetic field in response to a radiofrequency pulse. Such radiofrequency pulse is applied perpendicular to a main magnetic field created by a gradient coil, which is in charge of aligning the magnetic moments of hydrogen atoms. Upon application of the radiofrequency pulse, magnetic moments of hydrogen atoms rotate  $90^{\circ}$  with respect to the main field, creating a varying magnetic field which can be converted into a current through the use of coils.

The detection of such current is achieved through the use of sensors, and constitutes a crucial step for the creation of an image based on the information emanating from the magnetic resonance equipment. Bearing in mind that a 1.5 Tesla MRI contains around 80 sensing components, the key element in MRI is the data acquisition block which forms part of each individual sensor. This data acquisition block contains a sensor, a band pass filter, and a band pass Analog to Digital Converter (ADC). From these three elements, the one in charge of the final resolution so that the digital part can appropriately process each sensor's information is the ADC. Therefore, the accuracy of the ADC's performance influences image processing steps to be performed afterwards for the final creation of an image.

An Analog to Digital Converter can be built in several ways, either through a subsampling pipeline or band pass Sigma Delta. In both cases, the key elements which influence the resolution of the ADC are the operational amplifiers with which they are built up. Subsampling pipelines make use of operational amplifiers in order to sample the input signal in successive steps, whereas band pass Sigma Delta circuits use them to filter the quantification noise around a specified frequency.

The ADC which will be used for the purpose of this work is a band pass Sigma Delta modulator whose bandwidth and center frequency are respectively 1MHz and 140MHz. The main objective of this work is to build a model of a real operational amplifier to be used in the filter of the ADC.

#### 1.1 Objectives

The objectives of this work are divided as follows:

- 1. <u>Design of an operational amplifier model</u>. The design is focused on achieving a pre-defined Bode plot, and hence the objective is to create an operational amplifier which gives a magnitude and frequency response as close as possible to the Bode to be obtained.

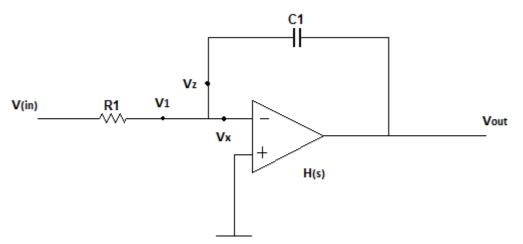

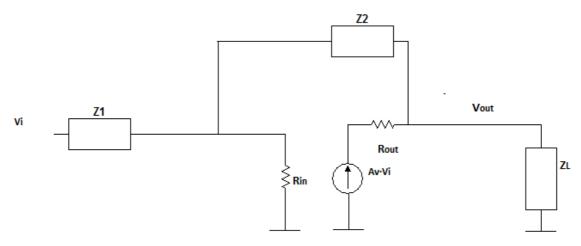

- 2. <u>Arranging the designed operational amplifier in an integrating configuration</u>. The objective is to obtain a "low frequency response" corresponding to that of an ideal integrator circuit and a "high frequency response" corresponding to the real pre-designed operational amplifier.

- 3. <u>Integrating the operational amplifier with the integrator configuration in a</u> <u>Sigma Delta Band Pass modulator model</u>. Such model contains among other elements, a band pass filter formed by two cascaded integrators. The

objective is to obtain a Sigma Delta modulator model which gives a "real" response due to the pre-designed operational amplifiers, and not an "ideal" one. Therefore, this third objective consists on introducing the operational amplifier model, arranged in negative feedback with a capacitor to provide the integrating function into another Simulink model of a Sigma Delta band pass modulator which was built by a colleague at the Electronics Technology department.

4. <u>Simulation</u> of each of the above mentioned objectives, as well as the entire model to extract the main imperaments such that the analog designer can use them to design the electrical circuit.

#### 1.2 Motivation

Sigma Delta modulators represent a means of obtaining high resolution analog to digital conversion. The removal of quantization noise from the band pass allowed by the system is achieved by two characteristic phenomena of this type of circuits: oversampling and noise shaping. The "tuned" output noise is then digitally low-passed filtered, whereas for the oversampling ratio, it determines the overall resolution of the modulator (in fact, they are linearly proportional). Indeed, Sigma Delta modulators present noticeable advantages due to these two phenomena, the only drawback probably being their limitation in terms of the wideness of the frequency band that they can convert. Increasing the signal band to be digitally converted implies the specific design of the operational amplifiers which are used in integrating configuration by Sigma Delta modulators. [1]

The desire to design a model of an operational amplifier is to be able to simulate a real response of the use of such systems in integrating configuration and ultimately, to use them in a Sigma Delta Band Pass modulator. The creation of a model meeting certain pre-specified criteria will enhance the behavior of the overall system, additionally, simulating a more realistic system by substituting a purely ideal integrator by a real one allows for a precise estimation of the outcome of the circuit it is modelling. The ultimate goal of such real model is to incorporate it in a Sigma Delta Band pass modulator in order to simulate the behavior of the entire system, thereby obtaining a description of the precise behaviour of a system which is going to be implemented in sensing signals produced during the performance of magnetic resonance imaging.

The underlying motivation of the whole procedure is to predict the real performance of the sensing circuit in magnetic resonance. Through the use of the mentioned models, the response provided could be precisely adjusted by tuning the values of the parameters that build up the system.

#### **1.3** Presenting the problem

When trying to improve a given system, the modelling and simulation of such system gives an accurate estimate of the actual behavior of the future system when built up. Data acquisition blocks which build up each of the sensors present in MRI equipment, represent a crucial step for the digitalization of the sensed signal and subsequent processing for the final formation of an image. The fidelity with which the analog to digital conversion is carried out determines the overall resolution of the data acquisition process. A system which presents useful properties in the ADC process is a Sigma Delta band pass modulator, which is composed of operational amplifiers arranged in integrating configuration, the number of which depends on the order of the system.

When modelling a Sigma Delta Band Pass modulator, the two cascaded integrators which build up the system are commonly approximated through the use of

Integrator

Simulink's integrator function:  $\frac{1}{s}$

The problem with such estimation, is that the system is treated as purely ideal, and this does not correspond to the actual, "real" behavior of the system. Furthermore, by creating an operational amplifier which meets a given criteria, the whole "integrator" can present more effective functions in the analog to digital conversion as compared to the ideal model. Hence it is needed to create a model which incorporates the functioning of a real operational amplifier. The resulting model will be manipulated in order to obtain from it the desired magnitude and frequency response. By tuning the parameters which build up the model, different responses will be created for different input frequencies.

The built operational amplifier model, will be arranged in integrating configuration and ultimatelty incorporated in a Sigma Delta band pass modulator in order to be able to simulate the behavior of the Analog to Digital Conversion process with high fidelity and accuracy.

### 1.4 Planning

The mentioned objectives were carried out in the following manner:

| Objective    | January | February | March | April | May | June |

|--------------|---------|----------|-------|-------|-----|------|

| 1.Design of  |         |          |       |       |     |      |

| an           |         |          |       |       |     |      |

| operational  |         |          |       |       |     |      |

| amplifier    |         |          |       |       |     |      |

| model        |         |          |       |       |     |      |

| 2.           |         |          |       |       |     |      |

| Integrator   |         |          |       |       |     |      |

| operational  |         |          |       |       |     |      |

| amplifier    |         |          |       |       |     |      |

| 3.           |         |          |       |       |     |      |

| Integration  |         |          |       |       |     |      |

| in a Sigma   |         |          |       |       |     |      |

| Delta Band   |         |          |       |       |     |      |

| Pass circuit |         |          |       |       |     |      |

| 4.           |         |          |       |       |     |      |

| Simulation   |         |          |       |       |     |      |

|              |         |          |       |       |     |      |

|              |         |          |       |       |     |      |

Table 1.4-1:Planning

#### **1.5 Regulatory frame**

In order to carry out the development of the work mentioned, several regulatory issues had to be taken into account to perform it in a legal manner.

To begin with, the most frequently used program was Simulink, where most of the modelling and simulation procedure was carried out. Simulink is a useful programming tool used frequently for modeling and simulation of dynamic systems, it also allows the analysis of such systems and is tightly integrated with Matlab's environment. This integration between both environments allowed the use of Matlab and Simulink simultaneously for the purpose of declaration of variables, saving data from Simulink models and plotting results. These programs could be used thanks to the license available through the university Carlos III, and hence both the modelling and simulation of the systems was performed at the university through the use of its computers with an installed Matlab software. Particularly, the work was developed at the Electronics Technology department.

Secondly, another program which was useful in the development of the work was Cadence Design Systems. It consists on an electronic design automation (EDA) software which results very useful in the design of integrated circuits. Once again, the license provided by the Univeristy Carlos III lead to the use of Cadence at the university's computers. Although Cadence was not used for the purpose of operational amplifier design, modeling or simulation, it was used by other colleagues at the Electronics department for the design of the Sigma Delta band pass system.

Finally, due to the confidentiality of the work which is carried out by the Electronics Technology department, a non-disclosure agreement (NDA) was signed to ensure the protection of the information shared during the development of the project.

### 2 Design of an operational amplifier

The first objective consists on the design of an operational amplifier model. The characteristics of the circuit were chosen to achieve a pre-defined Bode plot, hence the system was built taking into account the desire to obtain a particular response from it.

#### 2.1 State of the art

Operational Amplifiers play a significant role in circuit design due to their active participation in processes such as data conversion, sensors, filters and many more applications. The evolution of CMOS technology has established a general trend of scaling down dimensions, which have lead to a decrease in supply voltages while transistor threshold voltages are being kept constant. The major consequences of this size reduction trend are the decrease in open loop gain, an increase in transistion frequency (speed of operation), as well as the appearance of random offsets. Subsequently, the vertical cascoding of them in order to obtain high gains is becoming less useful. These facts call out for the need to implement multistage horizontal cascading to achieve low supply voltage implementation of operational amplifiers.[2]

Therefore, the objectives in these technological developments have been primarily focused on enhancing the effectiveness of compensation techniques, achieving appropiate offsets, reducing power cosumption and system dimensions and obviously keeping the noise to a minimum. In order to achieve this multiple systems have been developed.[2]

Single stage operational amplifiers are useful in terms of stability, due to the presence of a single pole. However, these systems present limitations regarding the DC gain that can be obtained with them. It is therefore needed to use higher order systems while at the same time maintaining the phase response of the system at unity gain frequency sufficiently higher than  $-180^{\circ}$ , a procedure which is known as "compensation techniques".[3]

#### 2.1.1 Single Stage Operational Amplifier Realization

The starting point of the discussion obviously begins with a single stage operational amplifier realization. An integrating function is desired for the operational amplifier under study, and the circuit elements which perform integrating functions are capacitors and inductors. The former which integrates current, and the latter, voltage.

Equation 2.1-1Voltage through a capacitor

$$v_c = \frac{1}{C} \int i_c dt$$

Equation 2.1-2: Current through an inductor

$$i_L = \frac{1}{L} \int v_L dt$$

However, in practice, it is easier to fabricate good quality capacitors and hence it will be capacitors the ones used for the purpose of integration.

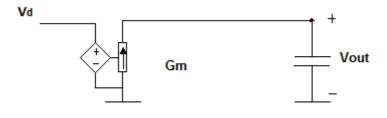

So, in order to obtain the integrating function it is needed to convert the voltage which enters through the amplifier (Vd) to a current, which is achieved through the implementation of the following circuit:

Figure 2.1-1: Ideal integrator

By using a voltage controlled current source (also known as transconductor) with a proportionality constant Gm (also known as transconductance), a current with a value of  $Gm \cdot Vd$  emerges from it. Such output current flows through a capacitor (C), resulting in a voltage which is equal to:

Equation 2.1-3: Ideal integrator output voltage

$$V_{out} = \frac{G_m}{C} \int V_d dt$$

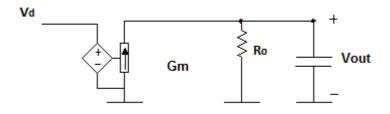

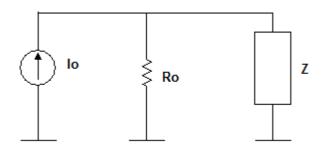

Where the term left outside the integral indicates the unity gain frequency. This is the simplest implementation of an integrating operational amplifier and obviously, an ideal one. However, since a real model is desired several considerations have to be taken into account. First of all, it is impossible to create an ideal current source, they always include an inherent output resistance, giving rise to the following circuit:

Figure 2.1-2: Real integrator

Taking this into account, and applying the Laplace transform to substitute the integrals, the difference between real and ideal circuits regarding their transfer functions is:

Table 2.1-1: Comparison between real and ideal integrator output voltage

IDEAL

$$\frac{V_{out}}{V_d} = \frac{G_m}{sC}$$

REAL

$$\frac{V_{out}}{V_d} = \frac{G_m R_0}{sCR_0 + 1}$$

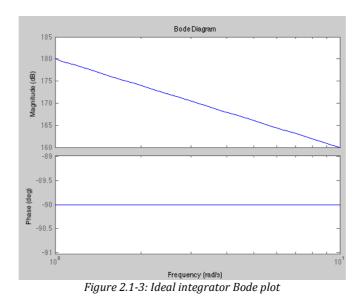

This shows that actually the difference between an ideal situation and a real one lies in the location of the poles. An ideal integrator contains a pole at the origin and a real one experiences a shift of that pole to greater frequencies of the Bode plot. Also, ideally an integrator has infinite DC gain, and a real one has a finite DC gain until the location of the pole, when it starts to integrate.

IDEAL

REAL

The difference between both Bode plots lies in the frequencies which have a value smaller than  $(1/CR_0)$ . Beyond that point, the behaviour is exactly the same. This can be explained by the impedance of the capacitor and ouput resistance; at very

high frequencies, the capacitor presents a higher impedance to the system than the resistance, hence most of the current will be flowing through the capacitor rather than the resistance. Regarding the unity gain frequency of the real system, we see that:

Equation 2.1-4: Unity Gain Frequency of a real integrator

$$\left| \frac{G_m}{jw_u C + \frac{1}{R_0}} \right| = 1$$

$$G_m^2 = w_u^2 C^2 + \frac{1}{R_0^2}$$

$$w_u^2 = \frac{G_m^2}{C^2} - \frac{1}{C^2 R_0^2}$$

This shows that, as long as the second term is small enough, or in other words, as long as  $C^2R_0^2$  is sufficiently large, the unity gain cut-off frequency will be the same for the real and ideal case. This will take place in almost every operational amplifier, because if this condition is broken, it will result in a system which does not work.

Recognizing that the term  $Gm \cdot R_0$  represents the low frequency (or DC) gain of the operational amplifier (A<sub>0</sub>), and taking into account the expression derived for the unity gain frequency (w<sub>u</sub>), the transfer function becomes:

Equation 2.1-5: Transfer function of a real integrator

$$\frac{V_{out}}{V_d} = \frac{A_0}{1 + s\frac{A_0}{W_u}}$$

Due to the presence of  $R_0$ , the DC gain of the operational amplifier is finite. Hoewever, for certain applications it is required that the DC gain be greater than a certain value which is not possible to reach with this basic circuit. Hence, it is needed to use a combination of various amounts of single stage operational amplifiers in different configurations to reach the desired DC gain, without compromising the stability of the system.

To conclude with single stage operational amplifiers, it is important to state that they are stable systems. This can be reasonably explained by using Nyquist plot, but more simply, by noticing that it is a first order system and therefore contains only one pole. Due to the presence of a single negative pole, the minimum phase response that the system can reach is  $-90^{\circ}$  caused by the phase lag contribution at frequencies higher than the pole of the system. [4][5][6][7][8][9][10][11][12][13][14]

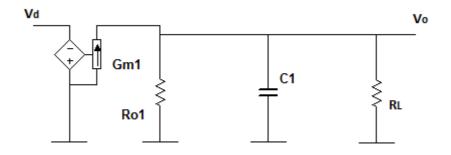

#### 2.1.2 Two Stage Miller Compensated Operational Amplifier

Single stage operational amplifiers present limitations regarding the DC gain that can be obtained with them. This is due to the presence of a finite output resistance emanating from the voltage controlled current source. Additionally, in the presence of external loads, the low frequency gain also becomes limited, since this impedance will be in parallel with the output resistor. The achievement of higher DC gains can be obtained by increasing  $R_0$  although this approach obviously doesn't apply for the case in which another resistor is present. In this case, it becomes necessary to use alternative models.

Two stage Miller compensated operational amplifiers deal with the increase in DC gain in the presence of external loads. This problem stems from the following circuit configuration:

Figure 2.1-5: External load in parallel with resistor

Obviously, the output voltage will not be equal to the product of the current source and the resistor, it must be taken into account that the resistor is in parallel with another load. An effective way to deal with this problem is to place a current controlled voltage source through the use of an operational amplifier which inlcudes the capacitor load in negative feedback configuration.

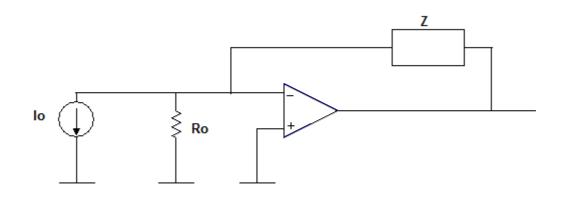

Figure 2.1-6: Circuit to deal with the presence of al external load

Ideally, even in the presence of  $R_0$  the output of this system will be the input current  $I_0$  times the external load. However, it must be taken into account that the operational amplifier is not ideal, and behaves effectively as a voltage controlled current source only in the range of frequencies where the loop gain is big enough. Taking into account that  $I_0$  represents the current resulting from a previous voltage controlled current source, and that the output resistance represents the resistance from such transconductor, the real representation of the above circuit becomes:

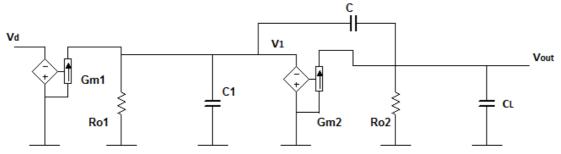

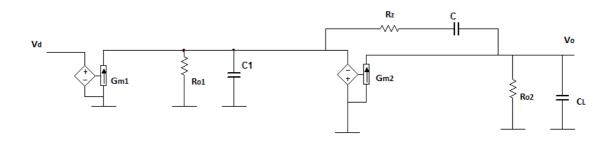

Figure 2.1-7: Two Stage Miller Compensated Operational Amplifier

For simplicity, the transfer function will be calculated in matrix form using the admittance matrix and voltage vector at each node and equating them to the total input current. The system will be solved using Cramer's rule and the reciprocal of resistances will be expressed as G:

Equation 2.1-6:: Two Stage Miller compensated Operational amplifier transfer function

$$\begin{bmatrix} s(C_{1}+C) + \frac{1}{R_{0_{1}}} & -sC \\ G_{m_{2}} - sC & s(C_{L}+C) + \frac{1}{R_{0_{2}}} \end{bmatrix} \begin{bmatrix} V_{1} \\ V_{out} \end{bmatrix} = \begin{bmatrix} -G_{m_{1}}V_{d} \\ 0 \end{bmatrix}$$

$$V_{out} = \frac{\begin{vmatrix} s(C_{1}+C) + \frac{1}{R_{0_{1}}} & -G_{m_{1}}V_{d} \\ G_{m_{2}} - sC & 0 \end{vmatrix}}{|s(C_{1}+C) + \frac{1}{R_{0_{1}}} & -sC \end{vmatrix}$$

$$\begin{cases} s(c_1 + c) + \frac{1}{R_{0_1}} & -sc \\ G_{m_2} - sc & s(c_L + c) + \frac{1}{R_{0_2}} \end{cases}$$

$$V_{out} = \frac{G_{m_1}(G_{m_2} - sC)V_d}{s^2(C_1C + CC_L + C_LC_1 + C^2 - C^2) + s(C(G_{m_2} + G_{0_2} + G_{0_1}) + C_LG_{0_1} + C_1G_{0_2}) + G_{0_1}G_{0_2}}$$

$$\frac{V_{out}}{V_d} = \frac{G_{m_1}(G_{m_2} - sC)}{s^2(C_1C + CC_L + C_LC_1 + C^2 - C^2) + s(C(G_{m_2} + G_{0_2} + G_{0_1}) + C_LG_{0_1} + C_1G_{0_2}) + G_{0_1}G_{0_2}}$$

By inspection one can see that the DC gain of the system is simply equal to the product of the individual DC gains at each stage, as well as for the location of the zero, which can be straightforwardly derived:

Equation 2.1-7: DC gain of Two Stage Miller Compensated Operational Amplifier

$$\frac{V_{out}}{V_d}(s=0) = \frac{G_{m_1}G_{m_2}}{G_{0_1}G_{0_2}}$$

Equation 2.1-8: Zero of Two Stage Miller Compensated Operational Amplifier

$$z = \frac{G_{m_2}}{C}$$

Regarding the poles, the common solution to a quadratic equation will not work due to the complexity of the coefficients a,b and c:

Equation 2.1-9: Solution to a quadratic equation

$$s = \frac{-b \pm \sqrt{b^2 - 4ac}}{2a}$$

and for simplicity, approximate methods will be applied. This approximation is based on the assumption that the difference of the magnitude of the roots is very big (i.e. the poles are very far apart), and consequently that both poles are real, because in the case of having roots which are complex conjugates of each other, their magnitudes will be exactly the same and the assumption does not hold.

Equation 2.1-10: Solution to a quadratic equation, in terms of the poles of the transfer function

$$as_1^2 + bs_1 + c = 0$$

$$as_2^2 + bs_2 + c = 0$$

Assuming  $|s_1| \ll |s_2|$ , the term  $as_1^2$  is negligible compared to the others, hence:

Equation 2.1-11: Approximation to find the first pole

$$bs_1 + c = 0$$

$$s_1 = \frac{-c}{h}$$

As for s<sub>2</sub>, c is negligible compared to the other terms, so:

Equation 2.1-12: Approximation to find the second pole

$$as_2^2 + bs_2 = 0$$

$$s_2 = \frac{-b}{a}$$

Substituting the coefficients, the values of the poles are:

Equation 2.1-13: Value of the poles

$$p_1 = \frac{-G_{0_1}G_{0_2}}{C(G_{m_2} + G_{0_2} + G_{0_1}) + C_LG_{0_1} + C_1G_{0_2}}$$

$$p_2 = \frac{-(C(G_{m_2} + G_{0_2} + G_{0_1}) + C_L G_{0_1} + C_1 G_{0_2})}{C_1 C + C C_L + C_L C_1}$$

For the purpose of comparing these expressions with the poles resulting from a system without the presence of the negative feedback capacitor, the first pole will be divided by  $G_{02}$  (both numerator and denominator) and the second one will be multiplied by  $\frac{1}{C+C_1}$ , giving rise to:

Equation 2.1-14: Scaling of the poles

$$p_{1} = \frac{-G_{0_{1}}}{C\left(\frac{G_{m_{2}}}{G_{0_{2}}} + 1 + \frac{G_{0_{1}}}{G_{0_{2}}}\right) + \frac{C_{L}G_{0_{1}}}{G_{0_{2}}} + C_{1}}}{\frac{-\left(\frac{CG_{m_{2}}}{C + C_{1}} + \frac{G_{0_{1}}(C + C_{L})}{C + C_{1}} + G_{0_{2}}\right)}{\frac{C_{1}C}{C + C_{1}} + C_{L}}}$$

Considering the case where there is no capacitor placed in negative feedback, the transfer function will simply be the multiplication of two cascaded single stage operational amplifiers, whose poles have been previously derived. The comparison of the poles of both systems is:

|       | Without C              | With C                                                                                                    |

|-------|------------------------|-----------------------------------------------------------------------------------------------------------|

| $p_1$ | $\frac{-G_{0_1}}{C_1}$ | $\frac{-G_{0_1}}{(G_{m_1}, G_{0_1}) - G_{1_1}G_{0_1}}$                                                    |

|       | C <sub>1</sub>         | $C\left(\frac{G_{m_2}}{G_{0_2}} + 1 + \frac{G_{0_1}}{G_{0_2}}\right) + \frac{C_L G_{0_1}}{G_{0_2}} + C_1$ |

| $p_2$ | $\frac{-G_{0_2}}{C_L}$ | $-\left(\frac{CG_{m_2}}{C+C_1} + \frac{G_{0_1}(C+C_L)}{C+C_1} + G_{0_2}\right)$                           |

|       |                        | $\frac{C_1C}{C+C_1} + C_L$                                                                                |

Table 2.1-2:Comparison of the poles in the absence and presence of a feedback capacitor

This comparison gives a clear insight into the so-called Miller effect: a capacitor connected in negative feedback presents itself to the input as a much larger value of capacitance than its actual value. This increase is actually a multiple of the gain of the amplifier, and results in a decrease in the lowest pole and and an increase in the highest one. The increase in the highest pole is justified by the fact that the numerator is increasing enormously, since  $G_{m2}$  is generally much bigger than  $G_{02}$ , whereas the denominator is only increasing moderately, hence producing a net increase in the location of the higher pole. The fact that the first pole decreases and the second one increases is known as pole splitting.

Overall, the advantage of implementing this circuit configuration compared to a single stage operational amplifier lies in the value of the DC gain, which is greater for this case than for the previous one:

Table 2.1-3: Comparison of the DC gains of single stage and two stage Miller operational amplifiers

|         | Single stage op amp | Two stage Miller op amp     |

|---------|---------------------|-----------------------------|

| DC gain | $G_m$               | $G_{m_1}G_{m_2}$            |

|         | $\overline{G_0}$    | $\overline{G_{0_1}G_{0_2}}$ |

Another advantage that this configuration presents appears when a resistive load is applied. In this case, the circuits will have the following configuration and DC gains:

#### SINGLE STAGE

Equation 2.1-15: DC gain of single stage operational amplifier with external load

$$G_{DC} = \frac{G_m}{G_{0_1} + G_L}$$

Figure 2.1-8: Single stage operational amplifier with external load

#### TWO STAGE MILLER

Equation 2.1-16: DC Gain of two stage Miller compensated operational amplifier with external load

$$G_{DC} = \frac{G_{m_1} G_{m_2}}{G_{0_1} (G_{0_2} + G_L)}$$

Figure 2.1-9: Two stage Miller compensated operational amplifier with external load

Regarding the single stage configuration, since  $R_L \ll R_0 \rightarrow G_L \gg G_0$ , the dc gain becomes:  $G_{DC} = \frac{G_m}{G_L}$

As for the two stage configuration, since  $R_L \ll R_{0_2} \rightarrow G_L \gg G_{0_2}$ , the DC gain appears to be:  $G_{DC} = \frac{G_{m_1}G_{m_2}}{G_{0_1}G_L}$

Now, since a large value can still be obtained with  $\frac{G_{m_1}}{G_{0_1}}$ , obviously the two stage configuration is a better alternative than the single stage for the case where a resistive load is applied.

However, due to the presence of two poles and one zero, stability cannot be always guaranteed as was the case for the single stage operational amplifier. In fact, the location of the poles and zeros must be rigurously studied before trying to implement such system. System stability is dependent on the presence of a feedback loop around the operational amplifier. The key to achieving system stability is to design a system such that the behaviour of the loop gain until the unity gain frequency, and the behaviour around it, resembles that of a single stage system. The following considerations have to be taken into account regarding the stability analysis of the system under study:

- 1. Negative poles introduce a phase lag of -90° each and the positive zero introduces a phase lag of -90°, hence the total phase lag at frequencies high enough will eventually be -270°

- 2. The phase margin, that is, the distance between the phase at unity gain frequency and -180°, has to be greater than -180° and sufficiently large.

In fact, traditionally the analysis begins with establishing a phase margin, and from there determine the values for the poles and zero. Considering the simplified transfer function to be:

Equation 2.1-17: Transfer function of a two stage Miller compensated operational amplifier

$$\frac{V_{out}}{V_d} = \frac{A_0 \left(1 - \frac{s}{z_1}\right)}{\left(1 + \frac{s}{p_1}\right) \left(1 + \frac{s}{p_2}\right)}$$

where  $A_0$  represents the DC gain and  $z_i$  and  $p_i$  the zeros and the poles, respectively, then the phase response at unity gain frequency will be:

Equation 2.1-18: Phase response at unity gain frequency of a two stage Miller compensated operational amplifier

$$\ll \frac{V_{out}}{V_d}(jw_u) = -\tan^{-1}\frac{w_u}{z_1} - \tan^{-1}\frac{w_u}{p_1} - \tan^{-1}\frac{w_u}{p_2}$$

and the phase margin becomes:

Equation 2.1-19: Phase margin of a two stage Miller compensated operational amplifier

$$\varphi_m = -\tan^{-1}\frac{w_u}{z_1} - \tan^{-1}\frac{w_u}{p_1} - \tan^{-1}\frac{w_u}{p_2} + 180$$

Now, since the expression for the zero has been previously identified to be  $z = \frac{G_{m_2}}{c}$  it is needed to identify an expression for w<sub>u</sub> so that the phase margin condition can be fulfilled by simply estimating the values of the poles. In this sense, the unity gain frequency results to be approximately the same as for the single stage realization  $w_u = \frac{G_{m_1}}{c}$ . So the problem now reduces to estimating the values of the poles in order to fulfill a certain phase margin condition, and from those values, the ones of the capacitors.

Finally, the complex expression derived for the poles can be simplified on the basis of several assumptions. First,  $G_{0_2} \gg G_{0_1}$ , and second  $C \gg C_1$ :

|       | Original values                                                                                                      | $G_{0_2} \gg$                                                | $C \gg C_1$                          |

|-------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------|

|       |                                                                                                                      | $G_{0_1}$ assumption                                         | assumption                           |

| $p_1$ | $-G_{0_1}$                                                                                                           | $-G_{0_1}$                                                   |                                      |

|       | $\overline{C\left(\frac{G_{m_2}}{G_{0_2}} + 1 + \frac{G_{0_1}}{G_{0_2}}\right) + \frac{C_L G_{0_1}}{G_{0_2}} + C_1}$ | $\overline{C\left(\frac{G_{m_2}}{G_{0_2}}+1\right)+C_1}$     |                                      |

| $p_2$ | $-\left(\frac{CG_{m_2}}{C+C_1} + \frac{G_{0_1}(C+C_L)}{C+C_1} + G_{0_2}\right)$                                      | $\frac{-\left(\frac{CG_{m_2}}{C+C_1}+G_{0_2}\right)}{C+C_1}$ | $\frac{-(G_{m_2}+G_{0_2})}{C_1+C_L}$ |

|       | $\frac{C_1C}{C+C_1} + C_L$                                                                                           | $\frac{C_1C}{C+C_1}+C_L$                                     |                                      |

|       |                                                                                                                      |                                                              |                                      |

Table 2.1-4: Comparison of the values of the poles originally and after the assumptions

The fact that C is given a value much greater than  $C_1$  translates into approximating C like a short circuit. With these simpler expression for the poles, it becomes easier to give values to the capacitors on the basis of the values obtained for the poles. Note that the simplified expression for the first pole gives a clear insight of the Miller effect, the term that accompanies the capacitor C is the factor by which the capacitor's value appears to increase when using this configuration.

Another consideration that must be taken into account is the fact that it is desired that the second pole be much greater than the unity gain frequency such that the integrator function is maintained until such frequency. [3][4][15][16][17][18][19][20]

#### 2.1.3 Two Stage Operational Amplifier with Right Half Plane Zero Cancellation

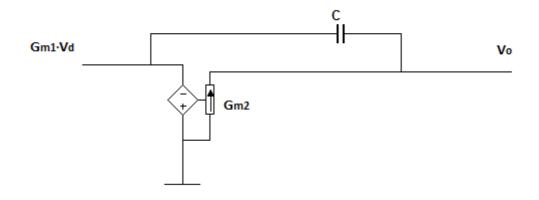

The previous implementation presents problems due to the presence of a right half plane zero, which causes an unwanted phase lag which must be dealt with if the purpose of integration is to be achieved. This can be achieved by "eliminating" the right half plane zero, which can be done by subtracting the value of the zero from the numerator of the transfer function. For simplicity assume the model and the transfer function to be:

Equation 2.1-20:Transfer function of the circuit

$$V_{out} = G_{m_1} V_d \left( \frac{1}{sC} - \frac{1}{G_{m_2}} \right)$$

Figure 2.1-10:Circuit under study

In order to maintain the integrating function while eliminating the zero at the same time, it is needed to add a voltage to the output of the system whose value is:

Equation 2.1-21Extra voltage needed to eliminate the zero

$$V_2 = \frac{G_{m_1}V_d}{G_{m_2}}$$

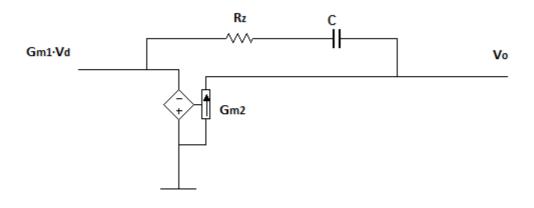

The simplest way to achieve this is to introduce a resistor in series with the negative feedback capacitor:

Figure 2.1-11 : Circuit configuration to eliminate the zero

Choosing the resistor to have a value of:

Equation 2.1-22: Value of resistor to eliminate the zero

$$R = \frac{1}{G_{m_2}}$$

The output voltage of the system becomes:

Equation 2.1-23: Output voltage with effective zero elimination

$$V_{out} = \frac{G_{m_1}V_d}{sC}$$

and the zero has been eliminated. For the general case where the value of the added resistor is equal to  $R_z$  the ouput voltage of the system, and the zero will be equal to:

Equation 2.1-24: Value of the zero in the presence of a resistor

$$V_{out} = G_{m_1} V_d \left( \frac{1}{sC} - \frac{1}{G_{m_2}} + R_z \right)$$

$$z_1 = \frac{-G_{m_2}}{(G_{m_2}R_z - 1)C}$$

Note that the zero could now be located in the left half plane, which is also advantageous compared to the two stage Miller compensated case. This is because it contributes with a phase lead instead of a phase lag and favours stability conditions of the system. Analyzing the overall system derived in the previous case, the following results:

Figure 2.1-12: Two stage Miller with right half plane zero cancellation circuit

The transfer function will be derived once again by matrix analysis by equating the input current to the product of the admittance matrix times the voltage vector at each node.

Equation 2.1-25 Transfer function of two stage Miller with right half plane zero cancellation

$$\begin{bmatrix} sC_1 + \frac{sC}{1 + sCR_z} + G_{0_1} & -\frac{sC}{1 + sCR_z} \\ G_{m_2} - \frac{sC}{1 + sCR_z} & sC_L + \frac{sC}{1 + sCR_z} + G_{0_2} \end{bmatrix} \begin{bmatrix} V_1 \\ V_{out} \end{bmatrix} = \begin{bmatrix} -G_{m_1}V_d \\ 0 \end{bmatrix}$$

Notice that depending on the value of Rz the zero either disappears or is located at different sites of the plane:

Table 2.1-5:Change in the value of the zero depending on the value of the resistor

| $R_z = \frac{1}{G_{max}}$ | $Z_1 \rightarrow \infty$              |

|---------------------------|---------------------------------------|

| $R_z < \frac{1}{G_{m_2}}$ | $z_1$ located in the Right Half Plane |

| $R_z > \frac{1}{G_{m_2}}$ | $z_1$ located in the Left Half Plane  |

It is important to bear in mind that the introduction of Rz has provoked an appearance of an extra pole. Regarding the "eliminated" zero and the "newly introduced" pole, it is observed that the new pole is located at a greater frequency than the old zero and the consequence of this is that less phase lag is obtained overall.

Overall, this system is better than the previous one in the sense that the positive zero can be elliminated, and better than the single stage operational amplifier in that the DC gain can be several orders of magnitude higher. [3][4][21]

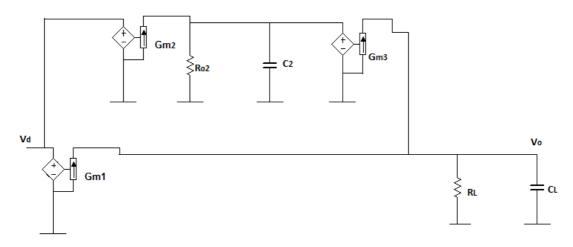

#### 2.1.4 Nested Miller Three Stage Operational Amplifier

Recalling the starting point of the two stage Miller compensated operational amplifier, where an ideal operational amplifier was substituted by a real single stage operational amplifier for the purpose of integration, the next step is to introduce in that same "ideal" operational amplifier a two stage real one and see what the behaviour of the system becomes.

Figure 2.1-13Nested Miller three stage operational amplifier

The first reason why this three stage operational amplifier is preferred with respect to a two stage one lies is the value of the DC gain, which is obviously going to be greater:

Equation 2.1-26:DC gain of nested Miller three stage operational amplifier

$$A_0 = \frac{G_{m_1}G_{m_2}G_{m_3}}{G_{0_1}G_{0_2}G_{0_3}}$$

Recalling the unity gain frequency of the operational amplifier being realized  $\left(w_u = \frac{G_{m_1}}{C}\right)$  and that of the two stage operational amplifier  $\left(w_u = \frac{G_{m_2}}{C_2}\right)$ , and defining the unity gain frequency of the last stage operational amplifier to be  $\left(w_u = \frac{G_{m_3}}{C_L}\right)$  A necessary condition in order for the overall system to behave like an integrator is:

Equation 2.1-27: Condition for nested Miller three stage operational amplifier to integrate

$$\frac{G_{m_3}}{C_L} > \frac{G_{m_2}}{C_2} > \frac{G_{m_1}}{C}$$

This condition always applies even in those cases where the cascade is composed of more systems, meaning that the operational amplifier which is located at the last (or innermost) position must have the highest unity gain frequency and the first (outermost) operational amplifier must have the lowest. This establishes a limit as to how many cascaded systems one can construct, because at some point, a limit will be reached in which the gain of the outermost operational amplifier will have to be extremely small or that of the innermost extremely large. In practice, the largest attainable relation of Gm/C is given to the innermost stage but this means that in the case where there are many stages the outermost will eventually have an impractical DC gain due to the small value of Gm. This is the reason why systems can be built with as many stages as desired but it is uncommon to see more than five systems cascaded in this configuration. Using three stages reduces somewhat the complexity as compared to five and it is a practical configuration in terms of compromising transconductance of the not the first stage. [3][4][15][16][17][18][19][20]

#### 2.1.5 Two Stage Feedforward Compensated Operational Amplifier

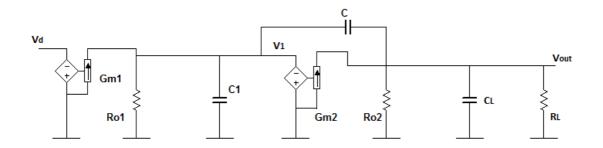

A different configuration of operational amplifiers can be constructed such that the voltage difference  $(V_d)$  at the input of the amplifier is integrated to reduce the steady state error of the system. Such system has the following configuration:

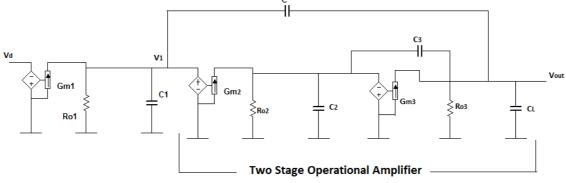

Figure 2.1-14: Two stage feedforward compensated operational amplifier

Where  $G_1$  and  $C_1$  represent the equivalent conductances and capacitances of placing  $G_{03}$  in parallel with  $G_{01}$  and  $C_3$  in parallel with  $C_1$ . As expected, the DC gain of the resulting configuration will be:

Equation 2.1-28: DC gain of two stage feedforward compensated operational amplifier

$$A_{0} = \left(\frac{G_{m_{1}}}{G_{L}} + \frac{G_{m_{2}}G_{m_{3}}}{G_{0_{2}}G_{L}}\right)$$

As it can be observed, it has a similar form to the Miller compensated DC gain, with the difference that there is one part of the circuit in charge of providing the highest amount of DC gain as possible ( $G_{m2}$  and  $G_{m3}$ ) and another part in charge of the integrating function ( $G_{m1}$ ). The presence of more capacitors and the different configuration among them gives an insight of the fact that there probably will be more poles and zeros, whose values will be different to those calculated previously.

This type of configuration is known as feedforward compensated operational amplifier, because the input signal (instead of the output) is being flown through a cascade of systems and fed into a distinct part of the circuit which is located downstream of the system.

The transfer function of the system will be:

Equation 2.1-29: Transfer function of two stage feedforward compensated opensated operational amplifier

$$\frac{V_{out}}{V_d} = \left(G_{m_1} + \frac{G_{m_2}G_{m_3}}{G_{0_2} + sC_2}\right) \frac{1}{G_L + sC_L}$$

Where it can be clearly observed the difference between the terms corresponding to the integrating part and the terms contributing to the increase in DC gain. The location of the poles and zeros are:

Equation 2.1-30: Value of the poles and zero for two stage feedforward compensated operational amplifier

$$p_{1} = \frac{-G_{0_{2}}}{C_{2}}$$

$$p_{2} = \frac{-G_{L}}{C_{L}}$$

$$z_{1} = \frac{-G_{m_{2}}G_{m_{3}}}{G_{m_{1}}C_{2}} - \frac{G_{0_{2}}}{C_{2}}$$

This leads into a simplified form of the transfer function taking into account the expressions for the poles and zero, as well as the expression for the DC gain:

Equation 2.1-31: Simplified expression for two stage feedforward compensated operational amplifier transfer function

$$\frac{V_{out}}{V_d} = A_0 \frac{\left(1 + \frac{s}{z_1}\right)}{\left(1 + \frac{s}{p_1}\right)\left(1 + \frac{s}{p_2}\right)}$$

Regarding the stability of the system under study, due to the presence of two poles which contribute to the phase of the system with a phase lag of -90° degrees each, and a zero which contributes with a lead of +90°; the stability of the system will be guaranteed as long as the zero and the poles appear sufficiently before the unity gain frequency. This way, the behaviour of the system at unity gain frequency will resemble that of a first order system, and the phase margin will be sufficiently separated from -180°. Otherwise, if the zero is located at a close proximity to the unity gain frequency, or if the zero is at a higher frequency than the unity gain one, the phase response of the system at 0dB will be very close or even at -180°, representing an unstable system. Considering a system which has a greater number of poles, the stability criterion becomes:

#### Equation 2.1-32: Condition for stability

$$p_i - z_i = 1$$

In other words, before the unity gain frequency, the number of poles minus the number of zeros must be one in order for the system to behave as a first order system and hence, to be stable. [3][4][22][23][24][25][26][27]

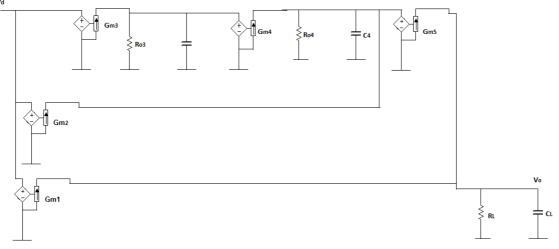

#### 2.1.6 Three Stage Feedforward Compensated Operational Amplifier

A way to improve the current system is to use the same idea recursively. That is, it is desired to integrate the error between the input terminals of an operational amplifier, and to "feed" the output into the resistor coming from the initial operational amplifier. This new approach substitutes the whole integrating functionality of the system for the two stage feedforward compensated operational amplifier just derived, giving rise to a three stage feedforward compensated operational amplifier which obviously will provide a higher DC gain:

*Figure 2.1-15Three stage feedforward compensated operational amplifier*

The transfer function of such circuit will be:

Equation 2.1-33: Transfer function of three stage feedforward compensated operational amplifier

$$\frac{V_{out}}{V_d} = \frac{G_{m_1}}{G_L + sC_L} + \frac{G_{m_2}G_{m_5}}{(G_{0_4} + sC_4)(G_L + sC_L)} + \frac{G_{m_3}G_{m_4}G_{m_5}}{(G_{0_3} + sC_3)(G_{0_4} + sC_4)(G_L + sC_L)}$$

Identifying the DC gain as:

Equation 2.1-34: DC gain of three stage feedforward compensated operational amplifier

$$A_0 = \frac{G_{m_1}}{G_L} + \frac{G_{m_2}G_{m_5}}{G_{0_4}G_L} + \frac{G_{m_3}G_{m_4}G_{m_5}}{G_{0_3}G_{0_4}G_L}$$

Where it is easily identifiable which parts of the circuit contribute the most to the increase in DC gain. The location of the poles is derived straightforwardly:

Equation 2.1-35: Values of the poles for three stage feedforward compensated operational amplifier

$$p_{1} = \frac{-G_{L}}{C_{L}}$$

$$p_{2} = \frac{-G_{0_{3}}}{C_{3}}$$

$$p_{3} = \frac{-G_{0_{4}}}{C_{4}}$$

Whereas the location of the zeroes comes from solving the equation:

Equation 2.1-36: Quadratic equation to find the values of the zeroes

$$z_{12} = \frac{-(b) \pm \sqrt{(b)^2 - 4ac}}{2a}$$

where:

Equation 2.1-37: Values of the coefficients of the quadratic equation

$$a = G_{m_1}C_3C_4$$

$$b = G_{m_1}G_{0_3}C_4 + G_{m_1}G_{0_4}C_3 + G_{m_2}G_{m_5}C_3$$

$$c = G_{m_1}G_{0_3}G_{0_4} + G_{m_3}G_{m_4}G_{m_5} + G_{m_2}G_{m_5}G_{0_3}$$

Assuming the values of the zeroes to be known, the transfer function can be simplified to:

Equation 2.1-38: Simplified expression of the transfer function of a three stage feedforward compensated operational amplifier

$$\frac{V_{out}}{V_d} = A_0 \frac{\left(1 + \frac{s}{z_1}\right)\left(1 + \frac{s}{z_2}\right)}{\left(1 + \frac{s}{p_1}\right)\left(1 + \frac{s}{p_2}\right)\left(1 + \frac{s}{p_3}\right)}$$

Now, regarding the stability of the system, a necessary condition which has been previously stated is that the number of poles minus the number of zeros must be one at the point of the unity gain frequency. That way, the system will behave as a first order system, that is, as if it had a single pole, and it will be stable and the phase margin will be around  $90^{\circ}$ .

This system is superior to the two stage feedforward compensated operational amplifier in terms of the value that can be achieved for the DC gain, and superior to Miller operational amplifiers in the sense that one part of the circuit is in charge of integrating the signal, whereas another provides the gain at zero frequency. Another advantage with respect to Miller compensated configuration is the presence of negative zeros as opposed to the positive zeros present in Miller configuration.

All the systems that have been presented show different advantages and drawbacks, the choice of which one to implement depends on the characteristics of the response that is desired to come out of a system [3][4][22][23][24][25][26][27]

#### 2.2 Operational Amplifier Design

The first objective of this work consists on the design of an operational amplifier behaving like an integrator, whose transfer function was determined prior to the design of the actual model.

In order to choose among the different options provided above, several considerations were taken into account regarding the transfer function which had to be obtained:

- 1. The gain of the operational amplifier at low frequencies had to have a value of 54dB

- 2. The unity gain frequency, and hence the Gain x Bandwidth product had to be 4.45GHz

- 3. The system decreased from 54dB to 0dB in approximately two decades.

- 4. The system could not reach a phase lower than -180°, it had to be stable.

- 5. The system had to have a phase margin of 94°, which means that its phase response at unity gain frequency had to be approximately equal to -86°.

Consequently, the pre-defined Bode to be imitated, had its poles and zeros located at certain frequencies whose values are:

| P <sub>1</sub> | 126.42MHz |

|----------------|-----------|

| P <sub>2</sub> | 317.56MHz |

| P <sub>3</sub> | 317.56MHz |

| $Z_1$          | 894.99MHz |

Z<sub>2</sub> 894.99MHz

The system chosen to model such behavior was the three stage feedforward compensated operational ampifier, which can be justified with the following arguments:

1. The DC gain of a three stage feedforward compensated operational amplifier is the following:

Equation 2.2-1DC gain for a three stage feedforward operational amplifier

$$A_0 = \frac{G_{m_1}}{G_L} + \frac{G_{m_2}G_{m_5}}{G_{0_4}G_L} + \frac{G_{m_3}G_{m_4}G_{m_5}}{G_{0_3}G_{0_4}G_L}$$

Since it is required to achieve 54dB, this means that:

$$A_0 = 10^{\left(\frac{54}{20}\right)} = 501.19$$

Although this represents a large value, it can perfectly be achieved through the combination of all the terms in the expression for  $A_0$ .

- 2. The unity gain frequency  $w_u$ =4.45GHz and hence a gain bandwidth product of this value can perfectly be achieved with such a system

- 3. The fact that the desired magnitude response decreased from 54dB to 0dB in two decades means that the system has to have at least two poles before the unity gain frequency. This is justified by the fact that one pole contributes to a magnitude response of -20dB/decade. So if the system only has one pole, in two decades the magnitude decreases -40dB. Hence, it is needed that the system that has to be built has at least two poles before the unity gain frequency.

- 4. The system could not reach a phase lower than -180°. Due to the fact that poles contribute to a phase lag of -90° and it has been determined that the system must have two poles before the unity gain frequency, it becomes necessary that the system contains at least one zero before the occurrence of -180° phase shift.

- 5. Having determined that the system had to be composed of at least two poles and one zero before unity gain frequency, now it must be taken into account the overall phase response of this combination. Negative zeroes, as is the case for three stage feedforward operational amplifiers, contribute to the phase response of a system with a phase lead of +90° (as long as they are located in the left half plane, which is the case for three stage feedforward systems). This translates into an overall phase response of -90°, however, it is desired a phase of -86° at unity gain frequency. Furthermore, as it can be observed in the Bode plot above, the system actually goes further up this -86° value. Therefore, two zeroes are needed instead of one.

- 6. Recalling the condition that has been stated already for stability, there must be one extra pole than zero before the unity gain frequency. Therefore, the system must have three poles and two zeros, all of them ocurring before the unity gain frequency.

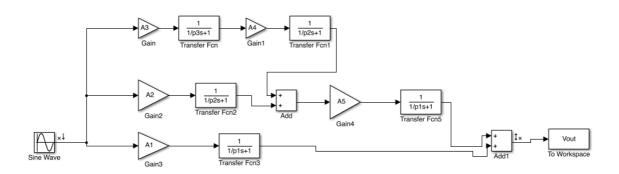

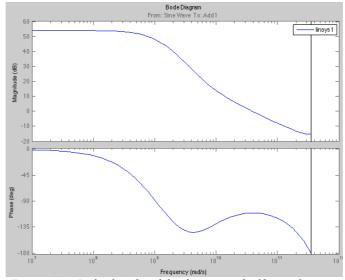

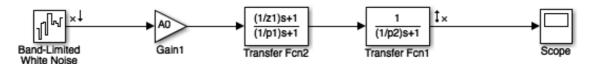

The development of such a system was carried out in Simulink, and variables were declared using Matlab workspace. The initial system was:

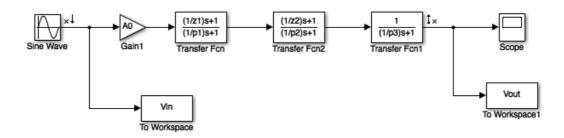

Figure 2.2-1:Simulink model of a three stage feedforward compensated operational amplifier

Several values were tried for the poles as well as for the zeros. Although theoretically a very similar Bode plot had to be obtained, the simulations showed a slightly different response to the one desired. However, since the most important considerations were the DC gain, the unity gain frequency, and making sure that the system did not present a phase response lower than -180°, the parameters which were finally chosen were:

| A <sub>0</sub>   | $10^{\frac{54}{20}} = 501.19$                                    |

|------------------|------------------------------------------------------------------|

| P <sub>1</sub>   | $10^{8.9} = 794.33 \times 10^6$ rad/s =                          |

|                  | 126.42MHz                                                        |

| P <sub>2</sub>   | $10^{9.3} = 1.99 \times 10^9 \text{rad/s} = 317.56 \text{MHz}$   |

| P <sub>3</sub>   | $10^{9.3} = 1.99 \times 10^9 \text{rad/s} = 317.56 \text{MHz}$   |

| $Z_1$            | $10^{9.75} = 56.23 \times 10^9 \text{rad/s} = 894.99 \text{MHz}$ |

| $\mathbf{Z}_2$   | $10^{9.75} = 56.23 \times 10^9 \text{rad/s} = 894.99 \text{MHz}$ |

| $\mathbf{f}_{s}$ | $4w_u = 1.12 \times 10^{11} \text{rad/s} = 17.8 \text{GHz}$      |

| Ts               | $\frac{1}{f_s} = 8.94 \times 10^{-12} s$                         |

Table 2.2-2Values for the variables of the three stage feedforward model

Where  $p_i$  represent the poles of the transfer function and  $z_i$  the zeros. The choice for the sampling frequency comes from the fact that it is desired to observe in the Bode plot the unity gain frequency. In order to be able to observe such frequency while at the same time avoiding the aliasing problem, Nyquist theorem must be fulfilled:

Equation 2.2-2: Nyquist theorem

$f_s \ge 2f_h$

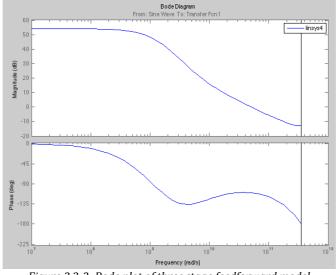

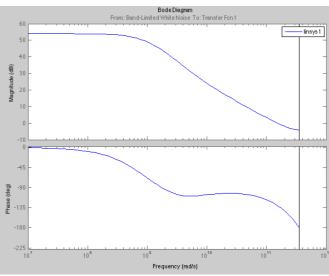

Where  $f_h$  represents the highest frequency component wanted to be observed. Since matlab performs the Bode plot in rad/s instead of Hertz, the choice for the sampling frequency to be entered for the sampling period was the one in rad/s. The output of such system gave rise to the following magnitude and phase response:

*Figure 2.2-2: Bode plot of three stage feedforward model*

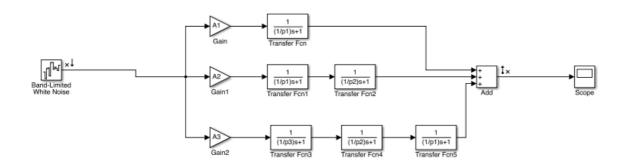

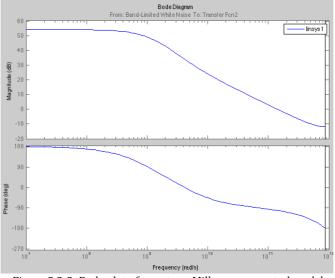

In addition to this system, another was built in a slightly different manner, representing each stage of the transfer function of the three stage feedforward operational amplifier separately and adding them together. This was done to verify that the behaviour of this system and the previous one was exactly the same.

Figure 2.2-3: Simulink model 2 of three stage feedforward compensated operational amplifier

Recall the transfer function corresponding to the system under study:

Equation 2.2-3: Transfer function of three stage feedforward compensated operational amplifier

$$\frac{V_{out}}{V_d} = \frac{G_{m_1}}{G_L + sC_L} + \frac{G_{m_2}G_{m_5}}{(G_{0_4} + sC_4)(G_L + sC_L)} + \frac{G_{m_3}G_{m_4}G_{m_5}}{(G_{0_3} + sC_3)(G_{0_4} + sC_4)(G_L + sC_L)}$$

Making the analogy between the model in Simulink and this transfer function, each of the gain boxes in simulink represents the DC gains of each term which is being added in the transfer function. In this sense:

Equation 2.2-4: DC gain at each stage of model 2

$$A_{1} = \frac{G_{m_{1}}}{G_{L}}$$

$$A_{2} = \frac{G_{m_{2}}G_{m_{5}}}{G_{0_{4}}G_{L}}$$

$$A_{3} = \frac{G_{m_{3}}G_{m_{4}}G_{m_{5}}}{G_{0_{2}}G_{0_{4}}G_{L}}$$

Therefore, each of the gain boxes in Simulink makes reference to circuit components of the system. Notice that this system is slightly different from the previous one in the sense that the poles are explicitly declared through variables in Matlab workspace, but the zeroes are not. Choosing the values of the poles to be the same as for the previous system and defining the new variables  $A_1$ ,  $A_2$  and  $A_3$ , the results obtained coincide exactly with the previous case.

Table 2.2-3: Values of the variables for model 2

| $A_1$          | 50.19        |

|----------------|--------------|

| A <sub>2</sub> | 200          |

| A <sub>3</sub> | 250          |

| P <sub>1</sub> | 126.42MHz    |

| P <sub>2</sub> | 317.56MHz    |

| P <sub>3</sub> | 317.56MHz    |

| fs             | 17.8GHz      |

| Ts             | 8.94 ×       |

|                | $10^{-12}$ s |

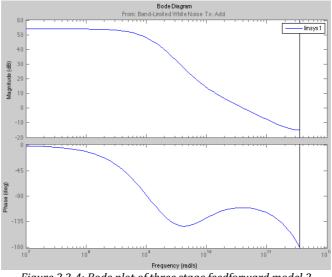

Figure 2.2-4: Bode plot of three stage feedforward model 2

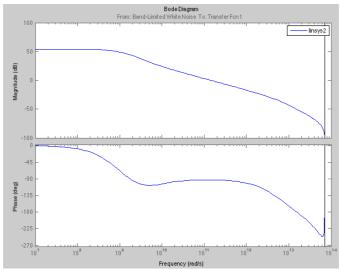

A last variant of the same system was built, with the purpose of resembling the three stage feedforward circuit as much as possible.

Figure 2.2-5: Simulink model 3 of three stage feedforward operational amplifier

There are a few considerations to bear in mind regarding this last version. First of all, as it can be seen:

Equation 2.2-5: DC gain of model 3

$$A_1 + A_2 A_5 + A_3 A_4 A_5 = G_{DC}$$

which leads to:

Table 2.2-4: Values of the variables for model 3 of three stage feedforward system

| A <sub>1</sub> | 50.19        |

|----------------|--------------|

| A <sub>2</sub> | 10           |

| A <sub>3</sub> | 2.5          |

| A <sub>4</sub> | 5            |

| A <sub>5</sub> | 20           |

| P <sub>1</sub> | 126.42MHz    |

| P <sub>2</sub> | 317.56MHz    |

| P3             | 317.56MHz    |

| fs             | 17.8GHz      |

| Ts             | 8.94 ×       |

|                | $10^{-12}$ s |

As it can be seen, the values of the poles as well as the sampling frequency and period remain exactly the same as for the previous models so that the same Bode plot is obtained. Also, the location of each of the poles within the system was not done arbitrarily. The "innermost" system must present the highest pole, and then the system must present poles which are successively smaller. If this rule is violated, then the integrating function will simply not work, and a completely different Bode plot will be obtained. The response of this last model was:

Figure 2.2-6: Bode plot of model 3 three stage feedforward system

As it can be observed by simple observation of the three Bode plots, the behaviour of the three systems is exactly the same, which was essentially what was expected, since they represent the same circuit configuration. The model chosen to work with to continue with the modelling procedure was the first one, which contains explicitly the complete transfer function with poles and zeroes. This was done because the system was simpler and smaller, although all the three systems are perfectly useful for the purpose of this work

#### 2.3 Alternative designs

Although the model described previously works for the purpose of obtaining the initially shown Bode plot, several alternatives were also tried to confirm that the three stage feedforward compensated operational amplifier was definitively the best choice.

#### 2.3.1 Two Stage Miller Compensated Operational Amplifier

As previously described, this configuration presents a transfer function which contains two poles and one zero, whose DC gain is:

Equation 2.3-1: DC gain of two stage Miller compensated operational amplifier

$$A_0 = \frac{G_{m_1} G_{m_2}}{G_{0_1} G_{0_2}}$$