### An Ultra Low Power Implantable Neural Recording System for Brain-Machine Interfaces

by

Woradorn Wattanapanitch

B.S., Cornell University (2005) S.M., Massachusetts Institute of Technology (2007)

Submitted to the Department of Electrical Engineering and Computer Science

ARCHIVES

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Electrical Engineering and Computer Science

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

June 2011

$\odot$  Massachusetts Institute of Technology 2011. All rights reserved.

| author                                                    |

|-----------------------------------------------------------|

| Department of Electrical Engineering and Computer Science |

| May 18, 2011                                              |

| lantified by                                              |

| Pertified by                                              |

| Associate Professor of Electrical Engineering             |

| Thesis Supervisor                                         |

| ccepted by                                                |

| /Leslie A. Kolodziejski, Ph.D.                            |

| Chairman, Committee on Graduate Students                  |

| Department of Electrical Engineering and Computer Science |

# An Ultra Low Power Implantable Neural Recording System for Brain-Machine Interfaces

by

#### Woradorn Wattanapanitch

Submitted to the Department of Electrical Engineering and Computer Science on May 18, 2011, in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering and Computer Science

#### Abstract

In the past few decades, direct recordings from different areas of the brain have enabled scientists to gradually understand and unlock the secrets of neural coding. This scientific advancement has shown great promise for successful development of practical brain-machine interfaces (BMIs) to restore lost body functions to patients with disorders in the central nervous system. Practical BMIs require the uses of implantable wireless neural recording systems to record and process neural signals, before transmitting neural information wirelessly to an external device, while avoiding the risk of infection due to through-skin connections. The implantability requirement poses major constraints on the size and total power consumption of the neural recording system.

This thesis presents the design of an ultra-low-power implantable wireless neural recording system for use in brain-machine interfaces. The system is capable of amplifying and digitizing neural signals from 32 recording electrodes, and processing the digitized neural data before transmitting the neural information wirelessly to a receiver at a data rate of 2.5 Mbps. By combining state-of-the-art custom ASICs, a commercially-available FPGA, and discrete components, the system achieves excellent energy efficiency, while still offering design flexibility during the system development phase. The system's power consumption of 6.4 mW from a 3.6-V supply at a wireless output data rate of 2.5 Mbps makes it the most energy-efficient implantable wireless neural recording system reported to date. The system is integrated on a flexible PCB platform with dimensions of 1.8 cm  $\times$  5.6 cm and is designed to be powered by an implantable Li-ion battery.

As part of this thesis, I describe the design of low-power integrated circuits (ICs) for amplification and digitization of the neural signals, including a neural amplifier and a 32-channel neural recording IC. Low-power low-noise design techniques are utilized in the design of the neural amplifier such that it achieves a noise efficiency factor (NEF) of 2.67, which is close to the theoretical limit determined by physics. The neural recording IC consists of neural amplifiers, analog multiplexers, ADCs, serial programming interfaces, and a digital processing unit. It can amplify and

digitize neural signals from 32 recording electrodes, with a sampling rate of 31.25 kS/s per channel, and send the digitized data off-chip for further processing. The IC was successfully tested in an *in-vivo* wireless recording experiment from a behaving primate with an average power dissipation per channel of 10.1  $\mu$ W. Such a system is also widely useful in implantable brain-machine interfaces for the blind and paralyzed, and in cochlea implants for the deaf.

Thesis Supervisor: Rahul Sarpeshkar, Ph.D.

Title: Associate Professor of Electrical Engineering

#### Acknowledgments

First of all, I would like to thank my advisor, Prof. Rahul Sarpeshkar, for his support and encouragement throughout my graduate school years. In these past six years under his guidance, I always regard him as an excellent example of a person with great technical brilliance, enthusiasm for learning, intuition to understand problems deeply, and, most of all, unwavering courage to tackle any difficult problem, which always inspires me to strive for the same. He not only has instilled in me technical knowledge for my future professional development, but also has taught me how to not give up when everything looked grim, and always encouraged me to try my hardest at overcoming all the obstacles that I am facing. I am truly grateful and privileged to be able to go through my graduate school years at MIT under his supervision.

What makes my graduate school experience truly enjoyable is the support from my colleagues including the past and present members of the AVBS group. My special thanks go to Dr. Soumyajit Mandal, Scott K. Arfin, Benjamin I. Rapoport, Daniel Kumar, Bruno Do Valle, and Dr. Lorenzo Turicchia. It has been an unforgettable experience to be able to work side-by-side with them throughout most of my years at MIT.

I am truly grateful for the support and encouragement of my family in Thailand. They always encourage me to focus on my study and accomplish my goal, and never worry about the situation at home. They have been waiting, day and night, for my return to Thailand in the past 11 years of my study in the United States, without ever complaining that it takes so long. I am eternally grateful to my father, Somsak Wattanapanitch, who instilled in me the love of science at a very young age. He always believed that one day his son would accomplish great things, and that belief has always encouraged me to never fail his expectation. I believe that his soul in heaven will be delighted to see that one of his son's dreams is about to be fulfilled.

Finally, I would like to give a special thank to my fiancée, Dr. Methichit Chayosumrit, whose love, support, and encouragement always make every single day of mine truly meaningful.

## Contents

| 1 | Int | roduction                                                            | 19 |

|---|-----|----------------------------------------------------------------------|----|

|   | 1.1 | Motivation                                                           | 19 |

|   | 1.2 | Previous Work                                                        | 21 |

|   | 1.3 | Our Approach                                                         | 23 |

|   | 1.4 | Author's Contribution                                                | 25 |

|   | 1.5 | Thesis Organization                                                  | 26 |

| 2 | An  | Energy-Efficient Micropower Neural Recording Amplifier               | 27 |

|   | 2.1 | Overall Architecture of the Neural Amplifier                         | 28 |

|   | 2.2 | Low-Power Low-Noise OTA design for gain stage                        | 31 |

|   |     | 2.2.1 Device sizing for maximizing $G_m$                             | 34 |

|   |     | 2.2.2 OTA Noise Analysis                                             | 37 |

|   |     | 2.2.3 Current mirror mismatch analysis                               | 40 |

|   |     | 2.2.4 Noise Efficiency Factor and its theoretical limit for OTA with |    |

|   |     | differential inputs                                                  | 42 |

|   | 2.3 | Measurement Results                                                  | 43 |

|   | 2.4 | Measurements of Local Field Potentials                               | 49 |

|   | 2.5 | Conclusion                                                           | 51 |

| 3 | Ult | ra-low-power 32-channel Neural Recording IC                          | 53 |

|   | 3.1 | System Architecture                                                  | 54 |

|   | 3.2 | Neural Amplifier                                                     | 56 |

|   |     | 3.2.1 Front-End Amplifier                                            | 59 |

|   |     | 3.2.2                             | Bandpass Filter                                            | 72                       |

|---|-----|-----------------------------------|------------------------------------------------------------|--------------------------|

|   |     | 3.2.3                             | Programmable Gain Amplifier                                | 75                       |

|   | 3.3 | Neural                            | Signal Digitization                                        | 77                       |

|   |     | 3.3.1                             | ADC Basic                                                  | 77                       |

|   |     | 3.3.2                             | ADC Design Considerations                                  | 81                       |

|   |     | 3.3.3                             | Basic Operation of the ADC                                 | 82                       |

|   |     | 3.3.4                             | Circuit Implementations of the ADC                         | 87                       |

|   | 3.4 | Analog                            | g Multiplexer                                              | 102                      |

|   | 3.5 | Serial                            | Programming Interface                                      | 105                      |

|   | 3.6 | Digital                           | l Control Unit                                             | 106                      |

|   | 3.7 | Experi                            | mental Results                                             | 115                      |

|   |     | 3.7.1                             | Benchtop Testing of the Neural Amplifier                   | 118                      |

|   |     | 3.7.2                             | Benchtop testing of the Analog-to-Digital Converter        | 122                      |

|   |     | 3.7.3                             | Wireless In-Vivo Testing of the Neural Recording System in |                          |

|   |     |                                   | Behaving Primate                                           | 124                      |

|   | 3.8 | Conclu                            | asion                                                      | 130                      |

| 4 | An  | Implar                            | ntable Wireless Neural Recording System                    | 131                      |

|   | 4.1 | System                            | n Overview                                                 | 131                      |

|   | 4.2 | Design                            | Considerations of the Internal Unit                        | 132                      |

|   |     | 4.2.1                             | Energy Efficiency vs. Flexibility                          | 132                      |

|   |     | 4.2.2                             | Power Minimization Strategies of the Internal Unit         | 133                      |

|   |     |                                   | Tower Minimization Strategies of the internal cine         |                          |

|   |     | 4.2.3                             | Powering the Internal Unit                                 | 135                      |

|   |     |                                   | <u> </u>                                                   |                          |

|   |     | 4.2.3                             | Powering the Internal Unit                                 | 135                      |

|   |     | 4.2.3<br>4.2.4                    | Powering the Internal Unit                                 | 135                      |

|   | 4.3 | 4.2.3<br>4.2.4<br>4.2.5           | Powering the Internal Unit                                 | 135<br>137               |

|   | 4.3 | 4.2.3<br>4.2.4<br>4.2.5           | Powering the Internal Unit                                 | 135<br>137<br>138        |

|   | 4.3 | 4.2.3<br>4.2.4<br>4.2.5<br>Archit | Powering the Internal Unit                                 | 135<br>137<br>138<br>140 |

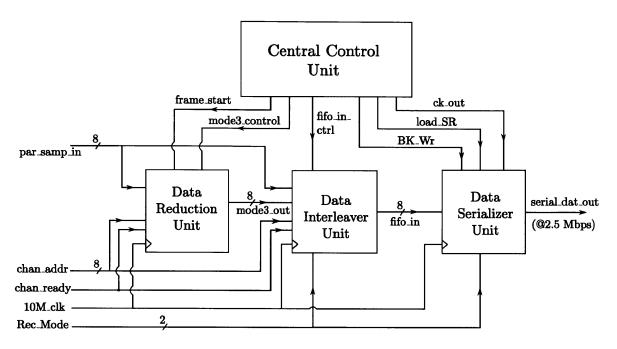

|   | 4.4 | Neural Data Processor                                         |

|---|-----|---------------------------------------------------------------|

|   |     | .4.1 Data Reduction Unit                                      |

|   |     | 4.2 Data Interleaver Unit                                     |

|   |     | .4.3 Data Serializer Unit                                     |

|   |     | 4.4 Central Control Unit                                      |

|   | 4.5 | Operation Control Unit                                        |

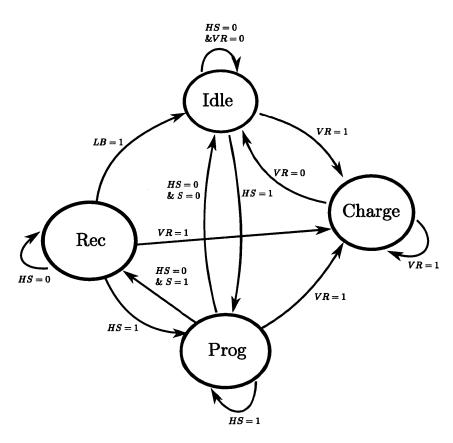

|   |     | 4.5.1 Design Considerations of the Operation Control Unit 156 |

|   |     | 1.5.2 Outputs of the Operation Control Unit                   |

|   |     | 4.5.3 Finite State Machine of the Operation Control Unit 160  |

|   | 4.6 | Programming Interface Unit                                    |

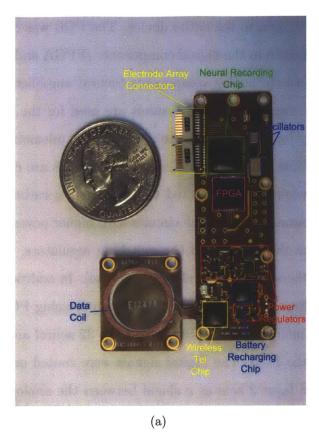

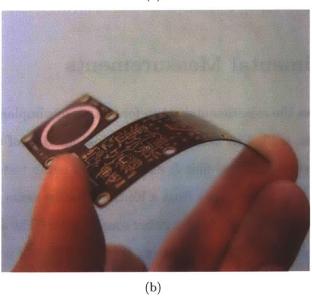

|   | 4.7 | Physical Design of the Internal Unit                          |

|   | 4.8 | Experimental Measurements                                     |

|   | 4.9 | Conclusion                                                    |

| 5 | Cor | lusions 175                                                   |

|   | 5.1 | Summary                                                       |

|   | 5.2 | Future Work                                                   |

|   |     |                                                               |

## List of Figures

| 1-1  | Conceptual diagram of our BMI system                                           | 25                  |

|------|--------------------------------------------------------------------------------|---------------------|

| 2-1  | Overall architecture of the Neural Amplifier                                   | 29                  |

| 2-2  | Block diagram of our neural amplifier including the input noise source         |                     |

|      | of the OTA                                                                     | 30                  |

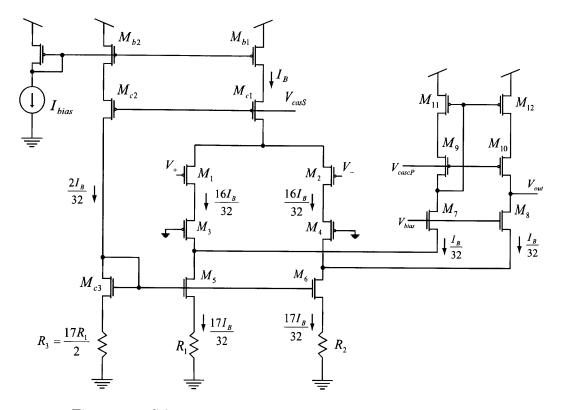

| 2-3  | Schematic of the low-noise OTA used in this design                             | 31                  |

| 2-4  | Circuit schematic for analyzing current scaling in the source-degenerated      |                     |

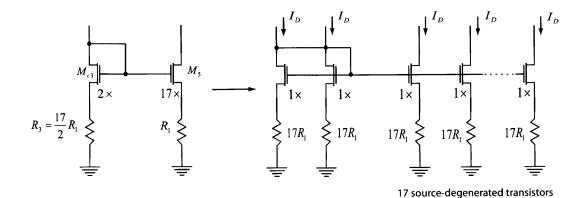

|      | current mirrors of Fig. 2-3                                                    | 32                  |

| 2-5  | Schematic of a standard folded-cascode OTA                                     | 34                  |

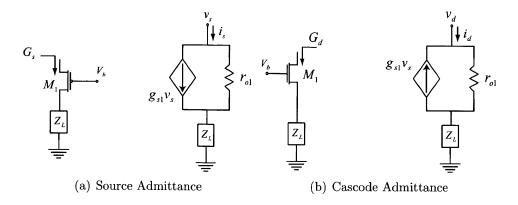

| 2-6  | Circuit schematics for obtaining admittance formula                            | 35                  |

| 2-7  | Circuit schematics for analyzing $V_T$ and $R$ mismatches in source-degenerate | $\operatorname{ed}$ |

|      | current mirrors                                                                | 40                  |

| 2-8  | A die micrograph of our neural amplifier                                       | 43                  |

| 2-9  | Measured transfer function of the neural amplifier configured for record-      |                     |

|      | ing neural spikes                                                              | 44                  |

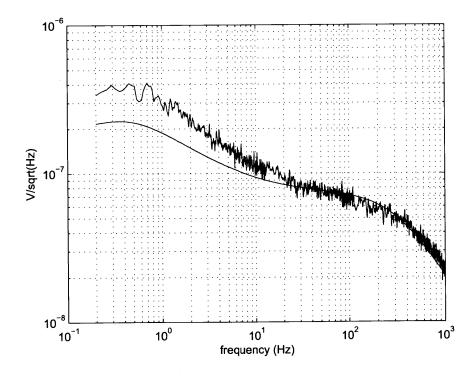

| 2-10 | Measured and simulated (smooth curve) input-referred noise spectra             |                     |

|      | of the neural amplifier configured for recording neural spikes                 | 45                  |

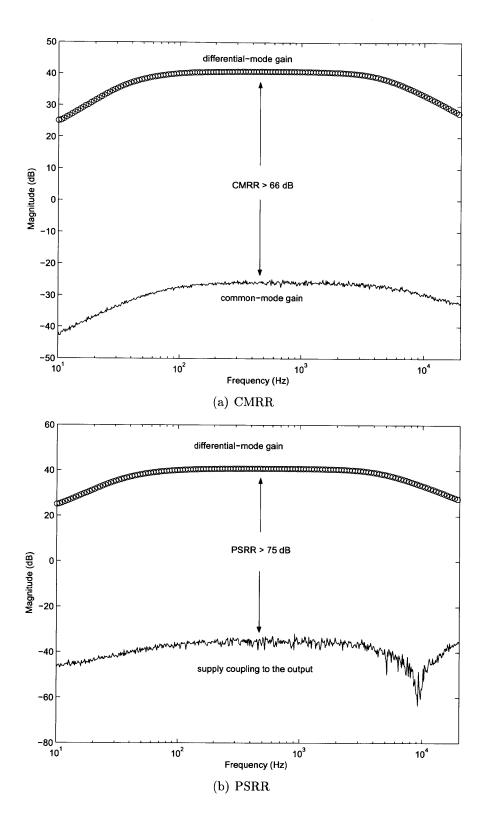

| 2-11 | CMRR and PSRR measurements of the neural amplifier configured for              |                     |

|      | recording action potentials                                                    | 47                  |

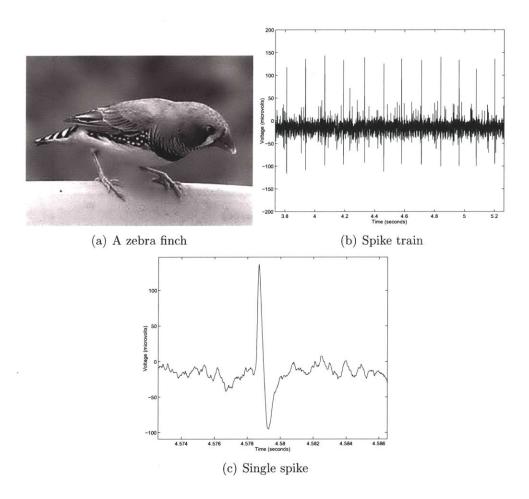

| 2-12 | Neural recording from a zebra finch's brain: (a) A zebra finch (b) Long        |                     |

|      | time trace (c) Short time trace                                                | 48                  |

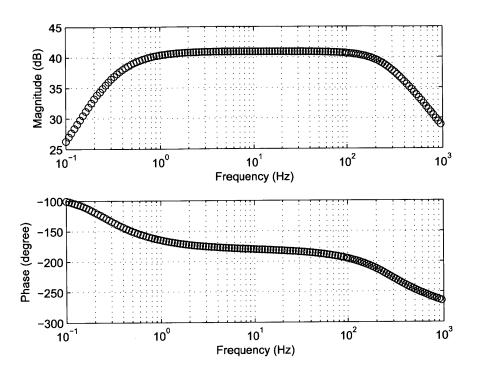

| 2-13 | Transfer function of the amplifier configured for recording LFP                | 50                  |

| 2-14 | Measured and simulated (smooth curve) input-referred noise spectra         |    |

|------|----------------------------------------------------------------------------|----|

|      | for the amplifier configured for recording LFP                             | 50 |

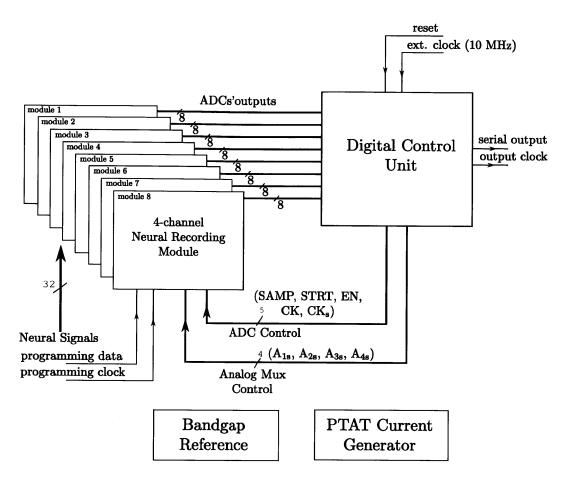

| 3-1  | Overall architecture of the 32-channel neural recording system             | 55 |

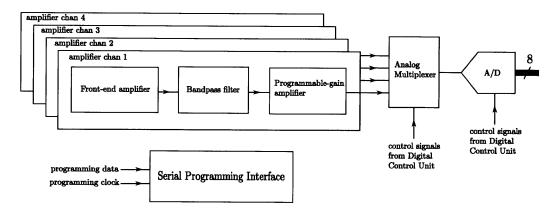

| 3-2  | Architecture of a 4-channel neural recording module                        | 55 |

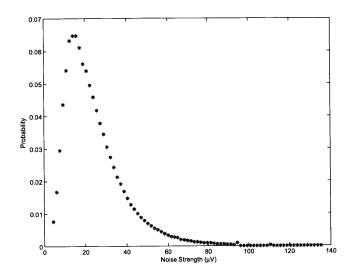

| 3-3  | An example of a probability distribution of the neural background noise    |    |

|      | measured from a recording array of 64 electrodes                           | 58 |

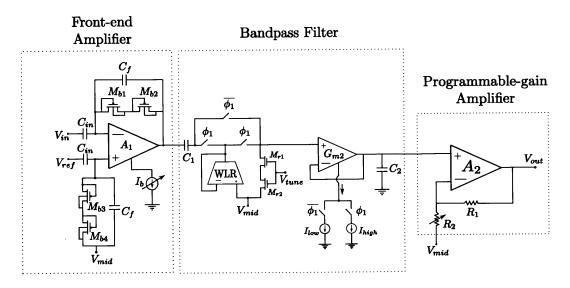

| 3-4  | Schematic of the neural amplifier consisting of three stages: i) front-end |    |

|      | amplifier ii) bandpass filter iii) programmable-gain amplifier             | 58 |

| 3-5  | Schematic of the front-end amplifier: (a) High-level schematic (b)         |    |

|      | Schematic of the amplifier $A_1$                                           | 60 |

| 3-6  | Small-signal diagram of the front-end amplifier                            | 61 |

| 3-7  | Feedback block diagram for analyzing the front-end amplifier               | 62 |

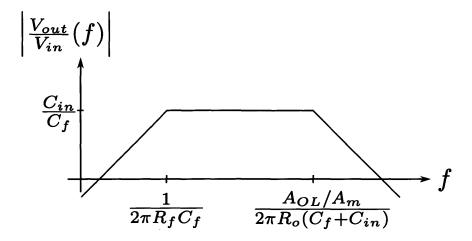

| 3-8  | Bode magnitude plot of the front-end amplifier's transfer function         | 64 |

| 3-9  | Small-signal diagram for the noise analysis of the amplifier $A_1$         | 66 |

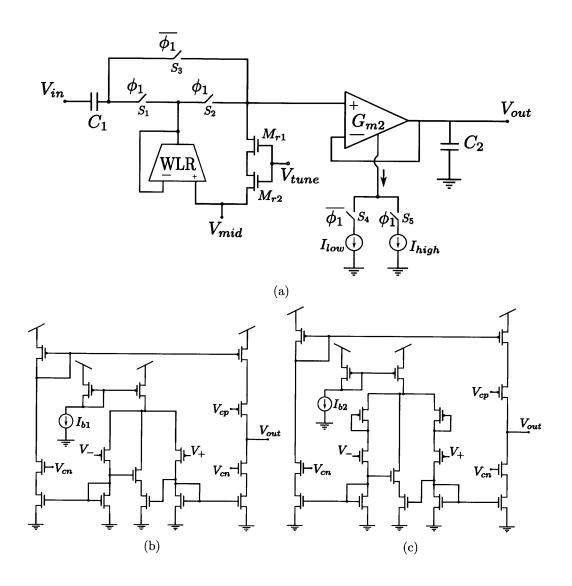

| 3-10 | (a) Schematic of the bandpass filter. (b) Schematic of the $G_{m2}$ -OTA.  |    |

|      | (c) Schematic of the WLR-OTA                                               | 73 |

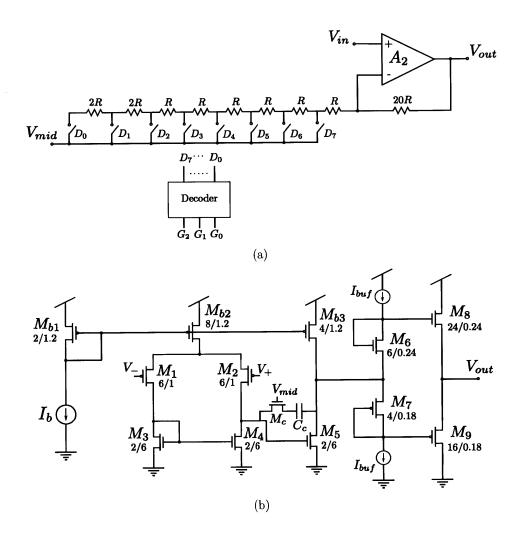

| 3-11 | (a) Schematic of the programmable-gain amplifier. (b) Schematic of         |    |

|      | the amplifier $A_2$                                                        | 76 |

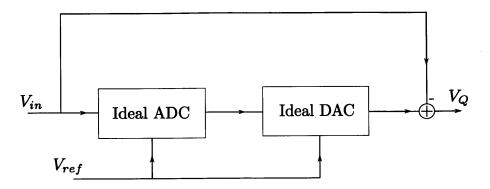

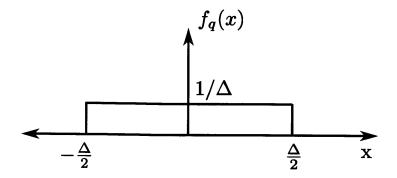

| 3-12 | Circuit diagram illustrating the concept of quantization noise             | 78 |

| 3-13 | Probability density function of an ideal ADC's quantization noise          | 79 |

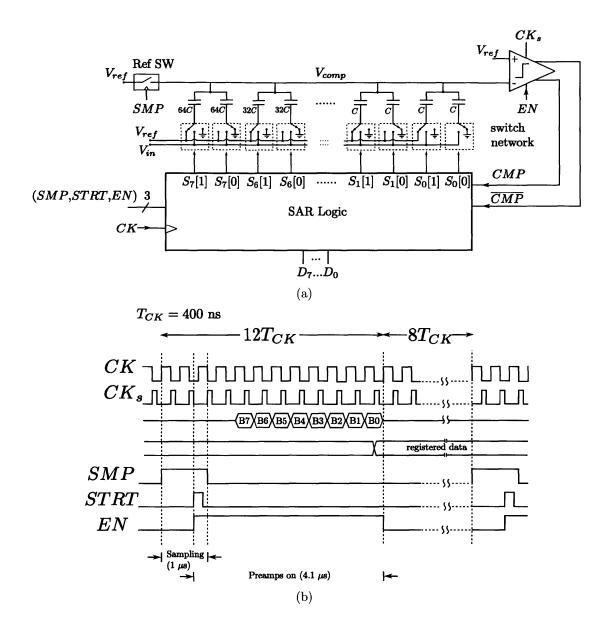

| 3-14 | (a) Schematic of the SAR ADC used in this neural recording system.         |    |

|      | (b) Timing diagram of the ADC.                                             | 83 |

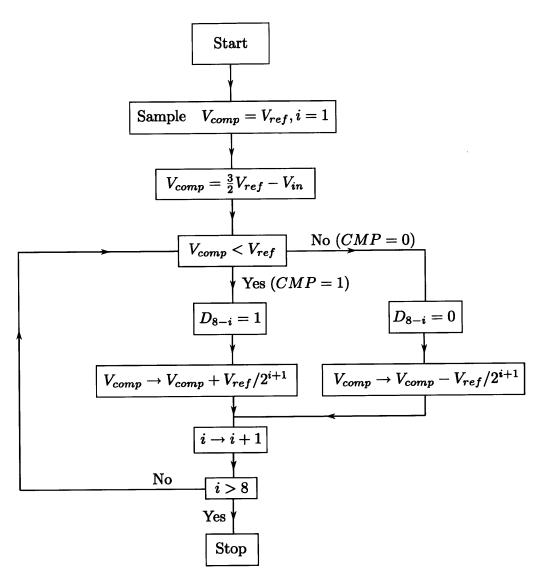

| 3-15 | Flow graph illustrating the operation of the successive approximation      |    |

|      | ADC                                                                        | 86 |

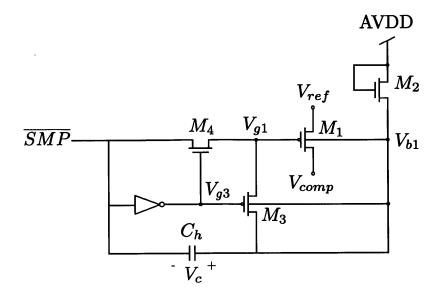

| 3-16 | Schematic of the bootstrapped reference switch                             | 88 |

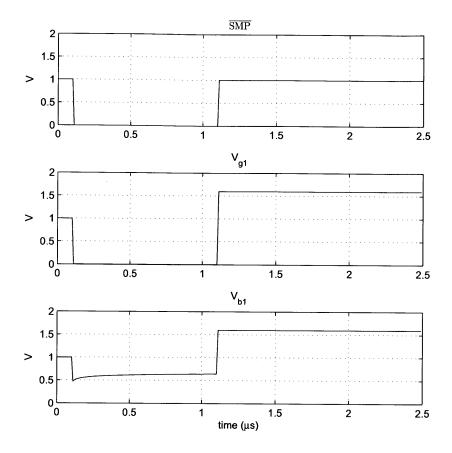

| 3-17 | Simulation result showing the node voltages of the reference switch in     |    |

|      | Fig 3-16                                                                   | 89 |

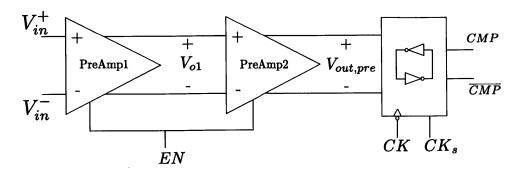

| 3-18 | Schematic of the comparator                                                | 90 |

| 3-19 | Schematic of the preamplifier                                              | 91 |

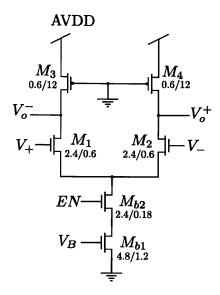

| 3-20 | Magnitude response of the preamplification stage. The low-frequency     |     |

|------|-------------------------------------------------------------------------|-----|

|      | gain is 30.9 dB (35) and $f_{-3\text{dB}} = 4 \text{ MHz}$              | 94  |

| 3-21 | Output noise density at $V_{out,pre}$                                   | 95  |

| 3-22 | Schematic of the latch                                                  | 96  |

| 3-23 | Schematic of the SAR logic                                              | 97  |

| 3-24 | Timing diagram of the SAR logic                                         | 97  |

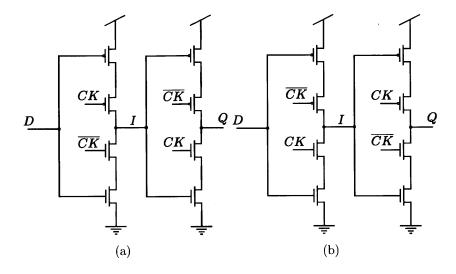

| 3-25 | (a) Schematic of $SR$ (b) Schematic of $\overline{SR}$                  | 98  |

| 3-26 | Schematic of the shift register $SR_i$                                  | 99  |

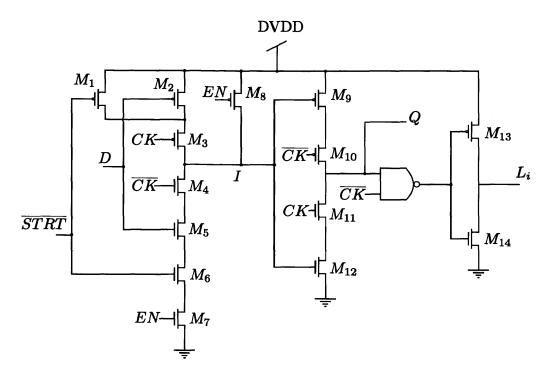

| 3-27 | Schematic of the switch drive register $SDR_i$                          | 100 |

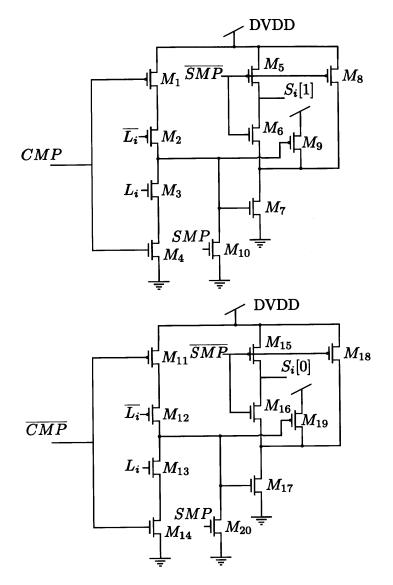

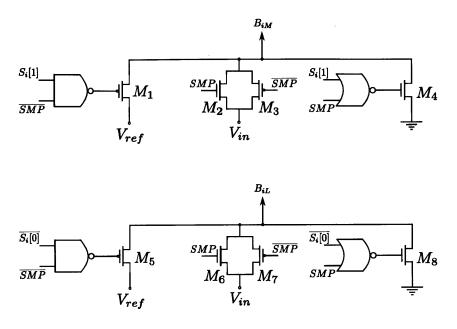

| 3-28 | Schematic of the switch network                                         | 102 |

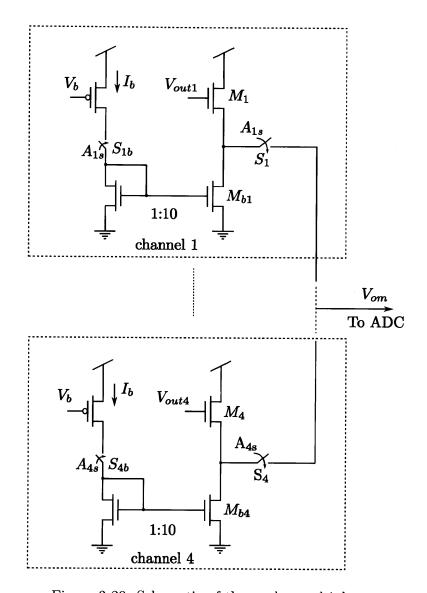

| 3-29 | Schematic of the analog multiplexer                                     | 103 |

| 3-30 | Timing diagram of the analog multiplexer's control signals              | 104 |

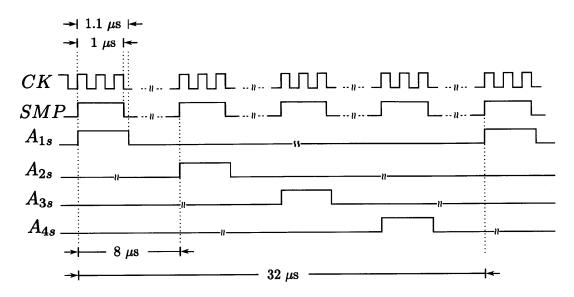

| 3-31 | Format of the programming packet for configuring each neural record-    |     |

|      | ing module                                                              | 105 |

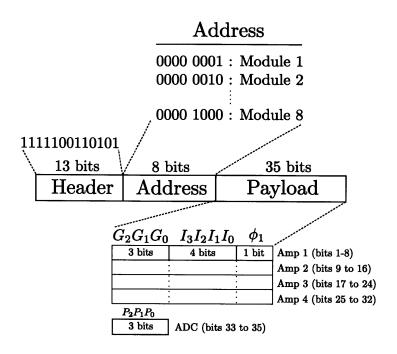

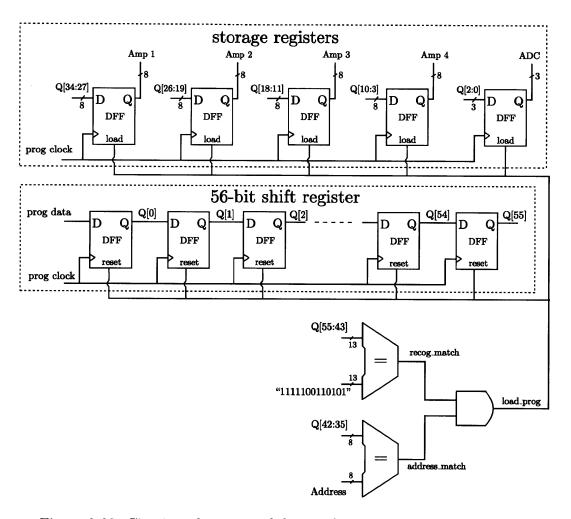

| 3-32 | Circuit architecture of the serial programming interface unit           | 107 |

| 3-33 | Block diagram of the Digital Control Unit                               | 108 |

| 3-34 | Block diagram of the Control Signal Generator                           | 110 |

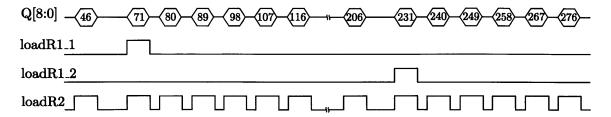

| 3-35 | Timing diagram of Digital Control Unit. $Q[8:0]$ is shown in decimal    |     |

|      | basis                                                                   | 111 |

| 3-36 | Timing diagram of the CK and $CK_s$ generation. Q[1:0] is shown in      |     |

|      | binary basis                                                            | 112 |

| 3-37 | Format of the outgoing data packet of the 32-channel neural recording   |     |

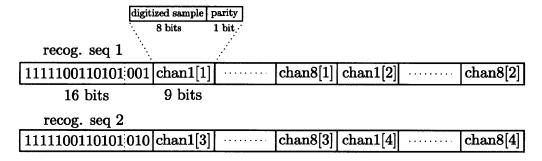

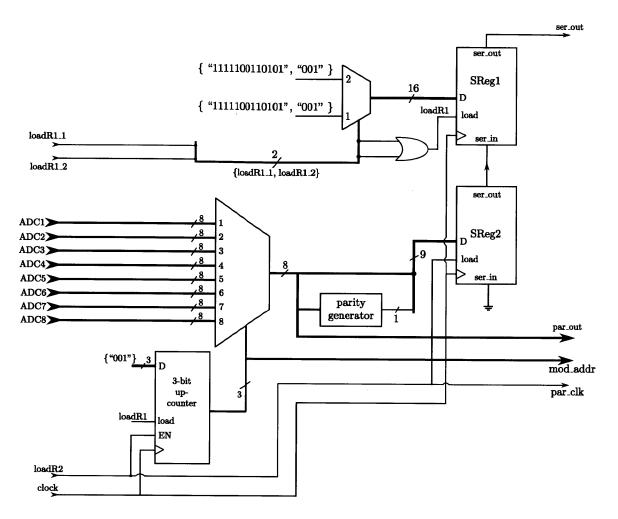

|      | system                                                                  | 112 |

| 3-38 | Block Diagram of the Data Packetizer                                    | 113 |

| 3-39 | Timing diagram of the loading signals for loading SReg1 and SReg2       | 115 |

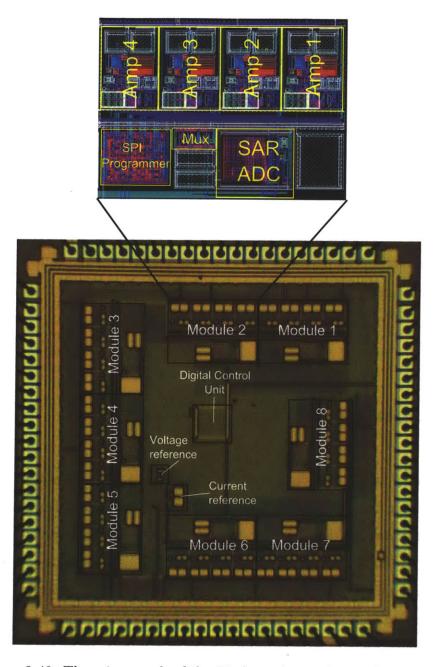

| 3-40 | The micrograph of the 32-channel neural recording system                | 116 |

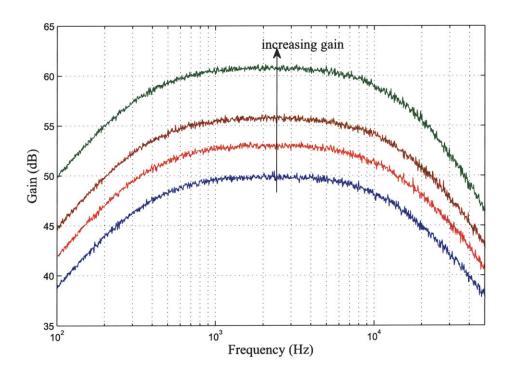

| 3-41 | Magnitude Responses of the amplifier at different gain settings in the  |     |

|      | spike recording setting.                                                | 117 |

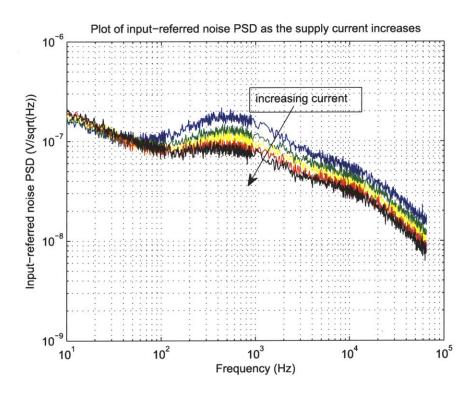

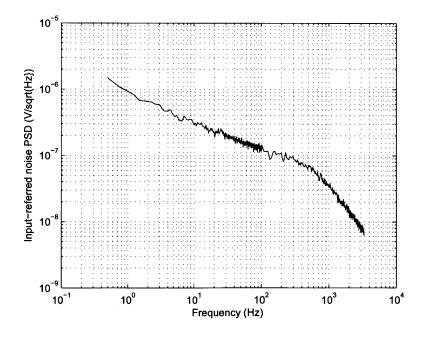

| 3-42 | Input-referred noise densities of the neural amplifier as the front-end |     |

|      | amplifier's supply current increases                                    | 119 |

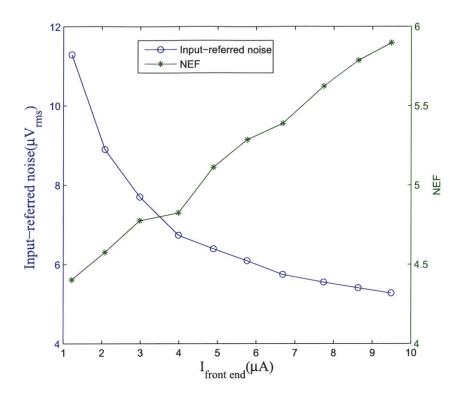

| 3-43 | Integrated input-referred rms noise and the NEF of the neural amplifier |      |

|------|-------------------------------------------------------------------------|------|

|      | vs. front-end amplifier's bias current                                  | 120  |

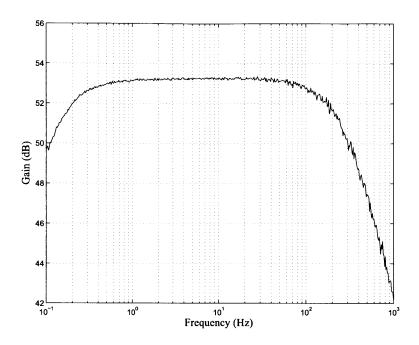

| 3-44 | Magnitude Response of the amplifier in the LFP recording setting        | 121  |

| 3-45 | Input-referred noise density in the LFP recording setting               | 121  |

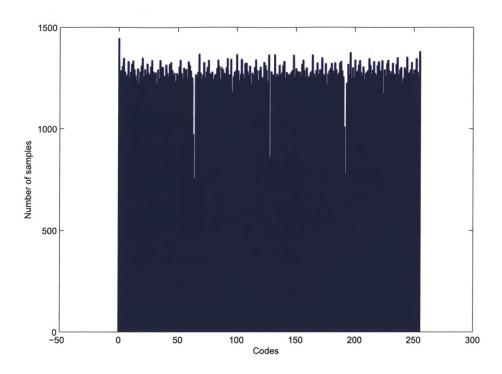

| 3-46 | Histogram of the ADC's output codes from the code density test          | 124  |

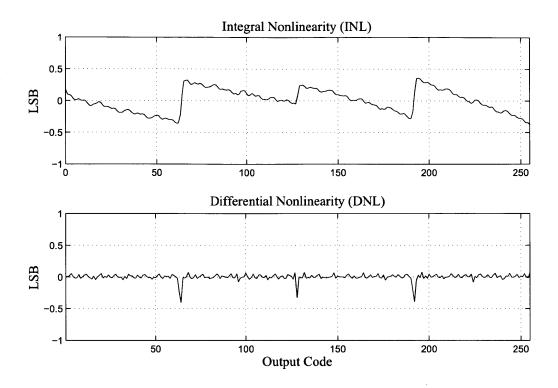

| 3-47 | Low-frequency INL and DNL plots of our ADC. The INL is obtained         |      |

|      | using the least-squared approximation                                   | 125  |

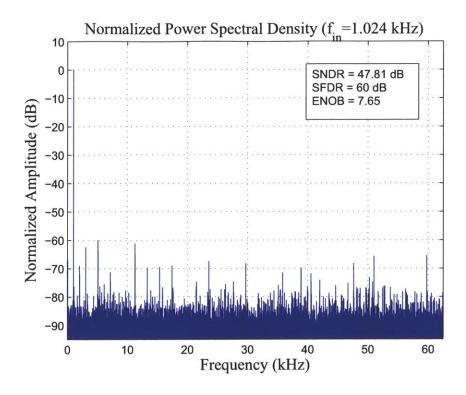

| 3-48 | Measured output spectrum of the ADC with a rail-to-rail input sine      |      |

|      | wave of 1.024 kHz                                                       | 126  |

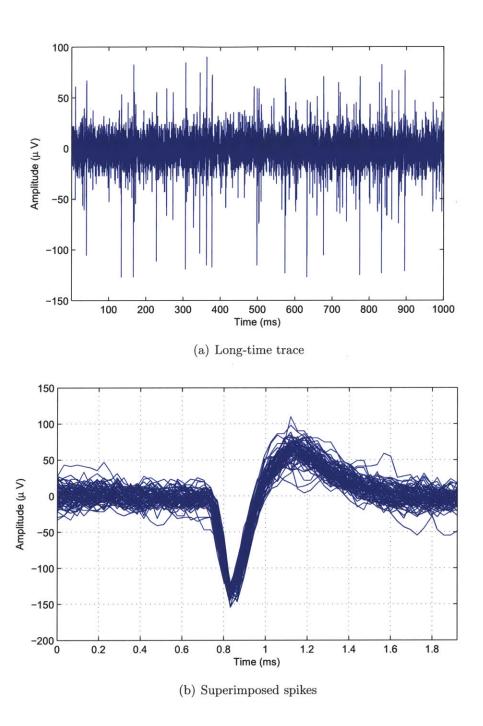

| 3-49 | Electrode-referred neural signals recorded from the brain of a rhesus   |      |

|      | macaque and transmitted wirelessly: (a) 1-second long raw neural data.  |      |

|      | (b) 74 superimposed spikes                                              | 127  |

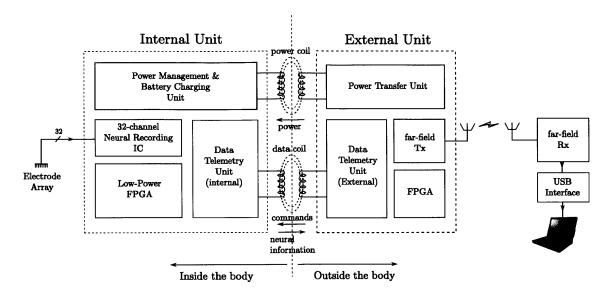

| 4-1  | Block diagram of our implantable wireless neural recording system       | 132  |

| 4-2  | Block diagram of the Internal Unit                                      | 140  |

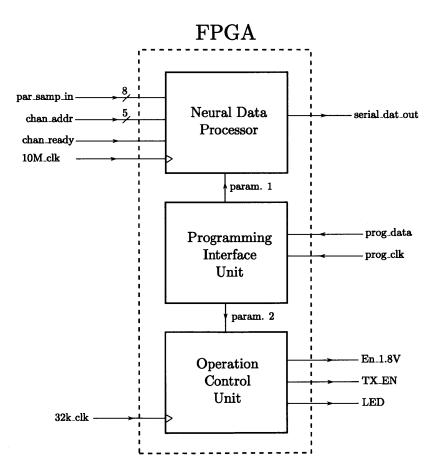

| 4-3  | Block diagram of the synthesized system on the FPGA                     | 142  |

| 4-4  | Block diagram of the Neural Data Processor implemented on the FPGA      | .147 |

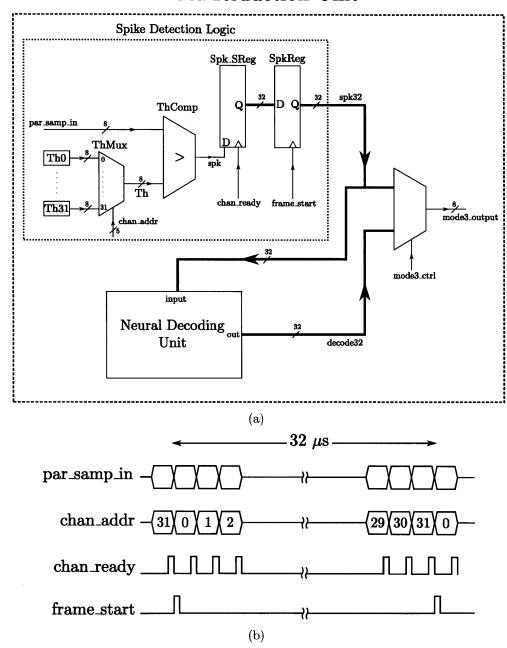

| 4-5  | (a) Block diagram of the Data Reduction Unit. (b) Timing diagram        |      |

|      | of the input signals                                                    | 149  |

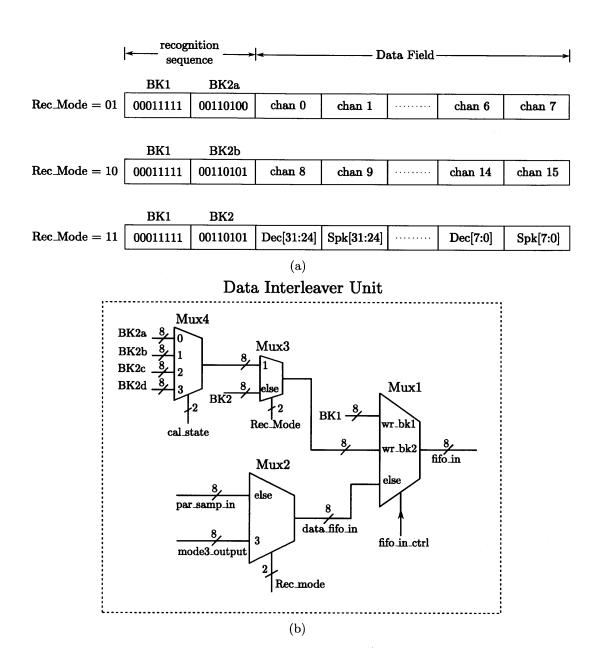

| 4-6  | (a) Output data format for different output modes. (b) Block diagram    |      |

|      | of the Data Interleaver Unit                                            | 151  |

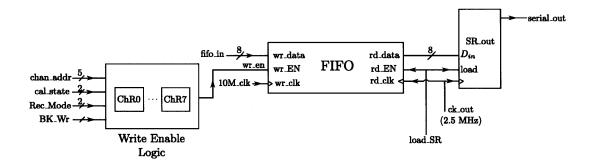

| 4-7  | Block diagram of the Data Serializer Unit                               | 153  |

| 4-8  | (a) Block diagram of the Central Control Unit. (b) Timing diagram of    |      |

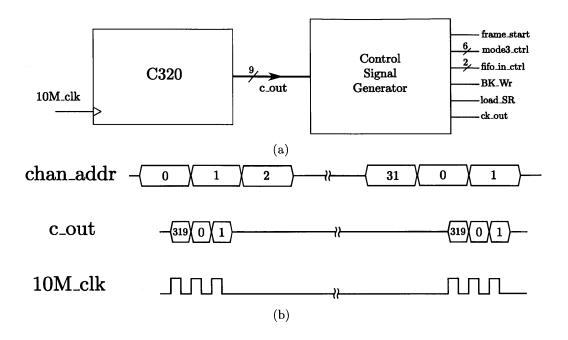

|      | the 9-bit counter C320 used in the Central Control Unit                 | 155  |

| 4-9  | State diagram of the state machine in the Operation Control Unit        | 161  |

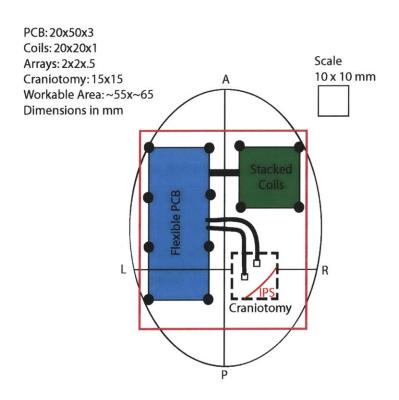

| 4-10 | Conceptual diagram showing the planned physical dimensions of the       |      |

|      | internal unit relative to the surgery area on a rhesus macaque's skull. | 164  |

| 4-11 | (a) Populated internal unit. (b) Flexible PCB substrate of the internal |      |

|      | unit                                                                    | 165  |

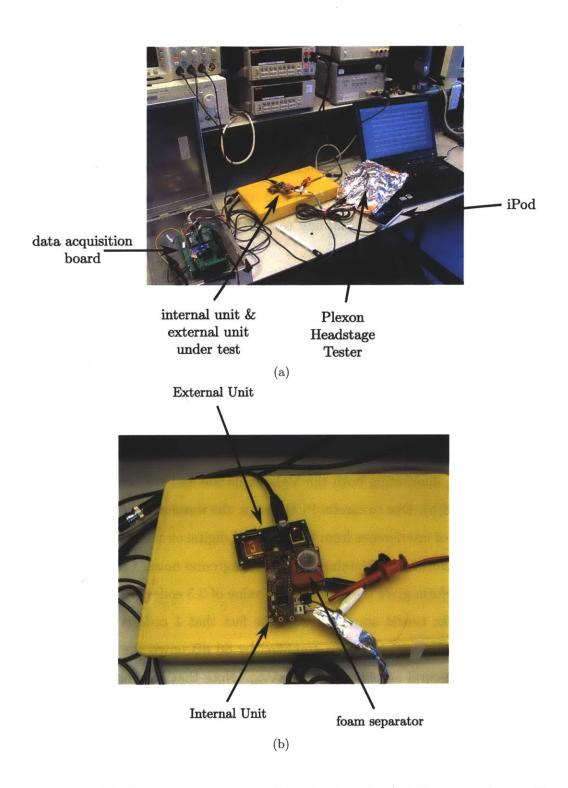

| 4-12 | (a) Experimental setup of the implantable wireless neural recording   |     |

|------|-----------------------------------------------------------------------|-----|

|      | system. (b) Internal unit and external unit under test                | 167 |

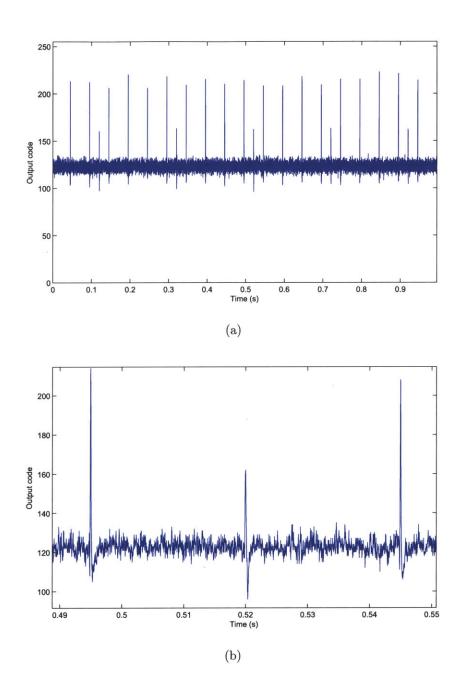

| 4-13 | Digitized neural data from one of the recording channels (gain $= 60$ |     |

|      | dB) of the implantable wireless neural recording system (a) Long-time |     |

|      | trace. (b) Short-time trace                                           | 169 |

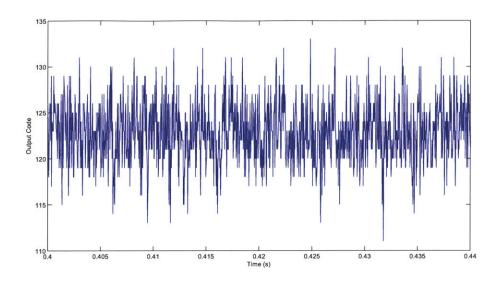

| 4-14 | A short-time trace showing the noise of the waveform in Fig. 4-13(a). | 170 |

## List of Tables

| 2.1 | Operating Points for Transistors in the OTA with $I_{tot} = 2.7 \ \mu A$ | 37  |

|-----|--------------------------------------------------------------------------|-----|

| 2.2 | Comparison of reported neural amplifiers                                 | 45  |

| 2.3 | Measured Performance Characteristics                                     | 46  |

| 2.4 | Measured Performance Characteristics of LFP Amplifier                    | 51  |

| 3.1 | Transistor sizings of the OTA in the amplifier $A_1$                     | 72  |

| 3.2 | Gains of the programmable-gain amplifier                                 | 75  |

| 3.3 | Performance Summary of the Neural Amplifier                              | 122 |

| 3.4 | Performance Summary of the Analog to Digital Converter                   | 125 |

| 3.5 | System Level Performance                                                 | 128 |

| 3.6 | Comparison to other state-of-the-art neural recording systems            | 129 |

| 4.1 | Rec_Mode vs. Output Format of the Neural Data Processor                  | 146 |

| 4.2 | Table summarizing the purposes of state machine's inputs                 | 160 |

| 4.3 | Parameter registers to be programmed by the user                         | 162 |

| 4.4 | Table summarizing the purposes of different "Op Code"                    | 163 |

| 4.5 | System Level Performance                                                 | 171 |

| 4.6 | Comparison to other state-of-the-art implantable wireless neural record- |     |

|     | ing systems                                                              | 172 |

## Chapter 1

### Introduction

This chapter of the thesis motivates the need for ultra-low-power implantable wireless neural recording systems, informs the readers of prior works in this area, presents the design approach of the system to be discussed later in this thesis, and outlines the organization of the thesis.

#### 1.1 Motivation

In the past few decades, direct recordings from the cortical area of the brain have enabled scientists to gradually understand and unlock the secrets of neural coding. With the aid of high-density microelectrode arrays, neural activities from a large population of neurons can be observed simultaneously with a spatial resolution down to that of a single cell [29], [35]. Many experiments in non-human primates [70], [64], [58] and a pilot clinical trial in a human subject [27] illustrated that control signals directly derived from spiking activities from a population of neurons in the cortical area of the brain can be used to successfully control and manipulate computer devices or robotic limbs. The study in [67] shows that cortical activities from a population of neurons can be used to control even a sophisticated device such as a robotic limb with multiple degrees of freedom. These studies have shown great promises for a successful development of practical brain-machine interfaces (BMIs) to restore lost body functions to patients with disorders in central nervous system

such as those suffering from spinal cord injuries. Practical BMI systems of the future will be portable and may enable the users to control dexterous robotic limbs or their natural limbs at a near-natural level.

Nevertheless, to reach a stage where such BMIs can be used chronically in humans, many challenges need to be solved. BMI systems require the use of neural recording systems to obtain neural data. In the studies mentioned earlier, neural recordings were performed with passive microprobes that were implanted in the cortical area of the brain. The implanted microprobes were then connected by a bundle of transcutaneous wires to external recording electronics. These recording electronics were normally large in size and consumed watts of power, and thus needed to be mounted on a rack or a subject's wheel chair. In addition, the transcutaneous connections also pose a major risk of infection due to the skin rupture, and thus must be eliminated in practical BMIs. Therefore, for clinically viable BMIs, the recording systems should be entirely implanted under the skin, while the recorded neural data and the power to operate the implants must be transferred through wireless means. This implantability requirement poses major constraints on the size and total power consumption of the recording systems.

To avoid excessive heat dissipation that may cause cell deaths in the surrounding tissues, the total power dissipation from the recording systems should be kept below a 10 mW range. For the battery-operated recording systems, low power consumption could prolong the time between recharges, thus expanding battery life to avoid frequent surgeries for battery replacements. Power dissipation of an implantable recording system is also a strong determinant of its size and cost. Low power consumption means that small batteries can be used to power the recording systems. In the case when the recording systems are to be continuously powered, a smaller RF coil can be used to receive RF power to operate the systems. With a small-sized implant, the cost of packaging reduces as well and the complexity of the surgical procedure for implanting such system may significantly decrease [53]. Due to these reasons, minimizing power consumption of implanted neural recording systems should be the priority in the design of BMIs.

#### 1.2 Previous Work

Many recording systems with intended use in wireless neural recording applications have been reported in the literature. A number of design approaches have been pursued that portray the compromise among design flexibility, turnaround time, power consumption, and sizes. Advances in integrated circuit (IC) technologies have enabled engineers to increase the number of recording channels and signal processing functions that can be put on a single chip, while still decreasing the size and improving performance. Such technology advancement provides an excellent mean for a development of neural recording systems since a large number of recording channels, signal processing functionalities, and wireless communication circuitry can be integrated in a small form factor, while consuming low enough power to make full implantations of such systems feasible. Thus, for the purposes of minimizing power consumption and reducing the size of the systems, an application-specific integrated circuit (ASIC) approach in which all functionalities are custom designed as integrated circuits (ICs) is normally pursued. However, this ASIC approach has a slow turnaround time due to the design and fabrication of the ICs. Furthermore, design flexibility is sacrificed since the functionalities cannot be easily changed once the ICs have been fabricated.

Examples of the systems that utilized the ASIC approach were reported in [42], [26], [62]. The system reported in [42] contains a total of 32 neural recording channels, which are grouped into four neural probes. Each 8-channel neural probe contains a front-end selection circuitry that multiplexes from 64 recording sites to eight neural amplifiers on the neural probe. The outputs of the eight neural amplifiers on each neural probe are time-multiplexed to drive an ADC on a data-compression ASIC. The data compression ASIC then utilizes a window thresholding method for spike detection to reduce the amount of data that needs to be transmitted wirelessly. The spike waveforms that cross predefined threshold levels and the corresponding addresses of the electrodes are reported at 5-bit resolution. Without a wireless transmission feature, the total power of the recording system including the four neural probes and the data-compression ASIC was reported to be 5.4 mW. This multi-chip system is

integrated on a 3-dimensional platform. The system in [26] integrates all the functionalities including neural signal amplification, data reduction, neural signal digitization, and wireless communication into a single chip. It contains 100 neural recording channels and includes a wireless data transmission feature by a fully-integrated FSK transmitter. The power and commands are transferred from an external unit to the implanted system via an inductive power link. The system utilizes a simple thresholding scheme with analog spike detection circuitry to reduce the amount of data that needs to be transmitted. The system allows one raw analog channel to be selected for full digitization at 10-bit resolution by an on-chip ADC. The total power consumption of the system is 13.5 mW. Another system reported in [62] contains 64 recording channels. To record from 64 channels, the system utilizes four 16-channel neural preconditioning ASICs in parallel. The preconditioning ASICs are interfaced with a neural processing unit which consists of two 32-channel neural processing chips [61]. The system also contains a bi-directional telemetry chip for transmitting neural data to the external world, and for receiving power, commands, and clock to operate the implant. The overall multi-chip system is integrated on a Si-platform and consumes a total power of 14.4 mW.

At the other end of the spectrum, many recording systems are constructed from commercially available parts which are integrated into a system at the printed-circuit-board (PCB) level. Some of these systems contain programmable logic devices such as Field-Programmable Gate Arrays (FPGAs), complex programmable logic devices (CPLDs), or microcontrollers, to implement digital signal processing functions for the recording systems. Clearly, this approach results in a faster turnaround time compared to the full-ASIC approach, and offers greater design flexibility due to the uses of programmable logic devices or microcontrollers. With such approach, signal processing algorithms can be readily modified even after the hardware has been built. The clear disadvantage of this approach is its high power consumption and the larger size of the systems. As a result, most systems constructed from this approach are not yet suitable for chronic implantation in human subjects since the power consumption is still too high to be considered safe for the surrounding tissues. However, these

systems have proved to be tremendously useful in neuroscience studies where animal subjects are employed [52], [49]. The system in [52] consists of an analog module interfaced with a digital module. The analog module consists of two 8:1 input analog multiplexers that multiplexes 16 input channels into two neural recording channels. Each recording channel consists of a unity-gain buffer, a differential amplifier, and a filter, all built from commercially-available parts. The digital module consists of a microcontroller with a built-in ADC. The microcontroller is interfaced with a compact flash memory for storing neural data during the experiment. The system reported in [49] contains a total of 96 recording channels which are grouped into three digitizing headstage modules. Each 32-channel module consists of two custom ICs, with each IC containing 16 neural amplifiers, a 16:1 analog multiplexer, and a digital-to-analog converter (DAC) to control offset voltages of the amplifiers. The two custom ICs are interfaced with commercially-available ADCs, while the clock and control signals for the custom ICs are generated from a commercially-available CPLD. The three digitizing headstage modules are interfaced with the implantable central communication module. The communication module consists of an FPGA, which is designed to reduce the amount of data received from the three headstages [50], the RF data transceiver for data and commands communications, voltage rectifiers and power regulators to generate DC supply voltages from received RF power. The total power consumption of the implantable part of this system is close to 2 W.

#### 1.3 Our Approach

It is my belief that, at present, the scientific community is still in an early stage of BMI system development. Neural data processing algorithms such as spike detection [40], [74], [9], spike sorting [73], [66], and neural data compression [39] are currently being developed by many research groups around the world to help improve performance of BMIs. While achieving low power consumption is a crucial aspect for the design of an implantable neural recording system, design flexibility should not be completely ignored. While an all-ASIC approach can result in low power consump-

tion and small form factor, at this stage, it might be too early for such systems to be widely useful. For instance, while the simple thresholding method in [26] might be effective at reducing the amount of data that needs to be transmitted, some important information such as spike amplitudes and spike shapes are lost, thus preventing the uses of many processing algorithms previously mentioned. On the contrary, flexible systems such as [49] can provide richer functionalities and these functionalities can even be modified during the experimental stage, even after the hardware has been built, by reprogramming the in-system programable logic devices. However, the total power consumption of close to 2 watts in [49] would prevent such system to be used chronically in human subjects.

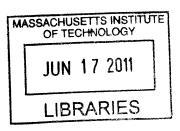

The most suitable approach at the current stage of BMI development might lie somewhere in between these two extremes. By combining good energy efficiency from low-power ASICs, and design flexibility from commercial programmable logic devices, a low-power neural recording system that is also highly programmable can be built. This thesis presents a development of such neural recording system with the goal of practical use in brain-machine interfaces. The ASIC approach is utilized for parts of the system that require excellent energy efficiency, while an FPGA is used where design flexibility is more important. Figure 1-1 shows the conceptual diagram of the implantable wireless neural recording system to be presented in this thesis. The system consists of an internal unit and an external unit. The internal unit consists of a front-end processing stage that amplifies and digitizes neural signals from recording electrodes. The digitized neural data from the front-end processing stage is then processed by a digital signal processing module on the internal unit, before the processed neural data is transmitted to the external unit via a wireless data telemetry system. The external unit receives the neural data and relays it to a remote device such as a computer or a robotic limb. For system programmability, the communication between the internal unit and the external unit is bidirectional. In addition to transmitting the processed neural data from the internal unit to the external unit (uplink), the wireless data telemetry system can transmit commands in the reverse direction to configure the parameters of the internal unit (downlink). In

Figure 1-1: Conceptual diagram of our BMI system.

addition, the external unit is responsible for delivering power wirelessly to charge the implanted battery that powers the internal unit.

Due to the stringent requirement on power dissipation inside the body, the goal of this thesis is to minimize power dissipation of the internal unit without compromising its performance. Since the power consumption of the front-end processing stage normally constitutes the majority of the total system power, it is implemented with a full-ASIC approach to achieve minimal power consumption. The processing of the digitized neural data is performed in an on-board FPGA to offer design flexibility during the system development.

#### 1.4 Author's Contribution

It might be clear to the readers that the amount of work required to develope an implantable wireless neural recording system, such as that shown in Fig. 1-1, is beyond what one PhD student can handle. The author has been very fortunate to be a part of an excellent research team, and to be the one responsible for integrating the system from various subsystems that other team members have designed. The major

contributions of the author to the neural recording system development are the design and integration of the internal unit, especially the signal processing aspects of it. As part of this thesis, the author has designed, built, and tested an energy-efficient neural amplifiers in a 0.5  $\mu$ m CMOS process. The knowledge gained from designing such neural amplifier was utilized to design a 32-channel neural recording IC in a 0.18  $\mu$ m CMOS process, which is the front-end processing stage of the internal unit. In addition, the author was responsible for the design of signal processing and control algorithms on the FPGA.

#### 1.5 Thesis Organization

While the overall neural recording system will be discussed, this thesis will focus on the design of the internal unit, especially on its signal processing and system control aspects. Chapter 2 presents the design, power and noise minimization techniques, and the experimental measurements of an energy-efficient neural recording amplifier. After the neural amplifier has been introduced, Chapter 3 presents the design and experimental measurements of the 32-channel neural recording IC that forms the heart of the internal unit of the neural recording system. The neural amplifier's topology of the system described in Chapter 3 is greatly influenced by the design techniques presented in Chapter 2. In Chapter 3, the design of each system component of the neural recording IC including the neural amplifier, the analog multiplexer, the analog-to-digital converter, the digital control unit, and the serial programming interface unit will be presented in detail. Experimental measurements from a wireless recording setup in a behaving non-human primate is also presented in this chapter. Chapter 4 discusses in more detail the design of the overall neural recording system, with the emphasis on the design of the internal unit and its signal processing aspect. Experimental measurements of the overall neural recording system is also presented. Chapter 5 concludes the thesis, discusses future work, and summarizes the author's contributions to the field of neural recording system design.

## Chapter 2

# An Energy-Efficient Micropower Neural Recording Amplifier

One of the most important components of BMIs is the neural signal amplifier. Neural signals from extracellular recording are very weak (typically with amplitude between 10  $\mu$ V and 500  $\mu$ V). As a result, amplification is needed before such signals can be processed further. Next generation high-channel-count BMIs will incorporate a large number of neural amplifiers (on the order of 100-1000, one for every electrode) to improve the decoding performance. For such applications, ultra-low-power operation is very important to minimize heat dissipation in the brain, preserve long-battery life, and maximize the time between recharges. To get clean neural signal recordings, it is important that the input-referred noise of the amplifier be kept low. Practically, the input-referred noise of the amplifier should be kept below the background noise of the recording site (5  $\mu$ V-10  $\mu$ V) [23]. However, designers must address the tradeoff between low-noise and low-power designs of the amplifier. For an ideal thermalnoise-limited amplifier with a constant bandwidth and supply voltage, the power of the amplifier scales as  $1/v_n^2$  where  $v_n$  is the input-referred noise of the amplifier. This relationship shows a steep power cost of achieving low-noise performance in an amplifier.

Prior to our design being reported in [69], many designs of neural amplifiers had been reported in the literature [24, 36, 41, 45]. Most of these designs consume power

near 100  $\mu$ W to achieve less than 10  $\mu$ V<sub>rms</sub> input-referred noise for bandwidths of 5-10 kHz. The designs in [36,41] consume power near 100  $\mu$ W to achieve about 8-9  $\mu$ V<sub>rms</sub> input-referred noise with approximately 10 kHz of bandwidth. The design in [24] achieves an input-referred noise of 2.2  $\mu$ V<sub>rms</sub> with 7.2 kHz of bandwidth while consuming 80  $\mu$ W of power. If such amplifiers are to be used in a multi-electrode array, with a power near 100  $\mu$ W per amplifier for most designs, the power required for the neural amplifiers can become the limiting factor for the whole multi-electrode system. To address this problem, we present a new micropower neural recording amplifier design. With our design, the power consumption per amplifier is low enough such that the total power consumption of a multi-electrode array may no longer be the bottleneck for the design of brain-machine interfaces.

This chapter is organized as follows. Section 2.1 discusses the high level operation of the amplifier. Section 2.2 describes the design principles and noise analysis used in the OTA to achieve a good power-noise tradeoff. Section 2.3 presents some measured lab bench and *in-vivo* results of the amplifier configured for neural spike recording. Section 2.4 presents experimental results when the amplifier is configured for LFP recording. Section 3.8 concludes the paper.

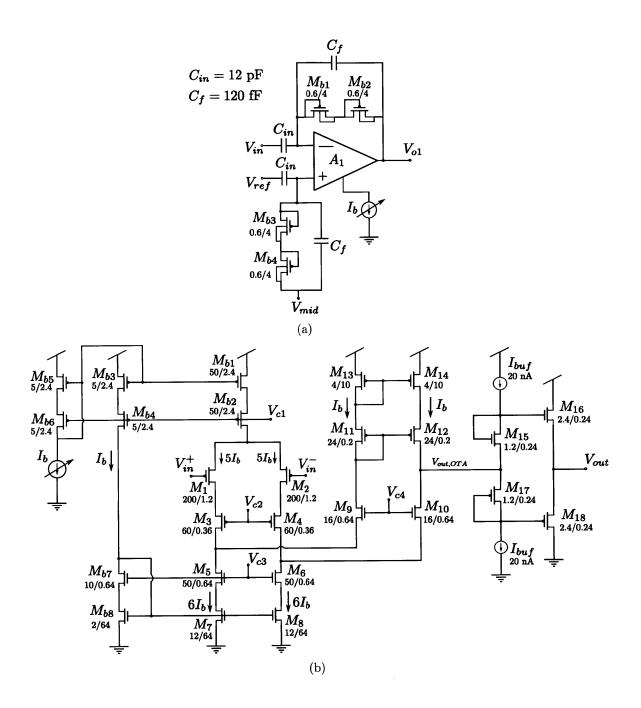

#### 2.1 Overall Architecture of the Neural Amplifier

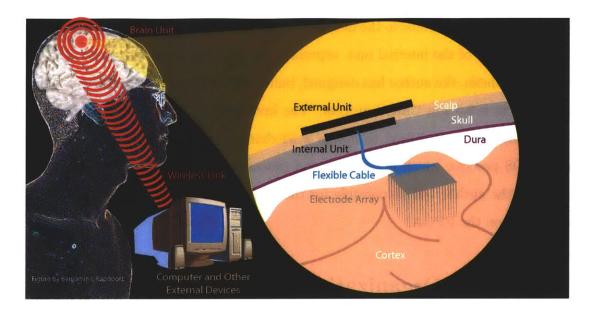

The overall schematic of the neural amplifier is shown in Fig 2-1. The topology of the gain stage is similar to the design in [24]. It uses a capacitively-coupled architecture to reject the DC offset that occurs at the electrode-tissue interface. This design includes a bandpass filter stage following the gain stage to shape the passband of the amplifier. The low-frequency high-pass cutoff of the gain stage is created by the MOS-bipolar pseudoresistor element [14] formed by  $M_{b1}-M_{b2}$  and the capacitance  $C_f$ . The capacitive feedback formed by  $C_f$  and  $C_{in}$  sets the midband gain of the amplifier to approximately 40.8 dB. The high-pass cutoff and the low-pass cutoff frequencies of the amplifier can be adjusted via  $V_{tune}$  and the bias current of the  $g_m$ -OTA in the bandpass-filter stage respectively. With the addition of the bandpass-filter stage,

Figure 2-1: Overall architecture of the Neural Amplifier.

the amplifier can be configured to record either the local field potentials (LFPs) (  $< 1~\rm Hz$  to 300 Hz) or neural spikes (300 Hz to  $> 1~\rm kHz$ ). For low-bandwidth LFP recording, the bias current of the OTA in the gain stage can be lowered to conserve power. It is worth mentioning that the high-pass cutoff frequency of the gain stage should be kept as low as possible. As reported in [45], placing a weak-inversion MOS transistor in parallel with  $C_f$  to create a high-pass filter with a cutoff frequency at a few hundred Hz introduces low-frequency noise that rolls off as  $1/f^2$  in power units due to the noise from the transistor being low-pass filtered by  $C_f$ . This low-frequency noise appears at the front-end and gets amplified by the gain of the amplifier thereby degrading the minimum detectable signal. In our design as well as in [24], however, the MOS-bipolar pseudoresistor element's noise is at very low frequencies since the MOS-bipolar pseudoresistor element has a much higher impedance than a weak-inversion MOS transistor. Therefore, low-frequency noise due to this element is filtered out well before the passband and does not appear in the frequency band of interest.

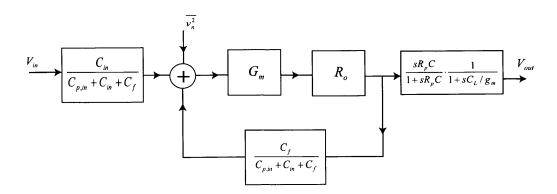

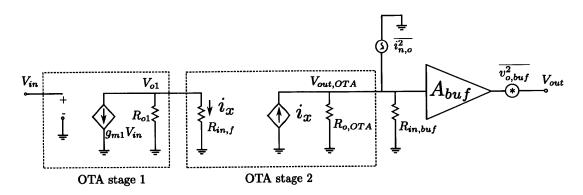

Figure 2-2: Block diagram of our neural amplifier including the input noise source of the OTA.

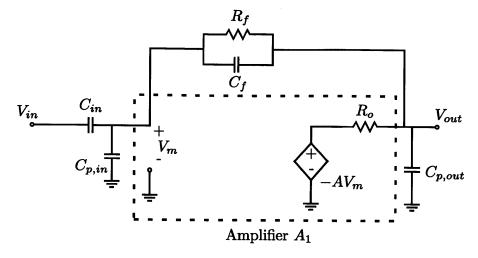

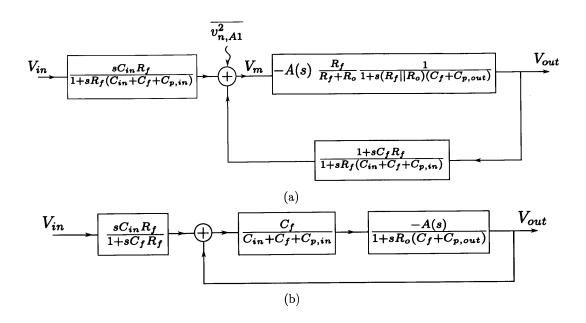

The operation of our amplifier can easily be understood by the block diagram of Fig 2-2. We include  $C_{p,in}$  to model parasitic gate capacitances at input terminals of the gain-stage OTA. The input referred-noise of the OTA is modeled as a  $\overline{v_n^2}$  term added to the system at the input of the gain-stage OTA. The gain-stage OTA is used as a high-gain amplifier and is modeled by  $G_m$  and  $R_o$  blocks where  $G_m$  and  $R_o$  represents the transconductance and the output resistance of the gain-stage OTA respectively. In the bandpass-filter stage,  $R_p$  is the resistance of the series PMOS transistors operating in the triode regime. The value of  $R_p$  is set by  $V_{tune}$ . The combination of C and  $R_p$  realizes the highpass cutoff frequency for the amplifier. From the small-signal block diagram in Fig. 2-2, assuming that  $G_m R_o$  is much higher than 1, we can express the transfer function of the neural amplifier as

$$H(s) = \frac{V_{out}(s)}{V_{in}(s)} = -\frac{C_{in}}{C_f} \cdot \frac{sR_pC}{1 + sR_pC} \cdot \frac{1}{1 + sg_mC_L}.$$

(2.1)

The midband gain of the amplifier is  $A_v = -C_{in}/C_f$ . The highpass cutoff frequency is at  $f_{HP} = 1/(2\pi R_p C)$  whereas the lowpass cutoff frequency is at  $f_{LP} = g_m/(2\pi C_L)$ . We can relate the input-referred noise  $\overline{v_n^2}$  of the gain-stage OTA to the input-referred noise  $\overline{v_{n,amp}^2}$  of the overall amplifier as

$$\overline{v_{n,amp}^2} = \left(\frac{C_{in} + C_f + C_{p,in}}{C_{in}}\right)^2 \cdot \overline{v_n^2}.$$

(2.2)

Figure 2-3: Schematic of the low-noise OTA used in this design.

The input-referred noise of the bandpass filter stage is insignificant and is not included in the block diagram since the gain of 40 dB of the gain stage alleviates the bandpass-filter stage's input-referred noise requirement. As a result, the power consumption of the bandpass filter stage is much smaller than that of the gain stage. Thus, to achieve low-noise performance, it is important to design the gain-stage OTA to have low input-referred noise. Section 2.2 describes the low-noise low-power design techniques used in this OTA.

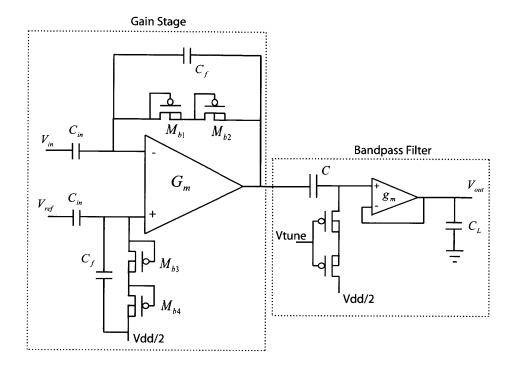

### 2.2 Low-Power Low-Noise OTA design for gain stage

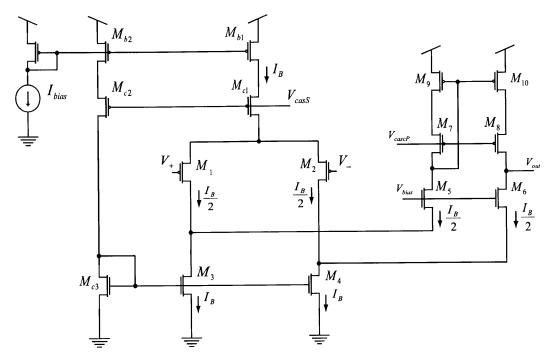

The schematic of the low-noise OTA is shown in Fig. 2-3. It is a modified version of a standard folded-cascode topology shown in Fig. 2-5. The OTA in Fig. 2-3 is biased such that the currents of the transistors in the folded branch  $M_7 - M_{12}$  are only a small fraction of the current in the input differential pair transistors  $M_1$  and  $M_2$ . In our design, the channel current in  $M_7 - M_{12}$  is scaled to approximately  $1/16^{th}$

Figure 2-4: Circuit schematic for analyzing current scaling in the source-degenerated current mirrors of Fig. 2-3.

of the current in  $M_1$  and  $M_2$ . The much lower current in  $M_7 - M_{12}$  makes the noise contributed by them negligible compared to that from  $M_1$  and  $M_2$ . As a result, we simultaneously lower the total current and the total input-referred noise of the OTA.

To ensure that such severe current scaling is achieved, we carefully set the bias currents of  $M_5$  and  $M_6$  through the use of the bias circuit formed by  $M_{b2}$ ,  $M_{c2}$  and  $M_{c3}$ . The current sources  $M_{b1}$ ,  $M_{b2}$  are cascoded to improve their output impedances and thereby ensure accurate current scaling. They operate in strong inversion to reduce the effect of threshold voltage variations. The source-degenerated current mirrors formed by  $M_{c3}$ ,  $M_5$  and  $M_6$  and resistors  $R_1$  and  $R_2$  set the currents in  $M_5$  and  $M_6$  such that the currents in  $M_7$  and  $M_8$  (the difference between the current in  $M_3$ and  $M_5$  and between the current in  $M_4$  and  $M_6$ ) are a small fraction of the currents in  $M_1$  and  $M_2$ . An analysis of mismatches in source-degenerated current mirrors is deferred until Section 2.2.3 and is important for robust biasing performance. In order to save power in the bias circuit, the current scaling ratio between  $M_{b1}$  and  $M_{b2}$  is 16:1  $(2I_B/32)$  as shown in Fig. 2-3. To set the currents in the folded-branch transistors to be  $I_B/32$ , which is  $1/16^{th}$  of the currents in differential-pair transistors, we set the current in  $M_5$  and  $M_6$  to be  $17I_B/32$ . Such current ratioing is achieved by making  $R_3$  to be  $17R_1/2 = 17R_2/2$ , and constructing  $M_{c3}$  as a parallel combination of two unit transistors while  $M_5$  and  $M_6$  are each constructed from 17 unit transistors in parallel. To clarify this scaling further, the current mirror formed by  $M_{c3}$ ,  $R_3$  and  $M_5$ ,  $R_1$  in Fig. 2-3 is transformed into an equivalent circuit comprised of many source-degenerated unit transistors as shown in Fig. 2-4. All source-degenerated unit transistors are identical and have the same gate voltage. For any gate voltage there is only one source voltage at which a unit resistor's current equals a unit transistor's current. Thus, the nominal channel currents in all unit transistors are identical and the total current in  $M_5$  is 17/2 times the current in  $M_{c3}$  as desired.

For the amplifier to have low input-referred noise, the transconductance  $G_m$  of the OTA needs to be maximal for a given current level. For the standard folded-cascode OTA shown in Fig. 2-5, the impedance looking into the sources of  $M_5$  and  $M_6$  is much smaller than the impedance looking into the drains of  $M_1 - M_4$ . As a result, the standard folded-cascode OTA achieves an overall transconductance  $G_m$  near  $g_{m1}$ , the  $g_m$  of  $M_1$ . However, if we lower the current in  $M_5 - M_{10}$  to be a small fraction of the current in  $M_1$  and  $M_2$ , the impedance looking into the sources of  $M_5$  and  $M_6$  can be a significant portion of the impedance looking into the drains of  $M_1 - M_4$  such that incremental currents do not almost all go through the sources of  $M_5$  and  $M_6$  in the current divider formed between the sources of  $M_5$  and the drains of  $M_1$  and  $M_3$ . Therefore,  $G_m$  is significantly less than  $g_{m1}$ . Section 2.2.1 explains how we achieve  $G_m$  near  $g_{m1}$  even with our extreme current scaling via the use of source-degenerated transistors  $M_5$  and  $M_6$  in Fig. 2-3.

In the standard folded-cascode topology shown in Fig 2-5, the current sources formed by  $M_3$  and  $M_4$  contribute a significant amount of noise due to their large channel currents. In this design, we replace the current-source transistors  $M_3$  and  $M_4$  in Fig. 2-5 with source-degenerated current sources formed by  $M_5$  and  $M_6$  and degeneration resistors  $R_1$  and  $R_2$  as shown in Fig. 2-3. With an appropriate choice of degeneration resistance, the noise contributions from the source-degenerated current sources are mainly from the resistors and can be made much smaller than the noise contributions from MOS transistors operating at the same current level. Another benefit of using source-degenerated current sources is that the noise from resistors is mainly thermal noise while NMOS current sources contribute a large amount of 1/f noise unless they are made with very large area. As a result, the 1/f noise in

Figure 2-5: Schematic of a standard folded-cascode OTA.

our neural amplifier is mainly from the input differential pair. Therefore, the input-differential pair is made with large-area PMOS transistors, which have lower 1/f noise than similarly-sized NMOS transistors in most CMOS processes.

#### 2.2.1 Device sizing for maximizing $G_m$

To achieve low input-referred noise, it is important that the transconductance of the OTA be maximized for a given total current. The maximum transconductance of the standard folded-cascode OTA that can be achieved is the transconductance of one of the transistors in the input-differential pair, say  $g_{m1}$ . As a result, it is advantageous to operate  $M_1$  and  $M_2$  in the subthreshold regime where a transistor's  $g_m$  is maximized for a given current level. Therefore,  $M_1$  and  $M_2$  need to have large W/L ratios. The lengths of  $M_1$  and  $M_2$  then need to be small such that their widths stay relatively small and the input capacitance of the amplifier is not too large.

In order to make sure that all the incremental current caused by the differential input goes through the sources of  $M_7$  and  $M_8$ , we cascode the input differential-

Figure 2-6: Circuit schematics for obtaining admittance formula.

pair transistors with  $M_3$  and  $M_4$  to increase their output impedances. The source-degenerated current sources formed by  $M_5$  and  $R_1$  and by  $M_6$  and  $R_2$  are designed to have large output impedances as well. The output impedances of the cascoded input-differential pair and the source-degenerated current sources need to be much larger than the impedance looking into the sources of  $M_7$  and  $M_8$  such that  $G_m$  is near  $g_{m1}$ .

Before we analyze the operation of the OTA in Fig. 2-3, we shall briefly review two useful admittance formulas. The first one is the formula for the admittance looking into the source of an MOS transistor when its drain is connected to an impedance to incremental ground as shown in Fig. 2-6(a). The second useful formula is the admittance looking into the drain of a cascode transistor as shown in Fig. 2-6(b). Using a nodal analysis, we obtain the two admittances to be

$$G_s = \frac{i_s}{v_s} = \frac{g_{s1} + 1/r_{o1}}{1 + Z_L/r_{o1}},\tag{2.3}$$

$$G_d = \frac{i_d}{v_d} = \frac{1}{r_{o1}} \cdot \left(\frac{1}{1 + g_{s1}Z_L + Z_L/r_{o1}}\right)$$

(2.4)

Let  $G_{s3}$  be the admittance looking into the sources of  $M_3$  and  $M_4$ ,  $G_{d5}$  be the admittance looking into the drains of  $M_5$  and  $M_6$ , and  $G_{s7}$  be the admittance looking into the sources of  $M_7$  and  $M_8$  of the OTA in Fig. 2-3. We can express the transconduc-

tance  $G_m$  of the OTA as

$$G_m = g_{m1} \cdot \left(\frac{G_{s7}}{G_{s7} + G_{d5}}\right) \left(\frac{G_{s3}r_{o1}}{1 + G_{s3}r_{o1}}\right). \tag{2.5}$$

We can express  $G_{s3}$ ,  $G_{s7}$  and  $G_{d5}$  by using (2.3) and (2.4) as

$$G_{s3} = \frac{g_{s3} + 1/r_{o3}}{1 + 1/(r_{o3}(G_{s7} + G_{d5}))}$$

(2.6)

$$\approx \frac{g_{s3}}{1 + 1/(r_{o3}(G_{s7} + G_{d5}))},$$

(2.7)

$$G_{s7} = \frac{g_{s7} + 1/r_{o7}}{1 + (1/g_{m11})/r_{o7}}$$

(2.8)

$$\approx \left(\frac{g_{m11}r_{o7}}{1 + g_{m11}r_{o7}}\right) \cdot g_{s7},$$

(2.9)

and

$$G_{d5} = \frac{1}{r_{o5}} \frac{1}{1 + R_1/r_{o5} + g_{s5}R_1} \tag{2.10}$$

where  $g_{si}$  and  $r_{oi}$  are the incremental source admittance of  $M_i$  with its drain at incremental ground, and the output resistance of  $M_i$  respectively. The expressions from (2.7)-(2.10) present the design constraints for sizing and biasing each device to achieve  $G_m$  close to  $g_{m1}$ . The size, the channel current and the simulated intrinsic gain  $(g_s r_o)$  of each transistor in the OTA are shown in Table 3.1. From (2.5), in order to make  $G_m$  close to  $g_{m1}$ , the ratios  $G_{s7}/(G_{s7} + G_{d5})$  and  $G_{s3}r_{o1}/(1 + G_{s3}r_{o1})$  should be made as close to 1 as possible. The ratio  $G_{s7}/(G_{s7} + G_{d5})$  represents the incremental current gain from the drain of  $M_3$  and  $M_4$  to the output. The incremental current gain from the input differential pair transistors to the drain of the cascode transistors  $M_3$  and  $M_4$  is  $G_{s3}r_{o1}/(1 + G_{s3}r_{o1})$ .

In order to maximize the ratio  $G_{s7}/(G_{s7}+G_{d5})$ , we try to make  $G_{d5} \ll G_{s7}$ . Since  $M_{11}$  and  $M_{7}$  have the same channel current,  $g_{m11} \approx g_{m7}$ . Therefore,  $g_{m11}r_{o7} \approx g_{m7}r_{o7} \gg 1$  and we have  $G_{s7} \approx g_{s7}$ . In order to make  $G_{d5} \ll G_{s7}$ , we need to minimize  $G_{d5}$ . From (2.10), we can minimize  $G_{d5}$  by making  $r_{o5}$  large and also making  $g_{s5}R_1 \gg 1$ . Therefore, we make  $M_5$  and  $M_6$  with large W/L ratios and with long channel lengths to achieve large  $g_{s5}$  and  $r_{o5}$  respectively. Then we choose  $R_1$  such that  $g_{s5}R_1 \gg 1$ .

In order to maximize the ratio  $G_{s3}r_{o1}/(1+G_{s3}r_{o1})$ , we need to make  $G_{s3}r_{o1}\gg 1$ . From (2.7),  $G_{s3}$  is approximately  $g_{s3}$  if  $G_{s7}r_{o3}$  is much greater than 1. Since  $G_{s7}\approx g_{s7}$ , we have  $G_{s7}r_{o3}\approx g_{s7}r_{o3}$ . Since the current in  $M_7$  is about 1/16 of the current in  $M_3$  and both transistors are operating in subthreshold,  $g_{s7}\approx g_{s3}/16$ . From simulation, we achieve  $g_{s3}r_{o3}$  of 119 which results in a  $g_{s7}r_{o3}$  of 7.43. The expression in (2.7) is thus reduced to  $G_{s3}\approx 0.88g_{s3}$ . Note that  $M_1$  and  $M_3$  have the same currents and the same channel lengths. Thus  $M_1$  and  $M_3$  should have  $r_{o1}=r_{o3}$ . As a result,  $G_{s3}r_{o1}\approx G_{s3}r_{o3}\approx (0.88g_{s3})r_{o3}=104$ . Therefore, the ratio  $G_{s3}r_{o1}/(1+G_{s3}r_{o1})$  is close to 1. As a result, we are able to achieve  $G_m$  close to  $g_{m1}$  even with sixteen-fold current scaling between the input differential-pair transistors and the folded-branch transistors.

### 2.2.2 OTA Noise Analysis

The noise in cascode transistors typically contributes little to the overall noise in an OTA [54] because these transistors self shunt their own current noise sources: A cascode transistor's current noise is attenuated by a factor of  $1/(1+g_sR)^2$  where  $g_s$  is its incremental source transconductance and R is the effective source-degeneration resistance respectively. Therefore, the only noise sources that are significant in Fig. 2-3 are due to non-cascode transistors, i.e., the differential-pair input transistors  $M_1$  and  $M_2$ , the resistors  $R_1$  and  $R_2$ , and the current-mirror transistors  $M_{11}$  and  $M_{12}$ . We

Table 2.1: Operating Points for Transistors in the OTA with  $I_{tot} = 2.7 \mu A$

| Devices          | $\mathbf{W}/\mathbf{L}$ $(\mu m)$ | $I_{\mathrm{D}}$ | $\mathbf{g_sr_o}$ | Operating Region              |

|------------------|-----------------------------------|------------------|-------------------|-------------------------------|

| $M_1, M_2$       | 399/1.2                           | $1.18~\mu A$     | 133               | subthreshold                  |

| $M_3, M_4$       | 100.5/1.2                         | $1.18~\mu A$     | 119               | $\operatorname{subthreshold}$ |

| $M_5, M_6$       | 204/6                             | $1.25~\mu A$     | 322               | $\operatorname{subthreshold}$ |

| $M_7, M_8$       | 3.6/1.5                           | 68~nA            | 164               | $\operatorname{subthreshold}$ |

| $M_9, M_{10}$    | 6/1.2                             | 68~nA            | 123               | $\operatorname{subthreshold}$ |

| $M_{11}, M_{12}$ | 3.6/2.2                           | 68~nA            | 458               | above-threshold               |

now perform an OTA noise analysis using a method similar to that described in [54].

The admittances looking into the sources of  $M_3$ ,  $M_5$ , and  $M_7$  are approximately  $g_{s3}$ ,  $g_{s5}$ , and  $g_{s7}$  respectively. Then the current transfer function from each significant current noise source in the OTA to an incrementally grounded output can be calculated to be

$$\frac{\overline{i_{n,out}^2}}{\overline{i_{n,M_1}^2}} = \left(\frac{G_{s3}r_{o1}}{1 + G_{s3}r_{o1}} \cdot \frac{G_{s7}}{G_{s7} + G_{d5}}\right)^2 \tag{2.11}$$

$$\approx \left(\frac{g_{s3}r_{o1}}{1+g_{s3}r_{o1}} \cdot \frac{g_{s7}}{g_{s7}+G_{d5}}\right)^2,$$

(2.12)

$$\frac{\overline{i_{n,out}^2}}{\overline{i_{n,R_1}^2}} = \left(\frac{G_{s5}R_1}{1 + G_{s5}R_1} \cdot \frac{G_{s7}}{G_{s7} + G_{d3}}\right)^2 \tag{2.13}$$

$$\approx \left(\frac{g_{s5}R_1}{1 + g_{s5}R_1} \cdot \frac{g_{s7}}{g_{s7} + G_{d3}}\right)^2, \tag{2.14}$$

and

$$\frac{\overline{i_{n,out}^2}}{\overline{i_{n,M11}^2}} = 1. \tag{2.15}$$

Since this circuit is biased such that  $g_{s3}r_{o1} \gg 1$ ,  $g_{s5}R_1 \gg 1$  and  $g_{s7} \gg G_{d5}$ ,  $G_{d3}$  as explained in Section 2.2.1, the expressions from (2.12)-(2.15) are reduced to 1. For the following discussion, we model the MOSFET's current noise as

$$\overline{i_n^2} = 4\gamma k T g_m \tag{2.16}$$

where k is Boltzmann's constant, T is the absolute temperature,  $g_m$  is the transconductance of the MOSFET, and  $\gamma = 2/3$  for above-threshold operation and  $\gamma = 1/(2\kappa)$  for subthreshold operation. From this noise model, we can calculate the input-referred noise of the OTA as the total output current noise divided by its transconductance  $g_{m1}^2$  to be

$$\overline{v_n^2} = \frac{1}{g_{m1}^2} \left( \frac{4kTg_{m1}}{\kappa} + \frac{8kT}{R_1} + \frac{16}{3}kTg_{m11} \right)$$

(2.17)

where  $M_1$  and  $M_2$  operate in weak inversion and  $M_{11}$  and  $M_{12}$  operate in strong

inversion. Let IC be the inversion coefficient of the transistor which is defined as the ratio of its channel current  $I_D$  to the moderate inversion characteristic current  $I_S$ where  $I_S$  is given by [65]

$$I_S = \frac{2\mu C_{ox} U_T^2}{\kappa} \cdot \frac{W}{L} \tag{2.18}$$

where  $U_T$  is the thermal voltage and is equal to kT/q, where q is the electron charge. Using the EKV model [16], we can estimate the  $g_m$  of each transistor to be

$$g_m = \frac{\kappa I_D}{U_T} \cdot \frac{2}{1 + \sqrt{1 + 4 \cdot \text{IC}}}.$$

(2.19)

We can then rewrite (2.17) as

$$\overline{v_n^2} = \frac{1}{g_{m1}} \cdot \frac{4kT}{\kappa} \left( 1 + \frac{2U_T}{I_1 R_1} + \frac{4}{3} \kappa \alpha \frac{I_{11}}{I_1} \right)$$

(2.20)

where  $\alpha=2/\left(1+\sqrt{1+4\cdot IC_{11}}\right)$ , which is less than 1, and IC<sub>11</sub> is the inversion coefficient of  $M_{11}$  and  $M_{12}$ . Equation (2.20) suggests that in order to minimize the input-referred noise of the OTA,  $I_1R_1$  should be large compared to  $2U_T$ . Furthermore, the current ratio  $I_1/I_{11}$  should be large compared to  $\frac{4}{3}\kappa\alpha$ . For our implementation, the ratio  $I_1/I_{11}$  is 16. For a total supply current of 2.7  $\mu$ A and 5.3 kHz bandwidth,  $I_1$  and  $I_{11}$  are approximately 1.18  $\mu$ A and 68 nA respectively. For  $R_1=240\mathrm{k}\Omega$ , the second and the third terms in (2.20) are  $1.8\times10^{-1}$  and  $5.4\times10^{-2}$  respectively, assuming a temperature of T=300 K,  $\kappa=0.7$  and  $\alpha=1$ . Equivalently, (2.17) is reduced to

$$\overline{v_n^2} = \frac{2kT}{\kappa g_{m1}} \times 2.47. \tag{2.21}$$

Equation (2.21) can be interpreted as 2.47 times the input-referred noise of a MOS transistor operating in weak inversion with a transconductance of  $g_{m1}$ . This means that our OTA effectively has only 2.47 subthreshold devices that contribute noise. This value is close to the theoretical limit of 2 noise sources in any OTA that uses two subthreshold MOS differential-pair transistors as an input stage. Effectively, our design has almost eliminated all other sources of noise except for that of  $M_1$  and  $M_2$ .

Figure 2-7: Circuit schematics for analyzing  $V_T$  and R mismatches in source-degenerated current mirrors.

### 2.2.3 Current mirror mismatch analysis

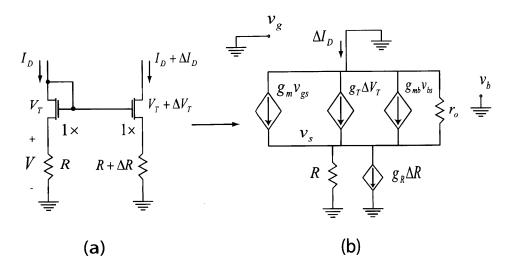

The key techniques for achieving good power-noise tradeoff in this amplifier are the uses of source-degenerated current mirrors and the severe current scaling ratio between the input-differential pair transistors and the folded-branch transistors. The severe current scaling scheme can work only if the current errors due to mirroring are well controlled: The amplifier would not work if the error due to current scaling is too large such that none of the current flows in  $M_7$ - $M_{12}$  in the OTA of Fig.2-3. Thus, we address and investigate this concern to ensure the correct operation of our amplifier. Let us consider the current matching between two unit transistors in Fig. 2-4 due to variations in the threshold voltage and variations in the source-degeneration resistance. We shall model these variations as errors in the parameters of each of the unit transistors of Fig. 2-4. Let the nominal current in one of the unit transistors of  $M_{c3}$  be  $I_D$  and consider the deviation in current  $\Delta I_D$  in one of the unit transistors of  $M_5$  from its nominal value due to deviations in the threshold voltage  $\Delta V_T$ and deviations in the source-degeneration resistor  $\Delta R$  as shown in Fig. 2-7(a). To model the threshold-voltage mismatch, we use the body-referenced current equation in saturation for an MOS transistor operating in weak inversion [65]. Let the nominal current in each unit transistor be described by

$$I_D = I_s e^{\kappa (V_{GS} - V_T)/U_T} \cdot e^{(1-\kappa)V_{BS}/U_T}.$$

(2.22)

where  $I_s$  is a constant scaling current which is the same for all unit transistors. Let V be the nominal DC voltage drop across R such that  $I_D = V/R$ . We define

$$g_T = \frac{\partial I_D}{\partial V_T} = -\frac{\kappa}{U_T} \cdot I_D = -g_m, \tag{2.23}$$

$$g_R = \frac{\partial I_D}{\partial R} = \frac{\partial}{\partial R} \left( \frac{V}{R} \right) = -\frac{1}{R} \cdot \frac{V}{R} = -\frac{1}{R} \cdot I_D.$$

(2.24)

and

$$g_{mb} = \frac{\partial I_D}{\partial V_{BS}} = \frac{1 - \kappa}{U_T} \cdot I_D. \tag{2.25}$$

By assuming that  $\Delta V_T$  and  $\Delta R$  are small, we can use a small-signal circuit model as shown in Fig. 2-7(b) to calculate the variation in nominal current  $\Delta I_D$  when  $\Delta V_T$  and  $\Delta R$  are considered as inputs to the system. With some analysis, the variation in the channel current due to variations in  $V_T$  and R is obtained to be

$$\Delta I_D = g_T \cdot \Delta V_T - (g_m + g_{mb} + 1/r_o) \cdot (\Delta I_D - g_R \cdot \Delta R) \cdot R. \tag{2.26}$$

Combining (2.26) with the results from (2.23) and (2.24) and using the relationship  $g_s = g_m + g_{mb}$ , we obtain the fractional change in channel current as a function of the fractional change in  $V_T$  and R to be

$$\frac{\Delta I_D}{I_D} = -\frac{1}{1 + g_s R + R/r_o} \cdot \frac{\Delta V_T}{I_D/g_m} - \frac{g_s R + R/r_o}{1 + g_s R + R/r_o} \cdot \frac{\Delta R}{R}.$$

(2.27)

Since  $M_{c3}$ ,  $M_5$  and  $M_6$  are biased in weak-inversion regime, their  $I_D/g_m$  is approximately 40 mV at room temperature. As seen from (2.27), the mismatch in threshold voltage as a fraction of 40 mV is attenuated by a factor of  $1 + g_s R + R/r_o$  and is negligible if  $g_s R \gg 1$ . In our design, we have  $g_s R \approx 12$ , thus, the fractional mismatch in threshold voltage is attenuated by more than a factor of 10 and does not play

a significant role in current mirror mismatch. In contrast, the fractional mismatch in channel current scales almost 1:1 to the fractional mismatch in R. However, the matching of passive components in most CMOS processes is much better controlled than the matching of transistors' threshold voltages. In our design, therefore, we try to achieve good resistor matching with careful layout.

# 2.2.4 Noise Efficiency Factor and its theoretical limit for OTA with differential inputs

To compare the power-noise tradeoff among amplifiers, we adopt the noise efficiency factor (NEF) proposed in [63] and widely used to compare neural-amplifier designs:

$$NEF = V_{ni,rms} \sqrt{\frac{2I_{tot}}{\pi \cdot U_T \cdot 4kT \cdot BW}}$$

(2.28)

where  $V_{ni,rms}$  is the total input-referred noise,  $I_{tot}$  is the total supply current, and BW is the -3 dB bandwidth of the amplifier respectively. The theoretical limit of the NEF of an OTA that uses a differential pair as an input stage is when the two differential-pair transistors are the only noise sources in the circuit. The input-referred noise of the OTA is then  $\overline{V_{ni}^2} = 2 \times 2kT/(\kappa g_m) = 4kT/(\kappa g_m)$  where  $g_m$  is the transconductance of a single differential-pair transistor. For minimum input-referred noise, the transistors should run in subthreshold, such that we have  $g_m = \kappa I_D/U_T$ . Assuming a first-order roll-off of the frequency response, the input-referred noise of the ideal OTA is expressed as

$$V_{ni,rms} = \sqrt{\frac{4kT \cdot U_T}{\kappa^2 I_D} \cdot \frac{\pi}{2} \cdot BW}.$$

(2.29)

Combining (2.28) and (2.29) and setting  $I_{tot} = 2I_D$ , we obtain the theoretical limit for NEF of any OTA that uses a subthreshold MOS differential pair to be

$$NEF = \frac{\sqrt{2}}{\kappa} \approx 2.02 \tag{2.30}$$

Figure 2-8: A die micrograph of our neural amplifier.

assuming a typical value of  $\kappa = 0.7$ . We now show that our experimental NEF is near this value, and our theoretical NEF was computed to be 2.47 from Section 2.2.2.

## 2.3 Measurement Results

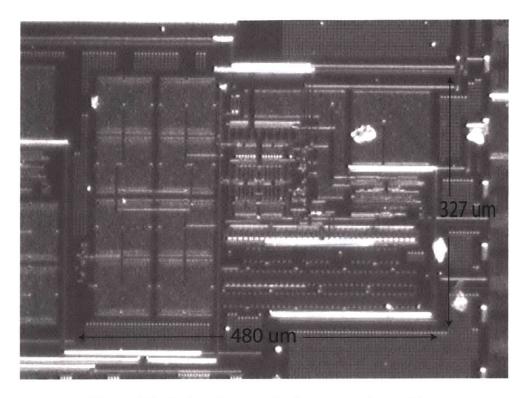

The amplifier was fabricated in a 0.5  $\mu$ m CMOS process through MOSIS. It was designed to give a gain of approximately 110 (40.8 dB) by setting the value of  $C_{in}$  to 14 pF and  $C_f$  to 120 fF. The OTA in the bandpass filter stage is a wide common-mode range OTA to reduce signal distortion in the case of large input amplitudes. The amplifier occupies a chip area of 0.16 mm<sup>2</sup>. A chip micrograph of our amplifier is shown in Fig. 2-8.

Four chips were tested on the lab bench and they exhibited very similar performance characteristics, indicating that the severe current-scaling scheme worked robustly. The measured transfer function of one of our neural amplifiers is shown in Fig. 2-9. The amplifier consumes 2.7  $\mu$ A including the current from the bias circuit

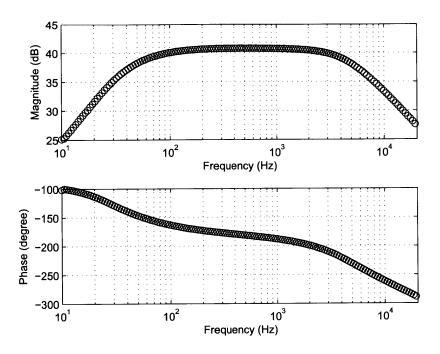

Figure 2-9: Measured transfer function of the neural amplifier configured for recording neural spikes.

$(M_{b2}, M_{c2} \text{ and } M_{c3})$  from a 2.8 V supply. We do not include the current  $I_{bias}$  shown in Fig. 2-3 since it can be shared by many amplifiers in the array. The -3 dB cutoff frequencies are adjusted to be at 45 Hz and 5.32 kHz. The amplifier is configured as an inverting amplifier, thus the phase is approximately -180° near the midband frequency.

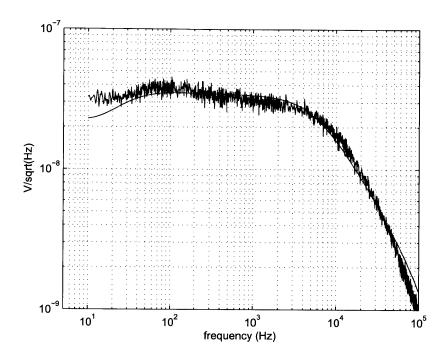

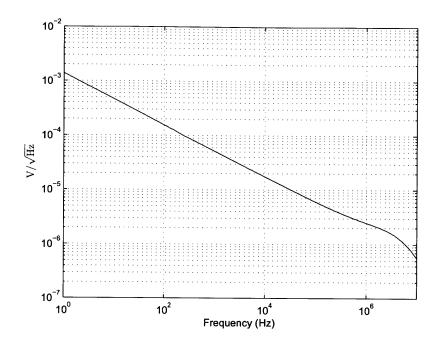

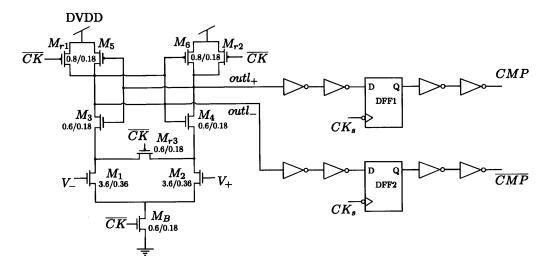

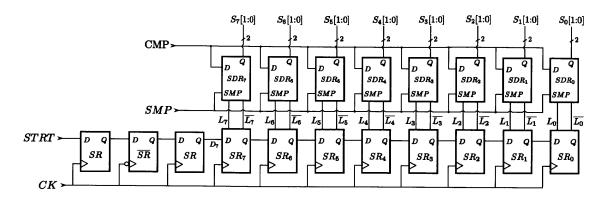

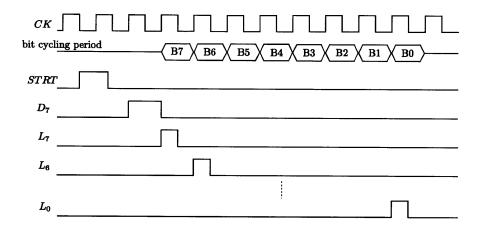

Fig. 2-10 shows the measured input-referred noise spectrum together with a circuit simulation of the noise spectrum with a similar noise model to the theoretical calculations (the smooth curve). There is a good agreement between the measured and simulated curves. The measured thermal noise level is  $31 \text{ nV}/\sqrt{\text{Hz}}$ . Integrating under the area of the measured curve from 10 Hz to 98 kHz yields a total input-referred noise of 3.06  $\mu\text{V}_{rms}$ , while the simulated result is 3.1  $\mu\text{V}_{rms}$ . With a high-pass cutoff frequency at 45 Hz, 1/f noise is filtered out and is not noticeable in the passband.

The NEF of this amplifier is calculated from the achieved experimental measurements to be 2.67. This value is close to 2.02 which is the theoretical NEF limit that has been calculated in 2.2.4 and also near our expected theoretical calculation of 2.47

Figure 2-10: Measured and simulated (smooth curve) input-referred noise spectra of the neural amplifier configured for recording neural spikes.

Table 2.2: Comparison of reported neural amplifiers

| Amplifier | Power            | Noise            | Bandwidth                                 | NEF  | Year      |

|-----------|------------------|------------------|-------------------------------------------|------|-----------|

|           | $\mu \mathrm{W}$ | $\mu V_{ m rms}$ |                                           |      | Published |

| [24]      | 80               | 2.2              | $0.025~{\rm Hz}\text{-}7.5~{\rm kHz}$     | 4    | 2003      |

| [20]      | 8.6              | 5.6              | 100 Hz-9.2 kHz                            | 4.9  | 2009      |

| [38]      | 40.3             | 1.94             | 0.2 Hz-8.2 kHz                            | 2.9  | 2009      |

| [72]      | 0.44-0.9         | 2.5              | $3.5~\mathrm{mHz}\text{-}292~\mathrm{Hz}$ | 3.26 | 2009      |

| [32]      | 14.8             | 4.3              | $10~\mathrm{Hz}\text{-}9~\mathrm{kHz}$    | 5.56 | 2010      |

| This work | 7.56             | 3.06             | $45~\mathrm{Hz}\text{-}5.32~\mathrm{kHz}$ | 2.67 | 2007      |

45

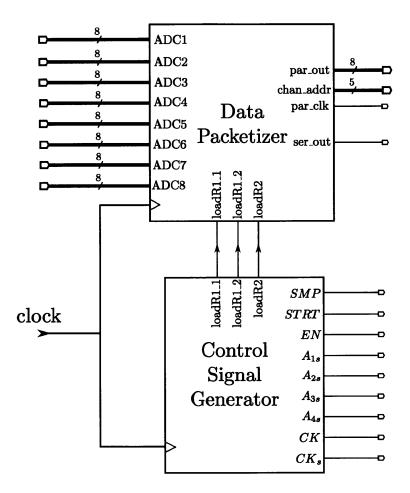

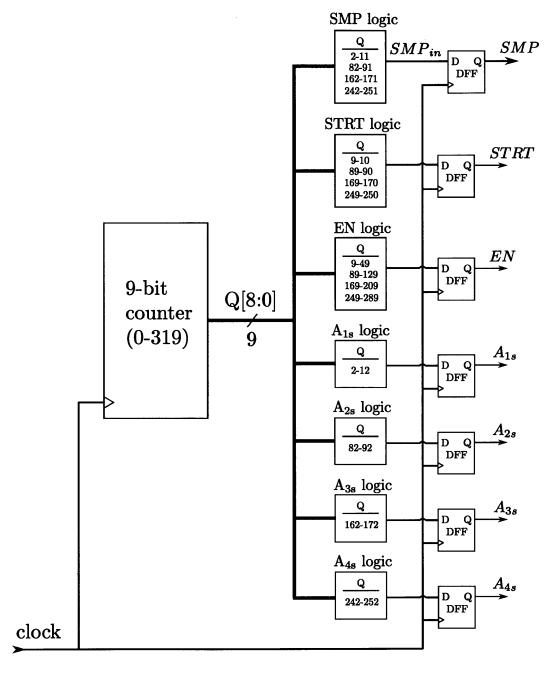

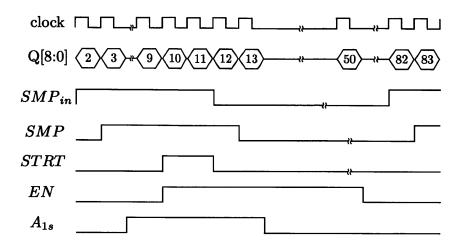

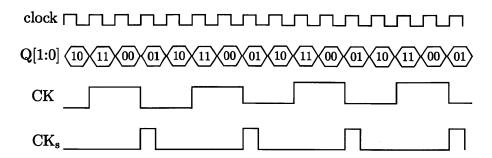

in (2.21). The good power-noise tradeoff of this amplifier is a result of minimizing the effective number of transistors that contribute noise. Moreover, almost all the power is consumed by the input-differential pair. Therefore, little power is wasted in less critical parts of the amplifier. Table 2.2 compares the NEF of this amplifier with those reported in the literature. Due to its energy-efficiency that is close to a limit determined by physics, this amplifier still achieves the best NEF among the more recently reported design, even though it was published earlier.