# Millimeter-wave GaN High Electron Mobility Transistors and Their Integration with Silicon Electronics

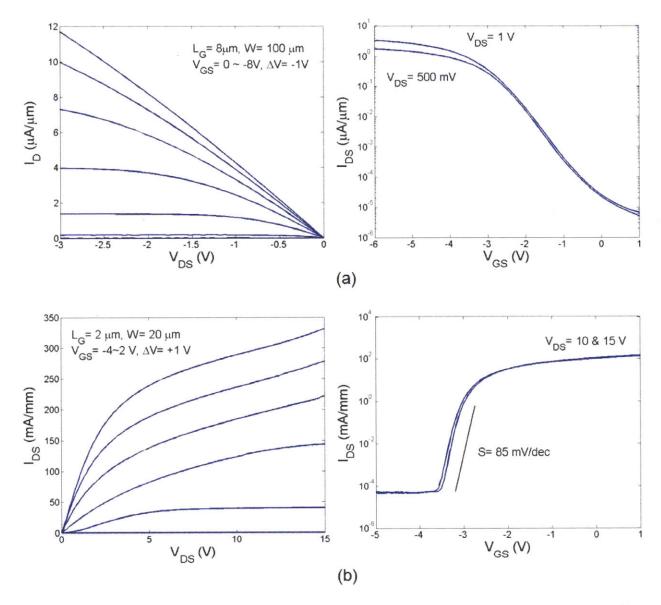

by

# Jinwook W. Chung

B.S., Electrical Engineering Korea Advanced Institute of Science and Technology, 2006 S.M., Electrical Engineering and Computer Science Massachusetts Institute of Technology, 2008

Submitted to the Department of Electrical Engineering and Computer Science in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

at the

MASSACHUSETTS INSTITUTE OF TECHNOLOGY MAR 1 0 2011 LIBRARIES

Massachusetts Institute of Technology

February 2011

© 2011 Massachusetts Institute of Technology. All Rights Reserved.

| Author       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

|              | Department of Electrical Eng                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | zineering and Computer Science<br>January 28, 2011 |

| Certified by | in the second se | 7                                                  |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Tomás Palacios                                     |

|              | Ássociate Pro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ofessor of Electrical Engineering                  |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Thesis Supervisor                                  |

| A ( 11       | Stern -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                    |

| Accepted by  | /                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Terry P. Orlando                                   |

|              | Pro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ofessor of Electrical Engineering                  |

|              | Chairman, Department C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Committee on Graduate Students                     |

# Millimeter-wave GaN High Electron Mobility Transistors and Their Integration with Silicon Electronics

by

Jinwook W. Chung

Submitted to the Department of Electrical Engineering and Computer Science on January 28, 2011 in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

#### ABSTRACT

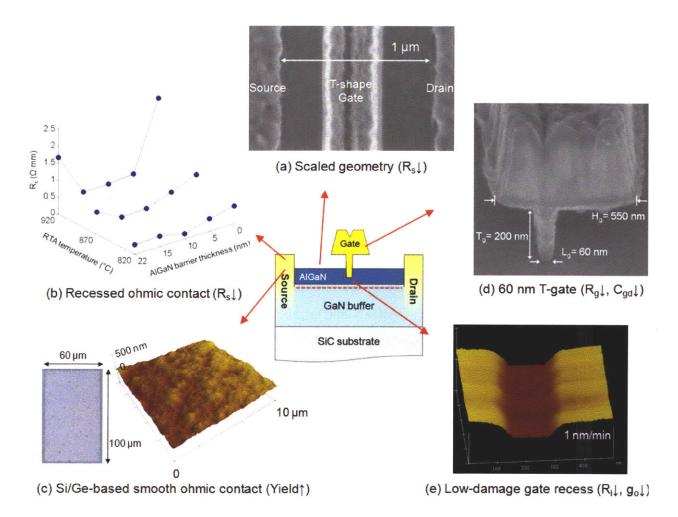

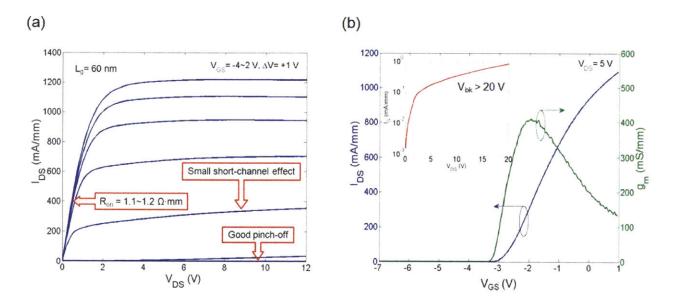

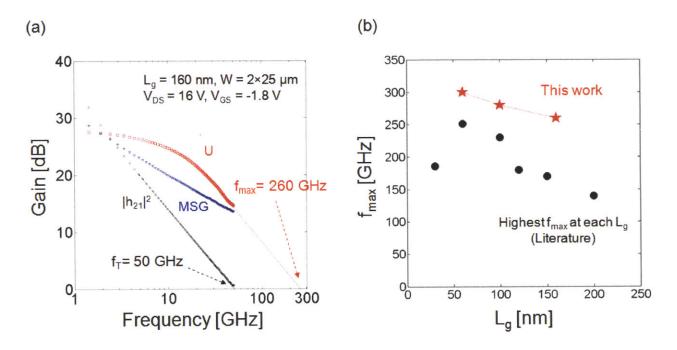

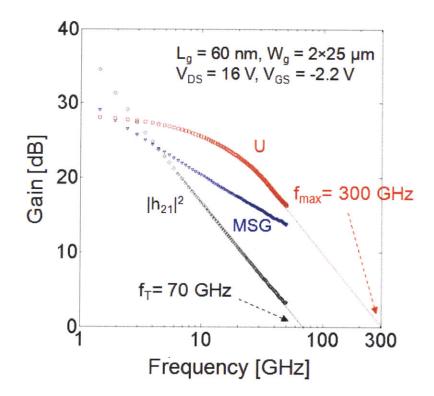

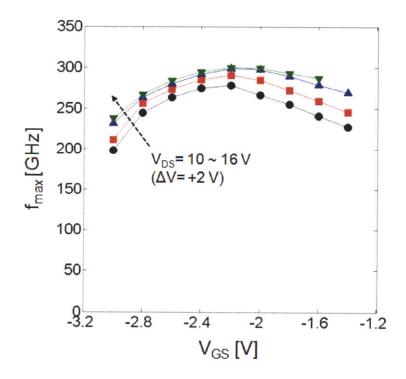

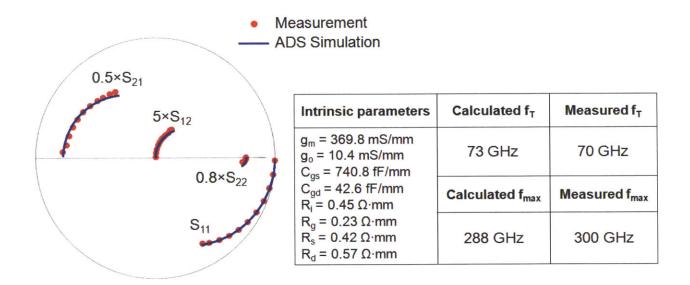

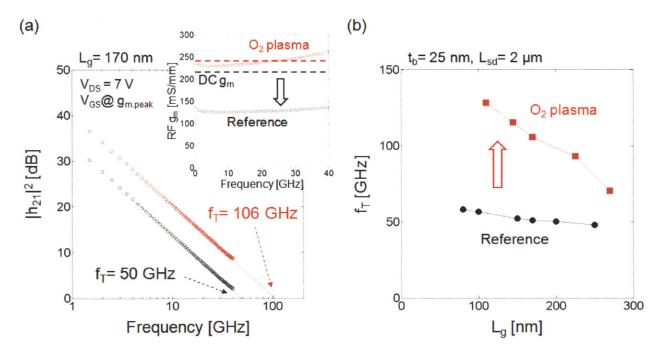

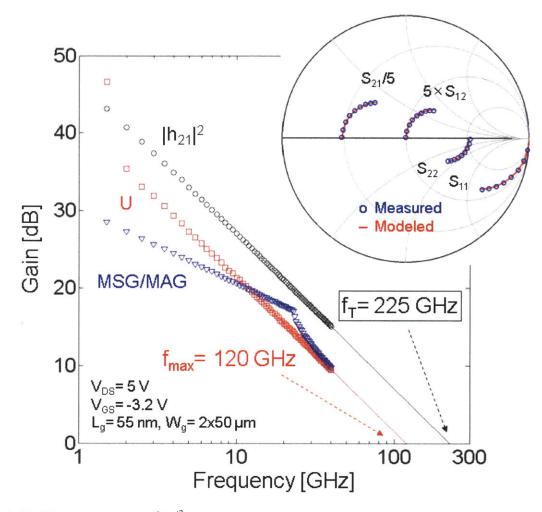

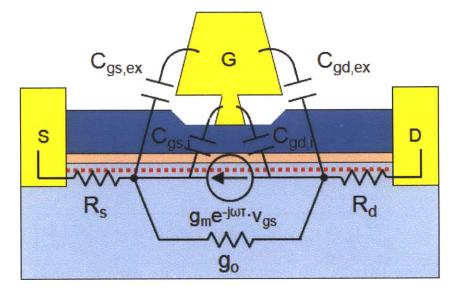

In spite of the great progress in performance achieved during the last few years, GaN high electron mobility transistors (HEMTs) still have several important issues to be solved for millimeter-wave (30 ~ 300 GHz) applications. One of the key challenges is to improve its high frequency characteristics. In this thesis, we particularly focus on  $f_T$  and  $f_{max}$ , two of the most important figures of merit in frequency performance of GaN HEMTs and investigate them both analytically and experimentally. Based on an improved physical understanding and new process technologies, we aim to demonstrate the state-of-the-art high frequency performance of GaN HEMTs. To maximize  $f_{max}$ , parasitic components in the device  $(R_i, R_s, R_g, C_{gd}, and g_o)$  are carefully minimized and the optimized 60-nm AlGaN/GaN HEMT shows a very high  $f_{max}$  of 300 GHz. The lower-than-expected  $f_T$  observed in many AlGaN/GaN HEMTs is attributed to a significant drop of the intrinsic transconductance at high frequency (RF  $g_m$ ) with respect to the intrinsic DC  $g_m$  (called RF  $g_m$ -collapse). By suppressing RF  $g_m$ -collapse and harmoniously scaling the device, a record  $f_T$  of 225 GHz is achieved in the 55-nm AlGaN/GaN HEMT. Another important challenge for the wide adoption of GaN devices is to develop suitable technology to integrate these GaN transistors with Si(100) electronics. In this thesis, we demonstrate a new technology to integrate, for the first time, GaN HEMTs and Si(100) MOSFETs on the same chip. This integration enables the development of hybrid circuits that take advantage of the high-frequency and power capability of GaN and the unsurpassed circuit scalability and complexity of Si electronics.

Thesis supervisor: Tomás Palacios Title: Associate Professor of Electrical Engineering

•

# Acknowledgements

My successful Ph.D. journey has only been possible because I was surrounded by the right people. I can honestly say that without the inspiration and support of the people around me, I would have never finished this journey. It is my great pleasure to thank the many individuals who have contributed to this work.

First and foremost, I would like to express my sincere gratitude to my research advisor Prof. Tomás Palacios. I still remember the moment when I first decided to join his group in September 2006. Working on nitride semiconductors was never in any plan that I have imagined for myself, however it was without a doubt one of the best decisions that I ever made and I truly appreciate his full support, candid advice, and endless encouragement to make my Ph.D. experience fruitful and exciting.

I gratefully thank my thesis committee members, Prof. Dimitri Antoniadis, Prof. Jesús del Alamo, and Prof. Judy Hoyt. It was my great honor to have them in my thesis committee and their invaluable suggestions and feedbacks largely improved this work.

I also would like to acknowledge the ONR MINE MURI and DURIP programs monitored by Dr. Paul Maki and Dr. Harry Dietrich, and the DARPA NEXT program monitored by Dr. John Albrecht for their continuous support to make GaN electronics a reality. In addition, many thanks go to the KFAS fellowship for the financial support during my entire Ph.D. years.

The work presented in this thesis extensively relies on device fabrication and processing. I would like to thank all the staffs in MTL, NSL, and SEBL at MIT. They are absolutely helpful and I strongly believe that one of the real strengths of MIT EECS is their excellent work and strong support. I have also been lucky to collaborate with Raytheon, Nitronex, TriQuint, Cree, and IQE, and acknowledge them for providing us state-of-the-art GaN samples.

My Ph.D. years have been enriched by many friends and colleagues. In particular, Taegsang Cho, Myungjin Choi, Hwanchul Yoo, Wonyoung Kim, and Jiye Lee made my days happy and enjoyable. Thank you for sharing wonderful years at MIT. I will not forget Taewoo Kim who was my life mentor, and Jaekyu Lee and Jungwoo Joh who inspired me in many ways. I also thank to friendship of TP group members, Bldg 39 friends, and Fab buddies.

Last but definitely not least, my deepest gratitude goes to my family who allowed me to dream and lifelong brothers who enabled me to move forward. They are simply my reason for living.

# Contents

| Chapter 1. Introduction                                           |    |

|-------------------------------------------------------------------|----|

| 1.1. History of GaN research                                      |    |

| 1.2. Millimeter-wave GaN HEMTs                                    |    |

| 1.3. Integration of GaN and Si electronics                        |    |

| 1.4. Project goal and thesis outline                              |    |

| 1.5. References                                                   | 21 |

| Chapter 2. Basics of GaN HEMTs                                    | 27 |

| 2.1. DC analysis                                                  |    |

| 2.1.1. Charge control model                                       |    |

| 2.1.2. Velocity-field relationship                                |    |

| 2.1.3. DC characteristics                                         |    |

| 2.2. RF analysis                                                  |    |

| 2.2.1. Two-port network                                           |    |

| 2.2.2. Small-signal equivalent circuit                            |    |

| 2.2.3. RF characteristics                                         |    |

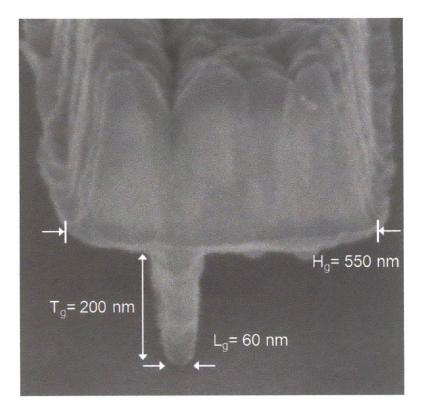

| 2.3. Fabrication technology                                       |    |

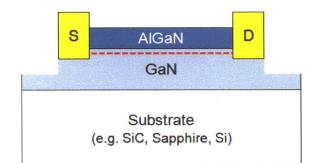

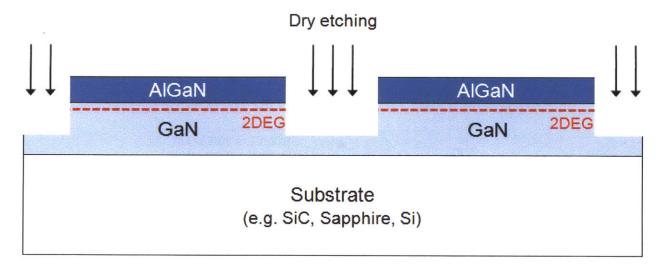

| 2.3.1. Isolation                                                  | 47 |

| 2.3.2. Ohmic contact                                              | 49 |

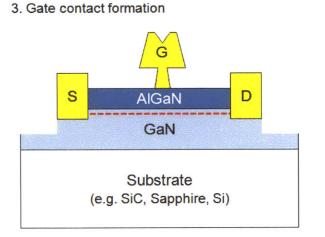

| 2.3.3. Gate contact                                               |    |

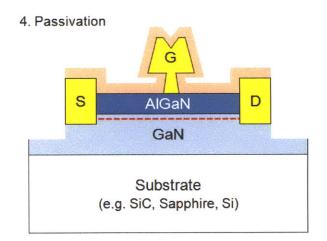

| 2.3.4. Passivation                                                | 55 |

| 2.4. References                                                   | 56 |

| Chapter 3. Optimizing Parasitic Elements for Improving $f_{max}$  | 61 |

| 3.1. Introduction                                                 | 61 |

| 3.2. Optimizing parasitic elements                                |    |

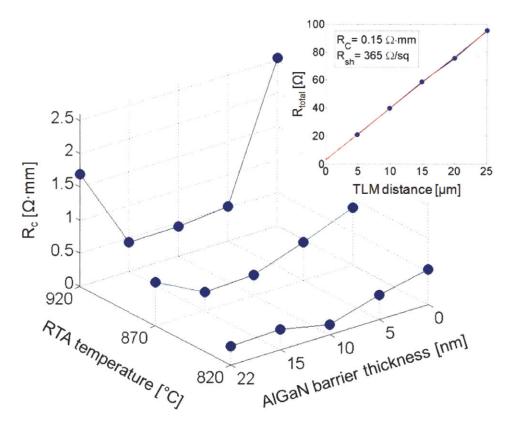

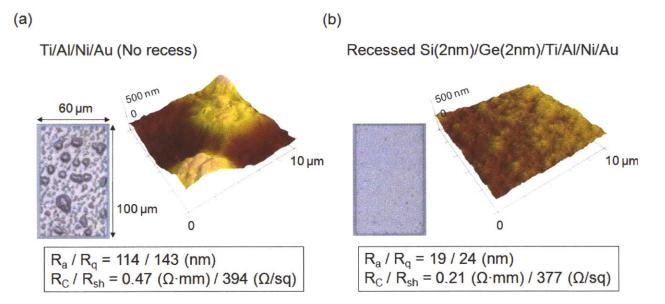

| 3.2.1. Source resistance $(R_s)$                                  |    |

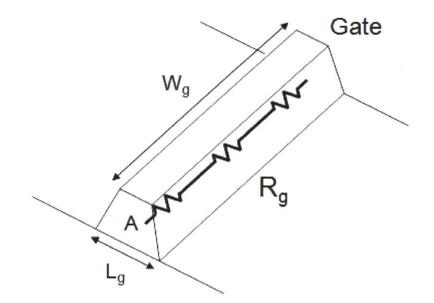

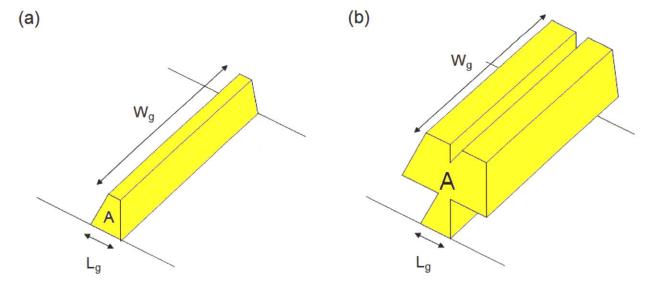

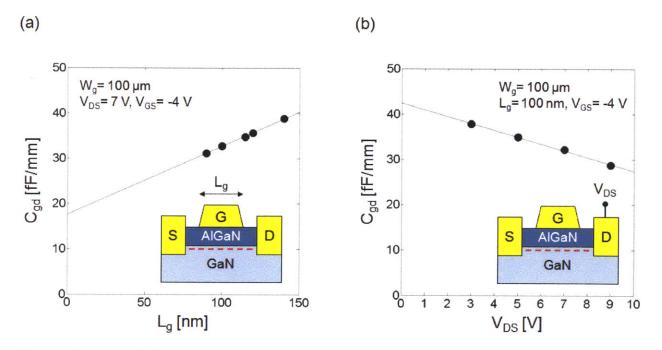

| 3.2.2. Gate resistance and gate-drain capacitance $(R_g, C_{gd})$ |    |

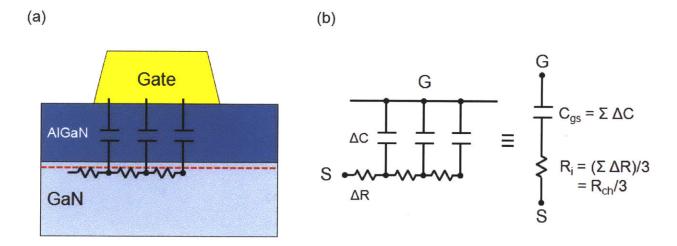

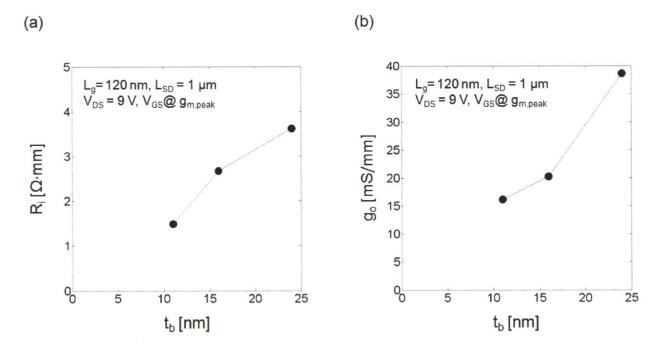

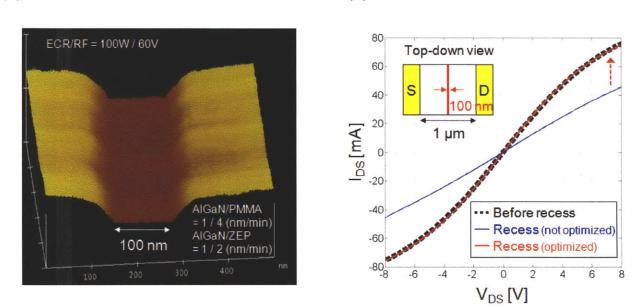

| 3.2.3. Input resistance and output conductance $(R_i, g_o)$ |  |

|-------------------------------------------------------------|--|

| 3.2.4. Process integration                                  |  |

| 3.3. Device characteristics                                 |  |

| 3.3.1. DC characteristics                                   |  |

| 3.3.2. RF characteristics                                   |  |

| 3.4. References                                             |  |

|                                                             |  |

| Chapter 4. Advanced Gate Technologies for Improving $f_T$   |  |

| 4.1. Introduction                                           |  |

| 4.2. Small-signal parameter extraction                      |  |

| 4.2.1. Modified small-signal equivalent circuit             |  |

| 4.2.2. On-wafer de-embedding                                |  |

| 4.2.3. Intrinsic parameter extraction                       |  |

| 4.3. RF $g_m$ -collapse                                     |  |

| 4.3.1. Summary of observations                              |  |

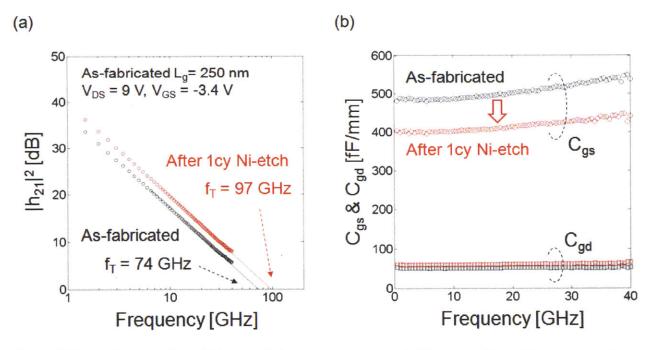

| 4.3.2. Effect of plasma treatment                           |  |

| 4.3.3. Origin of RF g <sub>m</sub> -collapse                |  |

| 4.3.4. Oxygen plasma treatment                              |  |

| 4.4. Advanced gate technology                               |  |

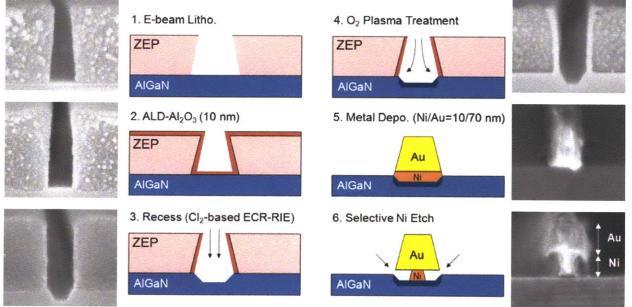

| 4.4.1. Al <sub>2</sub> O <sub>3</sub> -sidewall technology  |  |

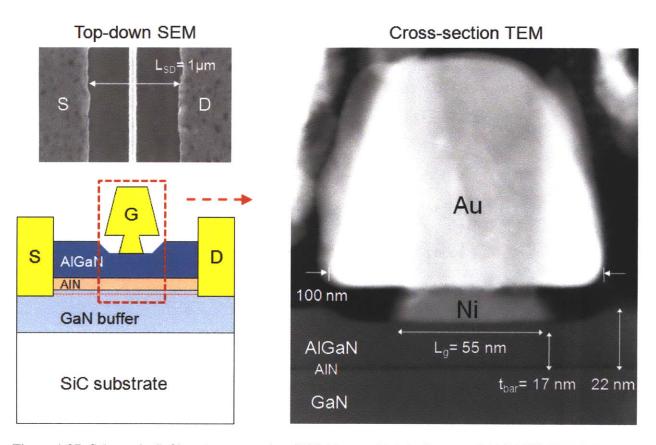

| 4.4.2. New gate process to maximize $f_T$                   |  |

| 4.5. Device characteristics                                 |  |

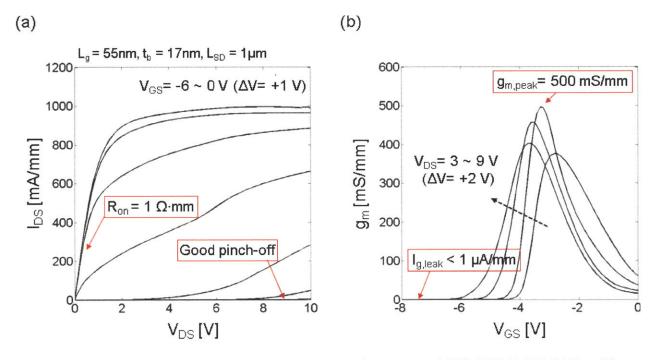

| 4.5.1. DC characteristics                                   |  |

| 4.5.2. RF characteristics | 126 |

|---------------------------|-----|

| 4.6. References           | 133 |

| Chapter 5. On-wafer Integration of GaN and Si(100) Electronics | 139 |

|----------------------------------------------------------------|-----|

| 5.1. Introduction                                              |     |

| 5.2. Challenges and new approach                               | 140 |

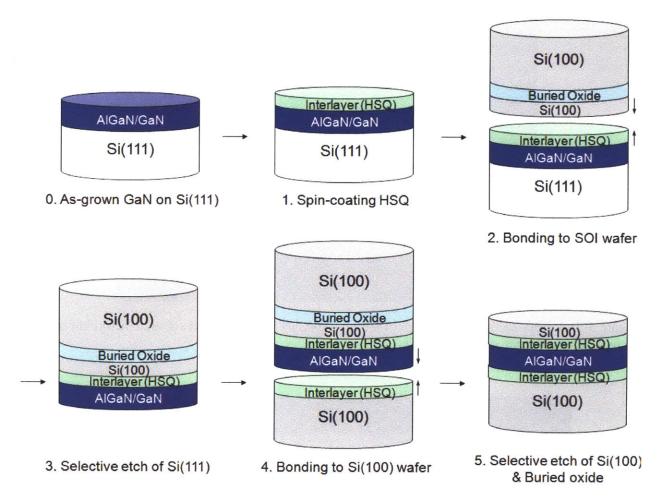

| 5.3. Layer transfer technology                                 |     |

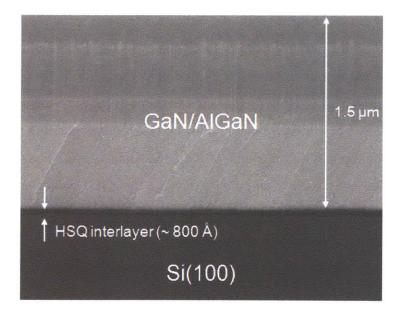

| 5.3.1. HSQ interlayer bonding                                  |     |

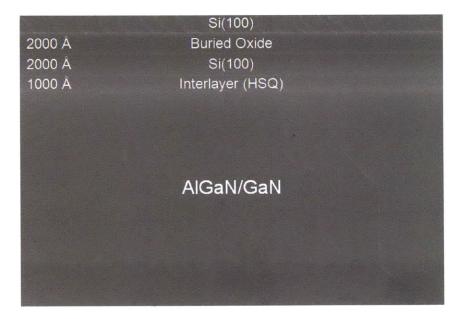

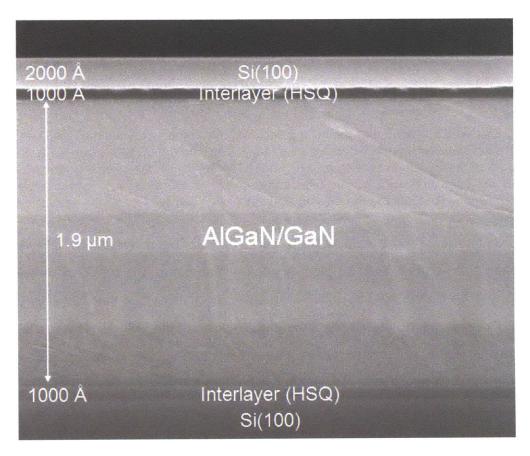

| 5.3.2. Si(100)-GaN-Si(100) hybrid substrate                    |     |

|----------------------------------------------------------------|-----|

| 5.4. On-wafer integration of GaN and Si(100) devices           |     |

| 5.5. New applications                                          |     |

| 5.5.1. On-wafer GaN/Si power regulator                         |     |

| 5.5.2. Enhancement-mode power transistor                       | 156 |

| 5.6. References                                                |     |

|                                                                |     |

| Chapter 6. Conclusions and Future Work                         |     |

| 6.1. Summary                                                   |     |

| 6.1.1. Reduction of parasitic elements for improving $f_{max}$ |     |

| 6.1.2. Advanced gate technologies for improving $f_T$          |     |

| 6.1.3. On-wafer integration of GaN and Si(100) electronics     |     |

| 6.2. Future work                                               |     |

| 6.2.1. Improvement of $f_T$ and $f_{max}$                      |     |

| 6.2.2. Investigation of RF $g_m$ -collapse                     |     |

|           | U                   | 0            | 1        |        |      |         |

|-----------|---------------------|--------------|----------|--------|------|---------|

| 6.2.3.0   | On-wafer inte       | gration of C | aN and S | i(100) | <br> | <br>172 |

| 0.2.3.    | on water nite       | Brutton of C |          | -(     |      |         |

| 63 Refe   | rences              |              |          |        | <br> | <br>173 |

| 0.0.10010 | i entees initiation |              |          |        |      |         |

| Appendix 1. Scattering Parameter Conversion Rules     | 177   |

|-------------------------------------------------------|-------|

| Appendix 2. Process Flow for High Frequency GaN HEMTs | 179   |

| Appendix 3. Process Flow for Si MOSFETs and GaN HEMTs | . 181 |

# **Chapter 1. Introduction**

## 1.1. History of GaN research

During the last 20 years, there has been an explosive evolution of nitride semiconductors (GaN, AlN, InN, and their alloys) in both optoelectronics and electronics. Remarkable breakthroughs achieved by numerous researchers and the unique properties of nitride semiconductors such as a direct bandgap tunable from 6.2 eV (AlN) down to 0.7 eV (InN), piezoelectricity, polarization [1], large breakdown voltage [2], biocompatibility [3], and high chemical and thermal stability [4] enabled this material system to be the prime choice for blue light emitting diodes (LEDs), blue laser diodes, and high-frequency high-power electronics.

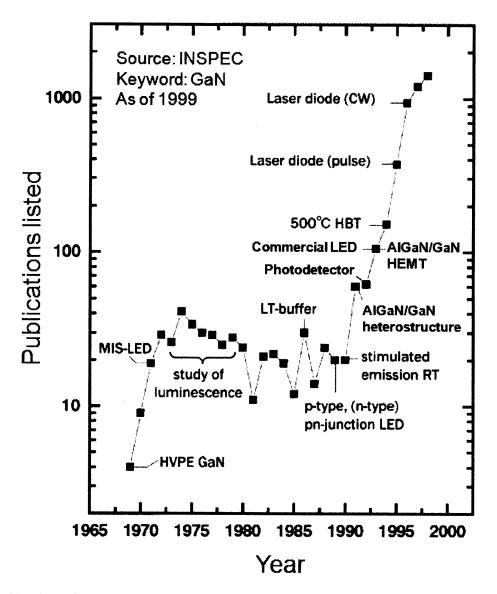

Figure 1-1 describes some of the major breakthroughs in nitride growth and technology in the early years [5]. What initially brought the nitrides to the realm of semiconductors for device applications could be the success in growing crystalline GaN on a sapphire substrate by hydride vapour-phase epitaxy (HVPE) in 1969 [6]. This event greatly inspired many researchers and foster the GaN research in its early stage of development. GaN was perceived as the best material for the fabrication of blue LEDs. However, in the late 1970s, the GaN research community faced challenges in growing high quality epitaxial films and, specially, producing ptype GaN. As a result, the activity on GaN research slowly declined in this period. This stagnation, however, did not last long. Two important milestones reignited GaN research: the growth of high-quality single crystal GaN with a specular crack-free surface by Amano et al. in 1986 [7] and the discovery of a way to produce p-type GaN by Amano et al. in 1989 [8] and Nakamura et al. in 1992 [9]. As shown in Figure 1-1, these two breakthroughs were an important inflection point for nitride semiconductor research. The great improvement and superior performance of the devices were instantly followed first in optoelectronics. Amano et al. demonstrated the first GaN LED with a p-n junction in 1989 [8]. Then, Nakamura et al. built on this work and optimized the design and process which led to a hike in device efficiency and enabled Nichia to launch the first commercial nitride-based LEDs in 1993 [5]. He also

Figure 1-1. Number of publications (based on INSPEC search) and activities of GaN research in the early years (modified from [5]). Marked events indicate when they were first achieved. GaN research in both optoelectronics and electronics progressed rapidly after demonstrating the growth of high quality GaN and conductivity control of both p- and n-type GaN in the early 1990s.

demonstrated the first nitride-based laser diode in 1996 [10]. Continuous achievements in recent years significantly boosted the power and efficiency of GaN optoelectronic devices and finally opened multibillion dollar industry.

In parallel to the revolution in optoelectronics, the high material quality enabled by optimized growth reactors was able to trigger intense research on GaN for electronic applications. One of the most widely studied electronic devices was the AlGaN/GaN high electron mobility transistor

|                                    |                          | Material     |                                |                        |              |                           |

|------------------------------------|--------------------------|--------------|--------------------------------|------------------------|--------------|---------------------------|

| Characteristic                     | Unit                     | Si           | <b>GaAs</b><br>(AlGaAs/InGaAs) | InP<br>(InAIAs/InGaAs) | SiC          | <b>GaN</b><br>(AlGaN/GaN) |

| Bandgap (E <sub>g</sub> )          | eV                       | 1.11         | 1.42                           | 1.35                   | 3.26         | 3.39                      |

| Critical breakdown field           | MV/cm                    | 0.3          | 0.4                            | 0.5                    | 3.0          | 3.3                       |

| Saturated (peak) electron velocity | ×10 <sup>7</sup><br>cm/s | 1.0<br>(1.0) | 1.3<br>(2.1)                   | 1.0<br>(2.3)           | 2.0<br>(2.0) | 1.3<br>(3.0)              |

| Electron mobility at 300 K         | cm²/Vs                   | 1350         | 8500                           | 5400                   | 700          | 2000                      |

Table 1-1. Some of the outstrip material properties of GaN compared to other semiconductor families.

(HEMT). This device attracted considerable attention soon after its excellent transport property was first reported in 1991 [11]. The AlGaN/GaN HEMT has unique and superior properties such as large sheet charge density (~  $1 \times 10^{13}$  /cm<sup>2</sup>), high peak electron velocity (~  $3.0 \times 10^{7}$  cm/s), high breakdown field strength (~ 3.3 MV/cm) and good thermal conductivity (> 1.5 W/cm·K). Since GaN is one of the few materials that can achieve high breakdown voltage and high electron velocity at the same time as shown in Table 1-1, it is particularly promising for RF power amplifiers. In only 20 years, AlGaN/GaN HEMTs have evolved tremendously from the initial devices with less than 50 mA/mm of output current and virtually no high frequency performance [12], to world-wide commercialization as power amplifiers in the microwave spectrum (1 ~ 30GHz). The excellent intrinsic properties of nitride semiconductors make them one of the best options for high-frequency high-power applications and AlGaN/GaN HEMTs have already shown an output power density of 32.2 W/mm at 4 GHz [13], 13.7 W/mm at 30 GHz [14], and 2.1 W/mm at 80.5 GHz [15] far surpassing other technologies (e.g. Si, GaAs, InP). Recently, Toshiba announced a commercial C-band (4 ~ 8 GHz) GaN HEMT that nearly doubles the gain compared to GaAs power amplifier [16].

## **1.2. Millimeter-wave GaN HEMTs**

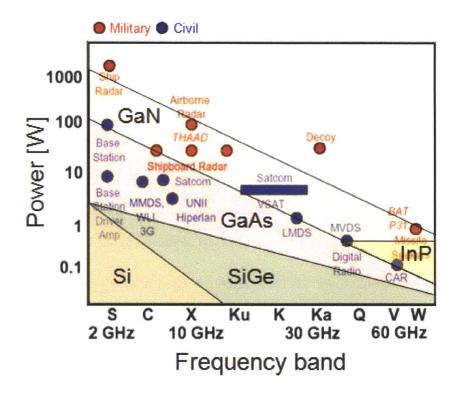

The rapidly growing wireless communication market and demanding military applications continuously require high-efficiency high-power GaN devices. Figure 1-2 shows required output power and operating frequency of RF power amplifiers for several military and civil applications. Different material systems (e.g. Si, SiGe, GaAs, InP) allow us to fulfill different requirements.

Figure 1-2. Required output power and operating frequency of RF power amplifiers for different military and civil applications. Different semiconductor materials are needed depending on the specific power and frequency requirements.

Due to the excellent properties of GaN, GaN can cover most of the requirements and offer superior performance to any other semiconductor in power amplifiers. For example, next generation cell phones and broadband satellite communications require amplifiers driving high power to reduce their size and operating at high frequencies to increase data transmission rate. From this point of view, wide bandgap material such as GaN is desirable because the ultimate breakdown field is determined by band-to-band impact ionization and its high electron velocity enables high frequency operation of the device. Although SiC shows comparable bandgap and breakdown field as GaN, GaN has an advantage over SiC in that GaN can be used to fabricate high electron mobility transistors (MESFETs). The HEMT structure allows higher electron mobility due to its reduced ionized impurity scattering as will be discussed in Chapter 2.

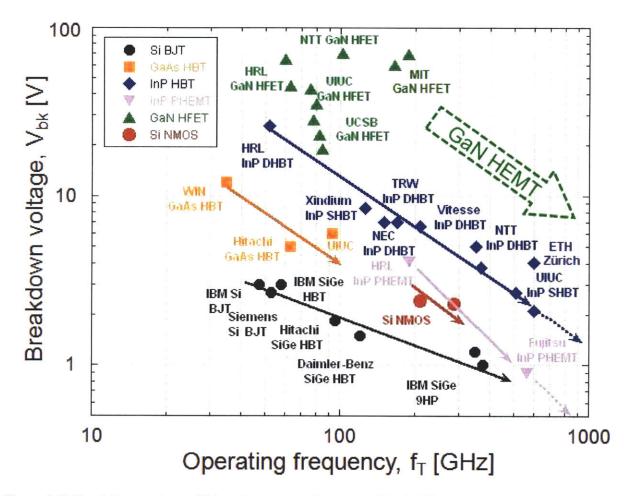

Figure 1-3 plots two typical figures of merit in high-frequency high-power applications, breakdown voltage and operating frequency (or current-gain cutoff frequency  $f_T$ ), for various semiconductor material systems [17]. There is a trade-off between breakdown voltage and

Figure 1-3. Breakdown voltage ( $V_{bk}$ ) and operating frequency ( $f_T$ ) of different material systems (modified from [17]). GaN HEMTs have a tremendous potential to outperform other competing materials for high-frequency high-power applications.

operating frequency, and in each material system this trade-off is characterized by its Johnson figure of merit [18]. The Johnson figure of merit is the product of the saturation velocity and critical electric field by the impact ionization initiated breakdown and it is a measure of suitability for high frequency power device applications. Among the various material systems typically used in power amplifiers, GaN HEMTs have already demonstrated the highest breakdown characteristics at frequencies up to 100 GHz and we can also expect higher breakdown behaviors at millimeter-wave (mm-wave) frequencies (30 ~ 300 GHz) by following the trade-off line (Johnson figure of merit) of GaN as shown in Figure 1-3. To understand what limits the high frequency performance of GaN transistors and to demonstrate state-of-the-art  $f_T$ -vs.- $V_{bk}$  results are some of the main motivations of this project.

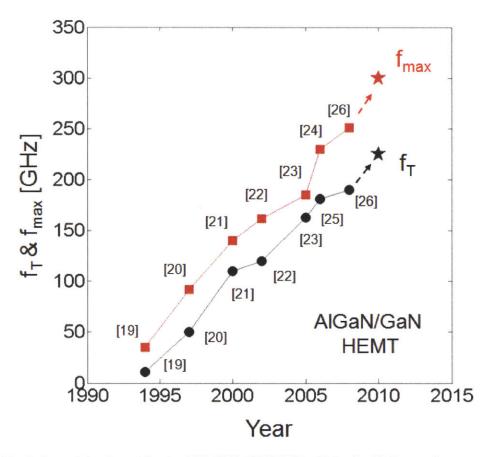

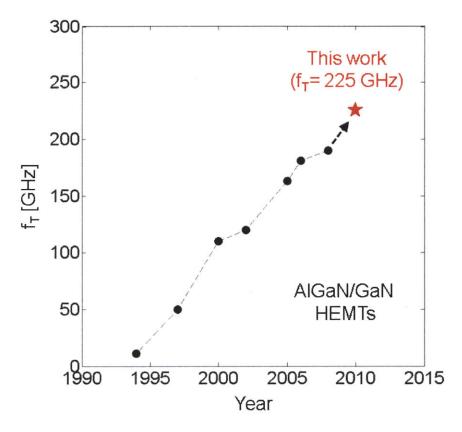

Figure 1-4. Evolution of the  $f_T$  and  $f_{max}$  in AlGaN/GaN HEMTs. Only the highest values reported in each year were plotted. In this work, we demonstrate state-of-the-art  $f_T$  of 225 GHz and  $f_{max}$  of 300 GHz in AlGaN/GaN HEMTs.

The excellent material properties of nitride semiconductors in conjunction with novel fabrication technologies have allowed very fast progress in the high frequency performance of GaN HEMTs. Figure 1-4 shows the evolution of frequency performance in AlGaN/GaN HEMTs over the last 15 years. In 1994, Khan *et al.* reported the first small-signal high frequency performance of an AlGaN/GaN transistor with 0.25  $\mu$ m gate length [19]. This transistor showed a current-gain cutoff frequency ( $f_T$ ) of 11 GHz and a power-gain cutoff frequency ( $f_{max}$ ) of 35 GHz. In 1997, Wu *et al.* demonstrated  $f_T$  of 50 GHz and an  $f_{max}$  of 92 GHz in a device with a gate length of 0.2  $\mu$ m [20]. In 2000, Micovic *et al.* improved frequency performance of AlGaN/GaN HEMTs to an extrinsic  $f_T$  of 121 GHz and  $f_{max}$  of 162 GHz with 0.05  $\mu$ m gate length [21]. In 2002, Kumar *et al.* obtained  $f_T$  of 163 GHz and  $f_{max}$  of 185 GHz with a gate length of 90 nm using Ge-spacer technology [23]. In 2006, Palacios *et al.* further increased  $f_{max}$  to 230 GHz

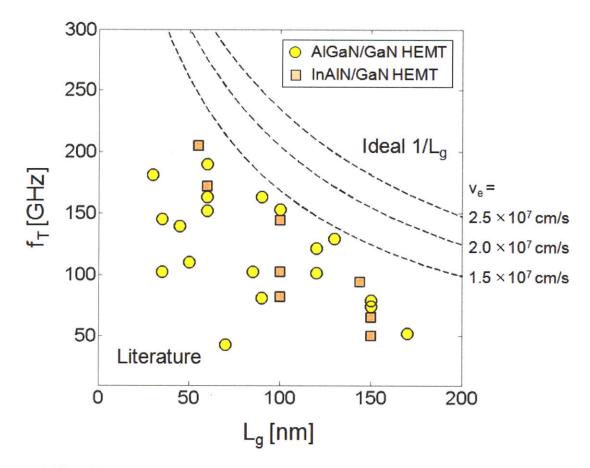

Figure 1-5. High frequency performance of deep-submicron GaN transistors reported in the literature. There is a very large variation of reported  $f_T$  in the literature even with the same  $L_g$ , as well as a considerable deviation of  $f_T$  from its ideal 1 /  $L_g$  scaling behavior.

with a gate length of 100 nm using InGaN back-barrier [24]. In the same year, Higashiwaki *et al.* achieved  $f_T$  of 181 GHz by scaling the gate length to 30 nm [25]. Finally in 2008, Higashiwaki *et al.* fabricated thin barrier AlGaN/GaN HEMTs with 60 nm gate length and demonstrated  $f_T$  of 190 and  $f_{max}$  of 251 GHz [26]. Throughout this thesis work, we demonstrate new record  $f_T$  and  $f_{max}$  of 225 GHz and 300 GHz, respectively in 2010 and add new points to Figure 1-4.

Although these results are excellent, there are still important issues that need to be overcome to further increase the performance of GaN HEMTs at mm-wave frequencies. One of the biggest challenges in mm-wave GaN HEMTs is that the typical frequency performance of these devices, as measured by the current-gain cutoff frequency  $(f_T)$  and the power-gain cutoff frequency  $(f_{max})$ , is lower than what the intrinsic material properties predict. Figure 1-5 shows  $f_T$  values reported in the literature as a function of gate length  $(L_g)$ , compared to the calculated  $f_T$  behavior from ideal gate length scaling. There is a large variation of reported  $f_T$  in the literature even with the same  $L_g$

and the reported  $f_T$  values are significantly lower than their expected values, especially for the shorter gate lengths. Since  $f_{max}$  is a function of  $f_T$ , we also observe a large variation of the  $f_{max}$  values reported by different groups and a considerable discrepancy between measured and expected  $f_{max}$ . Several hypotheses have been proposed to explain the lower-than-expected frequency performance. Some of them include short-channel effects in scaled devices [27], parasitic charging delay associated with the access regions [28], much larger effective gate length than the lithographic gate length [29], and degradation of the gate modulation efficiency by interface defects and traps [30]. However, it is still not clear which one of these effects is primarily limiting high frequency performance of GaN HEMTs and more detailed and systematic understanding is needed to identify solutions to this problem.

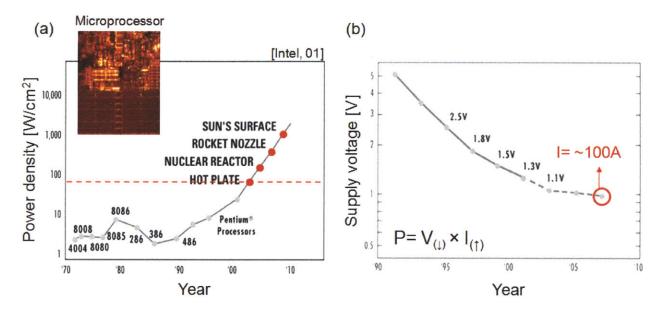

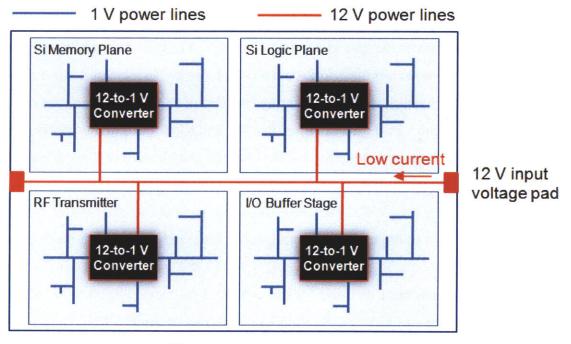

#### **1.3. Integration of GaN and Si electronics**

Another important challenge (and opportunity) in GaN HEMTs is their integration with silicon electronics. Over the last 50 years, Si electronics has revolutionized our world and one of the main drivers for this revolution has been Moore's law. One of the several possible interpretations of Moore's law states that the number of transistors on an integrated circuit (IC) doubles about every two years and this trend has hold for the last half a century [31][32]. However, as the device size gets smaller and smaller, it becomes more and more difficult and expensive to keep up with Moore's law. Physical limits of atomic structures and power density could limit device scaling by 2020 [33]. Thus, we need to find out alternative ways to keep increasing the circuit performance and functionality besides simply scaling down the device size. One way around the size limitation is to introduce new semiconductor materials. There are several material systems that offer better performance than silicon and by integrating them into Si ICs on an as-needed basis, one can expect higher performance as well as new functionalities and flexibilities. The compound semiconductor materials on silicon (COSMOS) program of the U.S. defense advanced research projects agency (DARPA) represents an excellent example of efforts to integrate InP HBTs and Si CMOS electronics [34]. However, in spite of the great commercial and military interest in nitride electronics, no work has been done on the integration of nitride semiconductors and Si CMOS electronics.

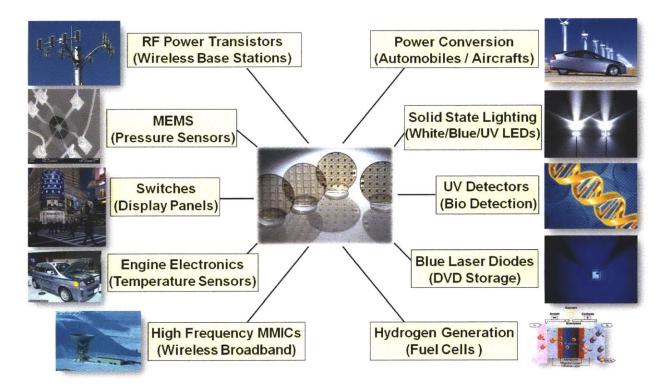

Figure 1-6. Summary of some of the many applications of nitride semiconductors.

GaN is one of the most promising candidates for the heterogeneous integration with Si. GaN has unique properties in both electronics and optoelectronics that Si cannot achieve. While Si electronics has shown unsurpassed levels of scaling and circuit complexity, GaN devices offer excellent high frequency/power performance as well as outstanding optoelectronic properties. In addition, GaN technology is matured enough for commercial applications and it is already widely used in a variety of fields such as solid-state lighting, power electronics, and energy harvesting devices as shown in Figure 1-6. The combination of the excellent properties of GaN with the low cost/high integration capabilities of Si technology would allow unprecedented device performance and flexibility, as well as new circuit functionality.

#### **1.4. Project goal and thesis outline**

This thesis has two main goals. The first one is to identify the main problems that limit the high frequency performance of GaN transistors and demonstrate novel solutions to overcome them. To understand the high frequency limitations of GaN transistors and to demonstrate state-of-the-art devices, we have performed a combination of systematic analysis of device characteristics

and development of advanced fabrication technologies. The second goal is to demonstrate the first integration of high performance GaN transistors with silicon (100) electronics on the same wafer through a scalable technology.

The thesis is organized as follows:

In chapter 2, the basic operation principles of GaN HEMTs are outlined. The important concepts and figures of merit of DC and RF characteristics are described. Also, a concise description of the standard fabrication process is provided.

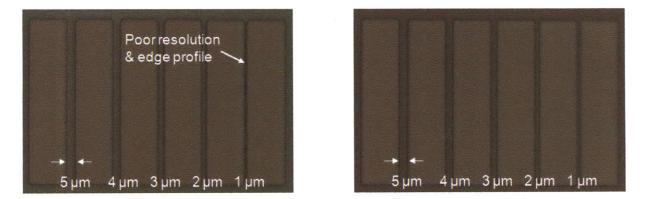

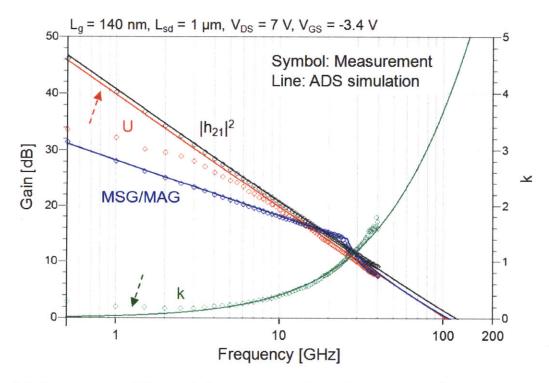

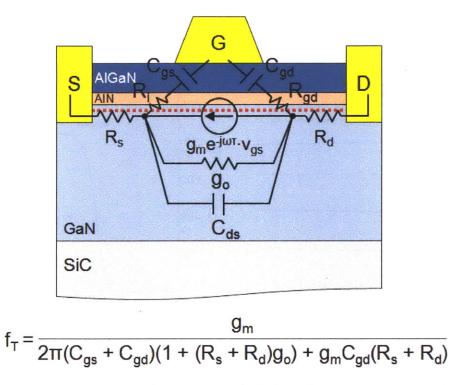

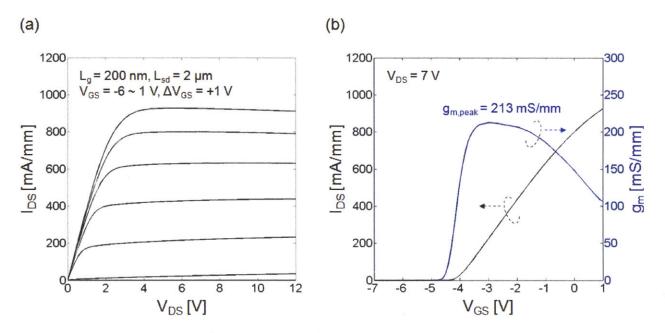

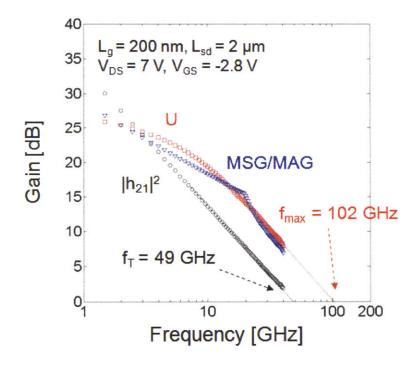

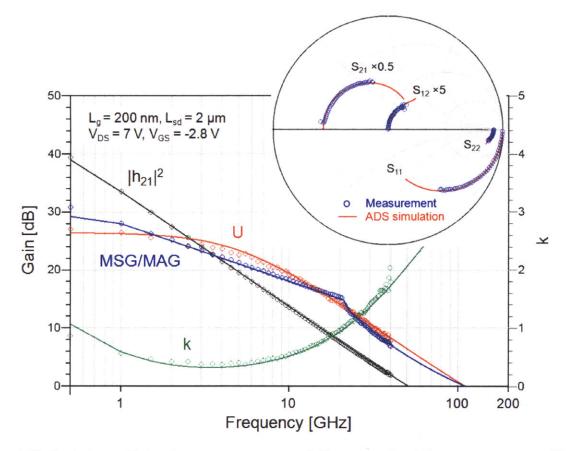

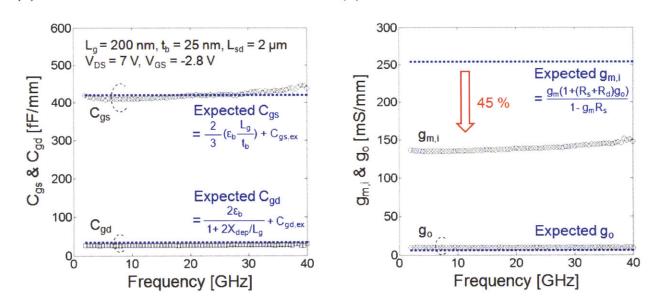

In chapter 3, the  $f_{max}$  of GaN transistors fabricated at MIT is optimized thanks to the development of new processing technologies that minimize parasitic components in the device operation. These technologies combined a low-damage gate recess, scaled device geometry, and recessed source/drain ohmic contacts to simultaneously enable minimum short-channel effects (i.e. low output conductance,  $g_o$ ) and very low parasitic resistances. AlGaN/GaN HEMTs on a SiC substrate with record  $f_{max}$  are demonstrated. For example, a 60-nm gate-length HEMT with recessed AlGaN barrier exhibited excellent  $g_o$  of 10.4 mS/mm,  $R_{on}$  of 1.1 ~ 1.2  $\Omega$ ·mm, and  $f_{max}$  of 300 GHz with a breakdown voltage of ~ 20 V. The obtained  $f_{max}$  is the highest reported to date for any nitride transistor. The accuracy of the  $f_{max}$  value is verified by small-signal modeling based on carefully extracted S-parameters.

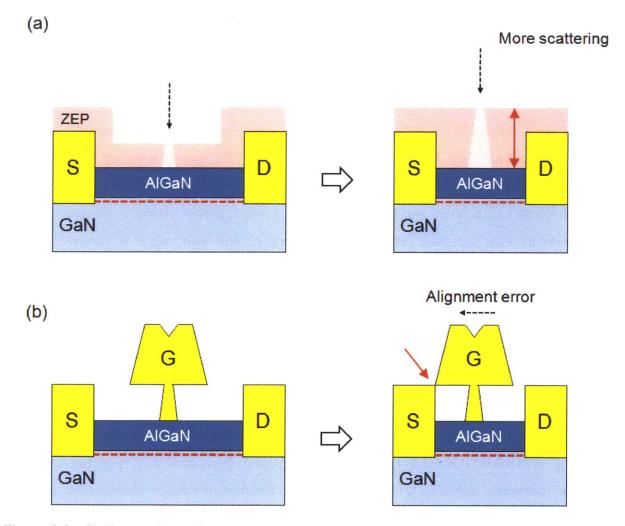

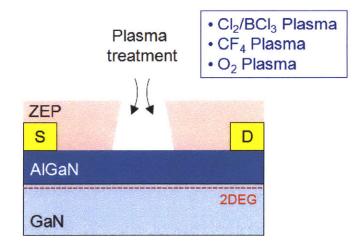

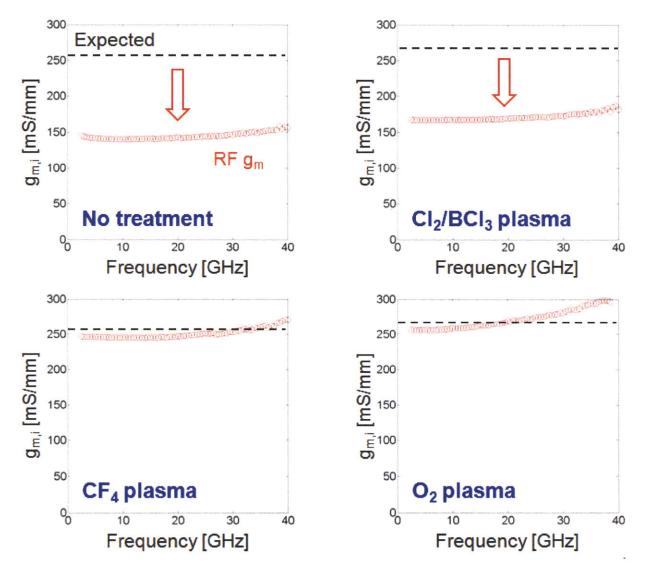

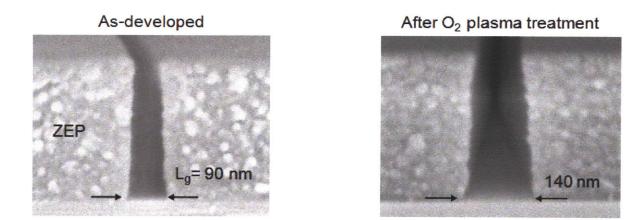

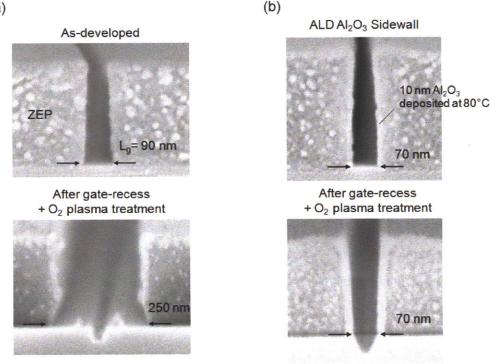

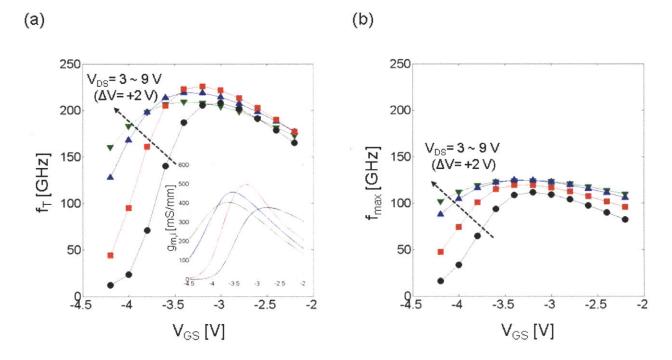

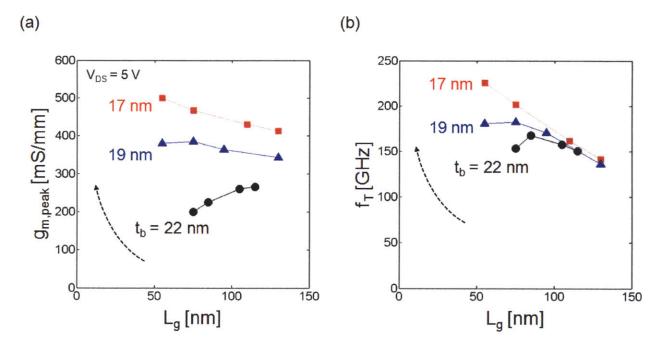

In chapter 4, advanced processing technologies are developed to demonstrate state-of-the-art  $f_T$  in GaN transistors. The lower-than-expected frequency performance observed in many AlGaN/GaN HEMTs is attributed to a significant drop of the intrinsic small-signal transconductance (RF  $g_m$ ) with respect to the intrinsic DC  $g_m$ . To reduce this RF  $g_m$ -collapse and improve high frequency performance, we have developed a new technology based on a combination of vertical gate-recess, oxygen plasma treatment, and lateral gate-etch technique which resulted in AlGaN/GaN HEMTs with a record  $f_T$  of 225 GHz for a gate length of  $L_g = 55$  nm, and 162 GHz for an  $L_g$  of 110 nm.

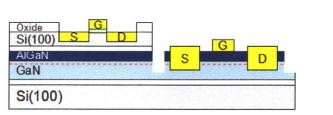

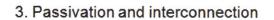

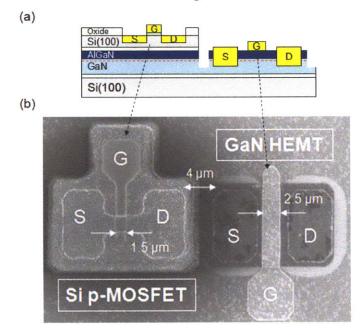

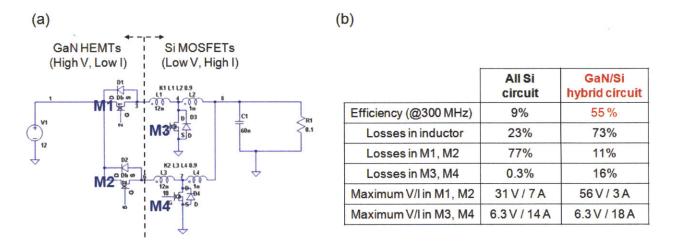

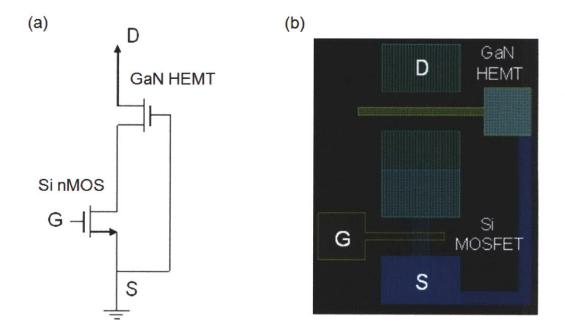

In chapter 5, the first on-wafer integration of Si(100) MOSFETs and GaN HEMT is demonstrated. A new layer transfer technology based on wafer bonding and etch-back process

was developed to enable on-wafer integration of both Ga- and N-face GaN HEMTs with Si(100) electronics. Using this technology, GaN and Si devices separated by less than 5  $\mu$ m from each other have been fabricated, which is suitable for building future heterogeneous integrated circuits.

In chapter 6, summary and conclusions are presented. Future work to further expand the frequency performance of AlGaN/GaN HEMTs beyond mm-wave frequencies is discussed. Also, research directions to investigate RF  $g_m$ -collapse and to improve the integration technology are provided.

# **1.5. References**

- [1] O. Ambacher, J. Smart, J. R. Shealy, N. G. Weimann, K. Chu, M. Murphy, R. Dimitrov, L. Wittmer, M. Stutzmann, W. Rieger, and J. Hilsenbeck, "Two-dimensional electron gases induced by spontaneous and piezoelectric polarization charges in N- and Ga-face AlGaN/GaN heterostructures," J. Appl. Phys., vol. 85, no. 6, pp. 3222-3233, Mar. 1999.

- [2] Y. Uemoto, D. Shibata, M. Yanagihara, H. Ishida, h. Matsuo, S. Nagai, N. Batta, M. Li, T. Ueda, T. Tanaka, and D. Ueda, "8300V blocking voltage AlGaN/GaN power HFET with thick poly-AlN passivation," *IEEE IEDM Tech. Digest*, pp. 861-864, 2007.

- [3] K. H. Chen, B. S. Kang, H. T. Wang, T. P. Lele, F. Ren, Y. L. Wang, C. Y. Chang, S. J. Pearton, D. M. Dennis, J. W. Johnson, P. Rajagopal, J. C. Roberts, E. L. Piner, and K. J. Linthicum, "c-erbB-2 sensing using AlGaN/GaN high electron mobility transistors for breast cancer detection," *Appl. Phys. Lett.*, vol. 92, no. 19, 192103, May. 2008.

- [4] F. Medjdoub, J. F. Carlin, M. Gonschorek, E. Feltin, M. A. Py, D. Ducatteau, C. Gaquiere, N. Grandjean, and E. Kohn, "Can InAlN/GaN be an alternative to high power/high temperature AlGaN/GaN devices?," *IEEE IEDM Tech. Digest*, 2006.

- [5] I. Akasaki, "Nitride semiconductors- impact on the future world," *Journal of Crystal Growth*, vol. 237-239, pp. 905-911, Apr. 2002.

- [6] H. P. Maruska and J. J. Tietjen, "The preparation and properties of vapor-deposited singlecrystalline GaN," *Appl. Phys. Lett.*, vol. 15, no. 10, pp. 327-329, Aug. 1969.

- [7] H. Amano, N. Sawaki, I. Akasaki, and Y. Toyoda, "Metalorganic vapor phase epitaxial growth of a high quality GaN film using an AlN buffer layer," *Appl. Phys. Lett.*, vol. 48, no. 5, pp. 353-355, Feb. 1986.

- [8] H. Amano, M. Kito, K. Hiramatsu, and I. Akasaki, "P-type conduction in Mg-doped GaN treated with low-energy electron beam irradiation (LEEBI)," *Jpn. J. Appl. Phys.*, vol. 28, no. 12, pp. L2112-L2114, Dec. 1989.

- [9] S. Nakamura, T. Mukai, M. Senoh, and N. Iwasa, "Thermal annealing effects on p-type Mg-doped GaN films," *Jpn. J. Appl. Phys.*, vol. 31, no. 2B, pp. L139-L142, Feb. 1992.

- [10] S. Nakamura, M. Senoh, S.Nagahama, N. Iwasa, T. Yamada, T. Matsushita, H. Kiyoku, and Y. Sugimoto, "InGaN-based multi-quantum-well-structure laser diodes," *Jpn. J. Appl. Phys.*, vol. 35, no. 1B, pp. L74-L76, Jan. 1996.

- [11] M. A. Khan, J. M. Van Hove, J. N. Kuznia, and D. T. Olson, "High electron mobility GaN/Al<sub>x</sub>Ga<sub>1-x</sub>N heterostructures grown by low-pressure metalorganic chemical vapor deposition," *Appl. Phys. Lett.*, vol. 58, no. 21, pp. 2408-2410, May. 1991.

- [12] M. A. Khan, A. Bhattarai, J. N. Kuznia, and D. T. Olson, "High electron mobility transistor based on a GaN-Al<sub>x</sub>G<sub>1-x</sub>aN heterojunction", *Appl. Phys. Lett.*, vol. 63, pp. 1214-1215, 1993.

- [13] Y.-F. Wu, A. Saxler, M. Moore, R. P. Smith, S. Sheppard, P. M. Chavarkar, T. Wisleder, U. K. Mishra, and P. Parikh, "30-W/mm GaN HEMTs by field plate optimization," *IEEE Electron Dev. Lett.*, vol. 25, pp. 117-119, 2004.

- [14] Y. F. Wu, M. Moore, A. Abrahamsen, M. Jacob-Mitos, P. Parikh, S. Heikman, and A. Burk, "High-voltage millimiter-wave GaN HEMTs with 13.7 W/mm power density," *IEEE IEDM Tech, Digest*, pp. 405-407, 2007.

- [15] M. Micovic, A. Kurdoghilian, P. Hashimoto, M. Hu, M. Antcliffe, P. J. Willadsen, W. S. Wong, R. Bowen, I. Milosavljevic, A. Schmitz, Y. Yoon, M. Wetzel, and D. H. Chow, "GaN HFET for W-band power applications," *IEEE IEDM Tech. Digest*, 2006.

- [16] Toshiba website: http://www.toshiba.com/taec/news/press\_releases/news\_pr\_10.jsp

- [17] M. Feng, S.-C. Shen, D. C. Caruth, J.-J Huang, "Device technologies for RF front-end circuits in next-generation wireless communications," *Proceedings of the IEEE*, vol. 92, no. 2, pp. 354-375, Feb. 2004.

- [18] E. O. Johnson, "Physical limitations on frequency and power parameters of transistors," *RCA Review*, vol. 26, pp. 163-177, Jun. 1965.

- [19] M. A. Khan, J. N. Kuznia, D. T. Olson, W. J. Schaff, J. W. Burm, and M. S. Shur, "Microwave performance of a 0.25 μm gate AlGaN/GaN heterostructure field effect transistor," *Appl. Phys. Lett.*, vol. 65, pp. 1121-1123, 1994.

- [20] Y.-F. Wu, B. P. Keller, S. Keller, N. X. Nguyen, M. Le, C. Nguyen, T. J. Jenkins, L. T. Kehias, S. P. DenBaars, and U. K. Mishra, "Short channel AlGaN/GaN MODFET's with 50-GHz f<sub>T</sub> and 1.7-W/mm output-power at 10 GHz," *IEEE Electron Dev. Lett.*, vol. 18, pp. 438-440, 1997.

- [21] M. Micovic, N. X. Nguyen, P. Janke, W.-S. Wong, P. Hashimoto, L.-M. McCray, and C. Nguyen, "GaN/AlGaN high electron mobility transistors with f<sub>T</sub> of 110 GHz," *Electronic Lett.*, vol. 36, pp. 358-359, 2000.

- [22] V. Kumar, W. Lu, R. Schwindt, A. Kuliev, G. Simin, J. Yang, M. A. Khan, and I. Adesida, "AlGaN/GaN HEMTs on SiC with f<sub>T</sub> of over 120 GHz," *IEEE Electron Dev. Lett.*, vol. 23, no. 8, pp. 455-457, Aug. 2002.

- [23] T. Palacios, E. Snow, Y. Pei, A. Chakraborty, S. Keller, S. P. DenBaars, and U. K. Mishra, "Ge-spacer technology in AlGaN/GaN HEMTs for mm-waver applications," *IEEE IEDM Tech. Digest*, 2005.

- [24] T. Palacios, A. Chakraborty, S. Heikman, S. Keller, S. P. DenBaars, and U. K. Mishra, "AlGaN/GaN high electron mobility transistors with InGaN back-barriers," *IEEE Electron Dev. Lett.*, vol. 27, no. 1, pp. 13-15, Jan. 2006.

- [25] M. Higashiwaki, T. Mimura, and T. Matsui, "30-nm-gate AlGaN/GaN heterostructure field-effect transistors with a current-gain cutoff frequency of 181 GHz," *Jpn. J. Appl. Phys.*, vol. 45, no. 42, pp. L1111-L1113, Oct. 2006.

- [26] M. Higashiwaki, T. Mimura, and T. Matsui, "AlGaN/GaN heterostructure field-effect transistors on 4H-SiC substrates with current-gain cutoff frequency of 190 GHz," *Appl. Phys. Express*, vol. 1, 021103, 2008.

- [27] G. H. Jessen, R. C. Fitch, J. K. Gillespie, G. Via, A. Crespo, D. Langley, D. J. Denninghoff, M. Trejo, and E. R. Heller, "Short-channel effect limitations on high-frequency operation of AlGaN/GaN HEMTs for T-gate devices," *IEEE Trans. Electron Devices*, vol. 54, no. 10, pp. 2589-2597, 2007.

- [28] T. Suemitsu, K. Shiojima, T. Makimura, and N. Shigekawa, "Intrinsic transit delay and effective electron velocity of AlGaN/GaN high electron mobility transistors," *Jpn. J. Appl. Phys.*, vol. 44, no. 6, pp. L211-L213, Jan. 2005.

- [29] Y.-R. Wu, M. Singh, and J. Singh, "Device scaling physics and channel velocities in AlGaN/GaN HFETs: Velocities and effective gate length," *IEEE Trans. Electron Devices*, vol. 53, no. 4, pp. 588-593, Apr. 2006.

- [30] M. C. Foisy, P. J. Tasker, B. Hughes, and L. F. Eastman, "The role of inefficient charge modulation in limiting the current-gain cutoff frequency of the MODFET," *IEEE Trans. Electron Devices*, vol. 35, pp. 871-878, 1988.

- [31] R. R. Schaller, "Moore's law: past, present, and future," *IEEE Spectrum*, vol. 34, no. 6, pp. 52-59, Jun. 1997.

- [32] S. E. Thompson and S. Parthasarathy, "Moore's law: the future of Si microelectronics," *Materials Today*, vol. 9, no. 6, pp. 20-25, Jun. 2006.

- [33] Intel website: http://www.intel.com/technology/mooreslaw/

- [34] S. Raman, T.-H. Chang, C. L. Dohrman, and M. J. Rosker, "The DARPA COSMOS program: the convergence of InP and silicon CMOS technologies for high-performance mixed-signal," *International Conference on Indium Phosphide and Related Materials* (*IPRM*), Jun. 2010.

25

-

# **Chapter 2. Basics of GaN HEMTs**

### 2.1. DC analysis

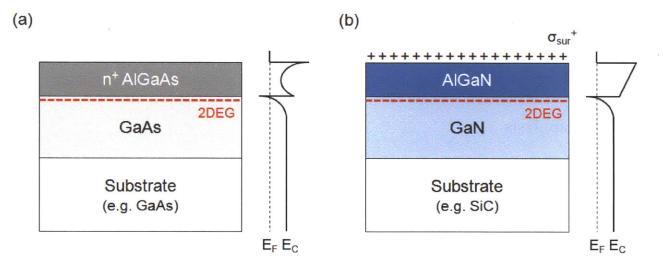

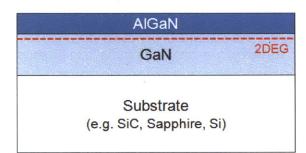

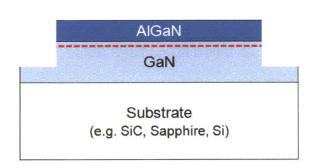

The High Electron Mobility Transistor (HEMT) is a field effect transistor incorporating a heterojunction between two layers of dissimilar crystalline semiconductors with different band gaps. The first HEMT was developed by Mimura et al. in 1980 [1] and the first commercial HEMT was used as a cryogenic low-noise amplifier for the radio telescope in 1985 which later discovered new interstellar molecules in the Taurus Molecular Cloud about 400 light years away [2]. The most important feature of the HEMT is the two-dimensional electron gas (2DEG), a gas of electrons which is induced at the heterojunction interface. Figure 2-1(a) shows the schematic of the widely studied AlGaAs/GaAs HEMT in which the wider band gap AlGaAs layer is ndoped to provide electrons to the 2DEG at the interface. The excess electrons in the AlGaAs layer diffuses toward the adjacent narrower band gap GaAs layer due to its lower energy level. The diffusion of these electrons creates an electric field in the direction to oppose the electron movement. The electron diffusion and electron drift balance each other, creating a junction at equilibrium similar to a p-n junction. Thus, electrons now reside in undoped narrower band gap GaAs layer forming the 2DEG. The 2DEG is tightly confined in the direction perpendicular to the heterojunction interface, however free to move in the parallel direction. The main advantage of the 2DEG in HEMTs is its higher electron mobility than in other field effect transistors such as metal-oxide-semiconductor field effect transistor (MOSFET) and metal-semiconductor field effect transistor (MESFET). The physical separation of the dopants (e.g. in the AlGaAs layer) from the mobile carrier electrons (e.g. in the GaAs layer) allows the 2DEG in HEMTs to have reduced ionized impurity scattering and high mobility.

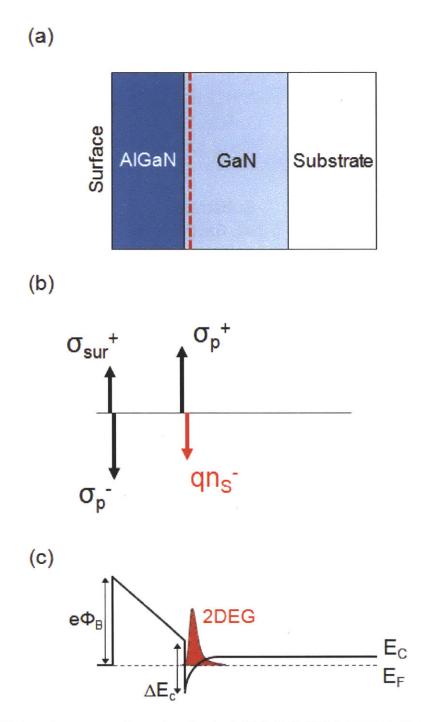

In nitride semiconductors, a commonly used material combination for HEMT structures is an AlGaN barrier and a GaN channel layer as shown in Figure 2-1(b). The AlGaN/GaN system benefits not only from its high electron mobility (~ 2000 cm<sup>2</sup>/V·s) but also from the high 2DEG density (~  $10^{13}$  cm<sup>-2</sup>) thanks to the large conduction band discontinuity between AlGaN and GaN. Contrary to AlGaAs/GaAs devices, the high 2DEG density is not induced by doping, but

Figure 2-1. Schematic cross-section of (a) AlGaAs/GaAs and (b) AlGaN/GaN heterostructure with associated conduction band diagrams. The 2DEG in AlGaAs/GaAs system is provided from the n-doped AlGaAs layer by the balance of electron drift/diffusion while the 2DEG in AlGaN/GaN system is produced by donor-like AlGaN surface states with the polarization field inside AlGaN layer. Intentional doping is not necessary to form the 2DEG in AlGaN/GaN system.

by donor-like surface states at the AlGaN surface facilitated by spontaneous and piezoelectric polarization electric field inside the AlGaN layer [3]. The 2DEG density in this case is mainly determined by the thickness of AlGaN layer and the amount of aluminum percentage in it.

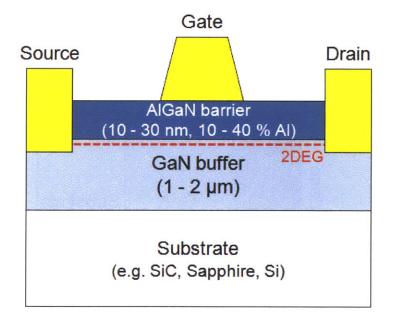

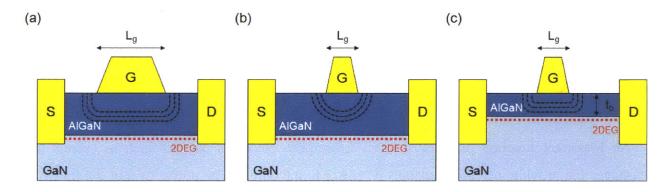

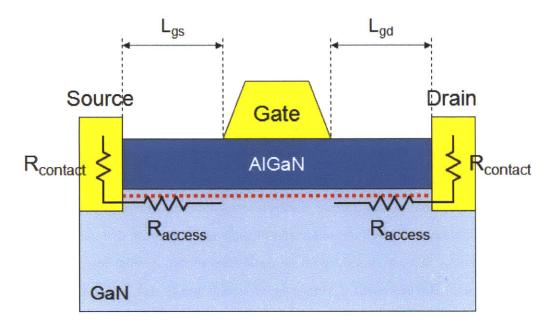

Figure 2-2 shows a schematic cross-section of a standard AlGaN/GaN HEMT. The current flows from the drain to the source ohmic contacts, and it is controlled by the voltage in the Schottky gate electrode, which varies the 2DEG density. Accurate modeling of carrier transport in AlGaN/GaN HEMTs typically requires solving the Schrödinger and Poisson equations, and sometimes even time-consuming Monte Carlo simulations. However, massive computational modeling/simulation can sometimes obscure the important physical concepts behind the HEMT operation. As an engineer, it is important to have an insight to solve practical challenges timely with an eye toward identifying problems and optimizing performance. In this regard, to develop equations that are compact enough to allow general analysis and problem solving is very useful. Therefore, in this section we will focus on a relatively simple analytical form, yet sufficient to estimate practical operation of GaN HEMTs. For the simple analytical model, the linear charge control approximation, the gradual channel approximation, and two-piece linear velocity-field model are used.

Figure 2-2. Schematic cross-section of a standard AlGaN/GaN HEMT.

#### 2.1.1. Charge control model

The charge distribution in HEMTs is determined by electrostatics and varied by applying a voltage to the gate electrode. A one-dimensional charge control model describes the behavior of the charge in the direction perpendicular to the heterojunction interface as a function of the gate voltage. Figure 2-3 illustrates a schematic diagram of an AlGaN/GaN HEMT structure along with resulting charge distribution and band diagram. From the point of view of charge control, the main difference between AlGaN/GaN HEMTs and conventional HEMTs is the origin of the electrons in the 2DEG. In conventional HEMTs, the channel electrons are provided by the intentionally doped barrier layer, while in AlGaN/GaN HEMTs they come from donor-like surface states. Under linear charge control approximation, the 2DEG charge density is given by

$$qn_s = C(V_{GS} - V_{th}) \tag{2-1}$$

where q is the electronic charge,  $n_s$  is the 2DEG carrier density, C is the gate capacitance per unit area, and the  $V_{th}$  is the threshold voltage. The 2DEG is assumed to behave as a perfect twodimensional sheet whose centroid is placed at a distance  $\Delta d$  from the heterointerface ( $\Delta d \approx 20$  Å for AlGaN/GaN system [4]). The physical origin of  $\Delta d$  is the spread of the 2DEG wave function at the AlGaN/GaN interface and C is given by

Figure 2-3. (a) Schematic cross-section of a standard AlGaN/GaN heterostructure along with (b) the charge distribution and (c) the conduction band diagram.  $\sigma_{sur}^+$  is the positively ionized surface state charge and  $\sigma_p$  is the polarization induced charge.

$$C = \frac{\varepsilon}{d_{AlGaN} + \Delta d} \tag{2-2}$$

where  $\varepsilon$  is the dielectric constant between the AlGaN surface and the 2DEG, and  $d_{AlGaN}$  is the AlGaN barrier thickness. The threshold voltage  $V_{th}$  is the gate voltage required to completely deplete the 2DEG carrier density ( $n_s = 0$ ) at the source end of the gate.  $V_{th}$  can be given by following the energy bands from the Fermi level in the metal to the lowest level of the triangular quantum well in the GaN and

$$V_{th} = \phi_B - \frac{\sigma_p \cdot d_{AlGaN}}{\varepsilon} - \frac{\Delta E_c}{q}$$

(2-3)

where  $\Phi_B$  is the Schottky barrier height,  $\Delta E_c$  is the conduction band discontinuity, and  $\sigma_p$  is the net polarization charge at the AlGaN/GaN interface ( $\sigma_p = \sigma_{p,AlGaN} - \sigma_{p,GaN}$ ). Thus, by substituting Eq. (2-2) and Eq. (2-3) into Eq. (2-1), the 2DEG charge density at the source end of the gate as a function of gate voltage  $V_{GS}$  can be written as

$$qn_s = \frac{\varepsilon}{d_{AlGaN} + \Delta d} \left( V_{GS} - \phi_B + \frac{\sigma_p \cdot d_{AlGaN}}{\varepsilon} + \frac{\Delta E_c}{q} \right)$$

(2-4)

#### 2.1.2. Velocity-field relationship

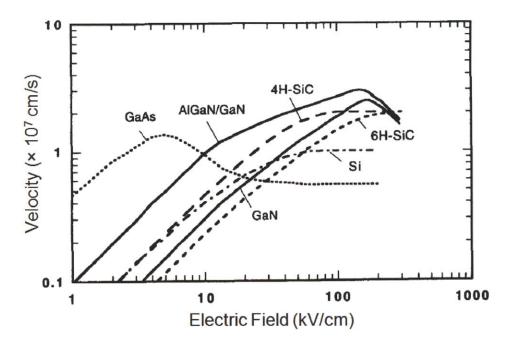

In general, the drift velocity of carriers at high electric fields deviates from the linear relationship observed at low fields. Figure 2-4 shows a plot of average electron drift velocity as a function of applied electric field for several semiconductors [5]. The drift velocity in AlGaN/GaN HEMTs, for example, peaks at approximately  $3 \times 10^7$  cm/s at an electric field of about 160 kV/cm and then decreases. At even higher electric fields, the drift velocity becomes saturated as in the case of GaAs to a value of about  $1 \times 10^7$  cm/s (not shown in Figure 2-4). The slope of the drift velocity versus electric field is the differential mobility and the negative differential mobility at high electric field is mainly due to the intervalley electron transfer [6].

Figure 2-4. Carrier velocity vs. electric field for several semiconductors [5].

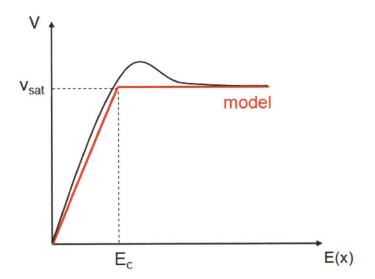

Typically, such a velocity-field relationship can be simplified by two-piece linear velocity-field model as shown in Figure 2-5.

$$v = \begin{cases} \mu E(x) & \text{for } E(x) < E_c \\ v_{sat} & \text{for } E(x) > E_c \end{cases}$$

(2-5)

where  $\mu$  is the low field mobility, E(x) is the channel electric field,  $E_c$  is the critical electric field for the velocity saturation, and  $v_{sat}$  is the carrier saturation velocity.

Figure 2-5. The velocity-field relationship in AlGaN/GaN HEMTs is simplified by two-piece linear velocity-field model ( $v = \mu E(x)$  for  $E(x) < E_C$  and  $v = v_{sat}$  for  $E(x) > E_C$ ).

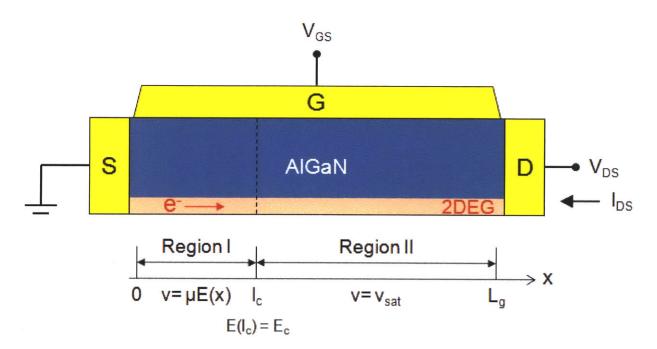

Figure 2-6. Schematic cross-section of the AlGaN/GaN HEMT structure used in this chapter to analyze the operating principle of GaN transistors. Extrinsic source and drain access regions are neglected and the origin of *x*-axis is set to the source end of the gate.

#### 2.1.3. DC characteristics

The intrinsic AlGaN/GaN HEMT is divided into two regions as shown in Figure 2-6, namely the linear region (Region I) and the velocity saturation region (Region II). During the device operation, a drain bias is applied and an x-dependent potential V(x) (or E(x) = dV(x)/dx) exists along the channel. In Region I, the electric field E(x) is smaller than the critical electric field  $E_c$  $(E(x) < E_c)$  and the electron drift velocity follows  $v = \mu E(x)$ . The boundary between Region I and Region II is set to the point where the magnitude of the electric field reaches the critical value  $E_c$ . In Region II, E(x) is high enough  $(E(x) > E_c)$  for the electrons to travel with their saturation velocity  $v_{sat}$ .

The drain current  $I_{DS}$  normalized to the gate width at any position x can be expressed as

$$I_{DS} = qn_s(x)v(x) \tag{2-6}$$

By taking into account the channel potential V(x) between the position x and the source end of the gate, the 2DEG charge density is given by

$$qn_s = C(V_{GS} - V_{th} - V(x))$$

(2-7)

In the Region I ( $E(x) < E_c$ ), substituting Eq. (2-5) and Eq. (2-7) into Eq. (2-6) leads to

$$I_{DS} = C(V_{GS} - V_{th} - V(x)) \cdot \mu \frac{dV(x)}{dx}$$

(2-8)

Rearranging the result yields a differential equation with separated variables, and integrating it over the Region I gives,

$$I_{DS} = \frac{\mu C}{x} \left[ (V_{GS} - V_{th}) V(x) - \frac{V(x)^2}{2} \right]$$

(2-9)

When the applied drain bias is small, the Region I extends over the entire channel and by substituting  $x = L_g$  and  $V(x) = V_{DS}$ , the drain current in the linear region of an AlGaN/GaN HEMTs can be written as

$$I_{DS,lin} = \frac{\mu C}{L_g} \left[ (V_{GS} - V_{th}) V_{DS} - \frac{V_{DS}^2}{2} \right]$$

(2-10)

The transconductance is defined as the rate of change in the drain current with respect to  $V_{GS}$  and can be obtained by differentiating Eq. (2-10) with respect to  $V_{GS}$ .

$$g_{m,lin} = \frac{\mu C}{L_g} V_{DS} \tag{2-11}$$

Now, if the applied drain bias is large enough to induce velocity saturation somewhere in the channel, Eq. (2-10) no longer holds. To derive the drain current in the saturation region, we focus on the boundary condition between Region I and Region II. In Eq. (2-9), solving for V(x) and E(x) gives,

$$V(x) = V_{GS} - V_{th} - \sqrt{(V_{GS} - V_{th})^2 - \frac{2I_{DS}x}{\mu C}}$$

(2-12)

$$E(x) = \frac{dV(x)}{dx} = \frac{I_{DS}}{\mu C \sqrt{(V_{GS} - V_{th})^2 - \frac{2I_{DS}x}{\mu C}}}$$

(2-13)

At the boundary between Region I and Region II where  $x = l_c$ , the saturation velocity  $v_{sat}$  needs to satisfy  $v_{sat} = \mu E(l_c) = \mu E_c$  following the two-piece linear velocity-field model. Thus, from Eq. (2-13) the drain current in the saturation region in AlGaN/GaN HEMTs can be calculated as

$$I_{DS,sat} = v_{sat} C \left[ \sqrt{(V_{GS} - V_{th})^2 + (l_c E_c)^2} - l_c E_c \right]$$

(2-14)

The saturation current is primarily controlled by the gate voltage  $V_{GS}$ . The transconductance in the saturation region is obtained by differentiating Eq. (2-14) with respect to  $V_{GS}$ .

$$g_{m,sat} = v_{sat} C \frac{V_{GS} - V_{th}}{\sqrt{(V_{GS} - V_{th})^2 + (l_c E_c)^2}}$$

(2-15)

In short gate length devices,  $l_c$  becomes small and Eq. (2-14) and Eq. (2-15) reduce to

$$I_{DS,sat} \approx v_{sat} C (V_{GS} - V_{th})$$

(2-16)

$$g_{m,sat} \approx v_{sat} C \tag{2-17}$$

It is noted that the saturation velocity  $v_{sat}$  can be replaced by the ballistic velocity  $v_{\theta}$  when the device operates in the ballistic region.

It should be noted that only the intrinsic part of AlGaN/GaN HEMT has been considered so far. The effect of the extrinsic components, such as source and drain resistances ( $R_s$  and  $R_d$ ), can be included by redefining  $V_{GS}$  and  $V_{DS}$  as

$$V_{GS} = V_{GS,ext} - I_{DS}R_s \tag{2-18}$$

$$V_{DS} = V_{DS,ext} - I_{DS}(R_s + R_d)$$

(2-19)

where  $V_{GS,ext}$  and  $V_{DS,ext}$  are externally applied voltages to the gate and drain electrodes, respectively.

# 2.2. RF analysis

As the operating frequency of the device increases to the microwave range (f = 300 MHz ~ 300 GHz,  $\lambda = c / f = 1$  m ~ 1 mm), standard circuit theory generally cannot be used directly to analyze the device and circuit. At such high frequencies, the wavelength of the signal is comparable to the physical dimension of the device and there exists appreciable phase shift in voltage or current over the physical extent of the device. The device can be analyzed by solving the complete Maxwell's equations, however it is mathematically complicated and often provides more information than what we need for most practical purposes. We are typically interested in terminal quantities such as voltage and current. For this purpose, the two-port network concept and associated small-signal equivalent circuit model are typically used to describe microwave transistors and to analyze frequency performance of the device.

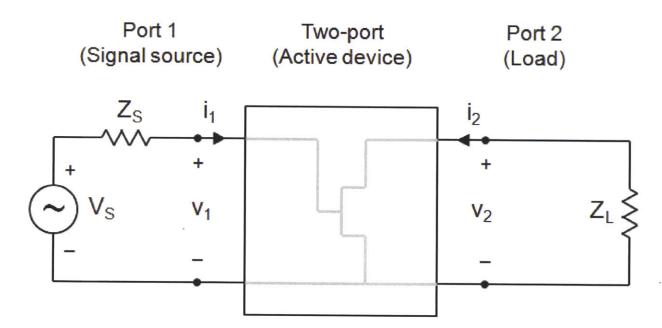

Figure 2-7. A microwave transistor (active device) regarded as a two-port network with signal source and load.

#### 2.2.1. Two-port network

Any active device, including microwave AlGaN/GaN HEMTs, can be treated as a two-port network as shown in Figure 2-7. Port 1 refers to the input connected to a signal source consisting of a voltage source  $V_s$  and a source impedance  $Z_s$ . Port 2 is the output connected to a load impedance  $Z_L$ . The input and output currents of the two-port network are denoted as  $i_1$  and  $i_2$ , while the input and output voltages are  $v_1$  and  $v_2$ . The two-port network analysis considers the active device as a black box whose input and output voltages and currents can be measured at each port. These terminal quantities can be related to several important figures of merit to characterize any active device. There is a number of parameter sets such as Y-, Z-, H-, or Sparameters which contain essentially the same information, but represent it in a different way. For example, the Y-parameters relate  $i_1$ ,  $i_2$ ,  $v_1$ , and  $v_2$  under ac short-circuit conditions as

$$\begin{bmatrix} i_1 \\ i_2 \end{bmatrix} = \begin{bmatrix} y_{11} & y_{12} \\ y_{21} & y_{22} \end{bmatrix} \begin{bmatrix} v_1 \\ v_2 \end{bmatrix}$$

$$i_1 = y_{11}v_1 + y_{12}v_2 \qquad i_2 = y_{21}v_1 + y_{22}v_2$$

$$y_{11} = \frac{i_1}{v_1}\Big|_{v_2=0} \qquad y_{12} = \frac{i_1}{v_2}\Big|_{v_1=0} \qquad y_{21} = \frac{i_2}{v_1}\Big|_{v_2=0} \qquad y_{22} = \frac{i_2}{v_2}\Big|_{v_1=0}$$

Figure 2-8. Two-port network characterized by the incident  $(a_1, a_2)$  and reflected  $(b_1, b_2)$  waves (S-parameters).

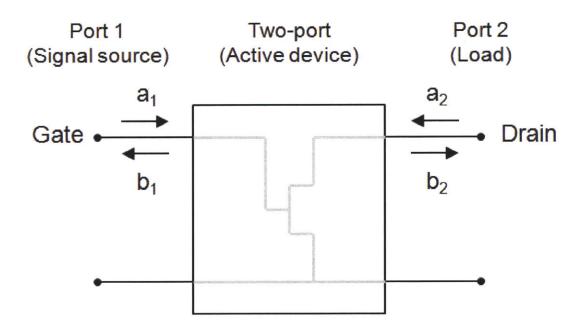

where  $y_{11}$  and  $y_{22}$  are the input and output admittances, and  $y_{12}$  and  $y_{21}$  are reverse and forward transfer admittances, respectively. Since the Y-parameters are more closely related to device physics and conceptually easier to interpret than other parameter sets, they are widely used for microwave devices. However, although Y-parameters are more easily interpretable, it is very difficult to measure external voltages and currents and to realize the required short-circuit terminations in the microwave range. Therefore, another set of parameters called S-parameters is typically used to obtain the device information. Then, the measured S-parameters are converted to Y-parameters to interpret its characteristics. The S-parameters are ratios of the powers of travelling wave signals and can be measured directly with a vector network analyzer. During the S-parameter measurement, each signal can be isolated by the termination with a matched load to eliminate its reflection. The use of the-more-difficult-to-implement short- or open-circuit terminations is, in that way, avoided. The S-parameters of a two-port network are expressed in a similar manner to the Y-parameters.

$$\begin{bmatrix} b_1 \\ b_2 \end{bmatrix} = \begin{bmatrix} s_{11} & s_{12} \\ s_{21} & s_{22} \end{bmatrix} \begin{bmatrix} a_1 \\ a_2 \end{bmatrix}$$

$$b_1 = s_{11}a_1 + s_{12}a_2 \qquad b_2 = s_{21}a_1 + s_{22}a_2$$

$$s_{11} = \frac{b_1}{a_1} \Big|_{output \ match} \qquad s_{12} = \frac{b_1}{a_2} \Big|_{input \ match} \qquad s_{21} = \frac{b_2}{a_1} \Big|_{output \ match} \qquad s_{22} = \frac{b_2}{a_2} \Big|_{input \ match}$$

where *a* and *b* are the powers of incident and reflected waves as shown in Figure 2-8.  $s_{11}$  and  $s_{22}$  are the input and output reflection coefficients, and  $s_{12}$  and  $s_{21}$  are reverse and forward gains, respectively.  $s_{11}$  and  $s_{21}$  are measured by terminating the output port with a matched load, while  $s_{12}$  and  $s_{22}$  are extracted by terminating the input port with a matched load. The conversion equations between the different sets of parameters (e.g. S- to Y-parameters) are given in Appendix 1.

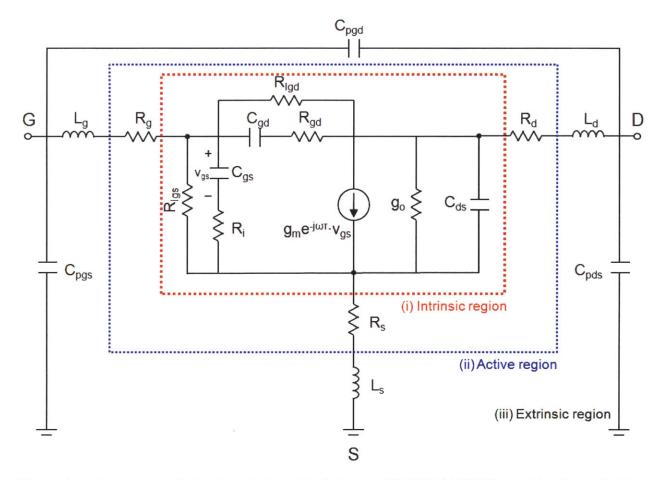

#### 2.2.2. Small-signal equivalent circuit

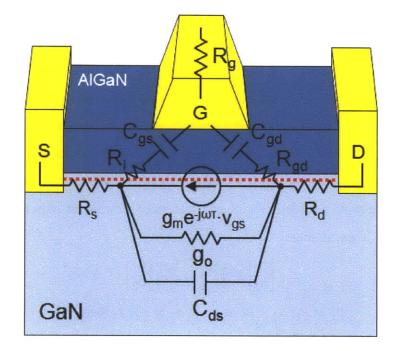

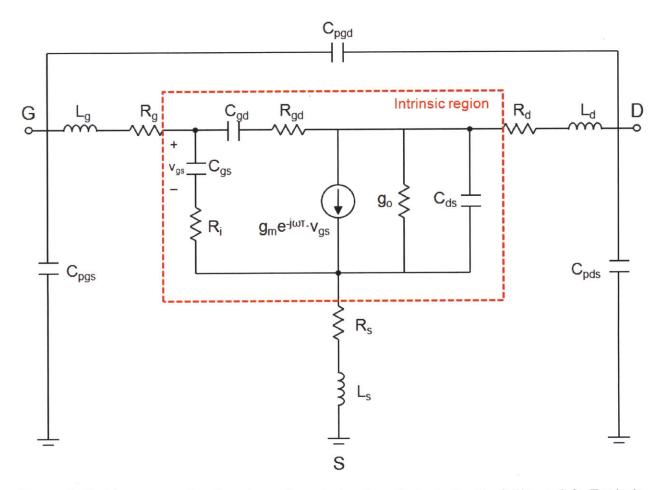

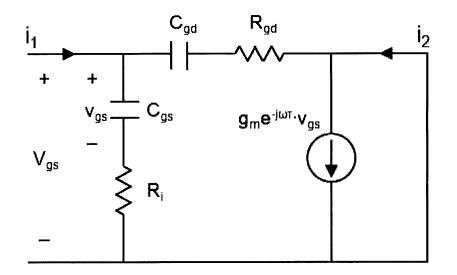

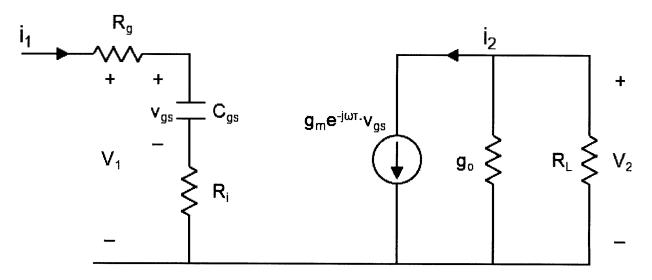

The high frequency operation of the device is often studied in terms of the small-signal equivalent circuit model. The small-signal implies that the magnitude of the signal voltage is on the order  $k_BT / q$  (~ 26 mV at T = 300 K). Under such a small-signal condition, nonlinear characteristics of a field-effect transistor such as an AlGaN/GaN HEMT can be linearized and described by a linear small-signal equivalent circuit with lumped elements, as shown in Figure 2-9. Each of the circuit elements has a physical origin in the device operation and their description is listed in Table 2-1. Figure 2-10 illustrates a more complete view of the small-signal equivalent circuit including parasitic pad capacitances and inductances.

Figure 2-9. Small-signal equivalent circuit elements for a HEMT structure (e.g. AlGaN/GaN HEMT).

Figure 2-10. More comprehensive view of small-signal equivalent circuit of Figure 2-9. Extrinsic parasitic pad capacitances and inductances are included. Intrinsic region of the device is highlighted by the red dotted line.

|                     |                 | Term                                                                      | Physical description                                              |  |

|---------------------|-----------------|---------------------------------------------------------------------------|-------------------------------------------------------------------|--|

| Extrinsic Intrinsic | C <sub>gs</sub> | Gate-source capacitance                                                   | Gate charge modulation by changing $V_{GS}$                       |  |

|                     | $C_{ga}$        | Gate-drain capacitance                                                    | Gate charge modulation by changing $V_{DS}$                       |  |

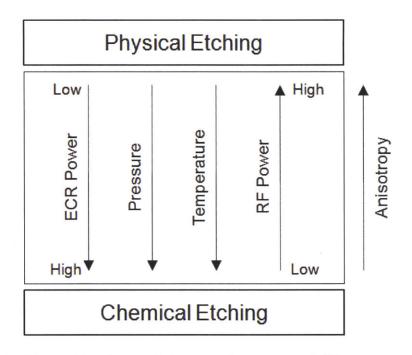

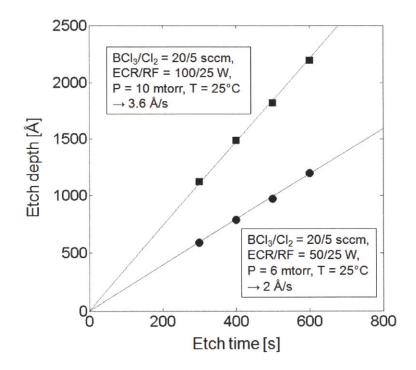

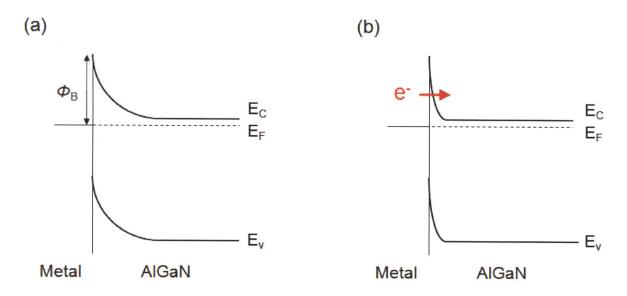

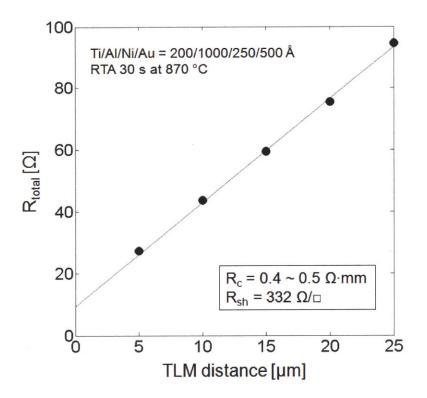

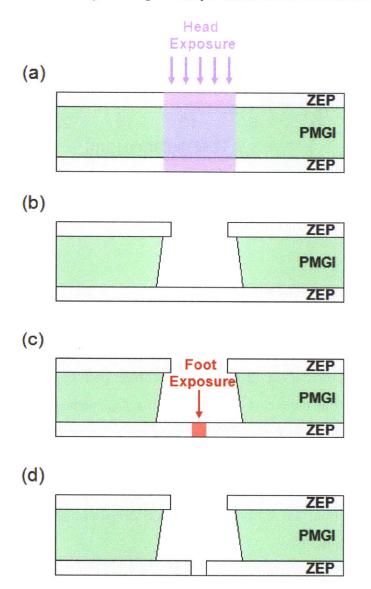

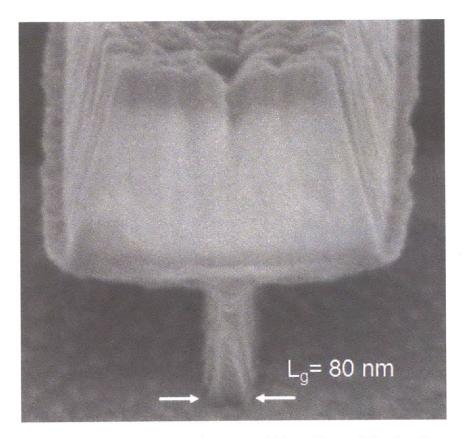

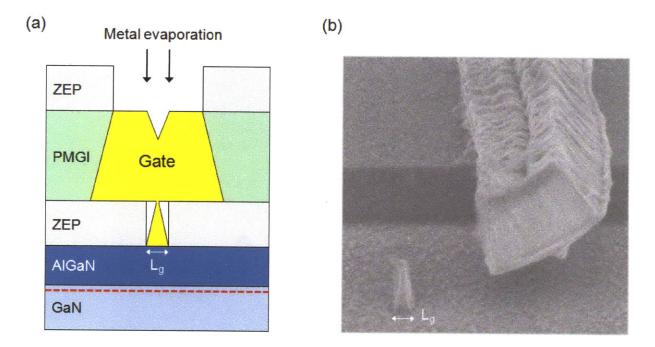

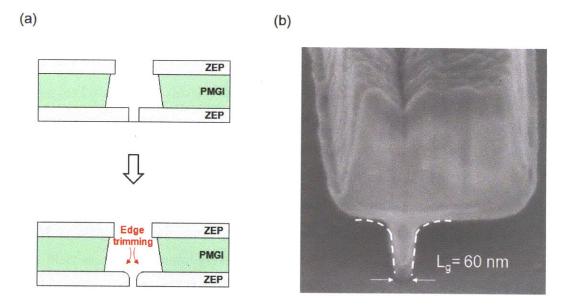

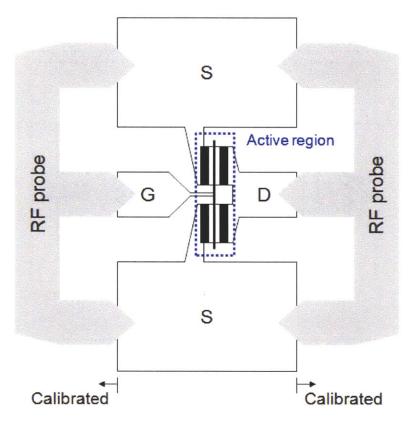

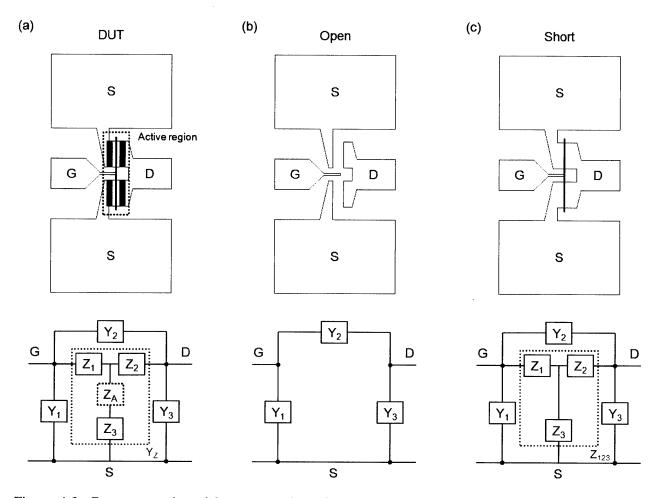

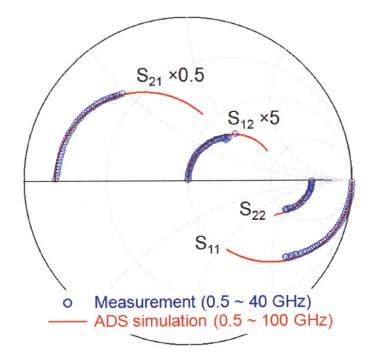

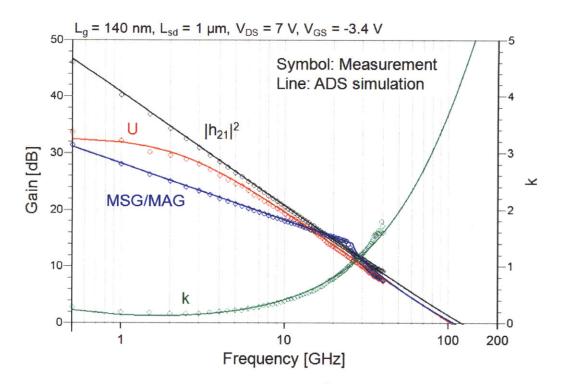

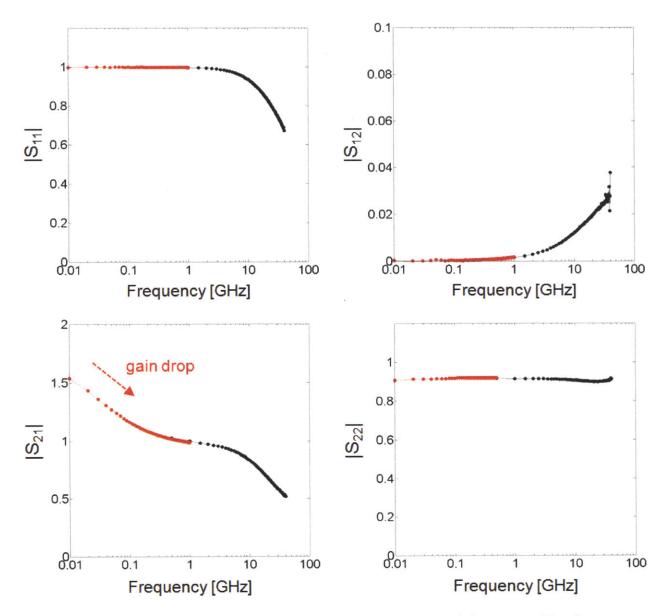

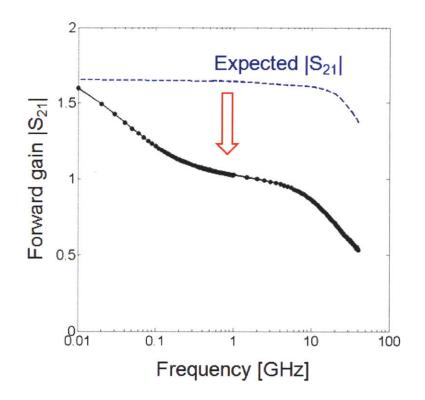

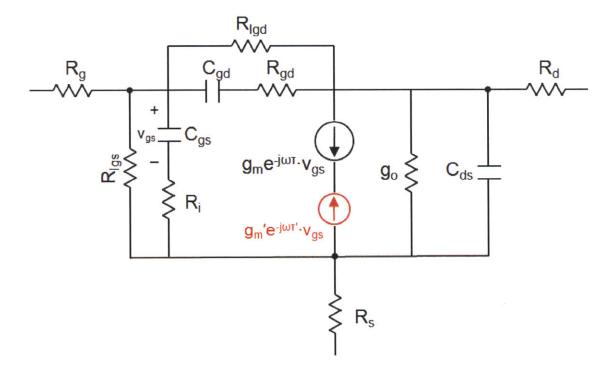

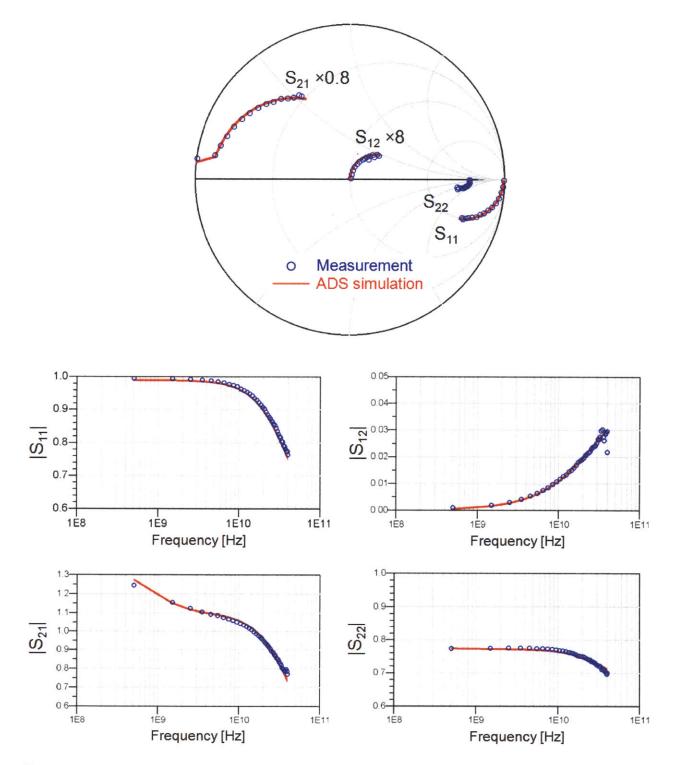

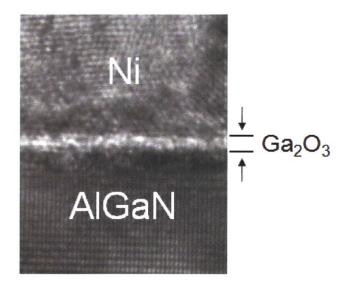

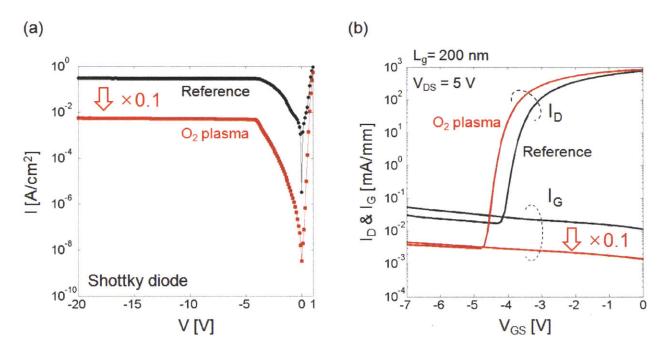

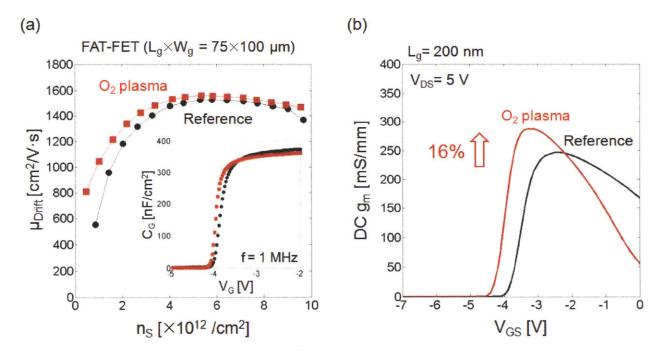

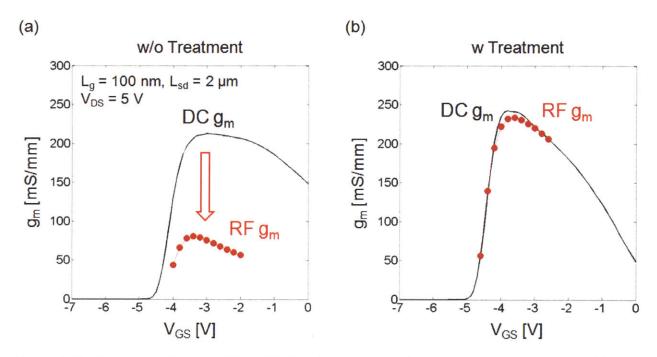

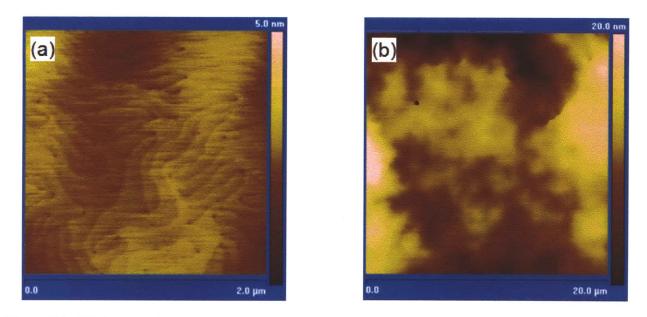

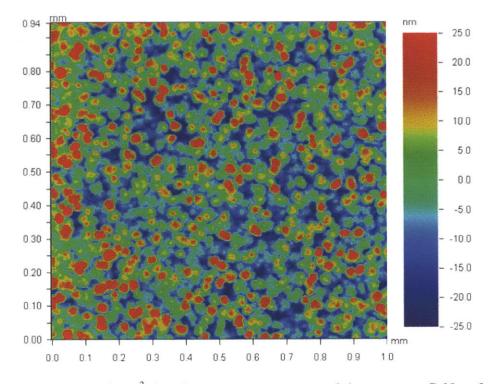

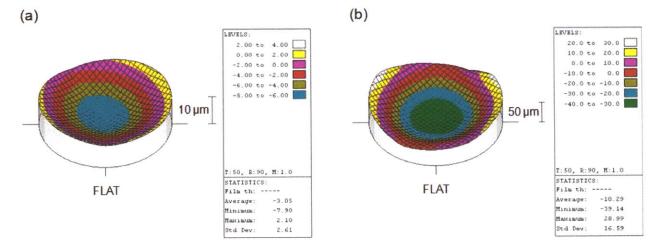

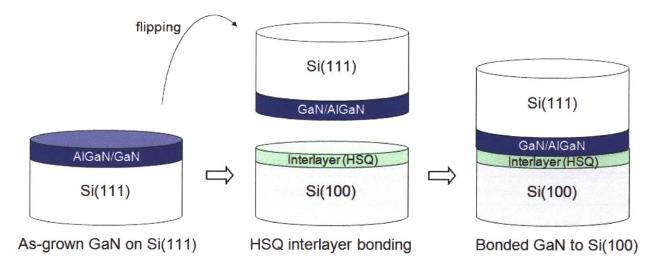

|                     | Cat             | Drain-source capacitance                                                  | Capacitance between drain and source (e.g. substrate capacitance) |  |