#### provided by DSpace@MI

# Optimization and Validation of Discontinuous Galerkin Code for the 3D Navier-Stokes Equations

by

## Eric Hung-Lin Liu

Submitted to the Department of Aeronautics and Astronautics in partial fulfillment of the requirements for the degree of

Master of Science in Aerospace Engineering

at the

## MASSACHUSETTS INSTITUTE OF TECHNOLOGY

## February 2011

© Massachusetts Institute of Technology 2011. All rights reserved.

| Author       |                                                     |

|--------------|-----------------------------------------------------|

|              | Department of Aeronautics and Astronautics          |

|              | January 27, 2011                                    |

| Certified by |                                                     |

|              | David L. Darmofal                                   |

|              | Professor of Aeronautics and Astronautics           |

|              | Thesis Supervisor                                   |

| Accepted by  |                                                     |

|              | Eytan H. Modiano                                    |

| A            | Associate Professor of Aeronautics and Astronautics |

|              | Chairman, Graduate Program Committee                |

# Optimization and Validation of Discontinuous Galerkin Code for the 3D Navier-Stokes Equations

by

Eric Hung-Lin Liu

Submitted to the Department of Aeronautics and Astronautics on January 27, 2011, in partial fulfillment of the requirements for the degree of Master of Science in Aerospace Engineering

#### Abstract

From residual and Jacobian assembly to the linear solve, the components of a high-order, Discontinuous Galerkin Finite Element Method (DGFEM) for the Navier-Stokes equations in 3D are presented. Emphasis is given to residual and Jacobian assembly, since these are rarely discussed in the literature; in particular, this thesis focuses on code optimization. Performance properties of DG methods are identified, including key memory bottlenecks. A detailed overview of the memory hierarchy on modern CPUs is given along with discussion on optimization suggestions for utilizing the hierarchy efficiently. Other programming suggestions are also given, including the process for rewriting residual and Jacobian assembly using matrix-matrix products. Finally, a validation of the performance of the 3D, viscous DG solver is presented through a series of canonical test cases.

Thesis Supervisor: David L. Darmofal

Title: Professor of Aeronautics and Astronautics

## Acknowledgments

I would like to give my thanks to all of my friends and colleagues who have made this research possible. First and foremost, I must thank my advisor, Professor David Darmofal who has given me a great deal of encouragement and guidance throughout our relationship. He even puts up with my inverted, "night-owl" sleep schedule. Professor Darmofal and I first met when I was a freshman at MIT. He offered me a summer, undergraduate research position with the Project X team. Six years later, I have continued to work on the Project X team, and my efforts have crossed over almost as many different topics. I am of course looking forward to continuing working with Professor Darmofal.

Speaking of the Project X team (who also put up with my inverted schedule), I would not be where I am today without the help, cooperation, and tireless efforts of all of them: Julie Andren, Laslo Diosady, Bob Haimes, Josh Krakos, JM Modisette, Huafei Sun, and Masayuki Yano. I would also like to thank past Project X members whom I worked with previously: Garrett Barter, Krzysztof Fidkowski, Todd Oliver; they were all a huge help when I was getting started. Masa deserves an additional thank you for sharing his deep knowledge of finite elements with me and fielding countless questions from me.

I would also like to thank my close friends, Isaac Asher, Sharmin Karim, Tom Morgan, and Kathy Ye, for providing support throughout this process and providing me with ample distractions when coding frustration left me at my wit's end.

Finally, I would like to thank the U.S. Department of Energy and the Krell Institute for awarding me with the D.O.E. Computational Science Graduate Fellowship. The CSGF Program has been a wonderful opportunity for me, both in terms of my research and in terms of meeting new and exciting people.

# Contents

| 1 | Intr | roduction                                            | 15        |

|---|------|------------------------------------------------------|-----------|

|   | 1.1  | Literature Review                                    | 19        |

|   | 1.2  | Optimization Basics                                  | 23        |

| 2 | The  | e Discontinuous Galerkin Finite Element Method       | <b>25</b> |

|   | 2.1  | DG Spatial Discretization                            | 26        |

|   |      | 2.1.1 Inviscid Component                             | 27        |

|   |      | 2.1.2 Viscous Component                              | 27        |

|   | 2.2  | Temporal Discretization                              | 28        |

| 3 | Con  | nputational Costs of the DG Method                   | 31        |

|   | 3.1  | Residual and Jacobian Evaluation                     | 31        |

|   |      | 3.1.1 Inviscid Discretization                        | 31        |

|   |      | 3.1.2 Viscous Discretization                         | 35        |

|   |      | 3.1.3 Quadrature                                     | 39        |

|   | 3.2  | Nonlinear Solve                                      | 39        |

|   | 3.3  | Linear Solve via ILU Preconditioned, Restarted GMRES | 40        |

|   | 3.4  | Example Problems                                     | 42        |

|   | 3.5  | Performance Limitations                              | 49        |

| 4 | The  | e Memory Hierarchy                                   | 59        |

|   | 4.1  | CPU Caches                                           | 60        |

|   | 4 2  | A Note about Multicore CPUs                          | 78        |

|              | 4.3  | Paging and Virtual Memory                               | 81  |

|--------------|------|---------------------------------------------------------|-----|

|              |      | 4.3.1 The Translation Lookaside Buffer                  | 83  |

| 5            | Opt  | imizing a DG Implementation                             | 91  |

|              | 5.1  | Residual and Jacobian Evaluation                        | 91  |

|              | 5.2  | GMRES                                                   | 97  |

| 6            | Vali | idation                                                 | 101 |

|              | 6.1  | Case 1: Diffusion                                       | 102 |

|              | 6.2  | Case 2: (Steady) Convection-Diffusion                   | 102 |

|              | 6.3  | Case 3: Poiseuille Flow                                 | 104 |

|              | 6.4  | Case 4: (Steady) Navier-Stokes                          | 106 |

| 7            | Con  | nclusion                                                | 111 |

|              |      | 7.0.1 Future Work                                       | 112 |

| $\mathbf{A}$ | Invi | scid and Viscous Fluxes for the Navier-Stokes Equations | 115 |

|              | A.1  | Inviscid Flux                                           | 115 |

|              | A.2  | Viscous Flux                                            | 116 |

|              | A.3  | Deriving the $\mathcal A$ Matrix                        | 116 |

| В            | Dou  | ible Data Rate Random Access Memory                     | 119 |

|              | B.1  | Bandwidth and Latency                                   | 121 |

|              |      | B.1.1 Bandwidth                                         | 121 |

|              |      | B.1.2 Latency                                           | 122 |

|              | B.2  | Memory Performance                                      | 123 |

| $\mathbf{C}$ | The  | e CPU                                                   | 125 |

|              | C.1  | Basic Data Flow                                         | 125 |

|              | C.2  | The CPU Pipeline                                        | 126 |

|              | C.3  | Branch Prediction                                       | 130 |

|              | C.4  | Out of Order Execution                                  | 137 |

| D       | GMRES Stopping Criterion                   | 145 |

|---------|--------------------------------------------|-----|

| ${f E}$ | Code Development Practices for Performance | 149 |

# List of Figures

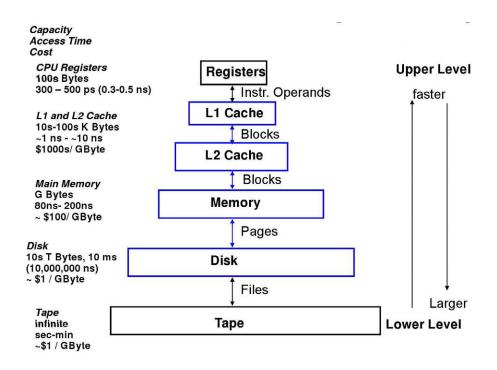

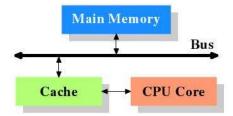

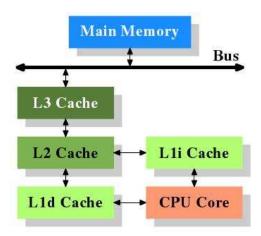

| 1-1 | A rendition of the cache hierarchy in modern computers[4]       | 17  |

|-----|-----------------------------------------------------------------|-----|

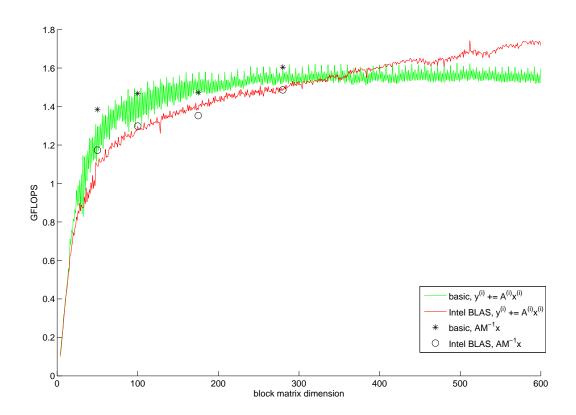

| 3-1 | Block-sparse matrix-vector multiply performance                 | 51  |

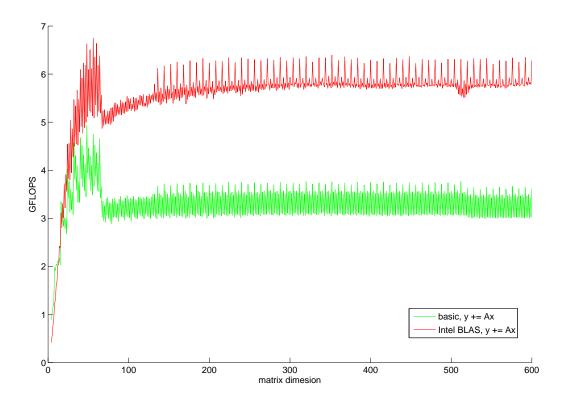

| 3-2 | Dense matrix-vector multiply performance                        | 54  |

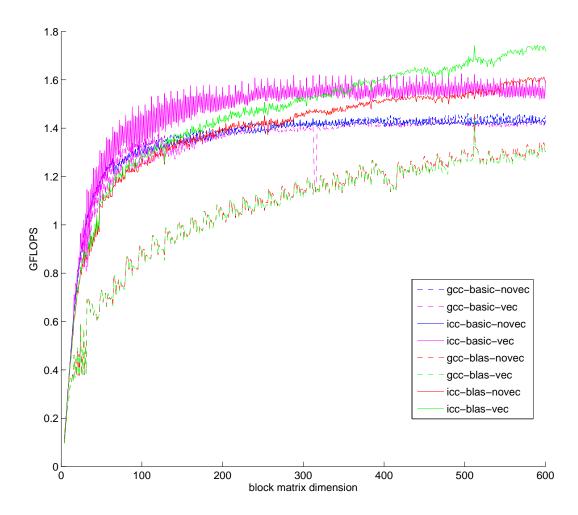

| 3-3 | Block-sparse matrix vector performance with different compilers | 57  |

| 4-1 | A simple 2 level cache hierarchy[20]                            | 60  |

| 4-2 | Multilevel cache layout                                         | 62  |

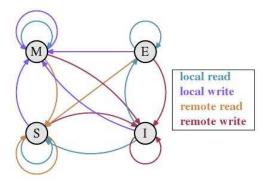

| 4-3 | The states of the MESI Protocol[20]                             | 79  |

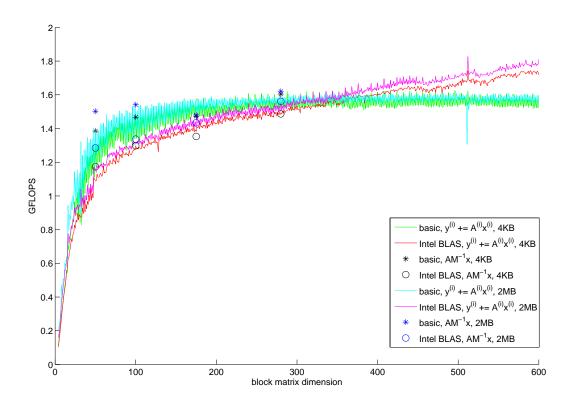

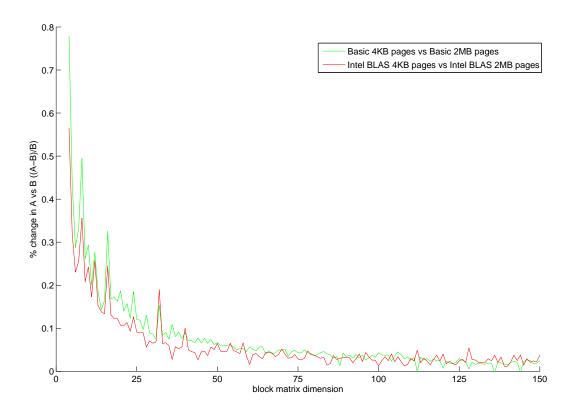

| 4-4 | Block-sparse matrix-vector multiply with 2MB pages              | 88  |

| 4-5 | 4KB pages versus 2MB pages                                      | 89  |

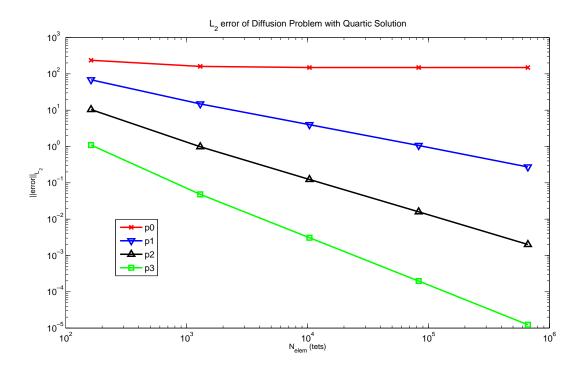

| 6-1 | $L_2$ -norm error convergence for Case 1                        | 103 |

| 6-2 | $H_1$ -seminorm error convergence for Case 1                    | 103 |

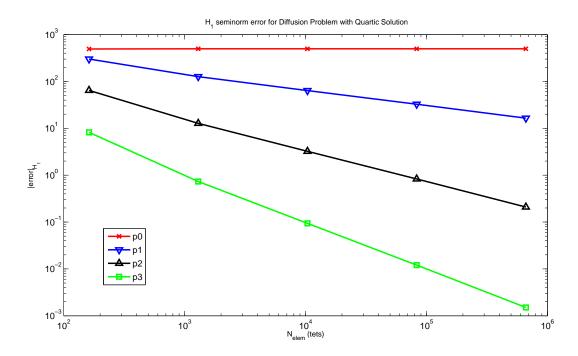

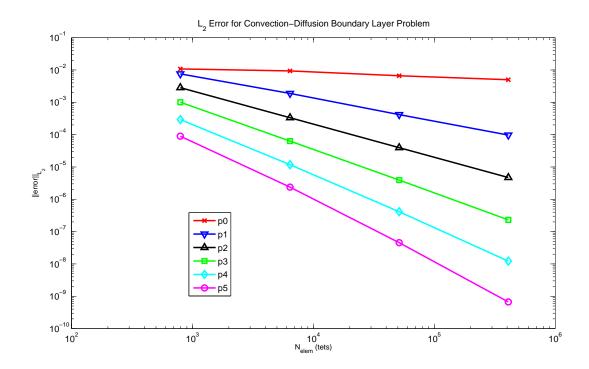

| 6-3 | $L_2$ -norm error convergence for Case 2                        | 105 |

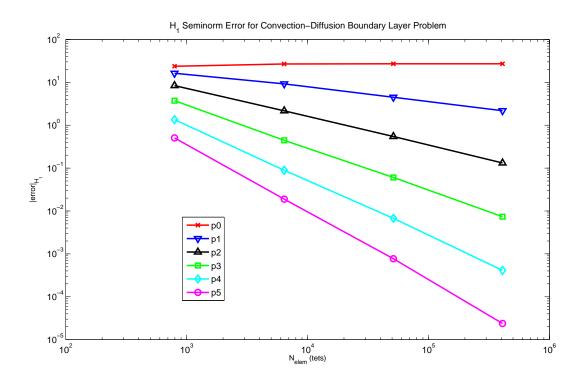

| 6-4 | $H_1$ -seminorm error convergence for Case 2                    | 105 |

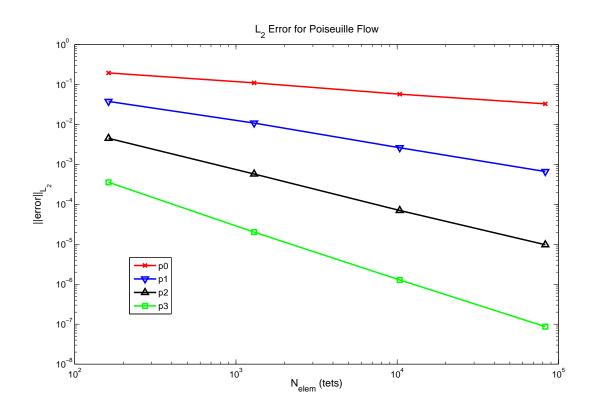

| 6-5 | $L_2$ -norm error convergence for Case 3                        | 106 |

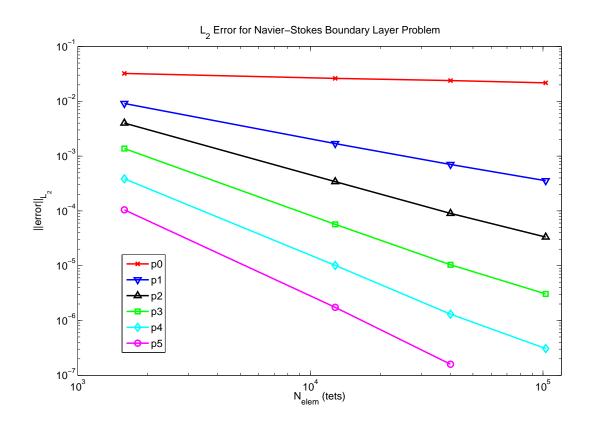

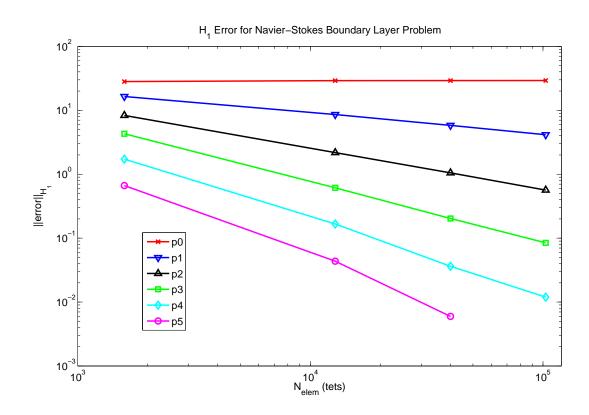

| 6-6 | $L_2$ -norm error convergence for Case 4                        | 108 |

| 6-7 | $H_1$ -norm error convergence for Case 4                        | 109 |

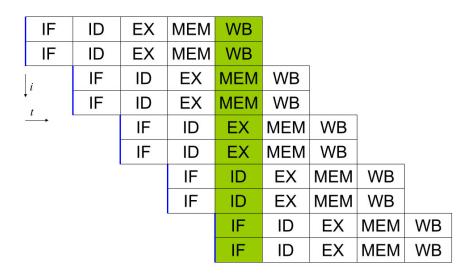

| C-1 | A simple CPU pipeline                                           | 127 |

# List of Tables

| 1.1 | Instruction latencies (in CPU cycles) for common operations |

|-----|-------------------------------------------------------------|

| 3.1 | Case 1 description                                          |

| 3.2 | Case 2 description                                          |

| 3.3 | Case 3 description                                          |

| 3.4 | Case 4 description                                          |

| 3.5 | Timing results for residual and Jacobian assembly           |

| 3.6 | Timing results for GMRES                                    |

| 3.7 | Comparison of total residual/Jacobian and GMRES times       |

| 3.8 | Comparison of GMRES stopping criterion                      |

| 3.9 | Block sizes for common governing equations                  |

| 4.1 | Core 2 (Penryn) cache characteristics                       |

| 4.2 | Core i7 (Nehalem) cache characteristics                     |

| 4.3 | AMD Phenom (K10) cache characteristics                      |

| 4.4 | Time to transpose a $m \times m$ matrix                     |

| 4.5 | Assembly commands for prefetching                           |

| 4.6 | Processor consistency example                               |

| 4.7 | TLB characteristics for various processors                  |

| 6.1 | Rate of convergence for Case 1                              |

| 6.2 | Rate of convergence for Case 2                              |

| 6.3 | Rate of convergence for Case 3                              |

| 6.4 | Rate of convergence for Case 4                              |

| A.1 | Inviscid (Euler) flux components           | 115 |

|-----|--------------------------------------------|-----|

| A.2 | Viscous flux components                    | 116 |

| C.1 | BTB characteristics for various processors | 136 |

| E.1 | Useful compiler options for icc and gcc    | 154 |

| E.2 | Useful compiler options for icc            | 155 |

| E.3 | Useful compiler options for gcc            | 156 |

| E.4 | Alignment of Primitives in Linux64         | 160 |

# Chapter 1

# Introduction

The classic approach to analyzing the performance of a numerical algorithm is to count the number of arithmetic operations required. For example, it is well known that the inner product  $x^Ty$  for  $x, y \in \mathbb{R}^n$  requires n floating-point multiplies and n-1 floating-point additions; or that the matrix product AB for  $A \in \mathbb{R}^{m \times k}$  and  $B \in \mathbb{R}^{k \times n}$  requires mnk multiplies and mn(k-1) additions. For dense inputs, exactly these amounts of computation must occur. The basic matrix-matrix product algorithm is a mere 10 lines of code. But the most advanced BLAS implementations involve thousands of lines of hand-crafted assembly.

Clearly, a simple count of arithmetic operations is insufficient. For starters, the multiplication operations are about 5 times as expensive as the additions. Additionally, in order to multiply two array elements, the computer must resolve their memory addresses. This amounts to additional integer multiply and add operations. However, the CPU also needs to access those addresses: memory access is the dominant cost by far. Memory accesses are around 50 times more costly than arithmetic operations for these types of algorithms. Table 1.1 contains the cycle-latencies of a few common CPU instructions (data movement, integer arithmetic, floating point arithmetic) along with the latency incurred by reading from main memory.

If the CPU always waited 200 cycles (memory access) to do 5 cycles (floating point multiplication) of work, the CPU would end up spending most of its time waiting. As

<sup>&</sup>lt;sup>1</sup>For sufficiently large problems; i.e., problems that do not fit in cache.

| Description                 | x86 ASM      | Latency       | Throughput       |

|-----------------------------|--------------|---------------|------------------|

| Move from r to r            | MOV          | 1             | 3                |

| Move from r to m            | MOV          | 2             | 1                |

| Move from m to r            | MOV          | 3             | 1                |

| Logic (AND, OR, XOR)        | AND, OR, XOR | 1             | 3                |

| int add                     | ADD          | 1             | 3                |

| 32-bit, signed int mult     | IMUL         | 3             | 1                |

| 64-bit, signed int mult     | IMUL         | 5             | $\frac{2}{3}$    |

| 32-bit, signed int div      | IDIV         | 14-23         | -                |

| 64-bit, signed int div      | IDIV         | 34-88         | -                |

| x87 double load/store       | FLD/FST      | 1-3           | $\frac{1}{3}$ -1 |

| x87 double add              | FADD         | 3             | 1                |

| x87 double mult             | FMUL         | 5             | 0.5              |

| x87 double div              | FDIV         | 6-21          | 0.05-0.2         |

| Packed int move             | MOVDQA       | 2             | 1                |

| Packed int add              | PADDQ        | 1             | 2                |

| Packed int mult             | PMULDQ       | 3             | 1                |

| Packed, aligned double move | MOVAPD       | 1-3           | 1-3              |

| Packed double add           | ADDPD        | 3             | 1                |

| Packed double mult          | MULPD        | 5             | 1                |

| Packed double div           | DIVPD        | 6-21          | 0.05-0.2         |

| register miss               | -            | 3-5           | -                |

| L1 cache miss               | -            | 10-20         | -                |

| L2 cache miss               | -            | $\approx 200$ | -                |

Table 1.1: Instruction latencies (in CPU cycles) for the Intel Core2 (45nm) processor[26]. The letters r,m,xmm indicate a general register, a memory address, and an XMM (SSE) register, respectively. All x87 instructions assume full precision (80 bits); note that double-precision SSE instructions are 64-bit. Latency indicates the time taken by the appropriate execution unit to complete the specified operation. Unless otherwise specified, all times assume that operands are already in registers and no exceptions (e.g., NAN) occured. Throughput is the maximum number of independent instructions of a type simultaneously in flight; a value of say 0.25 indicates that this instruction can be executed at most once every 4 cycles.

a result, modern CPUs have several levels of *cache*. Cache provides much faster access to data; for example, the L1 cache on an Intel Core 2 has a 3 cycle latency and the L2 cache has a 15 cycle latency. Unfortunately, due to expense, caches are very small compared to main memory; the latency and size of cache, memory, etc. scale inversely. In modern computers, the system of fast caches, main memory, and data storage in general is often called the *memory hierarchy*. Figure 1-1 provides a pictorial overview of the memory hierarchy of modern CPUs, showing some rough estimates for latencies and costs of various cache levels. The memory hierarchy is discussed at length in Chapter 4.

Figure 1-1: A rendition of the cache hierarchy in modern computers[4].

Over the last few years, the Project X group in the MIT Aerospace Computational Design Laboratory has been developing an hp-adaptive, Discontinuous Galerkin Finite Element Method (DGFEM). Thus far, research and development have focused on the underlying numerical algorithms. However, as problems of interest become increasingly complex (e.g., viscous flows in 3D), improving computational performance has come into the spotlight. In this thesis, we will survey the aspects of modern computer architecture that are most relevant to DGFEM methods, giving emphasis to the memory hierarchy. Finally, the correctness of

the DGFEM method in Project X will be demonstrated through a series of canonical test cases.

The goals of this thesis are as follows:

- Analyze the performance characteristics of a higher-order, DGFEM code (ProjectX)

on model problems that emphasize relevant modes of operation. Apply the analysis

to guide optimization of the residual and Jacobian assembly processes as well as the

linear solve.

- Validate the steady-state, viscous, 3D discretization of ProjectX by performing gridconvergence studies on various test cases.

- Produce this document as a guide and starting point for other researchers and engineers

interested in writing high-performance scientific codes. Many examples will be drawn

from a DGFEM implementation, but the ideas discussed are relevant to a much broader

class of programs.

While the present thesis concentrates on optimization of a serial implementation, most applications will require a parallel implementation. However, for the residual and Jacobian assembly, improvements to the serial performance reflect similarly in the parallel performance. Differences in relative improvements in the serial versus parallel performance would be attributable to the communication overhead, which is small for DG methods. For the linear solver, the same statement may be true, depending on how the parallel system is preconditioned. Thus, while parallel cases are not specifically discussed in this thesis, the serial optimization techniques remain relevant.

This thesis is organized as follows. The remainder of the introduction includes a review of relevant literature and an overview of software tools used in the optimization process. Chapter 2 covers the DG discretization of the Navier-Stokes equations, along with the computational costs of the DG method (residual and Jacobian assembly, nonlinear solver, linear solver). Example cases are provided, and major performance limitations in DG solvers are identified. Chapter 4 covers the memory hierarchy used in modern computers, including discussion of how to utilize it efficiently. Chapter 5 covers particular components of a DG

implementation that should be targeted for optimization. Chapter 6 presents the validation of a DGFEM solver for the Navier-Stokes equations in 3D. The appendices cover the implementation of viscous fluxes for the Navier-Stokes equations (Appendix A), the operation and performance of modern DDR memory modules (Appendix B), the operation of modern CPUs (Appendix C), two stopping-criterion choices for iterative linear solvers (Appendix D), and a collection of helpful, performance-enhancing coding practices (Appendix E).

## 1.1 Literature Review

While the theory of DG methods is well-developed, the literature contains relatively little on the optimization of DG implementations. However, regardless of the application, the need for efficient, high-performance codes is well recognized. This survey covers some relevant developments in CG methods, sparse iterative solvers, and dense linear algebra on traditional CPUs; references for implementing and optimizing DG methods and Krylov methods are also presented. Unfortunately, few works cited here discuss methods that are directly applicable to this thesis. For example, most sparse matrix-vector optimizations are designed for general sparse matrices.<sup>2</sup> But the principles used to guide these optimizations are relevant. The most common theme in the cited works is the importance of properly utilizing the memory hierarchy of the target architecture to improve performance.

As discussed in Chapter 4, modern CPUs (and GPUs) have very deep memory hierarchies. As a result, using algorithms that often access the slowest memory levels is generally sub-optimal. This fact is well-recognized by computer scientists, engineers, etc; thus fast algorithms must find ways to minimize communication between fast cache(s) and slow memory (or even slower hard disks).

The BeBOP group at the University of California, Berkeley is responsible for a great deal of work on communication-minimizing implementations of common linear algebra kernels [10, 34, 53]. [34, 53] discuss a class of communication-avoiding Krylov methods.<sup>3</sup> These

<sup>&</sup>lt;sup>2</sup>The Jacobian matrix arising from DG discretizations is special in that it possesses natural block structure. Jacobians from other discretizations (e.g., finite difference or finite volume) do not have this structure. Note that the DG block structure is not helpful when the blocks are tiny; i.e., the polynomial order and/or the number of states is low.

<sup>&</sup>lt;sup>3</sup>In parallel, communication refers to node-to-node data transfer. In serial, communication refers to

methods perform the same (asymptotically) amount of work as a s-step Krylov method, but involve only as much communication as a single step. The methods are divided into several kernels. For example, GMRES involves communication-avoiding matrix powers (computing  $b, Ab, A^2b, \ldots, A^sb$ ), block Gram-Schmidt, QR factorization of a "tall and skinny" matrix, and other relatively minor dense matrix operations. [34] also provides substantial discussion on the numerical stability of these methods. Unfortunately, these methods are currently limited to relatively weak preconditioners (e.g., Jacobi).

One particularly common technique for communication reduction is called blocking or tiling; blocking is important for both sparse and dense linear algebra, though the particulars of its implementation differ. For a (dense) matrix-matrix product, its optimality was proven by Hong for dense problems implemented sequentially (proof later strengthened to the parallel case by Irony). [10] extends previous analysis to include communication lower bounds for other direct linear algebra kernels (e.g., Cholesky, LU, QR, eigen/singular values, etc.) for both dense and sparse matrices, in both sequential and parallel environments. Implementation is not the focus of their work; indeed not all of the analyzed kernels have matching, optimal implementations.

[45] provides a detailed description and analysis of the blocking technique for dense matrix-matrix products. Optimized implementations of the BLAS<sup>4</sup> 3 function dgemm take heavy advantage of this optimization; BLAS 2 functions (e.g., dgemv) also utilize blocking, but the benefit is less substantial. Since optimized BLAS implementations are commonplace, many researchers attempt to improve memory performance by restructuring their code to utilize these routines [6, 21, 43, 44]. Outside of blocking for matrix-matrix products, [10] provides references for a number of other algorithms for direct linear algebra achieving optimal communication bounds.

For sparse linear algebra, the concept of minimizing memory transfers remains important, but the exact meaning of blocking is different. [35] provides a thorough discussion

memory reads and writes.

<sup>&</sup>lt;sup>4</sup>The Basic Linear Algebra Subroutines are a set of functions for solving problems that are fundamental in dense linear algebra. The functions are divided into 3 levels: BLAS 1, BLAS 2, and BLAS 3. BLAS 1 performs  $\Theta(m)$  work on  $\Theta(m)$  data; e.g., operations (scaling, dot product) on vectors. BLAS 2 performs  $\Theta(m^2)$  work on  $\Theta(m^2)$  data; e.g., matrix-vector operations and outerproducts. BLAS 3 performs  $\Theta(m^3)$  work on  $\Theta(m^2)$  data; e.g., matrix-matrix operations.

(implementation, analysis, experiment) of the two most common techniques, (sparse) cache-blocking and (sparse) register-blocking. [55] provides an important insight: the effectiveness of (sparse) cache-blocking is primarily governed by TLB misses;<sup>5</sup> [19] also notes the importance of TLB misses on sparse matrix operations (in the context of multigrid). One major issue with these optimizations is that the performance is strongly dependent on the sparsity pattern, in addition to block-size and computer architecture. The issue is often approached with auto-tuning, wherein a software package estimates performance for a given matrix type and generates specialized code accordingly. By comparison, static, architecture-targeted code (e.g., MKL, GOTO) can be generated for dense linear algebra; these routines often outperform auto-tuned code (e.g., ATLAS).

Baker's LGMRES and BLGMRES methods improved iterative solver performance by heuristically augmenting the Krylov subspace used in GMRES [8, 7]. LGMRES adds additional Krylov vectors based on previous restarts; BLGMRES adds additional right-hand sides. The Ax kernel of a BLGMRES solver with 4 right-hand sides could be expected to be 4 times as costly as Ax in standard GMRES, since there are 4 times as many Ax products and 4 times as many Krylov vectors. BLGMRES almost never cuts the number of GMRES iterations by a factor of the number of right-hand sides. The performance of BLGMRES depends on handling all right-hand sides simultaneously (by interleaving the vectors) instead of sequentially. This prevents loading A from memory repeatedly, an operation which is memory bandwidth-limited.

There has also been work implementing GMRES on GPUs for general sparse matrices[46, 70]. The focuses of these works is preconditioning and the sparse matrix-vector product kernel in GMRES, the latter of which is also discussed in [15]. These researchers implemented code on essentially the same hardware, but often saw very different performance gains. The differences are likely due to a combination of differing implementations and differing input matrices. Improving sparse matrix vector products on GPUs centers around selecting the best sparse storage format; while CSR (or CSC)<sup>6</sup> is usually adequate on CPUs. On the

<sup>&</sup>lt;sup>5</sup>TLB stands for Translation Lookaside Buffer; it is used to cache memory address translations from virtual to physical. See Section 4.3.1 for details.

<sup>&</sup>lt;sup>6</sup>Compressed Sparse Row or Column.

preconditioning side, the most common choice for GPUs was subdomain-wise block Jacobi with inexact local solves via ILU. Unfortunately this preconditioner does not exhibit weak scaling,<sup>7</sup> so its performance is lacking for higher order DG discretizations of the Navier-Stokes equations [18].

Residual and Jacobian assembly are far less analyzed than linear solvers. [54] summarizes the importance of this component of finite element methods:

Besides the solution of the set of linear equations, the element evaluation and assembly for stabilized, highly complex elements on unstructured grids is often a main time consuming part of the calculation. Whereas a lot of research is done in the area of solvers and their efficient implementation, there is hardly any literature on efficient implementation of advanced finite element formulations. Still a large amount of computing time can be saved by an expert implementation of the element routines.

They consider CGFEM on a vector machine (SX-6), which lives between modern CPUs and GPUs. The operation reordering they suggest substantially improves performance on a vector machine. However it is not the best choice for CPUs. Their ordering is not what [44] use, but it may have applications on GPUs as well. Also [54] provides examples that demonstrate the effectiveness of the restrict keyword; see Appendix E for details.

[44] considers the evaluation of the DG residual on GPUs, for Maxwell's Equations, which form a linear, hyperbolic system. They were interested in time-dependent problems; RK4 provided an explicit temporal discretization. Implicit-time solvers and elliptic operators were not considered; Jacobian assembly (especially with viscous terms) adds considerable complexity. Their work was also limited to linear representations of boundaries. The optimizations considered center around stating the residual assembly process using BLAS 3 functions.<sup>8</sup> Due to substantial restrictions on data layout imposed by current GPU BLAS implementations, [44] designs new algorithms and orderings to achieve better performance. Their work focused around how to divide the work of residual assembly across hundreds of GPU threads; how to store solution data and intermediate results to optimize memory

$<sup>^{7}\</sup>mathrm{An}$  algorithm scales weakly when increasing the problem size and number of processors such that the degrees of freedom per processor remains constant does not affect the run-time.

<sup>&</sup>lt;sup>8</sup>The technique of [44] is different than what will be suggested in Section 5.1 because [44] uses optimizations specific to DG discretizations of linear, hyperbolic equations using linear elements.

performance; and how and when to fetch data from memory so that numerous threads could be served in minimal time.

# 1.2 Optimization Basics

Avoiding premature optimization is always critical. Before proceeding with any code modification, a good first step is to evaluate which parts of the code are consuming the greatest amount of time ("hot spots") and which parts of the code are easiest to improve. Such evaluations are typically case dependent; for example, with flow solvers, steady solutions spend substantially more time in the linear solve than their unsteady counterparts. If a program component only consumes 1% of the runtime, then even if it could be removed completely, the speedup is only 1%. If that 1% gain costs months of development time, it may not be worthwhile. At the same time, if it takes a few hours of work, every little bit helps. For better or for worse, many complex programs do not spend the majority of their time in a single leaf routine; thus performance gains often come through a combination of many small gains, rather than through one large step.

Additionally, improving "wall-clock" performance needs to be weighed against decreases in "performance" measured in terms of code clarity, maintainability, and extensibility. For example, there are very few (if any) instances in finite element methods where developers should be coding in assembly language, even though carefully tuned assembly can provide the best performance as with some optimized BLAS libraries. The time required to develop and maintain code is also a resource, and the balance between performance measures like development and execution time will depend on the objectives of a code project.

A number of tools exist to aid in the profiling process. A few popular examples include OProfile[42], GNU gprof[22, 30], and Intel's VTune[37]. Profiling falls into two main categories: event-based and time-based. Time-based profiling attempts to measure how much time a program spends in each of its member functions.

Time-based profiling can be as simple as inserting system clock (or other timing mecha-

<sup>&</sup>lt;sup>9</sup>This analysis style follows Amdahl's Law, a well-known formula for computing the maximum possible speedup obtainable through parallelizing routines.

nism) calls around subroutines of interest; e.g., to test the amount of time taken in residual and Jacobian evaluation. Such methods are usually low-resolution, but provide easy access to the "big-picture." GNU gprof provides high resolution timing of every function call across the duration of a program run. It performs the measurement by inserting timing code at the beginning and end of every function. As a result, gprof (and tools like it) incur additional overhead from all the extra timing code; the effect of this overhead depends on both the number of function calls and the size of called functions. Fog[28] details how to obtain high resolution timing more precisely, inserting timing code only where the programmer desires. Intel's VTune package provides another alternative; it obtains timing results by randomly querying the program state and estimating the time distribution across different functions. This method involves much less overhead, but it also leads to inaccuracies.

Timing-based profiling provides information on what program components are the most expensive. But it provides little information on why. Event-based profiling fills this gap. Modern CPUs have a number of performance counters (also called event counters) on the chip. These counters are incremented whenever certain events occur; e.g., cache misses, instructions retired, branch misprediction, overloading performance-enhancing (hardware) buffers, etc. During the discussion on the memory hierarchy and the inner workings of the CPU, notes will be provided on relevant event counters. These counters can be accessed directly in code [28], but the process is not straightforward. OProfile and VTune both provide the ability to accumulate CPU events across entire program runs. For efficiency, both packages sample randomly. The random sampling does not hinder accuracy in a meaningful way because only functions incurring large numbers of events will be interesting. Programmers wishing for more direct control will need to access the performance counters individually, in code.

$<sup>^{10}</sup>$ Event counter names change from CPU to CPU; the counters discussed here will be taken from the Intel Core 2 only.

# Chapter 2

# The Discontinuous Galerkin Finite Element Method

In this work, governing equations that take the general form:

$$\frac{\partial}{\partial t}\mathbf{u} + \nabla \cdot \mathbf{F}^{inv}(\mathbf{u}) - \nabla \cdot \mathbf{F}^{vis}(\mathbf{u}, \nabla \mathbf{u}) = 0,$$

such as Euler and Navier-Stokes, will be considered. In the above,  $\mathbf{u}$  denotes the conservative state vector (of size  $N_{sr}$ ); e.g.,  $\mathbf{u} = [\rho, \rho v_i, \rho E]^T \in \mathcal{R}^{N_{sr}}$ , which is  $[\rho, \rho v_0, \rho v_1, \rho E]^T$  in 2D. Here,  $v_i$  denotes the components of velocity and E denotes the total specific internal energy. The inviscid and viscous fluxes are denoted by  $\mathbf{F}^{inv}, \mathbf{F}^{vis} \in \mathcal{R}^{N_{dim} \times N_{sr}}$ , respectively. In the following, only viscous fluxes of the form  $\mathbf{F}^{vis} = \mathcal{A}(\mathbf{u})\nabla\mathbf{u}$  will be considered. Note that  $\mathcal{A}(\mathbf{u})$  is a rank-4 tensor and  $\nabla\mathbf{u}$  is rank-2. The form of  $\mathcal{A}$  is given in Section A.3. For clarity, the governing equations written with indicial notation are given below:

$$\partial_t u_k + \partial_{x_i} F_{i,k} - \partial_{x_i} (\mathcal{A}_{i,j,k,l} \partial_{x_j} u_l) = 0$$

where k, l range over the state rank  $(N_{sr})$  and i, j range over the spatial dimension  $(N_{dim})$ .  $F_{i,k}$  denotes the  $N_{sr}$  components of  $\mathbf{F}^{inv}$  in each coordinate direction.  $F_{i,k}^{vis} = \mathcal{A}_{i,j,k,l}\partial_{x_j}u_l$  denotes the components of  $\mathbf{F}^{vis}$ . See Appendix A for a complete specification of the (continuous) inviscid and viscous fluxes for the Navier-Stokes equations.

# 2.1 DG Spatial Discretization

The following discussion will only outline the DG spatial discretization. Since this work is concerned with implementation issues and not theoretical developments, results are stated generally without proof. Further discussion of the DG spatial discretization used here can be found in [24, 23, 49, 57].

Begin by triangulating the domain  $\Omega \subset \mathcal{R}^{N_{dim}}$  into non-overlapping elements  $\kappa$ . Let  $T^h \equiv \{\kappa_e\}$  and  $N_{elem} = |T^h|$ . The DG method seeks a discontinuous approximation  $u^h$  (to the exact solution u) such that  $u^h|_{\kappa_e}$  belongs to the function space  $\mathcal{V}^{h,p}(\kappa_e)$ . The solution and test space is given by:

$$\mathcal{V}^{h,p} \equiv \{ v_k \in [L^2(\Omega)]^{N_{sr}} | v_k |_{\kappa} \circ f_{\kappa} \in [P^p(\kappa_{ref})]^{N_{sr}}, \ \forall \kappa \in T^h \},$$

where  $P^p$  denotes polynomials with degree at most p, and  $f_{\kappa}$  denotes the mapping from the reference element  $(\kappa_{ref})$  to physical space for the element  $\kappa$ .

Multiplying by the vector of test functions,  $v_k^h$ , and integrating, the semidiscrete,<sup>1</sup> weak form of the governing equations follows:

$$\sum_{\mathbf{k} \in Th} \int_{\kappa} v_k^h \frac{\partial u_k^h}{\partial t} + R^{h,inv}(\mathbf{u}^h, \mathbf{v}^h) + R^{h,vis}(\mathbf{u}^h, \mathbf{v}^h) = 0, \ \forall v_k^h \in \mathcal{V}^{h,p},$$

(2.1)

where  $R^{h,inv}$ ,  $R^{h,vis}$  denote the inviscid and viscous residuals, respectively; and  $\mathbf{u}^h$ ,  $\mathbf{v}^h$  indicate vector-valued arguments,  $u_k^h$ ,  $v_k^h$ . If source terms are present, then  $R^{h,sou}$  will also be present in Equation 2.1. Note that if the (strong) source terms contain first or higher derivatives, care is required to maintain the dual consistency of the discretization [57].

<sup>&</sup>lt;sup>1</sup>The time discretization will be handled later.

## 2.1.1 Inviscid Component

The inviscid discretization arises from multiplying  $\partial_{x_i} F_{i,k}$  by the test functions  $v_k$  and integrating by parts to obtain the weak form:

$$R_{\kappa}^{h,inv}(\mathbf{u},\mathbf{v}) \equiv -\int_{\kappa} \partial_{x_i} v_k^{\dagger} F_{i,k}(\mathbf{u}) + \int_{\partial \kappa} v_k \hat{F}_k(\mathbf{u}^+, \mathbf{u}^-, \mathbf{n}^+), \tag{2.2}$$

where the +,- superscripts refer to element  $\kappa$  and its appropriate neighbor, respectively; note that  $v_k$  always refers to test functions for  $\kappa$  evaluated over  $\kappa$ . The h superscripts  $(u_k^h, v_k^h)$  have been dropped for brevity. The full inviscid residual is formed by summing over the elements:  $R^{h,inv} = \sum_{\kappa \in T^h} R_{\kappa}^{h,inv}$ .  $\hat{F}_k$  is a numerical flux function (e.g., the Roe Flux). If some faces of  $\partial \kappa$  lie on  $\partial \Omega$ , then  $\hat{F}_k$  is modified to enforce boundary conditions weakly.<sup>2</sup>

## 2.1.2 Viscous Component

The viscous discretization is derived similarly. Here, the viscous, numerical fluxes are from the second method of Bassi and Rebay (BR2) [13, 14, 12]. In this method, the strong form of the governing equations is split into a system of first order equations:

$$\partial_t u_k + \partial_{x_i} F_{i,k}^{inv} - \partial_{x_i} \left( \mathcal{A}_{i,j,k,l} z_{j,l} \right) = 0 \tag{2.3}$$

$$z_{i,k} - \partial_{x_i} u_k = 0. (2.4)$$

Obtain the weak forms by integrating by parts after multiplying the first equation by  $v_k \in \mathcal{V}^{h,p}$  and the second by  $w_{i,k} \in \mathcal{V}^{h,p}$ :

$$R_{\kappa}^{h,inv} + \int_{\kappa} \partial_{x_i} v_k \mathcal{A}_{i,j,k,l} z_{j,l} - \int_{\partial \kappa} v_k^{\dagger} \widehat{\mathcal{A}_{i,j,k,l}} z_{j,l} n_i^{\dagger} = 0$$

(2.5)

$$\int_{a} w_{i,k} z_{i,k} + \int_{a} u_{k} \partial_{x_{i}} w_{i,k} - \int_{\partial a} w_{i,k}^{+} \hat{u}_{k} n_{i}^{+} = 0, \qquad (2.6)$$

<sup>&</sup>lt;sup>2</sup>A boundary state,  $u_k^b$ , is established based on outgoing characteristics and boundary data; the boundary flux is determined from these quantities.

where  $\hat{z}, \hat{u}$  are viscous numerical fluxes (i.e., traces). Setting  $w_{j,l} = \partial_{x_i} v_k \mathcal{A}_{i,j,k,l}$ , substituting for  $\int_{\kappa} \partial_{x_i} v_k \mathcal{A}_{i,j,k,l} z_{j,l}$ , and integrating by parts again<sup>3</sup> yields the viscous residual contribution,

$$R_{\kappa}^{h,vis} \equiv \int_{\kappa} \partial_{x_i} v_k \mathcal{A}_{i,j,k,l} \partial_{x_j} u_l - \int_{\partial \kappa} \partial_{x_i} v_k \mathcal{A}_{i,j,k,l} \left( u_k^+ - \{u_k\} \right) n_j^+ - \int_{\partial \kappa} v_k^+ \widehat{\mathcal{A}_{i,j,k,l}} z_{j,l} n_i^+ \quad (2.7)$$

Let  $\{u\} = \frac{1}{2}(u^+ + u^-)$  denote the average operator, and let  $[\![u]\!] = (u^+ - u^-)$  denote the jump operator.<sup>4</sup> The BR2 method involves setting  $\widehat{\mathcal{A}_{i,j,k,l}}z_{j,l} = \{\mathcal{A}_{i,j,k,l}\partial_{x_j}u_l\}$  $\eta\{\mathcal{A}_{i,j,k,l}r_{i,k}(\llbracket\mathbf{u}\rrbracket\mathbf{n}^+)\}$  and  $\hat{u}_k=\{u_k\}$ . The parameter  $\eta>3$  is required for stability on simplicial elements [24]; in this work, a more conservative  $\eta = 6$  is used, as in [56]. Boundary conditions are set by modifying these traces appropriately [24, 23, 49]. The lifting operator  $r_{i,k} \in \mathcal{V}^{h,p}$  is given by:

$$\int_{\kappa^{+}} \tau_{i,k}^{+} r_{i,k}^{f,+} + \int_{\kappa^{-}} \tau_{i,k}^{-} r_{i,k}^{f,-} = \int_{\sigma_{f}} \{\tau_{i,k}\} \llbracket u_{k} \rrbracket n_{i}^{+}

\int_{\kappa} \tau_{i,k} r_{i,k}^{f,B} = \int_{\sigma_{f}^{B}} \tau_{i,k}^{+} \left( u_{k}^{+} - u_{k}^{B} \right) n_{i}^{+}$$

for interior and boundary faces, respectively. The B superscript denotes a quantity over a face that lies on  $\partial\Omega$ ;  $\tau_{i,k} \in \mathcal{V}^{h,p}$ .

#### 2.2 Temporal Discretization

As in the method of lines, Equation 2.1 transforms to system of ODEs. First, a basis  $\{\mathbf{v}_m\}$ for  $\mathcal{V}^{h,p}$  is needed. Now  $\forall \mathbf{u} \in \mathcal{V}^{h,p}$ ,  $\exists U_m \in \mathcal{R}^{N_{bf}}$  such that  $\mathbf{u} = U_m \mathbf{v}_m$ . Considering all elements and states simultaneously, the ODE for Equation 2.1 is:

$$M\frac{d\mathbf{U}}{dt} + R(\mathbf{U}) = 0, (2.8)$$

where  $\mathbf{U} \in \mathcal{R}^{N_{elem}N_{sr}N_{bf}}$  is the vector of unknowns over all elements;  $R_m(\mathbf{U}) = R^{h,inv}(\mathbf{u}, \mathbf{v}_m) + R^{h,inv}(\mathbf{u}, \mathbf{v}_m)$  $R^{h,vis}(\mathbf{u},\mathbf{v}_m)$  involves evaluating the previous  $R^{h,inv},R^{h,vis}$  expressions for all  $N_{bf}$  basis functions; and  $M_{m,n}=\int_{\Omega}\mathbf{v}_{m}\mathbf{v}_{n}$  is the elemental mass matrix. The matrix M is of size

<sup>&</sup>lt;sup>3</sup>Integrating  $\int_{\kappa} \partial_{x_i} w_{i,k} u_k = \int_{\partial \kappa} w_{i,k} u_k^+ n_i - \int_{\kappa} w_{i,k} \partial_{x_i} u_k$  completes the terms required for dual consistency.

<sup>4</sup>The average and jump are taken component-wise if u is a vector.

$N_{elem}N_{sr}N_{bf} \times N_{elem}N_{sr}N_{bf}$ , composed of all  $N_{elem}$  elemental matrices  $M_{m,n}$ . Note that the mass matrix is block diagonal with at worst  $N_{elem}$  blocks of size  $N_{sr}N_{bf} \times N_{sr}N_{bf}$ . With the optimal ordering of unknowns,  $R_{e,k,n}$  (see Section 3.1.1), it improves to  $N_{elem}N_{sr}$  blocks of size  $N_{bf} \times N_{bf}$ ; furthermore, the same polynomial basis is usually taken for every state.

From here, any standard ODE solver can be applied. For unsteady problems, this work uses an IRK4 variant [69]. For steady problems, time-accuracy is not important. An implicit method is important to allow for very large time steps; Backwards Euler suffices:

$$\frac{1}{\Delta t}M\left(\mathbf{U}^{m+1} - \mathbf{U}^m\right) + R(\mathbf{U}^{m+1}) = 0. \tag{2.9}$$

The time step is controlled by calculating  $\Delta t = \min_e \Delta t_e$  where  $\Delta t_e = CFL^m \frac{h_e}{\lambda_e}$ .  $h_e, \lambda_e$  are per-element measures of grid size and maximum characteristic speed, respectively. The initial value of CFL is set low for robustness (i.e., so that non-physical transients arising from poor initial conditions do not derail the solver). After each successful iteration, CFL is increased by a constant factor to accelerate convergence.

Each time-step requires the solution of a nonlinear problem; this is handled with Newton's Method. Each Newton iteration requires the solution of a linear system. Here, a block-ILU preconditioned, restarted GMRES method with block MDF reordering was chosen as the linear solver.<sup>5</sup> The GMRES implementation used in this work follows the original algorithm [61, 62].

For unsteady problems, Newton iteration continues until the norm of the temporal residual is sufficiently reduced. Since time-accuracy is not important for steady problems, only one Newton step is taken by each nonlinear solve. The following update scheme results after linearizing about  $\mathbf{U}^m$ :

$$\mathbf{U}^{m+1} = \mathbf{U}^m - \left(\frac{1}{\Delta t}M + \frac{\partial R}{\partial \mathbf{U}}\Big|_{\mathbf{U}^m}\right)^{-1} R(\mathbf{U}^m). \tag{2.10}$$

Note that this scheme reduces to Newton's Method as  $\Delta t \to \infty$ . The nonlinear solver halts when  $||R(\mathbf{U}^m)|| \leq TOL$ .

<sup>&</sup>lt;sup>5</sup>ILU and MDF stand for Incomplete-LU (factorization) and Minimum Discarded Fill, respectively. See [18, 60] for details.

# Chapter 3

# Computational Costs of the DG Method

# 3.1 Residual and Jacobian Evaluation

The discussion here will be limited to interior faces. Boundary conditions generally make up a negligible portion of the overall residual and Jacobian assembly time, since they are applied on a set of measure 1 less than the problem domain.

In the following discussion,  $\phi$  refers to the basis functions for the polynomial interpolation space. In this thesis, a Lagrange basis (on uniformly distributed points) was used. For p-th order polynomial interpolant on a simplex,  $N_{bf} = p + 1$  in 1D,  $N_{bf} = (p+1)(p+2)/2$  in 2D, and  $N_{bf} = (p+1)(p+2)(p+3)/6$  in 3D.

## 3.1.1 Inviscid Discretization

#### Galerkin Residual

The basic kernel for the residual over elements due to an inviscid operator involves numerically integrating  $\int_K F_{i,k}(\mathbf{u}) \partial_{x_i} \phi$ . At a single quadrature point (in reference coordinates), computing the residual involves evaluating:

$$R_{g,k,n} = w_g \partial_{x_i} \phi_{g,n} F_{i,k}(\mathbf{U}_n \phi_{g,n}), \tag{3.1}$$

where n ranges over the basis functions, and g ranges over the number of quadrature points,  $N_{quad}$ . Note that the boldfaced terms indicate vectors of size  $N_{sr}$ . An index is avoided since the flux function requires the full solution (state) vectors as arguments. In particular, at a single quad point,  $\mathbf{U}_n \phi_n$  is a  $N_{sr}$ -vector, the product of a  $N_{sr} \times N_{bf}$  matrix and a  $N_{bf}$  vector. The weights  $w_g$  include the (reference) quadrature weights as well as a factor arising from the determinant of the geometric Jacobian, |J|, due to the change from physical to reference coordinates. Then the complete residual is computed by  $R_{k,n} = \sum_g R_{g,k,n}$ . The physical gradient of  $\phi_n$  uses the inverse (geometric) Jacobian,  $J_{i,j}^{-1}$ :  $\partial_{x_i}\phi_n = J_{i,j}^{-1}\partial_j\phi_n$ , where  $\partial_j\phi_n$  are the derivatives of  $\phi_n$  in reference coordinates.

At a quad point, the total cost is  $N_{dim}^3 + 4N_{dim}^2N_{bf} + 2N_{sr}N_{bf} + 2N_{dim}N_{sr}N_{bf} + C(F)$ . Note that these costs assume that the basis functions are precalculated. For now, the cost analysis will focus on the number of floating point operations, which also serve as an upper bound for memory costs. Memory access costs, which are generally more important, will be considered in Section 5.1, after covering the memory hierarchy (Chapter 4) and the CPU (Chapter C). The cost components of Equation 3.1 are:

- (Geometric) Jacobian:  $2N_{dim}^2 N_{bf}$  to compute  $J_{i,j} = X_{i,n} \partial_j \phi_n$ , where  $X_{i,n}$  are the global coordinates of the element's nodes;  $N_{dim}^3$  to compute  $J^{-1}$  and det(J).

- $\partial_{x_i}\phi_n$ :  $2N_{dim}^2N_{bf}$ .

- $u_k = U_{k,n}\phi_n$ :  $2N_{sr}N_{bf}$ .

- C(F): cost of computing the (continuous) convective flux; little can be done to improve the efficiency of such evaluations, so we will consider them as a "black box." In general, C(F) should only "scale" with physical dimension (linearly) and state rank (at most quadratically).

- Combining into  $R_{k,n}$ :  $2N_{dim}N_{sr}N_{bf}$ .

The previous expressions would be valid for isoparametric geometry representations; in other cases,  $N_{bf}$  should be replaced by  $N_{bf-geom}$ . Additionally, the convention used is that y = y + Ax, with  $A \in \mathbb{R}^{m \times n}$ , costs 2mn and  $z = z + xy^T$ , with  $x \in \mathbb{R}^{m \times 1}$  and  $y \in \mathbb{R}^{n \times 1}$ , also costs 2mn.

Asymptotic notation was avoided in this analysis. For many problems of interest, many of the cost-components of Equation 3.1 are important. First, the limit of large spatial dimension is not interesting:  $N_{dim}$  is 1, 2, or 3. Additionally, the limit of large  $N_{sr}$  may be interesting (e.g., for multi-species simulations), but for a given problem, it is a fixed quantity. The limit of large  $N_{bf}$  is more interesting, but many simulations are not run with  $P_5$  or  $P_{10}$ . At lower polynomial orders (e.g.,  $P_0$  or  $P_1$ ), the relative weights of the residual costs changes substantially. Thus,  $N_{dim}$ ,  $N_{sr}$ , and other numeric factors are given to provide intuition for the relative importance of various factors in the residual computation.

Although the element residual  $R_{k,n}$  is commonly thought of as a vector, its components are indexed over two indexes, the state rank and the number of basis functions. It is then convenient to think of  $R_{k,n}$  as a matrix of size  $N_{sr} \times N_{bf}$ . Additionally,  $R_{k,n}$  should be stored in (k,n) order; i.e., so that the index over basis functions is the faster-changing index. In this way, elemental mass matrices will be block-diagonal  $(N_{sr}$  blocks of size  $N_{bf} \times N_{bf}$  each), instead of a "scattered"  $(N_{sr}N_{bf}) \times (N_{sr}N_{bf})$  matrix with no useful structure. Inverting the block-diagonal mass matrix is a factor of  $N_{sr}^2$  cheaper.

In general, the index ordering in Equation 3.1 (and in the following discussion) is meaningful. It is suggested that DG implementations store residuals, temporary quantities, etc. in the layout implied by the left-to-right ordering of the indexes. So  $A_{i,j,k}$  could be declared  $A[N_i][N_j][N_k]$  in  $C.^1$  In the current discussion, we are summing  $R_{g,k,n}$  over g, so we can simply accumulate the added results in a single location.

#### Jump Residual

The basic kernel for faces (i.e., jump terms) involves numerically integrating  $\int_{\partial K} \hat{F}_k(\mathbf{u}) \phi$ :

$$R_{g,k,n}^{L} = w_g \hat{F}_{g,k} \left( \mathbf{n}_g^L, \mathbf{U}_n^L \phi_{g,n}^L, \mathbf{U}_n^R \phi_{g,n}^R \right) \phi_{g,n}^L$$

(3.2)

The superscripts L and R denote the element on the left and right of a face, respectively. The "sidedness" of an element is dependent on the convention for normal vectors. In the following discussion,  $n_i^L$  denotes the normal from the left to the right element;  $n_i^R = -n_i^L$

<sup>&</sup>lt;sup>1</sup>The use of multidimensional arrays in C is *only* recommended if the arrays are statically sized.

denotes the opposite, right to left normal.

A matching term to Equation 3.2,  $R_{g,k,n}^R$  is present for the contribution to the right-side elemental residual.  $\hat{F}_k$  refers to the numerical flux (e.g., the Roe Flux) in the face-normal direction.

At a quad point, the total cost of Equation 3.2 is  $2N_{dim}^2N_{bfL} + 3N_{dim}^2 + 4N_{sr}N_{bfL} + C(\hat{F})$ .  $N_{bfL}$  denotes the number of basis functions interpolating the left element; recall that an isoparametric geometry representation is assumed. For the right face, the cost expression is identical unless the right element's interpolation order is different; i.e., replace  $N_{bfL}$  by  $N_{bfR}$ . Here, evaluating the numerical fluxes,  $\hat{F}$ , will be more expensive than the continuous fluxes. At least for the Roe Flux, the cost "scaling" is linear in spatial dimension and at most quadratic in state rank, as with the continuous flux. But the constants involved are much larger. Lastly, the first two terms of the cost expression arise from computing the normal vector. Technically only the basis functions in dimension  $N_{dim} - 1$  are needed for the normals; i.e., the face-normals of a 2D element can be found using 1D basis functions.

#### Galerkin Jacobian

The basic kernel for the Jacobian of Equation (3.1) at a single quadrature point is:

$$\partial_{U_{a,m}} R_{g,k,n} = -w_g \partial_{x_i} \phi_n \partial_{u_a} F_{i,k}(\mathbf{U}_n \phi_{g,n}) \phi_{g,m}$$

(3.3)

Note that  $\partial_{U_{a,m}} R_{g,k,n}$  should be interpreted as  $A_{g,a,m,k,n}$ .

The cost per quadrature point is  $2N_{dim}N_{sr}^2N_{bf}+2N_{dim}N_{sr}^2N_{bf}^2+C(\partial_u F)$ . Here, costs that are redundant (e.g., J,  $\partial_{x_i}\phi_n$ , etc.) with the residual evaluation have been skipped. The new terms arise from:

- $\partial_{u_a} F_{i,k} \phi_m$ :  $2N_{dim} N_{sr}^2 N_{bf}$ .

- Combining into  $\partial_{U_{a,m}} R_{k,n}$ :  $2N_{dim} N_{sr}^2 N_{bf}^2$ .

- $C(\partial_u F)$ : the cost of computing the state derivatives of the continuous flux.

Unsurprisingly, the Jacobian computation is substantially more expensive, with the (generally) dominant term  $N_{dim}N_{sr}^2N_{bf}^2$  being a factor of  $N_{sr}N_{bf}$  larger than the largest residual

term,  $N_{dim}N_{sr}N_{bf}$ .

#### Jump Jacobian

The basic kernel for the Jacobian of Equation (3.2) at a single quadrature point, with respect to the left states, is:

$$\partial_{U_{a,m}^L} R_{g,k,n}^L = w_g \phi_n^L \partial_{u_a^L} \hat{F}_k \left( \mathbf{n}_g^L, \mathbf{U^L}_n \phi_{g,n}^L, \mathbf{U^R}_n \phi_{g,n}^R \right)$$

(3.4)

Differentiating with respect to the right states:

$$\partial_{U_{a,m}^R} R_{g,k,n}^L = w_g \phi_n^L \partial_{u_a^R} \hat{F}_k \left( \mathbf{n}_g^L, \mathbf{U^L}_n \phi_{g,n}^L, \mathbf{U^R}_n \phi_{g,n}^R \right)$$

(3.5)

Again, analogous expressions exist for the derivatives of  $R_{q,k,n}^R$ .

At a single quadrature point, the cost of Equation 3.4 is  $2N_{sr}^2N_{bfL} + 2N_{sr}^2N_{bfL}^2 + C(\partial_{uL}\hat{F})$ ; and the cost of Equation 3.5 is  $2N_{sr}^2N_{bfR} + 2N_{sr}^2N_{bfL}N_{bfR} + C(\partial_{uR}\hat{F})$ . The costs of computing the left and right derivatives of  $R_{g,k,n}^R$  are analogous, but not simply doubled, since some terms are shared between the four Jacobians being computed.  $C(\partial_u\hat{F})$  denotes the cost of computing the state derivatives of the upwinding operator (e.g., the Roe Flux). Again, the Jacobian cost is a factor of  $N_{sr}N_{bf}$  more expensive than the corresponding jump residual terms; not to mention that there are twice times as many Jacobian terms.

## 3.1.2 Viscous Discretization

The analysis and derivation of the viscous discretization is more complex. The implementation is also more involved than that of the inviscid terms, and the computational cost is greater. But the process still boils down to a combination of tensor products and tensor contractions.

In the following discussion, only the BR2 viscous discretization is considered; furthermore, it is implemented in a dual consistent fashion. More specifically, the following discussion assumes that quantities computed over an element  $\kappa$  do not influence its neighbors.<sup>2</sup> The

<sup>&</sup>lt;sup>2</sup>Galerkin terms with such "non-local" influence arise when viscous or source terms (involving derivatives)

computation of the BR2 lifting operator is described first, followed by its use in the viscous jump residual and Jacobian terms.

#### The BR2 Lifting Operator

On any particular left face  $\sigma^{f,L}$ , finding the lifting operator involves solving the following equation for  $r^{f,L}$  and  $r^{f,R}$ :

$$\int_{\kappa^L} \tau_i^L r_i^{f,L} + \int_{\kappa^R} \tau_i^R r_i^{f,R} = \int_{\sigma_f} \{\tau_i\} \llbracket u \rrbracket n_i^L$$

where  $\tau^L \in \mathcal{V}_h^p(\kappa^L)$  and  $\tau^R \in \mathcal{V}_h^p(\kappa^R)$ . The f superscripts are now dropped since the discussion only considers one face at a time. Due to the choice of basis,  $\tau_i^L r_i^L$  has support only in  $\kappa^L$ . Now consider the lift-corrected gradient of the conservative state vector,  $\partial_{x_i} u_k$ . Choosing  $\tau^L = \phi_m^L$  and  $\tau^R = \phi_m^R$  (pick the same  $\phi$  for all spatial dimensions i), and expanding  $r_{k,i} = D_{i,k,n} \phi_n$  in the polynomial basis,

$$\int_{\kappa^{L}} D_{i,k,n}^{L} \phi_{n}^{L} \phi_{m}^{L} = \int_{\sigma_{f}} \frac{1}{2} \phi_{m}^{L} \llbracket u_{k} \rrbracket n_{j}^{L}$$

(3.6)

$$\int_{\kappa^R} D_{i,k,n}^R \phi_n^R \phi_m^R = \int_{\sigma_f} \frac{1}{2} \phi_m^R [\![u_k]\!] n_j^L$$

(3.7)

These are evaluated using numerical quadrature. Since  $D^L$  and  $D^R$  are constant, the left-hand sides of the equations above can be rewritten in terms of the mass matrix  $M_{mn} = \int_{\kappa} \phi_n \phi_m$ :

$$M_{m,n}^{L}D_{i,k,n}^{L} = \frac{1}{2}w_{g}\phi_{g,m}^{L}\left(u_{g,k}^{L} - u_{g,k}^{R}\right)n_{g,i}^{L}$$

(3.8)

$$M_{m,n}^R D_{i,k,n}^R = \frac{1}{2} w_g \phi_{g,m}^R \left( u_{g,k}^L - u_{g,k}^R \right) n_{g,k}^L \tag{3.9}$$

where  $u_{g,k}^L = U_{k,o}^L \phi_{g,o}^L$  (similarly for  $u^R$ ), as before. These equations are easily solved for  $D^L$  and  $D^R$  by inverting the mass matrix.

When calculating the Jacobian, finding the derivatives of  $D^L$  and  $D^R$  (e.g.,  $\partial_{U_{a,m}^L} D_{i,k,n}^L$ ).

are discretized in an asymptotically dual consistent manner.

is straightforward (and requires little additional calculation) since the equations defining the lifting operator are linear. The derivatives of  $r_{i,k}^L$  are then  $\partial_{U_{a,m}^L} r_{i,k}^L = \partial_{U_{a,m}^L} D_{i,k,n}^L \phi_n$ . Note additionally that the derivatives of  $D^L$  and  $D^R$  are independent of state; e.g.,  $\partial_{U_{a,m}^L} D_{i,k,n}^L = M_{m,n}^{-1,L} \left(\frac{1}{2} w_g \phi_{g,m}^L \phi_{g,n}^L n_{g,i}^L\right) \equiv \delta_L D_{i,m,n}^L$  and  $\partial_{U_{a,m}^R} D_{i,k,n}^L = -M_{m,n}^{-1,L} \left(\frac{1}{2} w_g \phi_{g,m}^L \phi_{g,n}^R n_{g,i}^L\right) \equiv \delta_R D_{i,m,n}^L$  only need indices i, m, n.

When the derivatives are not needed, evaluating the auxiliary variable coefficients  $D^L$  costs  $2N_{dim}N_{sr}N_{bfL}N_{quad}+2N_{dim}N_{sr}N_{bfL}^2$ . If derivatives are needed,  $\delta_L D^L$  costs  $2N_{bfL}^2N_{quad}+2N_{dim}N_{bfL}^2N_{quad}$  and  $\delta_R D^L$  costs an additional  $2N_{dim}N_{bfL}N_{bfR}N_{quad}$ . With the derivatives computed,  $D^L$  can be computed as before or as  $D^Li, k, n = \delta_L D_{i,m,n}^L U_{k,m}^L - \delta_R D_{i,m,n}^L U_{k,m}^R$  at a cost of  $4N_{dim}N_{sr}N_{bfL}(N_{bfL}+N_{bfR})$ . Note that geometry costs were not counted since these are duplicate with computations that are already necessary for the jump residual or Jacobian. Additionally, it is assumed that the PLU-factorizations of the mass matrices have been precomputed.

# Residual Terms

The Galerkin residual term (Equation 3.10) for viscous operators is standard for finite element methods. However the jump contributions from the left and right faces have their numerical traces determined by the BR2 method. The left face term is given below (Equation 3.11); the right-face term is symmetric.

$$R_{g,k,n} = w_g \partial_{x_i} \phi_n \mathcal{A}_{i,j,k,l} \partial_{x_j} u_l \tag{3.10}$$

$$R_{g,k,n}^{L} = -w_{g} \partial_{x_{i}} \phi_{n}^{L} \mathcal{A}_{i,j,k,l}^{L} \llbracket u_{l} \rrbracket n_{j}^{L}$$

$$-w_{g} \phi_{n}^{L} \left( \mathcal{A}_{i,j,k,l}^{L} z_{j,l}^{u,L} + \mathcal{A}_{i,j,k,l}^{R} z_{j,l}^{u,R} \right) n_{i}^{L}$$

(3.11)

where  $\partial_{x_j} u_l = U_{k,n} \partial_{x_i} \phi_n$  is the spatial derivative of the states  $u_l$  in physical coordinates, and  $z_{j,l}^{u,L} = \partial_{x_j} u_l^L - \eta r_{j,l}^L$  denotes the lift-corrected state derivative.

For the Galerkin residual terms, the additional cost per quad point (over the inviscid residual) is  $2N_{dim}N_{sr}N_{bf}+2N_{dim}^2N_{sr}^2+C(\mathcal{A})$ .  $C(\mathcal{A})$  denotes the cost of computing the viscous  $\mathcal{A}$  matrix, which is generally substantially more expensive than computing the inviscid flux. Note that an additional cost of  $2N_{dim}N_{sr}N_{bf}$  was not incurred because the viscous flux can

be added to the inviscid flux directly.

For the jump residual terms on the left face, the additional cost per quad point is  $2N_{dim}^3 + 2N_{dim}^2(N_{bfL} + N_{bfR}) + 2N_{dim}^2(N_{bfL} + N_{bfR}) + 6N_{dim}N_{sr}(N_{bfL} + N_{bfR}) + 4N_{dim}^2N_{sr}^2 + 4N_{dim}N_{sr}^2 + C(D^L, D^R) + C(\mathcal{A}^L, \mathcal{A}^R)$ , where  $C(D^L, D^R)$  denotes the cost of evaluating the lifting coefficients and  $C(\mathcal{A}^L, \mathcal{A}^R)$  denotes the cost of computing  $\mathcal{A}$  on the left and right faces. As before, the right face costs are similar, but not necessarily double due to some quantities being shared.

### **Jacobian Terms**

Again, handling the derivative  $\partial_{u_a} \mathcal{A}_{i,j,k,l}$  is nontrivial. The dominant cost components (i.e.,  $N_{sr}^2 N_{bf}^2$ ) grow in the same way as the inviscid Jacobian terms, which should be clear from the expressions. For completeness, the Galerkin component,  $\partial_{U_{a,m}} R_{g,k,n}$ , and the (+ face) jump components,  $\partial_{U_{a,m}^L} R_{g,k,n}^L$  and  $\partial_{U_{a,m}^R} R_{g,k,n}^L$ , are given below:

$$\partial_{U_{a,m}} R_{g,k,n} = w_g \partial_{x_i} \phi_n \left( \partial_{u_a} \mathcal{A}_{i,j,k,l} \partial_j u_l \phi_m + \mathcal{A}_{i,j,k,a} \partial_j \phi_m \right)$$

(3.12)

$$\partial_{U_{a,m}^L} R_{g,k,n}^L = -w_g \partial_{x_i} \phi_n \left( \partial_{u_a^L} \mathcal{A}_{i,j,k,l}^L \llbracket u_l \rrbracket n_j^L \phi_m + \mathcal{A}_{i,j,k,a}^L n_j^L \phi_m^L \right)$$

(3.13)

$$+w_g\phi_n\left(\mathcal{A}_{i,j,k,a}^Lz_{j,m}^{\phi,L}+\partial_{u_a^L}\mathcal{A}_{i,j,k,l}^Lz_{j,l}^{u,L}\phi_m^L-\eta\mathcal{A}_{i,j,k,a}^R\partial_{U_m^L}r_j^R\right)n_i^L$$

$$\partial_{U_{a,m}^{R}} R_{g,k,n}^{L} = w_{g} \partial_{x_{i}} \phi_{n}^{L} \mathcal{A}_{i,j,k,a}^{L} n_{j}^{L} \phi_{m}^{R}$$

$$-w_{g} \phi_{n}^{L} \left( \mathcal{A}_{i,j,k,a}^{R} z_{j,m}^{\phi,R} + \partial_{u_{a}^{R}} \mathcal{A}_{i,j,k,l}^{R} z_{j,l}^{u,R} \phi_{m}^{R} - \eta \mathcal{A}_{i,j,k,a}^{L} \partial_{U_{m}^{R}} r_{j}^{L} \right) n_{i}^{L}$$

$$(3.14)$$

where  $z_{j,m}^{\phi,L} = \partial_{x_j}\phi_m - \eta \partial_{U_m^L} r_j^L$  is the lifted basis derivative.

The additional cost per quad point for the Galerkin Jacobian terms is  $2N_{dim}^2N_{sr}^3 + N_{dim}N_{sr}^2 + 2N_{dim}^2N_{sr}^2N_{bf} + C(\partial_u\mathcal{A})$ , where  $C(\partial_u\mathcal{A})$  denotes the cost of evaluating the state derivatives of  $\mathcal{A}$ .

For  $\partial_{U_{a,m}^L}R_{g,k,n}^L$ , the additional cost per quad point is  $4N_{dim}^2N_{sr}^3+2N_{dim}N_{sr}^2+2N_{dim}N_{sr}^2N_{bfL}+2N_{sr}^2N_{bfL}^2+2N_{dim}N_{bfL}(N_{bfL}+N_{bfR})+4N_{dim}N_{sr}^2N_{bfL}+C(\delta_LD^L,\delta_LD^R)+C(\partial_u\mathcal{A}^L,\partial_u\mathcal{A}^R).$  Evaluating  $\partial_{U_{a,m}^R}R_{g,k,n}^L$  incurs an additional  $2N_{dim}^2N_{sr}^3+2N_{dim}N_{sr}^2N_{bfL}+2N_{sr}^2N_{bfL}N_{bfR}+2N_{dim}N_{bfL}(N_{bfL}+N_{bfR})+N_{dim}N_{sr}^2+4N_{dim}N_{sr}^2N_{bfR}+C(\delta_RD^L,\delta_RD^R).$

# 3.1.3 Quadrature

So far, costs have only been given per quadrature point. Here, the number of quadrature points needed is discussed. The desired quadrature accuracy depends on the polynomial interpolation order for the solution  $(p_{sol})$  and for the geometry  $(p_{geom})$ . A particular quadrature formula is characterized by the highest polynomial order that it can integrate exactly. In this thesis, the requested order is  $2(p_{sol}+1)+p_{geom}-1$  for elements; for faces,  $2(p_{sol}+2)+p_{geom}-1$  is used.

In 1D, Gaussian Quadrature is common; it requires (p+1)/2 points to integrate a polynomial of order p exactly. Extensive listings of 2D and 3D quadrature rules have been published [65, 67]. For simplexes, the number of quadrature points scales as  $O((\frac{p+1}{2})^{N_{dim}})$  to integrate a polynomial of order p exactly. Exact counts are usually less than the previous, simple formula, which is an upper bound based on tensor product rules (of Gaussian Quadrature) for rectangular elements. The exponentiation by  $N_{dim}$  is important here. The number of quadrature points needed for element interiors is much larger than the number of quadrature points needed for element faces, since faces are one dimension "smaller" than interiors. This is especially true for high polynomial orders. However, the expense per quadrature point on faces is higher due to the need to calculate contributions from and to the left and right elements. Additionally, there are more faces than elements.

# 3.2 Nonlinear Solve

Each nonlinear (Newton) iteration is composed of two principal parts:

- Assembly of the residual and Jacobian

- Solution of a linear system

The cost of the nonlinear solve is dominated by these two components. Outside of the assembly and the linear solve, the nonlinear iteration only requires  $O(N_{elem}N_{sr}N_{bf})$  flops through a series of BLAS-1 operations. Further estimation of the nonlinear solver cost is not really possible, since the number of nonlinear iterations is strongly dependent on the

degree of nonlinearity in the problem, mesh resolution, etc. Improving the efficiency of the nonlinear solver is a balance between improving robustness and accelerating convergence. For example, using a very conservative line search algorithm, increasing CFL slowly, using highly-accurate linear solves, etc. will lead to more robustness but the number of nonlinear iterations could increase greatly. However, the heuristics used to control the nonlinear solve are not the focus of this thesis; see [59, 63] for overviews of popular globalization techniques and further references.

# 3.3 Linear Solve via ILU Preconditioned, Restarted GMRES

In most problems using implicit time-stepping, the linear solve will compose a major portion of the total compute time. In steady problems, the linear solve can make up more than 90% of the total cost. This section will focus on the cost of ILU preconditioned, restarted GMRES. However, the discussion here holds for most iterative linear solvers (especially other Krylov methods), since these methods are composed of a combination of sparse matrix-vector products and dense vector-vector products. In the following discussion,  $N_b = N_{sr}N_{bf}$  denotes the block-size. DG methods have the advantage of sparsity patterns that are naturally block-sparse, whereas many other discretizations (e.g., CG) often resort to reorderings to create block structure.

As with the residual and Jacobian assembly, the cost per "inner" GMRES iteration (i.e., building the Krylov basis) can be calculated exactly. However, as with the nonlinear solve, estimating the exact linear solver cost is difficult, since it is almost impossible to know the number of inner iterations a priori. If GMRES is restarted, it is similarly impossible to know the number of restarts (i.e., "outer" iterations) exactly. For (restarted) GMRES, the difficulty of the linear problem is dependent on the conditioning (more accurately, eigenvalue distribution) of the preconditioned Jacobian matrix.

ILU preconditioning is implemented in-place [18]. In-place ILU overwrites the Jacobian matrix with its ILU factorization; more commonly, the ILU factorization is stored separately,

doubling the memory requirement. The penalty is greater computational cost,<sup>3</sup> since Ax cannot be computed directly; instead  $\tilde{L}\tilde{U}x$  must be computed.

The dominant costs of the MDF reordering are: 1) computing  $C_{i,j} = ||A_{i,p,i,q}^{-1}A_{i,p,j,q}||_F$ , where i, j range over  $N_{elem}$  and p, q range over  $N_b$ ; and 2) searching over the list of unordered elements for the maximum weight element and updating the weights of that element's unordered neighbors. The former costs  $\frac{2}{3}N_b^3 + 2(N_f + 1)N_b^3$  flops per element; note that lower order terms  $(O(N_b^2))$  have been dropped.  $N_f$  denotes the number of faces of an element; i.e., the number of neighbors. For searching and updating weights, an asymptotically optimal  $O(N_{elem} \log N_{elem})$  comparisons is obtainable with an elementary min-heap data structure; 4 see [16] for example. Methods exist for reducing the big-O constant within the binary heap; alternative heap designs with better weight-update performance also exist.

[18] gives flop count estimates for  $AM^{-1}x$  kernel in "bare" ILU-GMRES without reordering and ILU-GMRES with MDF reordering.  $AM^{-1}x$  is computed once in each inner iteration. Again, note that the ILU factorization is computed in-place. Here, M denotes the preconditioning matrix, leading to the decomposition A = M + N. It is more efficient to compute  $AM^{-1}x = x + NM^{-1}x$ . The asymptotic cost of computing the ILU factorization is similar to that of the MDF reordering:  $\frac{2}{3}N_b^3 + 2(N_f + 1)N_b^3$  flops per element. In practice, MDF is slightly more expensive due to the  $O(N_{elem} \log N_{elem})$  term. Computing  $M^{-1}x$  costs  $2(N_f + 1)N_b^2$  flops per element. Lastly, [18] estimates  $\frac{2}{3}(N_f + 4)(N_f - 1)N_b^2$  flops per element for computing Nx when no reordering is used.<sup>5</sup> Experimentally, this estimate is too high. With MDF reordering, <sup>6</sup> the estimate is reduced to  $\frac{2}{3}(N_f + 4)(N_f - 2)N_b^2$ , which is reasonably accurate in practice[18].

The last major cost-component of GMRES is the Arnoldi iteration, excluding the cost of  $AM^{-1}x$ . This cost is difficult to predict unless the number of inner iterations is fixed. Let  $N_{inner}$  be the number of inner iterations and denote a restarted GMRES method by

<sup>&</sup>lt;sup>3</sup>More flops are required, but the amount of memory accessed is roughly equal. Thus in practice, the in-place method is often faster than its full-storage counterpart.

<sup>&</sup>lt;sup>4</sup>Brute force searches can require  $O(N_{elem}^2)$  comparisons or worse, which can be a substantial cost with as few as  $10^4$  elements.

<sup>&</sup>lt;sup>5</sup>Only an estimate is possible here, since the cost of Nx depends on the number of nonzero blocks in N, which is case-dependent.

<sup>&</sup>lt;sup>6</sup>[18] produces an argument for "Line" reordering which reorders elements along lines of strong convective coupling. But for convection-dominated flows, MDF produces similar results.

GMRES( $N_{inner}$ ). [61] recommends the Modified Gram-Schmidt (MGS) process for orthogonalizing the Krylov basis, which will be discussed here. Alternatives are covered in Section 5.2. The *i*-th step of MGS costs  $4N_bN_{elem}(i+1)$  flops. With  $N_{inner}$  steps, the total cost amounts to  $4N_bN_{elem}\left(\frac{N_{inner}(N_{inner}+1)}{2}+N_{inner}\right)$  flops. Lastly, the amortized cost of solving the least-squares problem arising in GMRES is very minor if the Hessenberg matrix generated by the Arnoldi process is QR-factored incrementally [62].

The previous estimate for Arnoldi can be somewhat misleading. First, after each inner iteration, GMRES produces the current residual norm should an update were taken immediately. Thus, the last outer iteration may not have  $N_{inner}$  inner iterations; particularly if only 1 outer iteration occurs, the previous MGS estimate could be very high. Additionally, there are many reasons not to have a constant  $N_{inner}$ . If a problem could be solved with 10 (outer) iterations of GMRES(100) or 1 iteration of GMRES(1000), the former would be preferred since the cost of its Arnoldi process is cheaper by a factor of 100. However, cases arise where GMRES(100) stagnates and potentially fails to converge. [9] proposes a simple, effective strategy for varying  $N_{inner}$  in a user-specified range.

Restarted GMRES implementations also need to deal with stagnation. When GMRES( $N_{inner}$ ) stagnates, convergence can slow substantially or even become impossible. A number of heuristics exist to detect stagnation and recover from it. Recovery entails increasing  $N_{inner}$  to enrich the Krylov space. [31] discusses a method for dealing with stagnation in restarted GMRES.

Finally, as demonstrated in Section 3.5, optimized BLAS implementations are often poor choices for computing the block-wise matrix-vector products required by GMRES. For many relevant block sizes, compiler optimized versions of a basic matrix-vector product routine outperform the BLAS. Benchmarking is required to determine when BLAS is a better choice for performance.

# 3.4 Example Problems

This section exhibits one unsteady and three steady example problems. In all cases, the nonlinear solver terminated when the nonlinear residual norm fell below  $10^{-12}$ . Except where

noted, the GMRES solver used at most 200 Krylov vectors per restart. The GMRES stopping criterion is the "fixed" criterion described in Appendix D, with  $K = 10^{-3}$ . This choice is discussed later in this section. All cases used ILU preconditioning with MDF reordering. In steady cases, the nonlinear solver starts with CFL = 1 and increases by a factor of 5 with each successful iteration. Note that all steady cases were initialized to converged solutions with interpolation order one less than the reported order; i.e., a  $P_3$  solution starts from a converged  $P_2$  solution. The component-costs are summarized in Tables 3.5, 3.6, and 3.7.

• Case 1: steady, inviscid flow over a Gaussian bump in 2D. The mesh is isotropic and structured, composed of triangular elements generated from a conformal mapping of a rectangle.

| Geometry                     | Guassian Bump |

|------------------------------|---------------|

| Mach Number                  | 0.20          |

| Angle of Attack              | 0.0           |

| Spatial Dimension            | 2             |

| Equation                     | Euler         |

| Solution Interpolation Order | 3             |

| Geometry Interpolation Order | 5             |

| Block Size                   | 40            |

| nElement                     | 20480         |

| DOF                          | 819200        |

| Jacobian Size                | 0.73GB        |

Table 3.1: Case 1 description

- Case 2: steady, viscous flow over a flat plate in 3D. The mesh is extruded from a 2D, anisotropic, structured mesh with boundary layer packing and element packing toward the leading edge singularity. The 2D mesh has 936 elements. The extruded mesh has 3 layers of elements in the z direction, with each extruded prism being divided into 3 tetrahedrons.

- Case 3: steady, viscous (Reynolds-Averaged) flow over an RAE 2822 airfoil. The RANS Equations are closed with the Spalart-Allmaras turbulence model. The mesh is generated from repeated iterations of a drag adjoint-based mesh adaptation strategy;

| Geometry                     | Flat Plate    |

|------------------------------|---------------|

| Reynolds Number              | $10^{6}$      |

| Mach Number                  | 0.25          |

| Angle of Attack              | 0.0           |

| Spatial Dimension            | 3             |

| Equation                     | Navier-Stokes |

| Solution Interpolation Order | 2             |

| Geometry Interpolation Order | 1             |

| Block Size                   | 50            |

| nElement                     | 8424          |

| DOF                          | 421200        |

| Jacobian Size                | 0.63GB        |

Table 3.2: Case 2 description

anisotropy was detected via the local Mach number. The mesh is anisotropic and unstructured. The RANS source terms were evaluated in a dual consistent fashion, following [57].

| Geometry                     | RAE 2822            |

|------------------------------|---------------------|

| Reynolds Number              | $6.5 \times 10^{6}$ |

| Mach Number                  | 0.3                 |

| Angle of Attack              | 2.31                |