# Analysis of Terabit/Second-Class Inter-Chip Parallel

### **Optoelectronic Transceiver**

by

Nguyen Hoang Nguyen

B.Eng. (Hons), Electrical Engineering, National University of Singapore, 2009

### SUBMITTED TO THE DEPARTMENT OF MATERIALS SCIENCE AND ENGINEERING IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

### MASTER OF ENGINEERING IN MATERIALS SCIENCE AND ENGINEERING

### AT THE

### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

#### **SEPTEMBER 2010**

© 2010 Massachusetts Institute of Technology All rights reserved.

| · •                 | · · / /                                                                                                |

|---------------------|--------------------------------------------------------------------------------------------------------|

| Signature of Author | Department of Materials Science and Engineering<br>August 12, 2010                                     |

| Certified by        | Lionel C. Kimerling<br>Thomas Lord Professor of Materials Science and Engineering<br>Thesis Supervisor |

| Accepted by         | Christopher Schuh<br>Chair, Departmental Committee on Graduate Students                                |

1

| MA        | SSACHUSETTS INSTITUTE<br>OF TECHNOLOGY |  |

|-----------|----------------------------------------|--|

|           | NOV 1 9 2010                           |  |

| LIBRARIES |                                        |  |

ARCHIVES

## Analysis of Terabit/Second-Class Inter-Chip Parallel

### **Optoelectronic Transceiver**

by

Nguyen Hoang Nguyen

Submitted to the Department of Materials Science and Engineering on August 12, 2010 in Partial Fulfillment of the Requirements for the Degree of Master of Engineering in Materials Science and Engineering

### ABSTRACT

Electrical copper-based interconnect has been suffering from fundamental physical loss mechanism and its current infrastructure will not be able to meet the increasing demand for data rates due to reaching the limit of the transmission bandwidth-distance product. Optical interconnect has been known as the candidate for taking over the obsolete electrical counterpart owing to the capability of transmitting data at high rates with low loss and the feasibility for parallel integration. Optoelectronic transceiver is one of the essential elements in optical interconnect system. This thesis scrutinizes a complete set of constituent technologies developed for a novel inter-chip parallel optoelectronic (OE) transceiver (known as Terabus transceiver) which is able to communicate data at the speed in the range of Terabit/second.

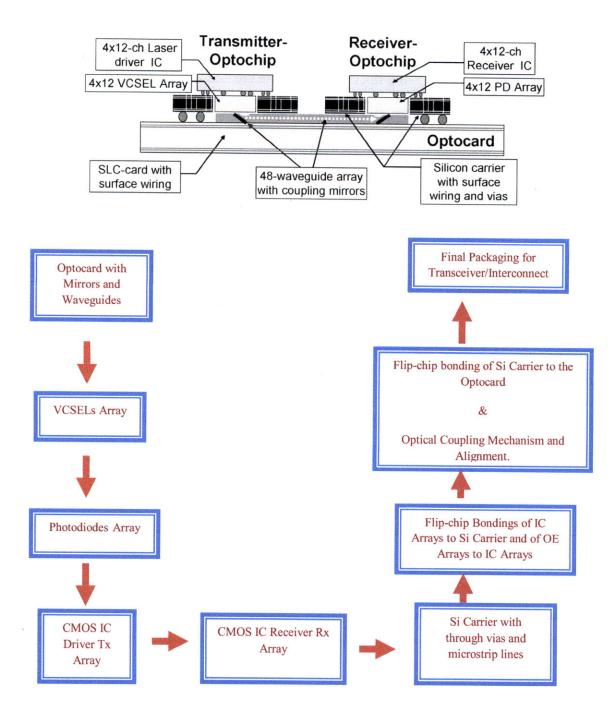

A novel packaging hierarchy and a creative design for an optical coupling mechanism devised to bring high-level integration and high-speed performance to a final package have been analyzed: Two 4x12 arrays (each < 9 mm<sup>2</sup>) of CMOS transmitter and receiver ICs have been flip-chip bonded to a silicon carrier interposer of  $1.2 \text{-cm}^2$  size. Other two 4x12 arrays of OE devices (VCSELs and photodiodes) with comparable size are then flip-chip bonded to the corresponding CMOS arrays attached to the silicon carrier, forming the Optochip assembly. The Optochip is in interface with an Optocard by the flip-chip bonding process between the silicon carrier and an organic card patterned with 48 integrated waveguides at density of 16-channel/mm and total length of 30 cm. The 985-nm operating wavelength of the lasers allows a simple optical design with emission and illumination through arrays of relay lenses directly etched into the backside of the OE III-V substrate. A novel design of  $45^\circ$ -tilted and Au-coated mirrors fabricated in 125-µm-pitch acrylate waveguides is to perpendicularly couple the light in and out of the core of these Optocard waveguides. Per-channel performance of up to 20 Gb/s for transmitter and of up to 14 Gb/s for receiver have been realized.

Lastly, the thesis has analyzed the market opportunity of the transceiver by reviewing the market situation, identifying contemporary competing technologies, assessing the market prospect and predicting the cost.

Thesis Supervisor: Lionel C. Kimerling Title: Thomas Lord Professor of Materials Science and Engineering

# Acknowledgements

I would like to take this opportunity to express my heartfelt gratefulness to whom by one way or another have provided me with support in the process to complete this thesis. Without the support, definitely, it would be pretty much impossible for me to complete this thesis with success.

First of all, I would like to thank Professor Lionel Kimerling for offering me a project to fulfill my M.Eng degree at MIT. I wanted a project which has both materials science and electrical/optical engineering in nature then I got. In both of the two meetings we went through at MIT, I was always given with patient guidance as well as valuable suggestions and recommendation for research from Prof Kimerling. I would like to thank MIT Materials Processing Center for offering me access to the CTR and Industry Consortium website from which I can approach the most up-to-date technology information in the field which is undeniably integral to the thesis.

I would like to thank Professor Chua Soo Jin from the National University of Singapore (NUS) for a timely discussion we had near the start of my final MIT M.Eng semester in Singapore, which helped me narrowing down the thesis topic and also for his enthusiastic guidance during the course of my thesis.

I would like to appreciate Mr Nguyen Xuan Sang, SMA direct PhD 2008, for his support in selecting and introducing references and for the discussions through which I have gained understanding and knowledge in nanomaterial processing.

I would like to thank Ms Lisa, Prof Kimerling's assistant for helping out dealing with logistic issues and delivering the thesis hardcopies to the Academic Office.

I would like to appreciate the support and understanding from the HR personnel manager at Schlumberger Singapore where I have been doing the internship since the last 2 month of thesis completion.

I would like to thank my Singapore-MIT Alliance classmates, AMM&NS 2009 intake, for the time we have experienced throughout the SMA 09-10 journey. Without the classmates, my SMA Dual Masters "challenge" would not be as memorable as it is.

I would like to appreciate the encouragement and understanding from my girlfriend, Le Khanh. She has encouraged me to get through hard and depressing moments of the thesis. For me, this thesis is indeed unforgettable.

Last but not least, I would like to thank my family for the enduring encouragement and indispensable support without which I would not be able to achieve what I have accomplished by now.

# **Table of Contents**

| PART | I |

|------|---|

|------|---|

| Background of Silicon Microphotonics and Optoelectronic Transceiver Fundamenta | als12 |

|--------------------------------------------------------------------------------|-------|

| CHAPTER 1: The coming Regime of Silicon microphotonics                         | 13    |

| 1. Why Silicon Microphotonics?                                                 | 13    |

| 2. Roadmap for Silicon Microphotonics                                          | 15    |

| CHAPTER 2: Optoelectronic Transceiver Fundamenta                               | 17    |

| 1. Overview                                                                    | 17    |

| 2. Parts of Optoelectronic Transceiver                                         | 18    |

| a. Optical Laser Source Technology                                             | 18    |

| Light Emitting Diode (LED)                                                     | 18    |

| Edge-Emitting Laser (EEL)                                                      | 19    |

| Vertical Cavity Surface Emitting Laser (VCSEL)                                 | 19    |

| Key Competitive Laser Source Technology                                        | 20    |

| Key Power Module Technology for Laser Source                                   | 21    |

| Recent Research Breakthrough in Ge Laser Source                                | 22    |

| b. Optical Detector Technology                                                 | 22    |

| Key Technology to Improve Responsiveness                                       | 23    |

| c. Modulator Technology                                                        | 24    |

| d. Packaging Technology                                                        | 25    |

| e. Monolithic Integration Consideration                                        | 25    |

| PART II                                                                        |       |

| Terabit/Second-Class Inter-chip Parallel Optoelectronic Transceiver            | 27    |

| CHAPTER 1: Overview of the Terabus Transceiver                                 | 28    |

| 1. Background                                                                  | 28    |

| 2. Introduction of the Transceiver                                             | 29    |

# b. CMOS Receiver Circuits......35 **CHAPTER 3: Silicon Carrier** Optochip Assembly, Optocard 2. Optochip Assembly, Optocard......42 a. Optochip Assembly......42 b. Optocard......44 3. Optical Coupling and Alignment, Packag g......45 a. Optical Couple and Alignment......45 i. Optical Coupling Mechanism......45 b. Packaging......48 i. Optochip-to-Optocard Packaging......48 ii. Thermal-Control Consideration for the Package......49 1. Measurement of Silicon Carrier Electrical Signal Path......51 a. Measurement of Differential Microstrip Lines on Silicon Carrier......52

CHAPTER 2: 2-D Arrays of VCSELs and Photodiodes

# b. Measurement of Differential Silicon Carrier Through Via......53

| 2. Measurement of Optocard Waveguide for Loss and Dispersion55         |

|------------------------------------------------------------------------|

| a. Optocard Waveguide Loss Measurements55                              |

| b. Optocard Wveguide Dispersion Measurement55                          |

| 3. Optochip Characterization                                           |

| Crosstalk Consideration                                                |

| Power Consumption budgeting consideration43                            |

| PART III                                                               |

| Market Opportunity                                                     |

| CHAPTER 1: Market Analysis62                                           |

| 1. The Supercomputing Market62                                         |

| 2. The need for standardization of inter-chip transceiver market       |

| 3. Competing Technologies66                                            |

| a. Electrical Copper-based Interconnect Technologies                   |

| b. Optical Interconnect Technologies                                   |

| The Intel Light Peak68                                                 |

| The Japan Project69                                                    |

| 4. Thoughts on the market prospect of optical interconnect/transceiver |

| CHAPTER 2: Production Cost Model73                                     |

| 1. The Process-Based Cost Model73                                      |

| 2. Case Study: The Cost Model of the Optoelectronic Transceiver76      |

| a. Attributes and Parameters76                                         |

| b. Process Flow for the Terabus Transceiver78                          |

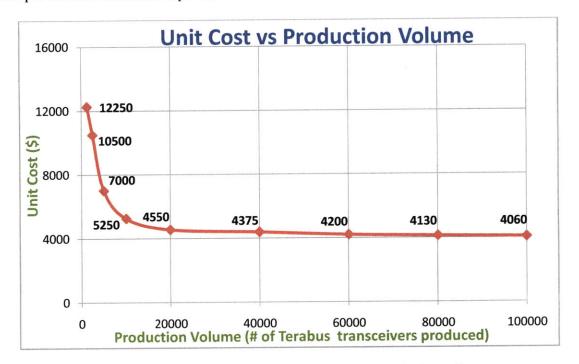

| c. The Economies of Scale81                                            |

| PART IV                                                                |

| Conclusion and Recommendation for Future Work                          |

| References                                                             |

| Appendix                                                               |

# List of Figures

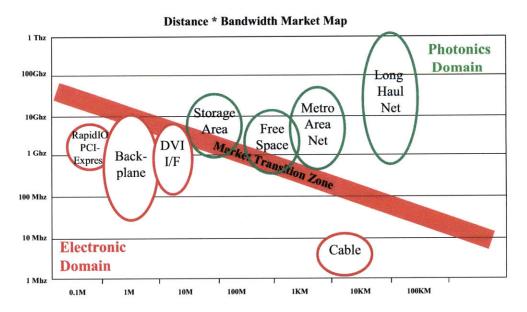

| Figure 1: Electronics-photonics domain transition border [1]                                                  | 13         |

|---------------------------------------------------------------------------------------------------------------|------------|

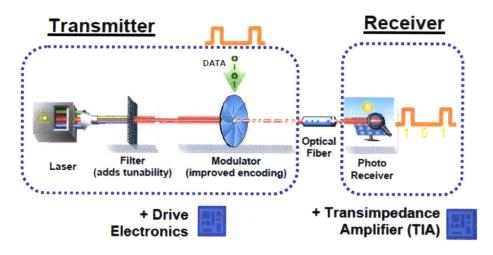

| Figure 2: Elements of an optical link [courtesy Intel]                                                        | 15         |

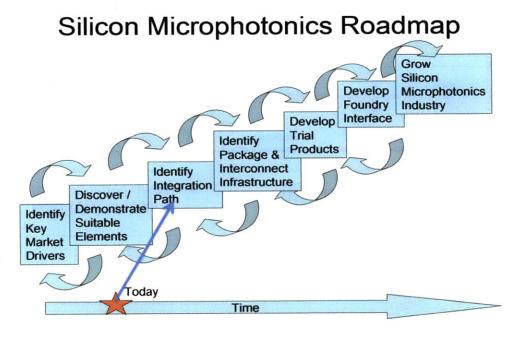

| Figure 3: Roadmap for Silicon microphotonics [Courtesy MIT CRT] [1]                                           | 16         |

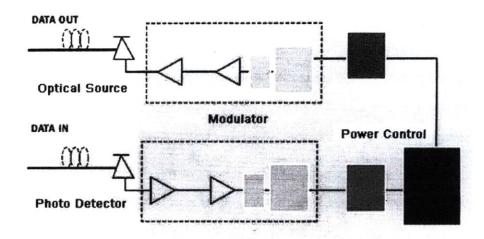

| Figure 4: Functional Block Diagram of a typical optoelectronic transceiver                                    | 17         |

| Figure 5: Structure of an edge-emitting laser [2]                                                             | 19         |

| Figure 6: Structure of a vertical cavity surface emitting laser [3]                                           | 20         |

| Figure 7: Laser built from germanium for optical communication, courtesy: MIT EMAT g<br>[4]                   | roup<br>22 |

| Figure 8: P-I-N photo detector                                                                                | 22         |

| Figure 9: Structure for laterally-coupled germanium diodes [1]                                                | 23         |

| Figure 10: Optoelectronic modulator [courtesy MIT]                                                            | 24         |

| Figure 11: Packaging for optoelectronic transceiver                                                           | 25         |

| Figure 12: Monolithic LED on Si substrate with CMOS technology [6]                                            | 26         |

| Figure 13: Schematic of Terabit/s package composed of Optocard with waveguides and transceiver Optochips [10] | 29         |

| Figure 14: Structure of Terabus/second transceiver [14]                                                       |            |

| Figure 15: Schematic (left) and photograph (right) of bottom-emitting VCSEL [15]                              | 32         |

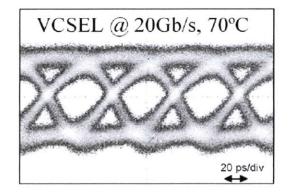

| Figure 16: Enlarged eye diagrams of 6-µm VCSELs at 10 and 20 Gb/s (70°C) [15]                                 | 33         |

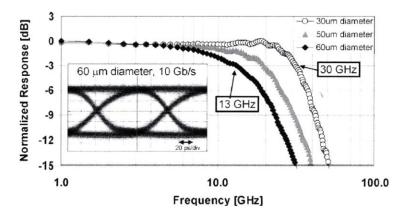

| Figure 17: Frequency response of photodiodes with different diameters at 1.5-V reverse bia [10]               | ıs<br>33   |

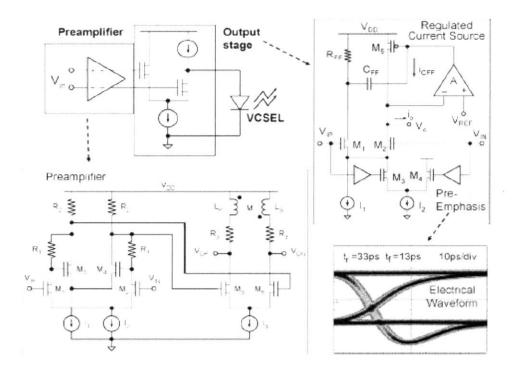

| Figure 18: Functional block diagram of a single-channel VCSEL driver IC [16]                                  | 35         |

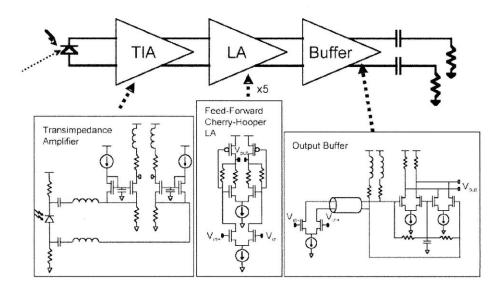

| Figure 19: Functional block diagram of a single-channel receiver IC [18]                                      | 36         |

| Figure 20: Top view of silicon carrier layout (left); structure of the transceiver (right)                    | 37         |

| Figure 21: Silicon carrier process flow [14]                                                                  | 39         |

| Figure 22: Cu collar for through via                                                                          | 41         |

| Figure 23: Top view of 3 wiring levels on top of silicon through vias: signal, power and ground [14]41                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 24: Solder micro bumps and array [20]43                                                                                                                                                                         |

| Figure 25: Flip-chip assembly procedure (left). Bottom view of Optochip: OE in cavity and UBM pads (right)44                                                                                                           |

| Figure 26: Layout of the Optocard (left) and cross-section with 62.5-µm-pitch integrated waveguides (right) (IBM)                                                                                                      |

| Figure 27: Optical coupling mechanism between OEs and the Optocard waveguides45                                                                                                                                        |

| Figure 28: Schematic diagram of mirror fabrication at the end of 48 Optocard waveguides (left). Photograph of fabricated sample illuminated by a white light (right)                                                   |

| Figure 29: Coupling efficiency of VCSEL (up) and Photodiode (down) to waveguide vs.<br>horizontal offset (x-y) [14]                                                                                                    |

| Figure 30: Entire Optochip-on-Optocard assembly (left) and bottom view of silicon carrier (right)                                                                                                                      |

| Figure 31: 3mm heat pipe in contact with test chip [23]49                                                                                                                                                              |

| Figure 32 a : Temperature distribution in test chip with no cooling (left) and result for temperature distribution in the entire package (right) [23]                                                                  |

| Figure 32 b: Local temperature distribution in the VCSEL chip with no cooling (left) and with heat pipe cooling (right) [23]                                                                                           |

| Figure 33: Electrical path (in red) on silicon carrier: strip line on the Optocard and silicon carrier through via, microstrip line [14]                                                                               |

| Figure 34: Layer dimensions of differential microstrip transmission lines on the silicon carrier (left) and its eye diagram (right) for 7-mm length at 20 GHz, PRBS 7-1 data pattern [14]52                            |

| Figure 35: S-Parameters ( $S_{11}$ and $S_{12}$ ) of the 7-mm silicon carrier microstrip line                                                                                                                          |

| Figure 36: Measurement setup for silicon carrier through via transmission [14]53                                                                                                                                       |

| Figure 37: Transmissions of the through via + the 7-mm Optocard line (red) and of the reference Optocard line only (blue)                                                                                              |

| Figure 38: Impulse response measurement of a 1-m multi-mode polymer optical waveguide at input and output (left). Evolution of Images of the single-mode fiber launch into the waveguide due to dispersion (left) [26] |

| Figure 39: Summary of pulse broadening results for 8, 17, 100 and 255-cm waveguides for both nm and 990 nm [25]                                                                                                        |

| Figure 40: Eye diagram at 20 Gb/s from a Terabus transmitter. The drive circuit included a circuit to compensate for the fall time of the VCSEL emission [26]                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 41: Received eye diagram of a transmitter Optochip to receiver link at 14 Gb/s (left). 10 Gb/s received eye diagram using low power variant circuits and reduced supply voltages [26]58      |

| Figure 42: Power consumption per bit rate for a single-channel 10-Gb/s error-free multi-mode fiber link. Inset: received eye of the 48 mW (22 mW for transmitter and 26 mW for receiver) link. [10] |

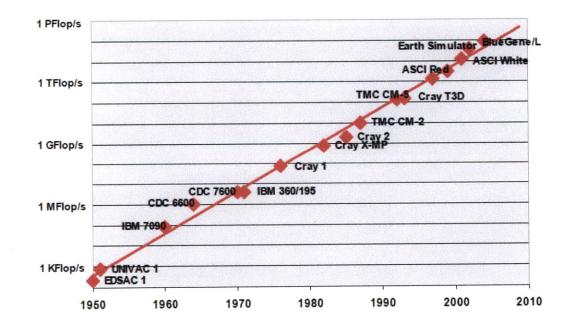

| Figure 43: Performance of the fastes computer systems for the last six decades compared to Moore's law [28]                                                                                         |

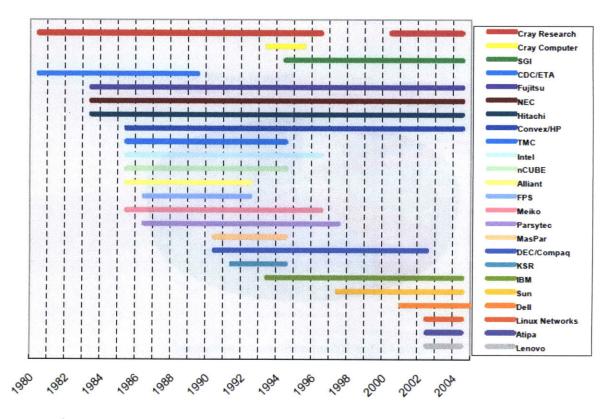

| Figure 44: Main active players in high performance computing market throughout time [28]63                                                                                                          |

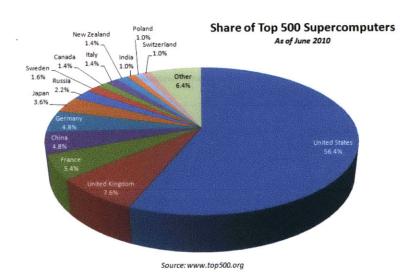

| Figure 45: Top 500 supercomputers by nations                                                                                                                                                        |

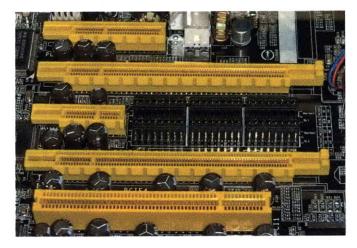

| Figure 46: PCI Express slots (from top to bottom: x4, x16, x1 and x16)67                                                                                                                            |

| Figure 47: Light Peak technology (Intel)68                                                                                                                                                          |

| Figure 48: Configuration of CPU-memory optical interconnection [35]70                                                                                                                               |

| Figure 49: Transceiver fabrication process flow                                                                                                                                                     |

| Figure 50: Unit cost vs. annual production volume for the 3 scenarios given in the report [37]81                                                                                                    |

| Figure 51: The transceiver cost sensitivity to annual Production Volume                                                                                                                             |

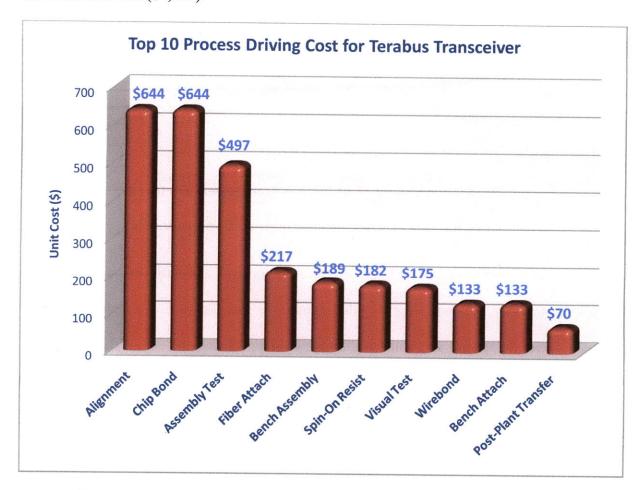

| Figure 52: Top 10 process driving cost for the Terabus transceiver at 30,000 units annually84                                                                                                       |

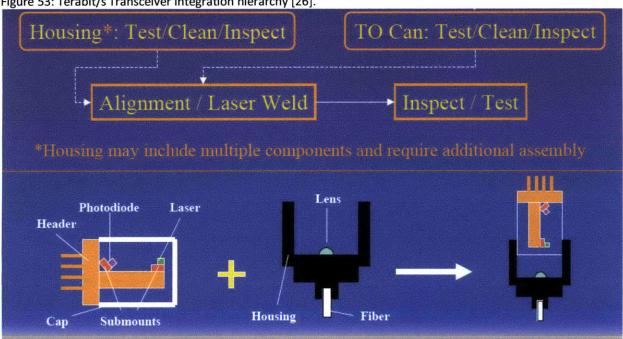

| Figure 53: Terabit/s Transceiver Integration hierarchy [26]86                                                                                                                                       |

| Figure 53: Terabit/s Transceiver Integration hierarchy [26]93                                                                                                                                       |

| Figure 55: Transceiver Optical Sub-Assembly Process Flow [37]93                                                                                                                                     |

|                                                                                                                                                                                                     |

# List of Tables

| Table 1: Comparison between two common EEL and VCSEL optical laser sources      | 18 |

|---------------------------------------------------------------------------------|----|

| Table 2: Standardization state for LAN optical connection (2008)                | 65 |

| Table 3: Front-end process modules in a transmitter PBCM                        | 74 |

| Table 4: Cleaving and back-end process modules in a transmitter PBCM            | 75 |

| Table 5: Process sub-model inputs (required for each process step, e.g., MOCVD) | 75 |

| Table 6: Financial Parameters Used for the Cost Model                           | 77 |

| Table 7: Operational Parameters Used for the Cost Model                         | 77 |

| Table 8: Terabus Transceiver Top Ten Cost Drivers                               | 85 |

# **BACKGROUND OF SILICON MICROPHOTONICS**

And

# **OPTOELECTRONIC TRANSCEIVER FUNDAMENTALS**

### CHAPTER 1: The coming regime of Silicon microphotonics

#### 1. Why silicon microphotonics?

Electronic communication links are degraded by fundamental physical loss mechanisms including dielectric losses and skin effect losses which are all functions of distance and bandwidth. In addition, near/far end crosstalk and noise aggravate these loss mechanisms. There is the maximum communication rate subjected to losses and noise levels for a given signal strength as stated by Shannon's law. As the demand for ever increasing bandwidth communication proceeds, the communication capability of electronic-based link gets asymptotic to this fundamental limit. Switching to alternative communicating platform is the essential trend. For many industries, photonics platform is the choice to replace electronics platform when the limitation is reached. Figure 1 shows the transition border (the red zone) between these two platforms based up on bandwidth-distance product criteria.

Figure 13: Electronics-photonics domain transition border [1].

As shown clearly, the Long Haul Net has been already in the photonics domain because of the high requirement for transmitting high bandwidth over long distance while conventional Cable is still in the electronics domain due to low requirement for high bandwidth transmission. Each of the above industries is increasing demand for bandwidth throughout the time, ultimately exhausting the practical capabilities of electronic-based solutions.

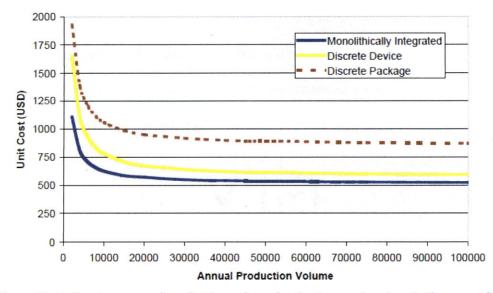

Challenge for the transition to take place is that: the advent of an optical replacement of suitable cost during this transition zone will enable earlier conversion, that's why the cost of photonic links will likely need to be competitive with the cost of copper-based counterparts. To make use of the economic advantage of silicon, the key to reduce cost will be monolithic integration, just as VLSI electronics. Integrated silicon microphotonics which is fabricated monolithically by CMOS process will achieve a complete set of microphotonics devices using available process in existing CMOS fabs.

The key drivers for silicon microphotonics which are bandwidth cost and bandwidth volume will increase pressure for monolithic photonics integration as well as for low cost and small form factor optical packaging and high-speed interconnect. Key discussed silicon microphotonics technologies which implement optical communication links would be receivers, transmitters, filters, packaging, source and integration strategies. The goal is that sources, detectors, and modulators, as well as passive components such as waveguides and filters are made from silicon or new photonics compatible materials, e.g. Ge, BaTiO3 etc, and acceptable dielectrics and metals.

Figure 2 schematically describes very well elements of silicon microphotonics technology required for a typical optical link.

14

Figure 14: Elements of an optical link [courtesy Intel].

These element technologies are comprised of the followings:

- Integrated Receiver Technology

- Modulator Technology

- Photonic Source Strategy

- Filter Technology

- Packaging and Interconnect Technology

#### 2. Roadmap for Silicon Microphotonics

According to Communications Technology Roadmap (CRT) and MIT Industry Consortium [1], the roadmap for silicon microphotonics is suggested as in Figure 3. There are several prominent characteristics of the roadmap listed as follow, noting that inter-step iterations are expected and essential for technology development:

- Steps in the roadmap illustrate a nature but not necessary linear

- Each block sets the foundation and justification for the subsequent block

- Subsequently blocks may uncover technology that impacts previous blocks

Figure 15: Roadmap for Silicon microphotonics [Courtesy MIT CRT] [1].

The strategy is that different companies will focus on different steps (blocks) in the roadmap, but work together to benefit from the infrastructure of other steps, forming the Microphotonics Industry Consortium.

### **CHAPTER 2:** Optoelectronic Transceiver Fundamentals

#### 1. Overview

The basic function of an optoelectronic transceiver is to receive optical signal which is laser light, convert it into electronic digital signal in terms of binary sequences of 1s & 0s; and in the reverse order, convert binary sequences of 1s & 0s into corresponding optical pulses and transmit them. That's where the name transceiver comes from, reflecting the two-way function of the device which can be described as transmitter and receiver altogether.

Figure 16: Functional Block Diagram of a typical optoelectronic transceiver.

A typical optoelectronic transceiver consists of 4 major parts: optical laser source, photo detector, electronic modulator and power control unit. Photo detector receives optical variations and converts into voltage and/or current variations whereas, when control signal which is a sequence of binary numbers of 1 & 0 comes in, the modulator dictates the optical laser source to

send out corresponding optical signals. Short-range optoelectronic transceiver functions to receive and transmit optical signal in the range shorter than 1 meter.

#### 2. Parts of Optoelectronic Transceiver

#### a. Optical Laser Source Technology:

The key function of an optical laser source is to convert electronic signal into optical light. There the following 3 alternatives:

- Light Emitting Diode (LED)

- Edge-Emitting Laser (EEL)

- Vertical Cavity Surface Emitting Laser (VCSEL)

Table 1: Comparison between two common EEL and VCSEL optical laser sources<sup>1</sup>.

| Specification             | EEL          | VCSEL    |

|---------------------------|--------------|----------|

| Application               | Telecom      | Datacom  |

| Active Region Confinement | 300*400*0.07 | 3*3*0.07 |

| Modulation Frequency      | 20GHz        | 120GHz   |

| Threshold Current         | 20mA         | 0.5mA    |

| Output Power              | 45mW         | 0.17mW   |

| Power Efficiency          | 0.89A/W      | 11.76A/W |

Key consideration for optical source in short range transmission would be modulation frequency and transmission power which are both determined by the size of the active region. With small active layer, the loss should be small, threshold current is reduced and modulation frequency would be larger.

#### Light Emitting Diode (LED):

LED has a simple structure which contains no confinement layer. Light can come out at any position with a wide range of energy spectrum. As the result, power output for LED is high

<sup>&</sup>lt;sup>1</sup> Refer to Reference [5], Table 2.1, page 10.

and LED is suitable for display and lighting applications. Since the modulation frequency of LED is relatively low, LED is simply not a good candidate for optical source in high-speed transceivers.

#### Edge-Emitting Laser (EEL):

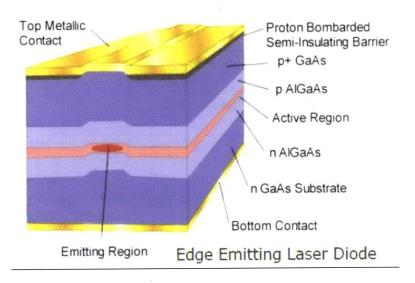

Figure 17: Structure of an edge-emitting laser [2].

In EEL, laser light is emitted laterally from the edge of the structure as shown as the emitting region in Figure 5. The active region is large enough to emit not too weak transmission power (~45mW, as can be seen in Table 1, but still much less than the transmission power of LED, which is  $\sim 0.1$ W) while can still achieve relatively high modulation frequency (~20 GHz, as can be seen in Table 1, but still smaller than the modulation frequency observed in VCSEL. With that balancing between emission power and modulation frequency, EEL is now the current technology for telecommunication.

#### Vertical Cavity Surface Emitting Laser (VCSEL):

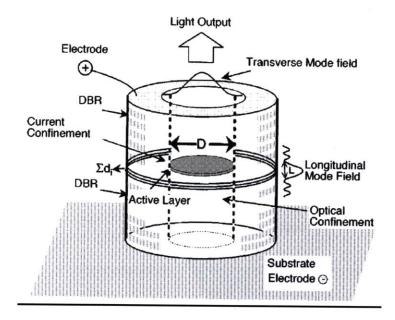

In this type of laser, the active layer is confined between two distributed Bragg reflectors (DBRs) which function as laser mirrors. Active area is further reduced by lateral oxidation

confinement, which significantly boosts up the modulation frequency capability (>100GHz) and reduces threshold current of the device down to several  $\mu A$ .

Figure 18: Structure of a vertical cavity surface emitting laser [3].

Having very high modulation frequency, VCSEL has been becoming the right choice for optoelectronic transceiver technology now and in future.

#### Key Competitive Laser Source Technology:

Two classes of technologies for active optoelectronics (laser sources) are emerging in research labs. Each involves semiconductor particles controllably made on the nanometer length scale: (1) Solution-processed devices using materials such as InAs, PbS, PbSe produce infrared lights and (2) Si-nanocrystal active devices which can be processed by existing CMOS-compatible technologies such as plasma-enhanced chemical vapor deposition (PECVD) to produce photoluminescence and electroluminescence [1].

#### Key Power Module Technology for Laser Source:

High-speed coherent sources have only been demonstrated through hybridization. In such cases, vertical-cavity surface-emitting laser or edge emitting laser are mounted on Si platform and coupled into appropriate waveguide [1]. Central photonic power source analogous to an electronic power supply may be cost effective, which could feed many ICs without a need for each chip to have its own laser. This benefit should be substantial in multi-link applications but may not be in single optical link. Direct modulation diode lasers (near source) will run at higher energy densities, and likely have lower reliability. Continuous wave lasers (far source) will need to be compatible with on-chip modulation, implying polarization, mode, loss and wavelength control.

#### **Recent Research Breakthrough in Germanium Laser Source:**

MIT researchers from the Electronic Materials Research Group (EMAT) led by Professor Lionel C. Kimerling have demonstrated the first laser built from germanium that can produce wavelengths of light for optical communication [4]. It is the first germanium laser to operate at room temperature. Different from other typical materials for lasers, germanium is easy to be integrated into existing processes of silicon chip manufacturing. Since the addition of germanium increase the speed of silicon chips (germanium has carrier mobilities larger than those of silicon), incorporating germanium into the manufacturing process is what almost all chip manufacturers have already done or started to do. This germanium-laser project which is carried out by the group has opened up the new level of monolithic integration for silicon microphotonics.

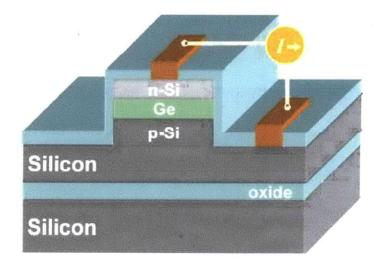

Figure 19: Laser built from germanium for optical communication, courtesy: MIT EMAT group [4].

#### b. Optical Detector Technology

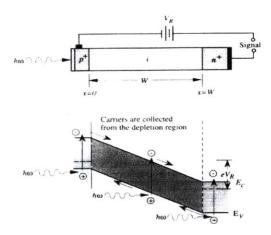

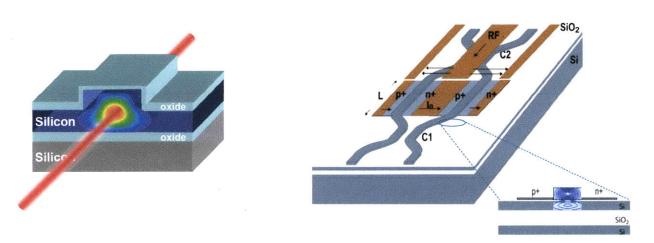

The key function of photo-detector for optical communication is to convert received optical signals into electrical forms, i.e. either voltage or current variations, for subsequent amplification and signal processing. The P-i-N photo detector consists of 3 layers: intrinsic layer 'i' sandwiched in between the 2 layer semiconductor n-type and p-type to enhance carrier generation by photon stimulation. Incident photons absorbed across the 'i' region would generate electron hole pairs (Figure 8). With voltage bias, these carriers are swept to the p and n regions and get recombined. As the result, the net current exists in the closed circuit. That's fundamentally how optical signal is converted into electrical current by a photo-detector.

Figure 20: P-I-N photo detector.

# Key Technology to Improve Responsiveness of Short-Range Detector by increasing Carrier Mobility:

With Ge on strained Si technique, modulation frequency up to 10GHz has been realized and especially the fabrication is compatible with existing CMOS infrastructure and supply chain. Research is uncovering a variety of way to utilize silicon platforms in receiver (detector) technology while hybridized mounted detectors have already been commercialized. Si itself is a rather poor absorber, i.e. its absorption depth is large, at most popular communication frequencies ( $\lambda$ >1µm). Short germanium absorption depths open the possibility of normal incidence coupled detector diodes, and the responsiveness of Ge extends into longer communication wavelengths especially under strain condition. Higher mobility of Ge allows even faster response.

Key question for silicon receivers is how to interface them to multi-mode fiber for normal incidence diode structures. Addition question for Ge is whether the intrinsic silicon lattice mismatch (4%) can be managed over noise [1].

Figure 21: Structure for laterally-coupled germanium diodes [1].

#### c. Modulator Technology

Figure 22: Optoelectronic modulator [courtesy MIT].

In silicon plasma modulator approach [1], silicon waveguide channel is flooded with carriers which alter the channel's refractive index. This variation of refractive index can be utilized in Mach-Zender interferometer structures to create light amplitude modulation. In other approach using electro-optic material such as barium titanate (BaTiO<sub>3</sub>) for modulators, the materials deposited on a buffer layer of magnesium oxide have shown some compatibility with standard silicon processing techniques. In other modulator research regarding quantum well structures in materials, Si nanocrystals on SiO<sub>2</sub>, for example, have shown electroluminescence and electro-absorption. Although still early in research, this is a possible solution for modulators as well as Si laser source.

Key remaining challenge for the current optoelectronic modulator technology is that Si plasma modulation and Si receiver are not likely compatible with each other. Plasma modulator probably needs Ge diode. Electro-optic materials like BaTiO<sub>3</sub> are still very much in question to be integrated with standard Si processing.

#### d. Packaging Technology

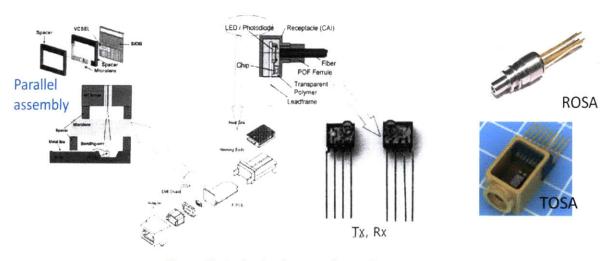

It is essential that all components discussed above would be able to be assembled into one highly small compact package. Package for discrete optical source or detector could be either ROSA or TOSA as shown in Figure 11. All of the components are finally put on same substrate and form the product. One of promising alternative technologies is parallel assembly which is ideal for VCSEL since light is emitted vertically [5].

Figure 23: Packaging for optoelectronic transceiver.

#### e. Monolithic Integration Consideration for Optoelectronic Transceiver

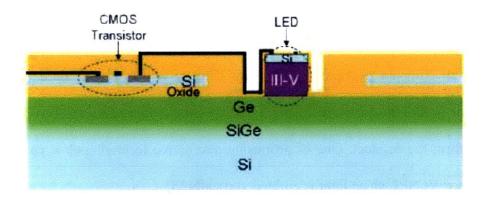

It is the key for silicon microphotonics that devices are built entirely on the Si substrate which can be fabricated using traditional CMOS processing techniques. Monolithic LED has been realized so far. Results of current research on edge-emitting laser (EEL) and vertical cavity surface emitting laser (VCSEL) show that monolithic integration for these optoelectronic devices are highly promising.

Figure 24: Monolithic LED on Si substrate with CMOS technology [6].

# **TERABIT/SECOND-CLASS INTER-CHIP PARALLEL**

# **OPTOELECTRONIC TRANSCEIVER**

### **CHAPTER 1:** Overview of the Terabus Transceiver

#### 1. Background

In the context of current technology, interconnect bandwidth requirements within highperformance computing systems keep increasing. This common trend is driven strongly by the ever-increasing processor speeds, number of processors per system and wide data bus capacity. Parallel optical interconnect between different blocks of the same circuit board or inter-board through back plane is very promising in terms of data throughput, integration density, power consumption and loss optimization as well as latency. With optical interconnect, the constraint on communication link length is undeniably much more liberated in contrary to electrical (copper) counterpart. Parallel optical interconnects based on multimode fibers with total data rates in the range of 100 Gb/s have been increasingly utilized over the next few years or more for links between racks of servers or between boards over lengths from one meter up to hundreds of meters. The debate now is on when optical interconnect will penetrate further within the board for chip-to-chip communication. The competition between optics and copper-based electrical backplanes for on-board interconnects is comprehensive in terms of speed, power efficiency, form factor and, last but not least, cost especially in the light of the advance in high speed electrical interconnects [7], [8]. It is obvious that there exists a critical bandwidth-length product above which optics is favorable because of power consumption [9] and signal integrity.

The key discussion topic for developers now is which interconnect architectures would significantly benefit from the high bandwidth and high level of density that optical technologies have to offer.

#### 2. Introduction of the Transceiver

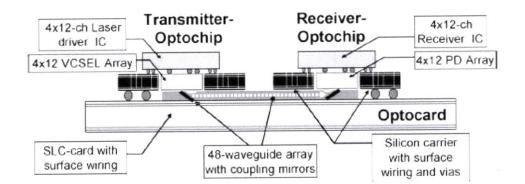

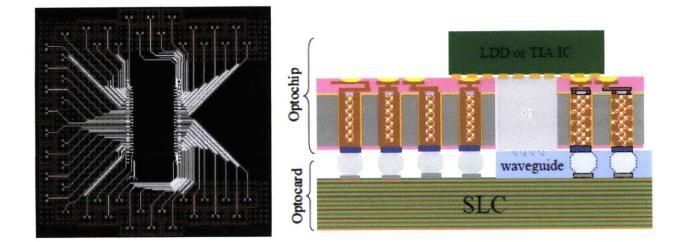

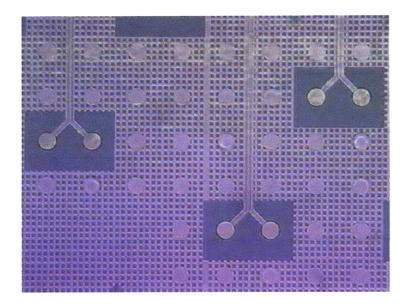

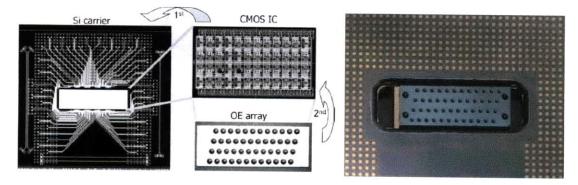

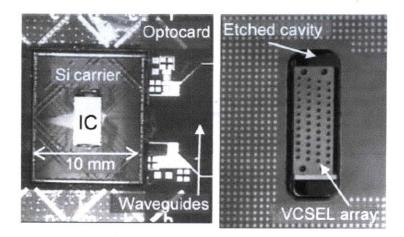

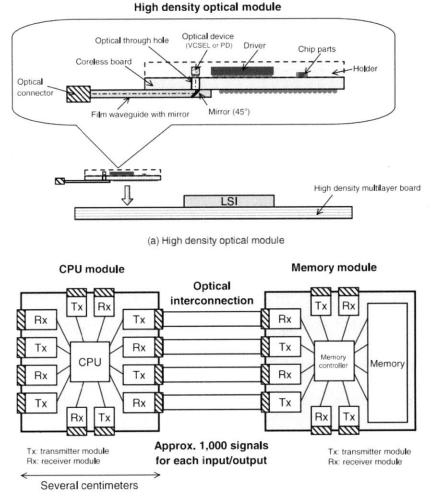

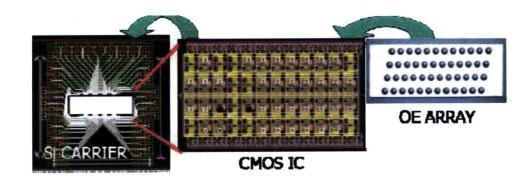

As one of excellent optical interconnect architectures, the Terabit/second-class inter-chip parallel optoelectronic transceiver has been developed under the IBM Terabus project. A complete set of technologies [10] has been proposed and developed to support terabit/second inter-chip data transfers over organic cards within high-performance servers, switch routers, and other intensive computing systems. The transceiver architecture (Figure 13) comprises of a chiplike optoelectronic packaging structure (Optochip), assembled directly onto an organic card (Optocard). In order to reduce the size and boost up the speed, integration parallelism is utilized such that the data rate per line is pushed up to 20 Gb/s and the total number of channels in the bus is designed to be 48 (4x12), achieving the overall data transfers in the range of 0.5-1 Tb/s. The 4-by-12 arrays of 985-nm vertical-cavity surface emitting lasers (VCSELs) and photodiodes (PDs) are flip-chip bonded to the corresponding driver and receiver IC arrays which are implemented by 130-nm CMOS technology. These 2 IC arrays are in turn flip-chip assembled onto a 1.2-cm<sup>2</sup> silicon carrier to complete the transceiver Optochip. One thing needs to be clear here is that the latter flip-chip process is carried out first and then followed by the former due to ease of fabrication which will be discussed subsequently in details.

Figure 13: Schematic of Terabit/s package composed of Optocard with waveguides and transceiver Optochips [10].

The silicon carrier has electrical through vias, high speed wiring and the 1.5 mm x 4.2 mm rectangular cavity to house the VCSEL and PD arrays. This 1.2-cm<sup>2</sup>-form-factor Optochip module aimed for low-power operation will transmit the data through a 62.5-µm-pitch array comprised of 48 parallel multimode optical waveguides patterned on the Optocard. A novel scheme for optical coupling between the Optochip and Optocard has been developed in which the optoelectronic (OE) arrays, which comprise of VCSELs and PDs, are backside emitting or illuminated through arrays of antireflection-coated micro-lenses etched onto the backside of the OE substrates. Right under the OE devices and inside the waveguides on the Optocard, 45°-tilted mirrors are subtly fabricated to creatively couple the light into and/or out of the array of waveguides (Figure 13).

Single channel has been demonstrated to operate up to 20 Gb/s for transmitter and 14 Gb/s for receiver. The per-channel power dissipation over multimode fiber is observed to be as low as 50 mW for 10-Gb/s single-channel links [10].

The Terabus project has been successful in designing the novel Terabit/s-class OE transceiver with prominent features: high bit rate, high level of channel density, which improved the device form factor, and low power consumption. Subsequently, to compete with purely electrical counterparts, highly reliable and cost-effective prototypes are essential. Therefore, the option criteria for electrical packaging, designs of IC and OE devices, waveguides and optical coupling are recommended as follow [10]:

- Utilization of flip-chip technology to reduce wire-bond parasitics.

- The choice of surface-laminar-circuitry (SLC) as an organic card for the Optocard to make use of high wiring density [11].

- Use of Si carrier interposer for Optochip packaging due to the through vias allow direct solder attachment of the Optochip and the Optocard and dense wiring connected to the ICs on top of the interposer [12].

- Use of CMOS ICs to optimize IC power efficiency and cost.

- Option of operating wavelength of 985 nm to allow simple optical design based upon the III-V GaAs/InP substrate and to permit direct integration of lenses onto the backside of the substrate [13].

Figure 14: Structure of Terabus/second transceiver [14].

The subsequent sections will analyze the high-speed OE transceiver in details regarding: components and circuits; fabrication, alignment and packaging; as well as optical, electrical characterization, results and evaluation. The structure is as follow:

- 2-D arrays of VCSELs and PDs; CMOS transmitter driver circuits (TX) and receiver circuits (RX).

- Silicon carrier; Optocard; optical coupling and alignment; packaging.

- Results and evaluation: simulations and measurements.

### CHAPTER 2: 2-D Arrays of VCSELs and Photodiodes

### **CMOS Transmitter Driver Circuits and Receiver Circuits**

#### 1. Vertical Cavity Surface Emitting Lasers

Figure 15: Schematic (left) and photograph (right) of bottom-emitting VCSEL [15].

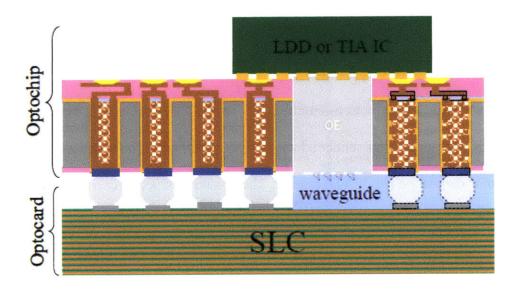

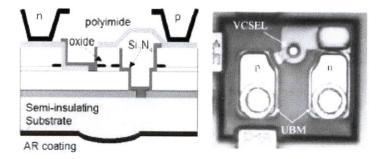

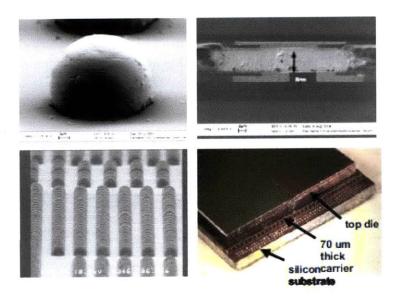

The schematic of the bottom-emitting 985 nm VCSEL structure is shown in Figure 15. The structures were grown on semiconductor GaAs substrate with low-pressure metal-organic chemical vapor deposition (MOCVD) reactor. The epitaxial structure consists of 27.5 pairs of n-type GaAs/Al<sub>0.9</sub>Ga<sub>0.1</sub>As bottom distributed Bragg reflector;  $1-\lambda$  cavity with multiple quantum well active region and 40 pairs of p-type Al<sub>0.1</sub>Ga<sub>0.9</sub>As/As<sub>0.95</sub>Ga<sub>0.05</sub> top distributed Bragg reflector [15]. The device have an oxide-confined structure which is optimized for low series resistance, low parasitics and high-speed operation at low current density while minimizing the excess free carrier loss to the device. The multiple quantum well active region contains three strained InGaAs/AlGaAs quantum wells and two thick graded AlGaAs layers to add up to the cavity thickness [15].

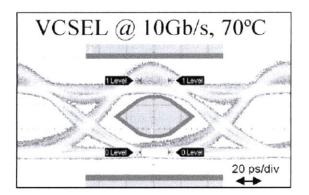

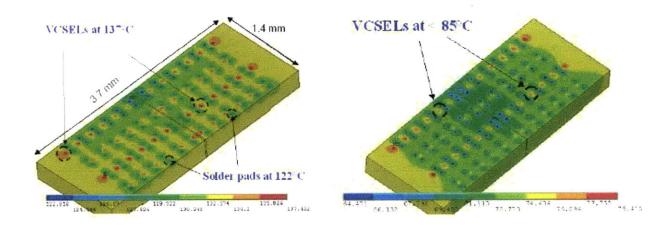

The VCSELs with apertures of 4, 6 and 8  $\mu$ m are fabricated and optimized for 70° – C operation [10]. An array comprised of 4x12 VCSELs is fabricated. The VCSELs with diameter of 4  $\mu$ m and 6  $\mu$ m have bandwidths all above 15 GHz and biasing currents of 2mA and 3mA

respectively [15]. All 48 VCSELs are identically modulated and each channel has extinction ratio above 6 dB.

Figure 16: Enlarged eye diagrams of 6-µm VCSELs at 10 and 20 Gb/s (70° C) [15].

Figure 16 illustrates 10 Gb/s and 20 Gb/s eye diagrams of a 6 µm VCSELs operating at 70°C.

#### 2. Photodiodes

Photodiodes with mesa structure are grown on Fe-doped InP substrate and are backside illuminated. The device responsivity is extremely sensitive to optical absorption in the p-InGaAs layer, requiring this layer to be as thin as possible. 4 sizes of 30, 40, 50 and 60  $\mu$ m are fabricated for the 2-D 4x12-photodiode array. The frequency response is calculated from Fourier transform of impulse response measurements with 2-ps pulses at 985 nm.

Figure 17 shows the inverse relationship between the 3-dB cutoff bandwidth and the diameter of the photodiode, i.e. the smaller the size, the larger the bandwidth, thus the better. At 1.5-V reverse biasing, 60- $\mu$ m photodiode has 3-dB cutoff bandwidth of 13 GHz while 30- $\mu$ m photodiode has the one of 30 GHz which is much larger. However, the smaller the size the better tolerance is required; therefore trade-off between bandwidth and tolerance needs to be taken into consideration. The photodiode responsivity is measured as 0.65 A/W at 985 nm [10].

#### 3. CMOS IC Arrays of VCSEL Driver Circuits and Receiver Circuits

The laser diode driver (LDD) (TX) [16] and receiver (RX) [17] IC arrays were fabricated by IBM in standard 130 nm CMOS process. Both of the two chip arrays can be attached to a common silicon carrier and to identical electrical pad layouts of 3.9 mm x 2.3 mm footprint. The fact that Terabus packaging in which OE devices are flip-chip bonded to the corresponding IC circuit arrays has minimized parasitic factors due to direct and short electrical connection feature has facilitated significantly the performance of these IC arrays. Each array contains 48 amplifier elements and uses 2 voltage sources.

#### a. CMOS VCSEL Driver Circuits:

The LDD array comprised of 48 channels is powered by a 2 voltage sources, one of 1.8 V for the input amplifier circuit and the other of 3.3 V for output stage and bias. Figure 18 shows the structure of each driver circuit which comprises of a differential amplifier, a dc-coupled transconductance output amplifier to supply required modulation current to the VCSEL. The high-output-impedance transconductance amplifier requires less voltage headroom and provides more tolerance to laser series resistance variations. Last but not least, the output stage utilizes a fall time compensation circuit to improve the optical eye symmetry at high data rates.

Figure 18: Functional block diagram of a single-channel VCSEL driver IC [16].

Two variations of the basic driver circuit were designed. A low-power design optimized for 10-Gb/s operation is capable of output modulation current swings of 5-6 mA. A high-speed version is capable of achieving data rates up to 20 Gb/s and supplying 11-mA modulation current [16].

#### b. CMOS Receiver Circuits:

The receiver array comprised of 48 channels is powered by dual 1.8-V supplies for amplifier circuits and a separate 1.5-3-V supply for the photodiode bias. Each receiver channel is structured by a low-noise differential transimpedance amplifier (TIA), a limiting amplifier (LA) and an output buffer as illustrated in Figure 19. TIA and LA circuits are designed to locate at the central region of the chip and fed by a common 1.8-V source. The output buffers, on the other hand, occupy the chip edges and are supplied by a separate 1.8-V source. This designed layout is purposely to avoid switching noise from large signals at the outputs from interfering with the small signals fed to the inputs of the highly sensitive front-end circuits.

Figure 19: Functional block diagram of a single-channel receiver IC [18].

As indicated in Figure 19, the limiting amplifier (LA) comprises of 5 cascaded differential Cherry-Hopper gain stages with an offset cancellation feedback loop around the final four stages [18]. The gain of the receiver is 80 dB. $\Omega$  provided that there is 600-m Vpp differential output signal at the minimum input current of 30  $\mu$ A.

## CHAPTER 3: Silicon Carrier

# Optochip Assembly, Optocard Optical Coupling and Alignment, Packaging

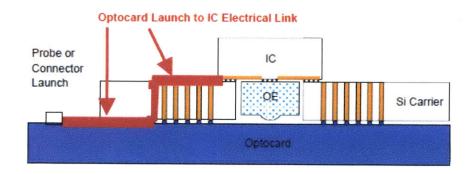

Through vias, high-speed wiring and a through cavity to house the optoelectronic (OE) modules are prominent features of silicon carrier that allow high level of integration density of electrical and optical component on a single substrate to meet small-form-factor requirement for high bandwidth, high performance computing systems. The state-of-the-art set of fabrication, alignment and packaging techniques using eutectic AuSn and SnPb solder systems, integratedrelay-lenses configuration and flip-chip technology has been utilized to realize the transceiver prototype, thank for the maturity of semiconductor processing and packaging industries which has been leveraging high density, high speed parallel optoelectronics, facilitating manufacturability.

## 1. Silicon Carrier

Figure 20: Top view of silicon carrier layout (left); structure of the transceiver (right).

#### a. Structure and Function:

Silicon carrier dimensioned 1.0 cm x 1.2 cm [10] is the basis for the Optochip packaging structure and assembled directly on top of the Optocard to complete the Terabit/second parallel transceiver. The silicon carrier provides a unique platform with fine pitch, high performance electrical interconnects and ability to integrate heterogeneous components including ICs and OE devices using cutting-edge flip-chip bonding technology [19]. The IC chips are flip-chip attached on top of the silicon carrier using fine-pitch eutectic AuSn solder. Electrical through vias allow transmitting signal and power from the Optocard up to the top surface of the silicon carrier. From that point, signal and power are fed into the ICs through high speed differential microstrip transmission lines patterned on top of the silicon carrier. A through rectangular cavity dimensioned 1.5 mm x 4.2 mm [10] is etched at the center of the silicon carrier to house the OE arrays. Significantly, this architecture effectively improves the optical coupling efficiency by minimizing the optical path length between the OE devices to the optical the waveguides structured on top of the Optocard beneath the silicon carrier, increasing module reliability as well as manufacturability by reducing the height of solder between the Optochip and the Optocard. The OE arrays are flip-chip attached to the IC arrays using eutectic AuSn solder while the silicon carrier is flip-chip attached to the Optocard beneath using eutectic SnPb solder. As the result, the highly compact, small-form-fact module has been achieved.

The silicon carrier is designed with three levels of back-end-of-the-line (BEOL) CMOS wiring to effectively distribute signals, power and ground. High speed differential microstrip transmission lines in charge of signal level (top most wiring) interconnect the IC bond pads on the silicon carrier to through-vias that connect to the Optocard. The top view of the silicon carrier is shown in Figure 20 (left) with the OE cavity cleared at the central region. Differential

microstrip transmission lines and through vias is also shown. The through vias for signal, power and ground are distributed on the three sides of the "C" shape (Figure 20) on the layout, freeing the remaining side to accommodate the Optocard waveguides that couple light between the OE devices.

#### b. Fabrication and Processing:

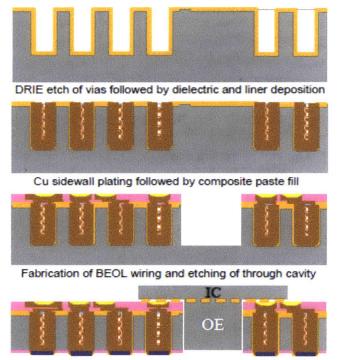

This section is to describe the process to fabricate silicon carrier with through vias, fine pitch wiring and through cavity. The robust process for fabricating electrical through vias is critical for the ability to transfer power and signals from top surface of the silicon carrier to the Optocard and vice versa. The fabrication of through-vias comprises of the following stages: via definition, sidewall insulation, via metallization, connection to terminals or surface wiring and through cavity creating and wafer thinning. The through vias are formed before adding fine pitch wiring and through cavity. The fabrication process flow is illustrated in Figure 21.

Wafer thinning, backside metallurgy, and IC-OE assembly

Figure 21: Silicon carrier process flow [14].

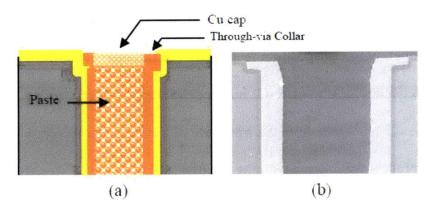

Silicon through vias are created using either wet or dry etch process. In this project [14], Bosch-typed deep reactive ion etch (DRIE) with a resist mask were used because of the advantage for alternating deposition and passivation steps to form through vias with smooth straight sidewalls. The vias are dimensioned as 70 µm in diameter with 225-µm pitch and 300 µm in depth, providing an aspect ratio greater than 4:1. After this etching process, the vias were insulated with thermal silicon dioxide (SiO<sub>2</sub>) and low pressure chemical vapor deposition (LPCVD) of silicon nitride (Si<sub>3</sub>N<sub>4</sub>); the purpose is to conformally cover high aspect ratio features which could be done by other alternative methods such as plasma enhanced chemical vapor deposition (PECVD). Subsequently, the via sidewalls were coated with adhesion and diffusion barriers of TaN/Ta and Cu seed using physical vapor deposition (PVD). Coverage of metal coating on via sidewalls was observed to be continuous. Due to the appreciable difference of thermal expansion coefficients between Si-bulk and Cu, which are 3 ppm/°C and 16 ppm/°C respectively, the via sidewalls were then partially electroplated with Cu to accommodate for the thermal expansion of Cu which may occur during thermal cycling in subsequent CMOS process stages. Modeling has shown that the expansion could reach 0.5  $\mu$ m or more in the case of fully – plated Cu via [14], which potentially results in cracking and fracture of silicon between the densely distributed vias. The vias were filled with a composite paste after excessive Cu had been washed out from the surface using chemical mechanical polishing (CMP). After that, the paste was taken out through sintering process steps to create strong, sealed structure such that BEOL wiring can be patterned over the top of the vias.

The 5- $\mu$ m thick Cu collars are created around top portions of the deep vias (Figure 22) to provide electrical contact planes between the surface wiring and the through vias.

(a) Schemetic; (b) SEM cross-section of plated through via before paste is filled.

Silicon carrier has inherited the accomplishment of current and previous generations of silicon processing technology to achieve high level of wiring compactness. Figure 23 [14] shows the three levels of BEOL CMOS wiring where two patterned Cu planes (power and ground) extend below the impedance matching signal level and where each signal line is connected to the collar of a through via.

Figure 23: Top view of 3 wiring levels on top of silicon through vias: signal, power and ground [14].

Au bumps with 25  $\mu$ m in diameter and 3-5  $\mu$ m in height were created on top of the silicon carrier through plasma deposition to prepare for flip-chip attachment of the ICs to the surface of it. Subsequently, a 1.5 mm x 4.2 mm and 300  $\mu$ m deep rectangular cavity was etched at the center of the silicon carrier from the front side of the wafer for the purpose of housing the OE module. This process was started with the use of a thick resist mask to pattern the cavity and the dielectric was cleared from the cavity region by the combination of highly selective oxide and nitride reactive ion etching. The cavity was etched up to the desired depth of 300  $\mu$ m by Bosch-typed deep RIE. Eventually, the wafer was thinned from the backside using wafer grind and polishing process [14] to the desired thickness of 300  $\mu$ m. Effectively, the previously blind vias and cavity now became the through features with the required thickness. Wet process etching using tetramethylammonium hydroxide (TMAH) was used to expose the through vias from the backside. PECVD oxide was deposited on the backside of the wafer to insulate the backside silicon. Subsequently, CMP was used to selectively remove the oxide out of the bottom surface of only the through vias for electrical connection to the Optocard.

## 2. Optochip Assembly, Optocard

## a. Optochip Assembly:

This assembly process comprises of the following 4 steps which are in sequence:

- Flip-chip bonding of ICs to the silicon carrier

- Flip-chip bonding of the OE arrays to the corresponding IC arrays

- Underfill application

- Flip-chip bonding of the Optochip onto the Optocard.

Figure 24: Solder micro bumps and array [20].

This hierarchical assembly procedure was started with flip-chip attachment of the ICs to the silicon carrier using eutectic AuSn (80% Au, 20% Sn) solder, followed by the flip-chip attachment of the OE arrays, which were now already assembled with the silicon carrier, to the corresponding IC arrays using the same soldering metal compound. Finally, the Optochip was attached to the Optocard using eutectic SnPb (63% Sn, 37% Pb) solder. Figure 24 illustrates examples of the solder micro bumps and an array used in flip-chip assembly process. The key point to note for this process is that the melting temperature of eutectic AuSn is 278°C during reflow<sup>2</sup> and greater than 400°C after reflow. This property allowed multiple level of attachment: the ICs were to be attached to the Si carrier first, after reflow the melting temperature of the AuSn solder joint has increased from 278°C to more than 400°C. Subsequently, the OE arrays were attached to the ICs while the ICs were still attached to the silicon carrier owing to the increase of the melting temperature after reflow. Figure 25 (left) describes well this particular sequence.

<sup>&</sup>lt;sup>2</sup> A process in which a solder paste is first used temporarily to attach one or several electrical components to contact pads; then the entire assembly is subjected to controlled heat, which melts the solder, permanently connecting the joint. Heating maybe carried out by reflow oven or infrared lamp or by soldering individual joints with a hot pencil.

The attachment was carried out using flip-chip bonding tool of better than  $2-\mu m$  alignment accuracy. The bottom view of the Optochip assembly with silicon carrier having under bump metallization (UBM) pads and through cavity together with ICs and OE devices in the cavity is shown in Figure 25 (right). The 4x12 lens array for optical coupling is also clearly seen.

Figure 25: Flip-chip assembly procedure (left). Bottom view of Optochip: OE in cavity and UBM pads (right).

Shear tests were performed on ICs-silicon carrier as well as OE arrays-ICs flip-chip bonds. Average bond strength force of greater than 0.4 kg for the former and of greater than 1 kg for the latter has been observed.

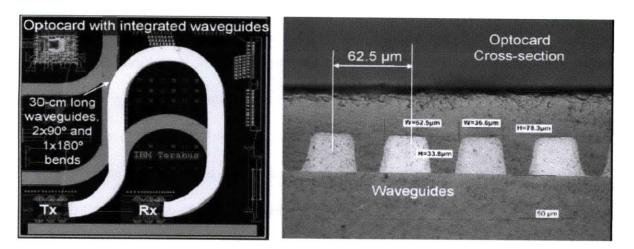

## b. Optocard:

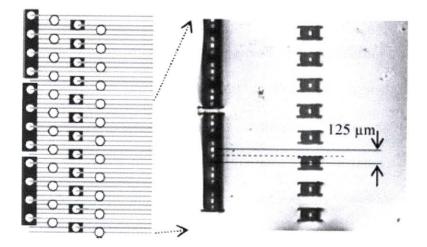

Figure 26: Layout of the Optocard (left) and cross-section with 62.5-µm-pitch integrated waveguides (right) (IBM).

The Optocard is a 15 cm x 15 cm printed circuit board made by surface laminar circuitry (SLC) technology. Figure 26 describes the top-view layout of the Optocard. The SLC has dielectric constant of 3.4 and loss tangent of 0.027. An acrylic layer is deposited on top of the SLC card by doctor blading<sup>3</sup>, waveguides are patterned into the layer using photolithography with UV exposure through a contact mask [21]. After that, a solvent will be used to remove the unexposed regions. Lastly, the cladding-core-cladding stack is thermally baked to complete the cure. The Optocard has been patterned with 48 multimode waveguides cross-sectioned of 35  $\mu$ m x 35  $\mu$ m on a 62.5- $\mu$ m pitch. The waveguide link (Figure 26) length is 30 cm, consisting of one 180° and two 90° bends with minimum bend radius of 28.5 mm, which has been proved to be free of bending loss since the required minimum bend radius is 25 mm.

## 3. Optical Coupling and Alignment, Packaging

## a. Optical Couple and Alignment:

#### i. Optical Coupling Mechanism:

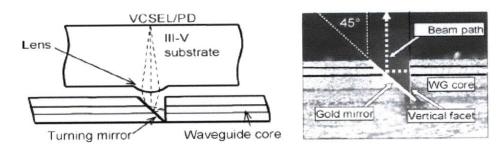

The transceiver has a novel coupling mechanism to guide the light emitted from the VCSELs to the photodiodes. The mechanism consists of the two 4x12 arrays of relay lenses. Each of these arrays is fabricated right on the back surface of the GaAs/InP substrate and exactly aligned to each of the VCSEL and photodiode arrays.

Figure 27: Optical coupling mechanism between OEs and the Optocard waveguides.

<sup>&</sup>lt;sup>3</sup> A common tape-casting method in which a ceramic powder slurry, containing an organic solvent such as ethanol and various other additives (e.g., polymer binder), is continuously cast onto a moving carrier...[Encyclopedia Britannica].

As illustrated in Figure 27, the lens images the laser/photodiode active region onto the waveguide core. The coupling mechanism also includes  $45^{\circ}$ -tilt mirrors to bend the light perpendicularly from the output of the lasers into the waveguide core and out of the waveguide core into the input of the photodiodes. The mirror surface is coated with a layer of gold to maintain high reflectivity. An optical underfill medium of index 1.5 which is comparable to the waveguide material was used to couple the OE lens surface to the one of the waveguide. According to optical modeling, a lens with radius of curvature of 110-120  $\mu$ m and conic constant of -2 (hyperbolic) in the GaAs/InP surface is proved to provide efficient coupling to the 35  $\mu$ m x 35  $\mu$ m waveguide core.

Figure 28: Schematic diagram of mirror fabrication at the end of 48 Optocard waveguides (left). Photograph of fabricated sample illuminated by a white light (right).

Figure 28 (left) shows a schematic diagram of the 48 Optocard waveguides patterned on a pitch of 62.5  $\mu$ m. The waveguides are arranged by a staggered 4x12 array of OEs. The mirrors in the outermost (left) row are ablated as three long mirrors for manufacturability. Each long mirror couples light between four waveguides and four OE devices in the first row of the Optochip. The smaller mirrors in the third row have the width of approximately 125  $\mu$ m on a pitch of 250  $\mu$ m. This layout allows light to be coupled at 125- $\mu$ m spacing instead of 62.5  $\mu$ m spacing, which

makes the fabrication much easier. As illustrated in Figure 28 (right), the mirrors are tested with a white light illumination. Some light is leaking through the neighboring channels of the illuminated channel in the large mirror due to the individual mirrors of row three only partially extend over the neighboring waveguides, allowing some light through to the row with large mirror. The laser-ablation process is now under refining to allow fabrication of smaller mirrors at 62.5-µm spacing.

## ii. Study for Tolerance of Optical Alignment:

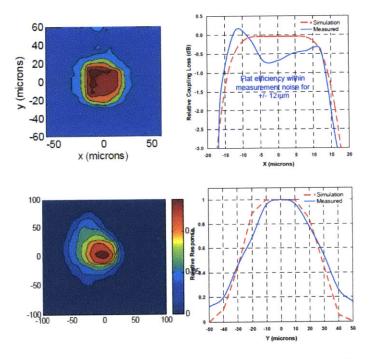

The investigation has been carried out on the sensitivity of the optical coupling efficiency to the mechanical alignment offsets of the relative position of a prototype Optochip to waveguides on prototype Optocard. 980-nm VCSEL and 60-µm-diameter photodiode were used.

By both simulation modeling and measurement, the sensitivity along the optical axis (z-axis) for VCSELs showed optimal coupling at lens-to-waveguide-core separation of 190  $\mu$ m with large and achievable tolerance of approximate  $\pm$  50  $\mu$ m.

47

The dependence on x-y (horizontal) alignment is more critical. Figure 29 (left) shows the contour plots with magnitude in color notation of the coupling efficiency dependence on the horizontal offsets. Figure 29 (right), for VCSEL-waveguide case (up), shows nearly constant coupling efficiency for the offset of  $\pm$  12 µm. For photodiode-waveguide case (Figure 29-down), the tolerance of  $\pm$ 10 µm has been realized. As clearly observed, the results obtained from prototype measurement (in blue) and simulation modeling (in dotted red) are in good agreement.

In conclusion, the system mechanical tolerance of budget of  $\pm 10 \ \mu m$  has been realized. Therefore, the state-of-the-art flip-chip alignment tools have sufficient accuracy budget (better than  $\pm 2 \ \mu m$ ) to satisfy the tolerance requirement.

#### b. Packaging:

### i. Optochip-to-Optocard Packaging:

## This part is in continuation with section 2: "Optochip Assembly, Optocard" of this chapter.

Before attaching the Optochip to the Optocard, the eutectic solder: SnPb (63% Sn, 37% Pb) is transferred onto the Optocard using injection-molded solder (IMS) technique [22]. Using IMS technique, the solder is deposited in the "C" shape on the Optocard around the waveguide mirror [10]. The IMS process provides the solder columns with approximately 200-µm height which is adequate clearance for Optochip over the 150-µm height of waveguide. Solder height correction is performed during the final attachment in which different temperature between the Optochip and the Optocard are utilized. A shear strength greater than 10 kg is achieved for the flip-chip Optochip-Optocard bonding. In flip-chip bonding, only passive alignment is allowed, as the result, the key constraint here is that the OE chip must be in be visible with the waveguide during the assembly, i.e. features on the OE devices are to directly contact features on the

waveguides. The top-view of the entire Optochip-to-Optocard assembly is shown in Figure 30 (left).

Figure 30: Entire Optochip-on-Optocard assembly (left) and bottom view of silicon carrier (right)

## ii. Thermal-Control Consideration for the Package:

Figure 31: 3mm heat pipe in contact with test chip [23].

Due to high level of integration, thermal control is the critical issue for the Terabus package. Especially in high-speed operation, temperature control is essential to ensure satisfactory lifetime of the OE device. The VCSEL threshold current has strong dependence on temperature and so does the photodiode leakage current. There are some critical design requirements. First, the Terabus structure is optimized to operate at 70°C.

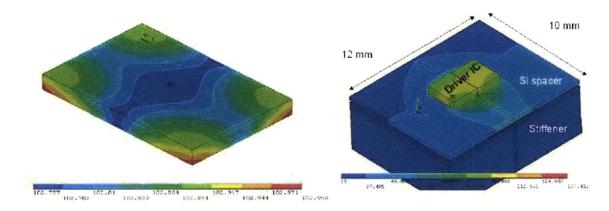

Figure 32 a : Temperature distribution in test chip with no cooling (left) and result for temperature distribution in the entire package (right) [23].

Second, the ICs are operating at low power where 100 mW per channel has been target in the initial phase. Based on the thermal simulations of the entire package (Figure 32a ), an additional cooling system has been recommended to cope with a heat flux of up to  $60 \text{ W/cm}^2$  [23]. As illustrated in Figure 31, the heat pipe is put in contact with the IC backside for cooling in evaluation phase of the package.

Figure 32 b: Local temperature distribution in the VCSEL chip with no cooling (left) and with heat pipe cooling (right) [23].

Figure 32 b illustrates the effect of the cooling mechanism (the heat pipe) on the thermal map of the VCSEL array. The temperature has significantly reduced throughout the chip with the pipe attached on top.

## CHAPTER 4: Results and Evaluation

## 1. Measurements of Silicon Carrier Electrical Signal Path

Figure 33: Electrical path (in red) on silicon carrier: strip line on the Optocard and silicon carrier through via, microstrip line [14].

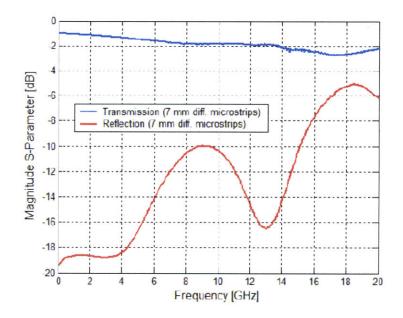

The Silicon carrier electrical path as illustrated in Figure 33 (in red) mainly includes a 7mm differential microstrip line on silicon carrier, a 0.3-mm differential silicon carrier through via and a 7-mm differential strip line on the Optocard. The link has been characterized up to 20 GHz.

The 7-mm strip line on the Optocard shows about 1.3-dB loss at 20 GHz excitation while the 7-mm microstrip line on silicon carrier shows approximately 3 dB-loss and the through via reveals 0.6-0.9 GHz dB-loss at the same frequency condition. With additional probing loss factors included, measured data shows that the entire link has 5-dB loss at 20 GHz and the 3-dB cutoff was reached at around 10 GHz [14].

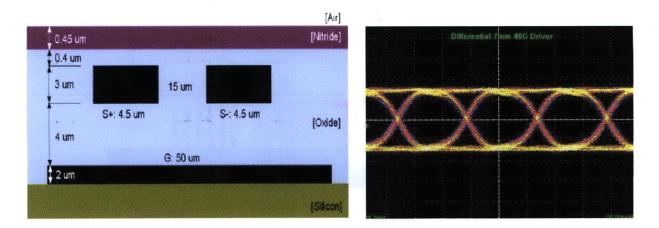

#### a. Measurement of Differential Microstrip Lines on Silicon carrier:

Figure 34 (left) shows the cross section with dimensions of a differential microstrip line on the silicon carrier which will be characterized in time as well as frequency domain using GSSG microprobes. The eye diagram<sup>4</sup> plotted for the 7-mm microstrip line is shown in Figure 34 (right). Since the eye pattern is observed to be "open", the line is qualified for 20-GHz operation.

Figure 34: Layer dimensions of differential microstrip transmission lines on the silicon carrier (left) and its eye diagram (right) for 7-mm length at 20 GHz, PRBS 7-1 data pattern [14].

A vector network analyzer is used to characterize the performance of the microstrip line in frequency domain. The calibration was set up using a reference substrate and the short-openload-through (SOLT) technique. The vector network analyzer will measure the S-parameters of the line to obtain both reflection coefficient ( $S_{11}$ ) and transmission coefficient ( $S_{12}$ ). The results obtained were coupled with the effect of probe launches and impedance mismatch between the measured microstrip line and the 100 $\Omega$  reference impedance of the vector network analyzer. Figure 35 plots out the dependence of the transmission (blue) coefficient and the reflection coefficient (red) of the 7-mm line on various operating frequencies, both are presented in dB.

<sup>&</sup>lt;sup>4</sup> In telecommunication, an eye pattern, also known as an eye diagram, is an oscilloscope display in which a digital data signal from a receiver is repetitively sampled and applied to the vertical input, while the data rate is used to trigger the horizontal sweep. It is so called because, for several types of coding, the pattern looks like a series of eyes between a pair of rails.

Figure 35: S-Parameters (S<sub>11</sub> and S<sub>12</sub>) of the 7-mm silicon carrier microstrip line.

From the plot, the measured insertion loss for the microstrip lines is approximately 2.2 dB at 20 GHz. In addition, from the S-parameters data obtained above, the attenuation of the line can be extrapolated using the T-parameters method proposed in [24] and with the aid of IE3D<sup>5</sup>. Results show that the extrapolated attenuation constant is 4.3 dB/cm at 20 GHz corresponding to 3-dB insertion loss of the line assuming it is ideally matched and the length is 7 mm [14].

## b. Measurement of Differential Silicon Carrier Through Via:

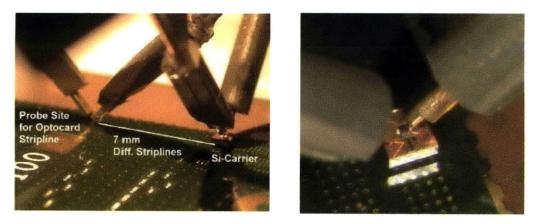

Figure 36: Measurement setup for silicon carrier through via transmission [14].

<sup>&</sup>lt;sup>5</sup> An antenna and microwave simulation software developed by Zeland Inc.

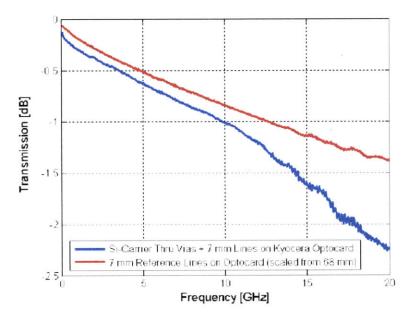

Figure 36 illustrates the measurement setup for probing the transmission of the silicon carrier through-via. The SOLT calibration technique using a reference substrate has been used. The measurement method is as described follow: first, the transmission of the system comprised of the silicon carrier through via and the 7-mm line on the Optocard has been obtained; second, the transmission of the 7-mm reference line on the Optocard has also been obtained. The deference of these two above transmissions indeed represents the upper limit (worst case) of the transmission for the silicon carrier through via since other loss and parasitic factors may be incorporated without using the reference line. The measurement of the two transmissions is plotted out in Figure 37.

Figure 37: Transmissions of the through via + the 7-mm Optocard line (red) and of the reference Optocard line only (blue).

At operating frequency of 20 GHz, the transmission of the system of through via and line is recorded as -2.25 dB while the transmission of the reference line is approximately -1.4 dB. Therefore, effectively, the transmission of the through via can be deduced approximately as -0.85 dB (since: 2.25 - 1.4 = 0.85). Since this result describes the worst-case scenario, the performance of the silicon carrier through via is expected to be better.

## 2. Measurement of Optocard Waveguide for Loss and Dispersion

## a. Optocard Waveguide Loss Measurements:

To measure the loss of the waveguides on top of the Optocard, a 30-cm multi-bent acrylate waveguides fabricated on a surface-laminar-circuitry (SLC) substrate has been used as a sample. The gold-coated mirrors are fabricated at either ends of the waveguide to couple the laser light at 90° in and out the waveguide [10]. The calibration setup for the mirrors is performed by using a reference 2-cm waveguide system. The 2-D mirror array allows access to 24 waveguides on a125-µm pitch. 980-nm continuous laser light is coupled into a single-mode fiber and imaged into the core of the waveguide. A large-area photo-detector is used to measure the light at the output.

The loss on average of the system is recorded as -4.8 dB, with a best channel loss of -3 dB which is corresponding to an average of 0.16 dB/cm and a loss of 0.1 dB/cm for the best case [10].

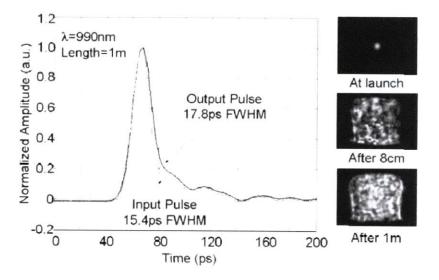

## b. Optocard Waveguide Dispersion Measurements:

To investigate the modal dispersion of the waveguides, 2-pico-second short pulse is propagated from a Ti:Sapphire laser at 990 nm through waveguides of different lengths [25]. The input and output pulses are measured with a 14-GHz photodiode on a high-speed sample scope. The impulse responses before and after propagation through a 1-m multi-mode waveguide are shown in Figure 38. The pulse broadening evolution is shown at the right of Figure 38, i.e. the initial stop-sized pulse is getting dispersed and broadens as it travels through the waveguide, the longer the length the worse the dispersion.

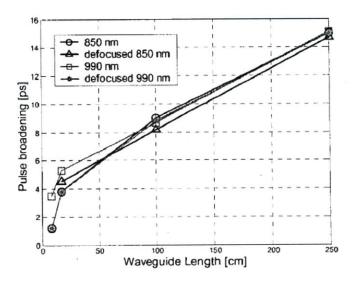

Figure 39: Summary of pulse broadening results for 8, 17, 100 and 255-cm waveguides for both 850 nm and 990 nm [25].

The dependence of pulse broadening on the waveguide lengths for the two wavelengths of 850 nm and 990 nm is illustrated in Figure 39 plots which are produced by deconvoluting the response of the photodiode and the sampling head [25]. The transfer function of different waveguide lengths can be deduced by a fast Fourier transform of the impulse responses [10]. The result shows that for links shorter than 1 m, dispersion will not be appreciable for operation at 40 Gb/s and below. For link 2.5 m long, the 3-dB bandwidth limitation caused by model dispersion decreases to 23 GHz compared to 50 GHz and 39 GHz for the 0.3-m and 1-m long, respectively.

It is useful to note that in organic waveguide, e.g. acrylate, the loss due to factors other than dispersion is significant because of the relatively high intrinsic absorption of this organic medium around 985 nm. Further advance in material technology is necessary for waveguide more than 1m long to perform multi-gigabit/s communication at this wavelength.

## 3. Optochip Characterization

High-speed testing at the Optochip level is carried out by wire-bonding the Optochips onto a printed circuit card with a cavity in the middle. It is possible to either turns on all 48 channels at the same time or just 6 channels each. The Optochip is characterized by connecting the transmitter and the receiver channels over a 5-m-long 50-µm multi-mode fiber (MMF) link [10]. Photodiode detectors with 30-µm diameter have been used in all experiment since the capability the handle high frequency.

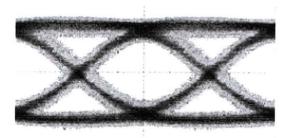

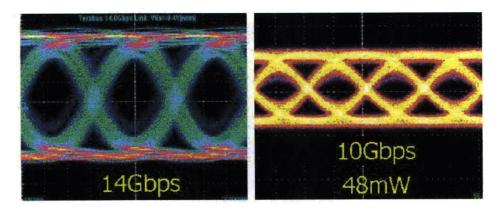

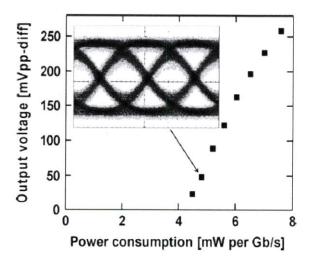

For the Transmitter Optochips, error-free (BER  $< 10^{-12}$ )<sup>6</sup> operation at 20 GHz has been measured [16] using a reference receiver. Figure 40 illustrates the corresponding eye diagram.

Figure 40: Eye diagram at 20 Gb/s from a Terabus transmitter. The drive circuit included a circuit to compensate for the fall time of the VCSEL emission [26].

<sup>&</sup>lt;sup>6</sup> BER (Bit error rate) is the number of received bits that have been altered due to noise, interference and distortion, divided by the total number of transferred bits during a studied time interval.

The results [26] have shown that these are the fastest directly-modulated VCSEL transmitters with CMOS drivers demonstrated to-date.