# St. Cloud State University theRepository at St. Cloud State

Culminating Projects in Electrical Engineering

Department of Electrical and Computer Engineering

5-2021

# Very Low Frequency Electrical Impedance Tomography Image Reconstruction System Using FPGA Software-Hardware Codesign

Monali Sinare

Follow this and additional works at: https://repository.stcloudstate.edu/ece\_etds

Part of the Electrical and Computer Engineering Commons

# **Recommended Citation**

Sinare, Monali, "Very Low Frequency Electrical Impedance Tomography Image Reconstruction System Using FPGA Software-Hardware Co-design" (2021). *Culminating Projects in Electrical Engineering*. 5. https://repository.stcloudstate.edu/ece\_etds/5

This Thesis is brought to you for free and open access by the Department of Electrical and Computer Engineering at theRepository at St. Cloud State. It has been accepted for inclusion in Culminating Projects in Electrical Engineering by an authorized administrator of theRepository at St. Cloud State. For more information, please contact tdsteman@stcloudstate.edu.

# Very Low Frequency Electrical Impedance Tomography Image Reconstruction System

# Using FPGA Software-Hardware Co-design

by

Monali Sinare

# A Thesis

Submitted to the Graduate Faculty of

St. Cloud State University

in Partial Fulfilment of the Requirements

for the Degree of

Master of Science

in Electrical Engineering

May, 2021

Thesis Committee: Yi Zheng, Chairperson Mahbub Hossain Shensheng Tang

### Abstract

Electrical Impedance Tomography (EIT) is an imaging technique which is noninvasive and uses the internal conductivity distribution of the object of interest to form a tomographic image. It is performed by applying electrodes to the surface of the object. An alternating current up to frequency 10kHz is applied through a pair of electrodes, and the induced voltage is measured on other electrodes. These current and voltage values are used to reconstruct the internal conductivity distribution. The EIT imaging is increasingly getting used in clinical applications, as it is safer, portable, and low cost if compared with available imaging technologies used in clinical settings.

The goal of this project is to develop a low frequency Zynq SoC-based EIT system. A Zynq 7020 device-based development board, Zedboard, interfaced with a customized hardware circuit, is used to develop a complete EIT system. A graphical user interface is developed using C# Graphic User Interface (GUI) application to control the hardware and visualize the results. It is a twelve-electrode system, and current injection and voltage measurement is performed through Zynq SoC. There are two image reconstruction algorithms developed, Gauss Newton One Step and Total variation. The algorithms are implemented in Zynq SoC using software-hardware co-design. The algorithms are also implemented in C#. The image reconstruction performance between the two algorithms is compared. The computation performance between Zynq SoC implementation and C# implementation is also compared to understand the feasibility of FPGA implementation of EIT image reconstruction algorithms.

# Acknowledgements

I would like to thank Dr. Yi Zheng, my advisor, and mentor for this thesis. I am grateful to Dr. Zheng for allowing me to work on this project. He has provided valuable insights throughout the development of this project. I would like to especially thank Dr. Zheng for his continuous support and encouragement throughout my entire study time at St. Cloud State University.

I would like to thank Dr. Mahbub Hossain and Dr. Shensheng Tang for being on the thesis committee. I would also like to thank Robert Dubois for helping me during the initial phase of this project.

Finally, I would like to thank my family, especially my son, for their patience and support.

# **Table of Contents**

| Page                                                                  |

|-----------------------------------------------------------------------|

| List of Table7                                                        |

| List of Figures                                                       |

| Chapter                                                               |

| 1. Introduction                                                       |

| 1.1 EIT in Biomedical Applications11                                  |

| 1.2 FPGA for EIT Image reconstruction System                          |

| 1.3 Objectives                                                        |

| 1.4 Thesis Organization                                               |

| 2. Electrical Impedance Tomography                                    |

| 2.1 Electrical Impedance Tomography Background                        |

| 2.2 Mathematical Background                                           |

| 2.3 Finite Element Method                                             |

| 2.4 Jacobian Matrix                                                   |

| 2.5 EIT Algorithms                                                    |

| 2.6 Prior Techniques 40                                               |

| 3. Previous Work Study                                                |

| 3.1 Study on human brain Activity and electrical impedance tomography |

| 3.2 Image Reconstruction and EIT                                      |

| Cha | pter                                               | Page |

|-----|----------------------------------------------------|------|

|     | 3.3 Real-Time Electrical Impedance Tomography      |      |

| 4   | EIT MATLAB Implementation                          | 59   |

|     | 4.1 About EIDORS                                   | 59   |

|     | 4.2 Design Description                             | 60   |

|     | 4.3 Test Results                                   | 62   |

| 5   | 5. XILINX Development Hardware and Software        | 64   |

|     | 5.1 Device Architecture                            | 64   |

|     | 5.2 Development Board                              | 67   |

|     | 5.3 Development Software                           | 69   |

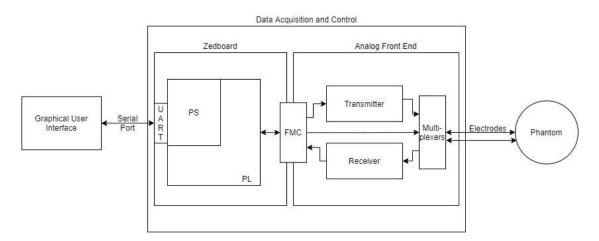

| 6   | 5. EIT System Architecture                         | 71   |

|     | 6.1 System Architecture                            | 71   |

|     | 6.2 Algorithm Implementation                       | 76   |

| 7   | 7. Analog Front End Design Study and Modifications | 82   |

|     | 7.1 Design Analysis                                | 82   |

|     | 7.2 Modifications to Operate on Low Frequency      | 88   |

| 8   | 8. FPGA Design Development                         |      |

|     | 8.1 Zynq SoC Design Description                    | 97   |

|     | 8.2 VIVADO Design                                  |      |

|     | 8.3 SDK Design                                     | 126  |

| 9   | 9. Graphical User Interface Design and Development | 154  |

5

| Chapter                                             | Page |

|-----------------------------------------------------|------|

| 9.1 Design Description                              | 154  |

| 10. Experiments and Results                         | 173  |

| 10.1 Analog measurements                            | 173  |

| 10.2 Image Reconstruction results                   | 175  |

| 10.3 System Implementation and Performance Analysis |      |

| 11. Discussion and Conclusion                       | 189  |

| Bibliography                                        | 193  |

| Appendix                                            | 200  |

| A. MATLAB EIDORS Code                               | 200  |

| B. VIVADO Design Flowcharts                         | 204  |

| C. SDK Code Flowcharts                              | 205  |

| D. C# Implementation Functional Flowchart           | 210  |

6

# List of Tables

| Table                                              | Page |

|----------------------------------------------------|------|

| 1. 1 Typical Tissue Resistivity [4], [5]           | 12   |

| 7. 1 Electrode stimulation and measurement pattern | 83   |

| 7. 2 Measurement for Channel 0                     | 94   |

| 8. 1 DDR Mapping                                   | 134  |

| 8. 2 ADC SPI EMIO Pin Assignment                   | 140  |

| 10. 1 Acquisition time at low frequency            |      |

| 10. 2 Algorithm computation time                   |      |

# List of Figures

| Figure                                                                   | Page |

|--------------------------------------------------------------------------|------|

| 2. 1 Typical EIT System Block Diagram                                    | 22   |

| 2. 2 Stimulation Pattern for Electrode Pair                              | 24   |

| 2. 3 Typical Triangular Element in 2D problem                            | 31   |

| 3. 1 C# Implementation Flowchart (Chen)                                  | 44   |

| 3. 2 Image for 16 rings and Tikhonov Prior (Chen)                        | 45   |

| 3. 3 C# Implementation Flowchart (Rabi)                                  | 47   |

| 3. 4 Conjugate Gradient Image result with 24 rings, Laplace Prior (Rabi) | 48   |

| 3. 5 Block Diagram of Analog Front End Hardware                          | 49   |

| 3. 6 FPGA Block Level Implementation (Senior Design Team)                | 53   |

| 3. 7 Timing Summary of FPGA design (Senior Design Team)                  | 54   |

| 3. 8 Device Utilization Report (Senior Design Team)                      | 55   |

| 3. 9 Flowchart for GUI Implementation (Senior Design Team)               | 57   |

| 4. 1 EIDORS Code Flowchart                                               | 60   |

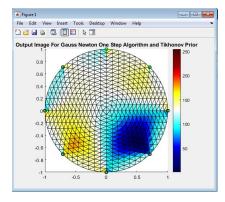

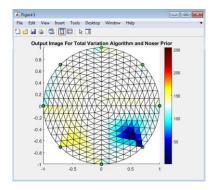

| 4. 2 Image with Gauss Newton One Step, 16 rings and Tikhonov Prior       | 61   |

| 4. 3 Image with Total Variation, 12 rings and Noser Prior                | 61   |

| 5. 1 Zynq FPGA SoC Architecture [38]                                     | 63   |

| 5. 2 Zedboard Block Diagram [40]                                         | 66   |

| 6. 1 Block Diagram of EIT System Implementation                          | 69   |

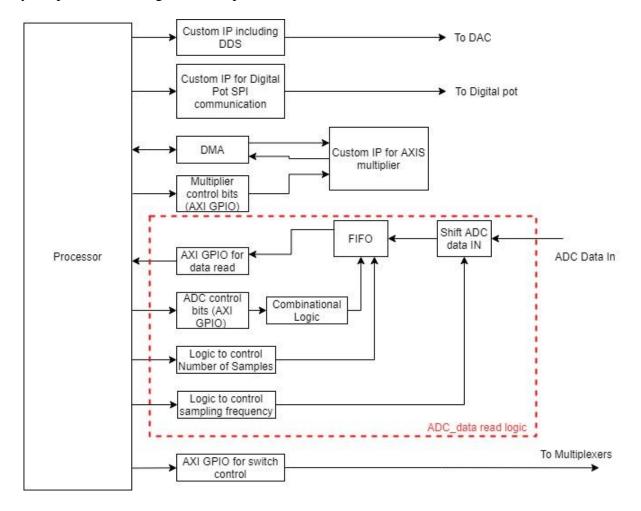

| 8. 1 VIVADO Functional block diagram                                     | 97   |

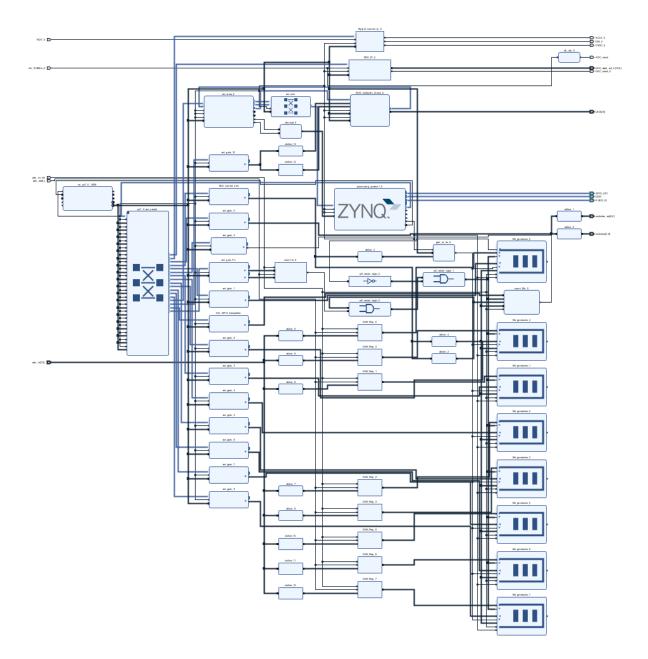

| 8. 2 Complete VIVADO Block Diagram                                       |      |

| Figure                                                   | Page |

|----------------------------------------------------------|------|

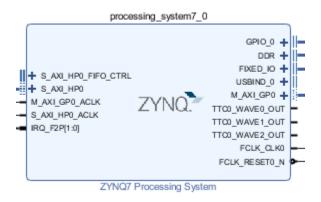

| 8. 3 Processor IP                                        | 99   |

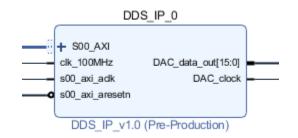

| 8. 4 DAC data generation IP core                         | 100  |

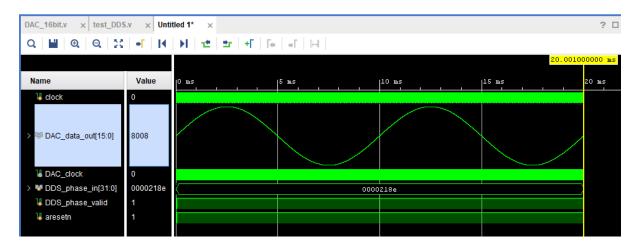

| 8. 5 Simulation waveform for 100Hz                       | 103  |

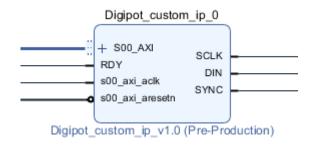

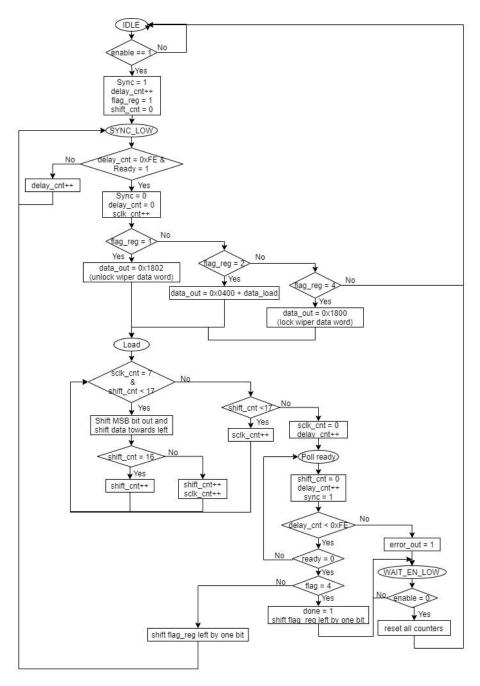

| 8. 6 Digital Pot control IP core                         | 104  |

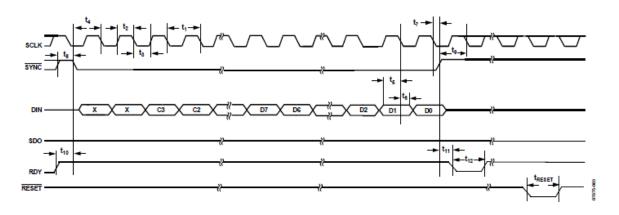

| 8. 7 Write Timing Diagram AD5293 [47]                    | 106  |

| 8. 8 AXI-lite register usage for digital pot programming | 107  |

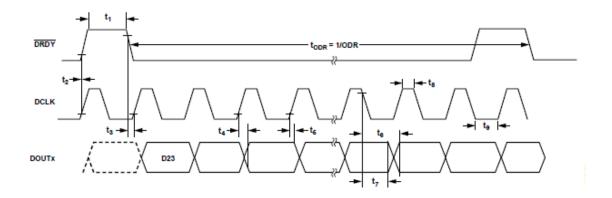

| 8. 9 ADC interface timing diagram[48]                    | 109  |

| 8. 10 ADC channel and shift register IP block            | 109  |

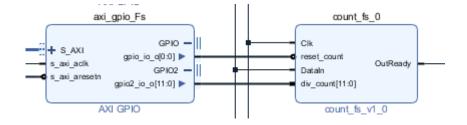

| 8. 11 Sampling frequency setting logic blocks            | 111  |

| 8. 12 sampling frequency division logic                  | 111  |

| 8. 13 Number of samples control IP block                 | 112  |

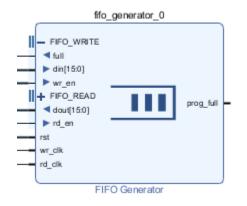

| 8. 14 FIFO IP Core                                       | 114  |

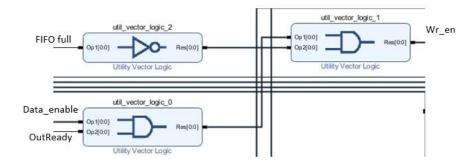

| 8. 15 Combinational Logic for FIFO write enable          | 115  |

| 8. 16 FIFO Read enable signal IP core                    | 115  |

| 8. 17 generate FIFO read enable logic                    | 116  |

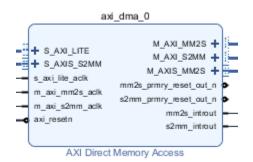

| 8. 18 AXI DMA IP Core block in the design                | 118  |

| 8. 19 AXIS multiplier IP core block                      | 119  |

| 8. 20 AXIS multiplier data load logic                    | 121  |

| 8. 21 ADC SPI communication format [48]                  | 139  |

| 8. 22 DMA transfer                                       | 144  |

| 8. 23 Wb computation code (SDK)                          | 146  |

| Figure   Page 1                                                       | Page |

|-----------------------------------------------------------------------|------|

| 8. 24 TV Denominator computation code (SDK)                           | .147 |

| 8. 25 Matrix Inversion logic flowchart (SDK)                          | .149 |

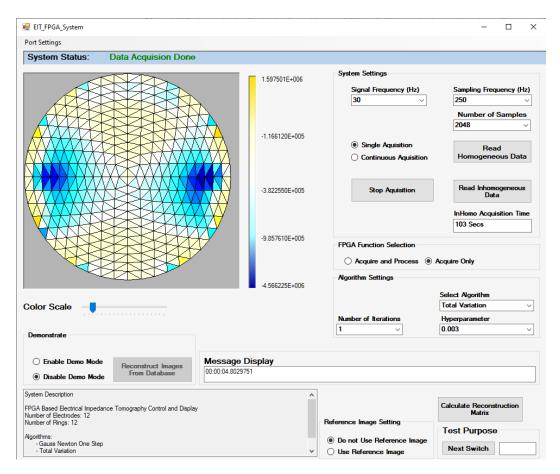

| 9. 1 GUI Design for EIT System                                        | .153 |

| 9. 2 Port settings form                                               | .156 |

| 10. 1 EIT System Hardware Setup                                       | .171 |

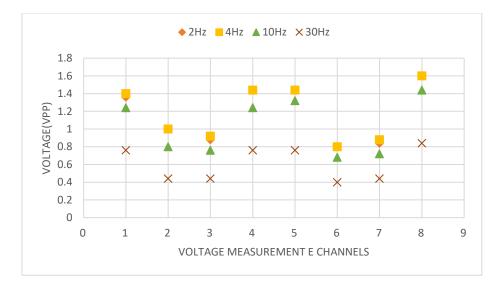

| 10. 2 Voltage measurement at 8 ADC channels for different frequencies | .172 |

| 10. 3 Tissue phantom used for the testing                             | .173 |

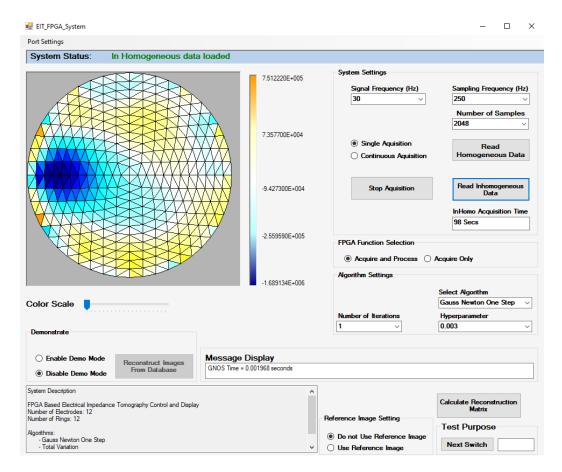

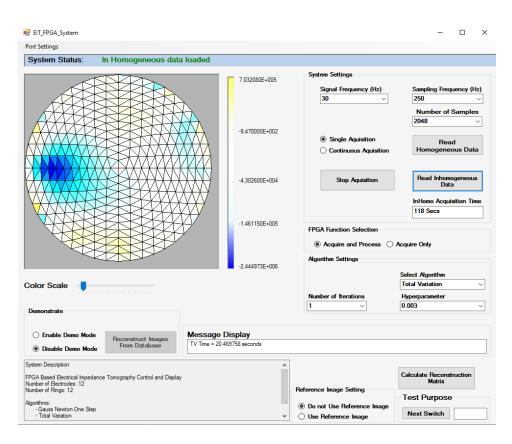

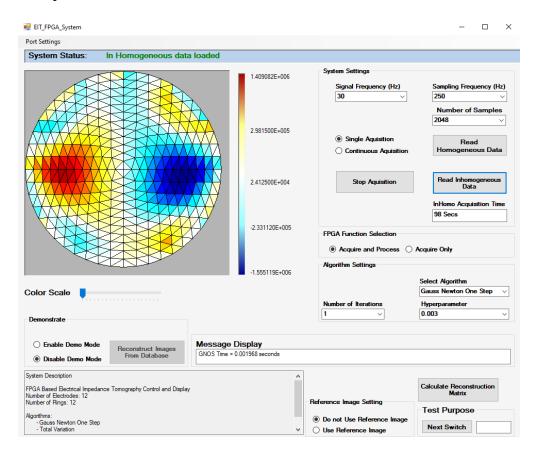

| 10. 4 Gauss Newton One Step Low Impedance Image at 30Hz               | .174 |

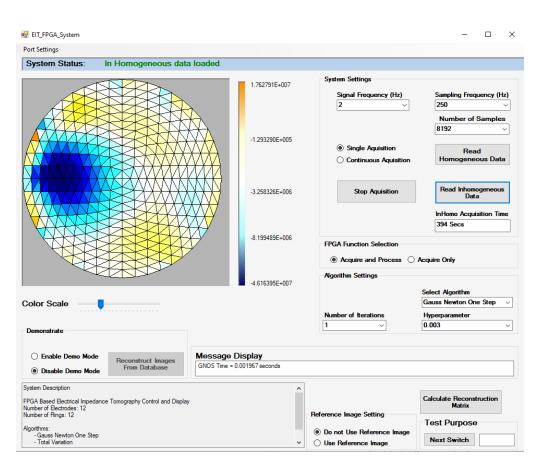

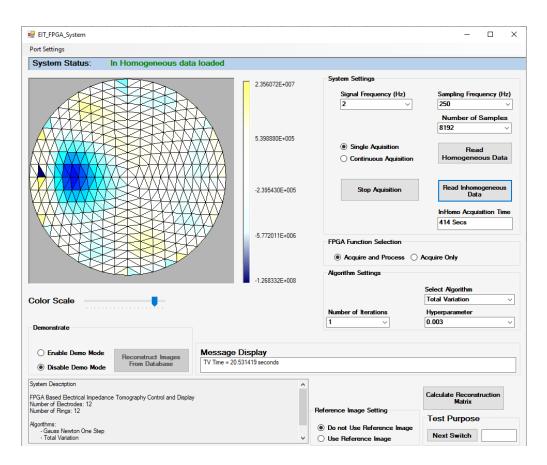

| 10. 5 Gauss Newton One Step Low Impedance Image at 2Hz                | .175 |

| 10. 6 Total Variation Low Impedance Image at 30Hz                     | .176 |

| 10. 7 Total Variation Low Impedance Image at 2Hz                      | .177 |

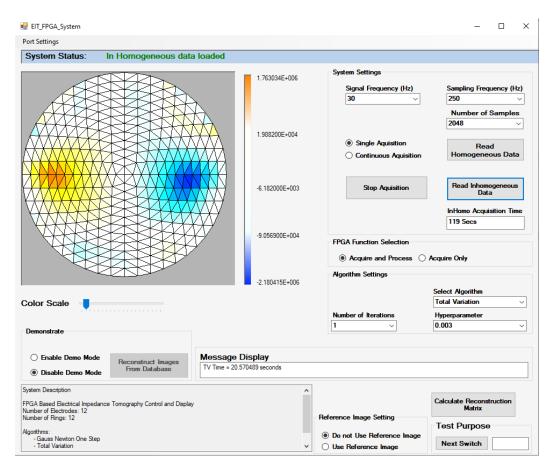

| 10. 8 Impedance change at two locations, with Gauss Newton One Step   | .179 |

| 10. 9 Impedance change at two locations, with Total Variation         | .180 |

| 10. 10 FPGA Design Device Utilization Report                          | .181 |

| 10. 11 FPGA Design Timing Summary                                     | .182 |

| 10. 12 Phantom holes measurements                                     | .185 |

| 10. 13 Low Impedance Anomaly detection                                | .186 |

#### **Chapter 1: Introduction**

Electrical Impedance Tomography (EIT) is the imaging technique that uses internal conductivity distribution to form an image of the medium. The EIT technology is being studied and improved for the last four decades[1]. In EIT, internal conductivity is estimated with the help of electrodes attached to the surface of the subject. A specific current is injected through one pair of the electrodes, and induced voltages are measured through the remaining electrodes. These current and voltage measurements are used to calculate the conductivity distribution over the internal area, which then can be used to form a tomographic image.

Electrical Impedance Tomography has various applications in the fields such as biomedical, geophysical, and industrial. EIT application is also being studied for semiconductor manufacturing, nanotechnology, and chemical engineering [2]. In the biotechnology field, the EIT is used for biological cell imaging.

### **1.1 EIT in Biomedical Applications**

Electrical Impedance Tomography imaging usage in healthcare is due to the fact that biological tissues have electrical properties. In EIT imaging, the tissue conductivity property is studied. A simple electrical model of a tissue constitutes a resistance and a capacitance; thus, the tissue conductivity varies with the frequency at lower range (<100kHz). Moreover, tissue conductivity depends on fluid content and ion concentration [3], hence different tissues show different conductivity. This makes it feasible to form the tomographic image of the internal of the body part of interest. Table 1.1 shows typical resistivity of some of the body tissues measured at different frequencies [4], [5].

| Tissue              | Resistivity (Ω-m) | Frequency |

|---------------------|-------------------|-----------|

| Muscle              | 2-4               | 10kHz     |

| Fat                 | 20                | 10kHz     |

| Lungs               | 10                | 10kHz     |

| Blood               | 1.6               | 10kHz     |

| Bone                | >40               | 10kHz     |

| Cerebrospinal Fluid | 0.80              | 50kHz     |

| Gray Matter         | 3.51              | 50kHz     |

| White Matter        | 3.91              | 50kHz     |

Table 1. 1 Typical Tissue Resistivity [4], [5]

Moreover, the EIT imaging is performed non-invasively and uses low alternating currents. If compared to the available imaging techniques such as CT or PET scan which uses ionizing radiation, or MRI which uses strong magnetic fields, EIT is much safer for the patient. EIT, unlike CT or MRI, can be used at the bedside of the patient. The instrumentation required to perform EIT makes it feasible to apply it to the patient on the bed and hence the visualization of tomographic image of the body part can be performed continuously. This advantage makes long term monitoring of the condition possible [4]. The most studied application of EIT is lung ventilation monitoring [3], [6]. The impedance change within lungs during the ventilation cycle is used to monitor the lung functioning. Another important application is brain imaging. The conditions such as cerebral ischemia , brain hemorrhage can be monitored using EIT, since the change in blood flow changes the conductivity[7]. Other notable applications of EIT which are under research are breast imaging, pediatric lung and cranial imaging[2]. During recent years, applications of EIT are also being explored in wearable healthcare systems[8].

Despite the potential benefits of EIT imaging in biomedical applications, it does not provide the spatial resolution as provided by more popular imaging techniques such as CT or MRI. There is an intensive research work being performed continuously in this area since last few decades. There are multiple algorithms proposed and implemented for improving the quality of reconstrued image. Moreover, there are various medical equipment manufacturers who are providing commercial EIT imaging systems [3], for instance, PulmoVista 500 by Drager or LuMon by Sentec.

# **1.2 FPGA for EIT Image reconstruction System**

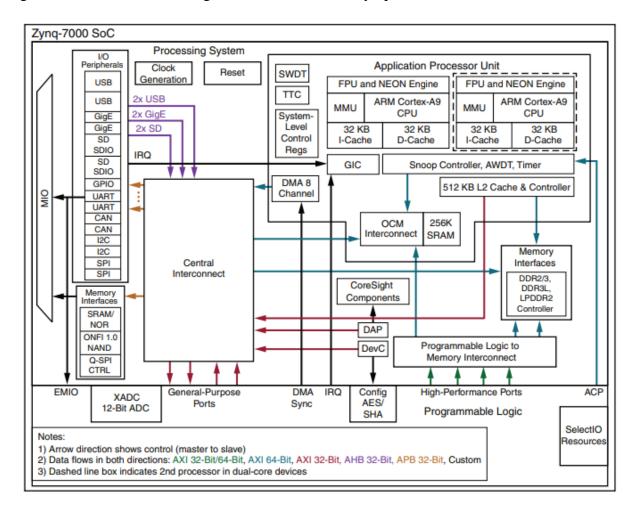

FPGAs are increasingly being used for implementing computationally complex designs. FPGAs provide high speed programmable logic arrays which can be used for parallel processing logic implementations. The Xilinx provided Zynq SoCs includes a single or dual core high performance ARM Cortex A9 based processor (PS) and high-performance programmable logic. It allows users to combine the computational power of processor and FPGA to develop efficient designs. Additionally, the SoCs provide a cost-effective solution as compared to fast processors and DSPs.

The SoC based EIT image reconstruction system[9] may provide a cost-effective solution for the parallel processing required by a EIT system.

### 1.3 Objectives

In this project, the feasibility of implementing EIT image reconstruction algorithms using parallel processing provided by FPGA is explored. A standalone and efficient EIT system for

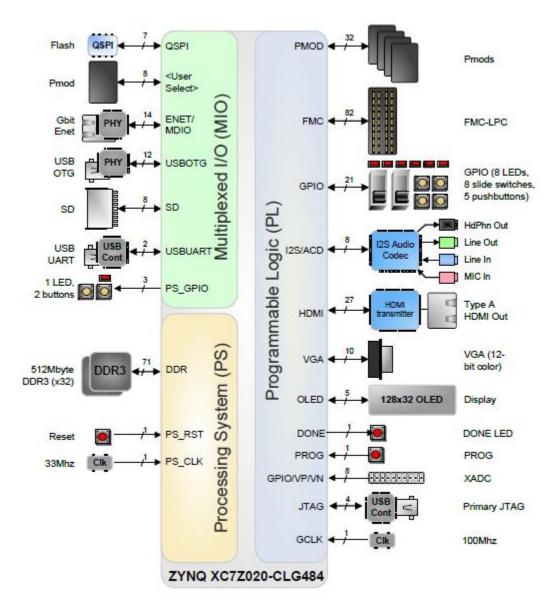

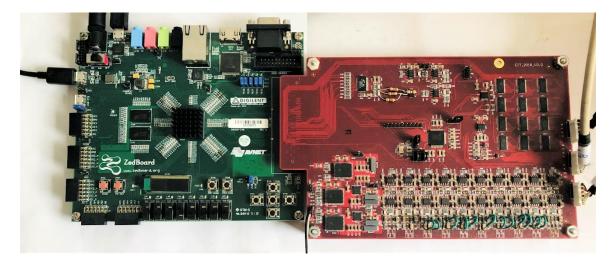

biomedical applications can be developed. A phantom made using animal skin gelatin is used as a body of interest, for the test purpose. A custom designed Analog Front End, designed by one of the senior design teams in Department of Electrical Engineering, St. Cloud State University is used. A Xilinx Zynq SoC development board, Zedboard is used as a controller and the image data processor. A graphical user interface (GUI) is designed using C# windows form application. For image reconstruction, two algorithms, Gauss Newton One Step and Total Variation are developed. The complete work can be divided as follows

- Study EIT Image Reconstruction Methods: It includes the study of Electrical Impedance Tomography methods and algorithms. It also includes the study of finite element method and its application in EIT. Two image reconstruction algorithms, Gauss Newton One Step and Total Variation are studied.

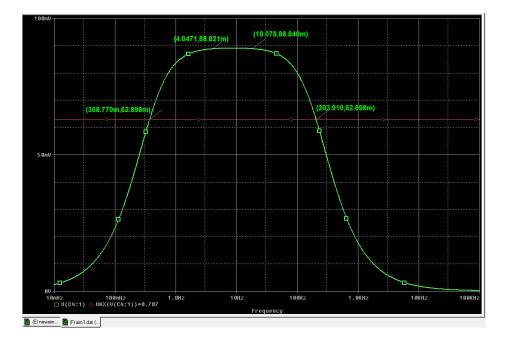

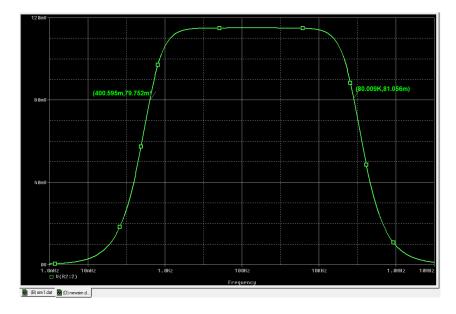

- 2) Study and Modify the Available Analog Front End Board: The AFE board designed by a senior design team, is designed to work with a frequency range of 100Hz to 100kHz. The AFE is modified to be able to work at lower frequency range from 1Hz to 30Hz. The EIT imaging at lower frequencies can be helpful in the cases like tissue edema.

- 3) Implement the Signal Generation and Acquisition Logic in FPGA: The AFE board includes a DAC to transmit the driving signal to the phantom and ADC to read the induced potential on the surface potential. The FPGA design for sinusoidal signal generation at various frequencies and data acquisition at different sampling rates is designed.

- 4) Develop a Communication Protocol for Serial Communication: The FPGA design requires few parameter settings transferred from GUI as well as the resulting image data is to be sent

to GUI for display. There is a serial communication link between Zynq SoC and GUI. A communication protocol is designed to transfer the data between GUI and Zynq SoC.

- 5) Implement the Gauss Newton One Step Algorithm: The one step image reconstruction algorithm, Gauss Newton One Step is developed in FPGA. The design is PS/PL co-design. The reconstruction algorithm is stored in PS DDR and transferred to PL for computation as per requirement.

- 6) Implement the Total Variation Algorithm: An iterative algorithm, Total Variation is developed in Zynq PS and PL. It is also a PS/PL co-design. Some part of the computation is developed in PS and some part of the computation is performed in PL.

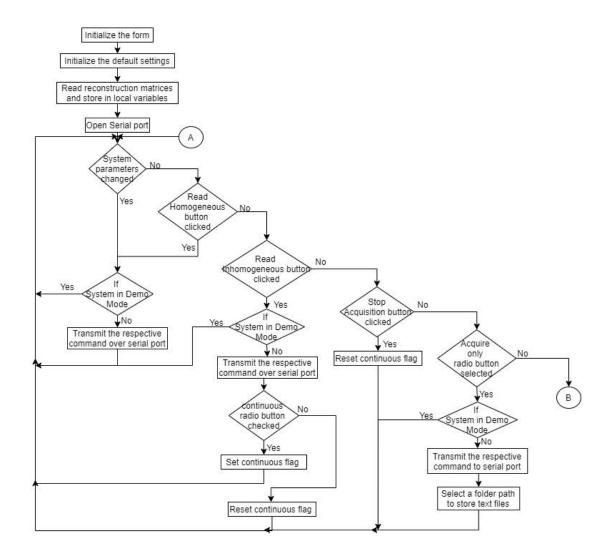

- 7) Design a C# Graphical User Interface: A GUI is developed using C# windows form application. The GUI can communicate with FPGA over serial port for transferring data to and from FPGA. It also includes the display of image data using finite element mesh.

- 8) Implement the Gauss Newton One Step and Total Variation Algorithms in C# Software: The Gauss Newton One Step and Total Variation algorithms are developed in software. This way, the FPGA can only be used for data acquisition. Also, further computationally complicated reconstruction algorithms can be developed in software.

- 9) Test the Complete System for Different settings: Experiments using different parameters such as different frequencies, number of samples, type of algorithms etc. are performed and results are analyzed.

# 1.4 Thesis Organization

Chapter 1, Introduction, includes a brief introduction of EIT imaging technique and its applications in biomedical. It also includes the project objectives description.

Chapter 2, Electrical Impedance Tomography, includes mathematical background for an EIT image reconstruction problem. It includes the finite element model, Jacobian Matrix, Prior techniques, and the image reconstruction algorithms. Two algorithms, Gauss Newton One Step and Total Variation algorithm are introduced.

Chapter 3, Previous work study, includes the review of the EIT projects performed by previous St. Cloud State University students. Two of the projects are software implementation using C# and one of the projects is an FPGA based standalone EIT system development.

Chapter 4, EIT EIDORS Implementation, includes a design description of a MATLAB code designed to study the EIT image reconstruction.

Chapter 5, Xilinx Development Hardware and Software includes the details of the FPGA development board used in this project. The Xilinx Zynq SoC based Zedboard is used. The Zynq SoC architecture and the Xilinx provided development software, VIVADO IDE is also discussed.

Chapter 6, EIT System Architecture, includes a block wise description of the complete EIT system developed in this project.

Chapter 7, Analog Front End, includes the description of the analog front-end hardware design developed by a senior design team. It also includes the design upgrade implementation done for the AFE to work at lower frequencies.

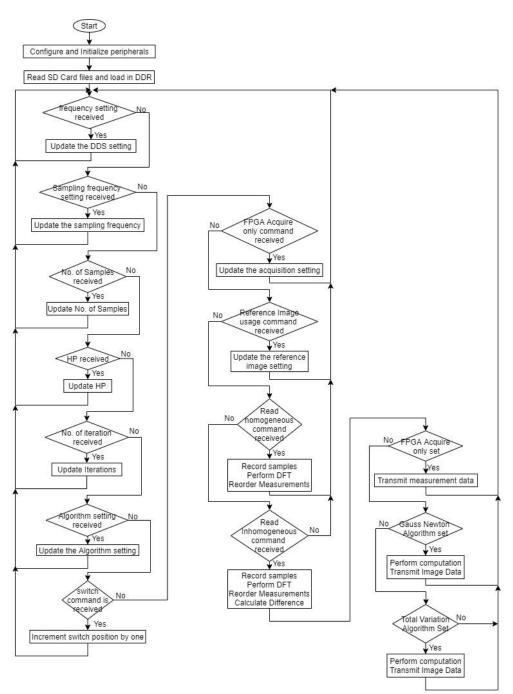

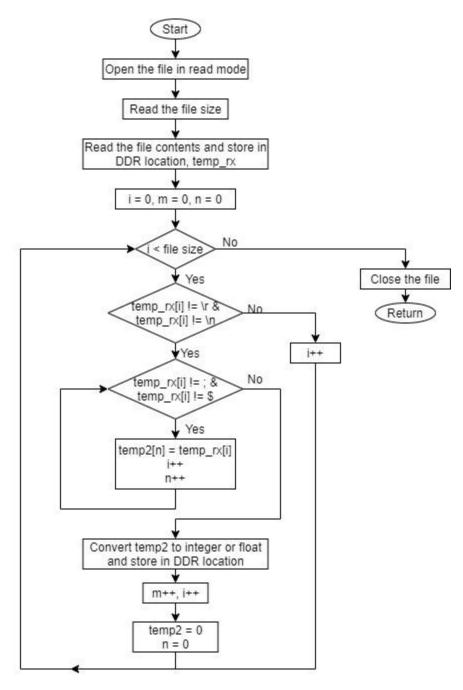

Chapter 8, FPGA Design Development, includes a detailed design report of the FPGA design. The Zynq SoC constitutes of FPGA and processor, this chapter covers the FPGA design as well as processor design developed in this project.

Chapter 9, Graphical User Interface Design and Development includes the detailed GUI front end design. The software design and communication protocol are discussed.

Chapter 10, Experiments and Results, includes the tests performed for validation of the various design aspects of the project.

Chapter 11, Discussion and Conclusion includes the discussion about the complete project work and the results obtained.

At the end, the SDK code and C# GUI code flowcharts are given in the appendix. It also includes a MATLAB code which was designed for a study during the preliminary work

#### **Chapter 2: Electrical Impedance Tomography**

In this chapter Electrical Impedance Tomography (EIT) technique is introduced with a typical EIT system and the mathematical description. The finite element method, Gauss Newton One Step and Total Variation algorithms are also introduced.

### 2.1 Electrical Impedance Tomography Background

In Electrical Impedance Tomography imaging technique, number of electrodes are placed around the body part of interest, an alternating current of less than ten milliamperes [10] at a frequency of up to 100kHz is applied through a pair of electrodes and resulting potential is recorded on the remaining electrodes. This process is repeated by using all electrodes one pair at a time as a current source. The recorded data is then passed through a mathematical algorithm to reconstruct an image of the internal impedance distribution of the body part of interest. The alternating current level used in EIT should follow the "patient auxiliary current" limit decided by the International Electrotechnical Commission (IEC) [10]. According to this standard, for frequency range from 0.1 Hz to 1 kHz, the current should be limited to 100  $\mu$ A, from 1kHz to 100kHz it should be 100*f*  $\mu$ A, where *f* is the frequency in kHz and from 100kHz and above it should be 10mA [4], [10].

The challenge in EIT image reconstruction problem is that the electric current passed through one electrode pair travels three dimensionally along the path of least resistivity [11]. This may affect the resulting voltage measurements at the other electrodes. In most available literatures, even though the data is collected from a three-dimensional body, an EIT image was reconstructed with an assumption that the body was two dimensional [11]. Thus, the reconstructed image does not really represent the true distribution of the conductivities of the body. In addition, the algorithm solved an inverse problem, thus solution is not unique. Calculating the conductivity distribution of the interior of the body of interest with known applied current and measured voltages at the boundary, makes the image reconstruction as inverse problem[11]. However, if the applied current and impedance distribution are known, the voltage can be calculated, it is called as the forward problem. In EIT image reconstruction, at first, an internal impedance distribution is assumed, and a forward model is generated, which can estimate the boundary voltages with given applied current and impedance distribution. The calculated voltages are compared to the measured voltages. Depending upon the difference between measured voltages and calculated voltage the impedance distribution is adjusted, and the process is repeated until the difference between actual and calculated voltages reduces to the acceptable level.

The forward problem is governed by partial differential equation. Hence, to solve the forward problem, numerical techniques such as finite element method (FEM), finite difference method (FDM) or boundary element method (BEM) can be used [12] [13]. The FEM divides a large system into smaller parts called as finite elements which can be polygons, whereas, the BEM requires for the object under investigation to have homogeneous conductivity distribution and the FDM uses the rectangular geometry. Hence, in clinical EIT, finite element method is preferred as it can model irregular and nonhomogeneous geometries more precisely.

With the help of forward model, a regularized non-linear solver can be used to obtain a unique and stable inverse solution. In last few decades various image reconstruction techniques and algorithms for EIT image reconstruction have been proposed and implemented. Those algorithms include modified newton Raphson [13], back projection, Gauss-Newton one step algorithm, Graz consensus Reconstruction algorithm for EIT (GREIT), conjugate gradient method, Total Variation etc. Artificial Neural Networks and Deep Learning are also getting studied for EIT image reconstruction in order to improve image quality [14]. There is an open source software EIDORS (Electrical Impedance and Diffused Optical Reconstruction Software) developed using MATLAB which can be used for forward and inverse modelling for EIT image reconstruction [15].

There are two imaging techniques in EIT, difference imaging and static imaging [4], [13]. In difference imaging, there are two subcategories, time difference and frequency difference. In time difference technique, the change in tissue conductivity measured at two different instances is calculated. This change is back projected to form an image showing changes in the conductivity distribution happened between two instances. In frequency difference imaging, the change in tissue conductivity at two different frequencies is calculated. Frequency difference technique is based on the fact that different tissues have different frequency response [14]. In static imaging, the absolute values of conductivity distribution are calculated and used to form an image. As mentioned above, there have been numerous algorithms studied and implemented to reconstruct the impedance distribution image. The imaging algorithms can be classified as iterative and non-iterative. The impedance image reconstruction is a non-linear problem since the internal impedance distribution is unknown, hence an iterative method could give the best result [4], but it would be computationally more expensive. In this project, two algorithms using time difference imaging are implemented, a one step that is non-iterative Gauss Newton One Step and iterative Total variation algorithm.

### 2.1.1 Advantages/Disadvantages of EIT

The Electrical Impedance Tomography is performed non-invasively. It uses up to ten milliamperes of alternating current [10] to inject through the body of interest to measure the induced potential and build the relative impedance image. This technique is less harmful as compared to the available imaging techniques such as Computed Tomography (CT) or Magnetic Resonance Imaging (MRI). CT uses ionizing radiation whereas MRI uses strong magnetic fields, both of which can be harmful for longer exposures to the patient. Because the EIT imaging technique uses few milliamperes current, it can be used for long term patient monitoring, for instance in cases where continuous lung ventilation needs to be monitored. The EIT systems mostly include hardware to generate low level constant current source, a data acquisition hardware and a computer for processing acquired data from multiple channels. This makes EIT systems portable. Another very important advantage is that EIT technique has faster imaging capabilities. Some of the commercially available EIT systems provide 40 images/seconds frame rate [3]. Real time imaging can be made possible due to such temporal resolution.

The major disadvantage of EIT systems is the technique has lower spatial resolution. In the EIT image reconstruction problem there can be a very small change on the surface potential for a large change in conductivity inside the body of interest. Also the final solution is very sensitive to noise introduced due to measurement artifacts [16].

# 2.1.2 Typical EIT System

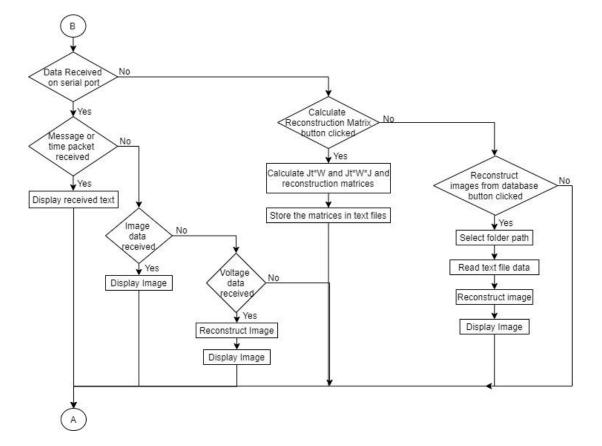

This section includes the description of typical EIT system. Figure 2.1 shows the block diagram

Figure 2. 1 Typical EIT System Block Diagram

The EIT system can be divided into two parts such as data acquisition and data processing. Following is the description of both parts in brief.

# 1. Data Acquisition and Control

As described above, in EIT, number of electrodes are placed on the surface of the subject of interest. To retrieve the internal conductivity distribution, an alternating current is applied to a pair of electrodes and resulting voltages on remaining electrodes are recorded. The current application is repeated in a pattern for other electrodes and respective voltages are recorded. For achieving this functionality, a current source is required. The current source is to be connected to different electrodes, in a pattern, hence a multiplexer can be used to connect one current source to a pair of electrodes. Similarly, the voltage readout from the remaining electrodes also needs to be taken from different electrodes in a pattern, hence a multiplexer can be used to choose which electrode to be connected to ADC. The multiplexers can be controlled through a microcontroller or a microprocessor. The controller needs to be used to control the system functionality as well as to transfer the acquired measurement data to the software for processing. The link between controller and software system can be wired or wireless.

### 2. Data Processing and Display

In EIT, the software system or a Graphical User Interface is required to set the parameters such as number of electrodes and current application pattern for the acquisition. The main functionality of the software should be to store the voltage measurements, run the image reconstruction algorithms and display the results. The typical EIT system software operational flow would include setting up the system parameters, creating a forward model, acquiring, and storing the measurement data, solving for the inverse solution, and displaying the reconstructed image.

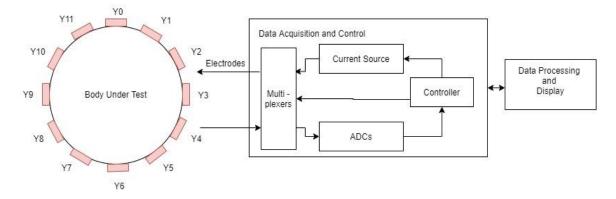

### 2.1.3 Stimulation and Measurement Patterns

When a current is applied using two electrodes on a surface of a body with homogeneous impedance distribution, it forms equipotential distribution inside the body. If there is a change in the impedance distribution the potential distribution varies accordingly, hence changing the potential on the boundary. Due to this the injected current and measured boundary potential can be used to approximate the impedance distribution of the internal of the body.

There are two current injection patterns, multiple electrode current drive and pair electrode current drive [4], [14]. In multiple electrode current drive pattern, the current is applied

to more than two electrodes and the potential is measured on all the electrodes. This current pattern is repeated till the current is injected through all the electrodes. This way the current density inside the body increases which also increases the sensitivity towards the impedance distribution measurements[4]. However, this method is not cost effective as well as it complicates the hardware design.

The pair electrode current drive is typically implemented in two ways, adjacent current drive, and opposite current drive. In adjacent current drive, the current is injected between two adjacent electrodes, as shown in figure 2.2 (a) and voltage is measured between remaining adjacent electrode pairs. This sequence is repeated till the current is injected through all the electrodes. Another pair electrode current drive type is opposite or pseudo-polar drive pattern [17]. In this drive pattern the current electrode pair is selected as opposite, as shown in figure 2.2 (b). The voltage is measured at the adjacent electrodes. In this project the opposite current drive pattern is used.

Figure 2. 2 Stimulation Pattern for Electrode Pair

### 2.2 Mathematical Background

In EIT, the problem is to reconstruct the internal conductivity distribution with the help of known applied current and measured voltages on the surface. In this section, the mathematical model required to solve the said problem is discussed.

In case of clinical EIT, the applied current is known, and the induced voltages are measured. From available current and voltage values, internal conductivity distribution is to be calculated, this makes it as an inverse problem. Moreover, according to Hadamard [14], a mathematical model of a physical problem is well posed if it satisfies the following conditions

- 1. A solution exists for all admissible data

- 2. The solution is unique for all the admissible data

- 3. The solution continuously depends on the data

In case of the EIT problem, there are more unknowns than the known parameters. Because of this a unique solution may not exist. Also, for any given measurement precision, the change in conductivity precision may be arbitrarily large and may go undetected. This makes the problem ill-posed[11]. To find a practical solution for this problem it is regularized using regularization methods. Also, for improving the situation of data dependency, some additional information about conductivity distribution is introduced. This a priori information constraints the solution and brings stability to the solution.

Mostly, the conductivity calculation is approached in two steps, forward problem, and inverse problem. If the current applied to the body is known along with conductivity distribution and voltage is to be calculated, it is called as forward problem. If the current applied and voltage measured is known and conductivity distribution is to be calculated, it is called as inverse problem.

In the following section, the mathematical expression behind forward and inverse problem are discussed.

### 2.2.1 Forward Problem

For solving EIT forward problem, a forward model is built in which the initial conductivity of the body is assumed. With the help of applied current and assumed conductivity, the boundary voltage is calculated. This computation is based on electromagnetism [7], [18].

In EIT computation, the low frequency signals are used so that the static field assumptions can be used[7], [18], [19]. This is because at low frequencies the wavelength is much greater than the dimension of a body of interest [7]. It is also assumed that the internal conductivity distribution is not affected by the electromagnetic field density, hence the conductivity anywhere can be treated as scalar [19].

The Maxwell's equations [19] for electric field E and magnetic field H in point format are given as follows

$$\nabla X E = -\frac{\partial B}{\partial t} \tag{2.1}$$

$$\nabla X H = \frac{\partial D}{\partial t} + J \tag{2.2}$$

where,

B = Magnetic flux

D = Electric Displacement

$$J = Current density$$

Using Ohm's law, the internal current density J in terms of electric field [20]is given by

$$J = \sigma E \tag{2.3}$$

where,  $\sigma$  is the internal conductivity distribution.

In case of EIT, the dimension of the object under investigation is much smaller than the wavelength of the signal applied, for example, if the applied signal frequency is 10 kHz the wavelength would be  $3x10^4$  meters. This makes the dimension of the object under investigation <1% of the signal wavelength. Hence, the internal electric field can be considered as static and can be defined in terms of the scalar potential (V) as follows

$$\mathbf{E} = -\nabla \mathbf{V} \tag{2.4}$$

where, V represents the scalar potential distribution within the field. Combining equations 2.4 and 2.3, we get

$$\mathbf{J} = -\sigma \nabla \mathbf{V} \tag{2.5}$$

If it is considered that there are no internal current sources [20], we get

$$\nabla J = 0 \tag{2.6}$$

Combining equations 2.5 and 2.6, we get

$$\nabla . \, \sigma \nabla \, \mathbf{V} = \mathbf{0} \tag{2.7}$$

Equation 2.7 is the partial differential equation (PDE) which dominates the EIT problem [21]. For a domain  $\Omega(x, y, z)$ , the equation 2.7 can also be written as

$$\frac{\partial}{\partial x}\sigma \frac{\partial V}{\partial x} + \frac{\partial}{\partial y}\sigma \frac{\partial V}{\partial y} + \frac{\partial}{\partial z}\sigma \frac{\partial V}{\partial z} = 0$$

(2.8)

For equation 2.7 to have a unique solution, the boundary condition needs to be defined [19]. If  $\partial \Omega$  represents the boundary, applying the Gauss's theorem for conservation of current [19], [20], we can write

$$\int_{\partial\Omega} j = 0 \tag{2.9}$$

where, j is the current density at the boundary. The current density at the boundary is given as [20]

$$\mathbf{j} = -\mathbf{J} \cdot \mathbf{n} \tag{2.10}$$

where, n is an outward unit normal to the boundary  $\partial \Omega$ . Using equation 2.5, equation 2.10 can also be written as

$$\mathbf{j} = \sigma \nabla \mathbf{V}.\mathbf{n} \tag{2.11}$$

Equation 2.7 and 2.11 represent the EIT forward problem [19], with the help of known conductivity and known applied current, the potential distribution V can be calculated.

### 2.2.2 Inverse Problem

The goal behind solving the inverse problem is to get the unknown internal conductivity distribution with the help of measured voltages and simulated voltages. By solving the forward problem, the simulated voltages at the boundary can be calculated. If  $V_m$  is the measured voltages at the boundary, then the solution can be approached by minimizing the difference between measured voltages and simulated voltages

$$V_m - F(\sigma) \approx 0 \tag{2.12}$$

where, F(.) is the forward operator which gives the simulated voltages which depends upon the conductivity distribution  $\sigma$ .

If  $F(\sigma)$  can be approximated by using Taylor series and considering only first order approximation, we get

29

$$F(\sigma) \approx F(\sigma_0) + \frac{\partial F(\sigma_0)}{\partial \sigma} (\sigma - \sigma_0)$$

(2.13)

where  $\sigma_0$  is the assumed initial estimation. Equation 2.13 can be written as

$$F(\sigma) \approx F(\sigma_0) + \boldsymbol{J}(\sigma - \sigma_0)$$

As  $J = \frac{\partial F(\sigma_0)}{\partial \sigma}$  is the Jacobian matrix of *F* calculated at  $\sigma_0$ . Hence, equation 2.12 can be re-written

as

$$V_m - F(\sigma_0) - J(\sigma - \sigma_0) \approx 0 \tag{2.14}$$

Putting  $\Delta V = V_m - F(\sigma_0)$ , which shows the variation in the measured potentials for change in conductivity [17], and  $\Delta \sigma = \sigma - \sigma_0$ , which shows the change in conductivity, then equation 2.14 becomes

$$\Delta \mathbf{V} \approx \mathbf{J} \Delta \sigma \tag{2.15}$$

Which gives

$$\Delta \sigma \approx \mathbf{J}^{-1} \Delta \mathbf{V} \tag{2.16}$$

Since Jacobian matrix is mostly not invertible, equation 2.16 is solved by minimizing the least squares errors as follows [19]

$$\Delta \sigma_{LS} = argmin(\|\mathbf{J}\Delta \sigma - \Delta \mathbf{V}\|^2) \tag{2.17}$$

Which gives, [19]

$$\Delta \sigma_{LS} = (\boldsymbol{J}^T \boldsymbol{J})^{-1} \boldsymbol{J}^T \Delta \boldsymbol{V}$$

(2.18)

Here, since there are a greater number of unknown conductivity elements than the known boundary measurements, the problem is ill-conditioned[19]. For getting a unique solution to this, regularization is needed. Regularization is a technique used to find more stable but approximate solution by applying a prior information. There are several regularization methods, but in EIT application Tikhonov regularization is commonly used[11]. It adds a regularization parameter with prior information.

Hence, equation 2.18 becomes [17]

$$\Delta \sigma = (\mathbf{J}^T \mathbf{J} + \lambda^2 R^T R)^{-1} \mathbf{J}^T \Delta \mathbf{V}$$

(2.19)

Where,  $\lambda$  is called as the hyperparameter or regularization parameter and R is the regularization matrix, which controls the smoothness of the solution [17]. There are various methods to calculate the regularization matrix R, for example, NOSER, Laplace, Tikhonov etc.

#### **2.3 Finite Element Method**

Finite element method (FEM) is a numerical method used to solve problems that are described by partial differential equations [22], [23]. In EIT, forward problem is solved with the help of finite element method [11]. An area under investigation is discretized as a group of non-overlapping finite elements such as triangles or quadrilaterals. In other words, a continuous physical problem is converted into discretized finite element problem with unknown nodal values. The process of analyzing any problem with finite element method [19], [23] involves

- Dividing the solution region into finite elements, also called as finite element mesh. The output of mesh generation consists of arrays of nodal coordinates.

- Selecting the interpolation functions to interpolate the field variables over the element.

- Deriving the equations for elements which relates the nodal values of the unknown function to other parameters.

- Finding the global equation system for the complete solution region by assembling the element equations.

- Solving the global equation system

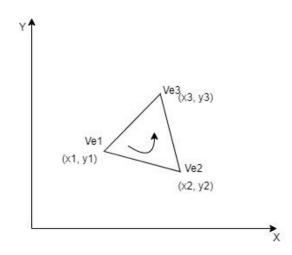

Consider, a domain is divided into finite number of triangles and the triangle shown in figure 2.3 represents an element in the finite element model with vertices denoted by node1 (x1, y1), node2 (x2, y2) and node3 (x3, y3). The problem statement here is to find the approximation for the potential  $V_e$  within an element e. The potential for each element then can be interrelated to find the approximate solution for the complete region.

Figure 2. 3 Typical Triangular Element in 2D problem

If the solution region is divided into N number of triangular elements, the approximate potential for the whole region can be represented as[24]

$$V(x, y) = \sum_{e=1}^{N} V_e$$

(2.20)

The common form of approximation for V within a triangular element is polynomial approximation as follows

$$V_e(x, y) = a + bx + cy \tag{2.21}$$

From equation 2.21, the potential at  $V_{e1}$ ,  $V_{e2}$ ,  $V_{e3}$  at the triangular element nodes 1,2 and 3 can be written as

$$\begin{bmatrix} V_{e1} \\ V_{e2} \\ V_{e3} \end{bmatrix} = \begin{bmatrix} 1 & x1 & y1 \\ 1 & x2 & y2 \\ 1 & x3 & y3 \end{bmatrix} \begin{bmatrix} a \\ b \\ c \end{bmatrix}$$

(2.22)

The coefficients a, b and c can be determined using equation 2.22 as follows

Solving for inverse of the coordinate matrix and substituting resulting equation into equation 2.21,

we get

$$V_{e}(x,y) = \begin{bmatrix} 1 & x & y \end{bmatrix} \frac{1}{2A} \begin{bmatrix} (x1y3 - x3y2) & (x3y1 - x1y3) & (x1y2 - x2y1) \\ (y2 - y3) & (y3 - y1) & (y1 - y2) \\ (x3 - x2) & (x1 - x3) & (x2 - x1) \end{bmatrix} \begin{bmatrix} V_{e1} \\ V_{e2} \\ V_{e3} \end{bmatrix}$$

(2.24)

where, A is the area of the element and given as

$$2A = \begin{vmatrix} 1 & x1 & y1 \\ 1 & x2 & y2 \\ 1 & x3 & y3 \end{vmatrix}$$

(2.25)

For the value of area A to be positive, the nodes numbering should be done counter clock wise as shown in figure 3 with arrow [23].

Equation 2.24 can also be written as

$$V_e = \sum_{i=1}^{3} \alpha_i(x, y) V_{ei}$$

(2.26)

where,

$$\alpha_1 = \frac{1}{2A} \left[ (x^2y^3 - x^3y^2) + (y^2 - y^3)x + (x^3 - x^2)y \right]$$

(2.27a)

$$\alpha_2 = \frac{1}{2A} \left[ (x_3y_1 - x_1y_3) + (y_3 - y_1)x + (x_1 - x_3)y \right]$$

(2.27b)

$$\alpha_3 = \frac{1}{2A} \left[ (x_1y_2 - x_2y_1) + (y_1 - y_2)x + (x_2 - x_1)y \right]$$

(2.27c)

Here,  $\alpha_i$  are the linear interpolation functions and called as element shape functions [24]. Equation 2.26 defines the potential within the triangular element as a function of the values of the potential at the element's three nodes.

From equation 2.7, EIT partial differential equation, if  $V_E$  is the actual solution and  $V_{FEM}$  is the approximate solution found by FEM, then [24]

$$\nabla . \, \sigma \nabla V_{FEM} - \, \nabla . \, \sigma \nabla V_E = R \tag{2.28}$$

where, R is the residual. Hence,

$$\nabla . \, \sigma \nabla V_{FEM} = R \tag{2.29}$$

As,

$$\nabla . \sigma \nabla V_E = 0$$

and  $\nabla . \sigma \nabla V_{FEM} \approx 0$ .

In the weighted residuals method, the weighted sum of the residuals over all the elements can be zero if proper weight can be found. Hence, the integral of the weighted residual over the medium  $\Omega$  will be zero [24].

$$\int_{\Omega} WRd\Omega = 0 \tag{2.30}$$

where, W is defined [24] as

$$W = \sum_{i=1}^{n} w_i \,\alpha_i \tag{2.31}$$

where,  $\alpha_i$  represents the shape functions for the element, and  $w_i$  are the weight coefficients, and n is the dimension of the element. Putting equation 2.29 in 2.30, we get

$$\int_{\Omega} W(\nabla .\, \sigma \nabla V_{FEM}) d\Omega = 0 \tag{2.32}$$

Rearranging and solving equation 2.32 by following the procedure given in [24], equation 2.32 can be written for k<sup>th</sup> element, assuming conductivity  $\sigma_k$  is constant along the element, we get

$$\int_{\mathbf{E}_k} \sigma_k \nabla V_e \cdot \nabla W d\Omega = \sigma_k \sum_{i=1}^3 V_{ei} \sum_{j=1}^3 w_j \ \mathcal{C}_{ij}^k$$

(2.33)

where,  $C_{ij}^k$  is called as the stiffness matrix for element k.

$$C_{ij}^{k} = \int_{\mathbf{E}_{k}} \nabla \alpha_{i} \cdot \nabla \alpha_{j} d\Omega$$

(2.34)

For entire mesh, equation 2.33 would be [24]

$$\int_{\Omega} \sigma_k \nabla V_e \cdot \nabla W d\Omega = \sum_{E=1}^N \sigma_k \sum_{i=1}^3 V_{ei} \sum_{j=1}^3 w_j C_{ij}^k$$

(2.35)

where, N is the total number of elements.

To calculate stiffness matrix, using equations 2.27a, 2.27b and 2.27c, we have

$$\alpha_1 = \frac{1}{2A} \left[ a_1 + b_1 x + c_1 y \right]$$

(2.36a)

$$\alpha_2 = \frac{1}{2A} \left[ a_2 + b_2 x + c_2 y \right]$$

(2.36b)

$$\alpha_3 = \frac{1}{2A} [a_3 + b_3 x + c_3 y]$$

(2.36c)

where,

$$a_1 = x2y3 - x3y2$$

;  $b_1 = y2-y3$ ; and  $c_1 = x1 - x3$

$a_2 = x3y1 - x1y3$ ;  $b_2 = y3 - y1$ ; and  $c_2 = x1 - x3$

$$a_3 = x_1y_2 - x_2y_1$$

;  $b_3 = y_1 - y_2$ ; and  $c_3 = x_2 - x_1$

Using equation 2.36a, 2.36b and 2.36c, the elemental stiffness matrix  $K^e$  is given as follows [24]

$$K^{e} = \frac{\sigma_{e}}{4A_{e}} \begin{bmatrix} b_{1}^{2} + c_{1}^{2} & b_{1}b_{2} + c_{1}c_{2} & b_{1}b_{3} + c_{1}c_{3} \\ b_{2}b_{1} + c_{2}c_{1} & b_{2}^{2} + c_{2}^{2} & b_{2}b_{3} + c_{2}c_{3} \\ b_{3}b_{1} + c_{3}c_{1} & b_{3}b_{2} + c_{3}c_{2} & b_{3}^{2} + c_{3}^{2} \end{bmatrix}$$

(2.37)

Assembling all the elemental stiffness matrices the Global Stiffness matrix K is formed and following system of equations is derived [24], [25]

$$[K]_{nxn}[V]_{nx1} = [I]_{nx1}$$

(2.38)

where,  $[V]_{nx1}$  is the matrix of potentials at all the nodes and  $[I]_{nx1}$  is the matrix of currents at all the nodes. Equation 2.38 can be written as

$$[V]_{nx1} = [K]_{nxn}^{-1} [I]_{nx1}$$

(2.39)

# 2.4 Jacobian Matrix

Jacobian matrix, in case of EIT, provides the relationship between voltage distribution on the region of interest's surface and the regions internal conductivity distribution[26]. Jacobian matrix is calculated using FEM, current injection pattern and electrode position[27]. A standard method to calculate Jacobian matrix is proposed in [25]. In this method, the Jacobian matrix is derived by differentiating equation 2.39 with respect to conductivity  $\sigma$  [25], we get

$$\mathbf{J} = \frac{\partial \mathbf{V}}{\partial \sigma_j} = -\mathbf{K}^{-1} \cdot \frac{\partial \mathbf{K}}{\partial \sigma_j} \cdot \mathbf{K}^{-1} \mathbf{I}$$

(2.40)

Which can be written as

$$\mathbf{J} = \frac{\partial \mathbf{V}}{\partial \sigma_j} = -\mathbf{K}^{-1} \cdot \frac{\partial \mathbf{K}}{\partial \sigma_j} \cdot \mathbf{V}$$

(2.41)

If there are M number of boundary measurements and N number of FEM elements, then  $\mathbf{J} \in \mathbb{R}^{M \times N}$ . In this method only stiffness matrix derivative is to be calculated to get  $\mathbf{J}$ .

#### **2.5 EIT Algorithms**

There are various image reconstruction algorithms used for EIT problem solving. There are two imaging techniques in EIT, difference imaging and static imaging. In this project, two algorithms based on difference imaging are implemented, Gauss Newton One step and Total Variation. In this section, both the algorithms are discussed.

#### 2.5.1 Gauss Newton One Step Algorithm

The Gauss Newton One Step solver is based on Gauss-Newton algorithm described in [25] . It is an improvement based on Gauss-Newton algorithm along with statistical consideration and prior information. It is used as a difference method. It uses regularized model to solve EIT inverse problem. The Gauss Newton approach uses the noise variance of the measurements and the covariance of the conductivity distribution for linearized image reconstruction[6]. Using this method, the solution to the inverse problem in EIT is estimated by minimizing [28]

$$\|\boldsymbol{J}\boldsymbol{\Delta}\boldsymbol{\sigma} - \boldsymbol{\Delta}\boldsymbol{V}\|_{\boldsymbol{\Sigma}_{n}^{-1}}^{2} + \|\boldsymbol{\Delta}\boldsymbol{\sigma} - \boldsymbol{\Delta}\boldsymbol{\sigma}_{*}\|_{\boldsymbol{\Sigma}_{m}^{-1}}^{2}$$

(2.42)

Where,  $\Delta \sigma_*$  is the initial estimation which is 0 in case of difference EIT [17].

$\sum_{n}$  is the covariance matrix of the measurement noise n.

$\sum_{m}$  is the expected image covariance. The covariance matrices are normally modeled heuristically from a priori considerations as follows

37

$$W = \xi_n^2 \sum_{n=1}^{n-1} (2.43)$$

And

$$R = \xi_m^2 \ \Sigma_m^{-1} \tag{2.44}$$

where,  $\xi_n$  is the average measurement noise amplitude and  $\xi_m$  is the a priori amplitude of conductivity change.

Here, W models the measurement accuracy and for difference EIT it is Identity matrix (I). R represents the regularization matrix. Various prior calculation methods are available to calculate the regularization matrix R, for example, NOSER, Laplace, Tikhonov etc.

Solving equation 2.42 gives the linearized, one step inverse solution as follows

$$\Delta \sigma = \left( \boldsymbol{J}^T \frac{1}{\xi_n^2} \boldsymbol{W} \boldsymbol{J} + \frac{1}{\xi_m^2} \boldsymbol{R} \right)^{-1} \boldsymbol{J}^T \frac{1}{\xi_n^2} \boldsymbol{W} \Delta \boldsymbol{V}$$

(2.45)

Let's put  $\lambda = \frac{\xi_n}{\xi_m}$ , then equation 2.45 can be written as

$$\Delta \sigma = (\mathbf{J}^T W \mathbf{J} + \lambda^2 R)^{-1} \mathbf{J}^T W \Delta V$$

(2.46)

The hyperparameter  $\lambda$  controls the tradeoff between the resolution and noise attenuation in the resulting image. Usually the hyperparameter is selected heuristically [29]. Few of the reconstructed results generated over a range of hyperparameter values are observed and the one with best result is selected. In this project, the hyperparameter value is used as 0.003, this value is used by the previous students who worked on the EIT image reconstruction project in St. Cloud State University.

### 2.5.2 Total Variation Algorithm

The Total Variation (TV) technique is a regularization method which allows the regularization of discontinuous parameters. The commonly used regularization techniques fall short of describing sharp variations in the reconstructed image whereas TV preserves the edges in reconstructions[30]. In many regularization matrices L2 norm is used which makes the solution biased towards smoother functions. TV uses L1 norm which makes it discontinuous and not differentiable at every point. The total variation of a conductivity image is defined as follows [31]

$$TV(\sigma) = \int_{\Omega} |\nabla \sigma| d\Omega$$

(2.47)

Where,  $\Omega$  is the region of interest. Let us consider the discretized version of the region (FEM), the conductivity is assumed to be piecewise constant over each element [31]. This also means the conductivity  $\nabla \sigma$  is non-zero only on the edges between the elements.

Hence, for the i<sup>th</sup> edge, shared by the FEM elements m(i) and n(i), the difference in conductivity is

$$\left|\sigma_{m(i)} - \sigma_{n(i)}\right| \tag{2.48}$$

The Total Variation of the entire image can be written as the sum of the TV of all the edges

$$TV(\sigma) = \sum_{i} l_{i} \left| \sigma_{m(i)} - \sigma_{n(i)} \right|$$

(2.49)

Where  $l_i$  is the length of the i<sup>th</sup> edge in the mesh.

Equation 2.49 can also be expressed as

$$TV(\sigma) = \sum_{i} |L_i\sigma|$$

(2.50)

Where *L* is the sparse matrix with one row for each edge and each row has two non-zero elements in the columns m(i) and n(i). Hence, the TV is the sum of the absolute values.

# TV algorithm for EIT

There are various algorithms developed for solving TV regularized problems. A few algorithms are described in [30]. For EIT application, Primal and Dual Interior Point Method (PDIPM) and Iteratively Reweighted Least Squares (IRLS) methods are mostly used. PDIPM introduces a smoothness parameter and a dual variable using the Cauchy-Schwartz inequality. [31] provides detailed explanation of PDIPM algorithm implementation for clinical EIT. The IRLS method solves a weighted least squares problem iteratively [32]. Both methods are available in EIODRS.

In this project, the Total Variation algorithm shown by Rabi Gartaula [33] is used. It uses one step Gauss Newton approximation step to find initial solution,  $\sigma_0$ , as follows

$$\Delta \sigma = (\mathbf{J}^T W \mathbf{J} + R^T R)^{-1} \mathbf{J}^T W \Delta V \tag{2.51}$$

For further iterations, a TV regularization parameter is calculated as follows

$$W_{\rm B} = \frac{0.5}{\sqrt{(R * \Delta \sigma)^2 + \beta}}$$

(2.52)

Where,  $\beta$  is a smoothness parameter and kept constant throughout iterations. This parameter is incorporated in equation 2.51 for further iterations, as shown in equation 2.53.

$$\Delta \sigma = \frac{J^T * W * \Delta V}{(J^T * W * J + R^T * W_B * R)}$$

(2.53)

Equation 2.52 and 2.53 are repeated for the set number of iterations.

### **2.6 Prior Techniques**

As mentioned in section 2.2, a prior information is introduced to stabilize the solution of the ill-posed problem[28]. The technique of applying prior information is called as regularization. There are different methods of prior calculation. In this section, three methods such as Tikhonov, NOSER and Laplace are discussed.

#### 2.6.1 Tikhonov Prior

It is the most used method of regularization in EIT inverse solution. The Tikhonov regularization uses differential operators which provides smooth solutions. If the elements of image are considered as independent with identical expected magnitudes, the regularization matrix [19] becomes,

$$R = I \tag{2.54}$$

Where, I is the identity matrix. This is called as zeroth-order Tikhonov regularization. This regularization provides the smooth solutions but does not preserve sudden changes in the image [34]. In this project, Tikhonov prior is used to reduce the complexity of the computation.

## 2.6.2 NOSER Prior

NOSER prior, stands for Newton's One Step Error Reconstruction, is also known as weighted diagonal prior[35]. In NOSER prior the regularization matrix [28] is calculated as

$$R = [diag(\boldsymbol{J}^T \boldsymbol{J})]^P \tag{2.55}$$

Where **J** is the Jacobian matrix. The exponent p needs to be selected carefully to keep balance between solution stability and image contrast [17] and p  $\in$  [0,1].

# 2.6.3 Laplace Prior

Laplace prior is a second order high pass filter[36]. For a finite element mesh, it is defined as -1 for each adjacent element and 3 for the element itself[28]. Hence, edges are preserved in Laplace prior as compared to Tikhonov and NOSER [36]. In other words, it preserves high frequency components such as edges in the image.

#### **Chapter 3: Previous Work Study**

There are few EIT image reconstruction project works performed by past St. Cloud State University students. Three of the projects were studied as a preliminary study for this project. Two of the projects were C# implementation of the EIT image reconstruction algorithms. Third project was FPGA based implementation which included complete EIT data acquisition as well as data processing system[9]. The hardware designed in FPGA based project is used in this project, with some modifications. In this chapter, a brief description of each project functionality and design is given.

#### 3.1 Study on human brain Activity and electrical impedance tomography [19]

#### 3.1.1 Design Description

It is a C# implementation of Gauss-Newton one step algorithm for EIT image reconstruction. Tikhonov, Laplace and NOSER priors are implemented. A graphical user interface (GUI) provides user with the options to set the available system parameters. The parameters required for FEM settings, stimulation, measurement data, prior selection and image reconstruction algorithm can be set through GUI. The measurement data that is the homogeneous and inhomogeneous data taken from a phantom and stored in text files is used to test the code. The C# implementation is designed by following the open source MATLAB implementation EIDORS.

For building finite element model (FEM), number of electrodes and number of rings is taken as input. The FEM is designed as a 2D circular model and discretized according to the number of rings entered by the user. There is a class defined to handle FEM model generation and it provides the model's nodes coordinate data, element assembly data and electrode positioning matrix.

The experiment setup is entered in the form of a stimulation pattern. It is created with the help of user entered data which is the current injection pattern, opposite or adjacent, and voltage measurement pattern and amplitude of the applied current. User can also set if the measurement from the drive pattern is to be used or need to be removed. This process interprets the stimulation information into a vector form.

Next, homogeneous data and non-homogeneous data are loaded. It is read through text files; hence user needs to browse and select the specific text file. The data is read from the file and stored in a matrix for further processing. If the measurement from drive pattern to be excluded, it is removed at this stage. Then, a difference data is calculated by subtracting homogeneous data from in-homogeneous data.

As Gauss Newton One step algorithm is implemented for image reconstruction, a prior needs to be selected. Depending upon user selection the prior R is calculated. At this stage, measurement noise covariance W and Jacobian Matrix J is calculated. User also needs to enter hyperparameter before starting reconstruction. The image reconstruction algorithm is designed according to its EIDORS implementation. Once the reconstruction button is clicked, the algorithm is run, and the resulting image is drawn on the GUI.

A brief flowchart of the design is created. Also, the code is tested with the given homogeneous and inhomogeneous data and the resulting images are shown in following section.

#### 3.1.2 Flowchart

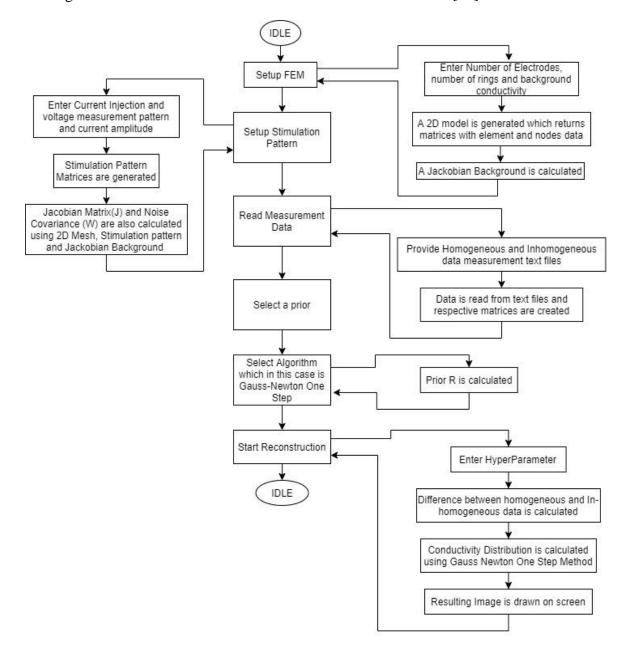

Figure 3.1 shows the workflow which summarizes C# code in [19]

Figure 3. 1 C# Implementation Flowchart (Chen)

# 3.1.3 Test Results

The C# implementation in this project is tested using an 8 electrode measurement data. The text files for homogeneous measurement and inhomogeneous measurement are available. The code is tested for different number of rings, the options for rings are 4,8,12 and 16, and different priors, the options for priors are NOSER, Tikhonov and Laplace. The result with 16 rings and Tikhonov prior is shown below in figure 3.2.

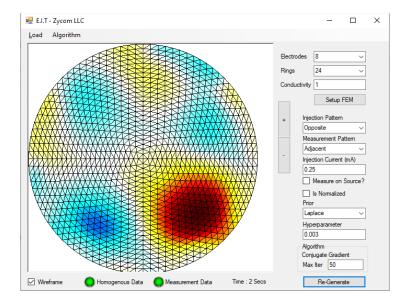

Figure 3. 2 Image for 16 rings and Tikhonov Prior (Chen)

#### 3.2 Image Reconstruction and EIT [33]

#### 3.2.1 Design Description

In this project, three EIT image reconstruction algorithms are implemented in C. The algorithms are Gauss Newton one step, Total Variation and Conjugate Gradient. A GUI is designed to allow user to enter the system parameters and measurement data files. Multithreading is also implemented in order to make the design more time efficient. The parameters that can be set from

the GUI are measurement data files, algorithm selection, FEM parameters, stimulation parameters, prior selection, hyperparameter and number of iterations.

The homogeneous and inhomogeneous data can be loaded from the menu option *Load* on GUI. The files can be loaded in two formats, txt and xls or xlsx. The data is stored in matrix format for further use.

The parameters used to build finite element model such as number of electrodes, number of rings and background conductivity can be entered from the textboxes available on GUI. On the click of Setup FEM button, a 2D Mesh is generated and FEM model is displayed on the GUI. Later, if the number of electrodes or number of rings are changed, the FEM model is updated accordingly. The Jacobian background matrix is also created.

The design implements three priors, Laplace, NOSER and Tikhonov. Default prior is set as Laplace and can be changed from GUI. If the prior is changed, the prior matrix is updated accordingly.

The algorithm selection can be done from the menu bar available on GUI. To reconstruct the image, an algorithm needs to be selected. The hyperparameter value can also be set from GUI. The maximum iteration parameter required in case of TV and conjugate gradient is set as 3 and 50 respectively, by default. There is a Re-generate button on GUI, if pressed the set algorithm gets executed and resulting image gets drawn on screen. A timer is used to check if the calculations are done and image is ready to be drawn.

## 3.2.2 Flowchart

Figure 3.3 shows the working flowchart of the C# design

Figure 3. 3 C# Implementation Flowchart (Rabi)

## 3.2.3 Test Results

The code was tested using available 8-electrode homogeneous and inhomogeneous data. All three algorithms for different rings and prior settings are tested and results are captured. The result with conjugate gradient algorithm, 24 rings and Laplace prior is shown below in figure 3.4.

Figure 3. 4 Conjugate Gradient Image result with 24 rings, Laplace Prior (Rabi)

# 3.3 Real-Time Electrical Impedance Tomography [9]

# 3.3.1 Design Description

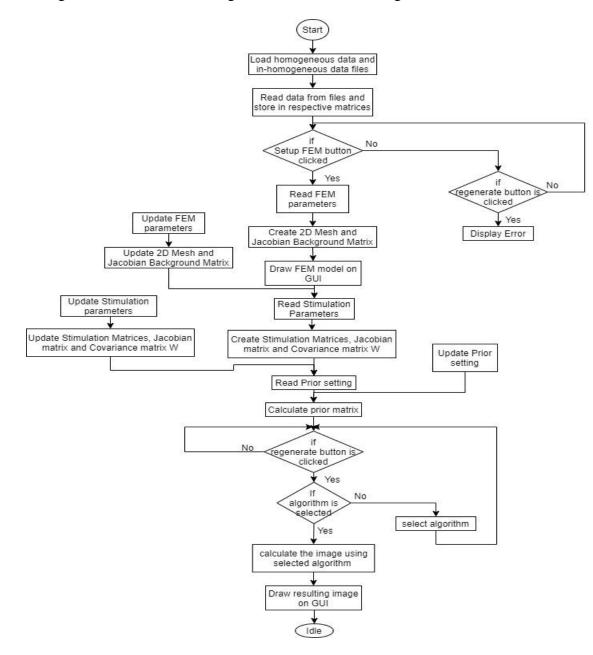

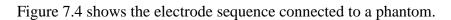

This project includes a complete system design for real time Electrical Impedance Tomography for head imaging. A FPGA based system is developed which can drive the electrodes, read the voltages at the electrodes, process the acquired data, and send the resulting image data to a C# based GUI for display. A 12-electrode system is used to connect to a circular phantom. Analog circuitry is developed to drive and read data to and from the electrodes. A Zynq 7020 device-based development board, Zedboard, is used to interface the analog circuit to the onboard Zynq FPGA. The Zynq FPGA controls the electrode interface as well as process the acquired data. Gauss Newton One step algorithm along with Tikhonov prior is implemented for image reconstruction. The C# GUI is designed to provide user with control over system operation, such as start, stop acquisition and processing etc. The GUI communicates with Zynq FPGA over serial port. It receives the processed data and displays it on the screen. The GUI also provides an option of one-time measurement and continuous measurement. With the continuous measurement option selected, the system is designed to be able to produce the image data continuously in real-time.

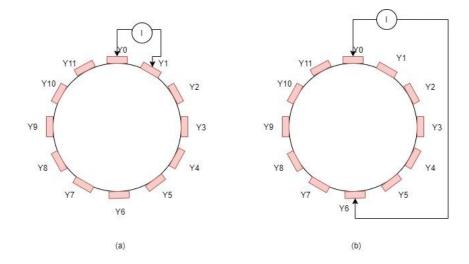

#### 3.3.2 Hardware Description

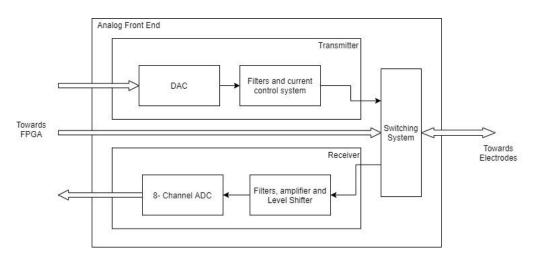

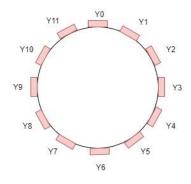

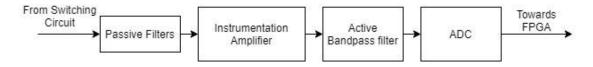

Figure 3.5 shows the block level representation of analog circuitry, Analog Front End board designed in this project to drive and read to and from the electrodes.

Figure 3. 5 Block Diagram of Analog Front End Hardware

The devices (ICs) used in AFE board are as follows

- DAC LTC1668

- Operational Amplifier OPA 2192

- Multiplexer ADG 1606

- Digital Potentiometer AD5293

- Instrumentation Amplifier AD8429

- ADC AD7761

- FMC Connector

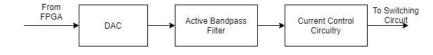

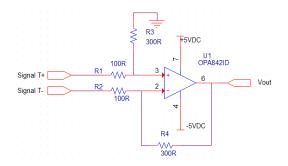

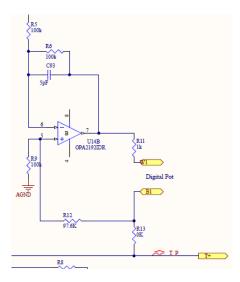

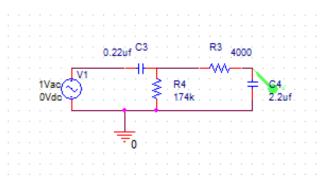

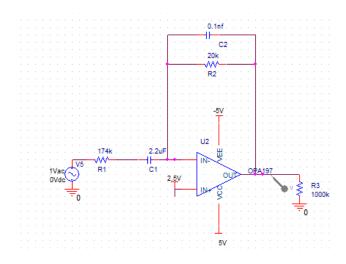

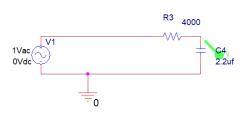

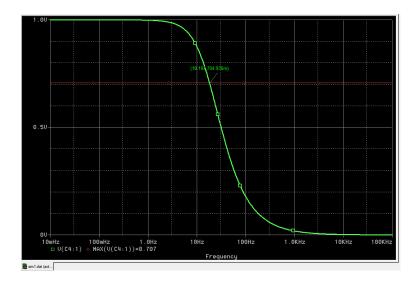

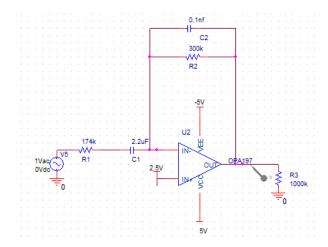

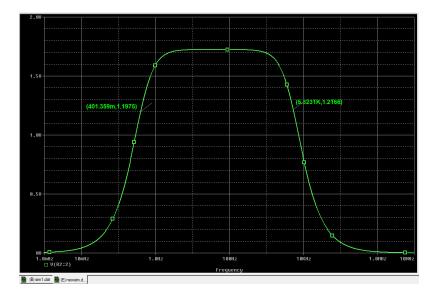

As shown in the block diagram, the AFE has two main sections, transmitter, and receiver. The transmitter section includes DAC, filters, and the constant current circuit to generate the sinusoidal signal to drive the electrodes. A digital data (16-bit) for a sinusoidal signal at different frequencies is generated in the FPGA. This digital data is converted to analog signal using Linear Technology LTC1668 DAC chip. The Linear Technology LTC1668 IC is a 16-bit 50Msps digital to analog converter. The DAC takes 16-bit input data and gives differential current output. The differential current output is filtered through an active bandpass filter designed for a range of 100Hz-100kHz. The filtered signal is passed through a current source before passing it to the electrodes through multiplexing switches. To limit the output current, a digital potentiometer, AD5293 is used. The value setting for digital potentiometer is controlled through FPGA.

In EIT systems, the current needs to be injected through each electrode in a pattern, hence a multiplexer arrangement using Analog Devices ADG1606 multiplexer IC is incorporated to connect the current signal to electrodes. The ADG1606 IC is 16:1 multiplexer. There are twelve such multiplexers used in the design and each multiplexer is connected to all twelve electrodes. Two of the multiplexers are connected to the differential current input coming from DAC, and other ten multiplexers are connected to the receiver circuit. This way, using the four select signals of the multiplexers, each multiplexer gets connected to one electrode each time. The select signals are controlled from FPGA to control the current application and voltage measurement pattern.

The induced voltage measurement is connected to the receiver circuit through the multiplexer section. As mentioned above, at every switch rotation, there would be two electrodes connected to inject the current and other ten electrodes to measure induced voltage. These ten electrodes are used in pairs to generate 8 measurements. Signal from each electrode is passed through a passive bandpass filter designed for a range of 150Hz to 300kHz. The filtered signal from adjacent electrodes are then passed through an instrumentation amplifier to generate one measurement output. The instrumentation amplifier stage is set with a gain of 7 [37]. The single ended signal is passed through an active bandpass filter designed for a range 70Hz to 398kHz. The filter also provides a gain of 2. Hence, effectively, the signal is applied with a gain of 14 before giving it to the ADC.

The Analog Devices AD7761 ADC is an 8-channel 16-bit ADC, with individual serial output for each channel. This ADC converts 8 channel analog data to digital and provides it at 8 serial outputs in 16bit format. The output of ADC is passed to the FPGA for further processing. The AFE is connected to the Zedboard through an FPGA Mezzanine Card (FMC) connector.

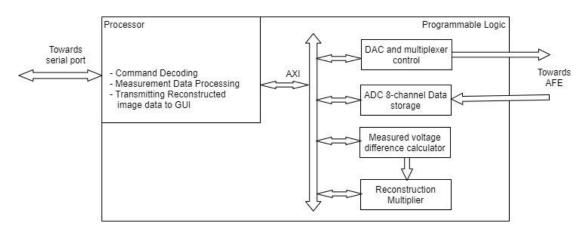

## 3.3.3 FPGA Implementation

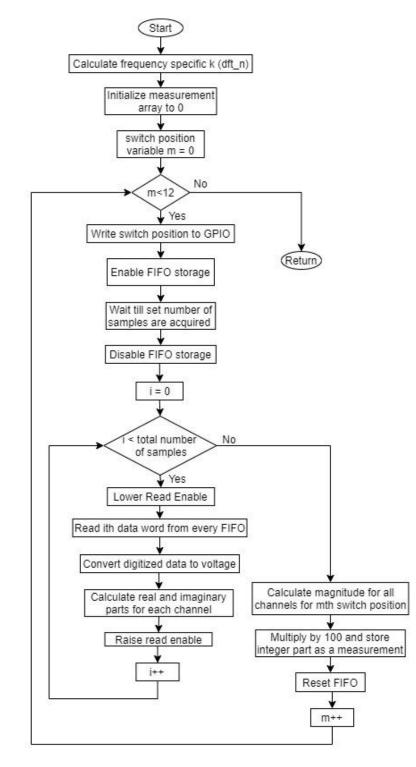

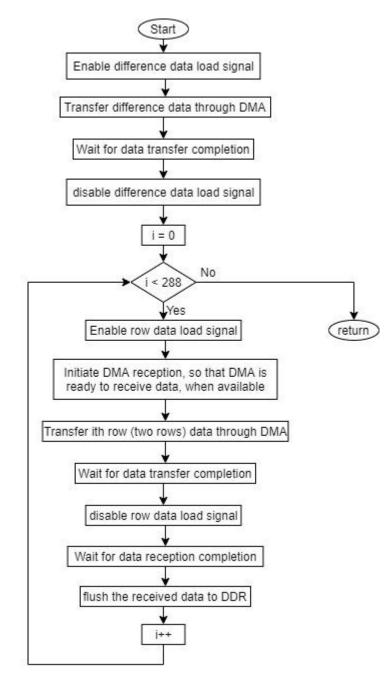

Zynq FPGA design constitutes two parts, programmable logic design and processor software design. The processor is mainly responsible for communicating with the GUI over serial port for getting the system configuration and sending the image reconstruction output data. The processor also reads digitized voltage measurement data from PL and processes it through DFT to get the magnitude of the measurement. This magnitude data is passed to the PL logic to use in reconstruction process.

The Programmable logic is mainly responsible for reconstruction algorithm implementation. The PL also generates the DAC signal as per the configuration received from processor and stores the ADC data readout for all 8 channels to pass to the processor. For image reconstruction, since Gauss Newton One Step algorithm is used, following equation governs the reconstruction process

$$\Delta \sigma = (\mathbf{J}^T W \mathbf{J} + \lambda^2 R)^{-1} \mathbf{J}^T W \Delta V \tag{3.1}$$

Where,  $\Delta \sigma$  = change in impedance, to be calculated

**J** = Jacobian Matrix

W = variance matrix

$\lambda =$  hyperparameter

R = Prior Matrix

$\Delta V$  = Difference voltage

Above equation can be written in the following format

$$\Delta \sigma = B \,\Delta V \tag{3.2}$$

where B is called as reconstruction matrix and given as

$$\mathbf{B} = (\mathbf{J}^T W \mathbf{J} + \lambda^2 R)^{-1} \mathbf{J}^T W$$

(3.3)

In the present system, most of the part of the reconstruction matrix can be kept constant. For instance, Tikhonov prior is fixed for this implementation. Additionally, the parameters required to calculate FEM such as number of electrodes, number of rings, current injection pattern, measurement pattern are also fixed. Hence, the reconstruction matrix is precalculated using MATLAB and stored as constant in the FPGA code. The difference voltage matrix is calculated using magnitude data provided by processor and the image data is calculated by multiplying reconstruction matrix and voltage difference matrix. The calculated data output is passed to processor where it transmits the data to GUI over serial port. Figure 3.6 shows the block diagram which summarizes the FPGA functionality

Figure 3. 6 FPGA Block Level Implementation (Senior Design Team)

## 3.3.4 FPGA Design Analysis

In this section, a detailed analysis of FPGA design is performed. The FPGA implementation is designed to drive and read data from 12 electrodes attached to a circular phantom, process the measurements in FPGA for impedance image reconstruction and transmit

the resulting image to GUI over serial port to display. In this design the reconstruction matrix in equation 3.3, is derived using MATLAB before programming the FPGA and used as a constant for solving equation 3.2. The reconstruction matrix size is 576X96, which is due to 12 rings, 12 electrode model. The homogeneous and inhomogeneous measurement data are retrieved in PS and passed to PL. The measurement matrix is 96X1 as there are 8 measurements and 12 total electrodes. The difference vector, which is 96X1 matrix, is calculated in PL. Hence, effectively, the row-wise multiplication of 576X96 matrix and 96X1 vector is performed in PL, that is equation 3.2, to get the output image. This multiplication output is transferred to GUI through processor and serial port. In this implementation, there are 96 multiplications which needs to be done one time to get one output. The present code implements two such multipliers and uses 192 DSP slices out of 220 available. Also, in this design the processor is used for serial communication and DFT implementation for measurement data magnitude calculation.

Figure 3.7 shows the timing summary of the present implementation. It is observed that the present design has the total negative slack of almost 1.7 us and 410 failing endpoints. Negative slack implies that the signal may not reach to the destination within the desired time. Total negative slack is the addition of all the worst negative slack violations [38].

| Setup                           |              | Hold                         |         |

|---------------------------------|--------------|------------------------------|---------|

| Worst Negative Slack (WNS):     | -18.883 ns   | Worst Hold Slack (WHS):      | 0.022 n |

| Total Negative Slack (TNS):     | -1739.044 ns | Total Hold Slack (THS):      | 0.000 n |

| Number of Failing Endpoints:    | 410          | Number of Failing Endpoints: | 0       |

| Total Number of Endpoints:      | 7844         | Total Number of Endpoints:   | 7844    |

| Timing constraints are not met. |              |                              |         |

#### **Design Timing Summary**

Figure 3. 7 Timing Summary of FPGA design (Senior Design Team)

Figure 3.8 shows the device utilization report of FPGA implementation. It is observed that, in the design most of the LUTs are used for data storage which makes total LUT utilization up to 82.28%. Also, in the design, two 96 input multipliers are implemented, which makes DSP utilization as 87.27%.

| Resource | Utilization | Available | Utilization % |

|----------|-------------|-----------|---------------|

| LUT      | 43773       | 53200     | 82.28         |

| LUTRAM   | 96          | 17400     | 0.55          |

| FF       | 9174        | 106400    | 8.62          |

| BRAM     | 64          | 140       | 45.71         |

| DSP      | 192         | 220       | 87.27         |

| 10       | 47          | 200       | 23.50         |

| MMCM     | 1           | 4         | 25.00         |

| PLL      | 1           | 4         | 25.00         |

Figure 3. 8 Device Utilization Report (Senior Design Team)

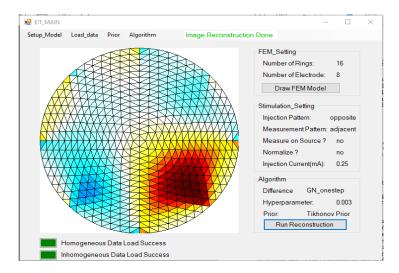

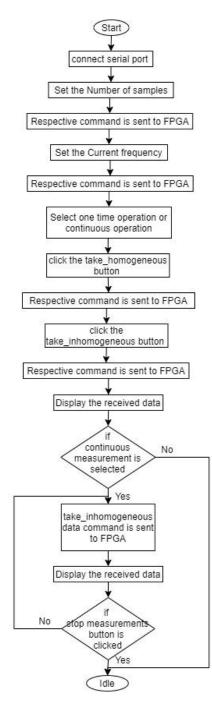

# 3.3.5 GUI Design Description

A graphical user interface is designed using C#, which communicates with Zynq FPGA over serial port. The GUI provides user with controls such as initiate reading homogeneous and inhomogeneous measurements. It also allows user to set the frequency of the injection current to be set as one of the following - 500Hz, 1kHz, 2.5kHz, 5kHz, 10kHz. The number of samples to be used to get magnitude of the measured signal through DFT can also be set as 512, 1024, 2048, 4096, 8192 samples, through GUI. A command structure is designed to communicate the instructions between GUI and Zynq FPGA.

Once measurements are done, the reconstruction calculations are performed inside FPGA and the resulting data is sent to GUI. The reconstruction data is stored in proper format and displayed on the GUI. A 2D Mesh calculation is performed to draw the reconstruction image on

the GUI. This operation of acquiring the data to printing the image on screen can be performed once or continuously, depending upon user selection. A handshaking command is used to initiate the communication repeatedly in case continuous operation is selected. Flowchart in figure 3.9 summarizes the working of C# code.

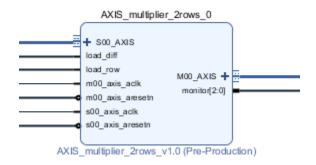

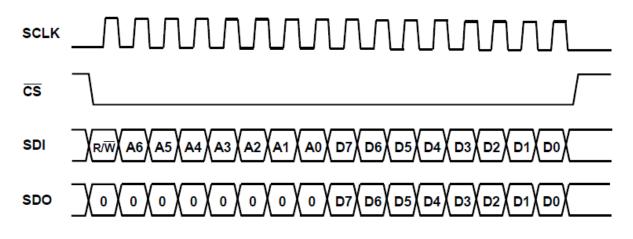

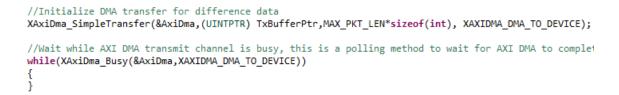

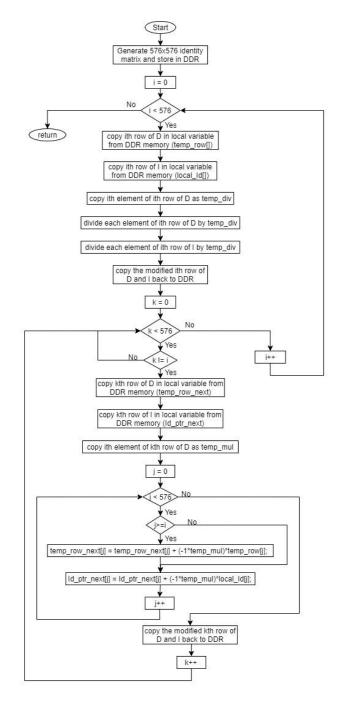

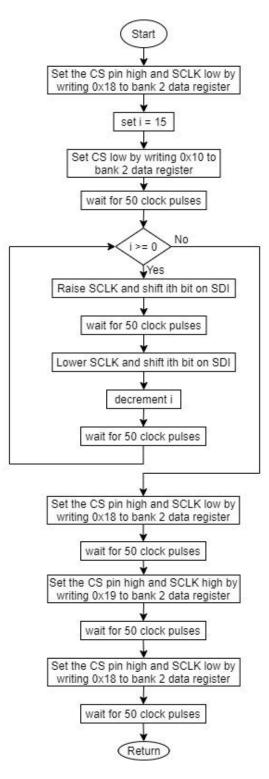

#### 3.3.6 System Performance