# **Programming a Paintable Computer**

### William Joseph Butera

SBEE, MIT, 1982 SM, MIT, 1988

Submitted to the Program in Media Arts and Sciences, School of Architecture and Planning, in partial fulfillment of the requirements for the degree of

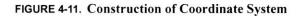

### **Doctor of Philosophy in Media Arts and Sciences**

at the

## Massachusetts Institute of Technology

February 2002

© MASSACHUSETTS INSTITUTE OF TECHNOLOGY, 2002. ALL RIGHTS RESERVED

Author \_\_\_\_\_ William Joseph Butera Program in Media Arts and Sciences

Certified by V. Michael Bove Jr. Principal Research Scientist Program in Media Arts and Sciences

Accepted by Andrew Lippman Chair, Departmental Committee on Graduate Students Program in Media Arts and Sciences

MASSACHUSETTS INSTITUTE OF TECHNOLOGY MAR 0 4 2002 LIBRARIES

# **Programming a Paintable Computer**

## **Bill Butera**

Submitted to the Program in Media Arts and Sciences, School of Architecture and Planning, in partial fulfillment of the requirements for the degree of

Doctor of Philosophy.

at the

Massachusetts Institute of Technology

February 2002

## Abstract

A paintable computer is defined as an agglomerate of numerous, finely dispersed, ultra-miniaturized computing particles; each positioned randomly, running asynchronously and communicating locally. Individual particles are tightly resource bound, and processing is necessarily distributed. Yet computing elements are vanishingly cheap and are regarded as freely expendable. In this regime, a limiting problem is the distribution of processing over a particle ensemble whose topology can vary unexpectedly.

The principles of material self-assembly are employed to guide the positioning of "process fragments" — autonomous, mobile pieces of a larger process. These fragments spatially position themselves and reaggregate into a running process. We present the results of simulations to show that "process self-assembly" is viable, robust and supports a variety of useful applications on a paintable computer.

We describe a hardware reference platform as an initial guide to the application domain. We describe a programming model which normatively defines the term process fragment and which provides environmental support for the fragment's mobility, scheduling and data exchange. The programming model is embodied in a simulator that supports development, test and visualization on a 2D particle ensemble.

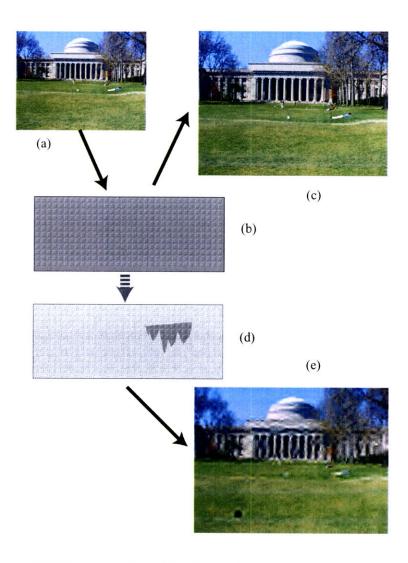

Experiments on simple combinations of fragments demonstrate robustness and explore the limits of scale invariance. Process fragments are shown interacting to approximate conservative fields, and using these fields to implement scaffolded and thermodynamic self-assembly. Four applications demonstrate practical relevance, delineate the application domain and collectively illustrate the paintable's capacity for storage, communication and signal processing. These four applications are Audio Streaming, Holistic Data Storage, Surface Bus and Image Segmentation.

Thesis Supervisor: V.Michael Bove Jr. Principal Research Scientist, Media Arts and Sciences, MIT

# **Dissertation Committee**

**Thesis Supervisor**:

V. Michael Bove Jr. \_\_\_\_\_ Principal Research Scientist Media Arts and Sciences, MIT

## **Thesis Readers**:

Edward Adelson \_\_\_\_\_ Professor Department of Brain and Cognitive Sciences, MIT

1

Neil Gershenfeld \_\_\_\_\_\_ Associate Professor Media Arts and Sciences. MIT

Gerald J. Sussman \_\_\_\_\_ Professor Department of Electrical Engineering and Computer Science, MIT

### Acknowledgments

### Even ordinary people like me can have extraordinary ideas. But it helps to have them while you are at MIT.

### My heartfelt thanks to ...

To my advisor, V. Michael Bove Jr., long a steadfast critic, ultimately a guiding hand, ever an approachable collaborator. Mike's interest in machine architecture runs deep. And the many hours we spent debating the relative merits of distributed versus centralized architectures crystallized the need to qualify this work early with simulated applications.

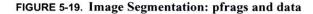

To my thesis readers, Neil Gershenfeld, Gerald Jay Sussman and Edward Adelson; masterful and selfless educators all, each with something fundamental to say about the nature of information and computation. Conversations with these men were empowering, refreshing, provocative, and always instructive. It was a series of meetings with Neil 27 months ago that launched this project, complete with conceptual grounding, articulated purpose and crucial support. Ensuing contact with Gerry and the amorphous computing group added background, a sense of shared purpose and the kind of litmus tests that can only come from a progenitor of the field. As both an accomplished vision scientist and a skilled generalist, Ted added additional focus on questions relating the basic nature of computation, (as opposed to ways to simply build a better computer). For this, and his vital sanity checks on the image segmentation application, I am especially grateful.

If this idea blossomed at MIT, it was conceived at Micronas-Intermetall, a mid-sized German IC manufacturer with a over-sized pioneering spirit. It was there, over years of lunch time brain-dumps, that the idea of a paintable computer began to take shape, anchored on the aspirations of a world class troupe of intrepid chip hackers. Hats off to Lubo, Sönke, Uli 7, Herbert, Bini, Christian, Milan, Martin, Werner, Hans-Jürgen, Heinrich, Rehmi, Uli S, Manfred, Dietmar, Kai, Klaus, Dieter, Stefan, Thomas, Peter, Fritz, Knut, and Dagmar. With them in mind, this document takes the form of a 170 page letter from camp — back to the industry that launched me on this adventure, and in particular to the Concept Engineering department at Micronas ... happy home for over six years.

Not surprisingly, this research owes an abiding debt of gratitude to my department; the Media Laboratory at MIT. To Nicholas Negroponte, founding director of the lab, for his skill, acumen, generosity and unshakable faith in the students' inner compass. To Walter Bender, current guardian of the MAS flame, for his early enthusiasm, penetrating insights and bulwark support during the formative phase of this research. To Linda Peterson for her fortitude, patience, administrative wizardry, and dedication to the well being of her charges. To Tom Gardos from Intel, and Mike Taylor from Motorola, for their masterful stage management of what ultimately became profoundly rewarding interactions with their respective companies. And finally, to my fellow students, particularly those in the Garden, and the Physics-and-Media groups, for their advice, inspiration, fellowship, patience, expertise, humor, and generational diplomacy. The world will be in good hands.

My appreciation and indebtedness likewise extend to elements of the greater MIT community. To Gerry Sussman, Hal Abelson, and Tom Knight and the rest of the amorphous computing group at MIT's Laboratory for Computer Science / AI lab, for inventing the field years before I wandered in, and for welcoming the newcomer with prolonged helpings of advice, encouragement and hard-earned wisdom. To Theresa Tobin, Sarah Wenzel and the rest of the staff at Hayden Memorial Library, for their cheerful forbearance and impromptu literary tutorials during my seven month occupation of their choicest authoring real estate. Few places on this (or possibly any other) campus offer as uplifting an environment in which to write as Hayden Library's second floor berths, perched in the alcoves of those towering bay windows with their sweeping view of the Charles River Basin and Boston's Back Bay.

In a dense constellation of gifted colleagues, singling people out for special recognition is seldom prudent and never fair. Yet this research is beholden to a cadre of compeers who have escorted this effort since its inception and whose frequent inputs were always telling and occasionally pivotal. Thanks to these, my venerable "second committee"; John Underkoffler, Joshua Lifton, Stefan Agamanolis, Radhika Nagpal, Steve Schwartz and Jim McBride. In this vein, my thanks also to professor Aaron Bobick at Georgia Tech for frequent counsel and his keen observations relating to the nature of biological computing, and to professor David Culler at U.C. Berkeley for insightful discussions and important feedback.

Of course my deepest thanks go to my family. Decades will pass before we will know if the sacrifice was worth it. But what value the reader finds in this work is most directly the product of a tight family whose members give all and ask for nothing in return. The harder the going, the more intense their support. To my brothers Joe, and Ed, my sisters Fran, Laura, and Viv, our two devoted parents Charlie and Barbara, my honored parents-in-law Helmut and Lydia, my brothers and sisters by marriage Oren, Bob, Irmgard and Otto, my precocious daughter Lara, and my wife-the-living-saint Loni. By the time any of you read this, I sincerely hope that pay-off time is in full swing.

# *Contents*

| CHAPTER 1 | Introduction 1                                                                                                                                                                                                                                                                                             |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | Scenario - Painting the Computing 1<br>The Problem - Programming Paintchips 4<br>The Solution - Self-assembly 5<br>Roadmap 7                                                                                                                                                                               |

| CHAPTER 2 | Background 9                                                                                                                                                                                                                                                                                               |

|           | IC Economics 9<br>Complex Adaptive Systems. 13<br>Self Assembly 15<br>Criteria for Success 17                                                                                                                                                                                                              |

| CHAPTER 3 | System Architecture: 21                                                                                                                                                                                                                                                                                    |

|           | <ul> <li>Hardware Reference Platform 22</li> <li>Component Subsystems 24</li> <li>Pushpin Computers 27</li> <li>Programming Model 33</li> <li>PM Specification 34</li> <li>Run Time Example 46</li> <li>Discussion &amp; Related Work 53</li> <li>Simulation Environment 56</li> <li>Summary 59</li> </ul> |

#### Contents

| Essential Process Fragments 63 |  |  |  |  |  |

|--------------------------------|--|--|--|--|--|

| Gradient 64                    |  |  |  |  |  |

| MultiGrad 71                   |  |  |  |  |  |

| Tessellation Operator 75       |  |  |  |  |  |

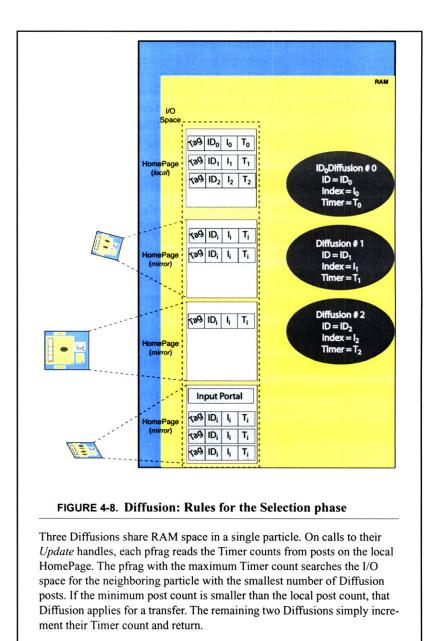

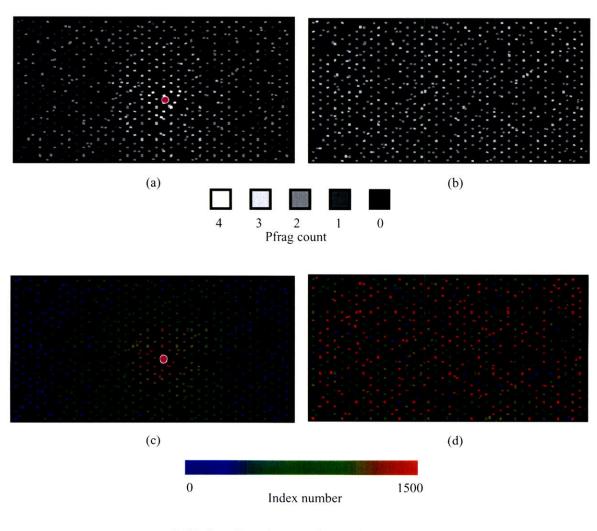

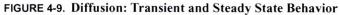

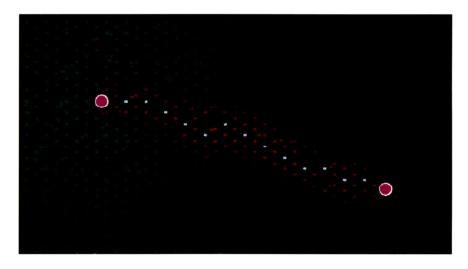

| Diffusion 82                   |  |  |  |  |  |

| Channel Operator 87            |  |  |  |  |  |

| Coordinate Operator 91         |  |  |  |  |  |

| Summary 95                     |  |  |  |  |  |

|                                |  |  |  |  |  |

| Applications 99                |  |  |  |  |  |

| Streaming Audio 100            |  |  |  |  |  |

| Holistic Data Storage 107      |  |  |  |  |  |

| Surface Bus 115                |  |  |  |  |  |

| Image Segmentation 128         |  |  |  |  |  |

| Discussion 140                 |  |  |  |  |  |

| Summary 143                    |  |  |  |  |  |

| Wrap up 147                    |  |  |  |  |  |

| • -                            |  |  |  |  |  |

| Colloquy 147                   |  |  |  |  |  |

| Contributions 155              |  |  |  |  |  |

| Future Work 156                |  |  |  |  |  |

| Bibliography 163               |  |  |  |  |  |

| Yield, Cost and Die Size 171   |  |  |  |  |  |

|                                |  |  |  |  |  |

Contents

# Scenario - Painting the Computing

In the next years, process technology will arrive at the point where autonomous computing elements can be scaled to the size of large sand kernels and sold at bulk prices. Coupled with a commensurate shrink in the footprint of sensors and actuators, the concept of "personal computing" will take on a radically new dimension. While the details of how people relate to this ultra-commoditized form of computing remain largely conjectural, a couple of points are already apparent:

- 1. As the computing elements become resilient to environmental stress, they will migrate off the expensive, precision engineered motherboards, and into every-day objects such as building materials, furniture, and clothing.

- 2. People will find it more natural to deal with computation as a bulk item, preferring to manipulate it by the jar full, by the bolt, by the cord, or by the shot glass.

One could loosely delineate commodity level computing as those instances where the price of the computing is so low that it is comparable to detergent and where the form factor is so small that it seamlessly blends into everyday environment. As a representative embodiment, we advance the notion of a *paintable computer*. Based on the architecture originally described by Sussman, Abelson and Knight [1], a pinless IC with an on board micro, program memory and a wireless transceiver, is reduced to the size of a small match head and powered parasitically. Several thousand of these particles would be suspended into a viscous medium and deposited it on surfaces like paint. Once exposed to power, they should boot and self organize their local address space. External I/O would be via physical contact with an object fitted with a transceiver whose protocols mimic the behavior of the chips.

While the details will change en route to practice, this notion of a *paintable* captures the essence of what could be a big part of our computing future: computation as a tangible, fluidly dispersible additive to ordinary objects. Want a surface to be smart? Add a layer of computing. Want it to be smarter? Add a second coat. Has the computing lost its luster? Get out the belt sander.

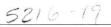

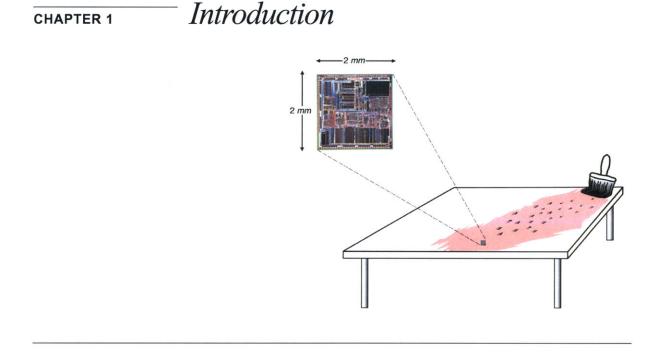

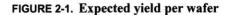

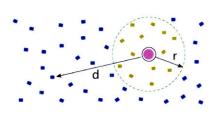

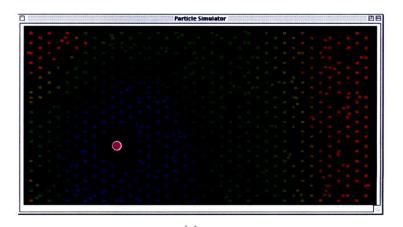

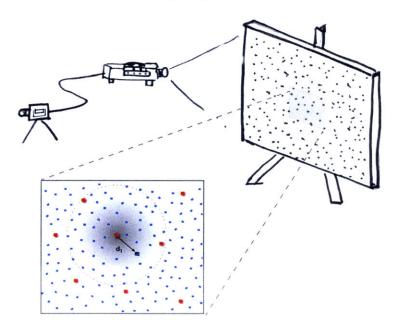

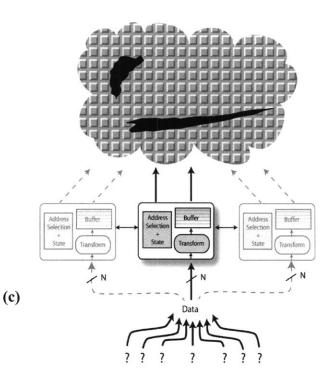

The atomic element of a *paintable* is the particle (fig 1-1*a*). Characteristic specs include a '486 class micro, an internal clock running at ~ 50 MHz, and 50-100K of RAM for code/data storage. All the I/O to the micro is gated through a wireless transceiver supporting a minimum duplex rate of 100 Kb/s.Communication is via asynchronous links to the nearest neighbors. A power subsystem harvests power from the immediate environment with minimal constraints on the particle's placement<sup>1</sup>.

Once exposed to power, each particle builds an enumerated list of the neighbors with which it can communicate (fig. 1-1b). There is no hardware support for recovering relative orientation or distance. And critically, no particle has any knowledge of the world beyond its communication radius.

<sup>1.</sup> Candidate techniques include chemical, optical, electrodynamic coupling or sliding mechanical contact to conductive planes.

#### Scenario - Painting the Computing

FIGURE 1-1. Paintable computer: particle and ensemble

Paintable computers are ensembles of homogeneous particles (a) each containing a micro, memory, a wireless transceiver and support for harvesting environmental power.

Particles are pseudo randomly positioned and communicate locally with their immediate neighbors (b). On boot-up, particles build an enumerated list of their neighbors. There is no hardware support for estimating distance or orientation. And particles are purposefully blind to the world beyond their communication radius.

#### Introduction

# The Problem - Programming Paintchips

Decades of research and productizing have failed to produce robust, general methods for programming massively parallel systems that could take hold in the marketplace. And the native architecture of a *paintable* seems to take a bad thing to a fatal extreme. Indeed the basic attributes read like a compiler designer's epitaph; *an unknown number of micros arranged in an unknown topology with slow, asynchronous local interconnects. Individually, each micro is too resource poor to do any useful work, yet the network message flow is chaotic and the unit reliability is low.* Here is a detailed look at the worst of these sorrows:

**Asynchrony** Clock level synchrony is out. Two neighboring particles can not be guaranteed to have the same clock rate, let alone lock them. Event level synchrony also seems beyond reach. In an unknown topology with sporadic unit failures, there is no way for a process on one particle to predict or direct the activity on a neighboring particle. Code running on one particle should therefore never explicitly synchronize to events generated on another particle.

extreme **Fault Tolerance** Allied with the inherent asynchrony is the propensity of individual particles to fail completely. A defining characteristic of a paintable computer is that the user should be permitted certain activity that will cause some particles to die. For example, if a *paintable* is layered onto a wooden surface, the user should think nothing of driving a nail into that surface, or machining it to an arbitrary shape.

**Network Locality** Particles can only communicate directly with other particles in the immediate spatial vicinity. A particle's knowledge of the environment stops completely at the border of this neighborhood. And even within this neighborhood, particles have no sense of relative orientation or distance to neighbors<sup>2</sup>.

Adaptive Topology Any truly *paintable* system will have final topology which is unknown at the time when the application code is written. While it will always be possible to recover an approximate coordinate system at runtime, no application code should prescribe a particular spatial layout of the processors. As a consequence, application code may not explicitly address a

<sup>2.</sup> While the size of the neighborhood can vary substantially, current experiments run on neighborhood sizes ranging from 8 to 20 particles.

particle by location neither as an absolute location nor as a relative location (eg. two hops north).

**Code Compactness** On-particle memory is very limited, inter-particle communication bandwidth is slow compared to processor speed, and there is no external support for virtual memory. Functions running on a given particle should therefore be self contained and sized to fit completely in a single particle.

While there is nothing to prevent particles from passing data or code to their neighbors, no process on a given particle can predict or control the state of processes running in the neighborhood.

**Combinatorics** A basic strategy of compiler design for massively parallel machines is to anticipate likely failure modes and adapt the data flow to optimize for speed and tolerance to foreseeable faults. This in turn imputes to the compiler designer the ability to predict and account for all possible hardware-related states surrounding a particular computational event.

For systems where the native combinatorics outstrip the compiler's ability to predict and adapt, the only option is to impose those restrictions necessary to limit the number of possible states. In many ways, the *paintable*, with its unconstrained placement of particles, represents a worst case in the combinatorics of the hardware and would require the largest number of restrictions to tame its complexity.

# The Solution - Self-assembly

Cumulatively, these hurdles suggest that it will never be practical to expect a human to structure a procedure for unrestricted use on this architecture. The starting point for this research is the claim that *if we can not get a human to structure the procedures, we are going to have to get the procedures to structure themselves.* Consequently, this work advances a programming model based on process self-assembly — the undirected reassembly of a process from randomly distributed fragments of code with state.

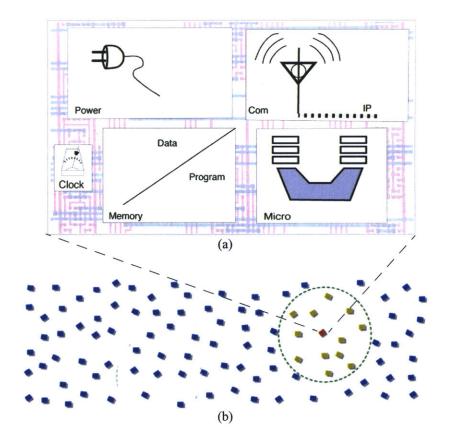

A ready analog to this notion can be found in the self assembly of materials. Selfassembly in the material domain is defined as "*the spontaneous organization of objects, under equilibrium conditions, into stable aggregates*"[7]. Investigators

#### Introduction

have reported measured success at assembling complex irregular structures from suitably treated component parts [22][29]. Often this assembly process is reversible, suggesting that one could start with a end structure, deconstruct it into its original parts, place the parts into a medium which supports mobility, and agitate them until the reassembly process achieves a local minimum — preferably in the original state (fig. 1-2)

A loose mapping between material self-assembly and process self assembly follows basic intuition. The component parts of the material structure correspond to fragments of a running process<sup>3</sup>. The assembled material structure corresponds to the

<sup>3.</sup> imagine the mapping the program and data space of a process onto a 2D memory, and then dicing that memory into irregular shapes. Each of these puzzle pieces would be a individual component in the self assembly.

Roadmap

original coded procedure represented as a 2D planar graph. And the fluid medium which supports the material self-assembly is the memory space of the machine on which the procedure is executed.

The mapping is necessarily vague, and different modes of material self-assembly will offer competing guidelines. It nevertheless points toward a powerful model for organizing computation. Processes which self assemble from mobile process fragments are potentially resilient to topological variations in the hardware, and should be robust to expansive changes in scale. With this behavior in mind, we state the thesis of this dissertation: "A programming model employing a self-organizing ecology of mobile process fragments supports a variety of useful applications on a paintable computer"

In support of this thesis statement, this work proffers several contributions:

- process self-assembly: a novel distributed programming methodology which maps existing techniques in material and virtual self-assembly to a broad class of dense ensembles of asynchronous, locally inter-networked computing nodes.

- a programming model built around a novel abstraction for inter-process communication, and the construct of a "process fragment" as the atomic element of process self assembly.

- illustrative examples of abstraction and modularity in process self-assembly.

- four applications that are both novel in their own right and that collectively demonstrate the *paintable*'s capacity for storage, communication and basic signal processing.

# Roadmap

The remainder of this document lays out the rationale, builds the tools, explores basic concepts, extends them to applications and then takes stock. Chapter 2 motivates the architecture from an economic perspective, reviews background and related work, and specifies the criteria for evaluating the research. Chapter 3 presents the hardware reference platform, the programming model, and a simulator that embodies them both. Chapter 4 uses six simple examples to illustrate basic process fragment behavior and to introduce important programming constructs. Chapter 5 explores the application domain with four examples implemented on the simulator. For each application, the purpose and underlying algorithms are explained, and the functionality is demonstrated. Chapter 6 states the conclusions, lists the contributions and speculates on avenues for future work.

Introduction

# CHAPTER 2 Background

This chapter presents the background and motivation. A review of the economic fundamentals of IC chip manufacturing highlights the growing impetus for computing on sand-sized nodes. Work on Complex Adaptive Systems advances an alternate model of computing that is well suited to finely distributed architectures, the important caveat being that applications built on this alternate model have stubbornly resisted engineering refinement. Work on directed self-assembly of natural and artificial systems has produced techniques for guiding the self assembly toward bounded compliance with a predefined target structure. The chapter concludes with a list of criteria by which the design component of this research can be evaluated.

## IC Economics

The search for techniques to program a *paintable* takes on an added urgency when you realize that you may soon need to use them. And a combination of feasibility and cost pressure make this a real possibility. The manufacturing capability for much of the *paintable* architecture will appear as a byproduct of the foreseeable advances in process technology. Indeed elements of the architecture are already in place (eg. micro and memory), while much of the remainder lies in the critical path of eagerly anticipated markets (eg. monolithic RF, active tagging).

Simple feasibility however is never sufficient to drive the deployment. Entrant technologies must always exhibit some compelling advantage over entrenched alternatives. For distributed computing on miniaturized nodes, the advantages include small size, portability and tolerance to harsh environments<sup>1</sup>. Beyond these limited specialty domains lie applications where finely distributed computing must contest directly with conventional architectures for use in mainstream information processing tasks. Here, one compelling advantage is cost, yes cost. Specifically, *dense ensembles of dust size computing elements support a price / MIP ratio with which centralized architectures can not compete, with potential for over 100-fold increases in compute capacity per unit cost*. The remainder of this section explains why.

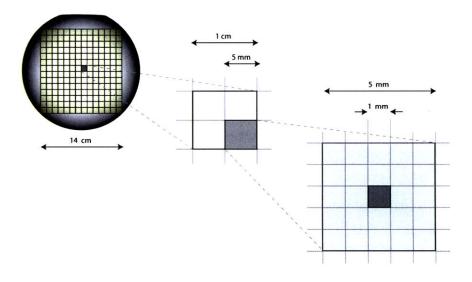

For IC's sold en mass in a consumer market, the first order determinant of the price is the size of the unpackaged die. Even immense one-time expenses for initial development and plant (~  $10^9$  \$) can be amortized over monthly sales of several million units. In an industry characterized by a dizzying dynamic, the fixed cost of fabricating a single wafer (~  $10^2$  \$) has remained comparatively stable for decades. These fixed costs include manufacturing of the raw silicon ingot, slicing it into wafers, marching it through the ovens, packaging, and testing at multiple stages throughout the process. With the unit area of processed wafer as the fixed cost, the manufacturing cost for an individual IC depends on the percentage of the wafer's dies which are functional — the *yield*<sup>2</sup>. Alternatively, given a constant yield, the cost of a single IC depends the area of the die<sup>3</sup>.

This simple relationship between yield, die size and unit cost have important consequences for economic viability of ultra-miniaturized computing nodes. A single defect is enough to render an entire die inoperable. By drastically minimizing the

an excellent example is the work on distributed sensor nodes. Centimeter scale nodes with power, computing, sending and communication are deployed ad-hoc and self organize to perform some coordinated sensing task. More detail in [50].

<sup>2.</sup> In this report, the term "yield" represents the percentage of a processed wafer that produces working dies.

<sup>3.</sup> Use of the die size as an estimate of manufacturing cost has a lower bound. For very small IC's, the minimum size can be defined by a pad ring — a rectangular ring of current drivers and contact pads for the bonding wires. And beneath a certain size, the cost of any IC is dominated by the packaging. However these lower bounds are seldom inviolate and often yield to technological advances in the face of economic pressure. For example, pin intensive IC's use ball grid arrays which, together with flip chip surface mounts have become an attractive alternative to explicit packaging.

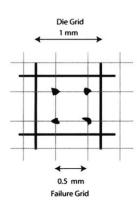

economic penalty incurred by each defect, smaller dies enjoy a natural cost advantage over larger ones. How much? Consider the abstracted instance of three architectures; a high performance CPU measuring 1 cm<sup>2</sup>, a smaller embedded microprocessor unit (MPU) measuring 25 mm<sup>2</sup>, and an ultra small microcontroller core (MCU) measuring 1 mm<sup>2</sup>. Contrived yet credible architectural features can be selected to render each of these architectures capable of equal amounts of compute capacity per unit area<sup>4</sup>. For example, at their nominal clock speeds;

1 CPU = 4 MPU's = 100 MCU's

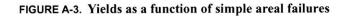

For defect-free manufacturing processes, these three architectures would deliver identical amounts of compute capacity per wafer. For processes where the yield is imperfect, the situation can be very different. Appendix A1 naively models process defects as point failures and steps through a coarse failure analysis based on three assumptions.

- 1. The likelihood of a failure at any given point is modelled as a 2D Poisson event

- 2. The presence of one failure within the boundary of a die is sufficient to classify the die as a reject.

- 3. Any one point failure will render one and only one die inoperable. Failures do not span boundaries to affect multiple dies.

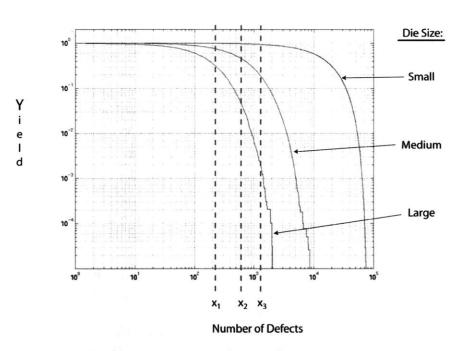

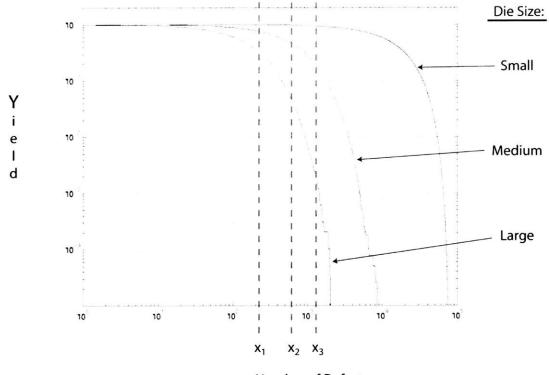

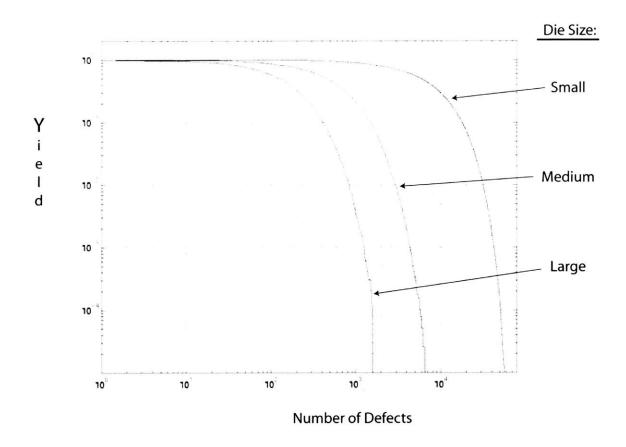

Proceeding from these assumptions, we can calculate the expected value for the aggregate compute capacity recoverable from a wafer. Fig. 2-1.compares this data for the three architectures on a single log-log plot. The independent axis shows the total number of defects per wafer. At the extreme right, failures blanket the wafer and all dies of all sizes are inoperable (...bummer). On the extreme left, the yield is perfect and the expected compute capacity is maximized for all architectures (...it's Miller time). In the middle is a region where the sensitivity to defects varies dramatically depending on the die size.

Along the line labeled  $x_3$  (corresponding to 1060 defects), 18,560 of the MCU's

(95 % of the wafer) are still viable and available for generating revenue. Likewise, 201 MPU's (26 % yield) and 1 CPU's (0.5% yield) remain functional. So at the point where only one large die remains operable, there is almost a 200× difference in yield between the large and small format dies.

4. CPU → 1 GHz clock, 5 stage pipeline MPU → 250 MHz clock, 5 stage pipeline MCU → 50 MHz clock, no pipelining. no onboard cache

#### Background

This log-log plot shows yield on a wafer as a function of defect count for three die sizes;  $1 \text{ cm}^2$  (large),  $25 \text{ mm}^2$  (medium), and  $1 \text{ mm}^2$  (small). Statistics for three sample defect rates (labelled  $x_1 x_2$  and  $x_3$ ) are broken out and listed in table 2-1 below. Note that in the instance where 1060 failures leave one large die functional, the yield differential between the large and small dies approaches a factor of 200.

| No. of Defects<br>(label from<br>plot of fig. 2-1) |                   | Yield <sup>a</sup> (number of functioning dies) |          |             |       |            |      |

|----------------------------------------------------|-------------------|-------------------------------------------------|----------|-------------|-------|------------|------|

|                                                    |                   | Small dies                                      |          | Medium dies |       | Large dies |      |

| 220                                                | (x <sub>1</sub> ) | 0.989                                           | (19,380) | 0.755       | (592) | 0.326      | (64) |

| 600                                                | (x <sub>2</sub> ) | 0.970                                           | (19,006) | 0.464       | (364) | 0.048      | (9)  |

| 1060                                               | (x <sub>3</sub> ) | 0.947                                           | (18,560) | 0.256       | (201) | 0.005      | (1)  |

TABLE 2-1. Yields for selected defect rates

a. The "yield" represents the fraction of the wafer occupied by functioning dies.

Process yields are among the most tightly guarded secrets in the IC industry. Yet products are commonly produced from processes operating in a yield regime of 30 %. And while a given process is often matured to support a much higher yield, the motivation can be undercut by the introduction of a succeeding IC process<sup>5</sup>.

The take away message from this section is; measured in raw compute capacity on silicon IC's, the large form factor, "high performance" dies are the among most expensive, inefficient form that computing can take. And that the only reason that we tolerate this surcharge is because we lack robust techniques for efficiently distributing our computing over numerous fine grain ensembles — an issue that is taken up in the next two sections.

# Complex Adaptive Systems.

Of course, the difficulty with the preceding analysis is that it treats raw compute capacity as a universal currency. Unfortunately, in the prevailing models of computation, not all ALU clock ticks are equal. Most computations that are expressed procedurally as a sequence of instructions on a Turing equivalent machine do not distribute efficiently, if they distribute at all. Comparisons based solely on compute capacity are inherently flawed in that they imply that a procedure runs on both architectures and produces identical results. In instances when this requirement is enforced, the cost advantage of the miniaturized nodes is all but lost in a sea of overhead for control and synchronization.

This section examines the work on Complex Adaptive Systems as a vehicle for recasting the concept of "computation" into a form that is more amenable to computing on *paintable* class architecture.

Design of contemporary computing systems has been constrained by a number of seemingly reasonable assumptions about architectural reliability and performance criteria of both the hardware and software. For example, few people are interested in a sorting procedure that, for a dramatic decrease in run time, will produce results that, while imperfect, are still "good enough". The difficulty in this case is the definition of "good enough". Similarly, given a procedural description of a task, few

<sup>5.</sup> consider the effect that bringing up a 0.1 micron process has on an existing 0.18 micron process. A 20% yield on the 0.1 micron line is equivalent to an 65% yield on the 0.18 line.

#### Background

people are interested in ultra-cheap yet faulty hardware that will get most of the job done most of the time. Computing was defined a series of discrete state transformations executed under direction of coded instructions assembled into a procedure. The only suitable computing elements were those that could read the instructions from the stream and then faithfully sequence through the associated computational events. The only suitable computations were those that could be uniquely described by a procedure. System designers internalized these assumptions into a mindset and set of axioms that guided the development of most man-made computing systems.

Scientists investigating the dynamics of natural phenomena have developed an alternative view of computation which has challenged elements of the computer designer's canon. Work on natural systems ranging from neurons to weather patterns has produced several key insights:

- these systems could be modeled to some level of fidelity by computational models. To the degree that this worked, the natural system could be regarded as 'computing' and doing so using 'hardware' that was heretofore regarded as unsuitable. It's not a computer, but it's computing!

- when comparing various models, investigators had to rethink the goals of the given computation in view of the goals of the entire system. For example, in time critical applications, doing half the job in a fourth the time may be preferable to running to completion, particularly if errors could be cleaned up downstream.

- the development of the computational models was at least indirectly informed by observed characteristics of the underlying hardware — ants, neurons, particle systems, Wall Street traders — all very non-traditional hardware.

An early example of this approach was David Marr's work on vision in the 1970's [32]. Departing from mantras of the time, he cast vision as a computational task and sought to characterize the computation on three levels: the *competence* (objective), the *algorithm* and the *hardware*. His approach was to hypothesize the objective of a given computation (building a visual precept) in the context of the goals of the larger system (survival). This first step was a precursor to any consideration of the algorithm and form of the hardware.

This and subsequent work on "Natural Computation" [4] broadened our formal definition of computation by establishing new metrics to measure the efficacy of computing devices and algorithms. Returning to the previous example, it is now acceptable to consider an imperfect sorting algorithm because the bounded algorithmic shortcomings could be balanced against speed of execution, size of the code, suitability for novel hardware and the ability to make up for inevitable errors later. Similarly hardware with bounded inconsistencies in performance can be seen as preferable if it is uniquely suited to a harsh environment, adaptive in some task specific way and is resilient to failures of its component parts.

This and related work on Complex Adaptive Systems provide the underpinnings for an alternative form of computing that is central to this research.

- Arbitrarily complex system behavior can be created from large numbers of simple processing elements.

- Reliable computation can be expressed as the aggregate statistics taken over a large set of local interactions. Dependence on statistics decouples the global result from the outcome of any one local interaction.

Work on StarLogo [43] captures the strengths and the pitfalls of this approach. Autonomous virtual creatures, coded with simple behaviors, interact to mimic the global behavior of slime mold, traffic jams and forrest fires. Using StarLogo as an experimental platform, even high school age children can synthesize complex phenomona. The drawback is that no insights emerge as to methods for engineering the second order behavior. Programming is largely trial and error.

# Self Assembly

Self-assembly appears in several forms, each distinguished by the complexity of the structures that they generate and the ease with which one can characterize (and replicate) the behavior.

**Scaffolded self-assembly.** Objects position themselves into shape complimentary receptacles. Any lock-and-key scheme qualifies as scaffolded self-assembly. A good example is the Fluidic Self-assembly technique from Alien Technology [1]. Small objects are cut to one of several different shapes and slurried over a surface. The surface is patterned with depressions whose shape matches one of the shape types of the objects. Objects in the slurry which contact a depression with matching shape tend to lock into place.

**Thermodynamic self-assembly.** Also called entropic self-assembly. Objects move under the influence of attractive and repulsive forces exerted on them by other objects. The net force exerted on an object corresponds to the object's instantaneous free energy. The aggregate structure corresponds to the configuration with the minimum free energy (at least a local minimum).

An oft cited example from nature is the water droplet. The repulsive forces exerted on water by the air favor shapes with the minimum exposed surface area. An early example from the regime of man made systems is the smooth flat beds of molten metal used in glass manufacture.

**Coded self-assembly.** This is the most complex form. Individual interactions are guided by coded instructions embedded in the agencies. An agency's selection of code is a function of the local environmental and the agency's instantaneous state. While the interactions are local, the codes which direct them can be arbitrarily complex.

This is the form of self-assembly most commonly employed in the coordinated activity of large ensembles of robots. Coded self assembly has the potential for managing complexity on a scale comparable to that of living systems. However it is the most difficult to characterize and emulate.

Systems which self-assemble offer a rich set of insights and techniques for use in information processing. The trick has been to map the behavior from the material domain to the virtual. Several research projects have taken up this challenge.

An early programming application of scaffolded self assembly was Hewitt's Planner[26]. Planner employed *pattern directed invocation* to dynamically assemble a process from a set of predefined software components. The hardware venue was a traditional single processor architecture. The atomic components were algorithms that were packaged for autonomous execution and labeled externally by patterned "keys". An executing component in need of a particular function would express the function as a key and broadcast a request. Available components with a matching key were candidates for servicing that request, with control passed to the selected candidate.

The work of the Amorphous Computing Group produced the first instances of coded self assembly targeted to domain characteristic hardware[1]. They defined the target hardware as a dense ensemble of randomly positioned miniaturized processing nodes, each running asynchronously and communicating locally. In the spirit of bulk commodities, individual particles were subject to sporadic failure, both individually in large groups.

In their original programming model, all code is permanently embedded in the particles at the time of manufacture. This code contains multiple functions that can be "woken up" in response to a number of predefined conditions. With the code statically positioned, the principal manifestation of the self-assembly is the assignment of property labels for the particles. While these labels can correspond to patterns of arbitrary complexity, they are all created by unsupervised local interaction, and each exhibits acceptable fidelity to a predefined target pattern.

Coore developed the concept of a "growing point" as a tokenized interrupt that used pheromones and tropisms<sup>6</sup> to direct its migration among the particles [14]. Nagpal extended the hardware model to approximate the mechanical properties of epithelial cells [40]. Radiating gradients carried messages and built estimates of the distance from dynamically selected reference points. Messages were combined with barrier synchronization to sequence the assignment of material properties and propagate new gradients.

The goal of this research is to extend virtual self-assembly to include fragments of a coded procedure as the atomic element of the assembly process.

## Criteria for Success

Ultimately, the success of this research is measured by the support it lends to the thesis statement. However, lurking behind this thesis statement were two larger agendas: 1) to provide a crucial enabling technology to an emerging architectural class, and 2) to demonstrate the class's practical importance. The conduct of this work necessarily involved a substantial design component for each of three core elements: a hardware reference platform to define the computing environment, a programming model that engendered self-assembly, and a set of applications to qualify the architecture's utility. Throughout, design decisions were made, often in the face of numerous alternatives.

As an additional vehicle for evaluating this research, metrics are presented for each of these three components. Some of these metrics can be expressed in checklist

<sup>6.</sup> This work makes heavy use of biological metaphors. In this case, "pheromones" are gradient fields with embedded state information. A "tropism" is a function of several gradient fields.

form and evaluated in a yes/no fashion. Others resist formal reduction and have to be argued rhetorically. Here is a breakdown of the questions that must be answered.

Hardware Reference Platform. As an architectural blueprint, the questions to be asked about the reference platform are:

- 1. How well does the reference model capture the fundamentals of an architectural class? Is it overdefined, underdefined? Does it capture the characteristics of interest without being unnecessarily restrictive?

- 2. Is it sane? Do any of the assumptions offend basic laws of physics or economics? Physical laws to watch are power consumption and communication capabilities. Economic "laws" relate the utility of the *paintable* to that of the more entrenched architectures such as classic embedded controllers. Are there foreseeable circumstances likely to obviate the *paintable* as an architectural class?

Programming Model: The specific metrics of interest here are:

- 1. Does the programming model adequately define its underlying abstractions, program components, and basic computing resources available in the particles?

- 2. Does the programming model support the fundamentals of self assembly? No claim is made to understand <u>the</u> fundamentals of self assembly. Rather, we are looking for faithful incorporation of a well articulated subset.

- 3. Does the programming model support data exchange among the assembled program components?

- 4. Does the programming model compromise any of the affordances of a *paint-able*? Does it have difficulty scaling when the number of particles spans several orders of magnitude?

**Applications:** There are many flavors of self assembly. Did we chose the right one? The answer should be evident in the applications. It is up to the applications to collectively demonstrate that the architecture supports performance sufficient to merit further attention. The evaluation criteria here are:

- 1. Are the applications "real"? Namely, are they functions that people currently use, could possibly use or that solve existing problems?

- 2. Do they make sensible use of the architecture? A handheld calculator running on a 250 GOP (giga-operations per second) machine doesn't count.

- 3. Is the performance robust under the variability inherent in a *paintable* (unpredictable topology, intermittent failures, expansive swings in the size of the ensemble, etc.)?

- 4. Is the specific application demonstrative of a broad class of algorithms?

5. Do the applications actually employ self assembly. Any procedure which could execute its entire function on a single particle or with many copies of a single process fragment is uninteresting.

Throughout remainder of this report, we will revisit these questions.

.

Onward ...

٠

Background

**CHAPTER 3**

# System Architecture:

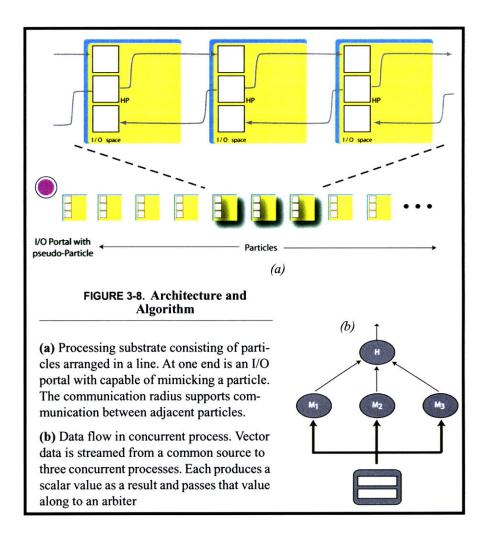

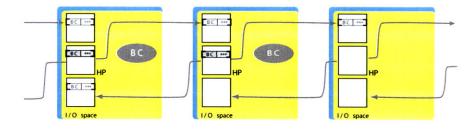

Programmable Particles, Computing Substrate

This chapter is the fine print — a lot of it. It presents a reference platform for the hardware, a detailed model for the programming, and a simulator that embodies them both. The centerpiece is the programming model. Novel abstractions for memory usage, inter-process communication and component interaction define a versatile new model for concurrent computation. The hardware reference platform describes the underlying computing environment with a model of a particle's internal architecture. Various component implementations are examined and subsumed into a single abstraction based on a universal machine fetching code and data from local memory while exchanging messages with networked neighbors via error-free channels. The concept of pushpin computing is outlined as a contemporary illustration of this architectural class. Finally, a dedicated simulator supports a graphical programming environment for development and test of software for the succeeding chapters.

This chapter is the lion's share of the research. It is voluminous and necessarily dense. By the end, you will know what you are programming and how to program it, but not why. The jumble of rules, abstractions and nomenclature will be consistent and often accordant with the metaphor of material assembly. Yet, it will take the next three chapters to ground them and motivate their use. Still, every good game has its rules, and the fun doesn't start until the rules have been read. System Architecture:

# Hardware Reference Platform

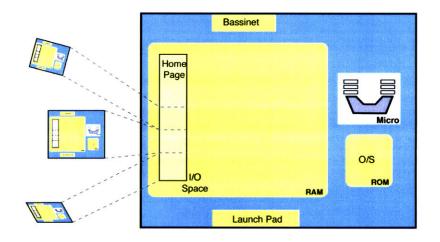

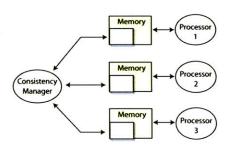

As a preamble to defining a modular programming model, this section describes a hardware reference platform that defines the computing environment inside the particles. The crucial attributes of this platform are that it is overtly conventional, universally programmable and tightly resource bound. Modest RAM storage, organized in a linear address space, contains executables that run on a single general purpose computing element. All external I/O is managed through a single networking subsystem which supports the abstraction of error-free data exchange with a small number of peripherals — in this case, spatially neighboring particles represented as virtual portals (fig 3-1). Four properties delineate this architectural class:

- 1. All addressable neighbors are spatially proximal to the particle with the neighborhood defined by the communication range of the network subsystem.

- 2. The number of addressable neighbors (N) can vary unpredictably, reflecting the fact that the number of neighboring particles within a communication range can vary; either intentionally or unintentionally. The network subsystem must respond by automatically adjusting the number of virtual peripherals ports that it maintains<sup>1</sup>.

- 3. Messages sent to the neighbors can exhibit probabilistic transit times and are not automatically acknowledged. While verification can always be explicitly requested, all messages have an unconstrained latency. Transit time (t) can be described by a probability density function p(t) which, after some multi-modal transients, asymptotically approaches zero as t → ∞. Conversely, messages that are received are assumed to be free of error<sup>2</sup>.

- 4. All code and data which is not prestored in a particle must come from neighboring particles — or other devices communicating under the guise of a particle. Any external device can exchange data with neighboring particles by adopting the particle's wireless protocols and mimicking its network behavior.

For the remainder of this report, we adopt the platform definition above as a sufficient description of candidate hardware. Any particle designed to this loose specification will be amenable to the tools and techniques of the succeeding text. By adopting this generic superset of the paintable as the reference platform, we side-

<sup>1.</sup> It is up to the network subsystem to maintain the mapping between the virtual port that represents each neighbor, and the actual neighboring particle.

<sup>2.</sup> This delegates to the network subsystem the task of error detection, error correction and, as necessary, request for retransmit.

#### Hardware Reference Platform

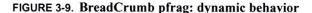

#### **FIGURE 3-1. Hardware Reference Platform**

The hardware reference platform maps the messy physicality of deeply embedded systems to the sterile virtual constructs that underlie coded procedures. Software modules execute on a standard fetch-decode-write computing element operating on local memory. The processor can also exchange messages with the neighboring particles, each represented locally by homogeneous virtual ports created and maintained by the network subsystem. The hardware supports Direct Memory Access (DMA) transfer between a port and the local network buffer.

The tight coupling between the physical world and the embedded particles is reflected in the nature of these virtual ports. They can appear and disappear unpredictably. However the number of virtual ports always reflects the number of actual particles with which the network subsystem maintains active contact. Transit time for the message is probabilistic, with a vanishing but nonzero likelihood that the message will fail to arrive. Particles can only communicate with other particles. External devices seeking to exchange data with a particle must mimic the wireless behavior of a particle in order to gain surreptitious access to a local neighborhood.

The reference platform makes no explicit mention of the powering subsystem because the choice of power source does not normatively impact the structuring of the software components — at least not directly. Indirectly, the support for pseudo-random positioning of the particles produces the variability in the size of a particle's neighborhood. — an effect that the networking subsystem must compensate for. step dependence on the engineering and economics of speculative subsystems for wireless networking and power harvesting, and admit an extended array of form factors and applications — from millimeter scale paintchips and laminar particles, to centimeter scale pushpins tacked up on a wall, to decimeter scale nodes air-dropped over open terrain, to meter scale buoys clustered on the open sea.

The remainder of this section expands on this platform definition with reviews of individual subsystems<sup>3</sup>, and a look at pushpin computing as an initial solution to the problems of power and networking. While stopping well short of a complete design, our treatment of the pushpin machines suffices for two crucial sanity checks:

- 1. an implementation of the reference platform can be built using commercially available components and materials

- at least one implementation of the reference platform supports a minimum risk path for monolithic integration into the 4 mm<sup>2</sup> size regime (i.e. is easy to integrate into a single low cost IC).

#### **Component Subsystems**

**Processor/Memory.** Each particle is fitted with a microprocessor which serves as the particle's universal computing element. All executable code resides in the particle's RAM and executes on the microprocessor. The instruction set must be rich enough to efficiently execute any instruction stream compiled down from a general purpose programming language such as C.

Minimum RAM size is 50K words organized in chunks of 8 bits or greater spread over a 16 bit address space. While not required, hardware assist for interrupt scheduling and for integer and floating point math is probably a good investment. The internally generated clock should support an operating range of 10-200 MHz, dynamically adjustable to account for available power and network bandwidth.

This definition admits many variations on common architectural themes; vanilla von Neuman CISC cores, Harvard architecture, super scalar, RISC, and VLIW. However, given the emphasis on power efficiency, the simpler bare bones models

<sup>3.</sup> Computing elements, networking and power.

may be preferable. Micros in this class are already manufacturable in sub 1mm<sup>2</sup> form factors<sup>4</sup>. Additional work remains to minimize the power consumption.

**Power.** There is nothing to preclude a particle from operating exclusively from battery storage. But most applications involving statically positioned particle ensembles will want to take advantage of harvestable power available in the immediate environment. There are almost as many power harvesting techniques as there are environments to harvest from; chemical, mechanical, optical, and

electro-magnetic coupling. Virtually any technique which produces an electrical potential across two points is of interest, provided that it affords the particle at least some latitude in its positioning — namely no precision placement and no dedicated interconnects.

Some example scenarios:

- photovoltaics: solar cells fitted to one or more sides of the package.

- chemical: (primitive battery) for centimeter scale packages distributed over a surface with the correct chemicals. Or for very small packages thrown into a vessel containing the correct chemicals (think stomach).

- structural: pins protruding from the particles pierce layered membranes to draw power from isolated planes. More detail is given below in the text on pushpin computing.

For most techniques of interest, the amount of available power will fluctuate depending on the particle's position, particle density and the material characteristics of the immediate environment. Consequently, the other subsystems must be able to match their consumption to the available power<sup>5</sup>.

In the selection of any power harvesting technique, the two dominant questions are: How much can we get? What is the minimum that we need? The amount of available power will vary greatly depending on the technique under consideration. The amount of power consumed will typically be dominated by the needs of the network subsystem<sup>6</sup>.

5. Possibly varying the frequency of the clock or by cycling through wake/sleep modes.

Consider the 1.2M transistors of Intel's venerable i486. A geometry-only shrink to 0.1 micron is sufficient to confine it to a 1 mm<sup>2</sup> area.

**Networking.** Data exchange between a particle and its environment is gated through the particle's network subsystem — a wireless transceiver that supports a minimum average particle-to-particle bandwidth of 100 kbs full duplex. As with the definition of the power subsystem, the term "wireless" does not mean contactless. Rather it implies "directionless" with a strict prohibition against precision hardwired interconnects that would constrain the positioning of the particles.

The reception area should be at least approximately circular, with a radius that yields an average neighborhood size of 8 or more particles. Within this radius, the network subsystem performs basic link management, periodically running its node discovery and verification functions to maintain an enumerated list of the neighboring particles with which it can speak. Changes in the neighborhood particle topology, both intended and unintended, are automatically reflected in this list. Channel coding and error detection/correction are employed as needed to maintain signal integrity and support the abstraction of a dedicated, error-free link.

Communication is strictly peer to peer with no inherent hierarchy among locally communicating peers<sup>7</sup>. As an example from contemporary practice, consider ethernet based LANs. All nodes connected to the medium (usually coaxial cable) are considered part of the local network. Signalling is one-to-many with one node transmitting while the remainder listen. Speaker assignment is contention based with instantaneous bandwidth relying on the statistics of random collisions. Mapping this analogy to an ensemble of paintable particles, the network connection among the P particles in an ensemble can be regarded as the aggregate of P overlapping mini-networks. Each mini-network is centered about one particle and is defined to consist of that particle and the neighbors with which it can communicate. Each particle defines at most one mini-network. But a particle with N neighbors will simultaneously be a member of up to N+1 distinct mini-networks.

While the term "wireless transceiver" naturally suggests near-field RF as the underlying link, there are a number of basic problems which motivate a look at alternatives.

<sup>6.</sup> The expectation is that 1mW will suffice for the micro.

<sup>7.</sup> A hierarchy can emerge from networking software layered onto the underlying communication link. However no hierarchical organization is implied by the hardware. This approach contrasts with Bluetooth style pico-nets and other standard cell-based networks.

- luminescence: while still a research topic, progress has been reported on efficient light-emitting structures which can be patterned directly onto CMOS dies [3]. Particles fitted with these light sources and omnidirectional photosensors could communicate through a physical medium whose translucency was matched to the desired communication radius. Motivation for this approach is the copious bandwidth native to optical signalling.

- electrostatics: for particles in the size regime of 10-200 mm<sup>2</sup>, two electrostatic techniques —capacitive coupling[34] and dissipative loading show initial promise. While the bandwidth is necessarily limited, the technology thresholds are modest enough to permit development using commercially available components.

- near-field RF: The recent past has witnessed spirited commercial interest in miniaturized RF transceivers, with a number of monolithic devices either already announced or in late stage development. The breadth and depth of this interest is sufficient to ensure a steady rate of progress in the bandwidth, footprint and power efficiency of mobile RF systems for at least the next years.

However, use of RF in particles presents several basic difficulties, depending on the scale. For use with particles on the size scale of several  $cm^2$  operating in open environments, the severe anisotropy of the reception area negates an assumption crucial to results in the following chapters. For particles on the sub 10 mm<sup>2</sup> size scale, the antenna design and the supra-GHz carrier frequencies represent the kind of obstacles that necessitate more basic research.

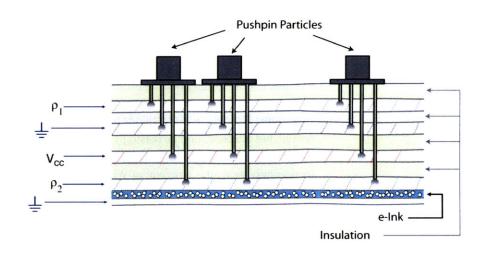

### **Pushpin Computers**

As a vehicle for characterizing the basic architecture, feasibility experiments were conducted on designs for pushpin computers. In the pushpin variant, particles are sized to the cm<sup>2</sup> scale, communication is based on electrostatic sensing, and power is delivered through catheterized pins that protrude from the package to make mechanical contact to rubbery conductive planes. While construction of a truly paintable IC would have involved protracted development at the component level, pushpin computers enjoy a relatively modest hardware threshold, and yet are functionally compliant with the reference platform.

As a precursor to a wider treatment by Lifton[34], initial experiments were performed on a 3-pin particle. Here, the computing elements are targeted toward bean sized packages with the three pins protruding from the base. The pins are of unequal length, catheterized so that only the tips make electrical contact. These 3-

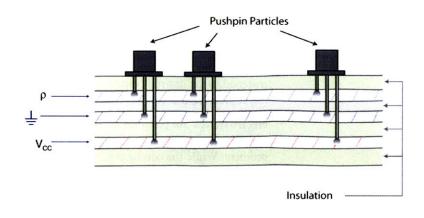

## FIGURE 3-2. Pushpin computers positioned in layered composite

A cross sectional view of composite populated with pushpin computers. 3-prong computing elements (pushpin computers) are thumb tacked into layered composite carrying supply voltage, ground, and a resistive layer used for signalling.

prong pushpins are thumb tacked into a planar composite consisting of seven sheets of soft rubbery silicone (fig. 3-2). Two of these layers are electrically conductive, separated by intervening layers that are non-conducting. The upper most active layer is resistive, with ohmic rolloff naturally limiting the range of any currentdriven signal radiating from a point source. In operation, pushpins are randomly positioned on the composite's surface and use the two longest pins to contact the conducting planes to draw power. The third pin contacts the resistive sheet and alternates between radiating a signal and listening for an answer.

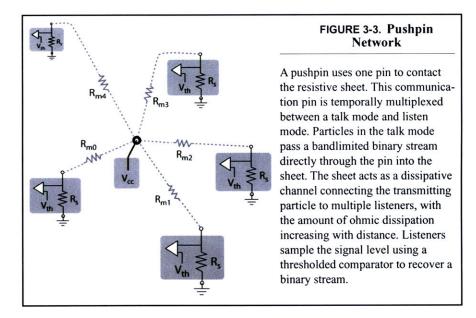

Fig. 3-3 shows a lumped parameter model for communication via a resistive sheet. The effective resistance between the communication pin of a transmitting particle to the ground pin of a receiving particle is modeled as the cascade of an effective sheet resistance  $R_{mi}$  and a fixed shunt resistance internal to the particle  $R_s$ . In the talk mode, a particle passes a bandlimited binary stream through the communication pin. Neighboring particles in listening mode sample the voltage drop across the shunt resistor using a comparator and a uniform threshold  $V_{th}$  to recover a binary stream. The effective resistance of the sheet increases with distance, essentially limiting the distance over which a logical high can be sensed.

#### Hardware Reference Platform

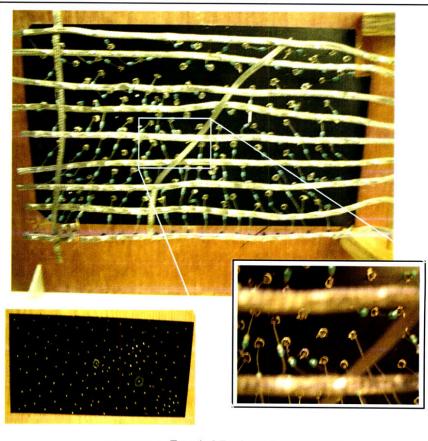

Three system characteristics crucial to any paintable networking method are the communication radii, the signalling bandwidth and the power dissipation. For the dissipative pushpin network, these performance figures were sampled using the test apparatus of fig. 3-4. A sheet of dissipative anti-static polymer, measuring  $6 \times 11$  inches, was fitted with a set of 330 sockets that were positioned irregularly and bonded using conductive epoxy. Transmitting particles were modeled by three unpopulated sockets onto which a signal could be externally applied. Receiving particles were represented by sockets populated with discrete resistors whose complimentary leads were connected to a ground plane.

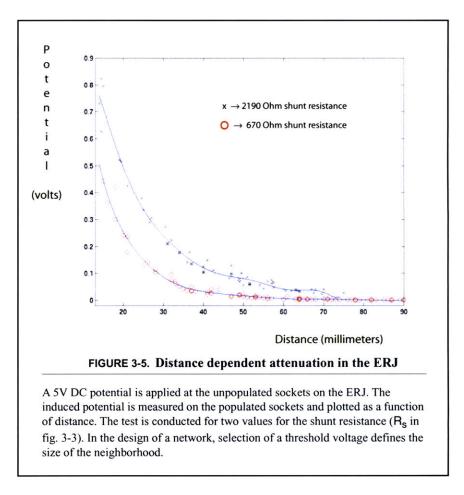

For a given point source, the size of the reception area is a non-linear function of three variables; the spatial density of the receivers, the absolute volume resistance of the unpopulated sheet<sup>8</sup> ( $R_v$ ) and the ratio of the sheet volume resistance to the shunt resistance ( $R_v/R_s$ ). Fig. 3-5 plots the signal strength as a function of distance for two values of ( $R_v/R_s$ ). Data was collected by applying 5 volts DC to an unpopulated socket. For each of the populated sockets, the induced voltage was measured

R<sub>v</sub> is estimated by averaging the point-to-point resistance between sample point pairs on an unpopulated sheet.

## FIGURE 3-4. Epoxied Resistor Jungle (ERJ)

**Top:** Front view of polymer sheet mounted in a wooden frame. 330 sockets are randomly positioned on the polymer and most populated with shunt resitors. The shunt reistors extend upward from the sockets to contact a conductive mesh that is tied to ground. All but three of the sockets are populated.

Left: Rear view of polymer with the base of the sockets exposed for electrical measurment. The bases of the unpopulated sockets are circles.

Right: close up of top showing one of the unpopulated socket.

at the base<sup>9</sup> along with the straight line distance back to the "transmitting" socket. This procedure was repeated for each of the three unpopulated sockets. Fig. 3-5 shows the sampled data points and a fitted curve. Note that for a given particle density, selection of a threshold voltage is sufficient to define the expected size of a neighborhood.

<sup>9.</sup> The point at which the shunt resister contacted the socket.

**Discussion.** Nothing in this brief treatment approaches closure on the many crucial implementation questions surrounding the hardware for pushpin computing. No data was gathered on the failure modes of the conducting silicone used in the power planes. And in the networking subsystem, no consideration was given to the additional power consumption or the bandwidth costs for clock recovery, channel coding or error management. These challenges and more have been taken up by Lifton[34].

The crucial message of this section is that the relevance of the programming model developed herein is not confined to a specific design for pinless paintchips with their speculative subsystems for power and communication. Rather, the programming model can be designed to an extended architectural class — one that includes tractable designs based on conventional components. Joint development of the hardware and software for ultra dense distributed computing can begin with manageable hardware that captures the essentials of the problem domain.

# **Programming Model**

To program a *paintable* is to program on both sides of a great divide. On the one side, programs must embody an organizing principle that anticipates the irregularity, asynchrony, fluctuation, expansive scale, and complex behavior of the particle collective. On the other side, programs must necessarily consist of modules which run on individual particles where the computing environment is well ordered, consistent, and reliable. This section presents a programming model (PM) for the *paintable*, and illustrates its application with a simple run-time example. The mechanism for extra-ensemble data exchange is revisited. Work on related programming models is reviewed.

But first, whence the metaphor of material self assembly?

Computation is often applied to model events in the physical world. A successful approach has been to pattern the structure of programs after the structure of physical events that they model. *Object oriented programming* organizes programs into 'objects' whose instantaneous state is internalized as a collection of state variables and whose exposed interface is a set of object-specific procedures. *Stream programming* uses delayed execution as a model for the progress of information through cascaded physical systems.

As computing migrates onto densely distributed embedded substrates, a programming abstraction based on material self-assembly<sup>10</sup> follows naturally. As with the *paintable*, the "hardware" in material self-assembly consists of numerous, unreliable components arranged in a heterogeneous ensemble whose native complexity strains traditional analytic techniques. Material self-assembly, when viewed as a computation, offers fresh approaches toward exercising quantitative control over these seemingly chaotic systems. Finally, a programming model based on material self-assembly captures the dichotomy inherent in computing on a *paintable*. Simple behaviors guiding local interaction must be engineered to yield global behavior which is complex, adaptive, yet to at least a degree, predictable.

<sup>10. &</sup>quot;self-assembly" is broadly defined to include several common variants (scaffolded, entropic, and coded) operating on a variety of substrates (biological cells, insect colonies, man made nano-structures).

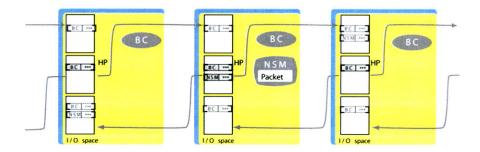

#### **PM Specification**

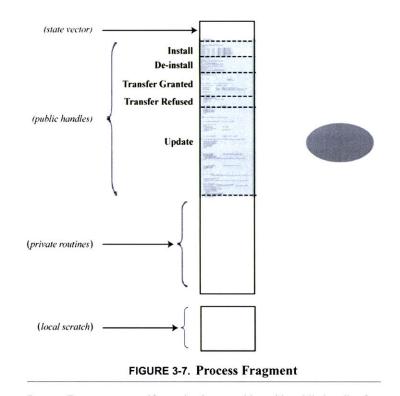

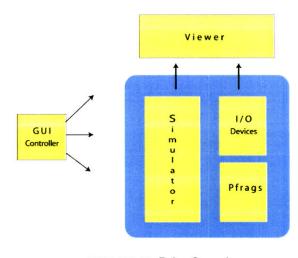

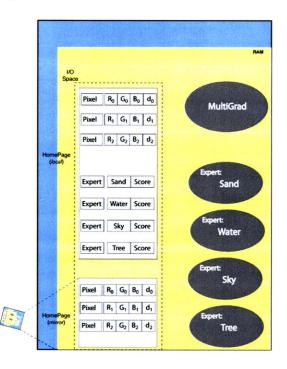

The programming model is built on three cornerstones; the process fragments, the shared memory partitions, and the embedded operating system (OS). Process fragments are autonomous, self contained computational elements that interact locally to perform coordinated tasks. Shared memory abstracts both the inter-process communication and the inter-particle transfer. The OS regulates the operating environment, schedules local resources and supports the process fragments with a collection of service functions packaged as a "toolkit".

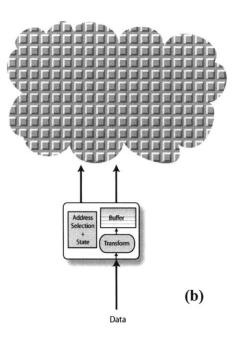

Once the programming model is in place, this text concludes by revisiting the model for I/O with the external environment. Additional detail is given on the required similarity between an I/O portal and a particle. The format and methods of data exchange are defined.

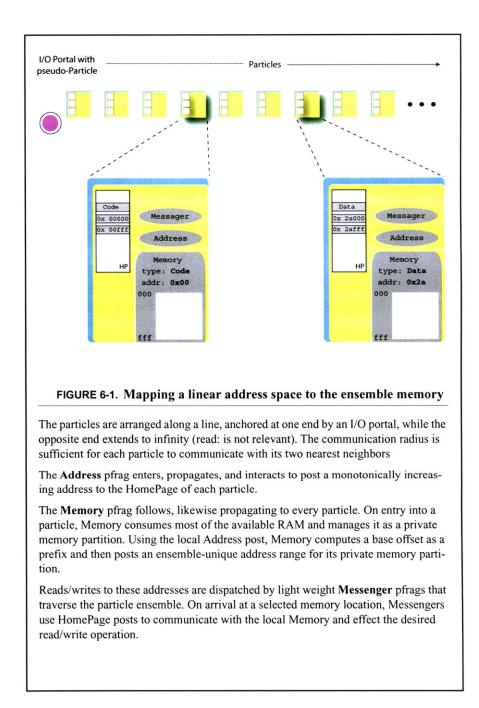

### **Particle Memory Organization**

Software on a *paintable* is organized into autonomous, self-contained executables referred to herein as "process fragments" (pfrags). All pfrags running on the particle's micro reside in the particle's RAM space. Most of the RAM is available for pfrag program and data. However a section of the RAM is reserved what is called the I/O space an area which is at least readable by any pfrag running on the particle's micro (fig. 3-6).

A subset of the I/O space is called the HomePage. The HomePage is an area where pfrags can both read and write tagged data. Any pfrag local to the particle can post to the HomePage. And posts to the HomePage are readable by all local pfrags.

The remainder of the I/O space is subdivided into mirrored instances of the Home-Pages of neighboring particles. When a pfrag on a given particle posts a piece of tagged data to the particle's HomePage, copies of that post appear at the mirror sites on all the neighboring particles. The caveat is that the latency in the mirroring operation is unconstrained.

The basic unit of information on these bulletin boards is the post — an instance of data that is tagged for identification. Posts are structured as key/value pairs, where the value component can be another key/value pair. The size of the posts is regulated by the particle's OS and is bounded by the space available on the HomePage.

The size of the local HomePage is determined by the particle's OS, which de-fragments the HomePage as necessary. The OS also dynamically maintains the size of

#### **Programming Model**

#### FIGURE 3-6. Organization of Particle's RAM

Most of the RAM is used as executable space for the currently running programs. However the IO space is reserved. A subset of the IO space — the HomePage — is available for programs to read and write tagged data. The remainder of the IO space is read-only.

the I/O space. For every neighbor with which a particle maintains an active contact, the OS allots a mirror site in the local I/O space for the neighbor's HomePage. The constituency of the neighborhood is periodically checked, and changes in the number of active neighbors<sup>11</sup> triggers an adjustment in the number of mirror sites.

Actual dimensions will necessarily be technology and task dependent. As an illustration, the simulations of the following chapters assumes a total particle RAM capacity of 50K words. Each HomePage is allotted 1K words. Each particle has an average of 15 neighbors, yielding an average I/O space of 16K words — roughly a third of the total RAM space.

Finally, two additional FIFO's are defined that support inter-particle transfer of the process fragments. The Bassinet is an input FIFO where incoming process frag-

<sup>11.</sup> Due to either a run time fault or the intentional appearance / disappearance of a particle.

ments are assembled during serial input. Similarly, the Launch Pad is a staging area where outgoing process fragments are buffered for streaming out to one of the neighboring particles.

## **Process Fragments**

The atomic element of the *paintable* programming model is the process fragment (pfrag). These are autonomous program entities that migrate among the particles and interact with the local environment. As a subclass of general computational processes, pfrags consist of coded behaviors and state. The state is internalized as data in a vector and the behaviors are defined by sequences of machine instructions. The additional restrictions that distinguish process fragments as a subclass can be reduced to three normative requirements:

- 1. They are self contained executables capable of fitting entirely in the RAM space of a single particle.

- 2. They gate their entire I/O through the I/O space in the particle's RAM, with writes directed to the HomePage and reads taken from anywhere in the I/O space.

- **3.** They define behavior for 5 functions which the particle's OS can issue to them at any time. These functions are public handles similar to the public methods of traditional Object Oriented Languages such as Java.

Sized to fit Conceptually, *paintable* process fragments are intended as self contained executables. In the strict sense, this means that no pfrag can allocate scratch memory or execute a branch instruction that points to an address outside the fragment's bounded address space. However, implementation has motivated three exceptions:

- A process fragment can request from the OS a parcel of scratchpad memory. This is a one time request that is made as part of the fragment's initial negotiations for entry into the particle. This memory is exclusively bound to the process fragment and is automatically freed when the fragment departs or is erased.

- The OS can also maintain a collection of library functions that it makes available to pfrags as needed<sup>12</sup>. The flip side is that a pfrag must be prepared for an instance when a requested function is not available.

<sup>12.</sup> See description of Pfrag Toolkit on page 42.

• Finally, while it is outside the spirit of this spec, there is nothing to stop a pfrag from using the HomePage as temporary data storage<sup>13</sup>.

**Gated I/O** All data traffic between a process fragment and its environment is gated through the I/O space and managed by calls to the OS. Data on the I/O space are organized as posts — variable length packets structured as key/value pairs.

Process fragments use OS function calls to query the number of neighboring HomePages that have been mirrored in the I/O space, to inquire as to the number of posts on a given HomePage mirror, to sense the available free space on the local HomePage, and to read / write the posts. These OS functions are limited to memory management. The OS has no capacity to interpret the keys in the posts or to preprocess the posts (i.e. no searching, sorting, or filtering). Pfrags must also be prepared for the case when lack of space on the HomePage causes posts to the HomePage to fail.

A process fragment receives the posts as a string of data with a reported length. It is up to the pfrag to interpret the keys in the post in order to assign meaning to the remaining data. There is no requirement that all posts be meaningful to all pfrags. Indeed, most posts will be indecipherable to most pfrags. The alternative would necessitate some sort of centrally maintained global semantic taxonomy — of potentially unbounded size. In the implementation of the following chapters, we circumvent this problem by limiting the key values to pfrag tags. These tags uniquely identify pfrag types and are assigned to the pfrag during authoring from a centrally maintained database accessible from the development environment.

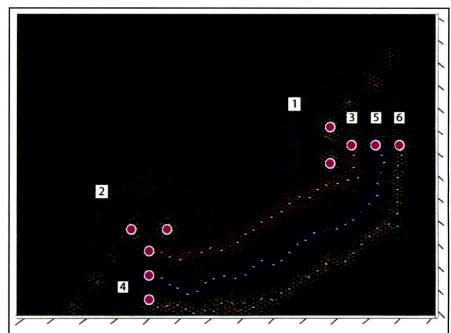

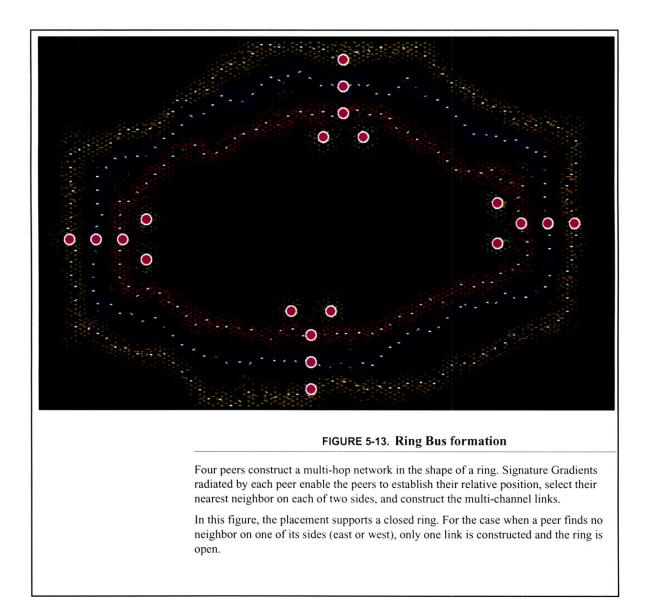

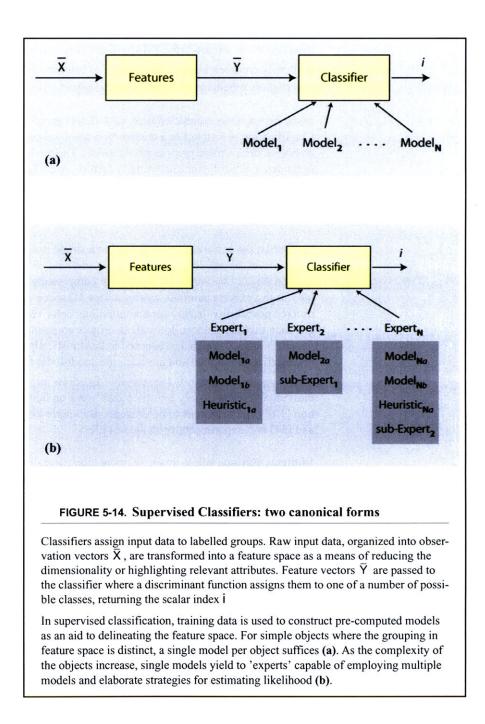

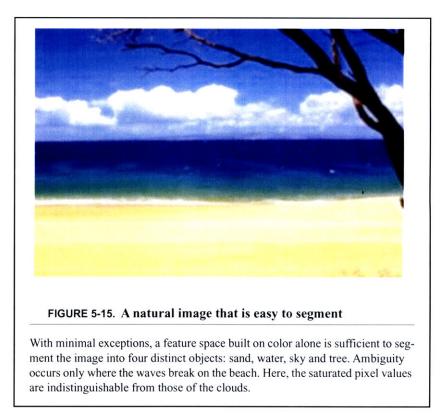

Process fragments do not communicate directly. Rather, they infer the type and state of other local pfrags from the posts in the HomePage. Currently, pfrags that wish to communicate with each other must do so by passing tagged posts back and forth through the HomePage. Work on the applications highlighted the shortcomings of this approach for data exchange. Future revisions of this spec will provide an alternative, probably involving message passing via the HomePage to set up DMA-style transfers between the pfrags.