## Cooperative Hierarchical Resource Management for Efficient Composition of Parallel Software

by

### Heidi Pan

Bachelor of Science in Electrical Engineering and Computer Science Massachusetts Institute of Technology, June 2001

Master of Engineering in Electrical Engineering and Computer Science Massachusetts Institute of Technology, June 2002

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

at the

### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

June 2010

JUL 1 2 2010

LIBRARIES

© Massachusetts Institute of Technology 2010. All rights reserved.

**ARCHIVES**

| Author        | ······································                                | ··· |

|---------------|-----------------------------------------------------------------------|-----|

|               | Department of Electrical Engineering and Computer Scien<br>May 21, 20 | ice |

|               | 1 - 1 1                                                               |     |

| Certified by. | Krste Asano<br>Associate Profess<br>Thesis Supervis                   | sor |

| Accounted by  |                                                                       |     |

| Accepted by   | Terry P. Orlan Chairman, Department Committee on Graduate Studen      | uu  |

### Cooperative Hierarchical Resource Management for Efficient Composition of Parallel Software

by

#### Heidi Pan

Submitted to the Department of Electrical Engineering and Computer Science on May 21, 2010, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

#### Abstract

There cannot be a thriving software industry in the upcoming manycore era unless programmers can compose arbitrary parallel codes without sacrificing performance. We believe that the efficient composition of parallel codes is best achieved by exposing unvirtualized hardware resources and sharing these cooperatively across parallel codes within an application.

This thesis presents *Lithe*, a user-level framework that enables efficient composition of parallel software components. Lithe provides the basic primitives, standard interface, and thin runtime to enable parallel codes to efficiently use and share processing resources. Lithe can be inserted underneath the runtimes of legacy parallel software environments to provide *bolt-on* composability – without changing a single line of the original application code. Lithe can also serve as the foundation for building new parallel abstractions and runtime systems that automatically interoperate with one another.

We have built and ported a wide range of interoperable scheduling, synchronization, and domain-specific libraries using Lithe. We show that the modifications needed are small and impose no performance penalty when running each library standalone. We also show that Lithe improves the performance of real world applications composed of multiple parallel libraries by simply relinking them with the new library binaries. Moreover, the Lithe version of an application even outperformed a third-party expert-tuned implementation by being more adaptive to different phases of the computation.

Thesis Supervisor: Krste Asanović

Title: Associate Professor

### Acknowledgments

I am extremely fortunate to have Professor Krste Asanović as my PhD advisor. He gave me incredible freedom to explore and mature. In fact, the Lithe project wouldn't have happened if he hadn't been so patient letting me learn my way up the system stack. He has also been my greatest resource, being so creative and knowledgeable. Thanks Krste for being such an amazing guiding force in my life for the past decade!

Thanks to Professor Arvind and Professor Saman Amarasinghe for agreeing to be on my committee, and for all of their great feedback on Lithe. Thanks again to Arvind for being my first and only UROP advisor, and introducing me to the wonders of computer architecture.

I am lucky to have met great mentors outside of school. Thanks to Robert Cohn, Geoff Lowney, and Joel Emer for always giving me great advice and encouragement. Thanks to Alan Khazei, who inspired me with the idea that any definition of a successful life must include serving others.

The best thing I did for Lithe was to convince Benjamin Hindman to join the project. He was an integral part of designing and implementing Lithe, as well as porting TBB and OpenMP. Being able to bounce ideas, get a fresh PL perspective, and simply hanging out into the wee hours working on paper submissions with him also made the project that much more enjoyable.

Thanks to Rimas Avizienis for porting his audio processing application to Lithe, and helping us to better understand real-time issues, especially since I seem to have a knack for needing him when he's at his busiest.

Thanks to Chris Batten for a conversation on the whiteboard of Cory Hall in the very early days of Lithe, in which he challenged me to really define what "scheduling" means. That led to our turning point of giving parent schedulers the control over how to allocate resources to their children, thus making Lithe into a truly hierarchically modular design. Chris' immense curiosity and logical reasoning has also been a real inspiration for me.

Thanks to Arch Robison for explaining the intricacies of TBB and IRML, as well as pointing us to the SPQR application. Thanks to Tim Davis for providing us with the SPQR code, and answering our many questions. Thanks to Greg Henry for helping us understand the behavior of MKL. Thanks to Niklas Gustafsson and David Callahan for interesting chats about ConcRT.

Rose Liu moved across the country with me three times in three consecutive years to follow Krste between Boston and Berkeley. I miss the days at ICSI, where we would dive into hours-long discussion on the topic of the day. I also never cease to be amazed at her tenacity to dig to the bottom of something.

I worked on the MTR project with Ken Barr. It was my first group project, and first

concrete project on SMPs. This was the project that really taught me how design something from scratch, and peaked my interest in cache coherence. Ken was also my hero for coming up with his own thesis topic from being inspired from a talk he attended.

Although I barely overlapped with Emmett Witchel in grad school, he not only set the precedence for systems research in our group, but the precedence for the design philosophy of providing efficient hardware mechanisms and enabling flexible software policies.

The people at MIT CSAIL taught me the important lesson of blurring the line between colleagues and friends. It was great to have gone through graduate school with Ronny Krashinsky, Michael Gordon, Sam Larsen, Mark Stephenson, Rodric Rabbah, Mark Hampton, Jessica Tseng, Steve Gerding, Jaewook Lee, Ian Bratt, Asif Khan, David Huynh, and many more.

Thanks to everyone at the ParLab for really opening my eyes up to the entire vertical stack, and making Berkeley instantaneously feel like a second home: Leo Meyerovich, Sam Williams, Kaushik Datta, Rajesh Nishtala, Archana Ganapathi, Bryan Catanzaro, Jike Chong, Barrett Rhoden, Kevin Klues, David Zhu, Karl Fuerlinger, Jimmy Su, Shoaib Kamil, Mark Hoemmen, Jim Demmel, John Kubiatowicz, Kurt Keutzer, Tim Mattson, and many more.

Thanks to Mary McDavitt for making it logistically possible for me to be physically on the West Coast and still graduate from MIT, and for making me feel like I still have roots back in Boston.

To Douglas Yeung and Alan Chen, the (only) other two undergrad friends my year who went for a PhD. To Vijay Janapa Reddi, who I'm really glad got stuck with me in a small cubicle at Intel Hudson for an entire summer.

I am blessed to be surrounded by loving friends and family. You know who you are, and I would be a completely different person without you in my life. Thanks to Michael Zhang for being my rock, and for being infinitely patient when I'm always stuck in grad school 3,000 miles away, regardless of which coast he's on. Thanks to my parents, Chung-Hsing Ouyang and Chung-Shih Pan, for being the most supportive and caring parents a girl could ever wish for.

# Contents

| 1 | Intr | roduction Parallel Programming Models              | 15<br>17   |

|---|------|----------------------------------------------------|------------|

|   | 1.2  | Composing Programming Models                       | 21         |

|   | 1.3  | Lithe Overview                                     | 24         |

| 2 | Coc  | operative Hierarchical Scheduling                  | 27         |

|   | 2.1  | Resource Model                                     | 27         |

|   | 2.2  | Cooperative Scheduler Hierarchy                    | 28         |

| 3 | Lith | ne Primitives                                      | 31         |

|   | 3.1  | Harts                                              | 31         |

|   | 3.2  | Contexts                                           | 32         |

| 4 |      | ne Scheduler Callback Interface                    | 33         |

|   | 4.1  | Transfer Callbacks                                 | 35         |

|   | 4.2  | Update Callbacks                                   | 37         |

| 5 |      | ne Runtime                                         | 39         |

|   | 5.1  | Runtime Interface                                  | 39         |

|   |      | 5.1.1 Functions for Sharing Harts                  | 39         |

|   |      | 5.1.2 Functions for Manipulating Contexts          | 43         |

|   | 5.2  | Runtime Implementation                             | 46         |

| 6 |      | •                                                  | <b>4</b> 9 |

|   | 6.1  | Task Scheduling Libraries                          | 49         |

|   |      | 6.1.1 Single-Program Multiple-Data (SPMD)          | 50         |

|   |      | 6.1.2 Threading Building Blocks (TBB)              | 52         |

|   | 6.2  | 6.1.3 OpenMP (OMP)                                 | 54<br>54   |

|   | 0.2  | 6.2.1 Barriers                                     | 56         |

|   | 6.3  | Domain-Specific Libraries                          | 58         |

|   | 0.0  | 6.3.1 Fastest Fourier Transform in the West (FFTW) | 58         |

| 7 | Eva  | luation                                            | 59         |

| • | 7.1  | Baseline Scheduling Library Performance            | 59         |

|   | 7.2  | Barrier Synchronization Case Study                 | 61         |

|   | 7.3  | Application Case Studies                           | 65         |

|   |      | 7.3.1 Sparse OR Factorization                      | 65         |

|    |      | 7.3.2 Real-Time Audio Processing              | 73 |

|----|------|-----------------------------------------------|----|

| 8  | Tow  | ard Composability                             | 79 |

|    | 8.1  | Implications for Application Development      | 79 |

|    | 8.2  | Implications for Parallel Runtime Development | 79 |

| 9  | Rela | ated Work                                     | 83 |

|    | 9.1  | Hierarchical Scheduling                       | 83 |

|    | 9.2  | Cooperative Scheduling                        | 85 |

|    | 9.3  | Global Resource Management Layer              | 86 |

| 10 | Con  | clusion                                       | 89 |

|    | 10.1 | Thesis Summary and Contributions              | 89 |

|    | 10.2 | Future Work                                   | 90 |

# List of Figures

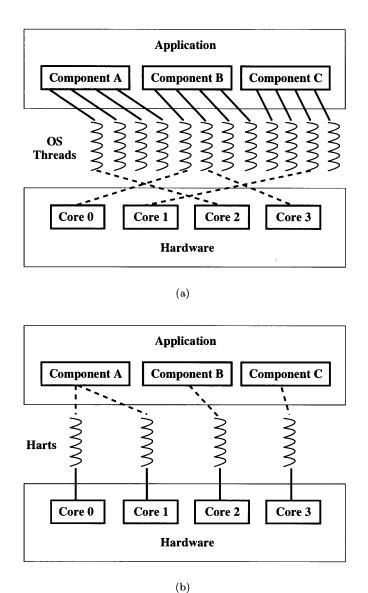

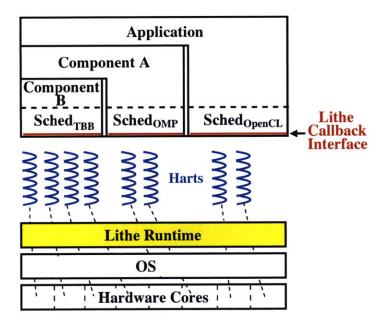

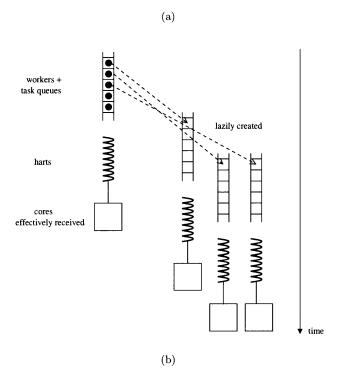

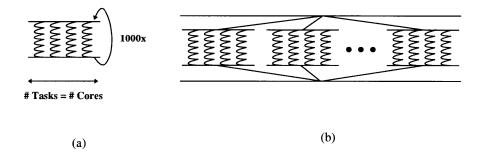

| 1-1 | (a) In conventional systems, each component is only aware of its own set of virtualized threads, which the operating system multiplexes onto available physical cores. (b) Lithe provides unvirtualized processing resources, or harts, which are shared cooperatively by the components, preventing resource oversubscription.                                                                                                           | 18 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

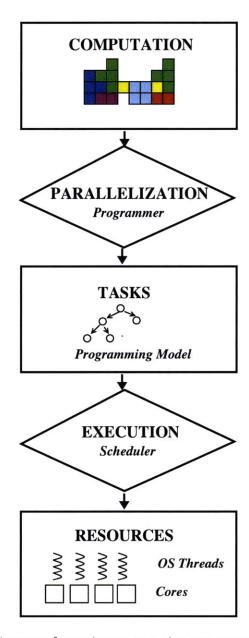

| 1-2 | The two main steps of mapping computation onto resources, encapsulated within each parallel software component. First, the programmer decomposes the computation into tasks. Then, the scheduler executes the tasks with its resources. The parallel programming model provides the task abstraction, and governs how computation behaviors and needs are translated into execution policies.                                             | 19 |

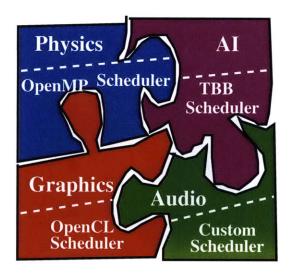

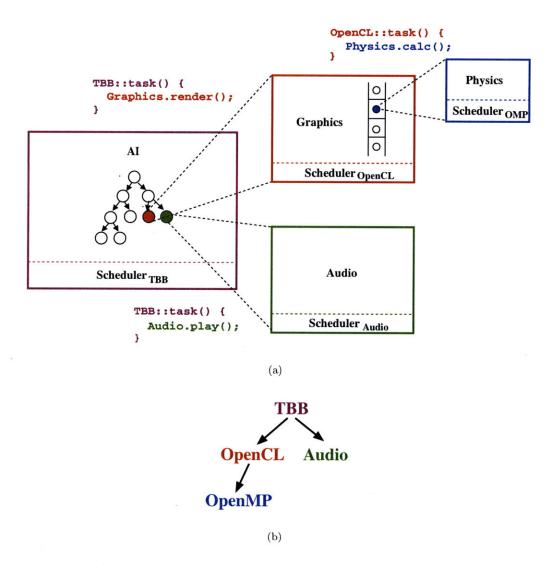

| 1-3 | An example gaming application composed of several parallel components, which are built in turn using different parallel libraries. The physics component is written using OpenMP [CMD <sup>+</sup> 01]. The AI component is written using TBB [Rei07], the graphics component is written using OpenCL [Gro].                                                                                                                              |    |

| 1-4 | The audio component is written using a customized framework                                                                                                                                                                                                                                                                                                                                                                               | 21 |

| 1-5 | The system stack with Lithe. Lithe establishes a hierarchy of schedulers based on the call structure of their corresponding computation. Each scheduler implements the standard Lithe callback interface, and calls into the Lithe runtime to use Lithe primitives for parallel execution.                                                                                                                                                | 24 |

| 2-1 | (a) The hierarchical call structure of the example gaming application. The AI component invokes the graphics and audio components as two of its TBB tasks. The graphics component, in turn, invokes the physics component as one of its OpenCL tasks. (b) The corresponding hierarchy of schedulers. TBB allocates resources between OpenCL, the custom audio scheduler, and itself. OpenCL allocates resources between OpenMP and itself | 29 |

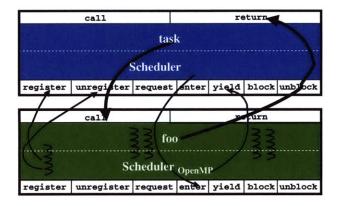

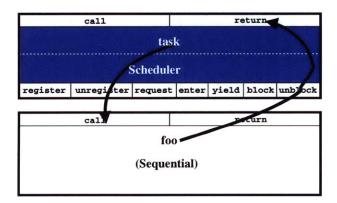

| 4-1 | The Lithe scheduler callback interface, which is orthogonal to the function call interface, enables the plug and play of an OpenMP, Cilk, or sequential implementation of foo. Furthermore, there is a separation of concerns between the high-level functionality of task invoking foo, and the low-level resource management of their respective schedulers exchanging harts                                                            | 34 |

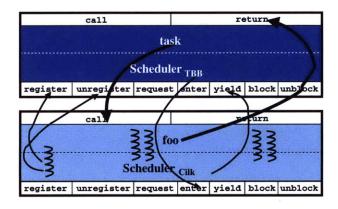

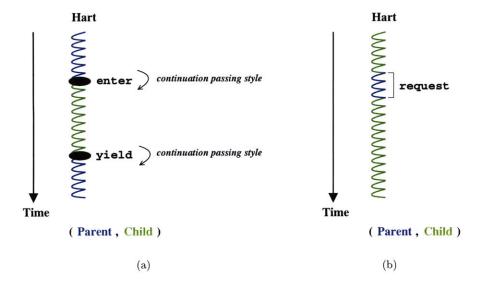

| 4-2        | (a) Transfer callbacks transfer control of the hart from one scheduler to another in continuation-passing style. (b) Update callbacks allow a scheduler to borrow a hart temporarily to process the given information and update its internal state.  An example scheduler using its task queue to manage two of its harts from independent enter callbacks.                                                     | 35<br>37        |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 5-1        | <ul><li>(a) foo is written in Cilk, and begins by instantiating a Cilk scheduler, which registers itself to obtain control of the current hart from the TBB scheduler.</li><li>(b) The same foo function can be reused in an OpenMP loop, since the Cilk scheduler is insulated from its parent scheduling environment, and does not care whether it is communicating with TBB or OpenMP as its parent</li></ul> | 41              |

| 5-2        | An example of how multiple harts might flow between a parent and child scheduler                                                                                                                                                                                                                                                                                                                                 | 42              |

| 5-3        | An example of transitioning from one context to another in a continuation-passing style using the Lithe runtime functions. A scheduler's enter callback starts on the transition context, launches a new context to run tasks, cleans                                                                                                                                                                            | 12              |

| - 1        | up that context using the transition context, then resumes another context.                                                                                                                                                                                                                                                                                                                                      | 44              |

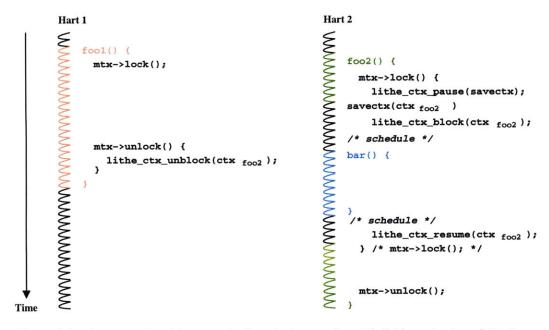

| 5-4<br>5-5 | Pseudocode example of a Lithe-compliant mutex lock                                                                                                                                                                                                                                                                                                                                                               | 45              |

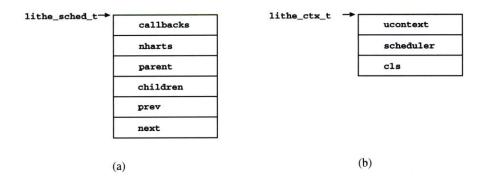

| 5-6        | the hart to execute bar, then resumes the unblocked context of foo2 The internal Lithe scheduler and context objects                                                                                                                                                                                                                                                                                             | $\frac{46}{46}$ |

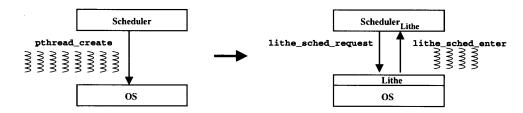

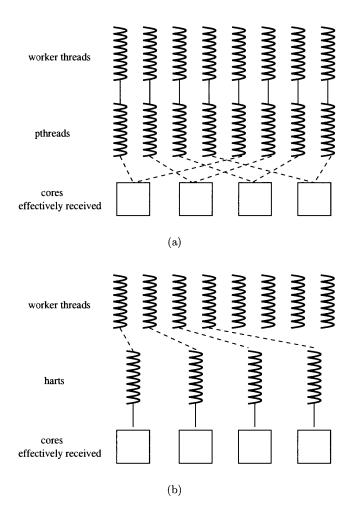

| 6-1        | Porting a scheduler to use Lithe replaces arbitrary pthread creation with                                                                                                                                                                                                                                                                                                                                        | <b>5</b> 0      |

| 6-2        | explicit requests for harts                                                                                                                                                                                                                                                                                                                                                                                      | 50<br>51        |

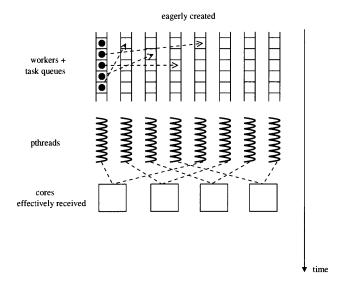

| 6-3        | (a) The original TBB implementation creates as many workers as the number of cores it thinks it has, without regard to other libraries within the application. (b) The Lithe TBB implementation lazily creates workers as it receives                                                                                                                                                                            |                 |

| 6-4        | more harts over time                                                                                                                                                                                                                                                                                                                                                                                             | 53              |

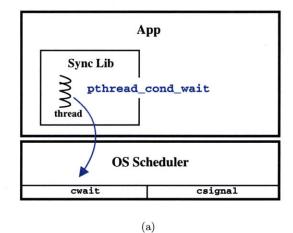

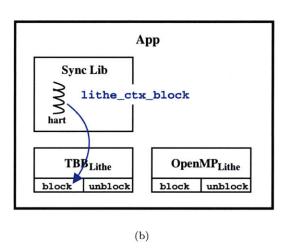

| 6-5        | necessary context switching and interference                                                                                                                                                                                                                                                                                                                                                                     | 55<br>57        |

|            | back to its user-level scheduler using lithe_ctx_block                                                                                                                                                                                                                                                                                                                                                           | 57              |

| 7-1        | (a) The baseline barrier microbenchmark of N SPMD tasks synchronizing with each other 1000 times at back-to-back barrier rendezvous. (b) Launching multiple baseline barrier microbenchmarks in parallel to examine the behavior of different barrier implementations in the face of parallel composition.                                                                                                       | <i>G</i> 1      |

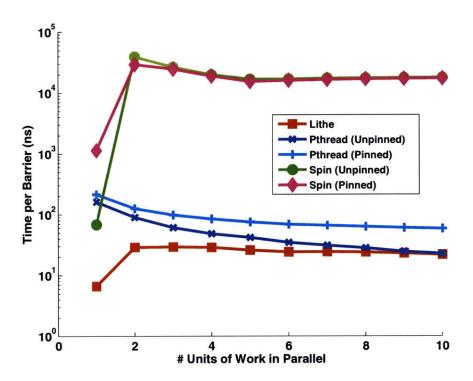

| 7-2        | Performance of different barrier implementations under different parallel composition configurations in terms of runtime in nanoseconds.                                                                                                                                                                                                                                                                         | 61<br>64        |

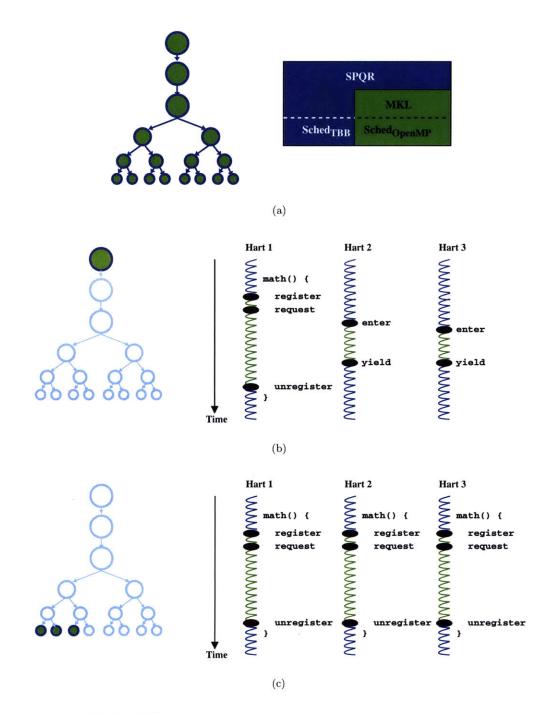

| 7-3         | (a) The SPQR computation represented as a task tree, where each task per-    |    |

|-------------|------------------------------------------------------------------------------|----|

|             | forms several parallel linear algebra matrix operations. The corresponding   |    |

|             | software stack for Tim Davis' implementation is also shown, where tasks are  |    |

|             | written using TBB, and each of the tasks calls MKL routines that are paral-  |    |

|             | lelized internally using OpenMP. (b) The execution of SPQR with Lithe at     |    |

|             | the point where only one task is executing and OpenMP gets all the harts.    |    |

|             | (c) The execution of SPQR with Lithe at the point where many tasks are       |    |

|             | executing and each OpenMP uses its only hart                                 | 66 |

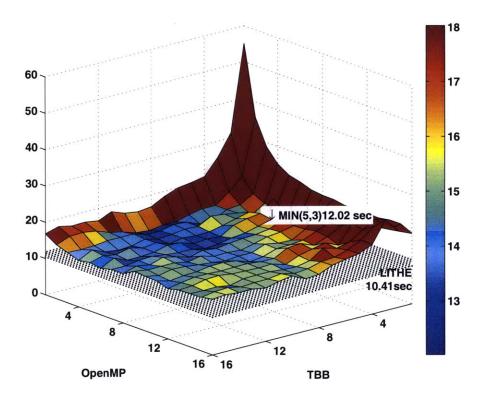

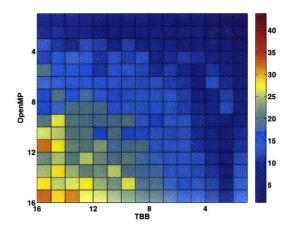

| 7-4         | Runtime in seconds for the original SPQR implementation across different     |    |

|             | thread allocations to TBB and OpenMP for the deltaX input matrix, com-       |    |

|             | pared with Lithe                                                             | 67 |

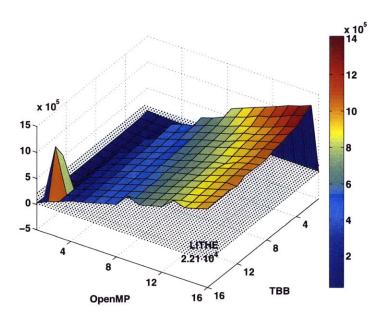

| 7-5         | Average number of runnable OS threads for the original SPQR implementa-      |    |

|             | tion across different thread allocations to TBB and OpenMP for the deltaX    |    |

|             | input matrix                                                                 | 69 |

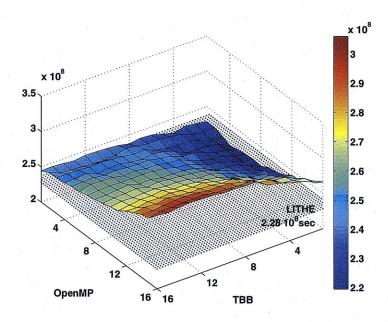

| 7-6         | Number of OS context switches for the original SPQR implementation across    |    |

|             | different thread allocations to TBB and OpenMP for the deltaX input matrix,  |    |

|             | compared with Lithe                                                          | 69 |

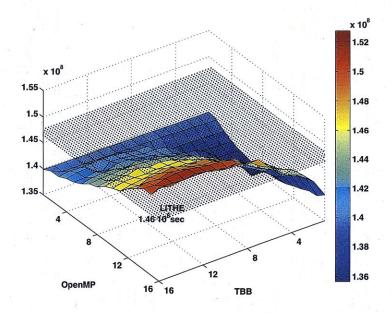

| 7-7         | Number of L2 data cache misses for the original SPQR implementation across   |    |

|             | different thread allocations to TBB and OpenMP for the deltaX input matrix,  |    |

|             | compared with Lithe                                                          | 70 |

| 7-8         | Number of data TLB misses for the original SPQR implementation across        |    |

|             | different thread allocations to TBB and OpenMP for the deltaX input matrix,  |    |

|             | compared with Lithe                                                          | 70 |

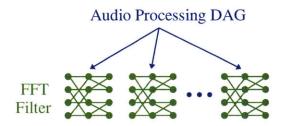

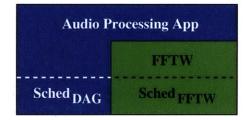

| 7-9         | The audio processing application consists of a DAG that applies an FFT       |    |

|             | filter to each of its input channels. The implementation composes a custom   |    |

|             | DAG scheduler with the FFTW scheduler                                        | 73 |

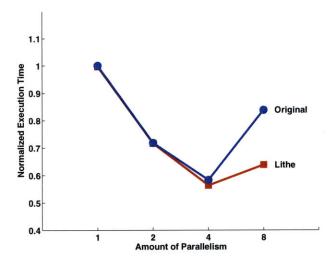

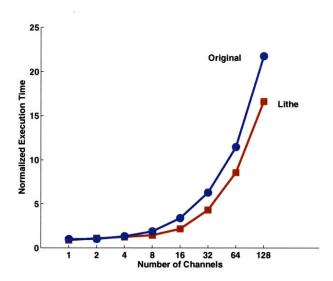

| 7-10        | Performance comparison of the original and ported implementation of the      |    |

|             | FFTW library computing an FFT of size 131,072.                               | 75 |

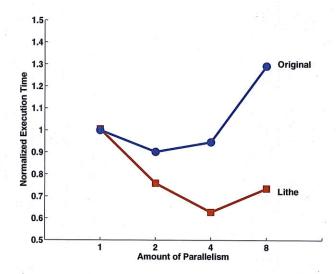

| 7-11        | Performance comparison of the original and ported FFTW implementation        |    |

| <b>=</b> 10 | of the FFTW library computing an FFT of size 32,768                          | 76 |

| 7-12        | Performance of the audio processing application with varying number of input | -  |

|             | channels with and without Lithe-compliant schedulers                         | 77 |

# List of Tables

| 4.1  | The standard Lithe callbacks                                                                                                                                                                                                                                                                             | 33  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.1  | The Lithe runtime functions and their corresponding scheduler callbacks. Note that the function, fn, passed to lithe_ctx_pause takes the current context as an argument                                                                                                                                  | 40  |

| 7.1  | Comparison of the standalone performance for the original and Lithe-compliant implementations of TBB, as measured in average runtime in seconds for three different microbenchmarks.                                                                                                                     | 60  |

| 7.2  | Comparison of the standalone performance for the original and Lithe-compliant implementations of OpenMP, as measured in average runtime in seconds for                                                                                                                                                   |     |

| 7.3  | three different microbenchmarks                                                                                                                                                                                                                                                                          | 61  |

| 1.0  | scheduling libraries.                                                                                                                                                                                                                                                                                    | 61  |

| 7.4  | The different barrier implementation and their compatible scheduler implementations. Refer back to Section 6.2.1 for details on the individual barrier implementations, and refer back to Section 6.1.1 for more details on the individual SPMD scheduler implementations. There are five total possible | 62  |

| 7.5  | barrier/scheduler configurations evaluated in this thesis                                                                                                                                                                                                                                                | 68  |

| 7.6  | SPQR (TBB/OpenMP) performance with and without Lithe on a 16-core AMD Barcelona (runtime in seconds)                                                                                                                                                                                                     | 68  |

| 7.7  | SPQR Context Switches                                                                                                                                                                                                                                                                                    | 71  |

| 7.8  | SPQR L2 Data Cache Misses                                                                                                                                                                                                                                                                                | 72  |

| 7.9  | SPQR Data TLB Misses.                                                                                                                                                                                                                                                                                    | 72  |

| 7.10 | SPQR (TBB/OpenMP) performance with and without Lithe on a 8-core                                                                                                                                                                                                                                         | . – |

|      | Intel Clovertown (runtime in seconds)                                                                                                                                                                                                                                                                    | 72  |

## Chapter 1

# Introduction

Building applications by composing modular libraries is a cornerstone of software engineering. Modularity enhances productivity. Functionality can be implemented once, and reused in different contexts and applications. Different libraries can be designed, built, and maintained independently by different teams. A complex application can be decomposed into smaller library modules that are easier to reason about. Modularity can also help with performance. A programmer can leverage the performance of a highly optimized library without having the expertise and time needed to achieve that level of sophistication. Finally, modularity enables specialization. Each library can implement its functionality in the most efficient manner, without having to accommodate the needs of other libraries and incurring the overhead of generalization. Each library can also use high-level, tailored abstractions that are most natural for expressing its own computation. Different libraries can choose different productivity-performance tradeoffs. A performance-critical portion of an application can be hand-coded in assembly, while a user interface portion can be written in a domain-specific language to enable rapid functionality updates.

With the increasing adoption of multicore microprocessors and parallelization of software libraries, modularity is evermore important. Parallel programming is hard. It is difficult to write correct, let alone optimized, parallel software. Programmers must be able to leverage each other's efforts through code reuse. Most programmers will not understand parallelism, and instead work at a higher abstraction level, so they must be able to use libraries without caring whether the libraries are parallel or sequential. Furthermore, we expect specialization to play a big role in delivering energy-efficient performance. Having more, but simpler, cores shifts much of the responsibility for attaining performance from hardware to software. But this also opens up the opportunity for software to leverage code-specific information to achieve the desired level of performance more efficiently, which is especially crucial now that battery life and electricity bills are first-order concerns.

Unfortunately, today's software cannot be modular because parallel composition does not work well. Composing disparate parallel libraries within an application can often cause the libraries to interfere with one another and degrade the overall performance. In fact, a parallel implementation of an application may actually run slower than a sequential implementation [Daved]. Current day parallel software vendors are becoming increasingly aware of this problem, but have only supplied ad hoc solutions. For example, Intel's Math Kernel Library (MKL) advises against using more than one parallel library within an application. It instructs its clients to call the *sequential* version of the library whenever it might be running in parallel with another part of the application [Int07]. Such solutions destroy any separation between interface and implementation, and place a difficult burden on programmers who have to manually choose between different library implementations depending on the calling environment. Worse still, a programmer writing a new parallel library that encapsulates MKL will just export the problem to its clients.

The crux of the problem is that systems today provide an inadequate foundation for building parallel programs: OS threads. The operating system exports threads as the abstraction for processing resources. User-level codes can create as many threads as they want, and map their computation onto these threads for parallel execution. The OS then time-multiplexes the threads onto the physical cores. However, threads are not free. The more threads there are, the more time it takes the OS to cycle through all of them, causing each thread to run at more infrequent and unpredictable times. Computation that is supposed to be tightly synchronized may not be able to run simultaneously, causing gratuitous waiting. Too many threads can also easily lead to resource oversubscription. More threads of execution will likely access more data, kicking each other's working set out of the shared caches and causing more TLB misses and page faults. Furthermore, most parallel codes cannot achieve perfect scalability, so using more threads to do the same amount of work produces diminishing returns.

One common solution is for user-level codes to only create as many OS threads as there are physical cores in the machine. However, this is a difficult goal to achieve in a modular fashion. Even if each software component creates a reasonable number of threads, the application can still collectively create too many threads when its components run in parallel. Hence, we need a systemic solution to coordinate the different software components within an application, rather than having the components implicitly use and share the machine resources by creating OS threads.

This thesis presents *Lithe*, a framework that enables efficient composition of parallel software components. Lithe provides the basic primitives, standard interface, and thin runtime to enable parallel codes to efficiently use and share processing resources. In particular, Lithe replaces the virtualized thread abstraction with an unvirtualized *hardware thread* primitive, or *hart*, to represent a processing resource (Figure 1-1). Whereas threads provide the false illusion of unlimited resources, harts must be explicitly allocated and shared amongst the different software components. Lithe can be inserted underneath the runtimes of legacy parallel software environments to provide *bolt-on* composability – without changing a single line of the original application code. Lithe can also serve as the foundation

for building new parallel abstractions and runtime systems that automatically interoperate with one another.

### 1.1 Parallel Programming Models

To better understand the overall composition problem, it helps to first understand the individual components that may be composed. This section describes how each parallel software component is built using a particular programming model, and the potential diversity of programming models that can be composed.

Each parallel software component encapsulates a computational problem to be computed by multiple processing resources. Its programming model governs how computational behaviors and needs are translated into execution policies. Figure 1-2 shows the typical steps in using a programming model to map computation onto resources. First, a programmer decomposes the computation into smaller, independent units of work, or *tasks*. Then, a language or library runtime – a *scheduler* – decides where and when to run the tasks. A programming model improves productivity by equipping the programmer with abstractions for framing the problem. It improves performance by equipping the scheduler with information on how the work should be executed. Finally, it improves efficiency by directly conveying pertinent information between the programmer and the scheduler.

Parallel programming models can vary in three main dimensions: computational pattern, level of abstraction, and restrictions on behavior. We describe each of those dimensions below, and discuss how choosing different design points along a dimension can affect productivity, performance, and efficiency.

1. Different programming models may embody different computational patterns [Mat04]. It is more natural to express certain types of computations using certain programming models. For example, fork-join parallelism is often well-suited for divide-and-conquer algorithms [BJL<sup>+</sup>95], whereas pipeline parallelism is often well-suited for video decoding algorithms [DHRA06]. The right programming model also helps the programmer decompose the computation in a way that minimizes the dependencies between the tasks. This boosts productivity, as fewer interface dependencies lead to a cleaner, more modular software architecture. This also boosts performance, as fewer data dependencies translate into less synchronization overhead and fewer scheduling restrictions. Furthermore, each computational pattern may encapsulate information that can be used by schedulers to order and co-locate tasks intelligently. For example, a transactor [Asa07] represents a group of tasks sharing state that should be scheduled onto the same core to maximize locality. Transactors connected by channels should be co-scheduled on neighboring cores to minimize communication costs. Using an appropriate programming model improves productivity and efficiency by sparing the programmer from having to annotate low-level performance-critical information and

Figure 1-1: (a) In conventional systems, each component is only aware of its own set of virtualized threads, which the operating system multiplexes onto available physical cores. (b) Lithe provides unvirtualized processing resources, or harts, which are shared cooperatively by the components, preventing resource oversubscription.

Figure 1-2: The two main steps of mapping computation onto resources, encapsulated within each parallel software component. First, the programmer decomposes the computation into tasks. Then, the scheduler executes the tasks with its resources. The parallel programming model provides the task abstraction, and governs how computation behaviors and needs are translated into execution policies.

the scheduler from having to process the annotations.

- 2. The level of abstraction may vary widely for different types of programming models. Domain experts with only tangential knowledge of programming may want to use high-level domain-specific abstractions. For example, MAX/MSP [Cyc] enables musicians to use a graphical drag-and-drop "language" interface to compose music synthesis building blocks, such as filters and oscillators. While higher-level abstractions may come with a heavier performance tax [BBK09], they enable non-experts to become productive, and create opportunities to convey domain-specific information that is relevant to scheduling decisions in a natural and efficient manner. A musician could use a language construct to express multiple input channels, for example, which would inform the language runtime scheduler about the potential parallelism between the channels. In contrast, that domain-specific knowledge about channels being independent may become lost if the musician were to use a more general programming model, or if the channel construct were implemented by layering on top of a more general abstraction. On the other hand, a low-level system programmer may know exactly how a computation should be executed to wring out every last drop of performance. Such a programmer could use low-level language constructs, such as Go's co-routines [Goo] to control the ordering of tasks, or Sequoia's array blocking and task mapping primitives [FKH<sup>+</sup>06] to control the movement of data across the memory hierarchy.

- 3. Programming models are often useful because of what they forbid, rather than what they allow. Restricting the space of possible behaviors makes the code easier to understand and more likely to be correct. A deterministic language can greatly reduce complexity, improve debuggability, and curtail data races when nondeterminism is not needed [BAAS09]. Partitioned global address space (PGAS) languages define data objects to be private by default, and help to prevent unintended sharing that often leads to hard-to-find bugs [YBC+07]. A more restrictive programming model can also simplify the corresponding runtime and scheduler. A general hierarchical task model may warrant a generic stack frame to represent each task, scheduling queues to store dynamically spawned tasks, and a sophisticated work-stealing algorithm to load balance the tasks. In contrast, a simpler data-parallel model could be implemented with just a global atomic counter that tracks the index of the next array element to be processed.

Using the wrong programming model for a particular computation can result in subpar performance. For example, Cilk [BJL<sup>+</sup>95] is considered to be high-performance and general purpose. However, it lacks expressiveness and destroys cache locality for certain linear algebra operations, achieving worse performance than an equivalent pipeline implementation [KLDB09]. Cilk has a fork-join programming model that enforces the completion of

Figure 1-3: An example gaming application composed of several parallel components, which are built in turn using different parallel libraries. The physics component is written using OpenMP [CMD+01]. The AI component is written using TBB [Rei07], the graphics component is written using OpenCL [Gro]. The audio component is written using a customized framework.

all child tasks before executing their parent's successor. In contrast, the pipeline model imposes no such false dependencies, allowing the necessary operations to be overlapped to avoid gratuitous idling. Additionally, Cilk is designed for divide-and-conquer algorithms, so it assumes that tasks within the same subtree of the task graph share the same data. But the most natural way of expressing the linear algebra computation in Cilk results in subtrees that contain tasks of the same type of operation working on different sets of data. The pipeline model is able to execute operations that share data consecutively on the same core. An alternate Cilk implementation groups operations that share data into the same task, which improves the locality but creates load imbalance and exacerbates the idling problem.

To achieve its desired level of productivity, performance, and efficiency, each component needs to utilize an appropriate programming model. Thus, we need to support the efficient composition of multiple parallel programming models.

### 1.2 Composing Programming Models

In practice, an application can be composed of many different parallel programming models. Figure 1-3 shows an example gaming application that incorporates physics, graphics, audio, and AI components. Each component can be built using a different parallel library or language, because they have very different computational behaviors and constraints (as described Section 1.1), or simply contain legacy or third-party codes that cannot be changed.

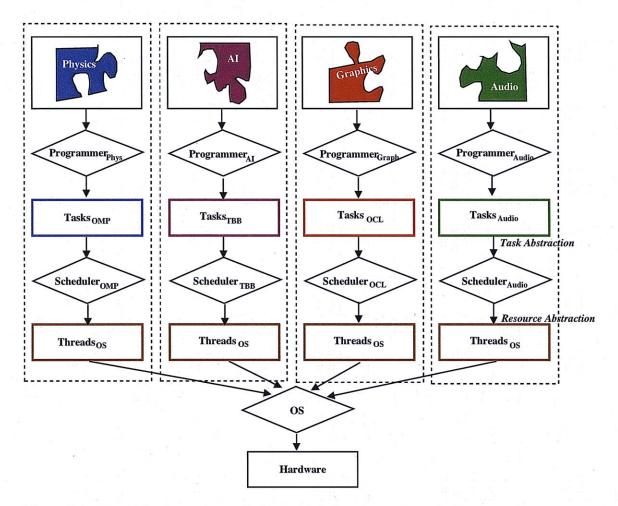

Figure 1-4: The main steps of mapping computation onto resources in the face of composition. Each scheduler supports a potentially different task abstraction, but uses the same resource abstraction. Each parallel software component is parallelized and managed independently, leaving the integration of components to the OS.

There are numerous potential complications in composing these heterogeneous components, from transposing data between different formats, to creating new language bindings. This thesis chooses to address a challenge that is unique to composing parallel components: the composition of multiple schedulers.

Figure 1-4 shows the steps of mapping computation onto resources in the face of composition. Each scheduler supports a potentially different task abstraction, but uses the same resource abstraction. The operating system virtualizes processing resources using threads to provide schedulers with autonomy and a clean execution environment. A scheduler operates on its own set of OS threads, and does not need to know about other schedulers. Each parallel software component is parallelized and managed independently, leaving the integration of components to the OS. This enables each component to be specialized by using an appropriate programming model, while enabling multiple parallel programming models to co-exist within the same application.

However, resource virtualization only provides design modularity, not performance isolation. Although each component's computation is decomposed and mapped independently onto its own OS threads, the different components can still interfere with one another during execution when all threads are time-multiplexed onto the same set of processing resources. Components can collectively create too many threads and a large memory footprint, inadvertently causing resource oversubscription and cache thrashing. Worse yet, schedulers often cannot function properly because they naively assume uninterrupted access to all of the machine's resources. A work-stealing scheduler [BJL+95, Rei07] should only spend the effort of stealing more tasks to execute on an "idle" core if no other schedulers are using that core. Ordering tasks to maximize the temporal reuse of cache-sized data blocks [WOV+07, TSG07] only works if no other schedulers are using the same cache. Overlapping the computation of the current task with prefetches for the next task to hide the latency of data transfers [TSG07] becomes useless if another scheduler evicts the prefetched data before it can be used. The execution behavior of each software component depends heavily on the OS thread-multiplexing policy and other components. It is thus difficult for any one scheduler to reason about its own behavior, let alone optimize its performance.

The main challenge, then, is to preserve design modularity between parallel software components, while giving each component more control over its own execution. We argue that this is best achieved by exposing *unvirtualized* hardware resources and sharing them cooperatively across parallel components within an application. Each scheduler would manage its own set of resources. This provides schedulers with the same type of autonomy and freedom to specialize as they had when managing their own threads. But given unvirtualized resources, the schedulers can now be effective in managing the parallel execution of its computation. The only tradeoff is that schedulers have to be cognizant of the fact that they may be sharing the machine resources with other schedulers. We believe that this slight increase in the complexity of low-level scheduling code is a small price to pay

Figure 1-5: The system stack with Lithe. Lithe establishes a hierarchy of schedulers based on the call structure of their corresponding computation. Each scheduler implements the standard Lithe callback interface, and calls into the Lithe runtime to use Lithe primitives for parallel execution.

to gain not only performance and efficiency, but also separation of concerns. High-level application developers can productively compose arbitrary libraries, instead of needing to understand the implementation of each library to avoid destroying performance through combining multiple parallel programming models.

#### 1.3 Lithe Overview

This thesis presents Lithe, a framework for schedulers to dynamically and flexibly share processing resources. Lithe provides a minimal common ground to enable an arbitrary and diverse set of schedulers to interoperate and compose efficiently. Lithe consists of the following components, as illustrated in Figure 1-5:

- Lithe establishes a cooperative, hierarchical relationship between all schedulers within an application based on the hierarchical call structure of their corresponding computation. The scheduler hierarchy distributes control over processing resources in a modular, specializable fashion. Parent schedulers choose how to allocate resources for their child schedulers to use, but do not micromanage how these children use the given resources.

- Lithe exports basic *primitives* for schedulers to use and share processing resources.

A hart represents a processing resource that is explicitly allocated and shared. A

context acts as the execution vessel for the computation running on the hart, so that the current computation can be suspended (and perhaps resumed elsewhere) without blocking the current hart.

- Lithe defines a standard scheduler callback interface that is implemented by all schedulers that want to manage their own harts and interoperate with other schedulers.

The callbacks encapsulate how a scheduler manages harts and child schedulers.

- Lithe provides a thin, user-level runtime system to facilitate the sharing of harts between schedulers, as well as execution with contexts. The runtime keeps track of the scheduler hierarchy, connecting children with their parent and invoking the appropriate callbacks to transfer harts between schedulers. The runtime also starts, pauses, and resumes contexts on behalf of their corresponding scheduler.

# Chapter 2

# Cooperative Hierarchical Scheduling

This chapter describes Lithe's cooperative hierarchical scheduling model that enables modularity and specialization of parallel codes without sacrificing overall application performance. Lithe advocates explicit resource sharing, rather than resource virtualization, to compose an arbitrary number of schedulers to use a finite set of machine resources. Below, we describe the common resource model used by each scheduler, and the hierarchical interaction between the schedulers to share resources.

#### 2.1 Resource Model

The Lithe resource model presents an accurate view of the machine resources that enables parallel components to achieve efficient modular scheduling. At any point in time, each scheduler is allocated an exclusive subset of the resources available to the application. Since an application can potentially employ many schedulers, each scheduler may not get as many resources as it would like. But once a scheduler is allocated a resource, it can do whatever it wishes with that resource. A scheduler also keeps its resources until it explicitly releases them. This cooperative resource model ensures that no other schedulers within the same application can use those resources simultaneously and cause unintentional interference. In addition, a scheduler can allocate and yield each of its resources independently to enable efficient fine-grained sharing. This curbs resource undersubscription by allowing a scheduler to relinquish individual resources whenever they are not needed, such as when a scheduler has to wait for additional tasks to be spawned, or for a synchronization or long-running I/O operation to complete.

Lithe enables modular scheduling by introducing resource sharing into the interface between parallel software components. Each software component encapsulates functionality, data, and execution control flow. While sequential components only specify a single thread

of control, parallel components may encapsulate multiple threads of control that may change dynamically based on the amount of available resources. With Lithe, each parallel component is given processing resources to manage without external interference or concern. In contrast to using virtualized resources, each scheduler can now precisely control the parallel execution of its computation and adapt its behavior to the number of available resources, rather than simply delineating the potential parallelism by specifying an arbitrary number of threads of execution a priori.

### 2.2 Cooperative Scheduler Hierarchy

Lithe establishes a hierarchy of schedulers for cooperatively sharing resources based on the hierarchical call structure of their corresponding computation. Each software component within an application can be a hierarchical composite of other software components. One component's "task" can contain both computation and a scheduler to manage that computation. Figure 2-1(a) shows the hierarchical structure of the gaming application example from Section 1.2. The AI component controls all of the gaming logic, and is implemented using TBB tasks. It invokes a graphics component to render some objects as one of its tasks, and invokes an audio component to play some sounds as another task. The graphics component, in turn, invokes a physics component as one of its OpenCL tasks to calculate the trajectory for each rendered object.

Figure 2-1(b) shows the corresponding scheduler hierarchy. The scheduler of the calling component is the *parent*, while the scheduler of the callee is the *child*. A parent scheduler allocates resources to its child schedulers, and its children give back the resources when they are done with them. By coupling resource allocation with control flow, Lithe makes each caller responsible for providing its callees with the resources needed to perform work on its behalf. This is already true in the sequential world, where a caller implicitly grants its only processing resource to a callee until the callee returns.

The scheduler hierarchy distributes control over resources in a hierarchically modular fashion. Every scheduler only has to communicate with its parent and its children. Peer schedulers are insulated from having to know about each other. Each leaf scheduler maps its unit tasks onto its allocated resources. Each parent scheduler "schedules" its composite tasks by deciding how to allocate its resources between the corresponding child schedulers. This enables a scheduler to prioritize between its tasks and accurately account for the usage of its own resources. But a parent does not micromanage how its children use their given resources, allowing the children to specialize as they please.

Figure 2-1: (a) The hierarchical call structure of the example gaming application. The AI component invokes the graphics and audio components as two of its TBB tasks. The graphics component, in turn, invokes the physics component as one of its OpenCL tasks. (b) The corresponding hierarchy of schedulers. TBB allocates resources between OpenCL, the custom audio scheduler, and itself. OpenCL allocates resources between OpenMP and itself.

## Chapter 3

## Lithe Primitives

Lithe provides two basic primitives, harts and contexts, to enable schedulers to perform efficient parallel execution. The *hart* primitive represents a bare-metal processing resource. The *context* primitive acts as the execution vessel for computation to run on a hart. This chapter describes each of these primitives in more detail, while the next two chapters describe how schedulers can use the Lithe callback and runtime interfaces to operate on these primitives.

#### 3.1 Harts

A hart, short for hardware thread, represents a processing resource. Within an application, there is a fixed one-to-one mapping between a hart and a physical hardware thread. There is typically one hardware thread per physical core, except for multithreaded machines like SMTs [TEE<sup>+</sup>96] where there are multiple harts per core.

The hart primitive is fundamentally different from the OS thread abstraction. Whereas a scheduler can create an unlimited number of threads on-demand, a scheduler must explicitly request harts and only use the harts that it is allocated. Threads can also be used to support various levels of abstractions. A scheduler can create as many threads as there are physical cores in the machine, and use them as a resource abstraction. Or a scheduler can create as many threads as there are tasks, and export them as a programming abstraction to its user. In contrast, a hart only represents resources, and a scheduler must explicitly multiplex its tasks onto its harts.

At any point in time, a hart is managed by exactly one scheduler, and each scheduler knows exactly which harts are under its control. We call the scheduler that is currently managing a hart the *current scheduler*. The current scheduler of a hart has exclusive control over not only the physical processing units, but also any private caches, TLB, and local store associated with the hardware thread. This prevents unintended inter-component cache and TLB thrashing, as well as unnecessary context switching overheads.

#### 3.2 Contexts

Each hart always has an associated *context*, which acts as the execution vessel for the computation running on the hart. The context primitive allows one to suspend the current computation by blocking its context, while allowing the underlying hart to continue "beating" and running other contexts. A blocked context stores the continuation of the computation, including the stack that the computation was using, and any context-local state.

Contexts support efficient overlap of communication with computation. A pending synchronization or I/O operation can block its context, and return the hart back to the current scheduler to do useful work in the meantime. The current scheduler can then choose to run another task or give the hart to another scheduler. Whereas OS thread-multiplexing may also achieve overlapped computation and communication, it does so by forcing fine-grained sharing without any regard to whether there are even synchronization or I/O latencies to mitigate, and without any say from the current scheduler about what to run instead.

Each scheduler is responsible for allocating and managing its own contexts, giving it full control over how to manage its stacks, and enabling optimizations such as linked stacks [vBCZ+03], stacklets [GSC96], and frames [Sta]. It is important for each scheduler to be able to manage its own stacks. Schedulers often store the execution state in the stack, so the stack implementation dictates both the task creation overhead and the parallel execution model [GSC96]. A scheduler can also allocate and manage any context-local state.

## Chapter 4

# Lithe Scheduler Callback Interface

This chapter describes Lithe's callback interface (Table 4.1), which is implemented by all schedulers within an application. The standardized interface enables any parent and child scheduler to share harts, providing interoperability between diverse parallel software components. The scheduler callback interface is orthogonal to the function call interface, as illustrated in Figure 4-1. This enables the separation of concerns between high-level functionality and low-level resource management, as well as provides "plug-and-play" interchange of any sequential or parallel implementation.

The callbacks form the backbone of Lithe's distributed modular scheduling. Upon instantiation, each scheduler is only aware of its current hart and parent scheduler. It is dynamically given additional harts or information from its environment whenever one of its callbacks is invoked. Callbacks fall under two categories: transfer and update (Figure 4-2). Using a hart to invoke a scheduler's transfer callback effectively transfers control of the hart over to the scheduler in a continuation-passing style. Using a hart to invoke a scheduler's update callback, on the other hand, only lets the scheduler borrow the hart to process the given information and update any relevant scheduling state. Below, we describe each of the callbacks in more detail.

| Callback                                                  | Type     | Invoker          |

|-----------------------------------------------------------|----------|------------------|

| <pre>void register(lithe_sched_t child);</pre>            | Update   | Child Scheduler  |

| <pre>void unregister(lithe_sched_t child);</pre>          | Update   | Child Scheduler  |

| <pre>void request(lithe_sched_t child, int nharts);</pre> | Update   | Child Scheduler  |

| <pre>void enter();</pre>                                  | Transfer | Parent Scheduler |

| <pre>void yield(lithe_sched_t child);</pre>               | Transfer | Child Scheduler  |

| <pre>void block(lithe_ctx_t ctx);</pre>                   | Transfer | Computation      |

| <pre>void unblock(lithe_ctx_t ctx);</pre>                 | Update   | Computation      |

Table 4.1: The standard Lithe callbacks.

```

tbb::task(){

foo(){

#pragma OMP parallel

:

}

}

```

```

tbb::task(){

foo(){

spawn bar();

;

}

```

```

tbb::task() {

foo() {

:

;

}

```

Figure 4-1: The Lithe scheduler callback interface, which is orthogonal to the function call interface, enables the plug and play of an OpenMP, Cilk, or sequential implementation of foo. Furthermore, there is a separation of concerns between the high-level functionality of task invoking foo, and the low-level resource management of their respective schedulers exchanging harts.

Figure 4-2: (a) Transfer callbacks transfer control of the hart from one scheduler to another in continuation-passing style. (b) Update callbacks allow a scheduler to borrow a hart temporarily to process the given information and update its internal state.

#### 4.1 Transfer Callbacks

Transfer callbacks are Lithe's minimalistic mechanism for a scheduler to transfer control of one of its harts to another scheduler. A scheduler effectively gains control of a hart when one of its transfer callbacks are invoked using that hart. The scheduler's code inside the transfer callback decides what to do with the hart, then carries out the decision by either executing a task with the hart or transferring the hart to another scheduler. Transfer callbacks are essentially entry points for additional harts to dynamically join a parallel software component after an initial hart has invoked the component and instantiated its scheduler.

Each transfer callback is invoked with a special context provided by the Lithe runtime system for the hart, called the transition context. A transition context also provides a small transition stack for the callback to execute with before it starts or resumes one of the scheduler's own contexts. Transition contexts remove the need to share stacks across parallel components during hart transfers by decoupling harts from stacks. This enables components to manage their stacks in diverse ways. This also prevents a component from accidentally trampling on another component's state, or inhibiting another component's continuation stack frame from being resumed. Because transfer callbacks are invoked with a transition stack, they must not return, but must instead explicitly resume another context or invoke another scheduler's transfer callback. Note that parallel languages and libraries will typically provide their tasks with a higher-level execution environment that abstracts

away harts and contexts, so only low-level scheduling codes will have to be written in such continuation-passing style.

Transfer callbacks enable a scheduler to inform another scheduler that it can use a hart by simply giving it the hart. No other harts need to be involved. The donor scheduler does not need to interrupt the recipient scheduler, and the recipient does not need to poll periodically to see if it has received more harts. Furthermore, a scheduler does not need to hand off tasks (in the form of threads) for its parent scheduler or the OS to schedule in order to access additional processing resources. This enables modularity, as a parallel component does not need to expose how it manages its parallelism. This also enables greater efficiency, as schedulers can adapt their policies to the number of available harts at any given time, and avoid paying the overhead of parallelization (including stack creation) until additional harts become available.

Below, we describe the three transfer callbacks defined by Lithe, which are differentiated by where the hart originated.

Enter The enter callback is invoked by a scheduler's parent to allocate the hart to the scheduler. The scheduler can use its additional hart to execute its unit tasks, or to grant to one of its children.

Yield The yield callback is invoked by a scheduler's child to give back a previously allocated hart. The scheduler can remember the fact that this child has yielded one of its harts to influence its future hart allocation decisions. The scheduler can then use the hart to execute other computation, grant the hart to another child, or return the hart back to its own parent.

Block The block callback is invoked with a hart that is currently managed by the scheduler. Rather than being invoked by another scheduler, the callback is invoked from within an executing task, typically by a synchronization or I/O library. The callback notifies the scheduler that the context previously running on the hart has been paused, and that the hart is now free to do other work. The callback enables a synchronization or I/O library to cooperate with the current scheduler to achieve efficient overlap of communication with computation. In addition, this allows a synchronization or I/O library to be interoperable with a wide range of schedulers, as well as allowing data, files, and devices to be shared and synchronized between tasks that are managed by different schedulers.

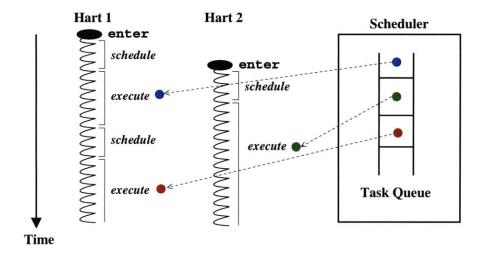

**Example** Each scheduler typically keeps track of its harts, children, and tasks. A scheduler's callbacks access and update this internal state concurrently to coordinate the parallel execution of its computation across multiple harts. Figure 4-3 shows an example scheduler with a task queue that is accessed by each of its enter callbacks.

Figure 4-3: An example scheduler using its task queue to manage two of its harts from independent enter callbacks.

### 4.2 Update Callbacks

Update callbacks are used when a scheduler wants to communicate information to another scheduler. An update callback uses the hart it was invoked with to update its scheduler's state appropriately, then returns to effectively send the hart back to its original scheduler.

Below, we describe the four update callbacks defined by Lithe.

Register The register callback notifies its scheduler about a new child scheduler, which has taken over the current hart to manage the task last scheduled on that hart. The scheduler can associate the child with the task managed by the child, so that it can later decide how to allocate harts to the child based on the importance of its task.

Unregister The unregister callback notifies its scheduler about the completion of a child scheduler. The scheduler uses this callback to clean up any state it may have associated with the child. A child may unregister with a different hart than the one it used to register itself, but it always registers and unregisters using the same parent context (and stack).

Request The request callback notifies its scheduler about how many additional harts a child scheduler wants. The same child can request harts multiple times between the time it registers and unregisters. The scheduler can use this callback to increment the child's unfulfilled request count, and possibly request additional harts from its own parent. The scheduler is not obligated to satisfy all of the requests, but it can use the information to help guide its scheduling decisions.

Unblock The unblock callback notifies its scheduler that a blocked context is now runnable. Similar to the block callback, unblock is invoked from a task. Unlike block, the invoking task, along with the hart, may be managed by a different scheduler if there is cross-component synchronization. The scheduler merely uses the callback to mark the context as runnable, rather than hijack the hart to resume the context. It can then choose to resume the context the next time it makes a scheduling decision for any one of its hart.

## Chapter 5

# Lithe Runtime

This chapter describes the Lithe runtime system, which facilitates hart sharing and context switching. The runtime consists of a small amount of user-level bookkeeping and transitioning code to maximize modularity between parallel software components. It keeps track of the hierarchy of schedulers, current scheduler for each hart, and the standard callbacks for each scheduler. It also provides the mechanism to transfer a hart atomically between different schedulers and/or contexts.

#### 5.1 Runtime Interface

The Lithe runtime provides functions to operate on the hart and context primitives, as listed in Table 5.1. The first set of functions enable schedulers to communicate with each other to share harts. The second set of functions can be used to start, pause, and resume contexts to use and share harts at a fine granularity. Below, we describe each function in detail.

#### 5.1.1 Functions for Sharing Harts

This section describes the runtime functions used by schedulers to communicate with their parent and child schedulers. The runtime is responsible for connecting a scheduler to its parent or child by invoking the appropriate callback.

Building the Scheduler Hierarchy A scheduler "registers" itself when it is instantiated from within the current task to manage the rest of the task's computation. By calling lithe\_sched\_register, the scheduler effectively establishes itself as the current scheduler's child and takes control of the hart.

The lithe\_sched\_register function performs a few basic steps to update the internal runtime state and inform the current scheduler. First, the function assigns the scheduler a unique handle of type lithe\_sched\_t. It then inserts the scheduler into the scheduler

| Lithe Runtime Interface         | Scheduler Callback Interface |

|---------------------------------|------------------------------|

| lithe_sched_register(callbacks) | register                     |

| lithe_sched_unregister()        | unregister                   |

| lithe_sched_request(nharts)     | request                      |

| lithe_sched_enter(child)        | enter                        |

| lithe_sched_yield()             | yield                        |

| lithe_ctx_init(ctx, stack)      | N/A                          |

| lithe_ctx_fini(ctx)             | N/A                          |

| lithe_ctx_setcls(cls)           | N/A                          |

| lithe_ctx_getcls()              | N/A                          |

| lithe_ctx_run(ctx, fn)          | N/A                          |

| lithe_ctx_pause(fn)             | N/A                          |

| lithe_ctx_resume(ctx)           | N/A                          |

| lithe_ctx_block(ctx)            | block                        |

| lithe_ctx_unblock(ctx)          | unblock                      |

Table 5.1: The Lithe runtime functions and their corresponding scheduler callbacks. Note that the function, fn, passed to lithe\_ctx\_pause takes the current context as an argument.

hierarchy, and records the scheduler's callbacks. Next, it invokes the current scheduler's register callback, identifying the new scheduler by the opaque lithe\_sched\_t handle. Finally, it updates the current scheduler of the hart to be the new scheduler, effectively giving the new scheduler control of the hart upon returning.

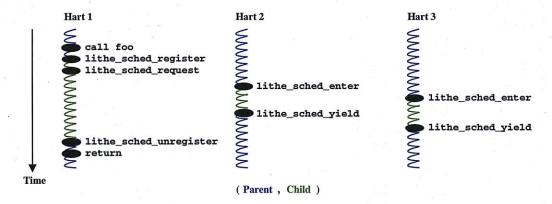

Figure 5-1(a) shows an example of using lithe\_sched\_register. A TBB task invokes a function, foo, which is written in Cilk. foo begins by instantiating a Cilk scheduler, which in turn registers itself to obtain control of the current hart from the TBB scheduler. Figure 5-1(b) shows how the Lithe runtime enables code reuse by insulating a scheduler from knowing its parent scheduling environment. The same Cilk implementation of foo can be reused within an OpenMP loop, since the Cilk scheduler does not care whether it is communicating with TBB or OpenMP as its parent.

Once a child scheduler completes its computation and no longer needs to manage harts, it calls lithe\_sched\_unregister. First, this runtime function waits until the unregistering scheduler has finished yielding all of its remaining harts to its parent, then invokes the parent scheduler's unregister callback. This is to prevent straggling harts from remaining under a child scheduler's control once the child has unregistered. Next, the function removes the unregistering scheduler from the hierarchy. Finally, it reverts the current scheduler of the hart to be the parent scheduler, effectively giving control of the hart back to the parent upon returning.

Requesting Harts To request additional harts, a scheduler invokes lithe\_sched\_request, passing the number of harts desired. This function relays the request directly to the parent scheduler by invoking the parent's request callback.

```

Hart

tbb::task() {

foo() {

cilk.init() {

lithe_sched_register(callbacks cilk);

}

Time

(a)

Hart

#pragma omp parallel

for (i = 0; i < N; i++) {

foo() {

cilk.init() {

lithe_sched_register(callbacks cilk);

}

Time

(b)

```

Figure 5-1: (a) foo is written in Cilk, and begins by instantiating a Cilk scheduler, which registers itself to obtain control of the current hart from the TBB scheduler. (b) The same foo function can be reused in an OpenMP loop, since the Cilk scheduler is insulated from its parent scheduling environment, and does not care whether it is communicating with TBB or OpenMP as its parent.

Figure 5-2: An example of how multiple harts might flow between a parent and child scheduler.

Allocation of Additional Harts A parent scheduler allocates a hart to a child scheduler by invoking the lithe\_sched\_enter function, and passing the child as an argument. This function updates the current scheduler to be the child, then invokes the child's enter callback using the transition context. This transfers the control of the current hart from a parent to the designated child in a continuation-passing style.

Whenever a scheduler is done with a hart, it can invoke lithe\_sched\_yield. This function updates the current scheduler from the child to the parent, then invokes the parent's yield callback using the transition context. This transfers the control of the current hart from a child back to its parent in a continuation-passing style.

Putting it All Together Figure 5-2 shows an example of how a parent and child scheduler use Lithe to cooperatively share harts. A parent component calls child component's foo function to do some computation. The implementation of foo then instantiates a scheduler to manage the parallelism within that function. The scheduler uses the initial hart to register itself with its parent scheduler, who is managing the parallelism for the invoking component, then requests additional harts from that parent scheduler. It then begins to execute the computation of foo using that hart.

After the parent scheduler has received the request, it may decide to grant additional harts to the new scheduler by invoking lithe\_sched\_enter on each of these harts. Each lithe\_sched\_enter, in turn, will invoke the new scheduler's enter callback, which uses its extra hart to help with executing the computation. When the scheduler is done with the computation, it yields all of the additionally granted harts by invoking lithe\_sched\_yield. It will also unregister itself with its parent scheduler, then return from foo.

#### 5.1.2 Functions for Manipulating Contexts

This section describes the runtime functions used to start, pause, and resume contexts. These functions enable portability by shielding schedulers from knowing the platform-specific details of how to save and set machine state. They also enable atomic context switching within and across parallel components.

Executing with Contexts A scheduler sets up a context by calling the lithe\_ctx\_init function and passing a stack for the context to use. The Lithe runtime identifies each context by an opaque handle of type lithe\_ctx\_t. A scheduler starts the context by invoking lithe\_ctx\_run, and passing it a function that should be invoked by the context. Note that after the computation using the context has completed, the context can be reused by subsequent calls to lithe\_ctx\_run. A scheduler cleans up a context by calling the runtime function lithe\_ctx\_fini.

Context-Local State A scheduler can associate some data with each context by calling the lithe\_ctx\_setcls function, and passing a pointer to the data. A scheduler can access the context-local state for the current context by invoking lithe\_ctx\_getcls.