# Firmware Development and Integration for ALICE TPC and PHOS Front-end Electronics

A Trigger Based Readout and Control System operating in a Radiation Environment

## Johan Alme

Dissertation for the degree philosophiae doctor (PhD) at the University of Bergen

10 August 2008

## **Acknowledgements**

Since I started on the PhD program in May 2004 there have been many big events in my life, both privately and professionally. I am now a married man, father to a beautiful daughter (soon there are two!) and owns a house and a station wagon. Brann has won the Norwegian championship for the first time in 44 years, Liverpool FC won the Champions League and Kiss and Black Sabbath - two of my all time favourite bands since I was a teenager - have played live in Bergen. Professionally I have finally come to the point where I can hand in my PhD-thesis. It has been four years where I have learnt a lot and got to know a whole lot of nice people from all parts of the world. I have travelled more than ever before and even got to visit some exotic places like for instance Wuhan, Chicago, Sardinia and of course CERN. It has been a great time!

First of all I would like to thank my supervisors Kjetil Ullaland and Dieter Röhrich for giving me this opportunity and for having belief in me. If you hadn't talked me into it, I wouldn't have tried to apply for a stipend for the fourth time in a row. Kjetil has guided and helped me in everything from the art of electronics to makeover of old houses. We have had long and valuable discussions where I might have disagreed with him in the start but normally not in the end. Dieter has stood up for me during heated debates and e-mail exchanges and has always been helpful whenever help was needed. In addition he has an amazing way of explaning the unexplainable in simple words. The two of you have really contributed into making the 4 years that I have put into this thesis an enjoyable and educational journey. The same goes to Bernhard Skaali at the University of Oslo who've formally been my boss during these years. Without you I would never have got this opportunity. I would also like to thank the Norwegian Research Council for financial support.

A very special thank also goes to my friend and colleague Ketil Røed with whom I shared an enormous amount of coffees and crackers as well as having generally interesting discussions about nothing and everything. We have worked closely together and I have found it to be very rewarding. Thanks also to Torsten Alt, Matthias Richter, Per Thomas Hille and Gerd Tröger for always being willing to answer my at times stupid questions and for making life at CERN enjoyable during my stays there (by for instance nighttime swimming activities with Per Thomas and Torsten). All the rest of the people in the Microelectronics group and the Nuclear Physics group at the University of Bergen, as well as the people involved from the Bergen University College, also deserve to be thanked. Some times for giving

valuable professional input, and all the time for being part of a great social environment that have made me look forward to go to the office every day (ok, I have to be honest – maybe not on Sundays).

My good friend Vegard Øvrelid deserves my highest appreciation for reading through my thesis and helping me getting my English grammar in a presentable shape.

Special thanks must go to my parents for always believing in me and supporting me, and for being loving grandparents to Liv. Liv deserves the biggest hug of all for filling my life with joy and laughter, even if she is an earlybird...

Finally, the deepest gratitude goes to my wife, Elen Siglen, for always supporting me, for her patience, and for keeping up with my long and endless stories of people she have never met and topics that don't interest her. You are an even better wife and better mother to our daughter that I ever could have dreamt of having. I love you.

Johan

Bergen, August 2008

#### **Abstract**

The readout electronics in PHOS and TPC – two of the major detectors of the ALICE experiment at the LHC – consist of a set of Front End Cards (FECs) that digitize, process and buffer the data from the detector sensors. The FECs are connected to a Readout Control Unit (RCU) via two sets of custom made PCB backplanes. For PHOS, 28 FECs are connected to one RCU, while for TPC the number is varying from 18 to 25 FECs depending on location. The RCU is in charge of the data readout, including reception and distribution of triggers and in moving the data from the FECs to the Data Acquisition System. In addition it does low level control tasks. The RCU consists of an RCU Motherboard that hosts a Detector Control System (DCS) board and a Source Interface Unit. The DCS board is an embedded computer running Linux that controls the readout electronics.

All the mentioned devices are implemented in commercial grade SRAM based Field Programmable Gate Arrays (FPGAs). Even if these devices are not very radiation tolerant, they are chosen because of their cost and flexibility, and most importantly the possibility to easily do future upgrades of the electronics. Since physical shielding of the electronics is not possible in ALICE due to the architecture of the detector, the radiation related errors need to be handled with other techniques such as firmware mitigation techniques.

The main objective of this thesis has been to make firmware modules for the FPGAs reciding in different parts of the readout electronics. Because of the flexibility of the designs, some of them have, with minor adaptations, been applied in different devices surrounding the readout electronics. Additionally, effort has been put into testing and integration of the system. In detail, the work presented in this thesis can be summarized as follows:

- Firmware design for radiation environments. All firmware modules that are designed are to be used in a radiation environment, and then special precautions need to be taken. Additionally, a state-of-the-art solution has been designed for protecting the main FPGA on the RCU Motherboard against radiation induced functional failures.

- Implementation of Trigger Handling for the TPC/PHOS Readout Electronics. The triggers are received from the global trigger system via an optical link and are handled by an Application Spesific Integrated Circuit (ASIC) on the DCS board. The problem is that the DCS board might have occasional down time

due to radiation related errors, so a special interface module is designed for the main FPGA on the RCU Motherboard. This module decodes and verifies the information received from the trigger system. As it is a generic design it has also been implemented as part of the BusyBox. The BusyBox is an important device in the trigger path of the TPC and PHOS sub-detectors.

- Implementation of the TPC/PHOS Front-end Electronics Detector Control System. This point includes several parts that are listed from bottom up:

- o *PHOS FEC Board Controller*. The PHOS FEC Board Controller is the lowest level of the DCS. It is an SRAM based FPGA that is in charge of monitoring the health status of the given FEC and configure vital parts of the PHOS Front-end. The design is based on the TPC Board Controller design, but it is functionally extended and has increased robustness against radiation related errors and other external errors.

- O Active Partial Reconfiguration Solution: A vital part of the Fee DCS is the Active Partial Reconfiguration Solution that deals with radiation related errors. This state-of-the-art design enables the possibility to clear any radiation related error in the configuration memory of the main FPGA on the RCU motherboard while not interfering with the operation of the design.

- o *RCU main FPGA DCS interface*. A small module translating the DCS bus protocol to an FPGA internal RCU bus protocol.

- o *TPC/PHOS DCS board firmware*. The DCS board firmware implements the communication path down to the registers on the RCU, and upwards towards the ARM CPU. As the DCS board might, from time to time, reboot because of radiation related errors, effort has been put into ensuring that this does not affect the data flow on the RCU Motherboard. Because of the flexibility of the DCS board, this firmware has been adapted to several other motherboards in the system.

- Testing and Verification of all firmware modules. All firmware modules have been extensively verified with computer simulation before being tested in real hardware.

- Maintenance of the DCS board for TPC/PHOS and of the different Fee firmware modules in general.

• System Integration and System Level Tests. A big contribution has been done integrating and testing all the modules and sub-systems. This concern both locally on the RCU and the BusyBox, as well as making all the devices play together on a larger scale.

As the presented electronics are located in a radiation environment and are physically unavailable after commissioning, effort has been put into making designs that are reliable, scalable and possible to upgrade. This has been ensured by following a systematic design approach where testability, version management and documentation are key elements. Some parts of the work described in this thesis have been published and presented in international peer reviewed publications and conferences.

# **Contents**

| ACKNOWLE   | DGEMENTS                                      | 3  |

|------------|-----------------------------------------------|----|

| ABSTRACT . |                                               | 5  |

| CONTENTS.  |                                               | 9  |

| CHAPTER 1  | THE ALICE EXPERIMENT                          | 15 |

| 1.1 Intro  | ODUCTION                                      | 15 |

| 1.2 LARC   | SE HADRON COLLIDER                            | 17 |

| 1.3 ALIC   | CE PHYSICS                                    | 18 |

| 1.4 ALIC   | CE DETECTOR                                   | 19 |

| 1.4.1      | Overview                                      | 19 |

| 1.4.2      | Time Projection Chamber (TPC)                 | 20 |

| 1.4.3      | PHOton Spectrometer (PHOS)                    | 21 |

| 1.4.4      | Other Detectors                               | 22 |

| 1.5 RADI   | ATION ENVIRONMENT OF THE FEE                  | 22 |

| 1.6 Onli   | NE SYSTEMS FOR THE ALICE TPC/PHOS ELECTRONICS | 23 |

| 1.6.1      | Experiment Control System                     | 23 |

| 1.6.2      | Trigger, Timing and Control System            | 24 |

| 1.6.3      | Data Acquisition System                       | 26 |

| 1.6.4      | High Level Trigger                            | 28 |

| 1.6.5      | Detector Control System                       | 28 |

| CHAPTER 2  | TPC AND PHOS FRONT-END ELECTRONICS            | 31 |

| 2.1 Intro  | ODUCTION                                      | 31 |

| 2.2 TPC    | FEE TOPOLOGY                                  | 33 |

| 2.3 PHO    | S FEE TOPOLOGY                                | 34 |

| 2.4 Fron   | IT END ELECTRONICS DEVICES.                   | 35 |

| 2.4.1      | TPC Front End Card                            | 35 |

| 2.4.2      | PHOS Front End Card                           | 36 |

| 2.4.3      | Readout Control Unit                          | 38 |

| 2.4.4      | PHOS Trigger Generation Hardware              | 42 |

| 2.4.5     | BusyBox                                             | . 43 |

|-----------|-----------------------------------------------------|------|

| CHAPTER 3 | DETECTOR CONTROL SYSTEM FOR THE FEE                 | 47   |

| 3.1 Intro | ODUCTION                                            | 47   |

| 3.2 DCS   | BOARD SOFTWARE                                      | 49   |

| 3.2.1     | Communication Software on the DCS board             | . 49 |

| 3.2.2     | The DCS Board Logical Architecture                  | . 50 |

| 3.3 DCS   | BOARD FIRMWARE                                      | 51   |

| 3.3.1     | Overview and Specification                          | . 51 |

| 3.3.2     | DCS board Flavours                                  | . 52 |

| 3.4 RCU   | COMMUNICATION MODULE                                | 53   |

| 3.4.1     | Overview                                            | . 53 |

| 3.4.2     | Modes of Operation                                  | . 54 |

| 3.4.3     | Definition of the interconnecting DCS-RCU bus lines | . 56 |

| 3.4.4     | RCU Interrupt Handling                              | . 56 |

| 3.4.5     | MessageBuffer Functional Overview                   | . 57 |

| 3.4.6     | MessageBuffer Configuration Block                   | . 57 |

| 3.4.7     | DCS Bus Protocol                                    | . 58 |

| 3.4.8     | Flash Bus Protocol                                  | . 59 |

| 3.4.9     | SelectMAP Bus Protocol                              | . 60 |

| 3.4.10    | Radiation Tolerance Measures                        | . 60 |

| 3.4.11    | BusyBox and Trigger-OR Flavour                      | . 61 |

| 3.5 RCU   | MAIN FPGA IN THE FEE DCS                            | 63   |

| 3.5.1     | Introduction                                        | . 63 |

| 3.5.2     | DCS Interface                                       | . 64 |

| 3.5.3     | Monitoring and Safety Module                        | . 66 |

| 3.6 PHO   | S FEC Board Controller                              | 68   |

| 3.6.1     | Introduction and Requirements                       | . 68 |

| 3.6.2     | TPC Board Controller                                | . 69 |

| 3.6.3     | PHOS Board Controller Introduction                  | . 70 |

| 3.6.4     | Registers                                           | . 72 |

| 3.6.5     | Health Monitoring                                   | . 74 |

| 3.6.6     | High Voltage APD Bias Settings                      | . 76 |

| ŝ    | 3.6.7 | RCU Communication                                          | 78  |

|------|-------|------------------------------------------------------------|-----|

| ŝ    | 3.6.8 | Radiation Robustness Measures                              | 79  |

| СНАР | TER 4 | RCU RADIATION TOLERANCE SOLUTION                           | 81  |

| 4.1  | Radi  | ATION EFFECTS IN INTEGRATED CIRCUITS                       | 81  |

| 4    | 4.1.1 | Single Event Effects                                       | 81  |

| 4    | 4.1.2 | Single Event Upset Mitigation Techniques                   | 83  |

| 4.2  | Сноі  | CE OF TECHNOLOGY                                           | 84  |

| 4    | 1.2.1 | FPGA Technologies                                          | 84  |

| 4    | 1.2.2 | Why an SRAM based FPGA is selected on the RCU              | 84  |

| 4.3  | ACTI  | VE PARTIAL RECONFIGURATION                                 | 85  |

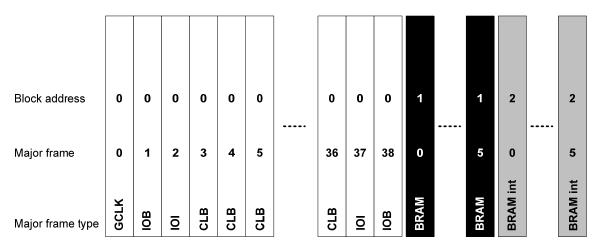

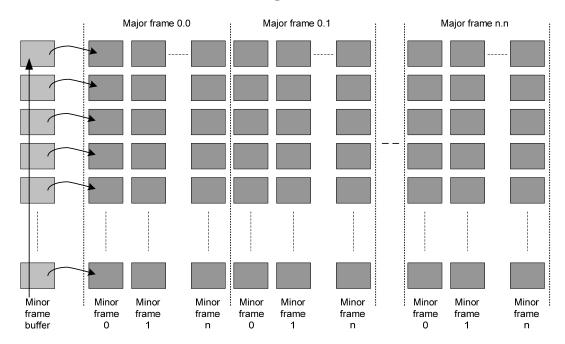

| 4    | 4.3.1 | Xilinx Virtex-II Pro XC2VP7 Architecture                   | 85  |

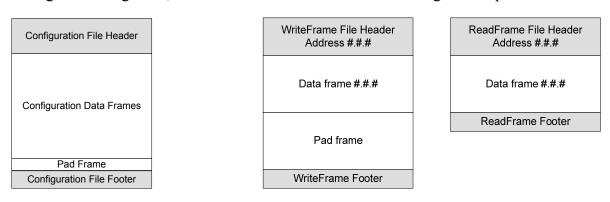

| 4    | 4.3.2 | Configuration of Xilinx Devices                            | 86  |

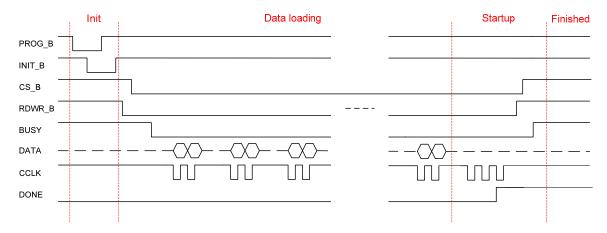

| 4    | 4.3.3 | SelectMAP Interface                                        | 88  |

| 4    | 1.3.4 | Limitations of Active Partial Reconfiguration              | 89  |

| 4.4  | ACTI  | VE PARTIAL RECONFIGURATION SOLUTION ON THE RCU MOTHERBOARD | 91  |

| 4    | 4.4.1 | Introduction                                               | 91  |

| 4    | 4.4.2 | RCU Flash Architecture                                     | 92  |

| 4    | 4.4.3 | Firmware Overview                                          | 94  |

| 4    | 4.4.4 | Registers                                                  | 95  |

| 4    | 4.4.5 | Available Commands                                         | 95  |

| 4    | 4.4.6 | Configuration Controller                                   | 96  |

| 4    | 1.4.7 | Power Up Detection                                         | 98  |

| 4    | 4.4.8 | SelectMAP interface Implementation                         | 99  |

| 4    | 4.4.9 | Radiation Tolerance Measures                               | 100 |

| 4.5  | INTE  | GRATION WITH THE FEE DCS                                   | 100 |

| 4.6  | ACTI  | VE PARTIAL RECONFIGURATION ON OTHER DEVICES                | 101 |

| 4.7  | Effe  | CTIVITY OF THE ACTIVE PARTIAL RECONFIGURATION              | 102 |

| СНАР | TER 5 | PROCESSING OF TRIGGER INFORMATION                          | 105 |

| 5.1  | Syst  | EM REQUIREMENTS AND OVERVIEW                               | 105 |

| 5.2  | TRIG  | GER RECEPTION AND HANDLING IN TPC & PHOS FEE               | 107 |

| 4    | 521   | Introduction                                               | 107 |

| 5.2.2     | Functional Requirements                      | 107 |

|-----------|----------------------------------------------|-----|

| 5.2.3     | Input from the Trigger System                | 109 |

| 5.2.4     | Fee Trigger Receiver Overview                | 111 |

| 5.2.5     | Channel A decoding                           | 112 |

| 5.2.6     | Channel B decoding                           | 112 |

| 5.2.7     | Trigger Sequence Validation                  | 114 |

| 5.2.8     | Output to Internal Logic                     | 116 |

| 5.2.9     | Registers                                    | 118 |

| 5.2.10    | Adaptions for the BusyBox                    | 119 |

| 5.2.11    | Radiation Tolerance Measures                 | 120 |

| 5.3 Trig  | GER DISTRIBUTION                             | 121 |

| 5.4 DATA  | A READOUT                                    | 121 |

| 5.4.1     | The Readout Process                          | 121 |

| 5.4.2     | Board Controller in the Data Readout Process | 124 |

| 5.4.3     | Event Building                               | 126 |

| 5.5 Busy  | yBox                                         | 127 |

| 5.5.1     | Basic Functionality                          | 127 |

| 5.5.2     | Firmware Architecture                        | 127 |

| 5.6 Con-  | CLUSION                                      | 129 |

| CHAPTER 6 | VERIFICATION AND TESTING                     | 131 |

| 6.1 Fund  | CTIONAL VERIFICATION OF THE FIRMWARE MODULES | 131 |

| 6.1.1     | Introduction                                 | 131 |

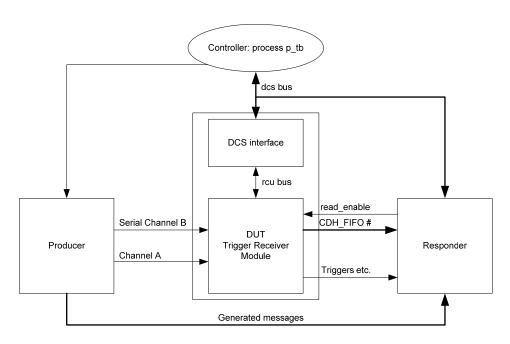

| 6.1.2     | Testbench for the Trigger Receiver Module    | 133 |

| 6.1.3     | Testbench for the PHOS Board Controller      | 134 |

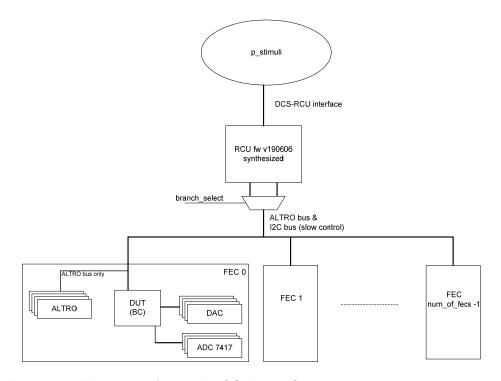

| 6.1.4     | Testbench for the RCU support FPGA firmware  | 135 |

| 6.1.5     | Testbench for the DCS board firmware         | 135 |

| 6.2 HAR   | DWARE TESTS OF THE FIRMWARE MODULES          | 135 |

| 6.2.1     | Trigger Receiver Module                      | 135 |

| 6.2.2     | PHOS Board Controller                        | 136 |

| 6.2.3     | RCU support FPGA                             | 138 |

| 6.2.4     | DCS board Firmware                           | 139 |

| 6.3 Irra  | DIATION AND FAULT INJECTION TESTS            | 140 |

| 6.4 S   | YSTEM INTEGRATION TESTS AND COMMISIONING      | 141 |

|---------|-----------------------------------------------|-----|

| 6.4.1   | Introduction                                  | 141 |

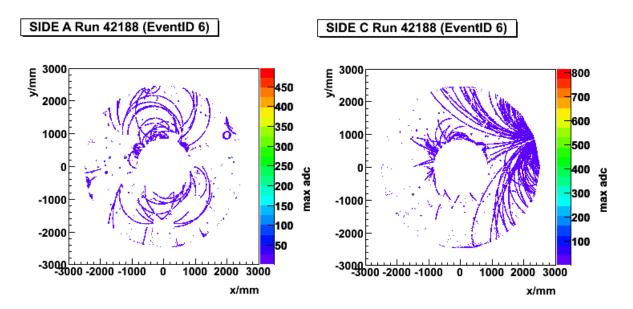

| 6.4.2   | TPC Electronics Commissioning                 | 141 |

| 6.4.3   | PHOS commissioning                            | 142 |

| 6.4.4   | Tests involving RCU firmware version 2.0      | 143 |

| СНАРТЕІ | R 7 ERROR HANDLING ON A SYSTEM LEVEL          | 145 |

| 7.1 In  | NTRODUCTION                                   | 145 |

| 7.2 E   | RRORS IN THE RCU MAIN FPGA                    | 145 |

| 7.2.1   | Consequences                                  | 145 |

| 7.2.2   | Proposed Solutions for Error Handling         | 146 |

| 7.3 E   | RRORS IN THE TRIGGER AND DATA PATH            | 148 |

| 7.4 E   | RRORS IN THE FEE DCS                          | 149 |

| 7.5 C   | ONCLUSION                                     | 150 |

| CHAPTEI | R 8 CONCLUSION AND OUTLOOK                    | 151 |

| APPENDI | X A LIST OF PUBLICATIONS                      | 153 |

| A.1     | PUBLICATIONS SIGNIFICANTLY CONTRIBUTED TO     | 153 |

| A.2     | ALL PUBLICATIONS                              | 153 |

| APPENDI | X B LIST OF ABBREVIATIONS                     | 155 |

| APPENDI | X C DESIGN METHODOLOGY                        | 159 |

| C.1     | Introduction                                  | 159 |

| C.2     | DOCUMENTATION                                 | 159 |

| C.2.    | l Requirement Specification                   | 159 |

| C.2.2   | 2 Coding Guidelines and In Code Documentation | 159 |

| C.3     | VERSION MANAGEMENT                            | 160 |

| C.3.    | l Release Versions                            | 160 |

| C.3.2   | 2 CVS                                         | 160 |

| C.4     | PUBLISHING                                    | 161 |

| APPENDI | X D TABLES AND FIRMWARE VERSION CHANGE LOGS   | 163 |

| D.1     | TABLE LEGEND                                  | 163 |

| D.2     | DCS BOARD FIRMWARE                            | 164 |

| D.2.    | l Tables                                      | 164 |

| D.2.2    | Version Change Log                                    |

|----------|-------------------------------------------------------|

| D.3      | RCU MAIN FPGA DCS INTERFACE 170                       |

| D.3.1    | <i>Tables</i>                                         |

| D.3.2    | Version Change Log                                    |

| D.4      | PHOS BOARD CONTROLLER                                 |

| D.4.1    | Tables                                                |

| D.4.2    | Version Change Log                                    |

| D.5      | RCU SUPPORT FPGA FIRMWARE 180                         |

| D.5.1    | Tables                                                |

| D.5.2    | Version Change Log                                    |

| D.6      | TRIGGER RECEIVER MODULE 184                           |

| D.6.1    | Trigger Receiver Firmware Tables                      |

| D.6.2    | Tables Defining Inputs to the Trigger Receiver Module |

| D.6.3    | Version Change Log                                    |

| D.7      | OTHER TABLES 194                                      |

| APPENDIX | X E INDEX                                             |

| REFEREN  | CES                                                   |

## **Chapter 1**

## The ALICE Experiment

This chapter gives a brief introduction to the ALICE experiment at CERN. Quark Gluon Plasma is discussed since the main goal of ALICE is to investigate its properties. An overview of the ALICE detector with a brief introduction to the various parts of the system is then given. The PHOton Spectrometer and the Time Projection Chamber are described more in detail, while the other sub-detectors are mentioned briefly. In addition the three main logical systems of the ALICE detector are described on an overall system level: The Trigger System, the Data Acquisition System (including High Level Trigger) and the Detector Control System.

## 1.1 Introduction

The Large Hadron Collider (LHC) is located at CERN<sup>1</sup> near Geneva, Switzerland. CERN is the largest research facility in the world for particle and nuclear physics. The LHC is a circular particle accelerator with two adjacent beams moving in opposite directions. In four different locations the beams intersect, allowing for collisions. The experiments using the Large Hadron Collider are located at these intersections, of which ALICE (A Large Ion Collider Experiment) is one. The main goal of ALICE is to study the properties of Quark Gluon Plasma. Quark Gluon Plasma is a state of matter defined by the quarks and gluons no longer being bound together and confined in Hadrons.

The ALICE detector is at the time of writing in the final stage of commissioning. It has an onion like architecture with several different sub-detectors surrounding the beam pipe in layers from inside to out, where it is wrapped by a magnet (5 meters tall and wide). All of the sub-detectors are tailor-made to detect different particles created in the collision.

<sup>1</sup> CERN is an acronym for Conseil Européen pour la Recherche Nucléaire which was a provisional council for setting up the laboratory, and was established by 11 European governments in 1952. Currently there are 20 member countries and 8 countries/organizations have so called observer status. http://www.cern.ch)

This thesis focuses on the instrumentation for two of the ALICE sub-detectors; the Time Projection Chamber (TPC) and the PHOton Spectrometer (PHOS), since most of the electronics are shared between the two sub-detectors. The TPC detector is the main tracking device in ALICE, and is a gas filled barrel exposed to both a magnetic and an electric field. Charged particles crossing the gas will ionize the atoms in the gas and then the electrons will drift in electric files to the end caps of the barrel. By measuring the arrival of the electrons at both ends of the chamber, the TPC will reconstruct the paths of the original charged particles. The electronics used for data readout are located at the end of the chamber directly behind the detector pads to minimize channel noise and crosstalk. This location implies that the radiation the electronics is there to measure will also be potentially harmful to the electronic devices. The PHOS detector is one of the outermost detectors in ALICE and is detecting photons from the collision. It is made of lead tungstate crystals, in which electromagnetic showers will be generated when the crystal is hit by high energy photons. The readout electronics are situated directly behind the crystals, and as for TPC, located in a radiation environment.

The data readout in ALICE is trigger based. This means that any collision will be detected by a group of fast detectors that will notify a central trigger system. The central trigger system will distribute triggers to the different sub-detectors to start buffering and readout of data. When the data is read out, it is moved from buffers in the readout electronics via an optical link to computer farms where further analysis is done before the data is stored to disk. As the potential data rate from the readout electronics sub-systems is approximately an order of magnitude higher than what can be stored to disk, or even transmitted over the optical data links, data processing and compressing are done by the readout electronics.

Because of the flexibility, the cost and the possibility to easily do future upgrades of the electronics, it has been decided to make extensive use of commercial SRAM based Field Programmable Gate Arrays (FPGAs) in the readout electronics. The other side of the coin is that these devices are generally not very radiation tolerant. The architecture of the ALICE detector is such that physically shielding of the electronics is not possible, which impose challenges in designing the electronics. This implies that the concern with radiation related errors need to be handled with other techniques such as firmware mitigation techniques.

The radiation environment is not the only challenge when designing the readout electronics. As the readout electronic devices are located directly on the detector devices, they are physically unavailable as soon as the ALICE detector is fully operative. It is vital that they are operated under stable temperatures and that if any

node in the system is misbehaving, it should immediately be powered off and analyzed whenever possible. This implies that a control system that can be operated remotely is needed.

## 1.2 Large Hadron Collider

The LHC is currently in the final stages of commissioning, and will be started at the 10. of September 2008. When finished, it will be able to accelerate hadrons to higher energies than any particle accelerator has ever done. The LHC has a circumference of 27 km and has two adjacent beam pipes where bunches of particles are accelerated to a beam energy of 5.5 TeV per nucleon for lead nuclei beams and 7 TeV for proton beams. The bunches are then collided within 4 experimental areas where four main experiments are located:

- ALICE (A Large Ion Collider Experiment): ALICE is specially designed to look for Quark Gluon Plasma (see section 1.3)

- *ATLAS (A Toroidal LHC ApparatuS)*: ATLAS is mainly looking for the Higgs boson, which can be understood as a missing piece in the standard model.

- *CMS (Compact Muon Solenoid):* CMS is also investigating physics in the TeV range and looking for the Higgs boson.

- *LHCb (LHC beauty):* LHCb is designed for investigating physics related to the bottom quark, particularly investigating CP violations in the b hadron interactions.

Additionally there are a few smaller experiments sharing the experimental areas doing forward physics<sup>2</sup>.

<sup>&</sup>lt;sup>2</sup> The experimental definition of forward physics is "All processes in which particles are produced at small polar angles (i.e. large rapidities)". Citation from: Pierre Van Mechelen - "Forward" Physics at the LHC - HERA-LHC Workshop - DESY - March 15, 2007

## 1.3 ALICE Physics

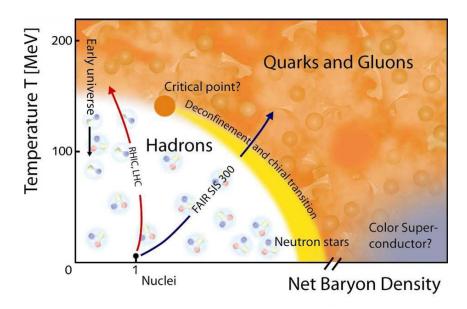

Figure 1-1: High Energy Physics Phase Diagram. From [1].

ALICE will study the properties of Quark Gluon Plasma. Normally, quarks can not exist alone, only when they are bound together into hadrons by the force carrier for the strong force (gluons). If trying to separate them, a new quark - antiquark pair would be created in the force field. When the temperature and/or pressure are high enough, the hadrons undergo a phase transition and Quark Gluon Plasma is formed. In Quark Gluon Plasma the quarks and gluons are deconfined like molecules in a gas. Figure 1-1 is a phase diagram showing the different phases of matter from hadrons to Quark Gluon Plasma. According to the Big Bang theory, Quark Gluon Plasma is believed to have existed up until the universe was 10<sup>-5</sup> seconds old. At this time the pressure and temperature had dropped so much that a process called freeze-out was taking place, in which the quarks and the gluons bound together to form different kinds of hadrons, amongst others the basic building blocks of nature; protons and neutrons. During the Pb-Pb collisions LHC will generate enough energy to create Quark Gluon Plasma.

It is not possible to observe Quark Gluon Plasma directly, only so called footprints can be detected. Details on the experimental observables can be found in for instance [2].

#### 1.4 ALICE Detector

#### 1.4.1 Overview

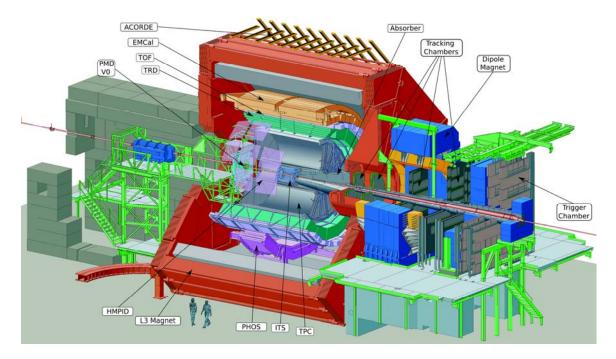

Figure 1-2: The ALICE detector. From [3]

Each of the collisions in LHC is called an event. An event produces a lot of secondary particles. Some of these secondary particles are so short lived that they decay long before leaving any detectable tracks. In order to look for the various decay products, ALICE is designed to be a multi component detector that studies different aspects of an event. Each component is used for measuring particle energies and momentum, and/or for distinguishing different particle types.

The ALICE detector is optimized to study heavy ion collision. The onion-like structure where the various sub-detectors are located in different layers from inside to out is shown in Figure 1-2. The interaction point is in the centre of the detector. Except for ACORDE (ALICE Cosmic Ray Detector), all the barell sub-detectors are located inside the L3 magnet, which is a 12.1 m x 5.75 m magnet generating a magnetic field of 0.5 T[3]. The data readout of ALICE is trigger based. This means that certain fast detectors are contributing to triggers that are distributed to the sub-detectors. The sub-detectors then start data buffering and readout operations.

The functionality of TPC and PHOS will be discussed in the next sections since the work described in thesis are implemented for these two sub-detectors.

#### 1.4.2 Time Projection Chamber (TPC)

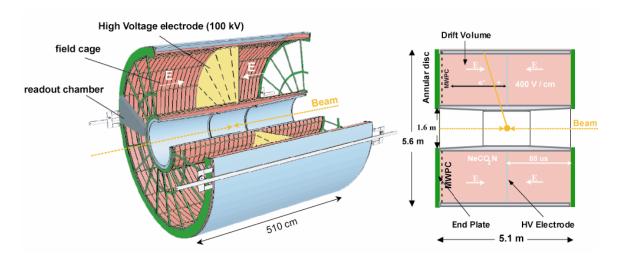

Figure 1-3: Layout of the ALICE TPC. To the left a three dimensional view and to the right are some details concerning the field cage.

The TPC [3, 4] is the main tracking detector in ALICE. As shown in Figure 1-2 it is surrounding the beam pipe outside of the Inner Tracking System detector. The layout of the TPC is shown in Figure 1-3. The TPC is a cylindrical gas volume of 88 m<sup>3</sup> that is divided in two drift regions by a high voltage electrode. The field cage seen in the figure has an inner radius of about 85 cm, and an outer radius of about 280 cm, and an overall length along the beam direction of 510 cm.

In the field cage the charged particles formed in the collisions ionize the gas and electrons drift in the electric field towards the end plates at each side of the detector. The gas in the ALICE TPC is a mixture of Ne,  $CO_2$  and  $N_2$ , which gives the wanted ionization properties and diffusion inside the field cage. The electrons in this gas mixture have, for an electrical drift field that is 400 V/cm, a drift velocity of 2.83 cm/ $\mu$ s. This means that electrons starting from the central plane take about 88  $\mu$ s to reach the end plates.

Each of the two end plates is divided into 18 sectors where conventional Multi Wire Proportional Chambers provide the required charge amplification. The readout plane is divided into 570132 pads of different sizes. As the track density is highest near the centre of the detector, the wire spacing and the pad size are smaller in that location to provide better spatial resolution.

Directly behind the readout pad plane is the location of the Front-end electronics (Fee) of the TPC. As a consequence, the Fee are located in a radiation environment with all the challenges this implies.

#### 1.4.3 PHOton Spectrometer (PHOS)

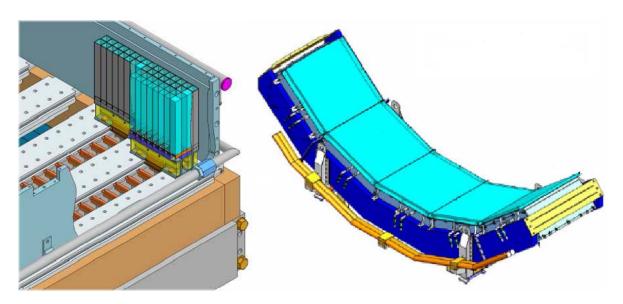

Figure 1-4: The PHOS detector. To the right are the 5 PHOS modules; to the left is the PHOS module with strip units installed onto cooling plates.

The PHOS detector [3, 5] is one of the outermost detectors in Figure 1-2, at a distance of 460 cm from the interaction point. In the initial run there will only be one PHOS module present, but the final configuration holds five modules with an angular coverage of 5\*20 degrees, as shown to the right in Figure 1-4. The pseudo rapidity coverage is -0.12 to 0.12.

Each PHOS module is built up of two different sub-detectors. The main detector is a highly segmented ElectroMagnetic Calorimeter (EMC), while the second detector is a Charged Particle Veto (CPV) detector. The EMC is measuring electromagnetic showers of up to 100 GeV via a large matrix of PbWO<sub>4</sub> crystals. The EMC for one PHOS module is segmented into 3584 detection cells, that each consists of a crystal and an avalanche photo diode. To increase the light yield and hence the energy resolution of the PbWO<sub>4</sub> crystals, the nominal operating temperature of the EMC modules are set to -25°C<sup>3</sup>. The crystal strips are located in a cold enclosure, whereas the Fee are located outside this enclosure.

The CPV detector is a Multi Wire Proportional Chamber that is placed on top of the EMC module with a distance of about 5 mm. The purpose is to discriminate charged particles from neutral particles. The CPV detector is currently only in a prototype version and will not be installed at the start up of LHC.

\_

<sup>&</sup>lt;sup>3</sup> The first installed PHOS module will operate at room temperature during the first year.

#### 1.4.4 Other Detectors

In addition to PHOS and TPC there are numerous other sub-detectors in ALICE, of which some are marked in Figure 1-2. The detectors can be divided into the central detectors and the forward detectors. The central detectors (or barrel detectors) are the detectors located around the collision point, while the forward detectors are located along the beam axis on the edge of the magnet. PHOS and TPC are central detectors. Details concerning the various sub-detectors of ALICE can be found in [3].

Detectors other than TPC and PHOS that are interesting in the context of this work are especially the ElectroMagnetic Calorimeter (EMCal) and the Forward Multiplicity Detector (FMD), since these detectors share many of the electronic components with TPC and PHOS. The location of EMCal is given in Figure 1-2. FMD is one of the forward detectors and measures the charged particles emitted at small angles relative to the beam. Of other important physics detectors are the Inner Tracking System, Transition Radiation Detector (TRD), Time of Flight Detector, the High Momentum Particle Identification Detector and the Muon Spectrometer. One of the main electronic components of TPC and PHOS, the DCS board (see section 0), is also in use on the TRD detector of which it was originally designed for.

The Level 0 (L0) trigger (see section 1.6.2) in ALICE combines the input from detectors with fast trigger capability (T0, V0, Silicon Pixel Detector (SPD), TOF, PHOS, EMCal, Muons, ACORDE). The T0 detector measures the event time with very good precision (< 25 ps). The V0 detector is used as minimum bias trigger and for rejection of beam gas background. ACORDE triggers on cosmic rays for calibration and alignment purposes. As PHOS and EMCal are electromagnetic calorimeters they detect a collision within the (L0) trigger decision window and can then participate in the trigger generation.

## 1.5 Radiation Environment of the Fee

One of the major challenges in building the ALICE detector is that the radiation which the detector shall measure is also potentially harmful for the electronics that will do the actual measurements.

The potential radiation damage to a device is dependent on the particle charge and energy. Simplified, a particle with high charge and low energy is more ionizing and thus more damaging than a particle with low charge and high energy.

There two types of radiation effects that are of concern for the electronics: 1) the cumulative effects, which are related to the total dose<sup>4</sup> that the electronics are exposed to over the lifetime of the project, and 2) the single event effects, which are caused by a single particle. Radiation effects in electronics are discussed in section 4.1.

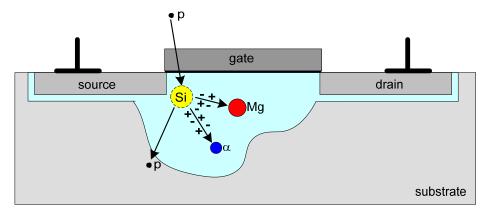

Due to the relatively low total dose of < 6 Gy cumulative effects are expected to be of little concern in the TPC electronics [6]. However, in the location of the TPC Fee, simulations of the radiation environment show a substantial amount of energetic hadrons (E > 10 MeV). A flux<sup>5</sup> of maximum 400 particles/cm<sup>2</sup>/s can be expected at the innermost part of the TPC. The flux is decreasing further away from the collision point and in the outermost part of the TPC the expected flux is  $\sim 130$  particles/cm<sup>2</sup>/s. Due to their low ionizing capability, low charge and high energy, these hadrons are not expected to directly cause a single event effect. Instead they can interact with the silicon nuclei producing highly ionizing secondary particles capable of inducing single event effects. Combined results from the simulation of the radiation environment and from irradiation tests can be used to predict the expected number of single event effects and functional errors in the electronics [7, 8].

For PHOS no similar simulations have been performed, but since PHOS is the outermost detector and the electronics are shielded by the crystals, both the flux and total dose for PHOS is expected to be significantly lower. However, this does not mean that the potential radiation effects on the electronics in PHOS can be ignored.

## 1.6 Online Systems for the ALICE TPC/PHOS Electronics

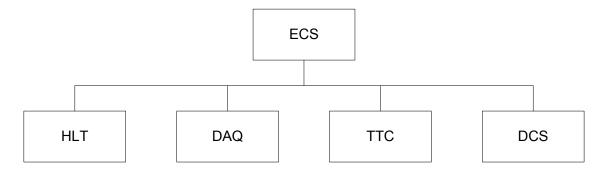

## 1.6.1 Experiment Control System

The different online systems in ALICE are controlled by a single overlying master system: the Experiment Control System (ECS)[9]. The ECS has several tasks. 1) It provides the operators with a unified view of the experiment and a central point from which to steer the experiment operations. 2) It permits independent and concurrent

<sup>&</sup>lt;sup>4</sup> The *dose* (or total ionizing dose) is the energy deposited by the charged particle in a given material and is measured in Gray (Gy). 1 Gy corresponds roughly to the generation of 4.10<sup>11</sup> electron-hole pair in 1 cm<sup>3</sup> silicon.

<sup>&</sup>lt;sup>5</sup> The flux is the number of particles passing through a given area per time unit, and can be considered as the intensity of the radiation. Flux is measured in particles/cm²/sec.

activities on parts of the experiment by different operators. 3) It coordinates the operations of the control systems active on each detector: the trigger control, the detector control, the Data Acquisition (DAQ) run control, and the High Level Trigger (HLT) control. These sub-systems exist in parallel to each other, having no or little cross communication between them.

Figure 1-5: The different online system discussed in the subsequent sections in context of the ECS. From [9].

## 1.6.2 Trigger, Timing and Control System

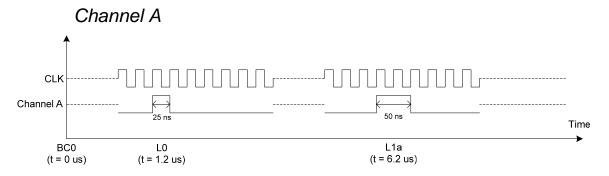

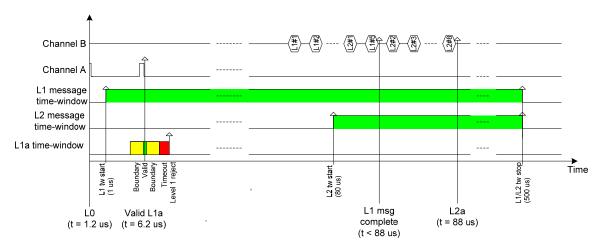

The heart of the ALICE Trigger, Timing and Control (TTC) System [3, 9] is the Central Trigger Processor (CTP) [10]. The CTP is designed to select events containing potential interesting physics at rates that are scaled down to suit the restrictions imposed by the bandwidth of the DAQ system and the HLT. One of the main challenges for the ALICE trigger is to make optimum use of the different subdetectors that are varying both in readout time and detection time. It is also important that the trigger selections are done in a way that is optimised for different running modes, normally Pb-Pb and p-p. The triggers generated by the TTC system are split into a three level hierarchy, of which the first two are considered as a fast first response to the sub-detectors. Each level of trigger is filtering out events that for some reason are not considered interesting. The L0 trigger is the fastest trigger and reaches detectors at 1.2 µs and is too fast to consider all the trigger inputs. A Level 1 accept (L1a) trigger arriving at the detectors at 6.5 µs includes all remaining fast inputs. All in all there are 50 potential inputs for the L0 trigger and 24 inputs for the L1a.

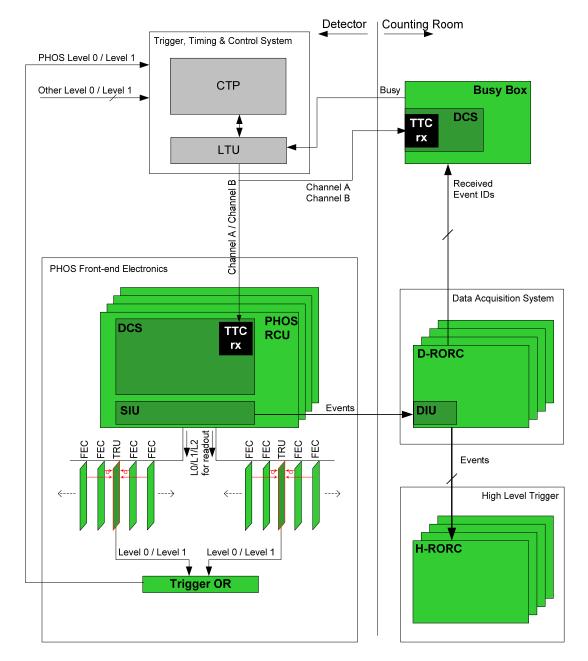

Figure 1-6: Sketch of the Fee for PHOS detector that shows how PHOS acts as a trigger detector as well as how PHOS uses triggers generated by CTP for data readout.

The final level of the trigger, the Level 2 accept (L2a) trigger, is decided by the past future protection condition. The purpose of this is to make sure that pile-ups corrupting the data are avoided within a programmable time interval before and after the collision. Under normal running conditions, this time is decided by the drift time of the TPC detector, i.e. it is issued 88 µs after the time of interaction. The L2a trigger is distributed to the sub-detectors as messages containing information identifying the event. The event identification consists of two parts: the Bunchcrossing ID and the Orbit ID. In the LHC, there are at all times 3563 bunches orbiting in each ring. The Bunchcrossing ID is the number of the bunch that is involved in the collision; while

the Orbit ID gives the number of times all bunches have rotated since the start of the run. Some of these bunches are empty. For p-p it is foreseen that 2808 bunches are filled with protons, while of Pb-Pb only 608 bunches have lead nuclei in them[11]. As a consequence the collision rate is far higher for p-p runs than for Pb-Pb runs.

The CTP distributes the triggers to the sub-detectors using Local Trigger Units (LTUs). There is one LTU per sub-detector. The LTU forwards the trigger signals to the Fee of each sub-detector, but can also be used in stand alone mode for debugging purposes. In this case software on the LTU is emulating the CTP behaviour. Figure 1-6 shows a sketch of the Fee for the PHOS detector that exemplifies the trigger distribution to the sub-detectors. The same logical overview is valid for TPC except for the part that involves the trigger generation. PHOS contributes to one of the trigger sources for L0 triggers and to three (high p<sub>t</sub>, mid p<sub>t</sub> and low p<sub>t</sub>) of the trigger sources for L1a triggers. More details on the data received by the Fee via the Trigger System are discussed in section 5.2.3.

An important feedback for the TTC system from the Fee is the *busy* signal. The *busy* signal is received by the LTU for the given sub-detector. The LTU forwards it to the CTP that masks any incoming triggers from being distributed to the Fee. This is needed if the buffers on the Fee are full and no more data can be accepted. For TPC, PHOS, FMD and EMCal this is solved by using an additional device: the BusyBox. The BusyBox sits outside of the radiation environment and asserts the *busy* signal based on information from the LTU and the DAQ system. A short overview over the BusyBox is given in section 2.4.5.

The CTP synchronizes all triggers received from the trigger detectors with the LHC clock[11]. The LHC clock has a frequency of 40.08 MHz. It is generated from the frequency of the orbiting bunches in the LHC, and distributed as the global clock for all the experiments using the LHC. For ALICE, this clock is distributed by the TTC system together with the triggers and the trigger messages.

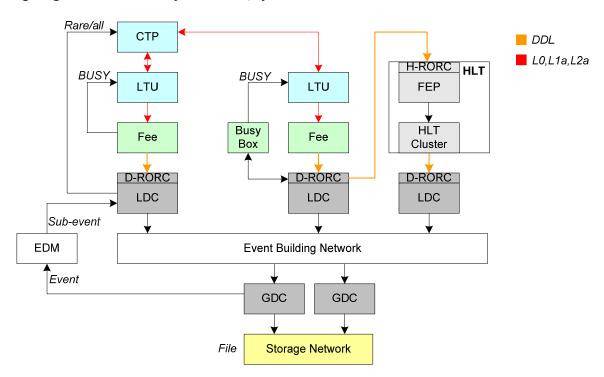

## 1.6.3 Data Acquisition System

The ALICE DAQ system is in charge of moving the data from the detector up to the central data storage of ALICE, concentrate the data and do the eventbuilding [3, 9]. An overview of the ALICE DAQ architecture including TTC and HLT is illustrated in Figure 1-7. This figure exemplifies the architecture for different sub-detector setups. Event fragments from the participating sub-detectors are injected on the Detector Data Links (DDLs) when an L2a trigger has arrived, and all different sub-detectors use the same standard protocol for data transmission. The DDL consists of

three parts. 1) The Source Interface Unit (SIU) which sits on the detector Fee, 2) the Destination Interface Unit (DIU) that is connected to the Data Readout Received Card (D-RORC), and 3) a duplex multi mode optical fiber which connects the SIU and the DIU. The data is collected by a D-RORC on the Local Data Concentrator (LDC). The role of the LDC is to ship the event fragments to a farm of PCs called Global Data Concentrators (GDCs), where complete events are built before being sent disc storage. The Event Destination Manager (EDM) tells the LDCs which GDC computer is available for event reconstruction. The software performing the data acquisition in the ALICE DAQ system is DATE (Data Acquisition and Test Environment). DATE collects the data from the DDLs connected to all detectors. The DAQ system includes a configurable list of which nodes that is expected to be participating in the run. This is the DAQ equipment list. If one of the nodes included in the list does not deliver any event fragments within a given timeout period, the ongoing run is aborted by the DAQ system.

Figure 1-7: The overall architecture of the Data Acquisition System, also including the interface to the High Level Trigger. From [3] (edited).

Several triggers are so frequent that the limiting factor is the performance of the DAQ system. Because of this the main task of the TTC system, the DAQ system and HLT is to select interesting physics events. In Figure 1-7 several ways of dealing with this is shown, of which one is the HLT reducing the amount of data stored to disk significantly. The HLT is briefly discussed in the next section. The *busy* signal is used to mask triggers in case the buffers on the Fee are full. For some sub-detectors the *busy* are set by the Fee itself, while for TPC, PHOS, EMCal and FMD, the *busy* is

set by an external device. Another way of masking triggers is done by the DAQ itself. The DAQ sets a flag to the TTC system if only events defined as rare should issue a trigger. By setting this flag when the temporary storage systems of the DAQ are in danger of being saturated it is ensured that the potentially most interesting events are kept for analysis.

#### 1.6.4 High Level Trigger

The purpose of the HLT [3, 9] is to reduce the overall data rate to fit the constraints given by the DAQ archiving rate that is 1 GB/s. This is achieved by event selection (trigger on event), selection of Region of Interest (RoI) and data compression. The HLT cluster is a PC farm with several hundred nodes for fast online data analysis. The events are filtered so that only events considered interesting are stored to disc for more detailed analysis. A copy of the raw data from the DAQ are forwarded through the D-RORC on the LDC to the HLT Readout Receiver Card (H-RORC) that sits on the Front-end Processor (FEP), see Figure 1-7. The FEP forwards the data to the HLT cluster. The output of the HLT is streamed back to the DAQ for permanent storage, containing region of interest information, trigger information, event summary data and the compressed event data itself.

## 1.6.5 Detector Control System

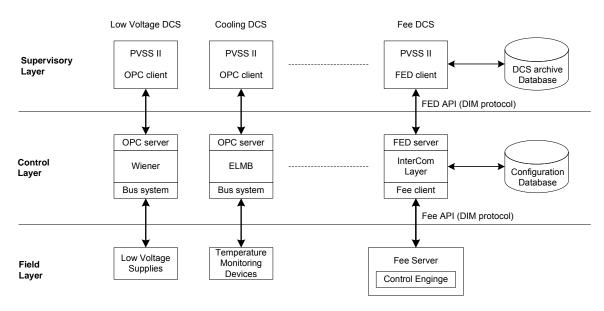

Figure 1-8: The three-layered logical architecture of the DCS exemplified with DCS for low voltage, cooling and Fee.

The primary task of the ALICE Detector Control System (DCS) [3, 9] is to make sure that the operation of the ALICE experiment is done safely in a correct manner. As all

experimental equipment can be operated/controlled remotely via the DCS, the complete ALICE experiment can be operated from a single location: the ALICE Control Room. The DCS is concerned with all parts of the detector from gas, cooling, ventilation, access control, and most importantly in the context of this work; the Fee. The DCS is a heterogeneous system where the tasks are distributed over many PCs and embedded computing devices. This ensures a scalable design, and allows independent operation of all the different parts involved.

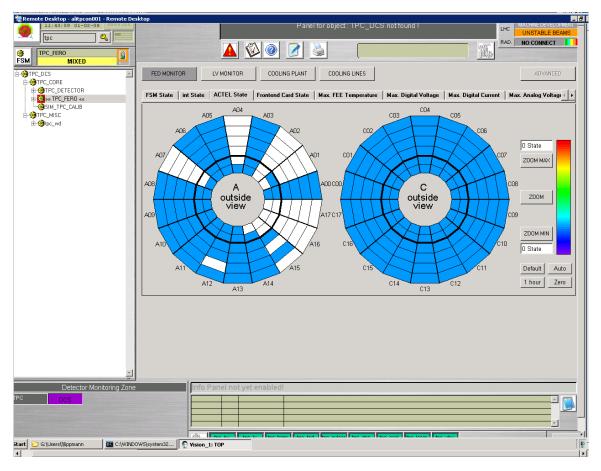

The DCS forms a three layered structure both physically and logically. This is shown in Figure 1-8 for the operation of low voltage, monitoring of temperatures and the Fee. The Supervisory Layer is the top level with the operator's user interface, implemented in a commercial Supervisory Control and Data Acquisition system: ProzessVisualisierungs- und Steuerungs-System (PVSS). Examples of such interfaces for the Fee DCS are given in Figure 3-10 and Figure 4-11. The Control Layer is a communication layer consisting of several PCs, and the Field Layer is where the different devices are found. All the nodes in the system work in parallel, feeding the operator with useful information concerning the status of the system, or responding to commands given at the top level.

The Fee DCS is responsible for configuring, monitoring and controlling the Fee of sub-detector systems, and it is important to notice that the control system is detached from the data flow. The control system is designed to automatically act upon different conditions that may occur in the equipment. The configuration task includes uploading configuration data to the Field Devices. This data is stored in the Configuration Database and includes physical location of the equipment, hardware addresses and different operational modes. This information covers both hardware and software. The DCS archive database is used for storing the monitored values.

## **Chapter 2**

## **TPC and PHOS Front-end Electronics**

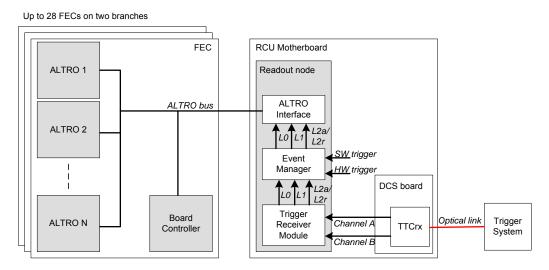

As TPC and PHOS Fee have a common design and share most of the components, the description of the two systems is combined in this chapter. In the introduction the Fee are put in context with the DAQ system, the DCS and the TTC system. Then the topology of the PHOS Fee and TPC Fee is discussed, before the different components of the Front-end electronics are presented.

#### 2.1 Introduction

The Fee of the ALICE TPC and PHOS detector consist of all the hardware components that are involved in the readout of the data and system monitoring and control. The Fee have to comply with strict requirements defined in [4] for TPC. The original requirements for PHOS are described in [5], but the Fee for PHOS have later been redefined and now the architecture and many of the components are the same for TPC and PHOS. Originally, the concept of the Fee was designed for TPC but because of the flexibility of the system it was adopted by other ALICE sub-detectors of which PHOS is one. Related to the readout and the control systems the following requirements must be fulfilled:

- As the Fee are sited close to the collision point, especially for TPC, the radiation tolerance is of vital importance. A major concern is that the electronics are operating in an environment that in itself is a source of errors. This radiation environment is described in section 1.5.

- The electronics are physically unavailable when the system is operative. This implies that remote operation of the Fee should be possible, and that vital components should be remotely upgradable. It also means that it is mandatory that the devices that cannot be upgraded are reliable and stable.

- The TPC event rate of central Pb-Pb and p-p events are 200 Hz and 1 kHz respectively. The TPC will at these rates produce about 140 GB/s and 710 GB/s of data each[12]. Per Readout Node this is about 650 MB/s and 3.28 GB/s produced data. The data throughput per Readout Node for PHOS is

slightly lower. As the bandwidth of the DDL is 200 MB/s, this implies that intelligent data compression and readout schemes must be implemented.

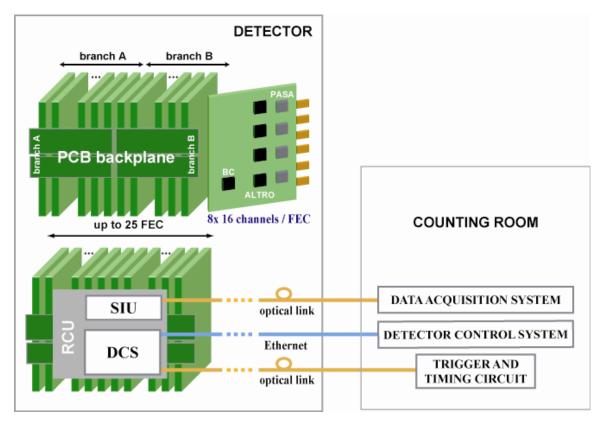

Figure 2-1: The TPC Fee. Top: Front End Cards from the same partition are connected by means of a custom backplane. Bottom: The RCU interfaces the partition with the Data Acquisition, Detector Control and Trigger Systems. From [13].

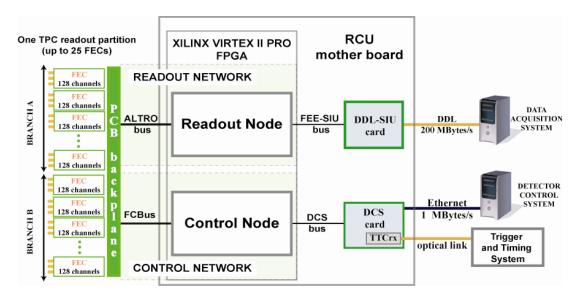

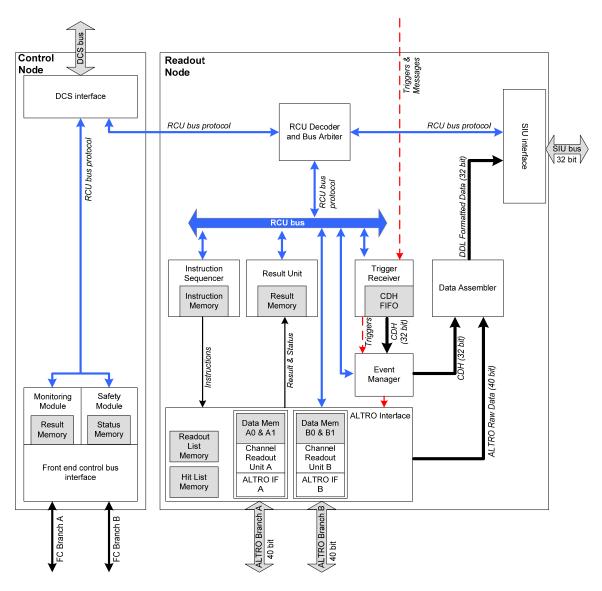

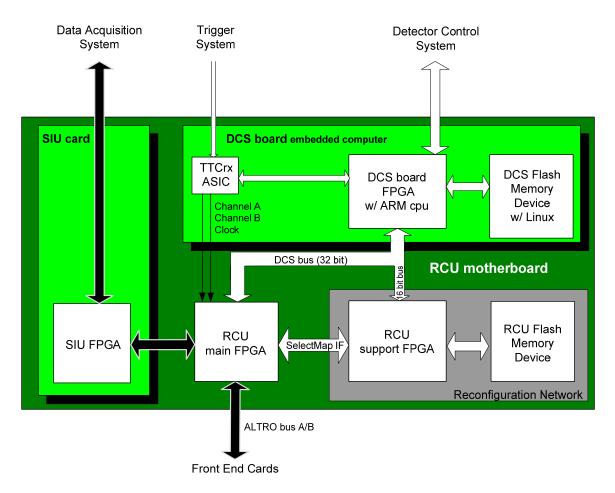

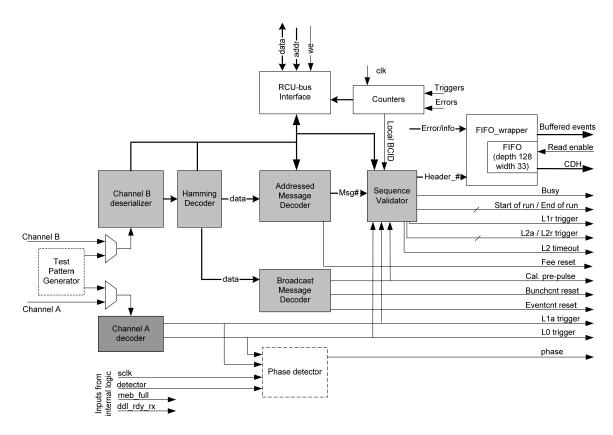

A schematic overview of the Fee for TPC in context with the online systems in ALICE is given in Figure 2-1. For both PHOS and TPC the Fee consist of a set of Front End Cards (FECs) that receive analogue data from the detector sensors. The FEC amplifies and shapes the analogue signal, performs analogue to digital conversion and digital filtering of the data. As shown in the topmost part in Figure 2-1 up to 25 FECs can be connected to one Readout Control Unit (RCU) via two separate branches for the TPC, while for PHOS there are always 28 FECs per RCU. As PHOS is also a trigger detector, there is additionally a Trigger Region Unit (TRU) board on each branch. The TRU is discussed in section 2.4.4. The bottom part of Figure 2-1 shows the RCU connected to the FECs via the backplanes. The RCU consist of the RCU Motherboard, the DCS board and the SIU. The DCS board acts as a node in the Field Layer of the DCS and connects to the higher hierarchical levels of DCS via a standard Ethernet connection. The DCS board is also the receiver of the master clock and triggers via an optical link to the TTC system. The SIU connects to the DAQ system and pushes the data out on the DDL. All these components are discussed in more details in the subsequent sections.

There are 216 RCUs in the TPC, reading out a total number of 570132 channels connected to equally many detector pads. In the final state of the PHOS detector with all five modules installed, there will be 20 RCUs that altogether serve 35840 channels connected to 17920 crystals (There is one high gain and one low gain channel per crystal).

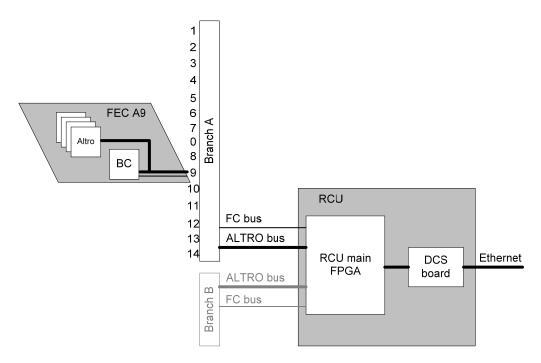

## 2.2 TPC Fee Topology

Figure 2-2: Each TPC sector is divided into 6 readout partitions with 18, 20 or 25 Front End Cards. Each readout partition is configured and readout using one RCU connected via two independent branches. From [13]

The TPC detector is divided into 36 sectors, 18 on each of the endplates of the TPC barrel. These sectors are divided into 2 readout chambers, the inner readout chamber and the outer readout chamber. There are 2 readout partitions in the inner chamber and 4 readout partitions in the outer chamber. One readout partition is read out by one RCU. As seen in Figure 2-2 there is an unequal number of FECs on the different partitions. In the area of the TPC covered by the inner readout chamber the occupancy is higher, and therefore the readout pads are smaller to provide a better spatial resolution. This implies that the number of channels in this region is higher, and more FECs are needed.

## 2.3 PHOS Fee Topology

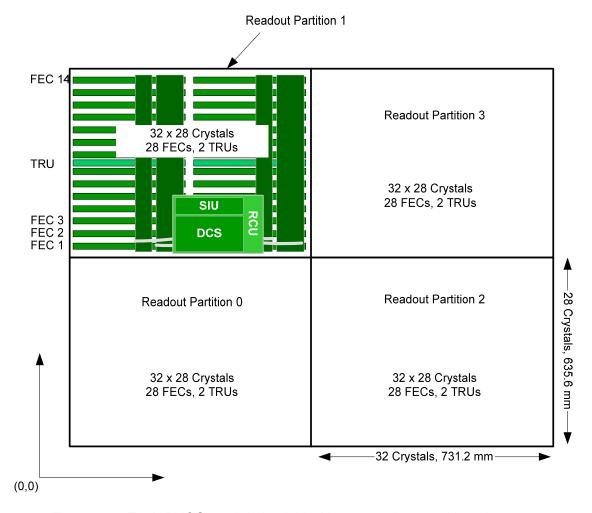

Figure 2-3: Each PHOS module is divided into 4 readout partitions in context of data readout. When in context of PHOS as a trigger detector, one branch is regarded as a trigger region and is served by one TRU.

The PHOS detector consists of 5 modules. Each PHOS module (Figure 2-3) is divided into 4 readout partitions that are served by 1 RCU each. One readout partition is mapped to a matrix of 32 x 28 crystals, reading out two channels per crystal divided into high gain and low gain. As for the TPC one branch consists of two PCB backplanes, one for data and one for control signals, and 14 FECs are connected per branch. Additionally for PHOS a ~40 cm flat ribbon cable extension connects the PCB backplanes to the RCU. The TRU on each branch defines this area to be a trigger region, connecting to all the FECs on the given branch. The TRU connects to the RCU using the same PCB backplane as the FECs.

#### 2.4 Front End Electronics Devices

#### 2.4.1 TPC Front End Card

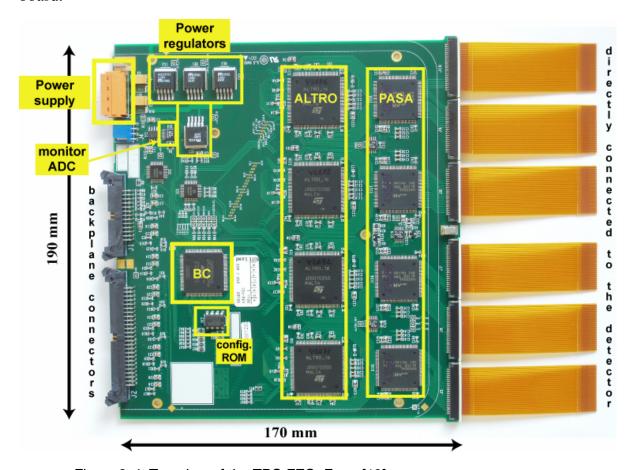

The TPC FEC (Figure 2-4) connects to the detector pads and processes the signals generated by the charges deposited on the pads. One pad maps to one readout channel. There are two important devices involved in the signal processing: the PreAmplifier ShAper (PASA) and the ALICE TPC Readout Chip (ALTRO) chip. On the FEC there are 8 PASAs and 8 ALTROs supporting altogether 128 channels per board.

Figure 2-4: Top view of the TPC FEC. From [13]

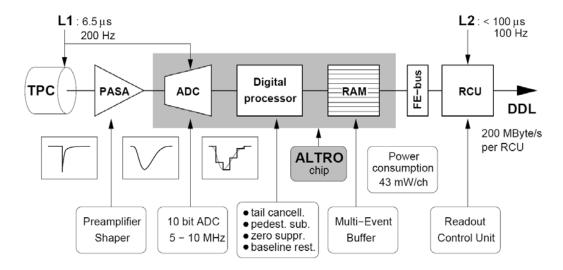

Figure 2-5 shows the signal processing path of each channel in the TPC Fee. The charge collected on the TPC pads is amplified and integrated by the PASA chip. It produces a pulse with a rise time of 150 ns and a shaping time of 190 ns. The pulse is then sampled by a 10 bit Analogue to Digital Converter (ADC) at a configurable rate of 2.5 MHz to 10 MHz. The digitized signal is processed by digital filters that allow for baseline restoration, pedestal subtraction, zero suppression and tail cancellation, before being buffered in a memory. The ADC and the digital processing logic are contained in the ALTRO [14]. The digital processing is configurable from the RCU.

Figure 2-5: Block diagram showing the signal path in the TPC Fee. From [3].

The controlling functionality on the FEC is maintained by the Board Controller, marked BC in Figure 2-4. The main task of the TPC Board Controller is to monitor the health of the FEC by reading voltage levels, currents and temperatures. The Board Controller is discussed in section 3.6.

#### 2.4.2 PHOS Front End Card

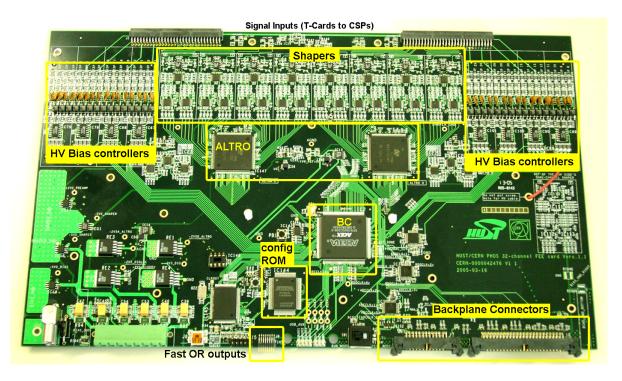

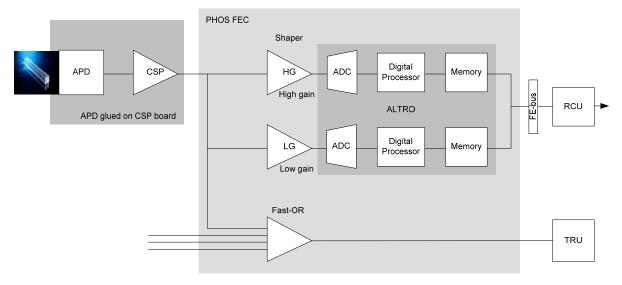

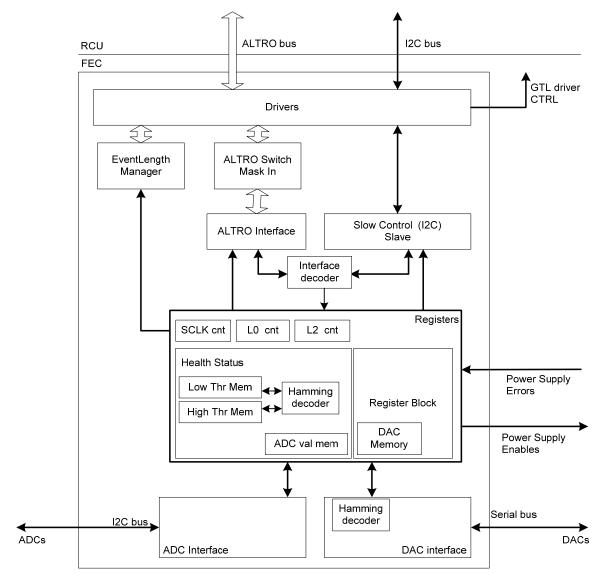

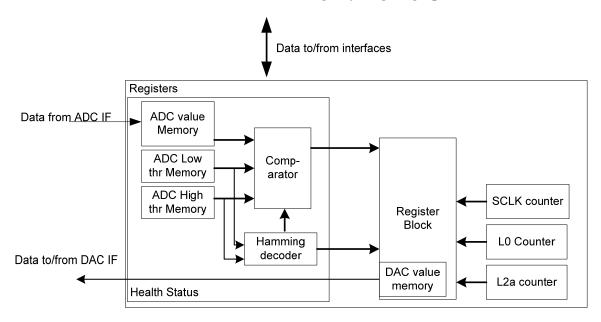

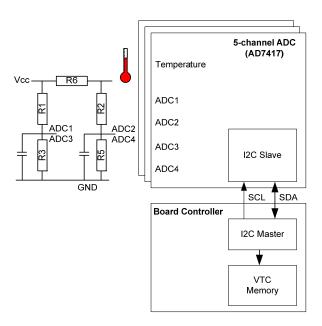

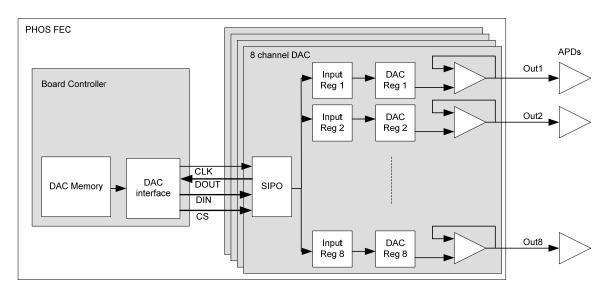

As seen by Figure 2-6, the PHOS FEC includes many of the same components as the TPC FEC. The PHOS FEC contains 4 ALTROs serving 32 inputs from the charge sensitive amplifiers (CSPs) that are split into high gain and low gain signals using altogether 64 ALTRO channels. The digital part from the ALTRO and to the backplane connectors is identical to the TPC FEC, but the PHOS FEC implements two additional features: 1) High Voltage Bias Controllers that sets the bias voltage to the APDs, and 2) the Fast-OR output to the TRU. This is a special fast shaper that sums 4 inputs into a Fast-OR output signal. With the 32 input channels, this gives 8 analogue sums per FEC that are made available on the output connector. The signal path of PHOS is shown in Figure 2-7. Except for the trigger generation part, it is similar to the signal path of the TPC FEC.

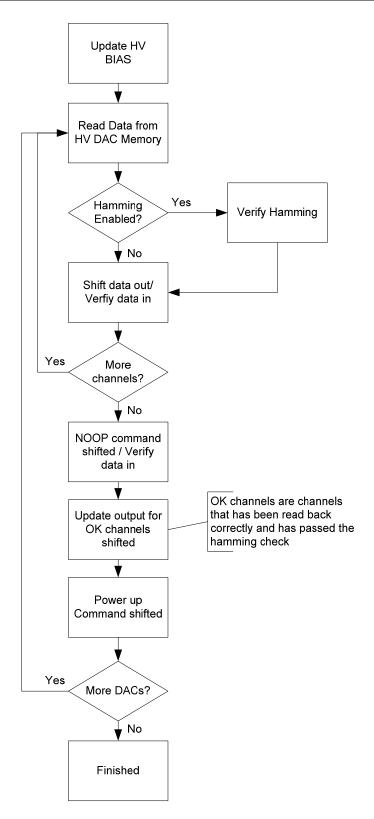

The Board Controller controls the board; monitoring voltage levels, currents and temperatures made available by 3 ADCs placed on different locations on the board. The Board Controller is also in charge of controlling the Digital to Analog Converters (DACs) that set the High Voltage Biases.

Figure 2-6: Top View of the PHOS FEC.

Figure 2-7: Block diagram showing the signal path of PHOS, including the trigger generation part.

### 2.4.3 Readout Control Unit

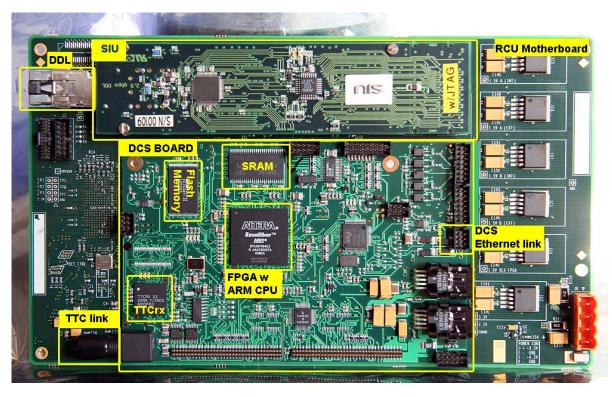

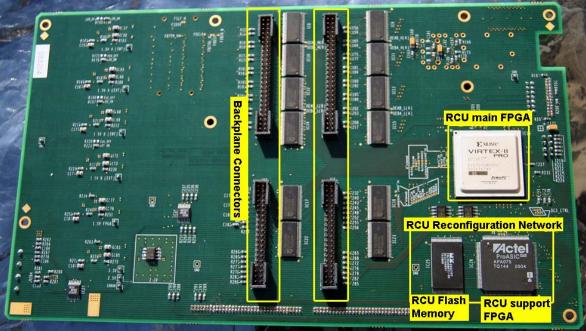

Figure 2-8: Top: The RCU top view including DCS board and SIU card. The RCU motherboard is in the back with the SIU card (top) and the DCS board (bottom) attached. Bottom: The RCU bottom view where the FPGAs and the connectors to the PCB backplane are located.

A picture of the RCU is shown in Figure 2-8. In the topmost part the three boards comprising the RCU are marked. The SIU [9] is on the top with the optical connector

to the DDL and the DAQ system. The DCS board is in the bottom with the optical link to the TTC system, and the Ethernet connection to the DCS. In the back is the RCU Motherboard.

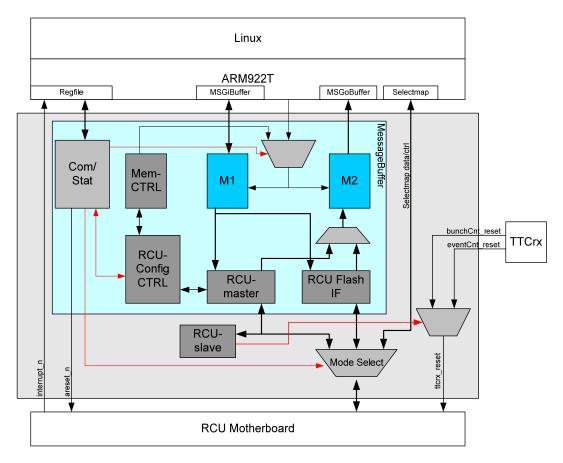

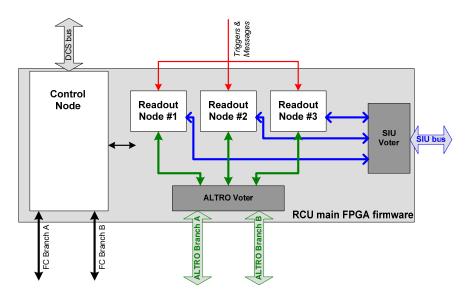

Figure 2-9: The architecture of the Fee for one readout partition in TPC. From [13].

The tasks of the RCU are twofold. 1) It moves the data from the FECs to the DDL, and 2) it controls the Fee sub-system consisting of the RCU with the belonging FECs. This is illustrated in Figure 2-9 for one TPC readout partition, but it is equally valid for a readout partition in PHOS.

To control the data readout, the RCU distributes two clocks to the FECs, the readout clock and the sampling clock. The readout clock is essentially the LHC clock forwarded via the RCU main FPGA to the FECs, while the sampling clock is generated in the RCU based on the LHC clock, and has a configurable frequency of 2.5 MHz – 10 MHz. The sampling clock is used by the ADCs in the ALTROs to sample the analogue data on the input.

### Readout Control Unit Motherboard

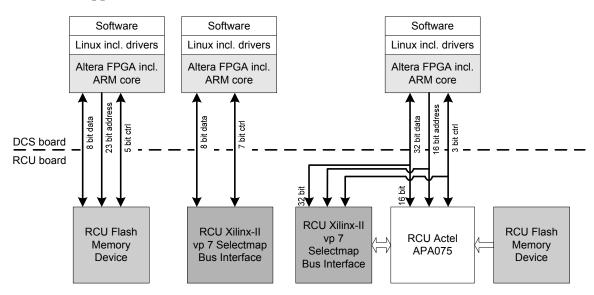

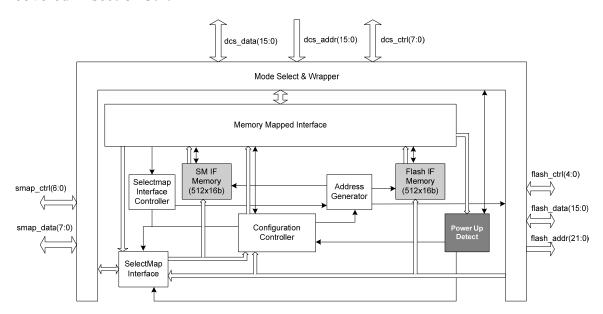

The RCU Motherboard hosts the FPGA that implements the readout and control functionality on the RCU (Figure 2-8, bottom). The RCU main FPGA is a Xilinx Virtex-II Pro XC2VP7[15, 16], and it has interfaces to the Gunning Transfer Logic (GTL) drivers that connect to the PCB backplanes, to the DCS board, and to the SIU card. As seen in Figure 2-9, the RCU main FPGA is a vital part of the data-path, and it is in charge of the basic controlling functionality of the Fee.

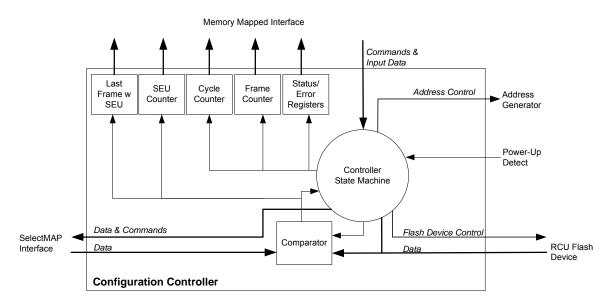

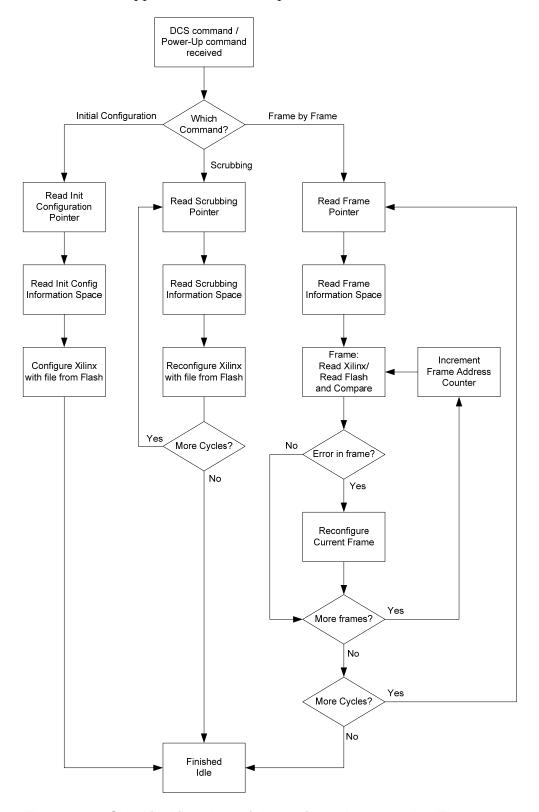

In addition to the RCU main FPGA, the RCU hosts one additional Flash based FPGA[17] and an 8 MB Flash Memory Device[18] that together implement the RCU

Reconfiguration Network. The configuration files for the RCU main FPGA are stored on the Flash Memory Device and the task of the RCU support FPGA is to configure the RCU main FPGA using these configuration files. This solution is extensively discussed in Chapter 4.

# Detector Control System Board

The DCS board<sup>6</sup> was originally designed for TRD, but because of the flexibility of the board it has been used for several other sub-detectors in ALICE. For TPC and PHOS the DCS board is in use on the RCU (Figure 2-8), but is additionally utilized on several other smaller systems: the BusyBox, the PHOS Trigger-OR, the PHOS led calibration system, and various small controlling systems for TPC (Gating grid, Laser etc.). As seen in Figure 2-8, the DCS board interfaces the higher levels via a 10Mbit/s Ethernet connection. The DCS board is also equipped with an SRAM device, a Flash Memory Device acting as a hard drive, and an Altera Excalibur FPGA with an embedded ARM processor core[19]. These components turn the DCS board into an embedded computer, on which a small tailor made version of Linux is installed. All ALICE sub-detectors that use the RCU as the readout controller use the same system setup of the DCS board. This is based on the TRD version[20], and all the software/firmware that the sub-detectors have in common is inherited from TRD, including the Linux operative system. The Linux is the main cause of the flexibility of the DCS board, making updates and maintenance straightforward to do.

An additional component not highlighted in Figure 2-8 is the small Lattice Complex Programmable Logic Device [21] (CPLD) that is in charge of the clock distribution and voltage regulator enabling. This makes it possible to power down the underlying Motherboard and change the clock frequency of the system clock. This component is not actively interfaced together with the RCU Motherboard since the RCU Motherboard is considered to always be powered on<sup>7</sup>, and the clock frequency of the RCU Motherboard is fixed to the LHC clock frequency.

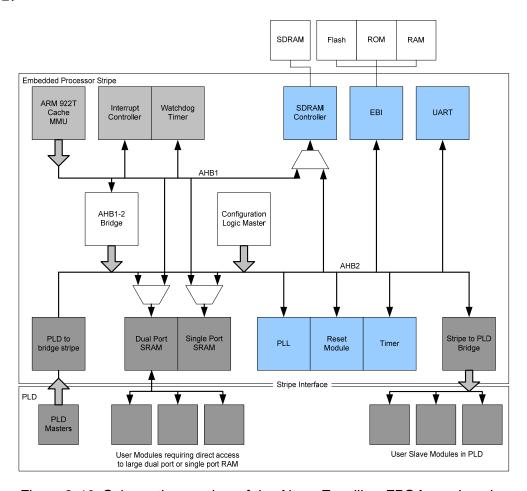

The Altera Excalibur FPGA is extensively described in [19]. The FPGA consists of two different parts. One part contains predefined modules like the processor core,

<sup>&</sup>lt;sup>6</sup> The DCS board is designed and built at the Kirchhoff-institute for Physics, University of Heidelberg. http://www.kip.uni-heidelberg.de/ti/DCS-board/current/

<sup>&</sup>lt;sup>7</sup> The actual reason for this is a hardware bug on the RCU Motherboard. The DCS board power-on-reset is connected without a diode to the FPGAs and a pull-up on the RCU motherboard. If the DCS board disables the RCU Motherboard voltage regulators, the pull-up will be changed to a pull-down which is strong enough to issue a reset. As a result, the DCS board will be rebooted immadiately if the RCU Motherboard is powered down.

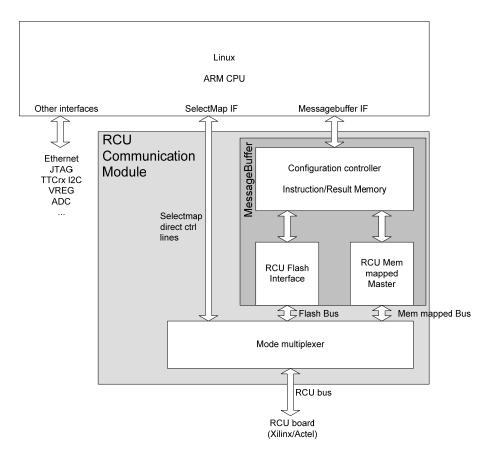

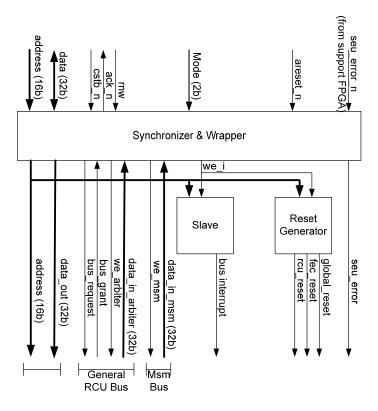

interrupt controller, various interfaces etc. The other part is the Programmable Logic Device (PLD), where the entire user defined logic is implemented. A schematic overview of the different components and how they are connected are found in Figure 2-10. The Excalibur device contains an ARM 922T embedded processor core that communicates to other modules using an AHB bus protocol. The internal communication is divided into two separate bus systems to ensure that the processor activity is unaffected by peripheral and memory activity. The AHB1-2 Bridge handles all transactions from the processor core to the PLD or slaves connected to the AHB2.

Figure 2-10: Schematic overview of the Altera Excalibur FPGA used on the DCS board. From[19].

Some of the key modules for the DCS board in Figure 2-10 are:

- *Dual Port/Single Port SRAM:* Important in several modules, like for instance the RCU Communication Module (section 3.4) and the Ethernet Module.

- Expansion Bus Interface (EBI) is used to communicate with the external Flash Memory Device.

- *Universal Asynchronous Receiver/Transmitter (UART):* This is very handy for debugging and testing as it provides a possibility to have the Linux command line available via the serial port of a connected PC.

- *Interrupt Controller:* Handles all the interrupts, also the ones coming from the PLD part. One of these interrupts is for instance fired when a FEC has been switched off due to an error situation handled by the RCU.

- Watchdog Timer: Resets the whole system, thus providing protection against software failures. On the DCS board it can be used to trigger a reboot of the board based on for instance radiation related errors as the reset of the Watchdog is controlled from software.

- *PLD to Stripe/Stripe to PLD Bridge:* These two bridges do the communication between the user logic in the PLD and the processor core.

## 2.4.4 PHOS Trigger Generation Hardware

# Overview Analog Digital TOF shower from crystals Analog sums FEC 1 FEC 2 L0 trigger L1 triggers (high, mid, low p,) TRU L0 trigger L1 triggers FEC 3 Trigger OR СТР FEC 14

Figure 2-11: Sketch emphasizing one trigger region of PHOS to show the data flow of the trigger detector functionality.

As the PHOS detector is fast enough to be used for L0 and L1a trigger decisions in ALICE. Each FEC in a trigger region submits analogue sums of the input signals to the TRU. These analogue sums are digitized and then processed by the FPGA on the TRU into L0 and L1a triggers. The Trigger-OR board combines triggers from all TRUs, and forwards them to the CTP. See Figure 2-11. The timing requirement for

generating the L0 trigger implies that PHOS must deliver the L0 trigger to the CTP 800 ns after the time of interaction. This includes the extra delay of 200 ns introduced by the cable length of 40 meters from the Trigger-OR to the CTP. The L0 and the L1a trigger is based on 8 analogue sums per FEC, performed on the FEC by fast summing shapers over a 2x2 crystal matrix, before being fed to the TRU.

## Trigger Router Unit (TRU)

The present version of the TRU contains a Xilinx Virtex-II Pro FPGA. 14 ADCs digitize the 112 analogue input signals received from the FECs, before entering the FPGA. The triggers are generated in the FPGA by summing up 2x2 analogue sums giving a total area of 4x4 crystals in space, and additionally summing up the analogue input signals in time over a time span of 100 ns. The L0 trigger is issued if the deposited energy given by the space time sum exceeds a programmable threshold between 10 and 230 MeV[22]. Three L1a triggers can be issued if there has been a valid L0 decision. These are based on three different programmable thresholds between 0.5 and 30 GeV. The thresholds are set to separate the events into high p<sub>t</sub>, mid p<sub>t</sub> and low p<sub>t</sub> events, based on the value of transverse momentum of the photon. The TRU is presented in [22] and the firmware solution is discussed in depth in[23].

# Trigger-OR

The purpose of the Trigger-OR board is to collect all the L0 and L1a triggers from the 40 TRUs in the PHOS detector. The L0 triggers are ORed through a fast OR gate. The same approach is currently used for the different L1a triggers as well.

The present concept of the TRU analyzing the data, while the Trigger-OR only forwards the triggers to the CTP might be changed in the future. Instead of sending triggers from the TRU, the raw data will be shipped, leaving the data analysis to the Trigger-OR. This opens the possibility to treat the PHOS detector as a whole, not being limited by the boundaries of a trigger region.

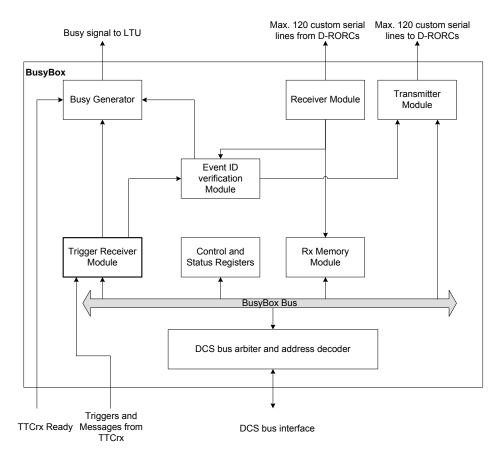

# 2.4.5 BusyBox

One important task of the readout system is to block the CTP from sending triggers if the buffers on the Fee are full and no more triggers can be handled. For all subdetectors using the RCU (TPC, PHOS, FMD and EMCal), the *busy* is generated by the BusyBox. The BusyBox is shown in Figure 2-12 and is a dedicated board that hosts two Xilinx Virtex-4 FPGAs and a DCS board. The sub-detector is considered busy 1) when the buffers on the FEC are full; 2) a trigger sequence is being received

from the TTC, or 3) when the TTC system sends a global reset to the Fee. To assert the *busy* line, the BusyBox needs to know what triggers are issued and how many multi event buffers are occupied in the Fee. The CTP will not send any triggers as long as the *busy* signal is asserted by one of the sub-detectors.

Figure 2-12: Picture of the BusyBox with open cover to display the components. The important components are labeled.

The trigger information is acquired by the Fee trigger reception logic (see section 5.2) communicating with the LTU via the TTC receiver chip (TTCrx) on the DCS board. This implies that the same logic is used to decode the trigger sequences as is used in the RCU. For information regarding the status of the buffers, communicating directly with the Fee would be inconvenient because it is located inside the detector in the radiation environment. The solution is to communicate with the D-RORCs which during a data readout operation receive the event-fragments from the Fee. For TPC there are 216 D-RORCs that are connected to the BusyBox via twisted pair LVDS cables. To be able to serve that many connections, add-on boards are needed for the BusyBox that are connected to the BusyBox board via flat cables. These are the connectors as seen in Figure 2-12. FPGA #1 will serve up to 120 LVDS pairs, while FPGA#2 serves the remaining 96. This also implies that for PHOS, a smaller

BusyBox with only one FPGA has been designed, that serves the 20 PHOS D-RORCs. The *busy* output is forwarded by the LTU to the CTP, which masks all possible trigger situations until the *busy* is released.

# **Chapter 3**

# **Detector Control System for the Fee**

In this chapter the Detector Control System for the Front-end electronics is described, focusing only on the field layer devices. The DCS is described top down, from the software on the DCS board, via the RCU and down to the Board Controller on the FECs. The work of this thesis is mostly concerned with DCS board firmware and PHOS Board Controller, and these two projects will be given more attention than the other modules of the Fee DCS. Several other motherboards also host the DCS board (for instance BusyBox and PHOS Trigger-OR), and the adaptation done to the DCS board firmware for these boards is discussed. The reconfiguration logic of the RCU Motherboard – which is a vital part of the Fee control system – is given special attention in a separate chapter

# 3.1 Introduction

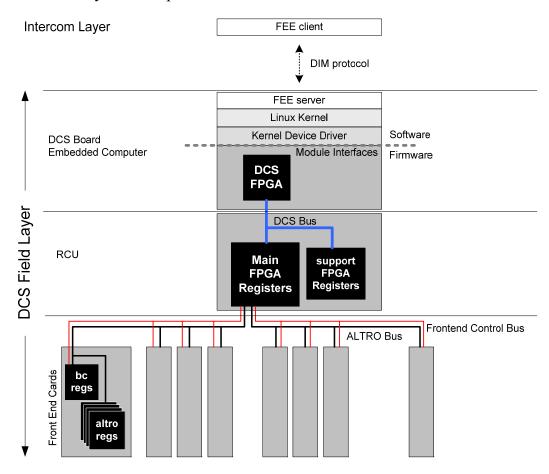

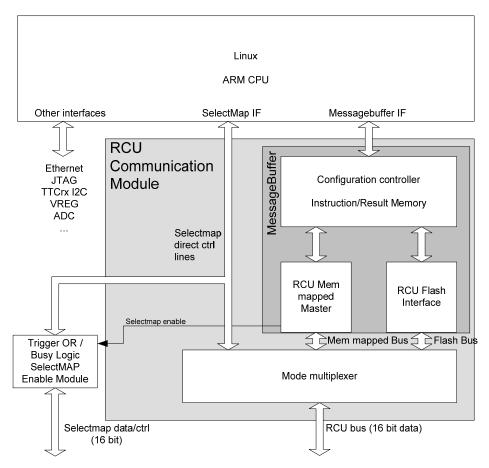

Whereas the general DCS architecture is discussed in section 1.6.5, this chapter will only focus on the DCS for the Front-end electronics; more precisely the Field Layer devices. Figure 3-1 shows a schematic of the Fee DCS Field Layer. The Front-end electronics Server (FeeServer) software running on the DCS board interfaces the higher levels, and custom made Linux device drivers communicate with the RCU. In the context of the control system, the RCU main FPGA device handles the monitoring and configuration of the FECs. The FECs both in TPC and PHOS host an SRAM based FPGA: the Board Controller. The Board Controller reads the temperature, voltages and currents from ADCs on the FECs and makes them available in memory. The monitored values on the FECs are read by the DCS using the Front-end Control (FC) Bus, where the RCU acts as an abstraction layer. These values are published to the higher levels by the FeeServer, and are displayed to the operator at a PVSS display in the ALICE control room.

If any measured value is violating a predefined threshold, it is of vital importance that the Fee DCS acts immediately. This implies that already at the firmware level, an automatic procedure must be applied to deal with such a situation or else it might lead to permanent damage of the FECs. It is also crucial that all actions taken at the lower levels are reported to the operator at the top. This includes interpreting and combining the status and error registers in the various firmware modules in an overviewable way for the operator.

Figure 3-1: Sketch showing the Field Layer devices for the TPC/PHOS Fee.

Another important issue in the context of the Fee DCS is the handling of radiation related errors. As the Fee are operating in a radiation environment, single event upsets (SEUs) can and will happen in the SRAM based FPGAs that are used throughout the system. The consequence for the RCU can be that the data flow will be interrupted, while an expected consequence for the DCS board is that the Ethernet communication to the higher levels is lost. The problem is partly handled at the RCU Motherboard by the RCU support FPGA that controls the configuration memory of the RCU main FPGA. This supervisory system is recognized as the Reconfiguration Network in Figure 2-8. It is a very important component of the DCS, and this topic will be specially covered in Chapter 4. For the DCS board no such solution exists, therefore it is vital that the DCS board has a possibility to discover that it is failing and reboot itself. Rebooting the DCS board will reconfigure the firmware on the FPGA, escaping from any SEU induced error situations. This also has its side effects. It implies that the DCS board will be offline for the time it takes to reboot, and erasing the contents in the FPGA makes the signals between DCS and RCU float. It

is very important that the status of the DCS board does not inflict on the operation of the RCU, or any other Motherboard that hosts the DCS board.

### 3.2 DCS Board Software

### 3.2.1 Communication Software on the DCS board

Each DCS board implements a FeeServer which the higher layer subscribes to as a client using DIM (Distributed Information Management) communication framework<sup>8</sup>. The core of the FeeServer is device independent. It provides general communication functionality, remote control and update of the whole FeeServer application. The core can be used for different devices, i.e. different detectors of the ALICE experiment. The device dependent actions are adapted for each specific device and are executed in separated threads. This makes a controlled execution possible.

The Control Engine implements the device dependent functionality of the FeeServer, which includes methods for initializing and cleaning up the device, as well as command execution and device data access. As the DCS board runs a Linux operating system, the access to the specific hardware is done via Linux device drivers. The use of device drivers to communicate with different parts of the hardware introduces an abstraction layer which decouples software from hardware. Updated firmware modules and device drivers with new functionality can at any time be inserted into the system. This establishes a system that is easy to maintain and can with little effort be modified to meet future demands, despite if the whole detector system is physical unavailable after project startup.

The Control Engine, FeeServer and the DCS architecture in general is extensively discussed in [24]. The DCS board including the Linux operative system is explained in [20].

\_

<sup>8</sup> http://www.cern.ch/dim

# 3.2.2 The DCS Board Logical Architecture

## DCS board Flash Memory Device Architecture

The 8 MB Flash Memory Device[18] that acts as a hard drive on the DCS board is divided into 4 memory banks where different key content is located:

- Armboot Bootloader and Firmware

- *Bootenv* The boot environment where for instance the board's MAC address is stored.

- *Kernel* The ArmLinux Kernel.

- *DCSrootfs* The root file system of the DCS board.

For the TPC/PHOS version of the DCS board, the Bootenv and Kernel are inherited directly from the TRD version with no changes applied. The Armboot part is naturally updated because of the needed firmware changes, and this is also true for the software part located on the DCSrootfs.

### The Root Filesystem

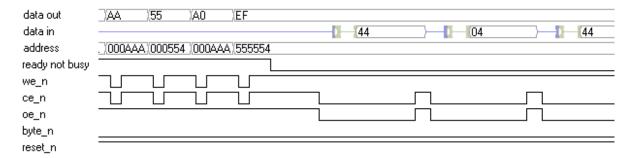

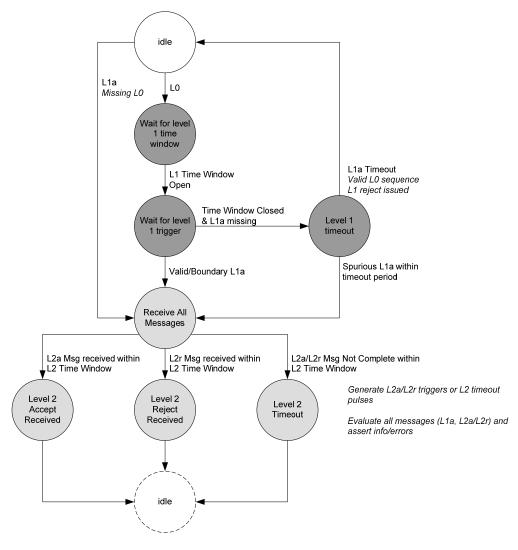

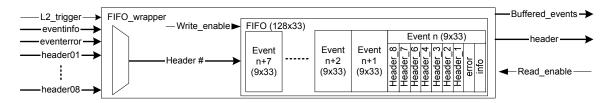

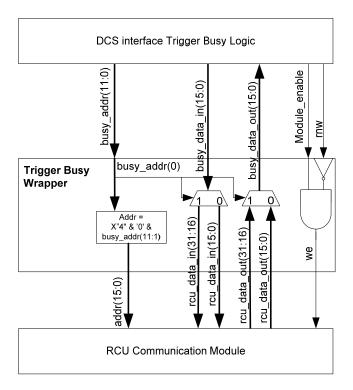

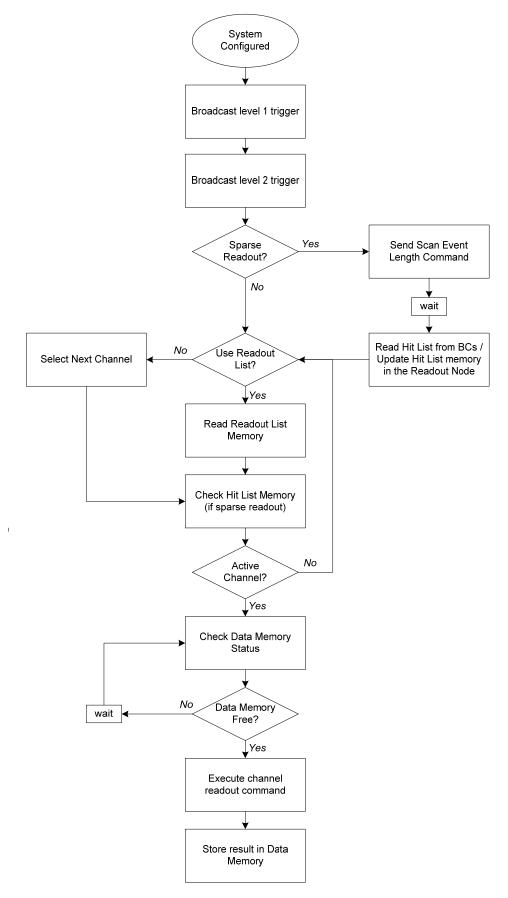

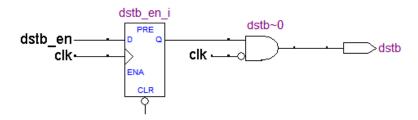

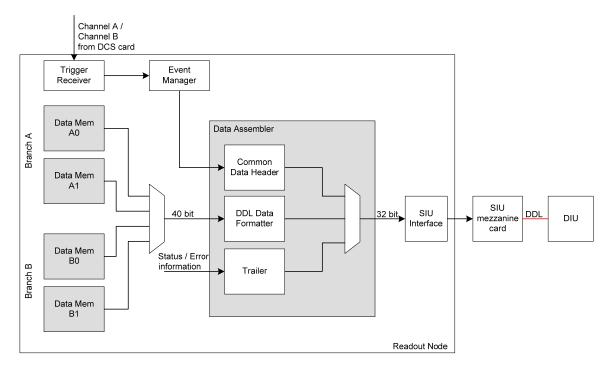

The root file system is formatted in the JFFS2 (Journaling Flash File System 2) type. JFFS2 is writable, fail safe against power loss, compresses data, takes care of wear leveling<sup>9</sup> and is often chosen for embedded systems.