22 April 2008

# Design and test of the Digital Opto Hybrid Module for the CMS Tracker Inner Barrel and Disks.

F. Benotto<sup>3)</sup>, R. Ciaranfi<sup>1)</sup>, R. D'Alessandro<sup>1)</sup>, N. Demaria<sup>3)</sup>, G. DeRobertis<sup>2)</sup>, S. Mersi<sup>1)</sup>

#### Abstract

One of the most important tasks to be performed in the CMS Tracker detector is the communication between hundreds of silicon modules and the central Control System under the supervision of the Data Acquisition System. To manage such complexity, modules are grouped in a hierarchical structure. Each group is controlled by a Communication and Control Unit (CCU). Several CCU form a ring with a Front End Controller as master. The entire Tracker Inner Barrel and Disks detector contains roughly 100 such rings called Control Rings. A description is given here of the implemented ring architecture for the detector and of the solutions found to provide a reliable and easy way to interconnect these groups.

<sup>&</sup>lt;sup>1)</sup> INFN and University of Firenze, Firenze, Italy

<sup>&</sup>lt;sup>2)</sup> INFN Bari, Italy

<sup>&</sup>lt;sup>3)</sup> INFN and University of Torino, Torino, Italy

## **1** Introduction

One of the most important tasks to be performed in the CMS Tracker detector [1] is the communication between hundreds of silicon modules and the central Control System under the supervision of the Data Acquisition System (DAQ). To manage such complexity, modules are grouped in a hierarchical structure. Each group is controlled by a Communication and Control Unit (CCU). Several CCU form a ring with a Front End Controller (FEC) as master. The entire Tracker Inner Barrel and Disks detector (TIB/TID) contains roughly 100 such rings called Control Rings.

In this manner the LHC clock and level one trigger are distributed through the many Control Rings. This architecture has one fundamental weakness. Namely the failure of one of the components can jeopardize the whole ring and so forfeit a non-negligible amount of detector modules. In the TIB/TID Control Ring size varies making it difficult to adopt a uniform connection scheme of the components. To address both issues a particular implementation of the CCU redundancy scheme was designed; one which allows great flexibility in the number of ring components itself while safeguarding ring operation in case of a component failure. To this purpose a dedicated board was constructed, which carries optical to electrical converters (Digital Opto-Hybrids) and distributes the ring signals to the CCU. This note covers the design and testing of the Digital Opto-Hybrid Module (DOHM) implementing the communications between FEC and CCU. Also mentioned are the technical details for the correct operation of the ring and the testing and quality assurance procedures followed. More than 100 DOHM PCB were produced and tested. Of these only one had to be reworked because of errors during assembly. The others were integrated in the inner tracker without any substantial problem arising.

The Control Ring implementation is given in section 2.1, after which a short description of the ring basic components follows. In section 2.4 the protocol used is reviewed and in section 2.5, some technical details are given of the CCU that obeys that protocol.

Section 2.6 is then dedicated to the description of the Digital Opto-Hybrid Module (DOHM), its design constraints and requirements that had to be satisfied. In section 2.7 the problem of redundancy in a control ring and the DOHM capability of coping with single point failures is described.

Section 2.8 focuses on the production of the boards and on the acceptance tests. Qualification procedures are described and quantitative measurements of various signal waveforms are shown. Conclusions follow in the last section.

## 2 Control Ring Implementation

Fig 1: Signals involved in the Control System.

The communication between FEC and CCU uses a token-ring protocol, with the FEC connected to the first CCU in the ring, which in turn is connected to the second, and so on up to the last, which closes the ring towards the FEC. This kind of topology left two choices open for the implementation: one with CCU connected directly one to each other with cables going directly to and from the CCU, the second, with CCU connected to a single board, designed in such a way as to build a CCU ring. The second option was chosen, as it was simpler to implement, given that additional elements had to be introduced in the system, such as a broadcast reset, which was to be sent in parallel to all of the CCU. But most important it allowed the implementation of a secondary ring (see later on) for redundancy which would have been nearly impossible because of space constraints in the case of the first solution (the number of connectors on the Mother Cables would have doubled).

Both the output and the input of the FEC are optical, while the communication between CCU is electrical; for the signal conversion a specific hardware was supplied by the CMS collaboration: a Digital Opto-Hybrid (or

DOH), which has two outputs (lasers) and two inputs (photodiodes), which are used for data and clock output and input.

Before entering in the details of the DOHM project a brief account of the constraints placed on the design will be given along with a few reminders of the main building blocks, some of which have already been described in other CMS Notes.

#### 2.1 Framework

The communication between FEC and modules is implemented in a multiple layer structure, the topmost layer being the FEC, followed by DOH, CCU and eventually the devices placed on the detector modules. Each layer has a different signal transmission, as sketched in Fig. 1. Every device acting as a switch between a layer and the following one has to perform a signal conversion from a physical protocol to another.

For the optical communications a good reference is [2], while LVDS specifications for CMS Tracker are in [3] and the CCU ring protocol is in [4], which contains also details on the I2C implementation of the CCU. Standard I2C specifications are in [5].

| Optical connector<br>position | Signal type | DOH connectivity and<br>direction |  |  |

|-------------------------------|-------------|-----------------------------------|--|--|

| 1                             | CLOCK A out | FEC → DOH A                       |  |  |

| 2                             | DATA A out  | FEC → DOH A                       |  |  |

| 3                             | CLOCK B out | FEC $\rightarrow$ DOH B           |  |  |

| 4                             | DATA B out  | FEC $\rightarrow$ DOH B           |  |  |

| 5-8                           |             | NOT USED                          |  |  |

| 9                             | DATA B in   | FEC ← DOH B                       |  |  |

| 10                            | CLOCK B in  | FEC ← DOH B                       |  |  |

| 11                            | DATA A in   | FEC ← DOH A                       |  |  |

| 12                            | CLOCK A in  | FEC ← DOH A                       |  |  |

Table 1: FEC optical connector mapping.

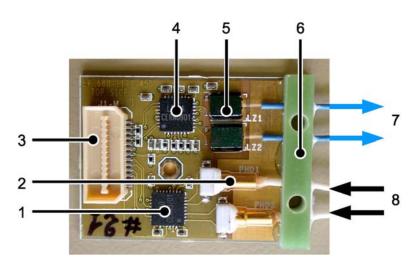

Fig 2: A Digital Opto-Hybrid: 1: RX40 ASIC. 2: Photodiodes. 3: NAiS 26-way Header connector. 4: LLD ASIC. 5: Lasers. 6: Fibre clamp. 7: Output clock and data. 8: Input clock and data.

## 2.2 The Front End Controller

The FEC is the Front End Control element for both the slow control link and the fast clock and trigger in the CMS tracker. It is implemented as a mezzanine module, i.e. a piggy-back board with a local bus interface. The mezzanine board can be plugged into different types of carrier board. For many test applications a PCI board is most suitable, for installation in the experiment a 9U VME board with eight FEC was produced.

A logic interface towards the controlling processor and a trigger encoder are implemented both on the PCI and the VME carrier boards. The trigger encoder takes the external clock and trigger signal as coded by the CMS Trigger System and generates the 40MHz clock for the token ring, inserting received trigger commands as missing ticks in the clock.

The whole chain of devices connected to the ring sees these missing pulses, but since the ring is a synchronous system, this is transparent to the ring devices themselves (namely DOH and CCU). Instead, devices not directly connected to the ring (such as detector modules) do need clock recovery, which is implemented through PLL devices.

As already briefly stated in the introduction, the ring connections must be redundant in such a way that a single component failure (i.e. a CCU belonging to a ring) will not jeopardize the whole ring and thus a fair sized partition of the tracker itself. For this reason the FEC has two double inputs and outputs for the clock and the data. The default ports are named A and the alternative ports are named B (see Table l); thus the FEC can be connected to two Digital Opto-Hybrids at the same time. The input and the output may be directed either to the primary DOH (A) or to the secondary one (B) and these can be used in any combination (for example input A and output B). The FEC transmits and receives over a ribbon of optical fibers, so that all of the eight lines can be connected at once.

#### 2.3 The Digital Opto Hybrid

Digital signals transmitted by FEC via optical links are converted into electrical signals by Digital Opto-Hybrids. The DOH is a compact radiation resistant transceiver assembly with two lasers and a laser driver ASIC (LLD [6,7]), and two photodiodes and a receiver ASIC (RX40 [8,9]), all mounted on a four layer hybrid (see Fig. 2). The RX40 implements an Automatic Gain Control Amplifier, which keeps a constant output signal irrespective of the input current emitted by photodiodes.

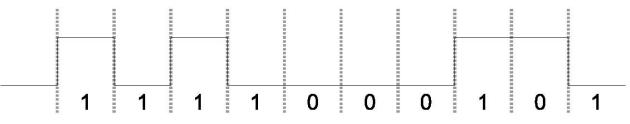

Fig 3: An example of NRZI encoded data.

The DOH footprint is 25x35 mm<sup>2</sup> and its height is five mm. The optical interface consists of four single-mode fibre pigtails with individual MU connectors. The two receiver channels on the DOH transmit the LHC 40 MHz clock (CLK) (as well as trigger and resynchronization signals) and control data (DATA) at 40 Mbits in the direction from the FEC to the ring of CCU over LVDS lines. The two transmitter channels send clock and data to the FEC from the ring of CCU.

The hard-reset for the front-end ASIC is also generated by the RX40 on the DOH, following reception of a reset request (a signal of at least 10 consecutive 0 levels on the DATA line) sent by the FEC over the DATA optical link channel. Whenever the reset is active, the LVDS block input is disconnected from the output of the limiting gain amplifier chain.

#### 2.4 The Communication Protocol

The architecture of a ring of CCU is functionally very similar to (and inspired from) the one used by commercial token ring networks (similar to the IBM Token Ring or FDDI). The ring consists basically of a number of node devices (the FEC and the embedded CCU), that are all capable of accepting and inserting data packets in the ring.

In this network implementation, to simplify the design of the CCU, the FEC node contains more complexity, such as the capability of directing the network traffic and of initializing and diagnosing the network. The basic token-ring message transmission protocol for the ring is based on the following mechanism:

- at start up the FEC starts circulating idle patterns in the ring;

- following initialization, the FEC inserts a special "token" data packet in the ring which starts circulating from node to node;

- all nodes not wanting to transmit will just forward the token to the next node;

- a node which wants to transmit information to another node waits for arrival of the network token; this node replaces the token with a data frame and retransmits it in the ring;

- all the nodes reached by the frame which are not the destination of the current frame just forward the frame;

- the destination node copies the passing frame, modifies just one symbol at the tail of the frame and forwards the rest of the frame to the network;

- the emitting node receives back its original frame with one symbol modified, removes it from the ring and regenerates an empty token.

Signals on the data line are sampled on the rising edge of the clock signal, using a NRZI encoding (Non Return to Zero with Invert 1 on change), where a 0 is represented by no change in leve1 and 1 is represented by change (see Fig. 3).

In addition, the data bits on the data line are transmitted using 4bit-to-5bit (4B/5B) encoding, chosen so as to reduce the probability of transmitting zeroes: the 4B/5B symbols used are such that there are never more than 3 consecutive zeros in the line, assuring an adequate number of line transitions, to avoid large DC shifts. The worst case DC unbalance deriving from the usage of this coding is estimated to be about 10%.

Another advantage of this coding is that it leaves free a set of symbols (sequence of bits) which do not encode any 4-bit-word and can be used as control symbols. Among these the most important is the idle symbol, defined as 11111. The idle symbol is always transmitted on the ring if there are no data packets, so as to vanish the DC shift at idle time. An unbalance in a fast transmission line is always undesirable, but all this care in reducing DC shifts brings also another benefit: the RX40 chip on DOH can assume that the average signal is halfway between high and low, in order to adjust its optical receiver's bias and amplification in real time, enhancing the robustness against changes in the optical gain of the transmission line.

To check the proper operation of the ring, a token packet is generated automatically by the FEC whenever the ring is initialized and travels around the ring. The above protocol assumes that an entire ring has only one circulating token or data packet at any one time. If the FEC has not seen a token or data frame during the timeout period (which is  $500 \ \mu$ s) it raises an alarm and creates a new token. The persistence of this alarm is an indication that the ring is not closed anymore.

## 2.5 The Communication Control Unit

More information about the CCU can be found in [4]. Here only the role of the CCU in the communication architecture is considered, with a few technical details.

The CCU are nodes of the token ring and receive instructions from the FEC either directed to themselves or to the I2C devices connected to them. The former case is used for example to read the status register of the CCU or to place data on its output lines. In the latter case, commands are translated to the I2C protocol and forwarded to the addressee; in case of a reply from the I2C device, the reverse process is done by the CCU, which addresses the packet(s) to the FEC.

The CCU device sits on a CCU-Module (or CCUM) which carries also a LVDS Mux, converting input LVDS signals to CMOS, readable by the CCU and vice-versa. Both CLK and DATA lines are converted and forwarded to the CCU, which generates the proper output packet synchronously with its output clock. CCU output clock and data are then translated back to LVDS by the same LVDS Mux device. This system guarantees the output frame to be in phase with the clock. CCU have also an external reset line to recover from possible protocol hangups.

To implement connection redundancy CCU have two inputs and two outputs: default and alternative. Upon power-up the default input and output are selected. To switch outputs from default to alternative a command is sent to the CCU node via token ring, changing the relevant bits in its command register. To switch the input a uniquely defined command must be sent through the same port one wants to activate. Any other command sent to a port which is not active is ignored.

## 2.6 The Digital Opto-Hybrid Module Requirements for TIB/TID

The DOHM board had to be assembled only with radiation-hard components, as any other component of the tracker. A very strict requirement was posed on the minimum temperature  $(-30^{\circ}C)$ , at which every component of the DOHM should operate. Different boards had to be implemented for the barrel layers (TIB) and for each of the three rings of detectors that compose a TID disk (R1, R2 and R3), because of different constraints in the

mechanical integration of the DOHM. Otherwise the electrical scheme solution is the same for barrel and disks. The DOHM has been first studied in INFN-Firenze, while the design, realization and test for the TIB and the TID implementations have been made respectively in INFN-Firenze and in INFN-Torino.

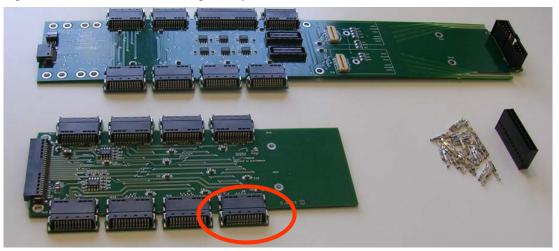

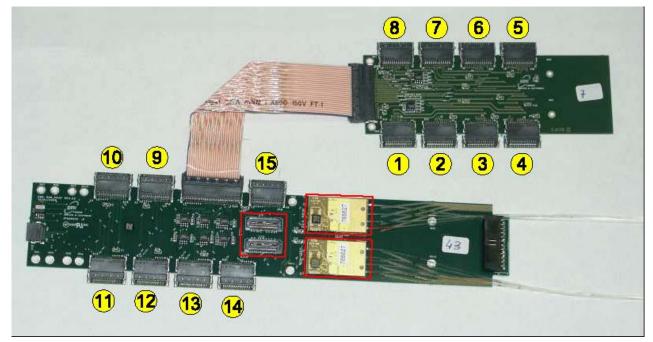

Fig 4: Two-board solution for variable TIB module grouping. The top board is the DOHM (up to seven CCU), the bottom board is a DOHM extender for rings with up to fifteen CCU. The red circle indicates one of the loop-back mini-boards. The Control Ring also needed redundancy control connections as described in the CCU specifications.

Fig 5: The three TID DOHM boards are shown respectively on top left, top right and on the bottom for R1, R2 and R3 TID Control Rings.

For TIB the Control Ring have different multiplicities depending on the layer, and can contain four, five, thirteen, fourteen or fifteen CCU. Thus a solution had to be found allowing the DOHM board to connect a variable number of CCU (see Fig. 4). The CCU are connected through flat cables to the DOHM; seven

connections are available on the main board and a further eight additional connections can be provided, when needed, by connecting an expansion board (named DOHM Extender) to a dedicated 40-pin ERNI connector.

The choice of producing a main board and an extender allowed to implement all the features on a single board and design a second, almost passive, board with lower costs and higher flexibility. This allowed also to reduce the amount of space taken up by the DOHM in all cases where only four or five CCU were needed for the ring.

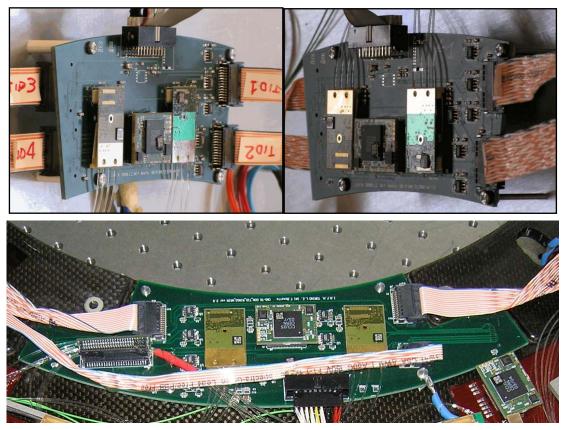

For the TID a Control Ring consists always of four CCU, therefore there was no need for an extension board, but dedicated DOHM boards with different form factors and orientation were needed for each TID ring in order to optimize the mechanical integration of the disks. Therefore there are three DOHM boards: R1, R2 and R3 types, see Fig.5.

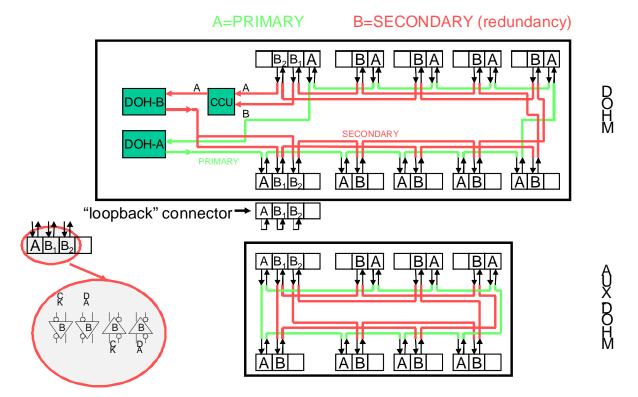

The diagram in Fig. 6 shows how the TIB DOHM implements the daisy chain topology needed to control all the CCU in each layer. Optical fibers from the FEC feed the DOH A primary and the DOH B secondary rings. Every "A-B" port sends data to and receives data from a CCU. "A" port is the primary one, while "B" port is the secondary one used for redundancy. Just before the first "A-B" ports there are LVDS buffers to drive the long connection between CCU (see details in red circles). If the required CCU in a ring are no more than seven no DOM-AUX-Extender is needed and a loop-back connector must be inserted. If the number of CCU is greater than seven, an extender board is required.

The primary ring connects CCU sequentially, while the two secondary rings skip one every two. In this way a failed "N" CCU can be removed from the ring using the previous "B" N-1 outputs. More details are given later in this section. The TID DOHM implementation for the redundancy follows the same topology restricted to four CCU.

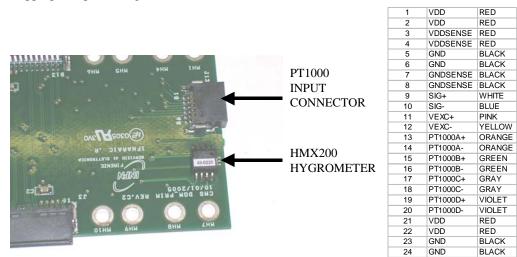

Lastly, temperature and humidity probes were deployed throughout the TIB/TID volume in a way that their readout would not be affected by possible ring failures and could even be performed with the ring not powered. These probes were wired through the DOHM so as to simplify the Tracker integration (Fig. 7). There are one humidity sensor placed on the board and two temperature probes (PT1000), with a four wire read out, coming from the TIB/TID volume with a specific connector on the DOHM for them. All these probes are directly connected to the pins of the DOHM power connector (Fig. 8).

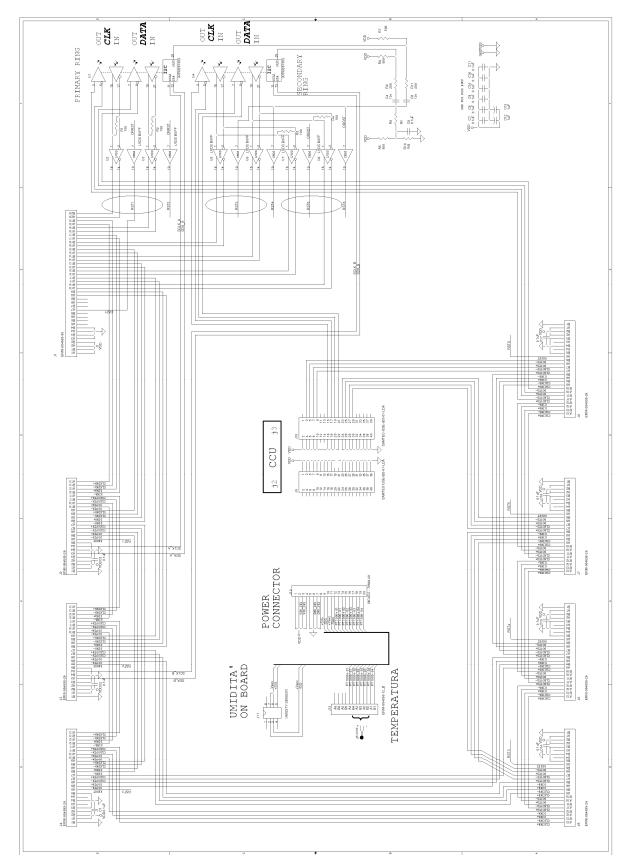

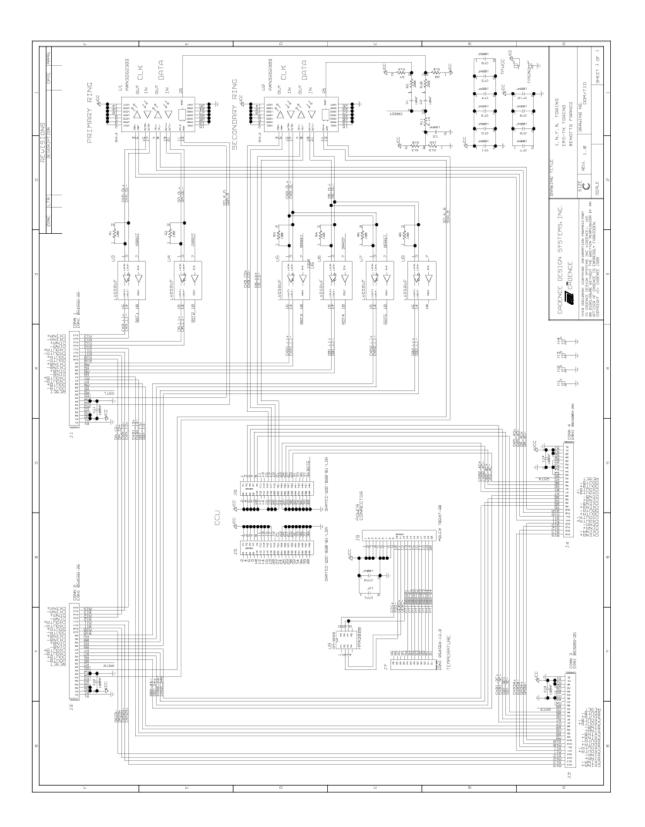

The full schematics for both the TIB and the TID DOHM boards are shown in Appendix A and B. In this last part of the section a bit more details on the board construction and usage are given.

Fig 6: Schematic view for the signal paths, with redundancy implemented via the red (secondary) paths.

All the needed hardware requires the same digital supply voltage (+2.5 V), so only two power planes were necessary: VDD and GND. Both TIB and TID DOHM are 6 layer printed circuit boards with the outermost layers used for the fast LVDS signals, the two innermost ones for the control signals and the two intermediate ones are continuous layers used for VDD and GND planes. Copper traces have been realized in 8 mils technology and the layout of the circuit has been designed with  $130\Omega$  impedance for the traces carrying the LVDS signals. The pin-out multiplicity on the power connector (Fig. 8) has been studied in order to have redundancy in case of possible single wire failures.

Control Rings are powered by dedicated power supplies, which have four independent 2.5 Volt sources per module. Each module has also a dedicated connector for the temperature and humidity sensors lines which are sent to the appropriate processing modules.

Fig. 7: On Board Sensor components

Fig. 8: DOHM Power Connector Pin-out

All CCU connectors carry primary and secondary LVDS clock and data, a broadcast reset line (ORRST) and power to the CCU. Only two CCU connectors out of 7 have additional I2C lines (J2 and J3 in the electrical scheme in Appendix A or #9 and #10 in Fig.9). These extra lines are used to control the DOH A and the DOH B nodes, for example to change the output laser driver's gain or bias (should this ever be called for). An additional CCU, needed to correctly implement the redundancy scheme, was added directly on the DOHM itself.

Fig. 9: A DOHM connected to its Extender. ERNI connectors for the CCU are numbered according to their order in the Control Ring. The socket for the dummy CCU and the two DOH are highlighted. The boards have loop-back connectors plugged in.

The connector for the Extender board brings both primary and secondary ring outputs directly from the DOH buffers. This means that if the Extender is present, a CCU connected to it will be ordered as first in the token ring. The output of the extender last CCU is then connected back to the next CCU on the main DOHM, thus closing that loop of the ring. If the Extender is not present, a loop-back connector replaces it, appropriately routing inputs to outputs so as to close the DOHM ring topology transparently. In this case, the first and second CCU in the ring are those connected to J2 and J3.

Another loop-back mini board can be connected to J2-J8 in place of a missing CCU. These are not completely transparent to the ring topology, as described in the following section.

#### 2.7 DOHM Redundancy Design

According to CCU specifications, the redundancy scheme for the CCU token ring foresees that the n-th CCU in the ring must have its default (A) output connected to the default (A) input of CCU # n+1 and its alternative (B) output connected to the alternative (B) input of CCU # n+2.

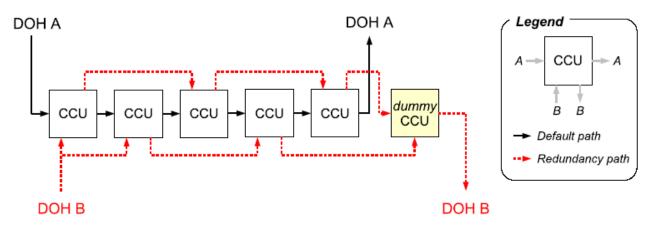

There are two obvious exceptions to this scheme: at the start and at the end of the ring, where CCU are connected to DOH. To connect the last and second last CCU B output, an additional CCU is needed with its default output connected to the B (redundant) DOH (while its B output is left unused). At the start of the ring, both the first and the second CCU receive B-DOH output at their B input. This is implemented in the DOHM by doubling the secondary DOH outputs with buffers. The resulting scheme is sketched in Fig. 10.

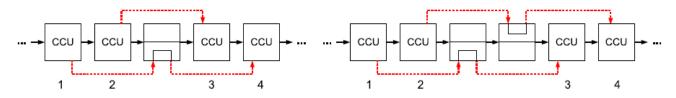

The TIB DOHM peculiarity is the variable number of loop-back connectors used in place of missing CCU: rings with four and five CCU will have three and two loop-back connectors respectively, while rings with thirteen, fourteen, and fifteen CCU will use the Extender board and have two, one or no loop-backs. Consider now the effect of a single loop-back connector (see Fig. 11). A loop-back connector connects an A input to its corresponding A output and a B input with its corresponding B output.

If one loop-back is inserted in the ring in place of a CCU, the right connection topology is broken: a CCU (the second ) will have both its A and B outputs connected to the following CCU (the third ) and another CCU (the first) will have its B output connected to a CCU further still away than the next one (the fourth). As a result, if CCU number two were to fail, reconfiguring the ring in order to exclude CCU number two would also exclude CCU number three, which is not acceptable.

Fig. 10: Default redundancy scheme

Fig. 11: Redundancy scheme as resulting from inserting one (left) or two (right) loop backs

However if two consecutive loop-back connectors are inserted in the ring, the correct topology is restored: as can be seen in the right part of the drawing in Fig.11, each n-th CCU has its B output connected to the B input of

CCU # n+2. Thus the first rule for loop-back connector insertion on the DOHM is: loop-back connectors must be inserted in pairs, into two adjacent slots.

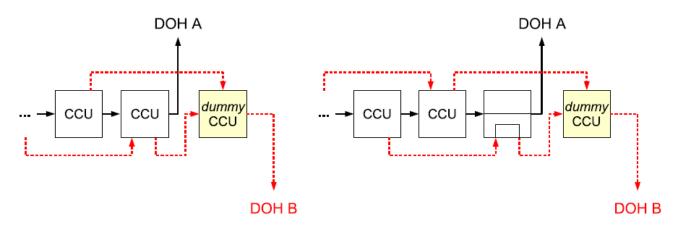

In case the total number of loop-back connectors needed is odd, the last one must be inserted in the slot next to the additional on board CCU (I.E. in the last slot of the DOHM). The ring topology changes somewhat, but the redundancy is kept, as sketched in Fig. 12.

In fact let us assume that the total number of CCU inserted is N. In the default scheme (left) the N-th CCU has its B output connected to the additional CCU A input and the (N-l)-th CCU B output is connected to the additional CCU B input. If a loop-back connector is inserted in the last position the connection order is reversed (N-th B to the additional CCU B and N-1 B to the additional CCU A), but all possible paths can still be obtained with a proper input output reconnection.

The FEC software needs to implement these two possible connection topologies for the additional CCU in a TIB/TID Control Ring, depending on the parity of the number of loop-back connectors.

Fig. 12: Redundancy scheme as resulting from inserting a loop-back in the last available slot.

Since the possible number of slots is either seven or fifteen the number of loop-back connectors is even if the number of CCU is odd and vice-versa. Thus the second rule in placing loop-back connectors in the ring is: if the number of loop-back connectors to be placed is odd, one of the loop-back connectors must be placed in the last slot of the ring and the remaining ones are to be placed according to the first rule (which makes them invisible to the ring topology).

A last rule stems from the DOH I2C nodes being driven only from the CCU connected to J2 and J3. Thus rule three states: no loop-back connector should be inserted into connectors J2 and J3.

These rules were used for TIB in assembling DOHMs in the final structure. The Tracker redundancy software implements the optimal algorithm to operate redundancy in the TIB. To simplify the FEC software, predefined addresses were given to the CCU according to the position along the ring, as detailed in Table 2.

Table 2: CCU address as a function of position in the ring. "Dummy" refers to the additional on board CCU. For TID only the first four addresses are used, plus the "dummy".

| 1    | 2    | 3    | 4    | 5    | 6    | 7    | 8     |

|------|------|------|------|------|------|------|-------|

| 0x77 | 0x7D | 0x7E | 0x3F | 0x5F | 0x6F | 0x7B | 0x73  |

| 9    | 10   | 11   | 12   | 13   | 14   | 15   | dummy |

| 0x79 | 0x7A | 0x3B | 0x5B | 0x6B | 0x67 | 0x6D | 0x7F  |

Redundancy control implies the need for two DOH on each DOHM. Normally only the primary DOH is used, but in case of a DOH or a CCU failure the secondary DOH can also transmit and receive data. It will be seen below how the redundancy between DOH is implemented in the TIB/TID DOHM, but for the moment notice that both DOH A and DOH B must be able to send a broadcast reset to the Control Ring.

This could have been implemented with a simple OR logic, but one of the most probable failures is due to the interruption of an optical line from the DOH to the FEC (optical fibres are very fragile). This condition results in an absence of light which is decoded by the DOH logic as a RESET signal (see above). Thus the RESET would be raised for an indefinite amount of time.

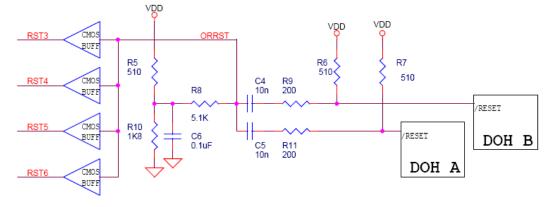

Fig. 13: Passive OR circuit

To avoid this problem, a couple of monostables can be inserted in these lines, but this solution is difficult to implement in radiation hard technology. Instead a simple circuit was used which implements a "passive OR" by joining the two RESET lines through capacitors and adding a pull-up on the output line (the RESET line follows inverted logic).

This ensures that the resulting ORRST signal is active for no more than 50  $\mu$ s, and that the circuit keeps functioning even in case of a shorted (or open circuited) DOH. The ORRST line carries an inverted CMOS signal and is buffered before being broadcast to all CCU (see detail in Fig.13).

## 2.8 DOHM Test and Quality Assurance

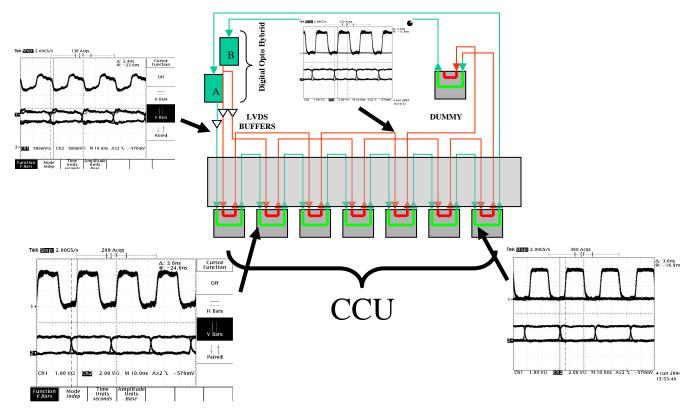

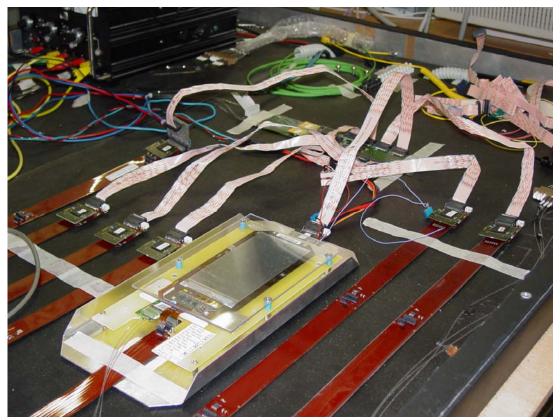

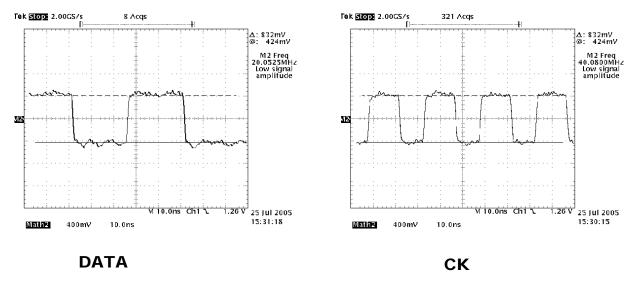

Test procedures for the quality assurance of the TIB/TID DOHM were defined and performed. The tests were of two kinds, electrical and functional. In Fig. 14 a simplified block diagram is shown of the main DOHM devices. Oscilloscope pictures show eye diagrams for Clock and Data signals at various PCB test points.

Fig. 14: Main signals of the DOHM

To screen out weak components all the boards were baked for 100 hours at 70 °C, after which they were cycled from  $-35^{\circ}$ C to  $+40^{\circ}$ C for 50 hours with a period of four hours. In order to test every DOHM produced, a test bench was set up (see Fig.15) with a PCI FEC and full complement of CCU. Electrical tests consisted in:

- 1) measuring the power supply decoupling capacitance;

- 2) measuring the supply voltages at different PCB test points;

- 3) measuring total current absorption;

- 4) verifying the signal integrity at every differential CCU Clock and Data input;

- 5) verifying the signal integrity of the Reset line for every CCU;

- 6) verifying the signal integrity of the I2C lines at the DOHA/B outputs;

- 7) testing the PT1000 temperature sensor connection through the board;

8) testing the relative humidity sensor connection with single arm resistance measurement (bridge configuration).

The display in Fig. 16 shows a test in the worst-case situation for signal integrity, with all loop-back connectors in place, so that the signal propagates across many discontinuities. The resulting zero-crossing point is still well defined and with clear transitions.

Fig. 15: Seven string test bench set-up.

For the functional tests a dedicated program was written to perform the following actions, in sequence:

- 1. Send a ring reset;

- 2. Scan the ring for all connected CCU, in order;

- 3. For every possible redundancy path with a single skipped element:

- (a) send a ring reset,

- (b) select the specific redundancy configuration by sending appropriate commands to the CCU,

- (c) list the CCU found in the ring after this has been reconfigured,

- (d) check the retrieved CCU configuration against the expected one.

Fig. 16: Differential signals in the ring.

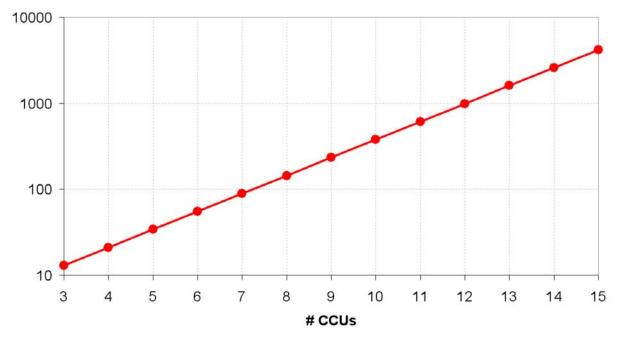

It was not possible to test all the possible redundancy paths, as their number grows exponentially with the number of CCU in a ring (see Fig, 17). A choice was made to anyway check all ring connections, by skipping each single element in the ring (including the DOH). This is enough to guarantee the correct functionality of the DOHM.

Fig. 17: Number of possible redundancy path as a function of the number of CCU in a ring.

Nearly two hundred DOHM were tested with this set-up both in Firenze and Torino and no failures were found. Once a DOHM passed the test a 2-D bar code was glued on it and its identity was stored in the construction database. At the beginning some problems were encountered when testing redundancy with fourteen and fifteen CCU in the ring. This turned out to be a problem related to the FEC firmware, which led to the development of an updated version of the firmware in collaboration with CERN FEC developers. As stated before, to ease the implementation of the redundancy software the CCU must have a fixed hardware address with respect to their geographical order in the ring. Thus a fixed set of addresses is always used for the CCU. In principle, the knowledge of the number of CCU in the ring, implies the knowledge of all their addresses (see Table 2). Of course this no longer holds once the ring has been reconfigured because of a device failure.

## **3** Conclusions

A dedicated PCB active carrier (DOHM) was designed, built and tested, for the distribution of clock and trigger signals in the Inner Tracker. The DOHM uses radiation hard electronics and implements resets and buffering for the various signals. This carrier board allows for Control Ring reconfiguration in case one of the modules on the ring is malfunctioning. Reconfiguration is performed via special command sequences sent to the CCU by the resident software on the FEC. Various possible single point failures were tested on the Control Ring structure implemented with the DOHM and in all instances the ring was successfully reconfigured. The DOHM carriers have undergone a series of tests both during production and later during assembly, including burn-in cycles. All DOHM have been found to be extremely reliable and once installed on the detector have performed as expected.

## References

[1] The Tracker Project Technical Design Report, CERN/LHCC 98-6; Addendum to the CMS Tracker TDR, CERN/LHCC 2000-016.

[2] J. Troska, G. Cervelli, E Faccio, K. Gill, R. Grabit, R. M. Jareno, A. M. Sandvik, and F. Vasey, Optical readout and control systems for the cms tracker, IEEE Trans. Nucl. Sci. 50, 1067 (2003).

[3] P. Moreira, Tech. Rep., CERN, EP division (1997), available at http://cms.trackercontrol.web.cern.ch/ CMSTrackerControl/manuals.htm.

[4] A. Marchioro. L. C., and P. C.. Tech. Rep., CERN, EP division (2002), available at http://cmstrackercontrol.web.cern.ch/CMSTrackerControl/manuals.htm.

[5] I2C Bus Specification, version 2.1, Philips Semiconductors (2000). document order number: 9398 393 40011.

[6] G. Cervelli. A. Marchioro. P. Moreira, and F. Vasey, A radiation tolerant laser driver array for optical transmission in the lhc experiments (2001), prepared for 7th Workshop on Electronics for LHC Experiments, Stockholm, Sweden, 10- 14 Sep 2001.

[7] G. Cervelli, P. Moreira, A. Marchioro, and E Vasey, Tech. Rep., CERN, EP division (2003), available at http://proj-lld.web.cern.ch/

[8] E Faccio, Moreira, A. Marchioro, and F. Vasey, Tech. Rep., CERN, EP division (2002).available at http://proj-rx40.web.cern.ch/proj%2Drx40/documents.htm.

[9] E Faccio, C. Azevedo, K. Gill, P. Moreira, A. Marchioro, and Vasey. F., Status of the 80Mbit/s receiver for the digital optical link (2000). prepared for 6th Workshop on Electronic for LHC Experiments, Cracow, Poland, 11-15 Sep 2000.

APPENDIX A