Particle Accelerators, 1990, Vol. 29, pp. 133–138

Reprints available directly from the publisher

Photocopying permitted by license only

© 1990 Gordon and Breach, Science Publishers, Inc. Printed in the United States of America

REPETITIVE VOLTAGE CONTROL OF THE MAIN RING MAGNET POWER SUPPLY FOR THE KEK 12 GEV PS.

T. SUENO, S. MATSUMOTO, K. MIKAWA, M. TODA, H. SATO, N. KUMAGAI and H. BABA National Laboratory for High Energy Physics, KEK, Tsukuba, Ibaraki. Japan

Abstract To improve to response and precision on a fine correction to the injection and or tracking level in a routine 0.4 Hz pulse operation, the main control cpu of the multimicrocomputer system has been exchanged to 32-bit cpu, MC-68020, with the coprocessor of floating calculation, MC-68881. As the results, the responses have been reduced to within 10s or less. Overhead of the floating calculation estimated at less than a second.

Because of light overhead of the main cpu, repetitive voltage control has been tried on a routine pulse operation of the power supply for the machine to suppress the steady lowest component of ripple, 50Hz. A preliminary result gives for the component to be decreased about a half level.

# INTRODUCTION

In operations of a big pulsed magnet power supply for the proton synchrotron (PS), it is important for steady parasitic ripple components of lower order harmonic voltages to be supressed into a desired level by appropriate devices, passive and or active filters. However, in general, these devices are expensive to be effective enough to the lower order ripples. If these ripples were cancelled out by direct computer control of thyristor converter, the initial cost of these filters would be within a reasonable level.

On the KEK-PS, we have tried for steady components of those ripples to be reduced in the applied voltages to the magnets by repetitive voltage control (VPC) algorithm, which is a kind of feed-forward control. The principle is based on the periodic or repetitive current control method (CPC)<sup>1,2</sup> for steady current deviations to a desired current pattern, except the frequency response. In the CPC, the frequency response of correcting transfer fuction have been confined in a lower frequency region, about 15Hz or less, to

assure the stability of the power system.

These steady ripples are generated by breaking symmetry among the ignition timing of SCR on multi-phase ac lines, by steady distortions of line voltage, or by noises including common mode.

On the 100Hz ripple of these residual ripple components, the main part has been derived by voltage imbalance of a single phase among three phases on the ac power line, but the major of the part has been cancelled out by the voltage imbalance control in the reactive power compensator, 16Mvar+4Mvar, of thyristor control reactor current type (TQC)<sup>3</sup>.

We aimed for the lowest order ripple, 50Hz, as the component to be reduced by the VPC.

## MAIN CPU SYSTEM

On the otherhand, the control computer system of multi-micro-cpu had carried out routine operation of the power supply by 600 Hz pattern data, since the January of 1987. The main cpu system had executed the desired tasks by a time sharing multi-task operating system, unix system III. However, a response of the system was rather slow even compared to the CPC loop, of which a comparatively slow response is allowable. A typical response on fine adjustments of tracking or injection for beam tuning was estimated at about 20s or 50s even after optimization to the control programs with a fixed point cal-Hardwares and softwares of the main cpu have been modifyed to improve on the response to a half or less, by reducing the overhead of floating point computation with double precision to hold the precision to the corrected data and by decreasing frequencies of the disk access on the fine adjustments, including data transfer between the main and the controller system linked in local area network with effective transfer rate, 20 kB/s.

## Hardware

On the hardware, the basic processing unit (BPU) have been replaced by a 32-bit cpu, MC-68020, with 20 MHz as the system clock and with the coprocessor(FPP), MC-68881, for a floating calculation on the local bus with 32-bit data bus, inspite of the system bus IEEE 796. The memory control unit has cash memories, 16kB, with no wait

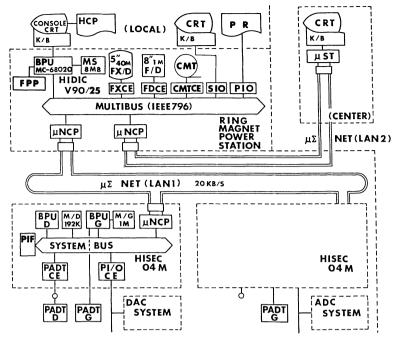

FIG. 1 Block diagram of the control computer system.

to the cpu clock on the internal bus. In order to reserve resident memory areas for the time sharing multi-task OS, the physical memory space has been extended up to 8MB composed of 1Mbit DRAM IC. And the hard disk up to 40MB, because of big system and application soft and of their working and data space. Moreover, casset MT of 20MB has backed up the disk. Fig. 1 gives a block diagram of the system.

#### Software

On the system software, upper version of the unix, system V, has served resident data memory area as the common memory to decrease the disk access for calculation of these corrected pattern data on the fine adjustments to injection or tracking. The main application programs by the language f77 are reinstalled by "fort" as an optimized high speed version of extended f77 released on the unix V. Another bottle neck was large volume of pattern data in data transfer of the LAN among the controllers. The neck has been amended by partial data transfer of modified pattern data and by an optimization of the procedure.

As the results, the overall response of fine adjustments are

within 10s or less. On major part of the response, the system works for data transfer, but negligibly small for the floating calcuration. The response of CPC is improved from 180s to 45s. The modified system has followed up as the main control computer since the last of 1987.

## CONTROL ALGORITHM

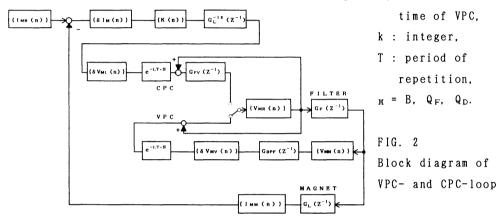

These improvements to processing capacity of the cpu system have been enable for the system to execute the VPC. In Fig. 2,  $L_T$ =kT : dead

The algorithm is equivalent to the one of CPC. Fig. 2 shows the VPC-loop in the CPC scheme. The transfer function(TF) of VPC,  $G_{\mathrm{BPF}}(z^{-1})$ , is finite impulse response (FIR) type with optimum taps  $G_{\mathrm{F}}(z^{-1})$  means the TF of thyrister converter and filter system.  $G_{\mathrm{L}}(z^{-1})$  the TF of the magnet system.  $\{V_{\mathrm{MM}}(n)\}$ ,  $\{\delta V_{\mathrm{MV}}(n)\}$  and  $\{V_{\mathrm{MR}}(n)\}$  are data series of measured magnet voltage, ripple component and reference voltage pattern respectively.

In order to avoid interference to the CPC, a trial VPC transfer fuction has a narrow band pass type. The center frequency is possible to chosed a suitable between the fudamental, 50Hz, and the Nyquist rate, 300Hz. The stability of these system is depend on the stability of the CPC and of the load. But, if the load without these loops is stable, the whole system with the loops is stable. The proof will be described in somewhere.

#### RESULTS

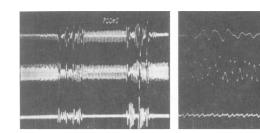

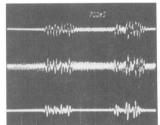

Top:  $\triangle I_{QF}(75^{MA}/DIV)$ , Center:  $\triangle I_{QD}(75^{MA}/DIV)$ , Bottom:  $\triangle I_{B}(150^{MA}/DIV)$ PHOTO 1. Ripple currents before VPC on 3.5GeV pulse operation.

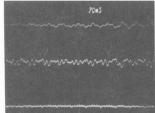

Top:  $\triangle I_{AF}(75^{MA}/D_{IV})$ , Center:  $\triangle I_{AD}(75^{MA}/D_{IV})$ , Bottom:  $\triangle I_{B}(150^{MA}/D_{IV})$ PHOTO 2. Ripple currents after VPC on 3.5GeV pulse operation.

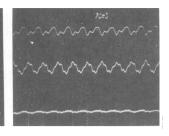

BEFORE VPC

AFTER VPC & DF ON

AFTER VPC & DF OFF

EJEC

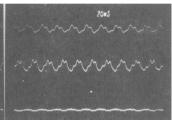

Top:  $\triangle I_{QF}(75^{MA}/_{DIV})$ , Center:  $\triangle I_{QD}(75^{MA}/_{DIV})$ , Bottom:  $\triangle I_{B}(150^{MA}/_{DIV})$ PHOTO 3. Ripple currents on 12GeV pulse operation.

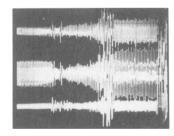

$\triangle I_{AF}$  (75 MA/DIV)

$\triangle I_{AD} (75^{MA}/_{DIV})$

$\triangle I_B$  (150 MA/DIV)

PHOTO 4. Injection ripple currents after VPC on 12GeV pulse operation.

For a preliminary test,  $[1-G_{MA}(z^{-1})]$  has been tried as the TF of the VPC, where  $G_{MA}(z^{-1})$  is a simple rectangular window with appropriate taps up to 15. This is rather crude, but useful.

In PHOTO 1 and 2, ripple currents by ripple current transformer (RCT) are given on a 3.5GeV pulse operation without active or dynamic filters. The reference pattern on PHOTO 1 has been corrected by the CPC, but not corrected by the VPC. The pattern on PHOTO 2 has been corrected to the one of the PHOTO 1 by the VPC. PHOTO 3 shows typical ripple currents from injection start to reset start timing (R) on a routine 12GeV pulse operation by correction mode of the CPC, of the VPC and of the dynamic filter. The dynamic filters work only on the flat tops of  $Q_{\rm F}$  and  $Q_{\rm D}$  for the sake of underdamping oscillation triggered by external disturbances and narrow dynamic range. PHOTO 4 gives injection ripple currents on the 12GeV operation by the VPC without dynamic filter.

Ripple currents are reduced in overall to a half level or less. That is, on the fundamental component, 50 Hz, the ripple would be suppressed down to  $10_{mA}$  level at injection, but the third,  $150\,\mathrm{Hz}$ , or other components in near region of 50Hz rather would increased. These components could not correct by the CPC, because of the ripple buried in the modulation noises of DCCT, if the frequency response had sufficiently wide region up to lower order harmonics. Another main source of the third is the TQC. In any case, it is necessary for the third to be reduced to a desired level. Though there were some other defects, these could be overcome by a more sophisticated TF of the VPC.

## REFERENCE

- S. Matsumoto, T. Sueno, K. Mikawa, M. Toda and H. Baba, Proc. 1987 IEEE Particle Accelerator Conf., March 16-19, 1987, Washington, D. C., pp. 689-691 (1987).

- T. Inoue, M. Nakano, T. Kubo, S. Matsumoto and H. Baba, in <u>Control Science and Technology for the Progress of Society</u>, edited by H. Akashi (Pergamon Press, London, 1981), vol. 6, pp. 3137-3142.

- 3. S. Matsumoto, H. Baba, H Sato, T. Sueno and K Mikawa, IEEE Trans. Nucl. Sci. NS-30 (1983) No. 4, 2932-2934.