## **Algorithms Incorporating Concurrency and Caching**

by

Jeremy T. Fineman

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

at the

## MASSACHUSETTS INSTITUTE OF TECHNOLOGY

September 2009

© Massachusetts Institute of Technology 2009. All rights reserved.

Λ

Author ...... Department of Electrical Engine ring and Computer Science September 4, 2009

Certified by ..... Charles E. Leiserson Professor Thesis Supervisor

Accepted by ..... Professor Terry P. Orlando Chairman, Department Committee on Graduate Students Electrical Engineering and Computer Science

| MASSACHUSETTS INSTITUT | í |

|------------------------|---|

| OF TECHNOLOGY          |   |

|                        |   |

ARCHIVES

SEP 3 0 2009

.

•

**Algorithms Incorporating Concurrency and Caching**

by Jeremy T. Fineman

Submitted to the Department of Electrical Engineering and Computer Science on September 4, 2009, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

#### Abstract

This thesis describes provably good algorithms for modern large-scale computer systems, including today's multicores. Designing efficient algorithms for these systems involves overcoming many challenges, including concurrency (dealing with parallel accesses to the same data) and caching (achieving good memory performance.)

This thesis includes two parallel algorithms that focus on testing for atomicity violations in a parallel fork-join program. These algorithms augment a parallel program with a data structure that answers queries about the program's structure, on the fly. Specifically, one data structure, called **SP-ordered-bags**, maintains the series-parallel relationships among threads, which is vital for uncovering race conditions (bugs) in the program. Another data structure, called **XConflict**, aids in detecting conflicts in a transactional-memory system with nested parallel transactions. For a program with work  $T_1$  and span  $T_{\infty}$ , maintaining either data structure adds an overhead of  $PT_{\infty}$  to the running time of the parallel program when executed on P processors using an efficient scheduler, yielding a total runtime of  $O(T_1/P + PT_{\infty})$ . For each of these data structures, queries can be answered in O(1) time.

This thesis also introduces the *compressed sparse rows (CSB)* storage format for sparse matrices, which allows both Ax and  $A^Tx$  to be computed efficiently in parallel, where A is an  $n \times n$  sparse matrix with  $nnz \ge n$  nonzeros and x is a dense *n*-vector. The parallel multiplication algorithm uses  $\Theta(nnz)$  work and  $\Theta(\sqrt{n}/\log n)$  span, yielding a parallelism of  $\Theta(nnz/\sqrt{n}\log n)$ , which is amply high for virtually any large matrix.

Also addressing concurrency, this thesis considers two scheduling problems. The first scheduling problem, motivated by transactional memory, considers randomized backoff when jobs have different lengths. I give an analysis showing that binary exponential backoff achieves makespan  $V2^{\Theta(\sqrt{\log n})}$  with high probability, where V is the total length of all n contending jobs. This bound is significantly larger than when jobs are all the same size. A variant of exponential backoff, however, achieves makespan of  $O(V \log V)$  with high probability. I also present the *size-hashed backoff* protocol, specifically designed for jobs having different lengths, that achieves makespan  $O(V \log^3 \log V)$  with high probability.

The second scheduling problem considers scheduling n unit-length jobs on m unrelated machines, where each job may fail probabilistically. Specifically, an input consists of a set of n jobs, a directed acyclic graph G describing the precedence constraints among jobs, and a failure probability  $q_{ij}$  for each job j and machine i. The goal is to find a schedule that minimizes the expected makespan. I give an  $O(\log \log(\min \{m, n\}))$ -approximation for the case of independent jobs (when there are no precedence constraints) and an  $O(\log(n + m) \log \log(\min \{m, n\}))$ -approximation algorithm when precedence constraints form disjoint chains. This chain algorithm can be extended into one that supports precedence constraints that are trees, which worsens the approximation by another  $\log(n)$  factor. To address caching, this thesis includes several new variants of cache-oblivious dynamic dictionaries. A cache-oblivious dictionary fills the same niche as a classic B-tree, but it does so without tuning for particular memory parameters. Thus, cache-oblivious dictionaries optimize for all levels of a multilevel hierarchy and are more portable than traditional B-trees. I describe how to add concurrency to several previously existing cache-oblivious dictionaries. I also describe two new data structures that achieve significantly cheaper insertions with a small overhead on searches. The *cache-oblivious lookahead array (COLA)* supports insertions/deletions and searches in  $O((1/B) \log N)$  and  $O(\log N)$  memory transfers, respectively, where B is the block size, M is the memory size, and N is the number of elements in the data structure. The *xDict* supports these operations in  $O((1/\varepsilon B^{1-\varepsilon}) \log_B(N/M))$  and  $O((1/\varepsilon) \log_B(N/M))$  memory transfers, respectively, where  $0 < \varepsilon < 1$  is a tunable parameter.

Also on caching, this thesis answers the question: what is the worst possible page-replacement strategy? The goal of this whimsical chapter is to devise an online strategy that achieves the highest possible fraction of page faults / cache misses as compared to the worst offline strategy. I show that there is no deterministic strategy that is competitive with the worst offline. I also give a randomized strategy based on the most recently used heuristic and show that it is the worst possible page-replacement policy. On a more serious note, I also show that direct mapping is, in some sense, a worst possible page-replacement policy.

Finally, this thesis includes a new algorithm, following a new approach, for the problem of maintaining a topological ordering of a dag as edges are dynamically inserted. The main result included here is an  $O(n^2 \log n)$  algorithm for maintaining a topological ordering in the presence of up to  $m \leq n(n-1)/2$  edge insertions. In contrast, the previously best algorithm has a total running time of  $O(\min\{m^{3/2}, n^{5/2}\})$ . Although these algorithms are not parallel and do not exhibit particularly good locality, some of the data structural techniques employed in my solution are similar to others in this thesis.

Thesis Supervisor: Charles E. Leiserson Title: Professor

#### Acknowledgments

I would first like to thank Charles E. Leiserson, my advisor. When Charles announced to my entire group that I would be graduating this year, that was the first I had heard of it. At that point, I thought he had tired of having me around. Now that we're nearing the end, however, and Charles is requesting changes to this document, I realize that he must still want me around. In all seriousness, though, I would like to thank Charles for putting up with me for all these years and for providing guidance in both research and my career. And for putting his signature on the cover sheet.

I would like to thank all of my collaborators, including Kunal Agrawal, Michael A. Bender, Gerth Stølting Brodal, Aydın Buluç, Martin Farach-Colton, Christopher Y. Crutchfield, Erik D. Demaine, Zoran Dzunic, Yonatan Fogel, Matteo Frigo, John R. Gilbert, Seth Gilbert, John Iacono, David R. Karger, Bradley C. Kuszmaul, Stefan Langerman, Charles E. Leiserson, J. Ian Munro, Jelani Nelson, Jacob H. Scott, Jim Sukha, and Robert E. Tarjan. They were invaluable in developing the solutions described later in this thesis.

Michael deserves particular attention and gratitude. He worked with me on a large fraction of the research that went into this thesis, and he has been a good friend and mentor throughout.

I would also like to thank all the other members of the SuperTech group not already mentioned, including Angelina Lee and Edya Ladan Mozes, as well as the members of the theory group. I would also like to thank all my friends for contributing to many dinner parties, dessert parties, game nights, and other activities that kept me sane.

I extend particular gratitude to the delicious pig who became the pulled pork that got cooked in the pot that burned me. Were it not for you, pig, I would not have had those wonderful blisters on my fingers for a few weeks of peak thesis-typing time.

Last but not least, I would like to thank Artessa for doing her best to curtail my thesis efforts. Without her, perhaps I would have finished months earlier.

This work was supported in part by NSF Grants ACI-0324974, CCF-0541209, CCF-0621511, CNS-0305606, CNS-0540248, CNS-0615215, CSR-AES 0615215, OCI-0324974, the Singapore MIT Alliance, Google Inc., and the Intel Corporation. Any opinions, findings, conclusions or recommendations expressed in this thesis are those of the author and do not necessarily reflect the views of these funding organizations.

vi

# Contents

| 1 | Intro | oduction                                    | 1  |

|---|-------|---------------------------------------------|----|

| 2 | Serie | es-Parallel Maintenance                     | 9  |

|   | 2.1   | The SP-order algorithm                      | 13 |

|   | 2.2   | The SP-fast-bags algorithm                  | 18 |

|   | 2.3   | A model of parallel programs                | 23 |

|   | 2.4   | The SP-ordered-bags algorithm               | 25 |

|   | 2.5   | The global tier of SP-ordered-bags          | 29 |

|   | 2.6   | The local tier of SP-ordered-bags           | 30 |

|   | 2.7   | Correctness of SP-ordered-bags              | 33 |

|   | 2.8   | Performance analysis                        | 38 |

|   | 2.9   | Related work on SP-maintenance              | 41 |

|   | 2.10  | Concluding remarks                          | 42 |

|   |       |                                             |    |

| 3 | Nest  | ed Parallelism in Transactional Memory      | 43 |

|   | 3.1   | CWSTM framework                             | 46 |

|   | 3.2   | CWSTM semantics                             | 47 |

|   | 3.3   | A naive TM                                  | 50 |

|   | 3.4   | CWSTM overview                              | 51 |

|   | 3.5   | CWSTM conflict detection                    | 53 |

|   | 3.6   | Trace maintenance                           | 60 |

|   | 3.7   | Highest active transaction                  | 61 |

|   | 3.8   | Supertraces                                 | 62 |

|   | 3.9   | Ancestor queries                            | 63 |

|   |       | Performance claims                          | 65 |

|   | 3.11  | Concluding remarks                          | 66 |

| 4 | Sche  | duling Under Uncertainty                    | 69 |

|   | 4.1   | Preliminaries                               | 71 |

|   | 4.2   | Independent jobs                            | 74 |

|   | 4.3   | Jobs with chain-like precedence constraints | 80 |

|   | 4.4   | Jobs with tree-like precedence constraints  | 85 |

|   | 4.5   | Stochastic scheduling                       | 85 |

|   | 4.6   | Concluding remarks                          | 86 |

| 5  | Con                                                                                                                                                                                                        | tention Resolution with Heterogeneous Job Sizes                                                                                                                                                                                                                                                                                                                                                                                                                    | 89                                                                                                                                       |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

|    | 5.1                                                                                                                                                                                                        | Traditional backoff with variable-sized jobs                                                                                                                                                                                                                                                                                                                                                                                                                       | 91                                                                                                                                       |

|    | 5.2                                                                                                                                                                                                        | Size-hashed backoff                                                                                                                                                                                                                                                                                                                                                                                                                                                | 94                                                                                                                                       |

|    | 5.3                                                                                                                                                                                                        | Concluding remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 101                                                                                                                                      |

| 6  | Para                                                                                                                                                                                                       | allel Sparse Matrix-Vector and Matrix-Transpose-Vector Multiplication Using Co                                                                                                                                                                                                                                                                                                                                                                                     | n-                                                                                                                                       |

|    |                                                                                                                                                                                                            | sed Sparse Blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 103                                                                                                                                      |

|    | 6.1                                                                                                                                                                                                        | Conventional storage formats                                                                                                                                                                                                                                                                                                                                                                                                                                       | 105                                                                                                                                      |

|    | 6.2                                                                                                                                                                                                        | The CSB storage format                                                                                                                                                                                                                                                                                                                                                                                                                                             | 107                                                                                                                                      |

|    | 6.3                                                                                                                                                                                                        | Matrix-vector multiplication using CSB                                                                                                                                                                                                                                                                                                                                                                                                                             | 109                                                                                                                                      |

|    | 6.4                                                                                                                                                                                                        | Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 113                                                                                                                                      |

|    | 6.5                                                                                                                                                                                                        | Experimental design                                                                                                                                                                                                                                                                                                                                                                                                                                                | 115                                                                                                                                      |

|    | 6.6                                                                                                                                                                                                        | Experimental results                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                          |

|    | 6.7                                                                                                                                                                                                        | CSB Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 122                                                                                                                                      |

| 7  | Inte                                                                                                                                                                                                       | oduction to Cache-Oblivious Dictionaries                                                                                                                                                                                                                                                                                                                                                                                                                           | 127                                                                                                                                      |

| /  | 7.1                                                                                                                                                                                                        | Previous cache-oblivious dictionaries                                                                                                                                                                                                                                                                                                                                                                                                                              | 127                                                                                                                                      |

|    | /.1                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 127                                                                                                                                      |

| 8  | Con                                                                                                                                                                                                        | current Cache-Oblivious B-Trees                                                                                                                                                                                                                                                                                                                                                                                                                                    | 131                                                                                                                                      |

|    | 8.1                                                                                                                                                                                                        | The concurrent-cache model                                                                                                                                                                                                                                                                                                                                                                                                                                         | 132                                                                                                                                      |

|    | 8.2                                                                                                                                                                                                        | Exponential CO B-tree                                                                                                                                                                                                                                                                                                                                                                                                                                              | 133                                                                                                                                      |

|    | 8.3                                                                                                                                                                                                        | Packed-memory CO B-tree                                                                                                                                                                                                                                                                                                                                                                                                                                            | 137                                                                                                                                      |

|    | 8.4                                                                                                                                                                                                        | Lock-free CO B-tree                                                                                                                                                                                                                                                                                                                                                                                                                                                | 143                                                                                                                                      |

|    | 8.5                                                                                                                                                                                                        | Concurrent CO B-tree discussion                                                                                                                                                                                                                                                                                                                                                                                                                                    | 146                                                                                                                                      |

|    |                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                          |

| 0  | The                                                                                                                                                                                                        | Lookahead Array: A Cache-Oblivious Dictionary With Faster Insertions                                                                                                                                                                                                                                                                                                                                                                                               | 147                                                                                                                                      |

| 9  |                                                                                                                                                                                                            | Lookahead Array: A Cache-Oblivious Dictionary With Faster Insertions                                                                                                                                                                                                                                                                                                                                                                                               | <b>147</b><br>148                                                                                                                        |

| 9  | 9.1                                                                                                                                                                                                        | Cache-oblivious lookahead array (COLA)                                                                                                                                                                                                                                                                                                                                                                                                                             | 148                                                                                                                                      |

| 9  |                                                                                                                                                                                                            | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                          |

|    | 9.1<br>9.2<br><b>The</b>                                                                                                                                                                                   | Cache-oblivious lookahead array (COLA)                                                                                                                                                                                                                                                                                                                                                                                                                             | 148<br>153<br><b>157</b>                                                                                                                 |

|    | <ul><li>9.1</li><li>9.2</li><li>The</li><li>10.1</li></ul>                                                                                                                                                 | Cache-oblivious lookahead array (COLA)       COLA:         COLA: experimental results                                                                                                                                                                                                                                                                                                                                                                              | 148<br>153<br><b>157</b><br>157                                                                                                          |

|    | <ul><li>9.1</li><li>9.2</li><li>The</li><li>10.1</li><li>10.2</li></ul>                                                                                                                                    | Cache-oblivious lookahead array (COLA)                                                                                                                                                                                                                                                                                                                                                                                                                             | 148<br>153<br><b>157</b><br>157<br>160                                                                                                   |

|    | <ul> <li>9.1</li> <li>9.2</li> <li><b>The</b></li> <li>10.1</li> <li>10.2</li> <li>10.3</li> </ul>                                                                                                         | Cache-oblivious lookahead array (COLA)                                                                                                                                                                                                                                                                                                                                                                                                                             | 148<br>153<br><b>157</b><br>157<br>160<br>160                                                                                            |

|    | <ul> <li>9.1</li> <li>9.2</li> <li><b>The</b></li> <li>10.1</li> <li>10.2</li> <li>10.3</li> <li>10.4</li> </ul>                                                                                           | Cache-oblivious lookahead array (COLA)                                                                                                                                                                                                                                                                                                                                                                                                                             | 148<br>153<br><b>157</b><br>157<br>160<br>160<br>165                                                                                     |

|    | <ul> <li>9.1</li> <li>9.2</li> <li><b>The</b></li> <li>10.1</li> <li>10.2</li> <li>10.3</li> <li>10.4</li> </ul>                                                                                           | Cache-oblivious lookahead array (COLA)                                                                                                                                                                                                                                                                                                                                                                                                                             | 148<br>153<br><b>157</b><br>157<br>160<br>160                                                                                            |

| 10 | <ul> <li>9.1</li> <li>9.2</li> <li><b>The</b></li> <li>10.1</li> <li>10.2</li> <li>10.3</li> <li>10.4</li> <li>10.5</li> </ul>                                                                             | Cache-oblivious lookahead array (COLA)                                                                                                                                                                                                                                                                                                                                                                                                                             | 148<br>153<br><b>157</b><br>157<br>160<br>160<br>165                                                                                     |

| 10 | <ul> <li>9.1</li> <li>9.2</li> <li><b>The</b></li> <li>10.1</li> <li>10.2</li> <li>10.3</li> <li>10.4</li> <li>10.5</li> <li><b>The</b></li> </ul>                                                         | Cache-oblivious lookahead array (COLA)                                                                                                                                                                                                                                                                                                                                                                                                                             | 148<br>153<br><b>157</b><br>157<br>160<br>160<br>165<br>166                                                                              |

| 10 | <ul> <li>9.1</li> <li>9.2</li> <li><b>The</b></li> <li>10.1</li> <li>10.2</li> <li>10.3</li> <li>10.4</li> <li>10.5</li> <li><b>The</b></li> <li>11.1</li> </ul>                                           | Cache-oblivious lookahead array (COLA)       COLA: experimental results <b>xDict:</b> A CO B-Tree With Optimal Update/Query Tradeoff         Introducing the x-box       Sizing an x-box         Sizing an x-box       Sizing an x-box         Building a dictionary out of x-boxes       Sizing an x-box         Worst Page-Replacement Policy         Lower bounds                                                                                               | 148<br>153<br><b>157</b><br>157<br>160<br>160<br>165<br>166<br><b>167</b>                                                                |

| 10 | <ul> <li>9.1</li> <li>9.2</li> <li><b>The</b></li> <li>10.1</li> <li>10.2</li> <li>10.3</li> <li>10.4</li> <li>10.5</li> <li><b>The</b></li> <li>11.1</li> <li>11.2</li> </ul>                             | Cache-oblivious lookahead array (COLA)                                                                                                                                                                                                                                                                                                                                                                                                                             | 148<br>153<br><b>157</b><br>157<br>160<br>160<br>165<br>166<br><b>167</b><br>169<br>170                                                  |

| 10 | <ul> <li>9.1</li> <li>9.2</li> <li><b>The</b></li> <li>10.1</li> <li>10.2</li> <li>10.3</li> <li>10.4</li> <li>10.5</li> <li><b>The</b></li> <li>11.1</li> <li>11.2</li> <li>11.3</li> </ul>               | Cache-oblivious lookahead array (COLA)                                                                                                                                                                                                                                                                                                                                                                                                                             | 148<br>153<br><b>157</b><br>157<br>160<br>160<br>165<br>166<br><b>167</b><br>169<br>170<br>173                                           |

| 10 | <ul> <li>9.1</li> <li>9.2</li> <li><b>The</b></li> <li>10.1</li> <li>10.2</li> <li>10.3</li> <li>10.4</li> <li>10.5</li> <li><b>The</b></li> <li>11.1</li> <li>11.2</li> <li>11.3</li> <li>11.4</li> </ul> | Cache-oblivious lookahead array (COLA)       COLA: experimental results         xDict: A CO B-Tree With Optimal Update/Query Tradeoff         Introducing the x-box         Sizing an x-box         Operating an x-box         Building a dictionary out of x-boxes         Final notes         Worst Page-Replacement Policy         Lower bounds         Most-recently used         Direct mapping         Concluding remarks                                    | 148<br>153<br><b>157</b><br>160<br>160<br>165<br>166<br><b>167</b><br>169<br>170<br>173<br>174                                           |

| 10 | 9.1<br>9.2<br><b>The</b><br>10.1<br>10.2<br>10.3<br>10.4<br>10.5<br><b>The</b><br>11.1<br>11.2<br>11.3<br>11.4<br><b>Lnc</b>                                                                               | Cache-oblivious lookahead array (COLA)                                                                                                                                                                                                                                                                                                                                                                                                                             | 148<br>153<br>157<br>157<br>160<br>160<br>165<br>166<br>167<br>169<br>170<br>173<br>174<br>175                                           |

| 10 | 9.1<br>9.2<br><b>The</b><br>10.1<br>10.2<br>10.3<br>10.4<br>10.5<br><b>The</b><br>11.1<br>11.2<br>11.3<br>11.4<br><b>Incr</b><br>12.1                                                                      | Cache-oblivious lookahead array (COLA)         COLA: experimental results         xDict: A CO B-Tree With Optimal Update/Query Tradeoff         Introducing the x-box         Sizing an x-box         Operating an x-box         Building a dictionary out of x-boxes         Final notes         Worst Page-Replacement Policy         Lower bounds         Direct mapping         Concluding remarks         Concluding remarks                                  | 148<br>153<br>157<br>157<br>160<br>160<br>165<br>166<br>167<br>169<br>170<br>173<br>174<br>175<br>177                                    |

| 10 | 9.1<br>9.2<br><b>The</b><br>10.1<br>10.2<br>10.3<br>10.4<br>10.5<br><b>The</b><br>11.1<br>11.2<br>11.3<br>11.4<br><b>Incr</b><br>12.1<br>12.2                                                              | Cache-oblivious lookahead array (COLA)         COLA: experimental results         xDict: A CO B-Tree With Optimal Update/Query Tradeoff         Introducing the x-box         Sizing an x-box         Operating an x-box         Building a dictionary out of x-boxes         Final notes         Worst Page-Replacement Policy         Lower bounds         Direct mapping         Concluding remarks         Pageire Strategy         Algorithm for dense graphs | 148<br>153<br>157<br>157<br>160<br>160<br>165<br>166<br>165<br>166<br>167<br>169<br>170<br>173<br>174<br>175<br>177                      |

| 10 | 9.1<br>9.2<br><b>The</b><br>10.1<br>10.2<br>10.3<br>10.4<br>10.5<br><b>The</b><br>11.1<br>11.2<br>11.3<br>11.4<br><b>Incr</b><br>12.1<br>12.2<br>12.3                                                      | Cache-oblivious lookahead array (COLA)                                                                                                                                                                                                                                                                                                                                                                                                                             | 148<br>153<br>157<br>157<br>160<br>160<br>165<br>166<br>165<br>166<br>167<br>169<br>170<br>173<br>174<br><b>175</b><br>177<br>178<br>182 |

| 10 | 9.1<br>9.2<br><b>The</b><br>10.1<br>10.2<br>10.3<br>10.4<br>10.5<br><b>The</b><br>11.1<br>11.2<br>11.3<br>11.4<br><b>Incr</b><br>12.1<br>12.2<br>12.3                                                      | Cache-oblivious lookahead array (COLA)         COLA: experimental results         xDict: A CO B-Tree With Optimal Update/Query Tradeoff         Introducing the x-box         Sizing an x-box         Operating an x-box         Building a dictionary out of x-boxes         Final notes         Worst Page-Replacement Policy         Lower bounds         Direct mapping         Concluding remarks         Pageire Strategy         Algorithm for dense graphs | 148<br>153<br>157<br>157<br>160<br>160<br>165<br>166<br>165<br>166<br>167<br>169<br>170<br>173<br>174<br>175<br>177                      |

# **List of Figures**

| l-1  | The machine model                                                                        | 1  |

|------|------------------------------------------------------------------------------------------|----|

| 1-2  | A chart showing the locality and parallelism exhibited by algorithms in each chapter     |    |

|      | of this thesis.                                                                          | 2  |

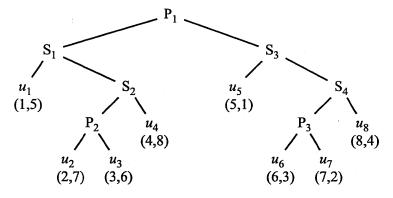

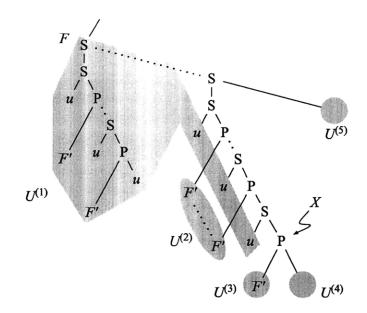

| 2-1  | A dag representing a multithreaded computation.                                          | 10 |

| 2-2  | The parse tree for the computation dag.                                                  | 10 |

| 2-3  | Comparison of serial, SP-maintenance algorithms                                          | 12 |

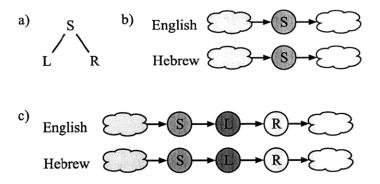

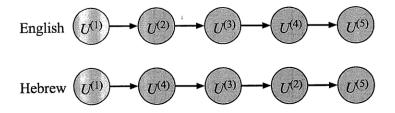

| 2-4  | An English and Hebrew ordering.                                                          | 14 |

| 2-5  | The SP-order algorithm written in serial pseudocode.                                     | 16 |

| 2-6  | An illustration of how SP-order operates at an S-node.                                   | 17 |

| 2-7  | An illustration of how SP-order operates at a P-node.                                    | 17 |

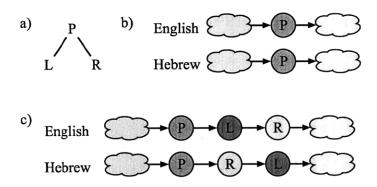

| 2-8  | A canonical Cilk parse tree                                                              | 19 |

| 2-9  | The SP-bags algorithm described in terms of procedures.                                  | 20 |

| 2-10 | The SP-bags algorithm written in serial pseudocode.                                      | 21 |

| 2-11 | The SP-ordered-bags algorithm written in parallel pseudocode.                            | 28 |

|      | The SP-Precedes procedure for the SP-ordered-bags algorithm.                             | 29 |

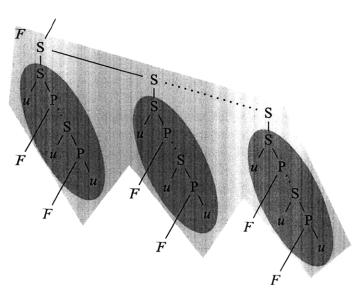

| 2-13 | The split of a trace around a P-node in terms of a canonical Cilk parse tree.            | 31 |

| 2-14 | An ordering of the new traces resulting from a steal.                                    | 32 |

| 2-15 | The local-tier SP-fast-bags algorithm written in parallel pseudocode                     | 34 |

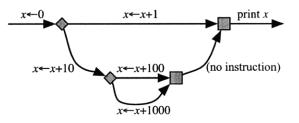

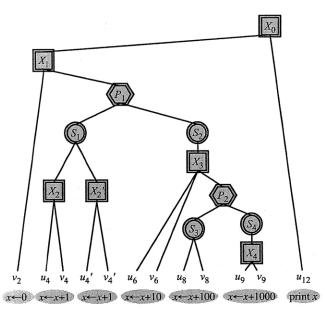

| 3-1  | A simple fork-join program that does several parallel increments.                        | 44 |

| 3-2  | The series-parallel dag for the sample program.                                          | 44 |

| 3-3  | The same program with the addition of transactions.                                      | 45 |

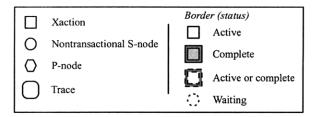

| 3-4  | A legend for computation-tree figures.                                                   | 47 |

| 3-5  | A computation tree for the program given by Figure 3-1.                                  | 48 |

| 3-6  | Pseudocode for a conflict-detection query.                                               | 52 |

| 3-7  | Pseudocode instrumenting a memory access.                                                | 54 |

| 3-8  | Code for cleanup up an aborted transaction.                                              | 55 |

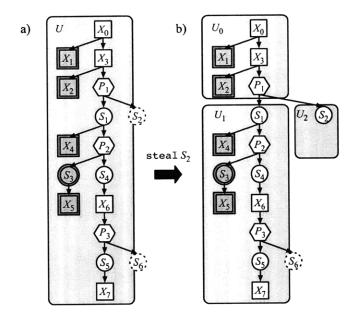

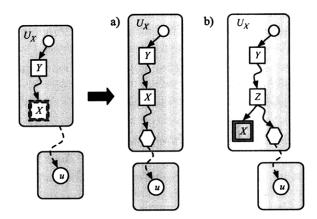

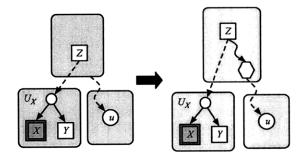

| 3-9  | Traces of a computation tree (a) before and (b) after a steal action                     | 56 |

| 3-10 | Pseudocode for the XConflict algorithm.                                                  | 57 |

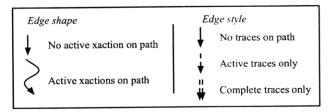

| 3-11 | The definition of arrows used to represent paths in Figures 3-12, 3-13 and 3-14          | 58 |

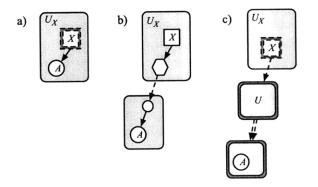

| 3-12 | The three possible scenarios in which $X$ is the nearest transactional ancestor of $B$   |    |

|      | that belongs to an active trace.                                                         | 58 |

| 3-13 | The possible scenarios in which the highest active transaction Y in $U_x$ is an ancestor |    |

|      | of <i>X</i>                                                                              | 59 |

| 3-14 | The scenario in which the highest active transaction Y in $U_x$ is not an ancestor of X. | 59 |

| 4-1  | Approximation ratios for SUU                                                             | 71 |

| 5-1        | Pseudocode for size-hashed backoff.                                                       | 97         |

|------------|-------------------------------------------------------------------------------------------|------------|

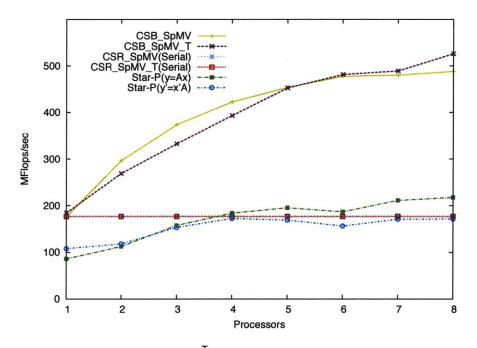

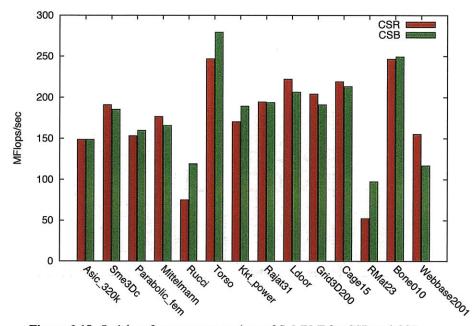

| 6-1        | Average performance of $Ax$ and $A^{T}x$ operations on our benchmark suite                | 104        |

| 6-2        | Parallel matrix-vector multiplication using CSR.                                          | 105        |

| 6-3        | Serial matrix-transpose-vector multiplication for CSR.                                    | 106        |

| 6-4        | Pseudocode for CSB matrix-vector multiplication.                                          | 110        |

| 6-5        | Pseudocode for subblockrow-vector multiplication used for CSB                             | 111        |

| 6-6        | Pseudocode for the subblock-vector product used for CSB                                   | 112        |

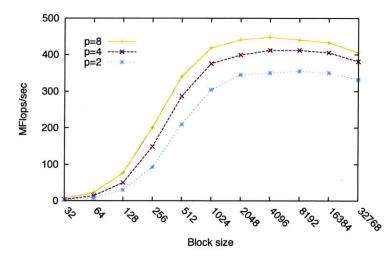

| 6-7        | The effect of CSB block size on SpMv performance.                                         | 117        |

| 6-8        | Structural information on the sparse matrices used in our experiments                     | 118        |

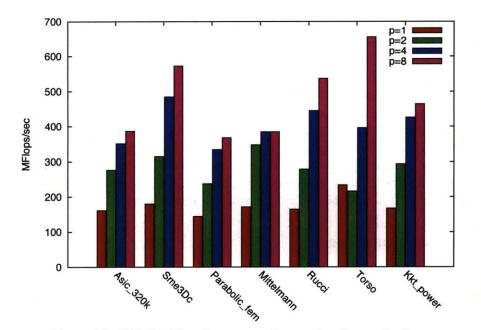

| 6-9        | CSB_SPMV performance on Opteron (smaller matrices).                                       | 120        |

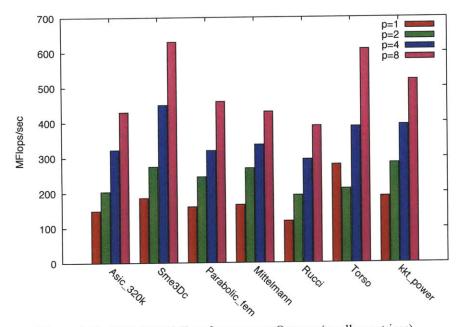

|            | CSB_SPMV_T performance on Opteron (smaller matrices).                                     | 121        |

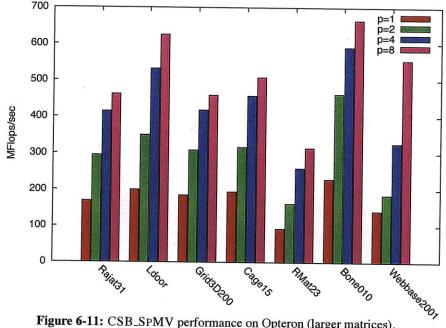

|            | CSB_SPMV performance on Opteron (larger matrices).                                        | 122        |

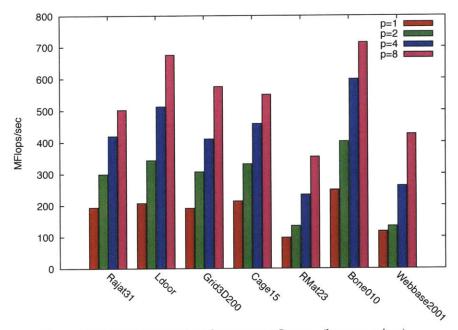

|            | CSB_SPMV_T performance on Opteron (larger matrices).                                      | 123        |

|            | Average speedup of CSB on smaller test matrices                                           | 123        |

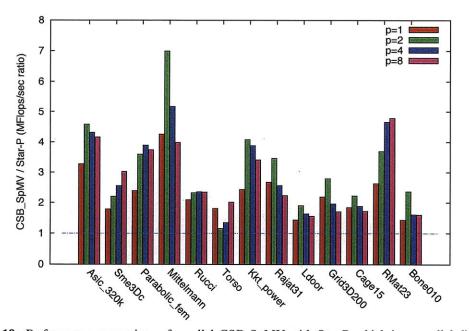

|            | Parallelism test for CSB_SPMV                                                             | 124        |

|            | CSB_SPMV performance on Harpertown.                                                       | 124        |

|            | CSB_SPMV performance on Nehalem.                                                          | 125        |

|            | Serial performance comparison of SpMV for CSB and CSR                                     | 125        |

|            | Serial performance comparison of SpMV_T for CSB and CSR                                   | 126        |

| 6-19       | Performance comparison of parallel CSB_SPMV with Star-P.                                  | 126        |

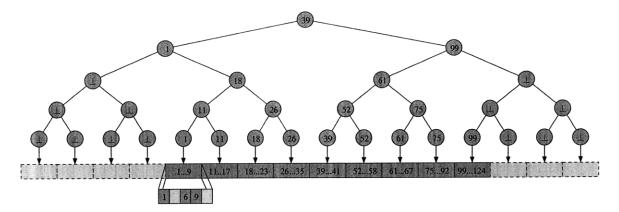

| 7-1        | Summary of known cache-oblivious dictionaries.                                            | 129        |

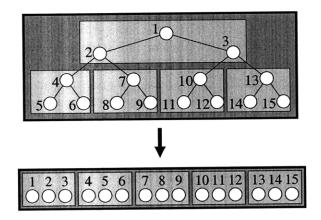

| 7-1<br>7-2 | The van Emde Boas layout.                                                                 | 129        |

| 12         |                                                                                           |            |

| 8-1        | An exponential CO B-tree.                                                                 | 133        |

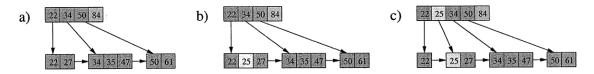

| 8-2        | An example of an insert into an exponential CO B-tree                                     | 134        |

| 8-3        | The modified van Emde Boas layout of a node in the exponential CO B-tree                  | 134        |

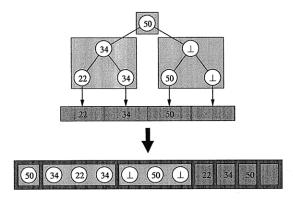

| 8-4        | A packed-memory CO B-tree.                                                                | 138        |

| 8-5        | An insertion into the packed-memory array.                                                | 140        |

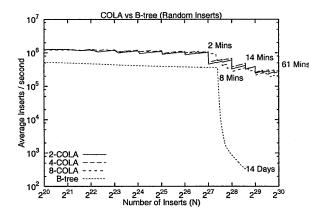

| 9-1        | Comparison of the COLA and B-tree for random insertions.                                  | 154        |

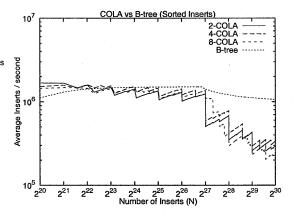

| 9-1<br>9-2 | Comparison of the COLA and B-tree for sorted insertions.                                  | 154        |

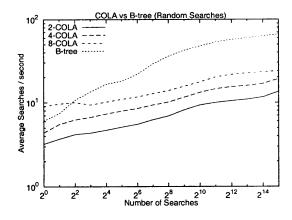

| 9-2<br>9-3 | Comparison of the COLA and B-tree for sorted insertions.                                  | 155        |

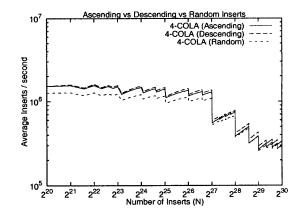

| 9-4        | Comparison of various insertion patterns into the COLA.                                   |            |

|            |                                                                                           | 100        |

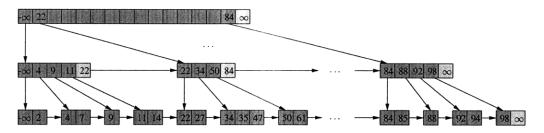

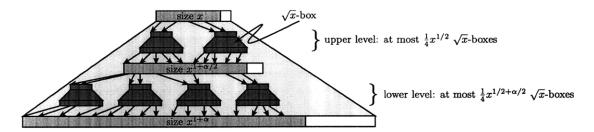

| 10-1       | The recursive structure of an $x$ -box                                                    | 158        |

| 10-2       | Buffer sizes for an x-box                                                                 | 158        |

| 10.1       | An answer $1_{2}$ of a clique for which the simple electric performs $\Omega(l^{2})$ work | 170        |

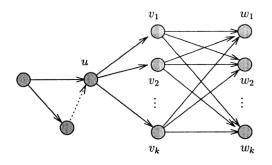

|            | An example of a clique, for which the simple algorithm performs $\Theta(k^2)$ work        | 178<br>180 |

| 12-2       | Pseudocode for updating labels.                                                           | 100        |

## Chapter 1

# Introduction

This thesis explores algorithms and data structures motivated by and designed for modern largescale computer systems, such as multicore computers. Achieving good performance on these machines entails designing algorithms that achieve good parallelism, thereby utilizing multiple processors effectively, and that have good locality, exploiting the cache to attain good memory performance. The goal of this thesis is to study various techniques for parallel and cache-efficient (specifically, so-called cache-oblivious) algorithms. Many of the solutions described in this thesis are data structural in nature, and many of the solutions exploit amortization in the analysis. Much of this thesis is really a study of amortized data structures in the context of practical problems motivated by modern computers.

Recently, most hardware vendors have abandoned their singlecore chips in favor of multicore designs. Intel, for example, announced in 2005 that their focus would be on multicore chips. Although most common machines today have between 2 and 8 cores, a general belief is that the number of cores will double every silicon generation (see, for example, [28]). Hence, highly parallel algorithms are necessary to exploit the full power of these machines.

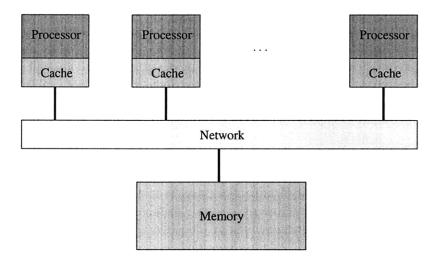

**Figure 1-1:** The machine model used for most of the algorithms in this thesis. Each processor is connected to a private fast memory, called the cache. Processors communicate through the shared main memory.

Throughout most of this thesis, I consider algorithms designed for a shared-memory machine, such as the one shown in Figure 1-1 (see also [117, Chapter 4]). As shown, each identical processor is connected to a private fast memory, called the *cache*. Processors are connected to main memory

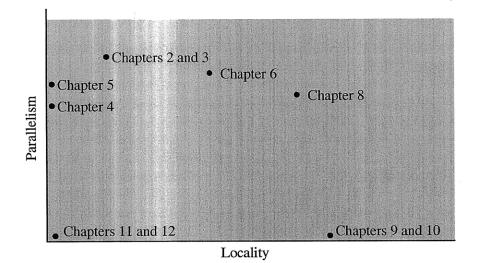

Figure 1-2: A chart showing how much locality and parallelism are expressed by each of the chapters in this thesis. The points here are subjective and should be taken as a guideline only. The x-axis here plots locality, with points towards the right exploiting the cache more effectively. The y-axis indicates concurrency or parallelism with higher points representing algorithms with more parallelism.

through some network, which is abstracted away throughout this thesis. Accessing the cache is much cheaper than accessing the shared memory, and thus good algorithms should exhibit locality to exploit the cache. In general, my algorithms are designed for a *symmetric multiprocessor (SMP)*, in which all memory locations (not currently residing in a cache) have the same access cost by each processor. My performance analyses depend on the uniform access cost, but algorithmic correctness does not. These algorithms thus apply to nonuniform access machines (NUMA), and the presence of locality in the algorithms suggests good performance there as well. Moreover, although Figure 1-1 shows only a single level of cache and a slow memory, many of the algorithms presented in this thesis generalize effectively to multilevel memory or cache hierarchies. In fact, one of the reasons I consider cache-oblivious algorithms is that cache-oblivious algorithms automatically generalize to multilevel memory hierarchies.

Figure 1-1 is consistent with common multicore processors today, such as all present Intel and AMD chips. Other types of multicores exist, such as the Sony-Toshiba-IBM Cell Broadband Engine with heterogeneous processors, or the Cray MTA with no caches. Although the algorithms in this thesis are not specifically designed for those types of machines, many of the techniques presented here may still be applicable.

Figure 1-2 shows a subjective chart of the locality and parallelism expressed by the algorithms within this thesis. The goal is to achieve algorithms in the upper-right, like those in Chapters 6 and 8, achieving both good locality and parallelism. As a step in this direction, I also consider algorithms that achieve either parallelism or locality. Chapters 2–6 and Chapter 8 address concurrency, whereas Chapters 7–11 address caching and locality. Chapters 2–5 are more infrastructural in nature, whereas Chapters 6 and 12 address algorithms at the library or application level.

#### Contributions

One of the key difficulties in designing parallel algorithms is coping with concurrent accesses to shared data. In some cases (e.g., the algorithm in Chapter 6), parallel tasks may be scheduled such that no two contending tasks execute at the same time. In this case, however, the parallel algorithm

must be structured to facilitate this scheduling, which is not a trivial task.

Much of this thesis focuses on more complex interactions among processors. When two parallel tasks operate on the same data, some mechanism for handling critical sections is required, in the form of semaphores [83] (or locks), or, more recently, transactional memory [119]. Dealing with critical sections adds more difficulty to the implementation of parallel codes. If the critical sections are too large, then parallelism decreases. If the critical sections are smaller, then the program becomes more complex. Complex parallel codes are prone to bugs like race conditions and deadlock. Moreover, it is not generally well-understood how to design algorithms that achieve provably good performance bounds while using locks or transactions.

This thesis makes two major contributions with respect to concurrency control. First, I provide algorithms that help the programmer to write correct parallel codes using locks or transactions, either by uncovering race bugs in programs with locks (Chapter 2) or by supporting conflict detection in a highly parallel transactional-memory system (Chapter 3). Second, these are themselves examples of parallel algorithms that achieve provably good performance despite their use of locks internally. Moreover, the solutions here include a novel approach for amortizing the cost of locking against the span of the computation.

Another goal of this thesis is to construct algorithms with good locality, thereby efficiently using memory caches on the machine. For large data sets, the cost of memory accesses may dominate the total runtime of an algorithm. Fortunately, memory is transferred in large chunks, and so by organizing data cleverly (to introduce locality), we can exploit the cache and drive down the total cost of the memory accesses. Most notably, my work on caching focuses on cache-oblivious dictionaries in Chapters 7–10. Many of the parallel algorithms included in this thesis, moreover, are structured to achieve some level of locality (notably, the algorithm in Chapter 6, but also to a lesser degree those algorithms in Chapters 2 and 3).

As a whole, this thesis aims to study many techniques for designing provably good parallel algorithms, also including some that use locks, and cache-oblivious algorithms.

Chapters 2 and 3 addresses mutual exclusion for fork-join programs<sup>1</sup>, providing tools that make it easier to guarantee program correctness. Both of these chapters describe solutions that are intended to be integrated into a parallel runtime system, essentially augmenting a parallel program with additional data structures to answer questions about the program as it is running. These algorithms essentially operate on input fork-join programs and augment them to address certain problems. Both of the parallel algorithms described in these chapters maintain a shared data structure that is accessed concurrently using locks for mutual exclusion. The analysis includes a novel technique for amortizing the cost of locking against the "span" of the underlying program. For a program with *work* (serial running time)  $T_1$  and *span* (also called critical-path length or depth)  $T_{\infty}$ , maintaining the centralized data structures in either of these chapters adds an overhead of  $O(PT_{\infty})$  to the running time of the parallel program when executed on P processors using an efficient scheduler. In contrast, the program without augmentation can be executed in  $O(T_1/P + T_{\infty})$  time. For both of these data structures, relevant queries can be answered in O(1) time without acquiring any locks.

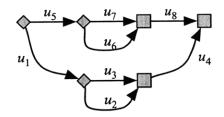

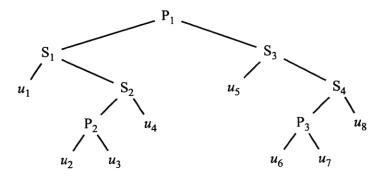

Chapter 2 address the problem of *series-parallel maintenance*, determining whether the structure of the program allows for two particular tasks to execute in parallel. Specifically, are tasks uand v logically serial or parallel? Answering this question is a key component of race detectors tools for uncovering race bugs in the program. Chapter 2 describes three algorithms, the serial SPorder and SP-fast bags algorithms, and the parallel SP-ordered-bags algorithm. Consider a parallel program with  $T_1$  work and  $T_\infty$  span. When augmented with SP-order or SP-fast-bags, the program

<sup>&</sup>lt;sup>1</sup>Fork-join programs are a restricted class of parallel programs with well-structured parallelism. Languages such as Cilk [54], NESL [53], and libraries such as TBB [174] all provide fork-join parallelism.

can be executed in  $O(T_1)$  time on a single processor while supporting queries in O(1) time. Both of these algorithms can be combined to form the SP-ordered-bags algorithm. When that program is augmented with SP-ordered-bags, it can be executed in  $O(T_1/P + PT_{\infty})$  worst-case time on Pprocessors. Here, queries can be answered in O(1) time, in parallel, without acquiring any locks. Chapter 2 represents joint work with Michael A. Bender, Seth Gilbert, and Charles E. Leiserson.

Chapter 3 considers conflict detection in a transactional-memory system that contains nested parallel transactions. Previous work on transactional memory (e.g., [119]) focuses on transactions that represent serial computation. In contrast, Chapter 3 considers adding transactions that contain parallel code blocks (that in turn contain nested parallel transactions) to fork-join programs. Allowing nesting within transactions exacerbates the problem of discovering conflicts among transactions and determining when one transaction must abort. Chapter 3 presents an algorithm for conflict detection in this complex setting. The key data structure, called XConflict, supports these queries and achieves the same performance bounds as SP-ordered-bags. That is, a program with  $T_1$  work and  $T_{\infty}$  span can be executed in  $O(T_1/P + PT_{\infty})$  worst-case time on P processors while augmented to maintain the XConflict data structure. Moreover, queries about conflicts among transactions can be answered in O(1) time without acquiring any locks. Chapter 3 represents joint work with Kunal Agrawal and Jim Sukha.

Chapters 4 and 5 consider scheduling problems. Specifically, Chapter 4 deals with a distributed scheduling problem, whereas Chapter 5 studies various backoff protocols in the presence of tasks that have different sizes.

Chapter 4 addresses scheduling under uncertainty, first introduced in [146], where each job has a stochastic failure rate. Specifically, an input consists of n unit-length jobs and m machines, where each job-machine pair has an independent failure probability when executing the job for unit time. This failure probability models machines crashing or taking too long to complete. There may be precedence constraints among jobs modeled by a directed acyclic graph (dag). The problem is to assign jobs to machines so as to minimize the expected **makespan**, which is the completion time of the last job to complete. A single job may be executed on multiple machines at the same time, thereby decreasing its aggregate failure probability. This thesis includes an  $O(\log \log \mu)$ -approximation when all jobs are independent (no precedence constraints),  $O(\log(n+m) \log \log \mu)$ -approximation when precedence constraints form chains, and  $O(\log(n+m) \log(n) \log \log \mu)$ -approximation when constraints form trees, where  $\mu = \min\{m, n\}$ . These results beat the previously best approximation ratios by at least an  $O((\log n)/\log \log \mu)$  factor. The solutions I present use many classic tools like LP rounding and competitive analysis. Chapter 4 represents joint work with Christopher Y. Crutchfield, Zoran Dzunic, David R. Karger, and Jacob H. Scott.

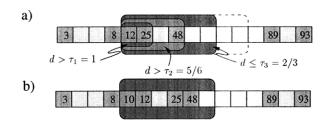

Chapter 5 considers randomized backoff, where processes/jobs make competing attempts to access a shared resource, but only one can gain control of the resource at a time. Here, I consider jobs that have nonuniform size. If an access attempt fails due to contention, then that process waits for a random amount of time (determined by the backoff protocol) before trying again. In the context of this thesis, backoff with jobs having different sizes is primarily motivated by transactional memory, where the "jobs" correspond to transactions in a program, all of which access the same memory location. This thesis presents the first theoretical analysis of randomized backoff when jobs have different sizes. I consider the case here when all jobs enter the system at the same time. Chapter 5 includes several contributions. First, the analyses show that binary exponential backoff achieves a makespan of  $V2^{\Theta(\sqrt{\log n})}$  with high probability for n jobs with total length V. This bound for jobs having different sizes is significantly worse than the  $\Theta(n \log n)$  bound achieved when all jobs have unit size [43]. This bound also suggests that *binary* exponential backoff is not a good choice for some transactional-memory systems. I also show that exponential backoff with a slower rate of backoff achieves  $O(V \log V)$  makespan. Finally, I improve the bounds further

by providing the *size-hashed backoff* scheme that is designed to work with a particular class of functions. I show constructively a class of functions allowing size-hashed backoff to complete with makespan  $O(V\sqrt{\log V}(\log \log V)^2)$  and prove the existence of functions that would allow size-hashed backoff to complete with makespan  $O(V(\log \log V)^3)$ . Chapter 5 represents joint work with Michael A. Bender and Seth Gilbert.

Chapter 6 returns to a fork-join parallel algorithm, but now at the application level instead of the runtime-system level. This chapter introduces a storage format for sparse matrices, called *compressed sparse blocks (CSB)*, which allows both Ax and  $A^Tx$  to be computed efficiently in parallel, where A is an  $n \times n$  sparse matrix with  $nnz \ge n$  nonzeros and x is a dense n-vector. The parallel multiplication algorithms use  $\Theta(nnz)$  work and  $\Theta(\sqrt{n} \lg n)$  span, yielding a parallelism of  $\Theta(nnz / \sqrt{n} \lg n)$ , which is amply high for virtually an large matrix. The storage requirement for CSB is essentially the same as that for the more-standard compresses-sparse-rows (CSR) [175] format, for which computing Ax in parallel is easy but  $A^Tx$  is difficult. Benchmark results indicate that on one processor, the CSB algorithm for Ax and  $A^Tx$  run just as fast as the CSR algorithm for Ax, but the CSB algorithm also scales up linearly with processors until limited by offchip memory bandwidth. Chapter 6 represents joint work with Aydın Buluç, Matteo Frigo, John R. Gilbert, and Charles E. Leiserson

One interesting aspect CSB is that it uses a recursive layout. Typically recursive layouts are used to exploit locality, but here the recursive layout allows for parallelism. Moreover, the multiplication algorithm introduces parallelism by duplicating shared-memory locations, thereby reducing the need for concurrency control on these locations. The analyses amortizes the cost of creating these extra memory locations against the cost of the actual multiplication, yielding a low overhead. Although I do not analyze the cache efficiency of CSB, the experimental study as well as the recursive layout suggest that CSB does achieve good spatial locality.

Chapters 8–11 address cache performance, including various cache-oblivious dynamic dictionaries in Chapters 8–10. A *dynamic dictionary* is a data structure that supports insertions, deletions, and predecessor queries on keyed data. Dynamic dictionaries that achieve good memory performance are the key data structures for filesystems and databases. The most famous memory-efficient dynamic dictionary is the B-tree [30, 70], which supports all three operations with  $O(\log_B N)$ memory transfers, where B is the *block size*, or number of records moved in each memory transfer. A *cache-oblivious* dynamic dictionary is a dictionary that achieves good performance without using the parameter B in the data structure. Several cache-oblivious dynamic dictionaries (e.g., [34, 35, 37, 41]), also called cache-oblivious B-trees, already exist. These previous cacheoblivious dictionaries, however, are all serial in nature. Chapter 7 provides a more detailed introduction to cache-oblivious dictionaries as well related work.

Chapter 8 provides cache-oblivious B-trees that support concurrent operations. These data structures build on previous versions of cache-oblivious B-tree and obtain similar performance bounds to the original data structures when operating serially. This chapter uses two main types of tools to facilitate concurrent operations. First, introducing randomization into the underlying data structures reduces the likelihood of overlapping expensive update operations. Second, the concurrent data structures make use of monotonic data movement. That is to say, the typical cache-oblivious B-trees move data in memory on update operations. The concurrent versions described in Chapter 8 aim to restrict this movement so that the address of a particular record can only increase over time, thereby facilitating concurrent operations. Chapter 8 represents joint work with Michael A. Bender, Seth Gilbert, and Bradley C. Kuszmaul.

Although the concurrent cache-oblivious B-trees are not the only parallel cache-oblivious algorithms in the literature, to my knowledge, these are the only ones that directly cope with multiple processors concurrently accessing the same data. Blelloch, Gibbons, and Simhadri [52], for example, provide general theorems stating that if an algorithm has low span and achieves good serial cache performance, then it achieves good parallel cache performance. Their results, however, assume that caches are noninterfering. There are also many examples of parallel cache-oblivious algorithms [51, 52, 67, 68, 100], but these typically also deal with computations where the data can be partitioned across processors, and there is little contention on shared locations.

Chapters 9 and 10 include dynamic cache-oblivious dictionaries that support a better insertion bound at a small cost to searches. The cache-oblivious lookahead array, described in Chapter 9, achieves inserts in  $O((\log N)/B)$  amortized memory accesses while still supporting searches in  $O(\log N)$  worst-case memory transfers. That is, insertions are improved by an  $O(B/\log B)$  factor whereas searches are worsened by only a  $O(\log B)$  factor. The xDict, described in Chapter 10, achieves the optimal tradeoff bound (proved in [59]), namely inserts in  $O((1/\varepsilon B^{1-\varepsilon}) \log_B(N/M))$ and searches in  $O((1/\varepsilon) \log_B(N/M))$  memory transfers. These data structures are the first to incorporate the technique of fractional cascading [64] into cache-oblivious data structures. The cacheoblivious lookahead array represents joint work with Michael A. Bender, Martin Farach-Colton, Yonatan R. Fogel, Bradley C. Kuszmaul, and Jelani Nelson, and the xDict represents joint work with Gerth Stølting Brodal, Erik D. Demaine, John Iacono, Stefan Langerman, and J. Ian Munro.

Chapter 11 also addresses caching, but with a paradoxical goal. In particular, this chapter aims to devise an online page-replacement strategy that achieves the highest possible fraction of page faults (or cache misses) as compared to the (worst) offline strategy. The goal here is not entirely serious, but the analyses may still be interesting in their own right. Since the aim is to reduce locality, and this chapter does not address parallelism, Figure 1-2 shows this chapter in the lower-left of the chart. I show that randomization is required to have a strategy that is competitive with the worst offline strategy. I also give a randomized strategy based on the most recently used heuristic and prove that it is the worst possible replacement policy. I also show that direct mapping is, in some sense, the worst page-replacement policy. This last result suggests that caches should use at least some degree of associativity. Chapter 11 represents joint work with Kunal Agrawal and Michael A. Bender.

Finally, Chapter 12 addresses dynamically maintaining a topological ordering in a dag. In particular, let G = (V, E) be a dag, and let n = |V| and m = |E|. We say that a total ordering on vertices is a **topological ordering** if for every edge  $(u, v) \in E$ , we have u appearing before v in the total ordering. This chapter considers the problem of maintaining a topological ordering dynamically as the underlying graph changes. Specifically, I address the incremental problem, in which we begin with an empty n-node graph  $G = (V, \emptyset)$  and edges are added one at a time. Throughout this process, a data structure maintains a topological ordering of the graph G, allowing for queries about relationships among vertices. Chapter 12 presents a new algorithm that has total cost  $O(n^2 \log n)$ for maintaining the ordering. Rather than attempting to place nodes in an ordered list (as in previous approaches), we assign each node a label that induces the ordering and can be updated efficiently. When the graph is dense, this algorithm is more efficient than existing algorithms. By way of contrast, the best prior algorithms achieve only  $O(\min\{m^{1.5}, n^{2.5}\})$  cost. These algorithms are all serial, and there is likely little locality. Chapter 12 represents joint work with Michael A. Bender and Seth Gilbert.

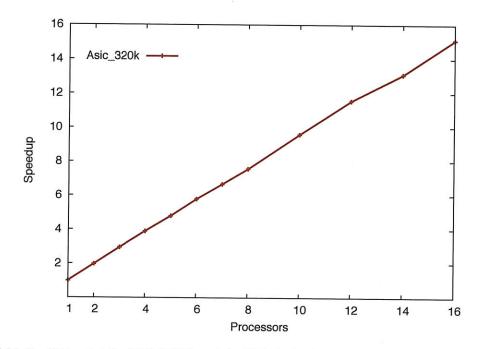

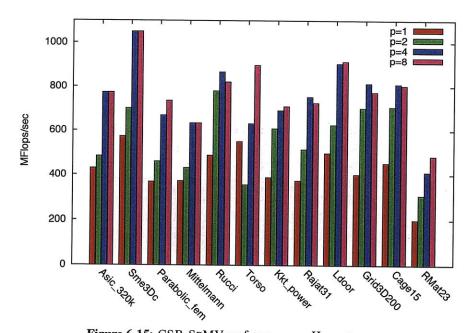

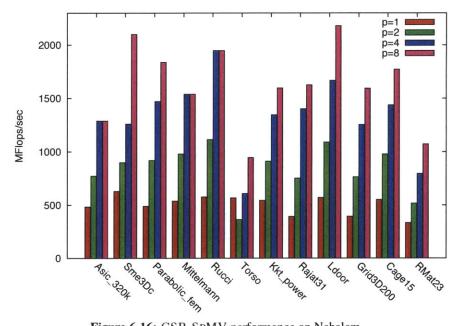

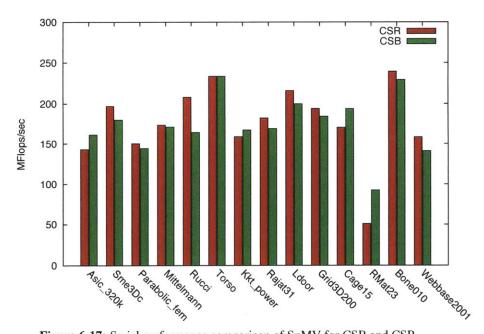

With the exception of the scheduling algorithms in Chapters 4 and 5 and the page-replacement problem in Chapter 11, all of the algorithms in this thesis incorporate data structures and amortization. These data structures have many similar themes that unify the topic areas. Some of the cache-oblivious data structures, particular the concurrent B-trees (Chapter 8) and the xDict (Chapter 10) use recursive layouts. A recursive layout also occurs in the parallel CSB algorithm in Chapter 6, but the goal in CSB is to provide parallelism, not locality.