PUBLISHED BY INSTITUTE OF PHYSICS PUBLISHING AND SISSA

RECEIVED: *March 15, 2007* REVISED: *May 16,2007* ACCEPTED: *May 25, 2007* PUBLISHED: *June 13, 2007*

## ATLAS liquid argon calorimeter back end electronics

The Liquid Argon Back End Electronics collaboration

A. Bazan,<sup>a</sup> F. Bellachia,<sup>a</sup> J. Colas,<sup>a</sup> G. Ionescu,<sup>a,1</sup> R. Lafaye,<sup>a</sup> S. Laplace,<sup>a</sup> G. Perrot,<sup>a</sup> L. Poggioli,<sup>a,2</sup> J. Prast,<sup>a</sup> H. Przysiezniak,<sup>a</sup> I. Wingerter-Seez,<sup>a</sup> B. Dinkespiler,<sup>b,3</sup> Y. He,<sup>b</sup> T. Liu,<sup>b</sup> R. Stroynowski,<sup>b</sup> A. Xiang,<sup>b</sup> J. Yang,<sup>b</sup> J. Ye,<sup>b</sup> H. Wilkens,<sup>c</sup> A. Blondel,<sup>d</sup> A. Clark,<sup>d</sup> M. Diaz Gomez,<sup>d</sup> I. Efthymiopoulos,<sup>d,4</sup> D. La Marra,<sup>d</sup> A. Léger,<sup>d</sup> L. Moneta,<sup>d,4</sup> S. Pernecker,<sup>d</sup> I. Riu,<sup>d,5</sup> L. Rosselet,<sup>d</sup> A. Straessner,<sup>d</sup> J. Ban,<sup>e</sup> S. Boettcher,<sup>e,6</sup> A. Gara,<sup>e,7</sup> J.A. Parsons,<sup>e</sup> S. Simion,<sup>e,2</sup> W. Sippach,<sup>e</sup> F. Henry-Couannier,<sup>f</sup> E. Monnier,<sup>f</sup> B. Repetti,<sup>f,8</sup> S. Tisserant,<sup>f</sup> A. Karev,<sup>g,11</sup> L. Kurchaninov,<sup>g,9</sup> H. Oberlack,<sup>g</sup> Lo. Fayard,<sup>h</sup> P. Matricon,<sup>h</sup> G. Unal,<sup>h,4</sup> M. Escalier,<sup>i,10</sup> F. Hubaut,<sup>*i*,3</sup> B. Laforge,<sup>*i*</sup> O. Le Dortz,<sup>*i*</sup> D. Martin,<sup>*i*</sup> P. Schwemling,<sup>*i*</sup> M.L. Chu,<sup>*j*</sup> S.-C. Lee,  $^{j}$  D.S. Su $^{j}$  and P.K. Teng $^{j}$ <sup>a</sup>LAPP - Laboratoire d'Annecy-le-Vieux de Physique des Particules, Université de Savoie, IN2P3-CNRS, Annecy-le-Vieux, France <sup>b</sup>SMU, Southern Methodist University, Department of Physics, Dallas, Texas, U.S.A. <sup>c</sup>CERN - Centre Européen pour la Recherche Nucléaire, Genève, Switzerland <sup>d</sup>Université de Genève, Département de physique nucléaire et corpusculaire, Genève, Switzerland <sup>e</sup>Columbia University, Nevis Laboratories, Irvington, New York, U.S.A. <sup>f</sup>CPPM - Centre de Physique des Particules de Marseille, Marseille, France <sup>8</sup>MPI, Max-Planck-Institut für Physik, Werner-Heisenberg-Institut, Munich, Germany <sup>h</sup>LAL - Laboratoire de l'Accélérateur Linéaire, Orsay, France <sup>i</sup>LPNHE - Laboratoire de Physique Nucléaire et de Hautes Energies, Universités Paris VI et Paris VII, Paris, France <sup>j</sup>Institute of Physics, Academia Sinica, Nankang, Taipei, Taiwan, Republic Of China <sup>1</sup> Now at Laboratoire des Images et des Signaux (LIS-INPG), Grenoble, France. <sup>2</sup> Now at LAL. <sup>3</sup> Now at CPPM. <sup>4</sup> Now at CERN. <sup>5</sup> Now at U. Autonoma Barcelona, Spain. <sup>6</sup> Now at Christian Albrechts University, Institute for Experimental and Applied Physics, Kiel, Germany. <sup>7</sup> Now at IBM T.J. Watson Research Center, U.S.A. <sup>8</sup> Now at Laboratoire d'Astrophysique de Marseille (LAM), France. <sup>9</sup> Now at TRIUMF, Vancouver, Canada. <sup>10</sup> Now at CEA, Saclay, France.

<sup>11</sup> On leave of absence from JINR, Dubna, Russia.

*E-mail:* julie.prast@lapp.in2p3.fr

ABSTRACT: The liquid argon calorimeters play a central role in the ATLAS (A Toroidal LHC Apparatus) experiment. The environment at the Large Hadron Collider (LHC) imposes strong constraints on the detectors readout systems. In order to achieve very high precision measurements, the detector signals are processed at various stages before reaching the Data Acquisition system (DAQ). Signals from the calorimeter cells are received by on-detector Front End Boards (FEB), which sample the incoming pulse every 25 ns and digitize it at a trigger rate of up to 75 kHz. Off-detector Read Out Driver (ROD) boards further process the data and send reconstructed quantities to the DAQ while also monitoring the data quality. In this paper, the ATLAS Liquid Argon electronics chain is described first, followed by a detailed description of the off-detector readout system. Finally, the tests performed on the system are summarized.

KEYWORDS: Electronic detector readout concepts (gas, liquid), Digital signal processing.

# Contents

| 1. | Intr | oductio  | Dn                                            | 2  |

|----|------|----------|-----------------------------------------------|----|

| 2. | LAr  | g electi | ronics chain                                  | 4  |

|    | 2.1  | Reado    | out architecture                              | 4  |

|    | 2.2  | Front    | End electronics                               | 4  |

|    | 2.3  | Back I   | End electronics                               | 6  |

|    |      | 2.3.1    | Optimal filtering                             | 8  |

|    |      | 2.3.2    | The Back End electronics system               | 9  |

|    |      | 2.3.3    | Timing and trigger control                    | 11 |

|    |      | 2.3.4    | Level-1 receiver system                       | 12 |

| 3. | LAr  | g Back   | End electronics description                   | 13 |

|    | 3.1  | VME      | crate                                         | 13 |

|    |      | 3.1.1    | Power supply                                  | 14 |

|    |      | 3.1.2    | Air and water cooling of the electronics      | 14 |

|    |      | 3.1.3    | Detector Control System (DCS)                 | 15 |

|    |      | 3.1.4    | Crate backplane and CP3 board                 | 16 |

|    | 3.2  | SPAC     | Master module                                 | 17 |

|    |      | 3.2.1    | Description and functionalities of the module | 17 |

|    |      | 3.2.2    | SPAC protocol and Slave ASIC                  | 18 |

|    |      | 3.2.3    | SPAC interface                                | 21 |

|    |      | 3.2.4    | Power consumption, power and reset procedures | 21 |

|    |      | 3.2.5    | SPAC design and manufacturing                 | 22 |

|    | 3.3  | TTC a    | and Busy module (TBM)                         | 22 |

|    |      | 3.3.1    | Timing, Trigger and Control distribution      | 22 |

|    |      | 3.3.2    | Busy collection                               | 23 |

|    |      | 3.3.3    | Control outputs                               | 23 |

|    |      | 3.3.4    | VME interface                                 | 24 |

|    |      | 3.3.5    | Power, reset and ESD considerations           | 24 |

|    |      | 3.3.6    | TBM design and manufacturing                  | 24 |

|    | 3.4  | ROD      | module                                        | 25 |

|    |      | 3.4.1    | FEB data input                                | 25 |

|    |      | 3.4.2    | TTC data input                                | 28 |

|    |      | 3.4.3    | Output flow                                   | 29 |

|    |      | 3.4.4    | SDRAM                                         | 29 |

|    |      | 3.4.5    | Serializer                                    | 31 |

|    |      | 3.4.6    | Busy handling                                 | 31 |

|    |      | 3.4.7    | VME interface and internal communication      | 32 |

|    |      | 3.4.8    | ROD design, manufacturing and tests           | 32 |

| 3.5 | Proces  | ssing Unit                               | 32 |

|-----|---------|------------------------------------------|----|

|     | 3.5.1   | Input FPGA (InFPGA)                      | 33 |

|     | 3.5.2   | Digital Signal Processor (DSP)           | 34 |

|     | 3.5.3   | Output FIFO                              | 37 |

|     | 3.5.4   | Control FPGA (ConFPGA)                   | 38 |

|     | 3.5.5   | Boot procedure                           | 39 |

|     | 3.5.6   | Power supply                             | 39 |

|     | 3.5.7   | JTAG chain                               | 39 |

|     | 3.5.8   | PU design and manufacturing              | 40 |

| 3.6 | Transi  | ition Module                             | 40 |

|     | 3.6.1   | FIFO memory                              | 41 |

|     | 3.6.2   | Flow control                             | 41 |

|     | 3.6.3   | Power, reset, ESD and EMC considerations | 42 |

|     | 3.6.4   | TM design and manufacturing              | 42 |

| 3.7 | ROD     | Injector                                 | 42 |

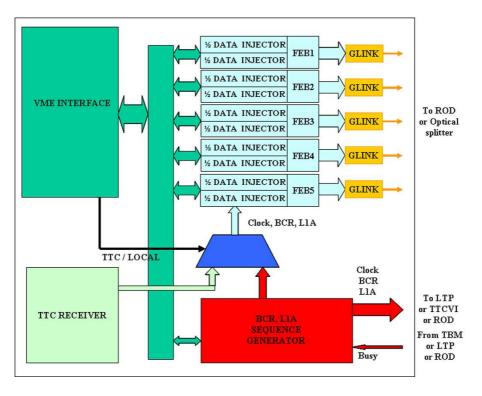

|     | 3.7.1   | TTC receiver                             | 43 |

|     | 3.7.2   | Sequence generator                       | 44 |

|     | 3.7.3   | Data injector                            | 45 |

|     | 3.7.4   | VME interface                            | 46 |

| BE  | system  | tests                                    | 46 |

| 4.1 | Injecto | or tests                                 | 46 |

| 4.2 | Config  | guration of the system                   | 47 |

| 4.3 | Speed   | of the DSP code                          | 47 |

| 4.4 | Comn    | nissioning in the cavern                 | 48 |

| Con | clusion |                                          | 49 |

#### 5. Conclusion

4.

### 1. Introduction

The ATLAS experiment [1] at the LHC is a general purpose detector designed to exploit the full physics potential of the LHC at CERN. The collider will produce proton-proton collisions at a centre-of-mass energy of 14 TeV, as well as heavy ion collisions.

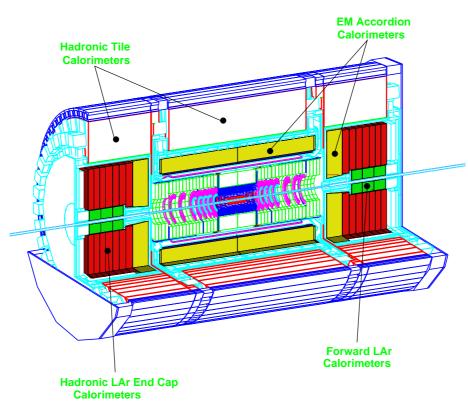

Liquid Argon (LArg) sampling calorimeters [2] are used in ATLAS for all electromagnetic calorimetry covering the pseudorapidity interval  $|\eta| < 3.2$ , as well as for hadronic calorimetry from  $|\eta| = 1.4$  to the acceptance limit  $|\eta| = 4.8$ . The ATLAS calorimeters are shown in figure 1, with the LArg system as well as the barrel hadronic system.

The LArg calorimeters consist of four sub-detectors and are contained within three cryostats. The central cryostat houses the electromagnetic barrel calorimeter (EMB), while each end-cap cryostat contains an end-cap electromagnetic calorimeter (EMEC), a hadronic end-cap wheel

**Figure 1.** Schematic 3D view showing the ATLAS calorimeter system with its EM barrel and end-cap LArg calorimeters, hadronic barrel and barrel-end tile calorimeters, hadronic LArg end-cap calorimeters and forward LArg calorimeters.

(HEC) and a forward calorimeter (FCAL). In total, about 196000 calorimeter cells are to be read out.

A choice of common electronics for all calorimeters standardizes the hardware and will simplify the maintenance. The HEC nonetheless uses cold preamplifiers.

The main tasks for the readout electronics are:

- to measure, for triggered beam crossings, the energy deposit in each calorimeter cell to better than 0.25% at high energy. The dynamic energy range will cover a maximum of 3 TeV down to a lower limit of 10 MeV set by thermal noise. Coherent noise over many cells used to measure the jet energy should be kept below 5% of the incoherent noise. The readout should proceed without any dead time up to a trigger rate of 75 kHz.

- to provide the trigger system with the energy deposited in trigger towers of size  $\Delta \eta \times \Delta \phi = 0.1 \times 0.1$ . The trigger processor combines the information from all ATLAS sub-detectors to

deliver at the 40 MHz bunch crossing rate a yes/no decision to read out the detectors.

An extensive phase of R&D led to the final design of the LArg readout electronics, which were then constructed, tested and installed in the ATLAS cavern, and finally underwent extensive commissioning. The whole chain is described in the following section, as an introduction to a detailed account of the back end electronics system.

### 2. LArg electronics chain

A general view of the readout architecture is given, followed by brief descriptions of the Front End (FE) and Back End (BE) electronics, as well as sections on the Timing and Trigger Control (TTC) and Level-1 receiver system.

### 2.1 Readout architecture

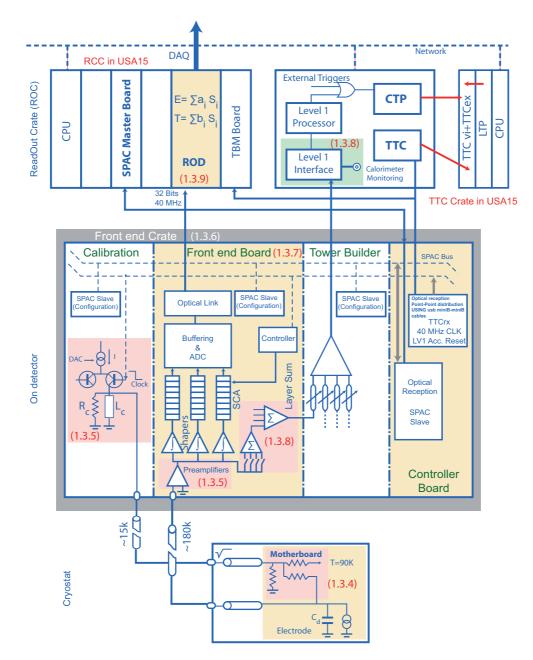

The high radiation levels in the vicinity of the detector on the one hand, and the necessity for a large signal dynamic range and for very low level coherent noise on the other hand, favour remote electronics combined with preamplification very near the detector. In addition, the large number of cables required imply data multiplexing in any off-detector solution. The final readout architecture takes into account all of these points and is sketched in figure 2.

When a charged particle traverses and ionizes the liquid Argon in the gap between a LArg electrode and an absorber, an ionization current is measured on the readout cells of the electrodes (see reference [2] for more details). The pulse height is proportional to the energy deposit of the particle. The analog signal is received and digitized by the Front End Boards (FEBs) which are mounted directly on the detector and are part of the Front End electronics. The FEBs send the digitized pulse via optical links to the Read Out Drivers (RODs) which are installed in a radiation-free area next to the detector cavern and are part of the Back End electronics.

A careful summation of the analog signals is also formed, mostly in the FEBs or in the Tower Builder Boards (Tower Driver Boards for the HEC; see following section), but also in a few special cases in the receiver system (barrel-EC transition region and FCAL) to build primitives which are sent to the BE trigger electronics. They are received, reshaped and summed into trigger towers of size  $\Delta \eta \times \Delta \phi = 0.1 \times 0.1$  before being transferred to the Level-1 calorimeter processor.

Each ROD (192 in total) can be connected to up to 8 FEBs (1524 in total) and can process the signals of up to 1024 detector cells. The RODs send the data through optical links, the S-links, to the Read Out Buffers (ROBs) hosted on PCs. At this stage, the acquisition changes from a push mode driven by the Level-1 trigger to a pull mode driven by the event-filter farm, where event selection and building is performed, and the data are finally recorded.

### 2.2 Front End electronics

The sensitive analog electronics are housed on the detector. Inside the cryostat, the calorimeter electrodes are grouped to form readout cells and small coaxial cables bring the cell signals to the cold-to-warm feedthroughs (see reference [2]). Front End electronics crates are mounted on the feedthroughs, in the crack between the barrel and end-cap calorimeters and at the rear of the end-caps. A Front End Crate contains several types of boards.

**Figure 2.** A block diagram of the readout electronics is shown, where the LArg calorimeter electrical circuit is schematized at the bottom of the figure, followed above by the on-detector Front End electronics crate (FEC) which contains amongst other modules the FEBs, while at the top left and right of the figure respectively are schematized a BE electronics crate containing the ROD boards (ROC: ROD crate) and a TTC crate.

- The calibration board injects precisely known current pulses through high precision resistors located in the cold, to simulate energy deposits in the calorimeters.

- Front End Boards which:

- amplify and shape the analog signals;

- sum the calorimeter cells by trigger tower within each layer depth, and prepare the input signals for the tower builder board (see following item);

- store the signals in an analog memory waiting for the decision by the Level-1 trigger;

- digitize the selected pulses and transmit the multiplexed digital results on optical fibres.

- Tower Builder Boards (TBBs), for the EM barrel and endcap calorimeters, perform the final level of analog summation to form trigger tower signals and transmit the analog signals to the Level-1 cavern (USA15) for digitization and processing by the Level-1 trigger processor. As well, the board which builds the HEC trigger towers is called the Tower Driver Board (TDB) since no summation is implied here. The function of this board is to produce differential signals and to drive 70 m trigger cables.

- Front End Crate controller boards (FECcont) receive and distribute the 40 MHz clock, the Level-1 trigger accept signal (L1A), as well as other fast synchronous signals and information, to configure and control the FEBs and calibration boards.

- Various monitoring boards which ensure that the LArg system is operating correctly. They collect the information from the mechanical sensors which measure the position and stresses of the detectors, from the temperature gauges for the cryogenics and the LArg (LArg Temperature Monitor Board), and from the LArg purity probes (LArg Purity Monitoring Board).

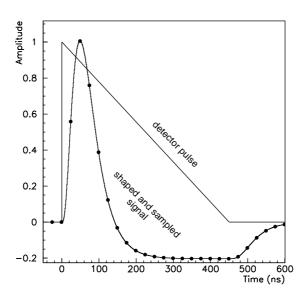

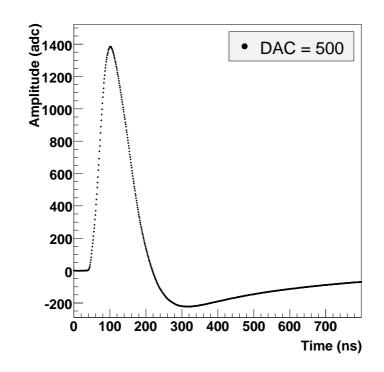

The FEBs perform the first signal processing step. Each FEB receives the signals of 128 LArg detector cells. The triangular-shaped pulse of the ionization current of each detector cell is first amplified. In the case of the HEC only, the preamplifiers are installed directly on the detector and not on the FEBs. The preamplifier output is sent to shaper chips which amplify the pulse, split it into three gain scales in the ratio 1/9.3/93 and apply a bi-polar shaping function to each scale. The signal is then sampled at 40 MHz in Switched Capacitor Array (SCA) chips which store the samples in analog form during the Level-1 trigger latency (< 2.5  $\mu$ s). Figure 3 shows the triangular pulse current in the LArg cell as well as the FEB output signal after bi-polar shaping and sampling.

When the Level-1 trigger decision arrives, the optimal gain scale is selected on an event-byevent basis. The SCA samples are then digitized at a 5 MHz rate in a 12-bit Analog-To-Digital Converter (ADC) which, together with the gain selection procedure, fulfills the required 16-bit dynamic range over the whole energy interval. The FEB data are finally sent via the 1.6 Gbit/s G-link optical links to the RODs.

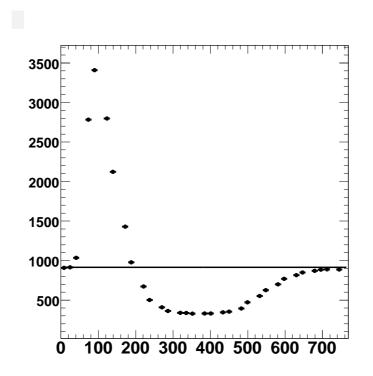

The time constant of the FEB shapers is chosen to minimize the overall noise level. The two main contributions are the electronics noise and pile-up noise, which respectively decrease and increase with the peak shaping time  $t_p$ , as can be seen in figure 4. The pile-up noise is due to back-ground events occurring in the same beam crossing as a signal event, as well as in beam crossings occurring before and after. Digital signal processing in the BE electronics further optimizes the signal to noise ratio as a function of the actual luminosity.

### 2.3 Back End electronics

The BE electronics are contained in and make use of three systems situated in three different locations: the ROD which is the core of the BE, the TTC and the Level-1 receiver. The BE system

**Figure 3.** Triangular pulse of the current in the LArg cell and the FEB output signal after bi-polar shaping. Also indicated are the sampling points every 25 ns. Even though a maximum of 32 samples can be attained, only a few samples are typically used (5 to 7) during normal data taking.

**Figure 4.** Noise level as a function of the peak shaping time  $t_p$ . The electronics noise decreases with increasing  $t_p$ , while the pile-up noise increases. The optimal shaping time depends on the LHC luminosity L.

must perform various tasks during physics and calibration runs. The physics mode is clearly the most demanding: the system reads the FE electronics, receives the TTC signals, processes the data and sends it to the acquisition system at a Level-1 rate of up to 75 kHz.

During calibration runs, signals of known intensity are generated and sent to the LArg detector cells by the calibration boards described previously. The trigger rate is lower than for physics ( $\sim$  10 kHz) due to the properties of the calibration pulser, and so there is more computation time

available in the RODs.

The BE must also distribute the timing clock and trigger to the FE electronics and the RODs, as well as configure and control the FECs. More precisely, the FEB and TTC data readout and processing imply:

- buffering the events to absorb fluctuations in the time of arrival of triggers and to optimize the use of the available readout bandwidth;

- generating a Busy to pace the trigger processor;

- checking the FEB data consistency and the synchronization with the TTC stream;

- processing and monitoring of the data;

- reducing the data volume by a factor of  $\sim 2$ ;

- sending out the processed data to the DAQ system.

All of these tasks must be performed fast enough to cope with the average Level-1 trigger rate of 75 kHz.

### 2.3.1 Optimal filtering

The optimal filtering (OF) method [3] is at the core of the BE processing role. The OF algorithm, implemented in the ROD Digital Signal Processors (DSPs; see section 3.5), calculates the energy for each cell while minimizing the noise contribution. For cells with an energy above a certain threshold (approximately 5% to 10% of all cells), the precise timing of the signal as well as a data quality factor, a kind of  $\chi^2$  allowing to flag cells with large pile-up contribution, are determined.

The signal pulse is sampled every 25 ns a programmable number of times, between 3 and 32. For physics, 5 samples are typically used, whereas for calibration, up to 32 samples can be taken. The energy *E* and time  $\tau$  of the signal pulse are calculated in a weighted sum of the sample amplitudes,  $s_i$ :

$$E = \sum_{i=1}^{N} a_i (s_i - ped)$$

(2.1)

$$E\tau = \sum_{i=1}^{N} b_i(s_i - ped) , \qquad (2.2)$$

where N is the number of samples and *ped* is the pedestal value of the corresponding readout channel. The optimal filtering weights,  $a_i$  and  $b_i$ , are evaluated while minimizing the dispersion in E arising from electronics and pile-up noise.

Since the error on  $\tau$  is inversely proportional to *E*, the time is calculated only for channels above a given energy threshold, in the same way as the quality factor  $\chi^2$ . A simplified  $\chi^2$ , ignoring correlations between the sampling points, is computed to compare the measured pulse shape to the ideal pulse:

$$\chi^{2} = \sum_{i=1}^{N} \left( s_{i} - ped - E(g_{i} - \tau g_{i}') \right)^{2}, \qquad (2.3)$$

**Figure 5.** The BE electronics racks in USA15. From left to right: the injectors rack with splitters above and the cooling system below, the FCAL and HEC rack, the EMEC-C rack, the EMEC-A rack and the four EMB racks. The 5 ROS racks can also be seen at the very end of the row.

where  $g_i$  and  $g'_i$  are respectively the normalized pulse shape and its derivative. These are estimated from the measured calibration pulse and from the electrical model parameters of the readout circuit (see reference [4] for more details).

### 2.3.2 The Back End electronics system

The BE electronics are situated in the Level-1 cavern (USA15), with approximately 70 m of optical fibres separating them from the detector. For each trigger, data from the TTC stream and from the FE electronics are pushed into the ROD modules where they are checked, processed, formatted and sent on a Read Out Link (ROL) to the ATLAS DAQ (see figure 2).

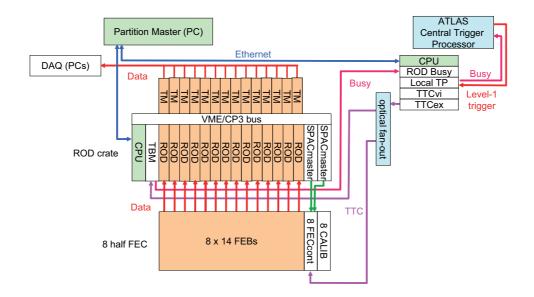

To increase modularity and allow for concurrent running of the various parts, the LArg calorimetry is split into 6 partitions: one for each half-barrel (EMB-A and EMB-C), one for each end-cap (EMEC-A and EMEC-C), one for the A side hadronic end-cap and forward calorimeter (HEC-A + FCAL-A) and one for the C side (HEC-C + FCAL-C). Partitioning is useful for debugging and calibration purposes, as well as for testing different parts of the detector independently of the others, during the installation phase and in case of problems during data taking. A photograph of the BE electronics racks can be seen in figure 5.

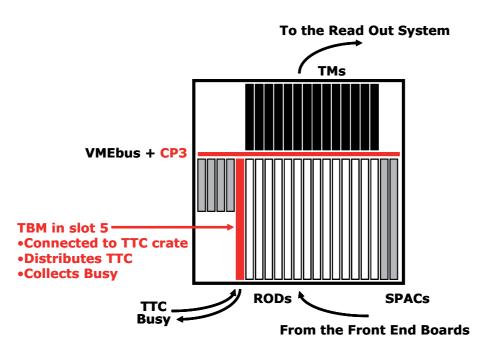

To each partition is associated a workstation (Partition Master), which controls and monitors the system, and a TTC sub-system (see section 2.3.3 for more details). A barrel partition e.g. EMB-A (see table 1 for the other partitions) is composed of 4 ROD crates and the associated FE electronics. Each ROD crate drives 8 half FECs and contains the following:

• A CPU connected to an Ethernet network controls the crate and the associated FECs.

**Figure 6.** Sketch of a barrel partition. A FE crate (bottom) is schematized sending data to a BE crate (middle). The TTC crate (upper right except for the Central Trigger Processor) receives (Trigger) and sends (Busy) signals from and to the ATLAS Central Trigger Processor. The TTC signals are then sent to the ROCs and FECs. Also shown are the Partition Master PC as well as the DAQ PCs.

- Two SPAC (Serial Protocol for the ATLAS Calorimeters) Master modules drive the 8 FECcont boards (one in each half FEC) to configure the various boards of the FEC and to read back status information.

- 14 ROD boards receive raw data from the  $8 \times 14$  FEBs of the partition and calculate the energy, time and data quality factor.

- A TTC and Busy Module (TBM) receives the TTC information and delivers the TTC signals to the ROD boards in the crate via a dedicated CP3 backplane board.

- The TBM also collects the ROD Busy signals via the CP3 backplane.

- Transition modules (TM) (one per ROD) transmit the ROD result to the DAQ through the S-links (4 per TM).

A sketch of a barrel partition is shown in figure 6.

Such an architecture provides a completely autonomous partition which can run independently from the others. The composition of the other LArg partitions is very similar although the number of modules scales down with the number of channels to be read out as shown in table 1.

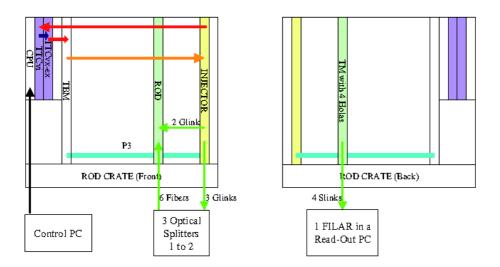

In addition, but in separate and dedicated crates, the ROD Injector module has been developed to simulate the flow of data coming from the FEBs and from the TTC system. It is used for testing the ROD boards and is described in detail in section 3.7. As an example, half a ROD crate (7 out of 14 RODs) can be driven using 6 Injectors.

| Partition    | EMB       | EMEC      | HEC-A + | HEC-C + | total |

|--------------|-----------|-----------|---------|---------|-------|

|              | A + C     | A + C     | FCAL-A  | FCAL-C  |       |

| Work station | 1 + 1     | 1 + 1     | 1       | 1       | 6     |

| TTC crate    | 1         | 1         | 1       | 1       | 4     |

| ROD crate    | 4 + 4     | 3 + 3     | 1       | 1       | 16    |

| Crate CPU    | 4 + 4     | 3 + 3     | 1       | 1       | 16    |

| SPAC Master  | 8 + 8     | 6+6       | 2       | 2       | 32    |

| CP3 board    | 4 + 4     | 3 + 3     | 1       | 1       | 16    |

| TBM          | 4 + 4     | 3 + 3     | 1       | 1       | 16    |

| ROD board    | 56 + 56   | 35 + 35   | 5       | 5       | 192   |

| TM board     | 56 + 56   | 35 + 35   | 5       | 5       | 192   |

| FEB          | 448 + 448 | 276 + 276 | 38      | 38      | 1524  |

| Calibration  | 32 + 32   | 28 + 28   | 5       | 5       | 130   |

| FECcont      | 32 + 32   | 24 + 24   | 5       | 5       | 122   |

| TBB          | 32 + 32   | 28 + 28   | -       | -       | 120   |

| TDB          | -         | -         | 5       | 5       | 10    |

Table 1. Components of the LArg partitions.

## 2.3.3 Timing and trigger control

The TTC system uses common ATLAS components and relies in particular on the optical fan-out system developed within the framework of RD12 [5]. Four 6U VME crates are used to implement the system, where up to two partitions are implemented in a single crate. The signal flow between the FE, BE and TTC systems is illustrated in figure 6. Each TTC partition contains:

- a CPU,

- a local Trigger Processor (LTP), responsible for transmitting either the ATLAS global timing and trigger signals or locally generated timing and trigger signals (e.g. calibration is done in local mode) to the the TTCvi and TTCex modules (see two items down),

- a ROD-Busy-Module. It receives from the TBM the combined result of all the ROD Busy signals of each ROD crate, and then delivers a partition wide Busy signal via the LTP to the Central Trigger Processor (CTP), which then throttles the trigger rate.

- TTCvi (TTC VME bus interface) and TTCex (TTC Encoder/Transmitter) modules [5]. The TTCvi encodes the TTC signals on two channels, one reserved for the L1A, the other for the LHC machine signals and various commands used by the system. These two signals are then sent to the TTCex, which merges them and performs the electrical to optical conversion. The optical signal is sent to the ROD crates and the FECs using optical fan-out modules, where it is electrically distributed to each relevant board.

One TTC link per ROD crate is needed, as well as two per half FEC for redundancy: in case of fibre or receiver failure, the second fibre is cabled replacing the previously connected one.

The LArg readout elements need the bunch-crossing signal (BC clock) from the LHC machine and the Level-1 accept signal (L1A) from the trigger system. The 40.08 MHz BC clock has to be precisely in phase, with minimal jitter, with the time of the crossings to benefit from the good timing characteristics of the calorimeters (better than 50 ps at high energy [1]). In addition, to synchronize all the readout elements, the LHC provides once per turn the Bunch Counter Reset signal (BCR) used to reset the Bunch Counter Identifier (BCID) in each readout element at a fixed time within the LHC cycle. The pre-defined LHC bunch structure will repeat itself every turn (every 88.924  $\mu$ s, which is equivalent to 3557 bunch crossings).

Processing prompt data from calorimeters and muon chambers, the CTP delivers a L1A signal to trigger the readout of events which fulfill a set of basic criteria, those which are most likely to contain interesting physics. Counting these L1A signals gives the Event Identifier (EVTID). This counter is synchronously reset by the Event Counter Reset (ECR) signal. Finally for each trigger, the CTP provides an 8-bit word to identify the type of trigger (physics, calibration,etc.). In addition, for testing and calibration purposes, a prepulse can be issued a pre-defined number of clock cycles before a calibration trigger is generated.

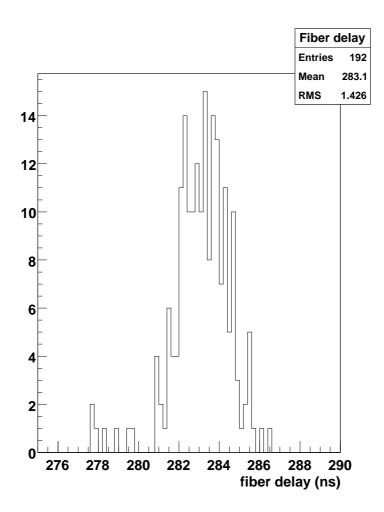

The trigger latency, which is the delay between the bunch crossing time and the time when the L1A signal arrives to the FE electronics, has been minimized to a value below 2.5  $\mu$ s. The TTC rack location has been chosen to minimize the length of the TTC fibres to the FECs and the associated contribution to the trigger latency. Figure 7 shows the measured delays in these fibres where an r.m.s. of 1.4 ns is observed. The precision of each measurement is better than 100 ps. The spread will be taken into account by programming a delay in a TTCrx [5] chip which receives the TTC signal in each of the FEBs. In addition, the programmable delay lines of the calibration boards are preset to reproduce the timing of signals generated by particles originating from the interaction point.

### 2.3.4 Level-1 receiver system

The receiver system is part of the trigger sum chain and interfaces the TBBs/TDBs to the calorimeter Level-1 processor. One function of the trigger sum chain is to convert the signal from energy to transverse energy. The final gain adjustment is left to the receiver, which must also account for attenuation in the cable between the TBB/TDB and the USA15 cavern. Because of the need for a continuously variable gain over a relatively small range, a stage of programmable gain is included in the receiver module. Level-1 requires the trigger sums to be grouped in  $\Delta \eta \times \Delta \phi$  bins and this is done via a daughter remapping board located on each receiver module. Finally the system can select any raw trigger sum signals for diagnostic tests using special monitoring modules located in the receiver crates.

The receiver chain consists of four op-amps: the first two are located on a 16-channel variable gain amplifier daughterboard, the third performs an RC integration and the fourth is a driver circuit which sends signals to the Level-1 calorimeter processor. Each receiver module services 64 channels, along with circuitry to select channels for monitoring purposes. A detailed description of the functionality of the receiver system is given in reference [6].

Each receiver crate contains 16 receiver modules, two monitoring modules, and one controller module. The crate is a standard 9U with a custom backplane, which is used to transport both the digital signals between the controller and the other modules, as well as the analog monitoring

**Figure 7.** Measured time delays (in ns) of signal travelling in the TTC fibres which link the TTC rack to the FECs. The precision of each measurement is better than 100 ps. The r.m.s. of the distribution is 1.4 ns.

signals. The LAr system consists of 6 receiver crates: 2 for the EMB, 2 for the EMECs and 2 for the FCAL and HEC. Two additional crates are for the Tile calorimeters.

The TBB receiver system cabling is described in detail in reference [7]. There are two receiver crates per rack, such that the entire receiver system occupies four racks.

### 3. LArg Back End electronics description

In the following sections, the ROD crate and its components are described in detail.

### 3.1 VME crate

The ROD crates are 21 slot Wiener 9U VME64x crates (Type UEV 6021-LHC9U-VME) for 9U VME cards with a remote water-cooled power supply [8]. Each crate measures 532.6 mm in height, 431.8 mm in width and is 720.0 mm deep. The crates are mounted in standard 52U LHC racks and contain: 1 CPU, between 6 and 14 RODs, 1 TBM, 2 SPAC Masters, a custom made CP3 backplane, and 6 to 14 TMs, according to the number of RODs.

Figure 8. Schematic top view of the ROD crate showing the locations of the various components.

The VME CPU, a Concurrent Technologies VP110 board [9], is installed in the first of the four 6U slots of the ROD crate. During system tests, the timing and trigger modules TTCvi and TTCex can be connected in the other 6U slots. Figure 8 illustrates a schematic top view of the ROD crate, where the locations of the various components are explicitly shown.

### 3.1.1 Power supply

The remote power supply unit (PSU) is mounted on the back of the rack and is water cooled. A drop-less coupling system ensures a leak-less connection even if the system is working at over pressure (5-6 bar). The power is supplied to the crate via a low inductance 50 cm long cable, to achieve low noise conditions for the fast-switching electronic devices [10].

The crate is supplied with the following voltages: +5V, +12V, -12V, +3.3V and +48V. The main consumers are the RODs and TMs. If there are 14 of each in a crate, currents of 73A at 5V, 50A at 3.3V and 7.5A at 48V are reached. The total power delivered by the PSU is about 900W.

The temperature of the VME power supplies are monitored with probes mounted on the power modules. Over-heating of the PSU can be caused by an interruption of the cooling water system in the ATLAS cavern, in which case the crates are shut down.

#### 3.1.2 Air and water cooling of the electronics

The electronics boards installed in the VME crates are cooled by air which flows in a closed circuit inside the rack. The air is cooled by heat exchangers installed above each ROD crate. Temperature probes mounted inside the crates above the RODs measure the air temperature. In case of overheating, the speed of the cooling fans below the boards is increased.

The ROD G-link HDMP-1024 chips require special water cooling to operate reliably at 80 MHz; the chip has to be kept below 35°C [11]. A cooling plate is mounted on the 8 G-link

**Figure 9.** A side view of a ROD board inserted into a crate, where the water and air cooling can be seen. Air fans are shown below the boards, whereas the water cooling plate for the G-links and the associated pipes are shown on the left-hand side of the board. One can also see the P1, P2 and P3 connectors on the right-hand side of the board, respectively from top to bottom.

chips, as shown in figure 9. Flexible water pipes are connected on the front-plate of the ROD with a drop-less coupling system. The water is distributed to each board by a 1U distribution unit.

To prevent water leaking into the electronics system, the cooling circuit is operated at a pressure which is between 300 and 400 mbar lower than the air pressure in the counting room. The cooling unit uses demineralized water, cooled down by the primary water system installed in the ATLAS cavern. The power to be dissipated from the G-links of all 192 ROD boards is about 2300 W, well below the maximum cooling power of 3860 W of the cooling unit. The plant is operated at a secondary circuit water temperature of +20°C and at a flow rate of 1.1m<sup>3</sup>/h with a maximum differential pressure of 2 bar [12]. One main distribution line connects the seven ROD racks in parallel, and serves the 17 water distributors mounted above the ROD and the Injector crates. The G-link chip temperatures are approximately 28°C in a stable ROD processing mode.

### 3.1.3 Detector Control System (DCS)

In addition to hardware control of the VME crates and the ROD cooling unit, the status of the BE electronics is continuously supervised by a software-based detector control system (DCS) [13]. The DCS checks in given time intervals the voltages, currents and temperatures measured inside the VME crate and its power supply. It also receives temperature, pressure and flow information from the ROD cooling station. The DCS software transmits warnings and alarms issued by the VME crate and cooling unit hardware controllers. It can also raise warnings and alarms by itself if certain parameters exceed pre-defined limits. One example is the monitoring of the temperature on the VME power supply, which should not exceed a certain limit to prevent a hazardous automatic shut-down of the VME power. This temperature alarm may be raised e.g. in case of a failure of the primary cooling system.

Figure 10. Front side of the CP3 board and point-to-point connections between the TBM and the ROD modules.

The information about the BE system is further transmitted to DCS components which supervise the status of the complete ATLAS calorimeter hardware and eventually the status of the whole ATLAS detector.

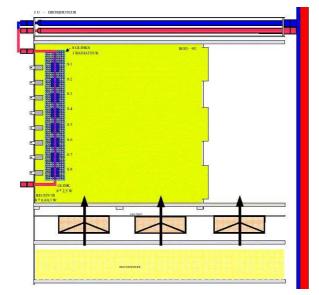

### 3.1.4 Crate backplane and CP3 board

The VME crate is equipped with the standard VME64 backplane supporting the 160-pin P1 and P2 connectors. This VME backplane is extended at the bottom by a custom made backplane, the CP3, supporting additional P3 connectors of the same type. The TM modules (see section 3.6) are situated at the rear of the crate while all the other electronics modules are inserted at the front.

The CP3 card is a passive printed circuit that links the TBM (see section 3.3) to the RODs (see section 3.4). It ensures the distribution of the TTC signals and the collection of the ROD Busy signals over point-to-point connections between the TBM slot number 5, and the ROD slots 6 to 21. It is capable of carrying the high speed digital TTC signals with minimal distortion, reflection, or cross talk. This requirement has been satisfied by the following implementations:

- Fast and low jitter Low Voltage Differential Signal (LVDS) chipset.

- A printed circuit with differential signal paths of  $100 \Omega \pm 10\%$  characteristic impedance. All the paths have a controlled impedance of  $50 \Omega$ . The two lines of a differential pair are routed on the same layer. They are equidistant and of same length.

For simplicity, and because they are less time critical, the ROD Busy signals run on 50  $\Omega$  single ended transmission lines. Figure 10 shows the front side of the CP3 and the point-to-point connections.

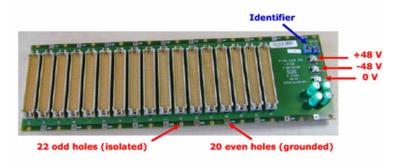

Each CP3 has a unique identifier defined by two rotary switches. This identifier is readable by the TBM from its P3 connector. In addition, the CP3 includes a few service lines that allow to read the TM identifiers through the TBM. In this manner, the TMs situated at the rear of the crates,

Figure 11. Rear side of the CP3 board and electrical connections.

as well as the ROD crates with their associated CP3 cards, can be identified by VME through the TBM, simplifying maintenance.

The CP3 also distributes the electrical power to the TMs. The floating 48 V voltage used by the TMs is brought from the VME backplane by means of two cables attached to the two upper taps situated on the CP3. The third tap, at the bottom, is used to connect the rack and CP3 ground connections. The CP3 is fastened onto the crate using 20 electrically grounded screws. Figure 11 shows the rear side of the CP3 and the electrical connections.

The CP3 measures 424.23 mm in width, 128.78 mm in height and is 4.64 mm thick. The VME64 connectors and the power taps have been inserted into the thick printed circuit without any soldering. The CP3 contains 3 signal layers and 5 equi-potential planes (see reference [14] for a detailed description of the CP3).

### 3.2 SPAC Master module

The SPAC Master 9U VME module is dedicated to the configuration of the FE electronics. There are two such modules per ROD crate but they are independent of the other crate boards, which are devoted to the data acquisition and are intensely active during physics or calibration runs. The SPAC Master modules are mainly solicited during the configuration phase, to properly set up the various FE system boards (FEBs, Calibration boards, TBBs, FECcont boards).

### 3.2.1 Description and functionalities of the module

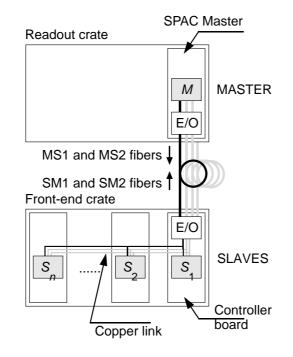

The SPAC Master Module is optically connected to a FECcont board that redirects the requested READ/WRITE requests to the various boards populating the FECs. The data are then transmitted from their host board to the SPAC Master board through the FECcont that handles the electrical to optical conversion. Figure 12 shows this architecture. In the FEC, signals are transmitted to the FEBs using a dedicated copper bus. The MS1,2,SM1,2 (Master-Slave line, Slave-Master line) fibres denoted on the figure are the four optical connections shared by a SPAC Master board and a FECcont.

The data transmission between the SPAC Master board and a FECcont is done through a serial link using a protocol developed specifically for the ATLAS calorimeters (see reference [15] for more details). The data are transmitted at a nominal rate of approximately 10 Mbits/s.

**Figure 12.** Functional layout of the SPAC configuration link showing the MS1,2,SM1,2 (Master-Slave, Slave-Master) optical connections shared by a SPAC Master board and a FECcont.  $S_1, ..., S_n$  are the SPAC Slave circuits which equip each FEB to implement the SPAC link. The E/O indicates where the electrical to optical conversions are performed.

The SPAC Master - FECcont data exchange is a key issue of the whole system, which cannot be configured without it. Hence the reliability is increased by doubling the SPAC links between a SPAC Master and a FECcont. Consequently, the FECcont implements 2 Slave circuits in a special configuration allowing data transmission even if one of them fails. Nevertheless, only one pair of SM-MS links is used according to a configuration bit in the SPAC Master Control word and in each FECcont Slave ASIC. In addition the SPAC Slave has been designed in such a way that if it fails, it should still be able to transmit the signals to the SPAC copper bus delivering electrical SPAC signals to the FEBs.

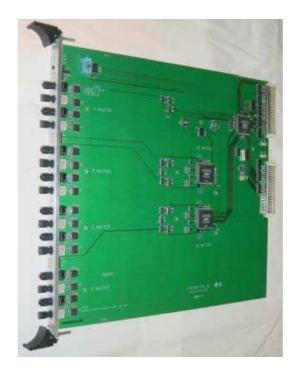

Each ROD crate contains 2 SPAC Master modules. Each board is equipped with 4 independent SPAC links to a FECcont. It has 8 optical transmitters and 8 optical receivers: 4 transmitters or receivers are used, while the 4 others are spares for reliability purposes. Each optical connection is unidirectional. A SPAC Master board is shown in figure 13, and its functional layout in figure 14 shows that 2 Master interfaces are implemented in a single Altera ACEX EP1K50 Field Programmable Gate Array (FPGA).

### 3.2.2 SPAC protocol and Slave ASIC

The SPAC protocol is a Master/Slave based protocol implementing a serial connection between one master and possibly multiple slaves (see reference [15] for a detailed description). Each FEC board requiring an online configuration is equipped with a dedicated on-board SPAC Slave interface ASIC which communicates to the SPAC Master board through the FECcont board. Whereas this chip is used in a standard slave mode on all the FEBs, it is used on the FECcont with a different

Figure 13. Photograph of a SPAC Master board equipped with 4 SPAC links.

**Figure 14.** Functional layout of the SPAC Master board. Two Master interfaces are implemented in a single Altera ACEX EP1K50 Field Programmable Gate Array (FPGA).

configuration (repeater mode) to allow SPAC frames transmission from/to the FECcont slave ASIC to/from the various FEBs slave ASICs.

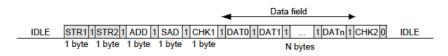

Figure 15. Data format of a SPAC transaction between SPAC Master and SPAC Slave.

The data transmission through the SPAC links is done using a Manchester encoding scheme [16] which increases the noise immunity of the transmission. The convention used is the following:

- a logical 1 is coded by a low to high transition (i.e. 50ns low, 50ns high at 10 Mbits/s);

- a logical 0 is coded by a high to low transition (i.e. 50ns high, 50ns low at 10 Mbits/s).

The system is formed of optical links operating at different wavelengths in order to benefit from existing qualified radiation hard components. The transmission through the MS links is done using 850nm transmitters on the SPAC Master whereas the SM links are implemented using 1310 nm transmitters on the FECcont. The SPAC Master module transmitters and receivers are off-the-shelf components, while those located on the FECcont are qualified for their tolerance to radiations.

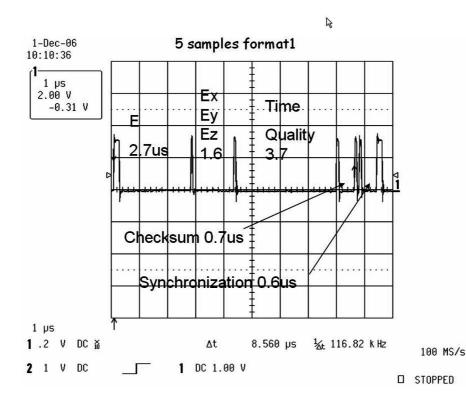

The data are transmitted in 9-bit words composed of a byte of useful data and a Continue/Last bit (logical 0 for the value Last). The data transmission format is described in figure 15. A SPAC frame consists of the following:

- A preamble string sent at the beginning of each data frame to restore a correct electrical level on the differential electrical or optical receivers on the receiving side (see STR1-STR2 in figure 15) which leads to very good transmission.

- The address of the SPAC Slave to which the SPAC frame is issued (ADD).

- The SPAC address of the on-board resources to which the SPAC frame is issued (SAD).

- A first checksum (CHK1) word which allows detection of badly transmitted addresses.

- The data words to be transmitted to the recipient (DAT1-n).

- A second checksum (CHK2) which tests the data integrity and can correct badly transmitted data with 1 or 2 bits flipped during transmission.

If a slave does not answer to a READ request, a configurable software timeout is generated by the online software. If a slave receives a bad frame (either a bad checksum or a frame inconsistency), it emits a SPAC interrupt to the Master and a flag is set in its internal Slave Status Register. The SPAC Master which receives the interrupt sets a flag in its status register.

While the slave modules use the LHC 40.08 MHz clock as a fundamental clock to transmit and receive the serial data, the SPAC Master modules use local 40 MHz oscillators as reference clocks. In the master device FPGA, the receiving SPAC data are sampled on the rising edge and on the falling edge of the local 40 MHz clocks and the transitions on the Manchester-encoded data are detected to recover the relevant information.

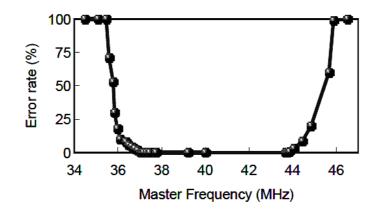

**Figure 16.** Transmission error rate in a SPAC link as a function of the SPAC Master FPGA frequency when the connected SPAC Slave ASIC is clocked with a 40 MHz signal. This shows that the system can easily tolerate a 2 MHz frequency misalignment.

| Power supply | Consumption | Fuse value |

|--------------|-------------|------------|

| 5 V          | <3 A        | 5 A        |

| 3.3 V        | 250 mA      | 500 mA     |

Table 2. Power consumption of the SPAC module.

The clocks on the SPAC Master board and on the Slave ASICs can be asynchronous and even have a small discrepancy in frequency. Figure 16 shows the error rate as a function of the frequency of the SPAC Master FPGA when the connected SPAC Slave ASIC is clocked with a 40 MHz signal. This shows that the system easily tolerates a 2 MHz frequency misalignment. The actual system will use very similar frequencies at both ends: 40 MHz from a crystal on the SPAC Master Board and the LHC clock on the FEBs.

### 3.2.3 SPAC interface

The SPAC Master allows one to use all the possible interfaces implemented on the SPAC Slave ASIC, which can access on-board resources (memory or registers [17]) through either a parallel interface or two Inter-Integrated-Circuit (I2C) links. In the first case, the command is directly interpreted and executed on the slave parallel interface. In the second case, the I2C command is built and put in a dedicated ASIC memory of the SPAC Slave; the SPAC Master then orders the SPAC Slave to issue this I2C command. Hence an I2C command requires at least one or more extra SPAC Master VME transactions with respect to writing/reading through the parallel interface. The SPAC Master Board is equipped with emission/reception First-In-First-Out's (FIFOs) which are used either to build the SPAC commands or to read back the expected information using VME transactions to the SPAC Master module.

### 3.2.4 Power consumption, power and reset procedures

The SPAC Master module has a power consumption of 15 W when SPAC transactions occur at the maximum SPAC link bandwidth. The electrical consumption is detailed in table 2. Four fuse carriers are mounted on the board and host two spare fuses of each type (5 A and 500 mA fuses).

Figure 17. Photograph of the TBM module.

At initialization, the VME interface reads the geographical address of the slot where the board sits and uses it to define the base address of the module. FIFOs are emptied and optical transmitters are idle. The RESET procedure has the same characteristics as the POWER-ON except that the VME interface is not reinitialized.

## 3.2.5 SPAC design and manufacturing

The SPAC Master module has 2 male right angle VME64x connectors. The Printed Circuit Board (PCB) measures 400 mm in height, 366 mm in depth and is 1.6 mm thick. The board is composed of eight layers: four signal layers and four ground and power layers. Thirty five modules were produced and tested: 31 used by the experiment and 4 spares. The full production of the boards was performed by a unique vendor and included PCB manufacturing, sub-contracting, procurement of the components, assembly, burn-in sequences, flying probe tests, front panel production and mounting. Functional tests were then performed on reception of all the boards: the four SPAC links of each module were connected to FECcont boards to check for errorless communication in any optical fibre configuration, and the optical power of the transmitters on the SPAC master modules was also measured and stored into a production database.

## 3.3 TTC and Busy module (TBM)

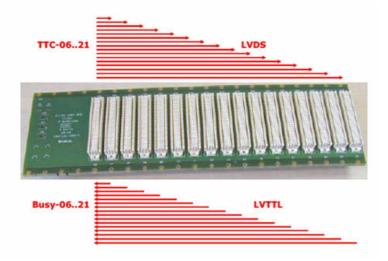

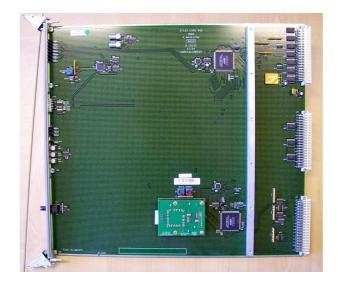

The TBM module distributes the TTC signals and collects the Busy signals inside each ROD crate (see reference [18] for more details), where it sits in slot number 5. Figure 17 shows a photograph of a module.

## 3.3.1 Timing, Trigger and Control distribution

The TBM receives signals from the TTC system via an optical fibre, with a TRR-1B43 optical receiver from TrueLight. The receiver converts the TTC optical signal into an electrical differential signal (LVDS). To set with a minimum amount of distortion a known inactive state on the TTC

lines, a slight bias is introduced between the positive and the negative inputs of the first electrical buffer. The TBM then duplicates the LVDS TTC signal and distributes it to each ROD module through the P3 connector, using point-to-point connections on the CP3 board.

At the receiving end on a ROD module, a pair of lines of 100  $\Omega$  differential characteristic impedance is ended by a 100  $\Omega$  resistor. If the slot is empty, the corresponding TTC signal is absent, due to the absence of the terminating resistor which is necessary to close the driver current loop.

While the TTC signal is electrically transmitted to the RODs, a copy of the TTC signal enters a TTCM mezzanine card [18] situated on the TBM, where a TTCrx chip decodes it. If the TTCrx ready-flag is false i.e. missing TTC signal, an interrupt is generated to warn the VME crate controller. The state of this flag is also visible on the TBM front panel. The TBM can be programmed to count the Level-1 triggers and to generate an interrupt after a pre-defined number of triggers. During calibration runs, the Busy signal is used in conjunction with this trigger count, in order to synchronize the data taking of all the sub-detector channels.

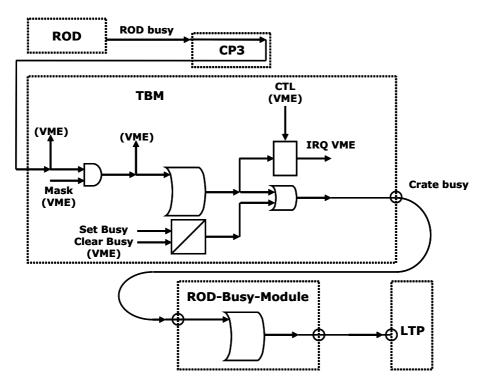

### 3.3.2 Busy collection

The TBM, which receives the ROD Busy signals from the P3 connector, enables or disables each of them according to a dedicated mask register, then makes a logical OR out of them to create the Crate-Busy signal. This signal is sent through a coaxial cable to the ROD-Busy-Module, which is situated in the TTC crate [19]. This module has 16 coaxial inputs and outputs their logical OR. The TBM also implements control and monitoring functions on the input signals.

The logic associated in the TBM with the Busy signals is contained in an FPGA, in conjunction with another FPGA dedicated to the VME interface (both FPGAs are ACEX EP1K50QC208-2 from Altera). The TBM can be programmed to generate a VME interrupt when the first ROD Busy signal arrives, as well as when all the ROD Busy signals disappear. A schematic view of Busy signal logic is shown in figure 18.

The Low Voltage Complementary metal-oxide-semiconductor (LVCMOS) Busy signals are active in the high logic state. Pull-down resistors (10 k $\Omega$ ) at the input of the TBM cause the empty slot lines to be inactive. The Busy lines on the CP3 board are long and consequently sensitive to reflections, and hence have a controlled 50  $\Omega$  characteristic impedance. Reflections are avoided by using a small resistor placed in series at the ROD side, thus absorbing the reflected wave.

After they have entered the TBM, the ROD Busy signals are individually masked or enabled. They can be read as they are at their inputs on the P3 connector or after the mask. In order to prevent unwanted triggers, the Crate-Busy signal is set ON at power-up or when the TBM is reset.

#### 3.3.3 Control outputs

The front panel Crate-Busy signal is available from a coaxial LEMO type connector. A second identical LEMO output is available for scope monitoring and a third one is under the control of Set and Clear VME commands. The first LEMO cable is used to connect the TBM to one of the 16 inputs of the ROD-Busy-Module. The 3 LEMO Control outputs are driven by 3 separate outputs of the Busy FPGA with 50  $\Omega$  resistors in series to prevent reflections.

**Figure 18.** The ROD Busy signals are collected by the TBMs and the ROD-Busy-Modules before being transmitted to the Trigger Processor.

### 3.3.4 VME interface

The TBM is connected to the VME-bus and has four interrupt sources: an end of calibration sequence (when a pre-defined number of Level-1 triggers has been reached), the first enabled ROD Busy ON, the last enabled ROD Busy OFF, and a lost TTC clock. The core of the VME interface is common to all LArg ROD boards. The registers that are specific to the TBM are implemented in its Busy FPGA. The low part of the VME address is transmitted by the VME FPGA to the Busy FPGA, allowing the commands that are dedicated to the TBM to be interpreted and executed in the Busy FPGA.

#### 3.3.5 Power, reset and ESD considerations

The TBM current consumption is 0.5 A on the +5 V and 0.6 A on the +3.3 V. Re-triggerable variable resistors are used as fuses. When the power is set on, the on-board logic is reset and the FPGAs automatically configure themselves in less than 1 second. To protect against hazardous electrostatic discharges (ESD), two copper strips establish a connection to ground through 2 M $\Omega$  resistors when the board is inserted into the crate.

### 3.3.6 TBM design and manufacturing

The TBM module has 3 male right angle VME64x connectors. It measures 400.05 mm in height, 360 mm in depth and is 2 mm thick. The top and bottom parts which slide into the VME crate rails are only 1.6 mm thick.

Many paths between integrated circuits on the board are longer than ten centimeters, and care has been taken to avoid parasitic reflections. The PCB of the TBM contains 3 signal layers and 5 equi-potential planes, and the same care has been taken for the routing of signals as for the CP3 (see section 3.1.4).

For the long unipolar paths, either a parallel or a series impedance matching has been implemented. The parallel matching is made of a Thévenin network placed at the end. The series matching is made of a 50  $\Omega$  resistor placed at the driver side. These matchings are used between the VME FPGA and the Busy FPGA. It was verified that pulses as short as 15 ns are correctly transmitted, while no matching is necessary for pulses beyond 100 ns.

Due to its large dimensions, the board is subject to mechanical distortions. When it is plugged into the VME crate, the board is maintained horizontally straight by the top and bottom rails of the cage. To avoid vertical distortions, a metal bar is screwed onto the board, near the VME connectors.

### 3.4 ROD module

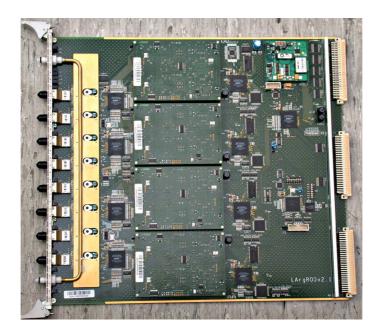

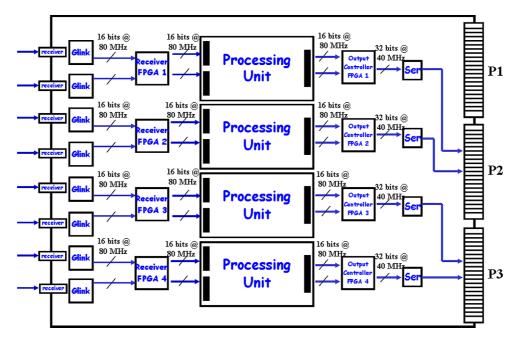

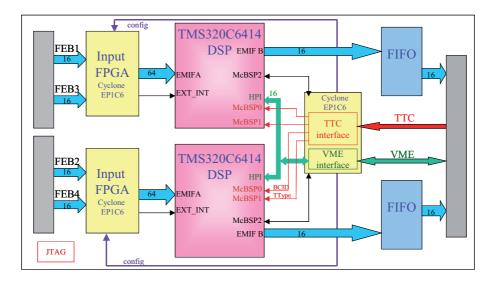

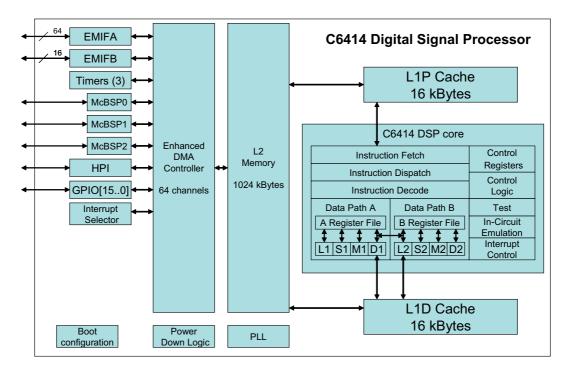

The Read Out Driver is at the core of the off-detector data processing. Each ROD module receives the digitized raw data from 8 FEBs through 8 optical fibres. This corresponds to 1024 (8  $\times$  128 channels/FEB) detector cells being read out. The module is composed of a ROD motherboard, equipped with 4 Processing Units (PUs) placed on separate daughterboards, each housing 2 Digital Signal Processors (DSPs). High performance plug-in DSPs are chosen to achieve an average processing time per event of less than  $\sim$  12  $\mu$ s, as required by the 75 kHz Level-1 trigger rate.

The ROD processes the data and sends the results of the DSP optimal filtering calculations (see section 2.3.1) to the TM installed at the back of the VME crate. When the ROD cannot output data towards the TM, it sends a Busy signal which paces the Level-1 trigger. For monitoring purposes, output data can also be sent to a Synchronous Dynamic Random Access Memory (SDRAM), where they are read out through the VME interface.

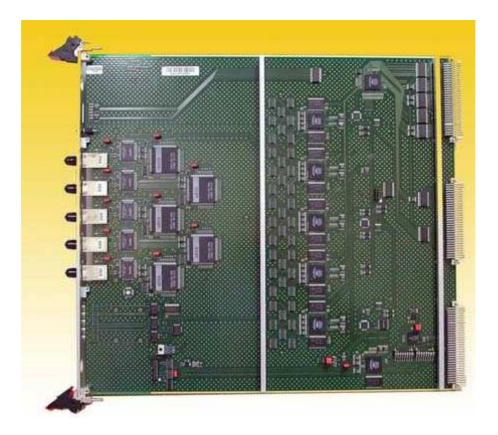

The LArg detectors are read out using 192 ROD modules. A photograph of a ROD board is shown in figure 19. RODs are also used for the ATLAS Tile calorimeter readout.

### 3.4.1 FEB data input

Data from one FEB are sent to a ROD through the 1.6 Gbit/s G-link optical link which encodes data from the 16 FE ADCs (128 calorimeter channels).

As shown in figure 20, the ADC event fragment format consists of the following 16-bit words: a frame-start word (all ones), two event header words, data words carrying the calorimeter signal data, an event trailer word, and at least one frame-end word to separate the next event (all zeros). For all words except the start and end of event, bit 14 is used as a parity bit to impose odd parity. More details about the FEB output data format are given in reference [20].

Data from each ADC are encoded on the FEB on a two-bit 40.08 MHz serial data bus. The even (odd) bits are transmitted on the 0 (1) output bit line with the most significant bit first. The resulting 32 bits at 40.08 MHz corresponding to the 16 ADCs are multiplexed in a custom made multiplexer component, the SMUX [21]. It was developed according to a 2:1 multiplexing in order to generate a stream of 16 bits at 80.16 MHz at the output of the FEB. In addition, the SMUX generates a flag which is set to 1 (0) for the multiplexer cycle when data from channels 0-63 (64-127) are sent. These 16 bits are then serialized by the HDMP 1022 G-link chip on the FEB.

**Figure 19.** Photograph of a ROD motherboard equipped with four processing units. The 8 optical receivers (see section 3.4.1) and the G-link cooling plate are clearly visible on the left-hand side of the board.

|                   | B15 | B14 | B13 | B12 | B11                       | B10 | B9  | <b>B8</b>      | <b>B</b> 7 | B6    | B5      | B4     | B3 | B2 | B1 | <b>B</b> 0 |

|-------------------|-----|-----|-----|-----|---------------------------|-----|-----|----------------|------------|-------|---------|--------|----|----|----|------------|

| W1                | 1   | 1   | 1   | 1   | 1                         | 1   | 1   | 1              | 1          | 1     | 1       | 1      | 1  | 1  | 1  | 1          |

| W2 : ctrl1        | 0   | Р   | 0   | 0   |                           | AD  | CID | D PHASE EVENTN |            |       |         |        |    |    |    |            |

| W3: ctrl2         | 0   | Р   | 0   | 0   |                           |     |     |                |            | BC    | D       |        |    |    |    |            |

| W4 : radd         | 0   | Р   | 0   | 0   | F                         | L   | В   | Α              |            |       |         | CEL    | LN |    |    |            |

| W5                | 0   | Р   | Ga  | ain |                           |     |     |                | ADC c      | hanne | l 0 san | ple 1  |    |    |    |            |

| W6                | 0   | Р   | Ga  | ain |                           |     |     |                | ADC c      | hanne | l 1 san | iple 1 |    |    |    |            |

| W7                | 0   | Р   | Ga  | ain |                           |     |     |                | ADC c      | hanne | l 2 sam | ple 1  |    |    |    |            |

| W8                | 0   | Р   | Ga  | ain |                           |     |     |                | ADC c      | hanne | l 3 san | ple 1  |    |    |    |            |

| W9                | 0   | Р   | G   | ain | ADC channel 4 sample 1    |     |     |                |            |       |         |        |    |    |    |            |

| W10               | 0   | Р   | G   | ain | ADC channel 5 sample 1    |     |     |                |            |       |         |        |    |    |    |            |

| W11               | 0   | Р   | G   | ain | ADC channel 6 sample 1    |     |     |                |            |       |         |        |    |    |    |            |

| W12               | 0   | Р   | G   | ain | ADC channel 7 sample 1    |     |     |                |            |       |         |        |    |    |    |            |

|                   |     |     |     |     |                           |     |     |                |            |       |         |        |    |    |    |            |

|                   |     |     |     |     |                           |     |     |                |            |       |         |        |    |    |    |            |

| WEVT-10<br>: radd | 0   | Р   | 0   | 0   | F                         | L   | В   | A CELLN        |            |       |         |        |    |    |    |            |

| WEVT-9            | 0   | Р   | Ga  | ain | ADC channel 0 last sample |     |     |                |            |       |         |        |    |    |    |            |

|                   |     |     |     |     |                           |     |     |                |            |       |         |        |    |    |    |            |

| WEVT-2            | 0   | Р   | G   | ain | ADC channel 7 last sample |     |     |                |            |       |         |        |    |    |    |            |

| WEVT-1 :<br>ctrl3 | 0   | Р   | 0   | 0   | 1                         | S   | Е   | SCAC status 1  |            |       |         |        |    |    |    |            |

| WEVT              | 0   | 0   | 0   | 0   | 0                         | 0   | 0   | 0              | 0          | 0     | 0       | 0      | 0  | 0  | 0  | 0          |

Figure 20. Event format at the input of the PU.

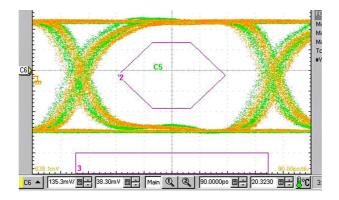

**Optical receiver and link.** Serial data from the FEBs are received by the ROD motherboard through eight optical receivers, the ORx. These are custom made devices and provide the optical to electrical conversion of the data. To reach the desired sensitivity (-17 dBm), special care was taken for the packaging and electrical filtering. The receivers can be seen in figure 19 on the left-hand side of the ROD board. Figure 21 shows the ORx eye pattern diagram, illustrating the high quality

**Figure 21.** Eye pattern diagram of an ORx chip. Entries inside the marked fiducial region provide a measure of the bit error rate, while the widths of the rise and fall lines represent effects of the timing jitter.

of the 1.6 Gbit/s transmission. Details of the ORx are given in reference [22].

The incoming data are deserialized by Agilent HDMP-1024 G-link chips and transmitted in 16-bit words to the receiver FPGAs. The HDMP-1024 chip allows one to reconstruct parallel FEB data as they were loaded into the HDMP-1022 transmitter chip located on the FEB. The chip set hides all the complexity of encoding, multiplexing, clock extraction, demultiplexing and decoding. An external quartz crystal provides an 80.16 MHz clock reference to the G-link chip, allowing the component to lock on the incoming data.

The G-link indicates the status of the optical link to the receiver FPGA by a link-ready bit. If the G-link loses the frame lock in the incoming data stream, it is set to 0 (false) and the G-link output data are composed of words with all bits set to 1.

**Receiver FPGA.** Four Altera EP1K100 receiver FPGAs are used on the ROD motherboard. The incoming data of two different G-link chips are sent to one receiver FPGA, which routes the data further to the PUs. In normal working mode, the data of one receiver FPGA are transferred to one PU. This is shown in figure 22.

In the so called staging mode, a PU receives the data from two FPGAs which are linked by a special data bus. The staging mode, with half the processors installed, allows for a ROD system with a reduced number of input links to the DAQ. This mode is used by the Tile calorimeter readout which has a less demanding processing power, since there are only 32 to 45 readout channels per FEB as compared to the 128 channels for the LArg calorimeters.

Data from each receiver FPGA are sent to the PU through a data bus, running at 80.16 MHz. FEB data are synchronized in the receiver FPGA using an 80.16 MHz clock made by an on-board Phase Lock Loop (PLL) chip and the 40.08 MHz TTC clock signal. In this way, the ROD data are synchronized with the LHC clock and not with the external G-link reference quartz clock.

In total, 18 bits are transmitted to the PU per FEB: 16 bits of data, the flag signal to distinguish data from channels 0-63 or 64-127, and the link-ready signal indicating if the G-link has lost the frame lock. In this case, the receiver FPGA does not transfer the incoming data to the PU.

In order to test the ROD board in stand-alone mode i.e. without optical data injection, an additional functionality has been added in the receiver FPGA. The embedded memory can be used to store a maximum of 1024 32-bit words (corresponding to one 5 sample FEB event). The simulated

Figure 22. Data distribution on the ROD board in normal mode, using all PUs and S-links.

Figure 23. Schematic view of the communication protocol between the TTC FPGA and the PUs.

event can be sent either a finite number of times or in a continuous loop to the PU, with the possibility to adjust the delay between events. The same event is duplicated and sent to both inputs of the PU, to simulate the arrival of data from two FEBs.

### 3.4.2 TTC data input

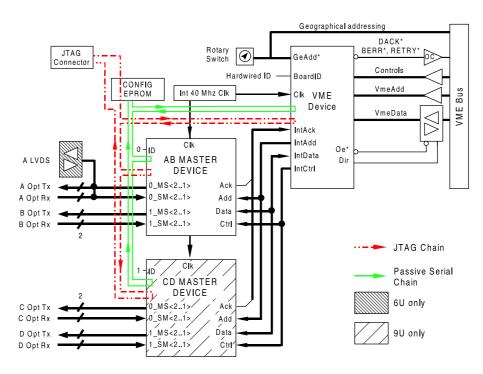

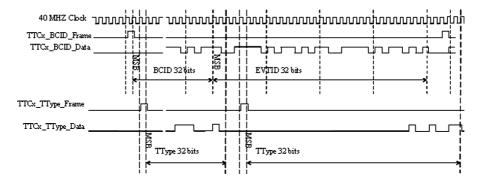

The TTC signal from the CP3 is received by the TTCrx chip which decodes it and sends the resulting signals to the TTC FPGA. The FPGA receives the Trigger Type information and the BC, BCR and ECR signals. It calculates the BCID and EVTID and then distributes all information to the PU through point-to-point connections. Figure 23 shows the communication protocol between the TTC FPGA and the PUs.

The TTC FPGA sends the BCID, the EVTID and the Trigger Type using 5 lines: one 40 MHz synchronization clock, two frame lines which define the beginning of an element transfer, and two serial lines for the data transmission. One frame line, with 2 phases of 32 bits, and one data line

Figure 24. Functional diagram of the Output Controller interfaces.

are used to transmit the 12-bit long BCID and the 32-bit long EVTID. The other frame line, with only one 32-bit phase, and data line are used to transmit the 8-bit Trigger Type.

Depending on the mode of operation, the clock is generated differently. During LHC running, the ROD board will receive the 40.08 MHz LHC clock from the CP3 backplane. In local or VME mode, the clock comes either from a local clock oscillator or from the Injector module (see section 3.7). The clock is distributed to each sub-module through point-to-point connections.

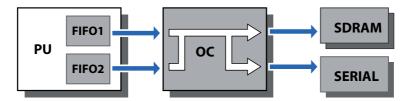

### 3.4.3 Output flow

The DSP 16-bit output data are stored in two FIFOs which are read by an Output Controller (OC). There are four OCs on a ROD module, one per PU. The OC reads the event fragments from the two DSP FIFOs and according to its configuration, outputs the data to the SDRAM and/or to the serializer chip. Figure 24 shows a functional diagram of the OC interfaces. The OC formats the event, including a header and a trailer according to the specifications given by the ATLAS DAQ group [23]. Table 3 shows the ROD event fragment format.

The OC reads the DSP FIFOs (16 bit wide) at 80 MHz and outputs 32-bit wide data at 40 MHz. FIFO data are stored according to the big-endian protocol, with the most significant word first. The protocol between the FIFOs and the OC is not based on the notion of event, but on data bunch, which can include a partial event or several events. The transfer from the FIFO is initiated by the OC as soon as the empty flag is false i.e. when the FIFO is no longer empty. The OC reads a 16-bit wide FIFO word at each rising edge of the 80 MHz clock, such that two clock periods are needed to obtain a 32-bit pattern.

The first 32-bit pattern contains the data bunch size, which can include a partial event or several events. The OC stores this value and decrements it at each new 32-bit word transferred. When the OC reaches the last word, it gives a 50 ns pulse on the Event End line, indicating to the PU that the whole data bunch is transferred. The first 32-bit pattern of an event contains its size: the number of 32-bit words in the current event, excluding itself but including the last word. The last word of the event must be 0xe0e000000. The OC verifies this and in case of an error, will set a flag in the status register and stop event transfers.

The OC always starts reading the FIFO associated to the first DSP of a PU (FIFO1), and then reads the second FIFO2. The event notion is kept: if the data bunch contains several events, they are read in one at a time, to let the OC format the ROD event fragment. A complete OC description is given in reference [24].

### **3.4.4 SDRAM**

The OC outputs the data to the SDRAM, and/or to the TM to send to the DAQ, or to both in the so

|          |      | Beginning of fragment (0xb0f00000)    |

|----------|------|---------------------------------------|

|          | OC   | Start of header marker (0xee1234ee)   |

| Header   |      | Header size (0x0000009)               |

|          |      | Number of Words of DSP1               |

|          | DSP1 | Format version (0x02040000)           |

|          |      | Source identifier                     |

|          |      | Run Number                            |

|          |      | Level 1 ID                            |

|          |      | Bunch crossing ID                     |

|          |      | Level 1 trigger type                  |

|          |      | Detector event type                   |

|          |      | Header event DSP1                     |

| Data and |      | Data                                  |

| status   |      | ÷                                     |

| elements |      | :                                     |

|          |      | End of event (0xe0e00000)             |

|          |      | Number of Words of DSP2               |

|          | DSP2 | Format version (0x02040000)           |

|          |      | Source identifier                     |

|          |      | Run Number                            |

|          |      | Level 1 ID                            |

|          |      | Bunch crossing ID                     |

|          |      | Level 1 trigger type                  |

|          |      | Detector event type                   |

|          |      | Header event DSP2                     |

|          |      | Data                                  |

|          |      |                                       |

|          |      | :                                     |

|          |      | End of event (0xe0e00000)             |

|          |      | Number of status elements (0x0000000) |

| Trailer  | OC   | Number of data elements               |

|          |      | (words DSP1 + words DSP2-9)           |

|          |      | Status block position (0x0000000)     |

|          |      | End of fragment (0xe0f00000)          |

**Table 3.** ROD event fragment format at the output of an output controller. The data words marked in *italic* are generated by the DSP but not sent in the event fragment.

called spy mode. The SDRAM mode allows one to read data through the VME bus and is mainly used for debugging purposes e.g. when the DAQ system is not available or for data consistency checks in the local CPU. The spy mode is mainly used during data acquisition, to check the quality of the incoming FEB data, without disturbing the DAQ data flow. In this mode, the data flow is

slowed down a little, since the SDRAM must be refreshed by the OC and synchronized with the serializer.

The spy mode is activated through VME, which also defines the number of words stored in the SDRAM. When the spy mode is enabled, the events are sent to the DAQ through the TM, and they are also stored in the SDRAM. When the SDRAM threshold is reached, the OC finishes copying the current event to the SDRAM and stops sending it data. From then on, the OC sends the events only to the DAQ and the SDRAM data can be read via VME without disturbing the TM event transfer. Once the SDRAM is emptied, the spy mode can be re-enabled.

The SDRAM is a 128 Mbit high speed DRAM. It is internally configured as a quad-bank DRAM with synchronous interface. Each bank is organized in 4096 rows  $\times$  256 columns  $\times$  32 bits. Read and write accesses to the SDRAM are burst oriented: accesses start at a selected address and continue for a programmed number of locations. The SDRAM is designed to operate at 3.3V and requires 4096 auto refresh cycles every 64 ms (at least one command every 15625  $\mu$ s).

The SDRAM status and control flags (enable, empty flag, full flag, etc.), as well as its READs, WRITEs and refreshing are handled by the OC.

### 3.4.5 Serializer

The output data are sent to the TM through the VME backplane (P2 and P3 connectors). Each ROD to TM channel uses one DS90CR483/484 serializer-deserializer chipset and is implemented in differential LVDS. This mechanism reduces the noise associated with the transmission. The chipset converts 48 bits of Transistor Transistor Logic (TTL) or Low Voltage TTL (LVTTL) level data into 8 LVDS data streams running at 240 MHz. The output of one OC consists in a 48-bit bus: 32 bits of data, 6 bits of control signals generated for the S-link, and 10 spare bits. The TM receives, deserializes and sends the data to the corresponding S-link mezzanine board.

A total of 14 LVDS pairs (28 pins) are required per OC in the P2 and P3 connectors: 8 pairs for data transmission to the TM, 5 pairs for return information and one pair for the ROD 40 MHz clock signal which is transmitted in parallel with the data streams. The 5 return bits from the S-link are the following: the Link Full flag indicating the Read Out System (ROS) is busy, the Link Down flag indicating the communication with the DAQ is no longer ensured, and the 3 Return Lines LR0, 1 and 2 from the ROS. These 5 signals are converted from LVDS to LVTTL level and sent to the corresponding OC FPGA for analysis.

A complete OC description is given in reference [24].

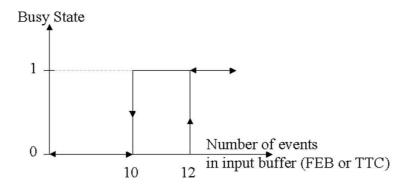

#### 3.4.6 Busy handling

The ROD module generates the Busy signal and sends it to the TBM through the CP3 board. There are 8 sources of Busy per ROD Module: one per DSP. Each source is individually maskable to isolate faulty or disconnected PUs. Busy signals are then logically *ORed* and a LED on the ROD front panel gives the status of the Busy. The status and duration of the Busy signals from each source are also available through VME. After a POWER-ON, the Busy output is forced to avoid incoming triggers during the initialization phase. For more details about the Busy module of the ROD board, see reference [25].

#### 3.4.7 VME interface and internal communication

The VME bus system consists of 4 sub-buses: the Data Transfer bus, the Arbitration bus, the Priority Interrupt bus and the Utility bus. Data transfer is asynchronous, supporting modules with a broad variety of response times. See reference [25] for more details on the VME bus system.

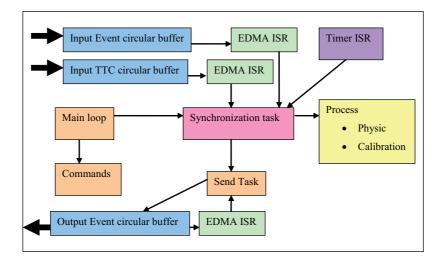

An adjustable timeout is implemented in the ROD module and if it is reached, the ROD sends a Bus ERror (BERR) signal to the VME bus. This timeout is adjustable up to 800  $\mu$ s. The VME Configuration ROM / Control and Status Register Requirements (CR/CSR) are also implemented in the ROD module. This includes a ROM containing the serial number of the board, as well as the possibility to change the base address of the board in the crate. This function also allows enabling or disabling of the ROD module.