## 3)

## FLIP CHIP ATTACHMENT METHODS: A METHODOLOGY FOR EVALUATING THE EFFECTS OF SUPPLIER PROCESS VARIATION AND SUPPLIER RELATIONSHIPS ON PRODUCT RELIABILITY

by

#### **SHERRY L. CLOUGH**

B.S.E. Industrial and Operations Engineering, University of Michigan, 1991

Submitted to the Sloan School of Management and the Department of Materials Science Engineering in partial fulfillment of the requirements for the degrees of

#### MASTER OF SCIENCE IN MANAGEMENT and MASTER OF SCIENCE IN MATERIALS SCIENCE ENGINEERING

## at the MASSACHUSETTS INSTITUTE OF TECHNOLOGY June 1998

© 1998 Massachusetts Institute of Technology. All rights reserved.

| Signature of Author                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           | May 8, 1998<br>Sloan School of Managemen<br>Department of Materials Science Engineering         |

| Certified by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           |                                                                                                 |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           | Roy Welsch, Thesis Advisor Professor of Management Science                                      |

| Certified by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -         |                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           | Frederick McGarry, Thesis Advisor<br>Professor of Materials Science Engineering                 |

| Accepted by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |                                                                                                 |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           | Larry Abeln, Director of Master's Program  Sloan School of Managemen                            |

| Accepted by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |                                                                                                 |

| • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ÷         | Linn W. Hobbs                                                                                   |

| MARCACHICEETTS INCRITETE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           | John F. Elliott Professor of Materials<br>Chairman, Departmental Committee on Graduate Students |

| Agricultural control of the control | Same Take |                                                                                                 |

JUN 251998

, 1

# FLIP CHIP ATTACHMENT METHODS: A METHODOLOGY FOR EVALUATING THE EFFECTS OF SUPPLIER PROCESS VARIATION AND SUPPLIER RELATIONSHIPS ON PRODUCT RELIABILITY

by

#### SHERRY L. CLOUGH

Submitted to the Sloan School of Management and the Department of Materials Science Engineering on May 8, 1998 in partial fulfillment of the requirements for the degrees of Master of Science in Management and Master of Science in Materials Science Engineering at the Massachusetts Institute of Technology

#### **Abstract**

This thesis examines how variation in supplier processes, as well as supplier relationship strategies, can affect product performance for an automotive electronics company. An examination of supplier process variation is a method that is used to uncover potential problems up front during the development phase. Consequently, processes can be adjusted during the product development cycle rather than after the product is in production when it is much more difficult and costly to adjust processes and correct potential problems. I have proposed a statistical methodology that can be used to determine how modifications in supplier processes can adversely affect product performance. An electronics packaging technology, termed flip chip, provides the technological foundation for the research. More specifically, the manufacturing processes of three materials used in the flip chip package - underfill, solder mask, and IC passivation - were analyzed to determine how variation in these processes could affect the adhesion characteristics of the flip chip package.

The results of the research indicate that the current underfill material used in the flip chip package maintains its adhesion capability even when there is substantial variation in the underfill process. The results indicate that there may be degradation in adhesion capability of the solder mask material with slight changes in the solder mask process. Additional studies indicate that die passivation may also exhibit variation in adhesion capability with changes in passivation process parameters.

Supply chain management strategies play an integral role in the product and process development. A firm's supply chain management strategy will have an impact on the likelihood of obtaining cooperation from suppliers to carry out a process variation study such as the one that was completed during this research project. The role of suppliers in the development of a new technology will be examined. Recommendations for the formation and management of supplier relationships are included, specifically as these relationships relate to the ability of a company to quickly adopt the capabilities to develop and implement a new technology.

#### **Thesis Advisors**

Professor Roy Welsch, Sloan School of Management Professor Frederick McGarry, Materials Science Engineering

### **Acknowledgments**

I gratefully acknowledge the support and resources provided to me through the Leaders for Manufacturing Program, a partnership between MIT and major U.S. manufacturing companies.

I would like to thank my two thesis advisors at MIT, Roy Welsch and Frederick McGarry. They have been invaluable sources of help and guidance throughout the internship and the writing of the thesis.

I would also like to thank the many people at Delphi Delco Electronics Systems who helped me make this project a success. I would especially like to thank my supervisor, Fred Kuhlman, for all of his support and assistance during the course of the internship. I would also like to thank my mentor, Jan Harmeyer, for providing me with advice and encouragement.

The last two years at LFM have been a truly remarkable experience for me. I feel privileged and honored to be a member of the LFM class of 1998. My classmates are an exceptional group of very talented people. I thank them for making my two years at LFM an enriching and fun experience.

I would also like to thank my significant other, Brandon. I feel very fortunate to have him in my life. He has provided me with much joy and happiness during the last few months. I am very appreciative of his support and patience during the writing of this thesis. I am looking forward to spending many more years together with him.

This thesis is dedicated to my family. My wonderful parents Ralph and Nancy have always been there for me. They have provided me with love, support and encouragement throughout my life. My brother Don, along with being a wonderful brother, is a great friend. He always keeps me laughing and helps me to maintain my perspective on life.

## **Table of Contents**

| Al | BSTRACT        |                                                         | 3  |

|----|----------------|---------------------------------------------------------|----|

| A  | CKNOWL         | EDGMENTS                                                | 5  |

| T  | ABLE OF        | CONTENTS                                                | 7  |

| T  | ABLE OF        | FIGURES                                                 | 11 |

| T  | ABLE OF        | TABLES                                                  | 11 |

| 1. | INTRO          | DDUCTION                                                | 13 |

|    |                | TVATION                                                 |    |

| 2. | СОМР           | ANY & PROJECT BACKGROUND                                | 21 |

|    |                | IPANY BACKGROUNDIPANY BACKGROUND                        |    |

| 3. |                | CHIP TECHNOLOGY                                         |    |

| ٠. |                | CHIP HISTORY                                            |    |

|    |                | CHIP MARKETS                                            |    |

|    |                | CTRONICS PACKAGING OVERVIEW                             |    |

|    | 3.3.1          | Level 1 Technology                                      |    |

|    | 3.3.1          |                                                         |    |

|    | 1.1.1          |                                                         |    |

|    | 1.1.1          | 1 1                                                     |    |

|    | 1.1.2          | Level 2 Technology                                      |    |

|    | 1.1.2          | 6                                                       |    |

|    | 1.1.2          |                                                         |    |

|    |                | CHIP ASSEMBLY PROCESS                                   |    |

|    | 1.4.1          | Flip Chip Solder Bumping                                |    |

|    | 1.4.2          | Flux Dispense and Component Placement                   |    |

|    | 1.4.3          | Reflow                                                  |    |

|    | 1.4.4          | Cleaning                                                |    |

|    | 1.4.5          | Underfill Dispense                                      |    |

|    | 1.1.6          | Underfill Cure                                          |    |

|    | 1.5 Issu       | IES WITH USING FLIP CHIP ON ORGANIC SUBSTRATES          |    |

|    | 1.5.1<br>1.5.2 |                                                         |    |

|    |                | Failure Mechanisms CHIP ADHESION                        |    |

|    | 3.6.1          | Shear Stresses                                          |    |

|    | 3.6.2          | Distance from Neutral Point (DNP)                       |    |

| 4. | 2.3.2          | JER MATERIAL PROCESSES                                  |    |

| ₹. |                | DERFILL                                                 |    |

|    | 4.1 UNL        | Desired Material Properties                             |    |

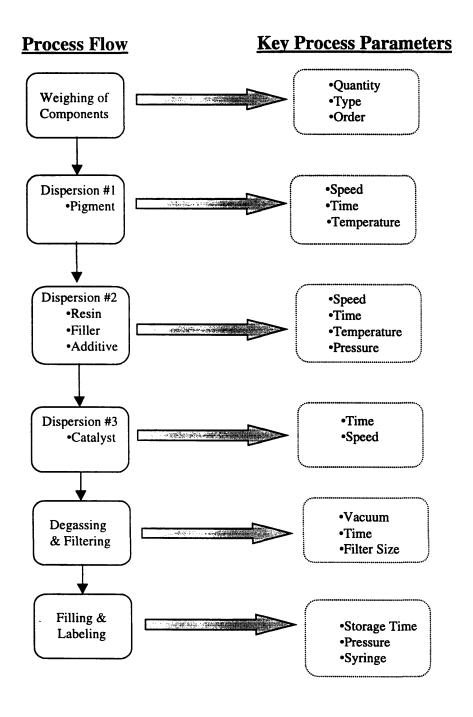

|    | 4.1.2          | Process Flow & Key Process Parameters                   |    |

|    | 4.1.3          | Key Process Parameters for Underfill                    |    |

|    |                | DER MASK                                                |    |

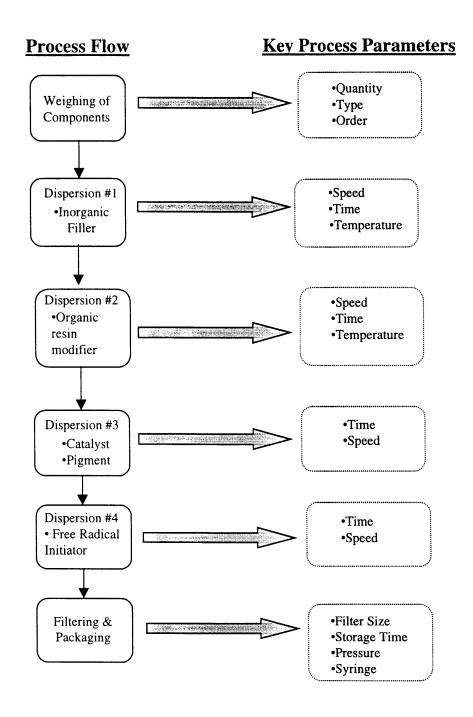

|    | 4.2.1          | Mask Mixing Process Flow and Key Parameters             |    |

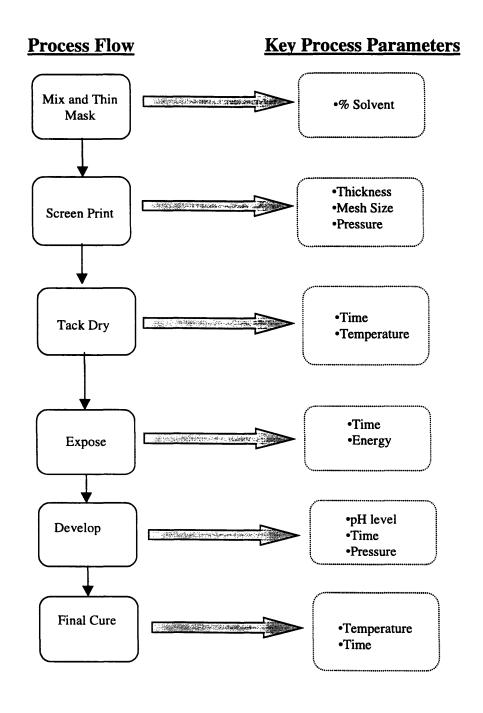

|    | 422            | Solder Mask Application Process Flow and Key Parameters |    |

|    | 4.3 PAS        | SIVATION                                                     | 55         |

|----|----------------|--------------------------------------------------------------|------------|

|    | 4.3.1          | Silicon Nitride                                              | 55         |

|    | 4.3.2          | Polyimide                                                    | 55         |

|    | 4.3.3          | Passivation Key Process Parameters                           | 56         |

| 5. | EXPE           | RIMENTS AND DATA COLLECTION                                  | 57         |

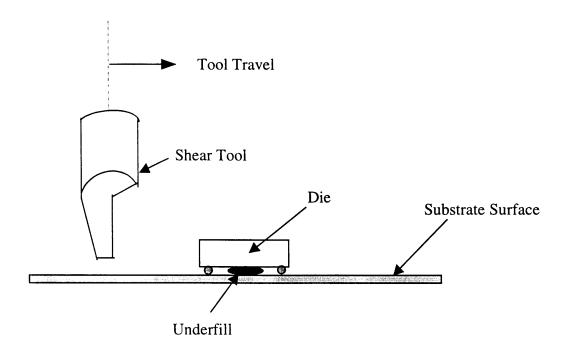

|    | 5.1 DES        | CRIPTION OF TEST METHOD                                      | 58         |

|    | 5.1.1          | Test Equipment                                               | <i>5</i> 8 |

|    | 5.1.2          | Test Procedure                                               | <i>58</i>  |

|    | 5.2 DES        | IGN METHODOLOGY                                              | 60         |

|    | 5.2.1          | Underfill                                                    |            |

|    | 5.2.           |                                                              |            |

|    | 5.2.1          |                                                              |            |

|    | 5.2.2          | Solder Mask                                                  |            |

|    | 5.2.3          | Die Passivation                                              |            |

|    |                | A ANALYSIS                                                   |            |

|    | 5.3.1          | Underfill Data AnalysisSolder Mask Data Analysis             |            |

|    | 5.3.2<br>5.3.3 | Die Passivation Data Analysis                                |            |

|    | 5.3.3<br>5.3.3 | ·                                                            |            |

|    | 5.3.           | •                                                            |            |

|    | 5.3.           | •                                                            |            |

| 6. | SUPP           | LIER RELATIONSHIP STRATEGY                                   | 75         |

| ٠. |                | RGER WITH DELPHI AUTOMOTIVE SYSTEMS                          |            |

|    |                | GLE SOURCE VS. MULTIPLE SOURCES                              |            |

|    |                | TNERSHIPS                                                    |            |

|    | 6.3.1          | DDES's Strategic Supplier Partnerships                       |            |

|    | 6.3.2          | Purchasing/Engineering Relationship                          |            |

|    |                | SE STUDY: UNDERFILL SUPPLIER & DIE SUPPLIER                  |            |

|    | 6.4.1          | Underfill Supplier (US)                                      |            |

|    | 6.4.2          | Die Supplier (DS)                                            |            |

| 7. | . RESU         | LTS AND RECOMMENDATIONS FOR FURTHER STUDY                    |            |

| •  |                | SULTS FROM DATA ANALYSIS & RECOMMENDATIONS FOR FURTHER STUDY |            |

|    | 7.1.1          | UnderfillUnderfild                                           | 85         |

|    | 7.1.2          | Solder Mask                                                  |            |

|    |                | 2.1 Recommendations for Further Study                        |            |

|    | 7.1.3          | Die Passivation                                              |            |

|    | 7.2 RE         | COMMENDATIONS FOR FUTURE PROJECT APPROACH                    | 89         |

|    | 7.2.1          | Adhesion Test Specification and Test Method                  |            |

|    | 7.2.           |                                                              |            |

|    |                | PPLIER RELATIONSHIP STRATEGY RECOMMENDATIONS                 |            |

|    | 7.4 LE         | SSONS LEARNED                                                | 92         |

| 8  | . CON          | CLUSIONS                                                     | 95         |

|    | 8.1 TE         | CHNOLOGY CONCLUSIONS                                         |            |

|    | 8.1.1          | Underfill                                                    | 97         |

|    | 8.1.2          | Solder Mask                                                  |            |

|    | <i>8.1.3</i>   | Die Passivation                                              |            |

|    | 8.2 Su         | PPLIER RELATIONSHIP CONCLUSIONS                              | 98         |

| A  | APPENDD        | K A                                                          | 10         |

|    |                |                                                              | 400        |

| Δ  | APPENDI)[      | ( B                                                          | 1103       |

| APPENDIX C      |     |

|-----------------|-----|

| Data for Chip A |     |

| DATA FOR CHIP B | 100 |

| DATA FOR CHIP C |     |

| BIBLIOGRAPHY    | 109 |

## **Table of Figures**

| FIGURE 1 - FLIP CHIP PACKAGE SCHEMATIC                                       | 14   |

|------------------------------------------------------------------------------|------|

| FIGURE 2 - SIDE AND TOP VIEWS OF AN ATTACHED FLIP CHIP                       | 23   |

| FIGURE 3 - ELECTRONICS PACKAGING HIERARCHY                                   | 27   |

| FIGURE 4 - WIRE BONDING ATTACHMENT SCHEMATIC                                 | 29   |

| FIGURE 5 - TAB ATTACHMENT SCHEMATIC                                          |      |

| FIGURE 6 – SIDE AND TOP VIEWS OF ATTACHED FLIP CHIP                          | 31   |

| FIGURE 7 - SCHEMATIC OF A THROUGH-HOLE CONNECTION                            | 32   |

| FIGURE 8 - SCHEMATIC OF A SURFACE MOUNT CONNECTION                           | 33   |

| FIGURE 9 - FLIP CHIP ASSEMBLY PROCESS                                        |      |

| FIGURE 10 - EFFECT OF FILLER CONTENT ON VISCOSITY AND CTE                    | 47   |

| FIGURE 11 - UNDERFILL PROCESS FLOW AND KEY PROCESS PARAMETERS                | 51   |

| FIGURE 12 - SOLDER MASK MANUFACTURE PROCESS FLOW AND KEY PROCESS PARAMETERS. | 53   |

| FIGURE 13 - SOLDER MASK APPLICATION PROCESS FLOW AND KEY PROCESS PARAMETERS  | 54   |

| FIGURE 14 – SIDE VIEW OF DIE SHEAR TOOL                                      |      |

| FIGURE 15 – TOP AND SIDE VIEWS OF SAMPLE POPULATED TEST COUPON               |      |

| FIGURE 16 - ALTERNATIVE SITUATIONS IN SUPPLIER MANAGEMENT <sup>17</sup>      | 79   |

|                                                                              |      |

| Table of Tables                                                              |      |

| Table of Tables                                                              |      |

| TABLE 1 - FLIP CHIP DIMENSIONS                                               | 16   |

| TABLE 2 - DESIRED PROPERTIES OF UNDERFILL MATERIAL <sup>12</sup>             | 45   |

| TABLE 3 - SUMMARY OF DATA REPORTED BY UNDERFILL SUPPLIER                     |      |

| TABLE 4 - SOLDER MASK TEST MATRIX                                            | 65   |

| TABLE 5 - DIE TEST MATRIX                                                    | 67   |

| TABLE 6 - UNDERFILL TEST RESULTS AND COMPARISON WITH SUPPLIER DATA           | 68   |

| TABLE 7 - SOLDER MASK TEST RESULTS                                           | 69   |

| TABLE 8 - CHIP A TEST RESULTS                                                | 71   |

| TABLE 9 - CHIP B TEST RESULTS                                                | 72   |

| TABLE 10 - CHIP C TEST RESULTS                                               |      |

| TABLE 11 - COMPARISON OF SUPPLIER ATTRIBUTES                                 | 84   |

| TABLE 12 - UNDERFILL TEST RESULTS AND COMPARISON WITH SUPPLIER DATA          | 85   |

| TABLE 13 - STRENGTHS AND WEAKNESSES OF SUPPLY CHAIN STRATEGY                 | 99   |

| TABLE 14 - DATA AND ANOVA RESULTS FOR UNDERFILL EXPERIMENT                   | 101  |

| TABLE 15 - RAW DATA AND T-TESTS FOR PHOTOPOLYMER EXPERIMENT                  | 103  |

| TABLE 16 - RAW DATA AND T-TESTS FOR PHOTOINITIATOR EXPERIMENT                |      |

| TABLE 17 - RAW DATA AND T-TESTS FOR FILLER EXPERIMENT                        |      |

| TABLE 18 - RAW DATA AND ANOVA RESULTS FOR CHIP A                             |      |

| TABLE 19 - RAW DATA AND ANOVA RESULTS FOR CHIP B                             |      |

| TABLE 20 - RAW DATA AND ANOVA RESULTS FOR CHIP C                             | .107 |

### 1. Introduction

As the rate of change continues to accelerate in today's global economy, companies must continually strive to shorten their development cycles. As new technologies emerge, the ability to quickly adopt and implement these technologies will be a source of competitive advantage. Along with the focus on the ever-increasing rate of change, there is a greater focus on the need for companies to establish systems that ensure superior product quality and reliability. In order to compete in today's marketplace, companies must have a quality system in place that delivers a defect-free product to their customers. This thesis will propose a methodology to improve quality and product reliability during the product development phase, when it is easiest and least costly to correct potential quality problems. The thesis also examines the role that supplier relationships play in the development of a new technology. Supply chain strategies are just as important as the product and process strategies in the rapid adoption of emerging technologies.

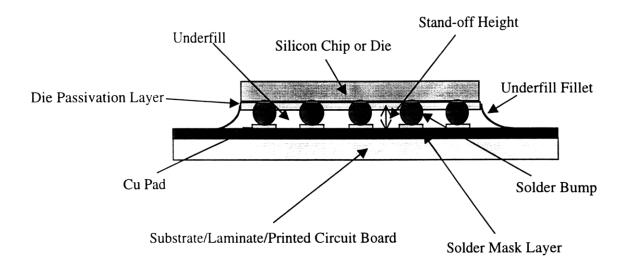

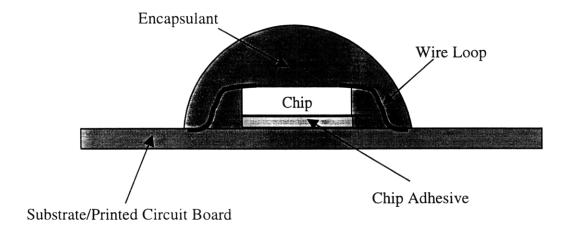

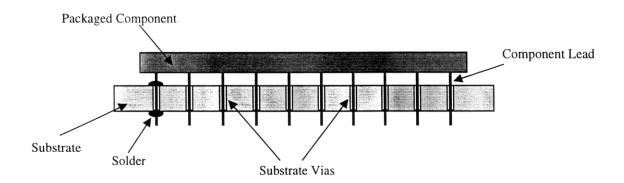

The research for this thesis was conducted at an automotive electronics supplier. In the drive for smaller, cheaper and lighter assemblies in the electronics industry, flip chip has emerged as a key technology to achieve these goals. The Internship Company, Delphi Delco Electronics Systems (DDES), is currently in the process of developing flip chip technology for laminate substrates that will be incorporated into several of its electronic control modules. I will refer to the flip chip package and the components that comprise the flip chip package frequently throughout the thesis. To familiarize the reader with the terminology, a schematic of a flip chip package is shown in Figure 1. A brief definition for each of the components that comprise the flip chip system follows the schematic.

Figure 1 - Flip Chip Package Schematic

#### Flip Chip

Flip chip employs soldering directly between the integrated circuit die face and the interconnecting substrate. Solder bumps are deposited onto the chip termination lands. The chip is then aligned to the proper circuitry on the substrate and bonded in place using reflow soldering techniques.

#### Silicon Die or Chip

Silicon die or chip is the integrated circuit. Die, chip and IC will be used interchangeably throughout the thesis.

#### Die Passivation Layer

Die passivation is a layer of material deposited onto the underside of the IC. . Passivation coats the final metal and chip. Passivation provides moisture, ionic and physical protection to the chip as well as electrical insulation to the limiting metal contained in the IC. The passivation type and deposition method will vary with the chip technology and semiconductor fab facility. Some common types of passivation are silicon nitride, oxy-nitride and polyimide.

#### Substrate/Laminate/Printed Circuit Board

Laminate substrates are multilayer, organic printed circuit boards. They are formed from epoxy resins reinforced with glass fibers. The conductive material, copper, is plated onto the laminate sheets and etched to form the metal pattern. The substrate type referred to throughout this thesis is commonly known as FR-4 (flame retardant epoxy).

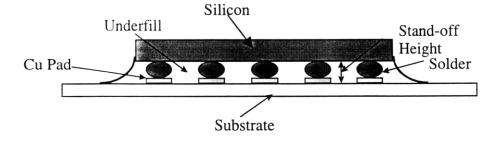

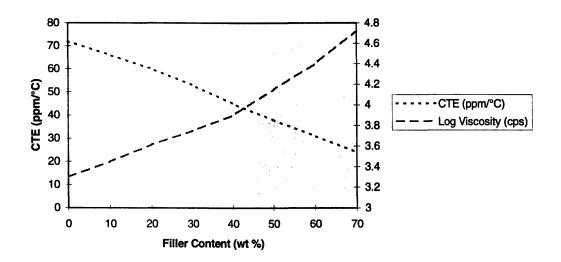

#### Underfill

The underfill consists of an anhydride-cured, epoxy resin, which is filled with silica particles. Underfill acts to mechanically couple the die and substrate together to locally constrain the Coefficient of Thermal Expansion (CTE) mismatch between the die and substrate. The underfill redistributes the stress from the solder joints to the chip, substrate and epoxy.

#### Solder Mask Layer

Solder mask (also known as solder resist) is the outermost layer of material on the printed circuit board. Solder mask is applied to the entire PCB surface, except for solder or contact lands, to both prevent solder wetting during the assembly process and to provide protection from environmental damage after assembly. Solder mask is an organic material comprised of epoxy and inorganic fillers.

#### Solder Bump

The solder bump consists of eutectic 37Pb/63Sn solder. The solder melts during the reflow stage to form the interconnection between the die and the substrate. The solder is deposited onto the die using one of several methods, which depend upon the materials chosen for the solder and the chip design. Three of the most common methods are solder evaporation, solder electroplating and solder screen printing.

Table 1 lists typical dimensions for a flip chip package. These dimensions are typical for a flip chip system and could vary depending on the chip and technology employed. Bump pitch refers to the distance from the center of one bump to the center of

an adjacent bump. Stand off height refers to the vertical distance between the substrate and die.

| Attribute        | Dimension         |

|------------------|-------------------|

| Silicon Die      | 250 mil X 250 mil |

| Die Thickness    | 10 mil            |

| Stand Off Height | 4 mil             |

| Bump Diameter    | 6 mil             |

| Bump Pitch       | 8 mil             |

| Number of Bumps  | 100               |

Table 1 - Flip Chip Dimensions

Flip chip technology is not new to the electronics industry. Flip chip attachment methods have been used for over 30 years in hybrid products (which contain ceramic substrates). However, using flip chips on laminate substrates is a new technology for the electronics industry. Because there are many reliability issues involved with using flip chip on laminate in the extreme environment of an automobile, the design and process technologies have undergone extensive capability studies, testing and verification to ensure superior product reliability. The methodology contained in this thesis describes one way in which product reliability can be improved.

#### 1.1 Motivation

The motivation for the research conducted during this internship was to determine if slight variation in supplier processes could adversely affect product reliability in a new technology, which is termed flip chip. Several years ago, DDES made the decision to begin using flip chip as a method of attaching semiconductors to the circuit boards that it assembles. There were several reasons for incorporating this technology into its products. DDES's primary customer, General Motors, wanted one of the engine control modules to be mounted directly on the engine. This meant that there were size limitations in how large the electronic assembly could be. The flip chip attachment method enables a

reduction in size. Flip chip was also a key enabler to meet customer's cost targets, since the cost of flip chip is less than the cost of using traditional packaged die.

Using flip chip attachment methods on laminate substrates is still a largely unproven technology. There are many reliability issues that must be addressed to assure superior product reliability. Several years ago a large study was undertaken to find a set of materials in the flip chip assembly that would exceed reliability targets, which is measured by the number of thermal cycles that are completed. (Mean time to failure, MTTF, is a common measure of reliability.) After expending significant research and development resources, DDES was able to find a material set that would exceed their specifications. However, the reliability of this material set is precarious in that even slight changes in the formulation or processing of any one material could dramatically affect the reliability of the entire flip chip assembly. DDES has experienced situations in which slight changes in the formulations or the processing of a material has resulted in adverse effects in flip chip performance and reliability.

In general, DDES can cite many examples in which slight changes in either its own processes or the processes of its suppliers have resulted in adverse consequences. Performing an ex ante process variation study in the development phase is a method of determining how changes in processes can potentially alter product performance. This information can then be used to communicate to the suppliers what the tolerances for their processes must be in order to assure the needed level of reliability.

In order to successfully complete a process study such as this, cooperation and assistance from suppliers is necessary. The ideal situation is when a supplier is a full partner in the product development cycle. However, it is uncommon for suppliers to be fully integrated in the design and development of a new technology. Rather, suppliers are often competing amongst each other for customers, and in many cases are reluctant to share proprietary information with their customers. The key to having supplier cooperation for a study such as this is designing the appropriate incentive scheme and having the necessary supplier relationship strategy in place so that suppliers are motivated to participate fully in a study such as this. During the course of the internship, I was able

to obtain the necessary cooperation from some suppliers. However, I was not able to obtain assistance from other suppliers, which hindered my ability to fully complete the proposed study. These differences in supplier responsiveness and supplier relationships will be explored later in this thesis.

#### 1.2 Thesis Organization

The thesis has been organized into the following chapters.

#### Chapter 1 - Introduction

This chapter provides an introduction to the project, the motivation for the project, and a description of the organization of the thesis.

#### Chapter 2 - Company and Project Background

This chapter provides the reader with some necessary background information on the Dephi Delco Electronics Systems and the project itself. It also describes the goals of the project.

#### Chapter 3 - Flip Chip Technology

This chapter describes the flip chip technology in detail. Included are overviews of the history of flip chip technology to date, flip chip markets, electronics packaging, and the flip chip assembly process. This chapter also describes the critical reliability issues associated with using a flip chip package on FR-4 (laminate) substrates, and the typical failure modes observed with flip chip packages. Finally, there is a discussion of flip chip adhesion, as well as an explanation as to why adhesion is critical to flip chip reliability.

#### Chapter 4 - Supplier Material Processes

This chapter describes the three materials that are the focus of my research: underfill, die passivation and solder mask. For each material, I have provided an overview of what the material is composed of, how it is manufactured and what the key product and process parameters are. I have specifically pointed out those parameters that are viewed as critical for flip chip adhesion.

#### Chapter 5 - Experiments and Data Collection

This chapter describes the experiments that I conducted. An overview of the test methods and the design methodology are described. This chapter also includes summaries of the data and data analysis that were performed during the internship.

#### Chapter 6 – Supplier Relationship Strategy

This chapter presents all of the management issues and findings that I researched during the internship. I have discussed DDES's recent change in its strategy as a result of a global sourcing initiative and a recent merger with Delphi Automotive Systems. I have compared and contrasted the traditional supplier relationship with the "supplier partnership" that has become popular with many companies. An overview of DDES's current strengths and weaknesses with its supplier relationship strategy is also included in the context of current knowledge in the industry regarding advantages and disadvantages of forming supplier partnerships.

#### Chapter 7 - Results and Recommendations for Further Study

This chapter summarizes the findings from the data analysis that was performed and provides recommendations for further study. I have also included an overview of the lessons learned from this project, and how a project such as this might best be approached in the future. Additionally, other recommendations that relate to this project are included.

#### Chapter 8 - Conclusions

This chapter summarizes the key findings in the thesis as well as reiterates the main recommendations.

## 2. Company & Project Background

This chapter provides the reader with some necessary background information on the Internship Company as well as an introduction to flip chip technology. This chapter also provides the background for the internship project as well as the specific goals for the research.

#### 2.1 Company Background

The analysis in this thesis was developed during a research internship at Delphi Delco Electronics Systems (DDES). DDES is an automotive electronics supplier that is headquartered in Kokomo, Indiana. Approximately 80% of DDES's sales are to its parent company, General Motors (GM). While the majority of DDES's operations are located in the Midwest, the division does have thirty-six facilities in fifteen countries. DDES currently employs 31,000 people worldwide, and its reported revenues were \$5.6 billion in 1997. DDES designs and manufactures a variety of automotive electronics components, including engine control modules, air bag modules, anti-lock brake modules, radios, instrument clusters, heater/air controls, pressure sensors and voltage regulators. DDES also has a captive, in-house semiconductor fabrication division that supplies 40% of the ICs required for DDES products.

During the course of the internship, GM merged DDES with the other wholly owned components divisions, collectively known as Delphi Automotive Systems. The integration of DDES with Delphi creates an automotive systems supplier that can more effectively compete in global markets by developing new electronically enhanced vehicle systems. Delphi's strategy is to offer OEM automobile manufacturers competitive products that have complete systems capability and that can be fully integrated into the vehicle architecture. While it is not completely known how the merger will affect DDES, there are certain to be many changes in the organizational structure as Delphi moves to integrate DDES more fully into the division.

During the last ten years, the business climate has changed dramatically for DDES, specifically with respect to its relationship with General Motors. DDES used to

be a captive supplier to GM. It was a given that DDES would supply GM's needs for the automotive electronics that DDES manufactured, at a price that was determined by DDES. However, that relationship has changed with GM's global sourcing initiative. Now, DDES must compete globally with other automotive electronics suppliers on the basis of price, quality and delivery. The increased competition has forced DDES to make significant price cuts. In order to maintain the margins that DDES needs for reinvestment, there is a tremendous cost cutting initiative occurring within the company. In fact, DDES has also begun a global sourcing initiative with its suppliers, similar to that of GM's initiative, in order to drive down the costs of raw materials.

Because DDES is no longer assured of GM's business, DDES is aggressively pursuing new business opportunities outside the realm of GM. Growth in the future will be achieved primarily through seeking new international customers as well as through select acquisitions and joint ventures. DDES's strategy is to aggressively continue to cut costs while offering products with increased electronic functionality through a focus on safety, security, communications and convenience. Additionally, the merger with Delphi will certainly open up new doors and potential customer opportunities by aligning key design, manufacturing and marketing competencies. Competition among the automotive electronics suppliers is intense, and DDES knows it must meet customer expectations in terms of quality, cost and delivery to be able to satisfy its existing customers and to grow its customer base.

## 2.2 Project Background

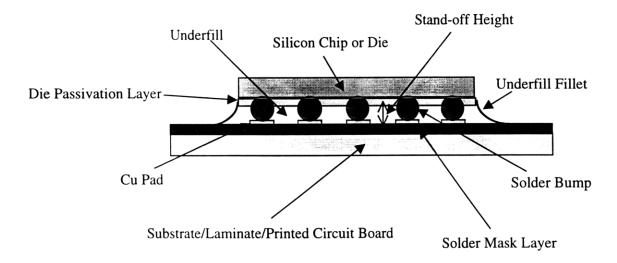

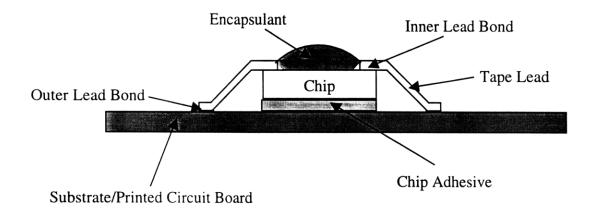

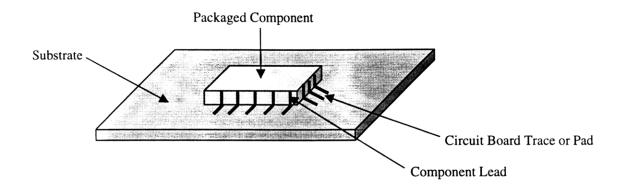

In order to achieve the aggressive cost reductions that were necessary to meet its customer's price requirements (and at the same time continue to be a profitable division of Delphi Automotive Systems), DDES had to make some major modifications to the way it had traditionally designed the electronic control modules. One of the major changes, which is the focus of this thesis, was in the way the integrated circuits (IC's) are attached to the circuit board substrate. DDES is planning to incorporate flip chips on laminate printed circuit boards in several of its electronic control modules. Flip chip is a method used to mount bare semiconductor die (known as just die in the industry) to a

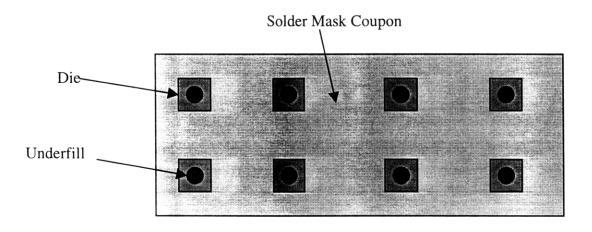

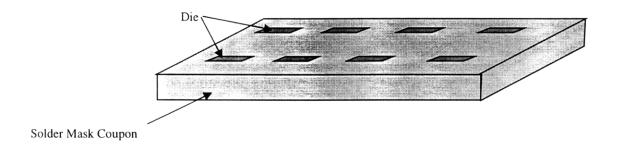

substrate. Mechanical and electrical connections are accomplished simultaneously by reflowing solder bumps on the die to make contact with the metal pads on the substrate. Figure 2 displays both a side view and top view of a flip chip attached to the substrate. Chapter 3 presents a detailed description of the flip chip assembly process.

Figure 2 - Side and Top Views of an Attached Flip Chip

Flip chip technology is not new to the electronics industry. The industry, including DDES, has been using flip chips for over 30 years in its hybrid products. In hybrids, an inorganic ceramic serves as the substrate material. However, the flip chip attachment method had not been utilized on laminate substrates in the past. Because this is a new technology for DDES, and because there are many reliability issues involved

with using flip chip on laminate in the extreme environment of an automobile, the design and process technologies have undergone extensive capability studies, testing and verification to ensure superior product reliability. My research during the internship has dealt with one aspect of product reliability: understanding how variation in supplier processes can impact flip chip reliability. Specifically the goals of the internship were as follows:

- Study material variations at the supplier level that can degrade flip chip adhesion.

The scope of the project included three materials used in the flip chip mounting process: underfill, solder mask and die passivation.

- Utilize a die shear test method as a means to performing sensitivity analysis

experiments on how variation of the key process parameters for each material can

change adhesion characteristics.

- Based upon the results of the experiments, communicate my findings back to the suppliers so that they could develop meaningful process specifications for the manufacture of flip chip assembly materials.

- Study the relationships that DDES currently has with its suppliers, and document

DDES's current strategy for supplier relations and supply-chain management,

specifically as they relate to the global sourcing initiative and the merger with

Delphi. I will analyze the strengths and weaknesses of the existing system and

make recommendations for improvements based upon current knowledge of the

best practices.

## 3. Flip Chip Technology

The driving forces in the electronics industry are requiring smaller, lighter, and cheaper assemblies. The trend in the microelectronics industry is toward faster device speed, higher heat dissipation, lower cost, higher throughput, higher yields and enhanced reliability. Flip chip connection methods offer numerous advantages as compared with conventional interconnection methods such as wire bonding. (Section 3.3.1.1 includes a description of wire-bonding techniques). Several of the primary advantages of flip chip are: <sup>1</sup>

- In flip chip connections, the short interconnect distances allow for a fast signal response combined with a low inductance.

- Flip chip mounting requires a minimum amount of space on the substrate.

This results in significant savings in substrate material as well as in the overall board area required for the circuit board assembly.

- Because of the face-down configuration, the whole surface of the die can be

used for different array configurations, which allows for the highest number of

input/output connections.

## 3.1 Flip Chip History

IBM developed the first flip chip application in the early 1960's as an alternative to manual wire bonding. This technology, referred to as Controlled Collapse Chip Connection (C4), was developed as a method of achieving extremely high interconnect densities for high-end mainframe systems.<sup>2</sup> In the C4 process a high melting point 97Pb/3Sn alloy is deposited onto wettable chip pads on the die surface, which is then mounted on a ceramic substrate face down.<sup>2</sup> The solder bumps on the die match up with wettable substrate lands. The solder is reflowed to simultaneously form all electrical and mechanical connections between the die and the substrate. Flip chips mounted on a ceramic substrate have been used extensively for more than 30 years in the computer and

automotive industries. In fact, Delphi Delco Electronics Systems (DDES) was one of the first users of flip chips for ceramic substrate (hybrid) applications.

Due to the high cost of ceramic substrates (and, secondarily, the cost of licensing fees paid to IBM for use of the C4 process), there has been a lot of work directed toward new, cheaper processes, such as flip chip mounted on FR-4 (organic laminate) substrates. IBM at Yasu, Japan has been assembling solder-bumped flip chips on organic printed circuit boards since 1990, mainly for the personal computer and larger mainframe systems.<sup>3</sup> The process resembles the C4 technology in that it uses solder bumps to make these connections between the die and board, but it uses a low melting point eutectic 37Pb/63Sn solder to avoid thermal damage to the laminate substrate.

#### 3.2 Flip Chip Markets

Currently flip chips represent approximately 2% of the semiconductor industry output, but that number is growing rapidly. Today's large users of flip chips for electronics applications are found in various industries, including automotive, computers, hand-held consumer electronics and medical equipment. Each industry has different requirements for its products and varying reasons for using flip chip technology. The automotive industry, for example, requires very good reliability with high temperatures, high humidity, and significant thermal cycling. The computer industry desires high speeds with good electrical performance. The hand-held consumer electronics industry desires small, lightweight products with low self-inductance.

There is extensive research being done to evaluate flip chip processes. Much of the research is focused on developing low-cost, high-volume production processes for flip chip. A low-cost flip chip mounting process, however, is only realized by decreasing the process/assembly costs. This is due to the fact that the cost savings are balanced by the additional cost for the deposition of the bumps and testing of the chips. A key means for achieving reasonable costs is for the flip chip assembly process to be compatible with the standard Surface Mount Technology (SMT) reflow process (and therefore existing equipment and process knowledge).

#### 3.3 Electronics Packaging Overview

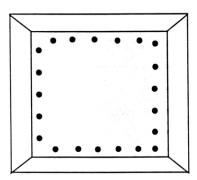

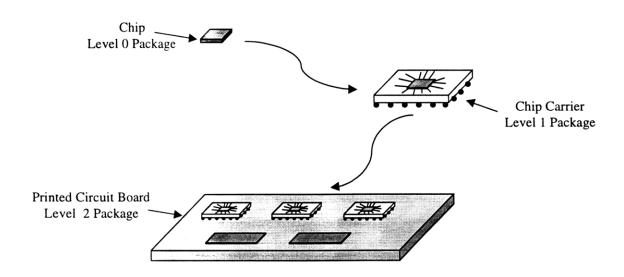

Electronics packaging has traditionally served four functions to assure an IC's performance: power distribution, signal distribution, heat dissipation and circuit protection.<sup>5</sup> Each of these functions must be taken into consideration when designing components for circuits, and tradeoffs usually exist which include cost, size, reliability and testability. Electronic packages are typically classified into levels based on the number and sophistication of the electronic assembly of which they are comprised. Figure 3 provides an illustration of this hierarchy scheme.<sup>5</sup>

Figure 3 - Electronics Packaging Hierarchy

The semiconductor chip is considered to be the lowest level of packaging. As such it is classified as Level 0. The chip is mounted into a chip carrier module, which is considered the Level 1 connection. Level 2 packaging is sometimes referred to as the electrical circuit assembly. At this level, the individual chip carriers are mounted on a common base, usually a printed circuit board (PCB). Several Level 2 assemblies can be

interconnected into a complete electronics assembly, which represents the Level 3 connection.

#### 3.3.1 Level 1 Technology

Micro-bonding is the collective name for the techniques used to make connections between the electronic circuits on the semiconductor chip and the surrounding circuitry. To allow for connections between the chip and the outside world, single chip carriers usually contain a metallized pattern, which is commonly referred to as a lead frame. The surrounding circuitry may be an IC package or conductors on a substrate. Three methods are commonly used in the industry to make the interconnections between the chip and the lead frame: wire bonding, tape-automated bonding (TAB), and direct chip attach, also known as flip chip. Flip chip will be discussed in detail throughout the remainder of the thesis.

#### 3.3.1.1 Wire Bonding

Wire bonding is the most popular method for connecting the die to the package. Wire bonding is accomplished by mounting the backside of a chip to a package with a conductive epoxy. Gold or aluminum wires are then bonded sequentially using a combination of heat, pressure and/or ultrasonic energy. There are three types of wire bonding: ultrasonic, thermocompression and thermosonic ball/wedge. See Figure 4 below for a schematic of a die wire bonded to a substrate. Chip on board (COB) is a micro-bonding technique used to bond bare die to the PCB. The chip is covered with a glob top after wire bonding.

Figure 4 - Wire Bonding Attachment Schematic

Wire bonding is still by far the most commonly used technique for Level 1 connections. There are several advantages to wire bonding. It is fast and flexible, as well as being a standardized and balanced process (up to 7 wires per second), which is compatible with all plastic and hermetic types of packaging. However, there are several notable disadvantages with wire bonding. The minimum pitch for wire bonding is approximately 100 µm, which limits the input/output capacity of the die. (Pitch refers to the distance between adjacent wires). Additionally, wire bonding may lead to parasitic interconnections between wires, and there is a reduced yield for larger number of bondings since each bond is made individually.

#### 3.3.1.2 Tape-Automated Bonding (TAB)

Tape-Automated Bonding (TAB) currently comprises less than 2 percent of the dies assembled worldwide. TAB uses thermocompression bonding to attach bumped die to patterned metal on polymer tape. This is also known as inner-lead bonding (ILB). See Figure 5 below for a schematic of a die attached to a substrate using TAB methods. The chip is then encapsulated and the individual die are then removed from the tape and packaged using outer-lead bonding (OLB).

Figure 5 - TAB Attachment Schematic

TAB offers several advantages over wire bonding. A substantial increase in throughput can be achieved since all leads are bonded at once. Additionally, the interconnection density is greatly increased. As with wire bonding, there are several disadvantages to utilizing TAB methods. The ILB process requires the formation of bumps either on the die or tape, which can add cost to the process. Additionally, the tooling and equipment cost may be prohibitive and the availability of the necessary equipment may be an issue.<sup>6</sup>

#### 3.3.1.3 Flip Chip (or Direct Chip Attach)

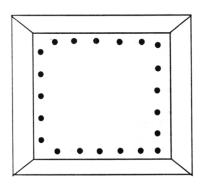

Flip chip will be discussed in detail throughout the remainder of the thesis. However, I will present a short explanation here to familiarize the reader with flip chip attachment methods. Flip chip employs soldering directly between the integrated circuit die face and the interconnecting substrate. Solder bumps are deposited on the chip termination lands. The chip is then aligned to the proper circuitry on the substrate and bonded in place using reflow soldering techniques. In this way, the interconnection bonds between the chip and substrate are made simultaneously, which reduces fabrication costs. Figure 6 displays a schematic of the side view and top view of a flip chip attached to a substrate.

Figure 6 - Side and Top Views of Attached Flip Chip

Flip chip offers several advantages over wire bonding and TAB methods. Because flip chip does not require the use of bonding wires or leads to patterns outside the die's perimeter, flip chip achieves the highest ratio of active silicon surface to substrate area. Additionally, flip chip provides the shortest interconnect distances, the highest packaging density with the most efficient use of the substrate area, and better reliability because of the direct connection between the chip and substrate. The main disadvantages with using flip chip are the potential thermal stress complications, the inability to rework flip chips, difficult flux removal, and the inability to pretest/burn in the die prior to assembly. The thermal stress complications associated with soldering flip chips to laminate substrates will be discussed in detail throughout the remainder of the thesis.

#### 3.3.2 Level 2 Technology

Level 2 technology is the collective name for the techniques used to connect a chip carrier module to an electronic circuit assembly or substrate. The extension of the metal lead frame in the chip carrier to the outside package serves to connect the chip circuitry to the second level of packaging.<sup>7</sup> To facilitate interconnections, metallized conductor paths for signal and power transmission, footprints for mounting the chip carriers, and vias for signal propagation and heat transfer between the various board surfaces are formed on the substrate.<sup>7</sup> There are two primary methods used for the Level 2 connection: through-hole mounting and surface mounting.

#### 3.3.2.1 Through-Hole Technology

Through-hole technology describes a method of connecting electronic components to a substrate by inserting the leaded components into plated through-holes in the substrate. When inserted, component leads protrude through the bottom-side surface of the circuit board. Mechanical attachment is achieved by passing the substrate through a molten-soldering process, commonly known as wave soldering. Electrical connection is achieved from the leads of the chip component through the solder to the plated through-holes. Figure 7 displays a schematic of a through-hole connection.

Figure 7 - Schematic of a Through-Hole Connection

#### 3.3.2.2 Surface Mount Technology

With surface mount technology (SMT), electronic components are placed and attached directly to the surface of the printed circuit board. The electrical and mechanical connection is made with solder that has been reflowed. Figure 8 displays a schematic of a component attached by using surface mount technology.

Figure 8 - Schematic of a Surface Mount Connection

SMT grew rapidly during the 1980's, and is now the dominant technology. SMT is largely an automated process, using equipment known as pick-and-place or chip shooters, since component leads and terminal ends must line up accurately with the corresponding pads on the surface of the printed circuit board. SMT is becoming the dominant technology over through-hole mounting, largely because SMT allows the products to have smaller weights and size, which is in line with market demands. SMT also possesses several other advantages as compared to through-hole technology, which are summarized as follows:

- higher functionality and more features: shorter signal paths which gives better signal speeds and high frequency performance.

- higher packing density on the circuit board with a smaller mounting height.

- simpler shape of components allows for simpler automated assembly and the mounting technique is flexible.

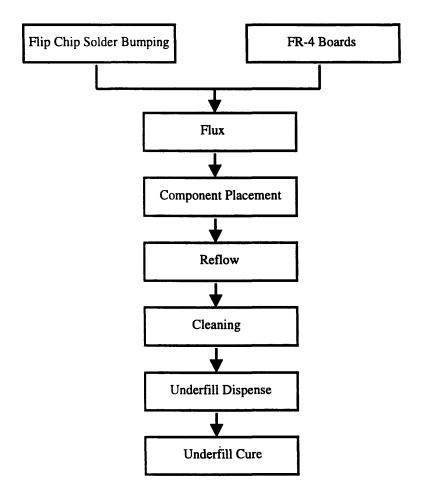

## 3.4 Flip Chip Assembly Process

One of the biggest advantages of using flip chip connection methods is that it is compatible with existing surface mount materials and processes. Traditional pick and place equipment as well as solder reflow ovens can be used for assembling and soldering flip chip packages. This allows greater flexibility for companies who desire to use the same assembly lines for both flip chip and other traditional surface mount components. While flip chip assembly is similar to traditional surface mount processes, there are several notable differences. Figure 9 displays a flow chart of the main processes involved in flip chip attachment. A brief description of each process follows.

Figure 9 - Flip Chip Assembly Process

#### 3.4.1 Flip Chip Solder Bumping

Solder bumping is the process by which solder is deposited onto the die. There are several methods utilized for bump deposition, which depend upon the materials chosen for the solder and the chip design. Three of the most common methods are solder evaporation, solder electroplating and solder screen printing. Screen printing is used as the deposition method when the pitch size is large. Screen printing is much cheaper than either evaporation or plating techniques. Solder bumps should be evaluated in terms of their electrical, mechanical and material properties. From an electrical point of view the solder bump should provide a low resistance electrical path. From a mechanical point of view the bump interface must form a bond of sufficient strength in order to maintain

integrity during normal operating conditions. Another important mechanical property is the uniformity of the bump geometry across a die. Common defects include missing bumps, damaged or non-spherical bumps, pattern deviations and passivation damage.

#### 3.4.2 Flux Dispense and Component Placement

Flip chips can be placed onto the substrate using automated pick and place SMT equipment. SMT equipment utilizes a machine vision system to achieve the necessary placement accuracy. Flux is applied to either the flip chip (using a dip method) or to the substrate (using a screen printing method) prior to the actual placement of the chip. The flux aids in the wetting of the solder by removing oxides from the surface of the bond pads. Flux also serves as a tacky agent to hold the flip chip in place during solder reflow.

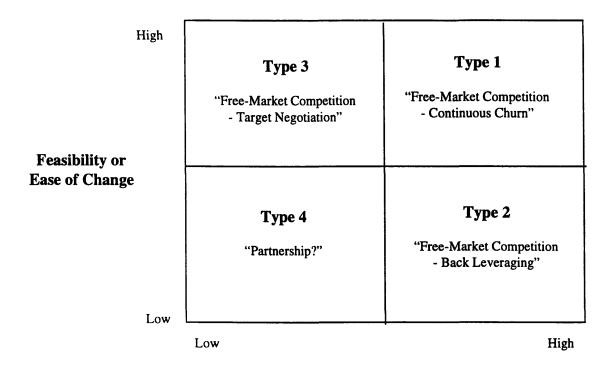

#### **3.4.3** Reflow