PS/RF/Note 96-03 8 January 1996

## RF AMPLITUDE NORMALIZER (PS/RF-HC 3189)

M. Paoluzzi

## 1. CIRCUIT DESCRIPTION

The rf amplitude normalizer (shown in figure 1.1) provides two variable gain amplification chains (IC 2, IC3,Q1, Q2) with a maximum gain of ~76 dB.

Each of the two variable gain amplifiers contained in the AD 600JN has a -3 dB bandwidth of 35 MHz and the two units contained in a chip are cascaded to obtain the required dynamic range.

Gain control is internally provided by an AVC loop (half of IC1 plus detector) which stabilizes the Out Gap signal at +4 dBm ( 1Vp-p ).

The gain of both chains is then

G = +4 dBm - Pin gap [dB]

The gain control voltage follows a logarithmic law with a scaling of ~ 64 dB/V with 0 dB corresponding to ~ -55 mV.

Figure 1.1 - Circuit Schematic Diagram

At the price of a reduced dynamic range the AVC loop compensates the gain loss at high frequency due to amplifier bandwidth and this results in a deviation of the gain control voltage scaling for frequencies higher than 10 MHz.

Half of IC 1 is used as a comparator and its output (SK3 pin 6A) will be high when the rf present on the Gap input will be higher than the level selected by an external reference (SK3 pin 7A).

The external reference scaling corresponds to the gain control voltage but with inverted in sign.

To maintain the signal quality over the whole dynamic and frequency ranges, adequate isolation between inputs and outputs of the two amplifying chains had to be provided. This is obtained by the layout and the shielding plate (PS/RF-HC 3189/8-4) installed on the printed circuit W-Side (behind IC1 and IC3).

## 2. TECHNICAL CHARACTERISTICS

The main characteristics of the circuit are listed in table 2.1 and plotted in the following figures.

| Parameter                   | Value      | Units | Notes                       |

|-----------------------------|------------|-------|-----------------------------|

| Frequency Bandwidth         | 0.2 to 20  | MHz   |                             |

| In Gap Amplitude Range      | +4 to -60  | dBm   |                             |

| Out Gap Amplitude           | +4 +/- 0.5 | dBm   |                             |

| Grid In - Out Gain          | 0 to 60    | dB    | see text                    |

| Gap - Grid Gain Difference  | < 0.5      | dB    | +4  dBm < Gap In < -46  dBm |

|                             | <0.6       |       | -46 dBm < Gap In < -56 dBm  |

|                             | < 0.7      |       | +56 dBm < Gap In < -60 dBm  |

| Gap - Grid Phase Difference | < 2        | deg   | +4 dBm < Gap In < -36 dBm   |

|                             | <3         |       | -36 dBm < Gap In < -56 dBm  |

|                             | < 5        |       | +56 dBm < Gap In < -60 dBm  |

| Out Gap Settling Time       | < 100      | μs    |                             |

Table 2.1 - Rf Normalizer Specifications

Figure 2.1 - Gap Chain T.F P = +4 dBm Figure 2.2 - Gap Chain T.F P = -56 dBm

## **3. ADJUSTMENT**

|               | By visual inspection verify that the module does not present evident                                                                                                                                                                                 |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | By visual inspection verify that the module does not present evident                                                                                                                                                                                 |

| SI<br>U<br>pl | nanufacture errors and verify on the printed circuit welding side that all<br>SMD components are present.<br>Using the mechanical supports mount the module on a good conducting<br>plane.<br>Also verify that the module has been properly cleaned. |

**Power Supplies and Reference Voltage Test**

| 2.1 | Verify that +/-6 V are present on IC1 pins 4 and 8 respectively.              |

|-----|-------------------------------------------------------------------------------|

| 2.2 | Verify that on R7 the voltage on one side is -12 V and on the other side is - |

|     | 6.2 V +/-5%                                                                   |

| 3   | Input Matching Measurement                                                    |

|-----|-------------------------------------------------------------------------------|

|     |                                                                               |

|     |                                                                               |

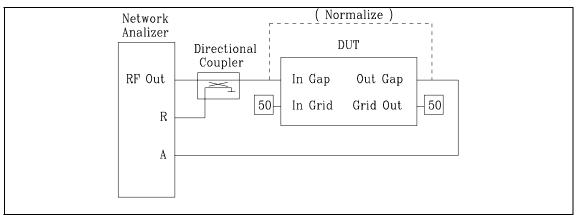

| 3.1 | By means of the test set-up shown in figure 4.1 verify that the return losses |

|     | of inputs 'IN GAP' and 'IN GRID' are better than -18 dB in the frequency      |

|     | range 200 kHz 20 MHz .                                                        |

| 4   | Output Level Adjustment                                                                                               |

|-----|-----------------------------------------------------------------------------------------------------------------------|

|     |                                                                                                                       |

|     |                                                                                                                       |

| 4.1 | Apply a 1 MHz, 100 mV peak signal on input 'IN GAP' and adjust P1 so as to obtain 500 mV peak on the output 'OUT GAP' |

| 5   | Transfer Function Measurement                                                                                                                                                  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |                                                                                                                                                                                |

|     |                                                                                                                                                                                |

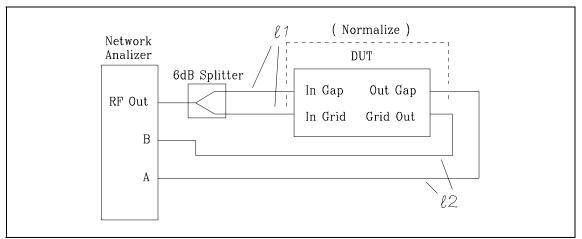

| 5.1 | By means of the test set-up shown in figure 4.2 verify that the transfer function for the given input power lays within the specified limits (figures 2.1, 2.2 and Table 2.1). |

| 6   | Output Amplitude and Phase Difference Measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

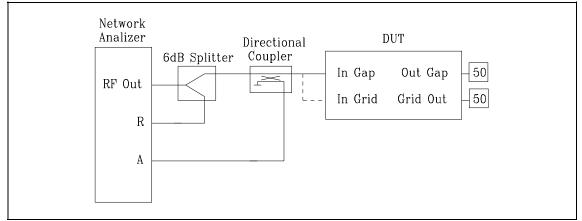

| 6.1 | By means of the test set-up shown in figure 4.3 measure the gain and phase differences between 'OUT GAP' and 'OUT GRID'.<br>Verify that the gain and phase differences for the given input powers lay within the specified limits (figures 2.3, 2.4, 2.5, 2.6 and table 2.1).<br>If the phase difference lays within the specified limits no length compensation is required and <i>I</i> for the module labeling is 0.<br>If the phase difference exceeds the specified limits try to adjust the elecrical delay on the network analizer (Grid Input ) so as to compensate for the error. If this manipulation succeeds then take note of the required <i>I</i> for the module labeling. |

| 7 | Miscellaneous Measurements |

|---|----------------------------|

|   |                            |

|   |                            |

| 7.1 | Check that with both inputs 'IN GAP' and 'IN GRID' the output noise does     |

|-----|------------------------------------------------------------------------------|

|     | not exceed $\pm$ 100 mV and that the voltage on R20 is $\ge$ 1.5 V.          |

| 7.2 | Apply to 'IN GAP' a 1MHz -40dBm signal and verify that applying on           |

|     | SK3, pin 7A a voltage of -700 mV, pin 1 of IC1 goes positive while with a    |

|     | voltage of -650 mV it goes negative.                                         |

| 7.3 | Apply to 'IN GAP' a 20MHz -40dBm signal and verify that applying on          |

|     | SK3, pin 7A a voltage of -800 mV, pin 1 of IC1 goes positive while with a    |

|     | voltage of -740 mV it goes negative.                                         |

| 7.4 | Apply on both inputs a 1 MHz signal and check on a scope that the outputs    |

|     | remains sinusoidal when the input signal amplitude lays in the range -56     |

|     | dBm to $+10 dBm$ .                                                           |

| 7.5 | Apply to 'IN GAP' a 1 MHz 200 mV peak rf burst of length $> 200 \ \mu s$ and |

|     | check that 'OUT GAP' stabilizes to 500 mV peak within 100 $\mu$ s.           |

At the end of the procedure put a drop of paint on P1, label the module ' $\Delta \ell = xx$  ns' (the value has been computed at point 6.1) and 'OK + DATE'.

Figure 4.1 - Input Matching Measurement Set-Up

Figure 4.2 - Transfer Function Measurement Set-Up

Figure 4.3 - Amplitude and Gain Difference Measurement Set-Up