### Compiling for Coarse-Grain Reconfigurable Architectures

by

M. Morris E. Matsa

Submitted to the Department of Electrical Engineering and Computer Science

in partial fulfillment of the requirements for the degree of

Master of Engineering in Computer Science and Engineering

at the

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

June 1997

© M. Morris E. Matsa, MCMXCVII. All rights reserved.

The author hereby grants to MIT permission to reproduce and distribute publicly paper and electronic copies of this thesis document in whole or in part, and to grant others the right to do so.

.:

Author ..... Department of Electrical Engineering and Computer Science May 23, 1997 Certified by ..... Thomas F. Knight, Jr. Senior Research Scientist sis Supervisor Accepted by ..... Arthur C. Smith Chairman, Department Committee on Graduate Theses

#### **Compiling for Coarse-Grain Reconfigurable Architectures**

by

M. Morris E. Matsa

Submitted to the Department of Electrical Engineering and Computer Science on May 23, 1997, in partial fulfillment of the requirements for the degree of Master of Engineering in Computer Science and Engineering

#### Abstract

Increasing silicon area and inter-chip communication costs allow and require that modern general purpose computing devices incorporate large amounts of processing on a single die. The increased area permits a wider choice of architectures to perform this computation. The traditional approach to utilizing this silicon area is to place one, or a few, large processing elements on the die (microprocessors). This style of computation achieves its performance by dynamically issuing new instructions at a very high rate. On the other hand, it has long been recognized that much faster, more efficient processing is possible using application-specific and, even more significantly, computation-specific processing elements. More recently, academic and industry efforts have been working to use very fine-grain reconfigurable devices (such as FPGAs) in order to attain this performance. Instead of large processors, these devices place a large number of very small processing elements on the die, and connect them in a configurable network. Coarse Grain Reconfigurable Architectures (CGRAs) are a hybrid of these architectures, one that is capable of both dynamic instruction streams and application-specific optimizations. Depending on the way in which a CGRA is configured to run a given application, it can emulate a processor solution, a fine-grain reconfigurable device, or a hybrid between the two. Although initial indications are that CGRAs will be very efficient, it is not yet known how to best design these devices. Our group has implemented a prototype CGRA device called MATRIX. This thesis introduces several intermediate representations for the configuration of a MATRIX chip, each with the ability to specify higher level concepts than the previous languages and thus better suited to describing the algorithm being implemented while avoiding the unimportant configuration details. We then describe new tools that have been designed to convert these representations into an application to run on MATRIX. To compile the more advanced intermediate representations these tools include placement, routing, and power minimization algorithms. Using these tools, we compile down specific applications and emulations of many different general purpose computing architectures in order to achieve a better understanding of how to most efficiently program using MATRIX. After compiling for MATRIX, we vary the backend of the compiler so that we can experiment with compiling for similar architectures in an effort to analyze the usefulness of the various features of this architecture. In this way, we learn which of MATRIX's features are useful for mapping various applications, and we make design suggestions for general CGRAs. We also develop insights into techniques for placement and heuristics for using these hybrid architectures. Finally, by designing an intermediate representation which can be compiled from a high-level language, as well as being easily converted into an application running on MATRIX, we will help define the role of high-level synthesis in compiling for Coarse Grain Reconfigurable Architectures.

Keywords: CAD, FPGA, Coarse Grain, Reconfigurable, Placement, Routing, Power Minimization, High-Level Synthesis

Thesis Supervisor: Thomas F. Knight, Jr. Title: Senior Research Scientist

### Acknowledgments

I would like to thank everyone in my life, but it seems most appropriate to use this space to thank the people in the Reinventing Computing group at the MIT Artificial Intelligence Laboratory.

- Ethan Mirsky and Ian Eslick for developing MATRIX and for introducing me to the group, without which I could not have written this thesis. I used several figures from Ethan's thesis.

- Jeremy Brown and Amit Patel for being my officemates. Amit put up with me while I was testing MATRIX and Jeremy put up with me while I did my thesis.

- Yael Levi, a high school student from the RSI program, for being the first person to attempt programming for MATRIX without understanding the hardware. Working with Yael gave me a better idea of how to abstract MDL+ from MATRIX. She also contributed to the polynomial example of chapter 6.

- André DeHon. Many of the ideas in here originated as his. MATRIX is a direct result of his years of work into the nature of computing, and MDL+ is a direct result of discussions with him at the beginning of my research. My ramblings about high-level synthesis and the future of computing are largely a result of our discussions and our reading of the literature.

- Daniel Hartman was involved in all levels of the design of the MATRIX chip, including most of the layout. An EECS renaissance man, he also discussed a few high-level synthesis papers with me, as well as discussing a plethora of MDL+ issues with me both specific details and general views about the future of MATRIX, MDL, and computing. I believe that Dan is the only person who actually dared read through my code. "My god, you are a 6-3."

- Thomas F. Knight, Jr., without whom the Reinventing Computing group would not even exist. It has been said behind his back that he is the kind of thesis advisor that other students wish they had.

- The United States of America, the Department of Defense, the Advanced Research Projects Agency, and all United States taxpayers.

This research is supported by the Advanced Research Projects Agency of the Department of Defense under Rome Labs contract number F30602-94-C-0252.

# Contents

| 1 | Introduction |                                   |    |

|---|--------------|-----------------------------------|----|

| 2 | The          | e MDL Family of Languages         | 21 |

|   | 2.1          | Background                        | 21 |

|   | 2.2          | An Abstract view of MDL languages | 24 |

|   | 2.3          | The Anatomy of the MDL+ compiler  | 26 |

|   | 2.4          | Multi-level MDL+ Programming      | 29 |

| 3 | MA           | TRIX                              | 31 |

|   | 3.1          | Architecture Overview             | 31 |

|   | 3.2          | Basic Unit                        | 32 |

|   | 3.3          | Interconnect Network              | 34 |

|   | 3.4          | Network Ports                     | 36 |

|   | 3.5          | Control                           | 38 |

|   | 3.6          | Deployable Resources              | 39 |

| 4 | MD           | DL+ as Better MDL                 | 41 |

|   | 4.1          | Language Basics                   | 42 |

|   |              | 4.1.1 Basic Statement Structure   | 42 |

|   |              | 4.1.2 Identifiers                 | 43 |

|   |              | 4.1.3 Numbers                     | 43 |

|   |              | 4.1.4 Compare/Reduce Numbers      | 43 |

|   |              | 4.1.5 Don't Cares                 | 44 |

|   |              | 4.1.6 Copying Constructs          | 44 |

|     | 4.1.7  | Inheritance 4                   | 4        |

|-----|--------|---------------------------------|----------|

|     | 4.1.8  | Reserved Words <sup>*</sup>     | 5        |

|     | 4.1.9  | Lists                           | <b>5</b> |

|     | 4.1.10 | Ordering Directions             | 6        |

|     | 4.1.11 | Going Beyond MATRIX 4           | 6        |

|     | 4.1.12 | Definitions                     | 7        |

|     | 4.1.13 | Type Checking 44                | 9        |

|     | 4.1.14 | Output                          | 0        |

| 4.2 | Langu  | age Constructs                  | 1        |

|     | 4.2.1  | Constants                       | 1        |

|     | 4.2.2  | Bitvecs                         | 2        |

|     | 4.2.3  | Sub-BFU Constructs              | 4        |

|     | 4.2.4  | BFU Networks                    | 5        |

|     | 4.2.5  | BFU Configs                     | 6        |

|     | 4.2.6  | BFU Controls                    | 0        |

|     | 4.2.7  | BFU Powers                      | 4        |

|     | 4.2.8  | Ports                           | 5        |

|     | 4.2.9  | BFU Ports                       | 8        |

|     | 4.2.10 | Memories                        | 0        |

|     | 4.2.11 | BFUs 8                          | 1        |

|     | 4.2.12 | Layouts                         | 4        |

|     | 4.2.13 | Connects                        | 8        |

|     | 4.2.14 | IOports                         | 0        |

|     | 4.2.15 | Chips                           | 1        |

|     | 4.2.16 | Summary 9                       | 4        |

| 4.3 | Auton  | natic Driving Phase             | 5        |

|     | 4.3.1  | Motivation for Driving 9        | 15       |

|     | 4.3.2  | What the Driver Does            | 96       |

|     | 4.3.3  | Programming in MDL+1.1          | )1       |

| 4.4 | Error  | Reporting and Interface Details | 12       |

| 5 | Inte | lligent | Phases of the MDL+ Compiler        | 105 |

|---|------|---------|------------------------------------|-----|

|   | 5.1  | The M   | IDL+ Router                        | 111 |

|   |      | 5.1.1   | Syntax                             | 111 |

|   |      | 5.1.2   | Semantics                          | 112 |

|   |      | 5.1.3   | 8-Bit Microprocessor               | 114 |

|   |      | 5.1.4   | Benefits                           | 115 |

|   | 5.2  | The M   | IDL+ Placer                        | 116 |

|   |      | 5.2.1   | Syntax                             | 117 |

|   |      | 5.2.2   | Semantics                          | 117 |

|   |      | 5.2.3   | 8-Bit Microprocessor               | 119 |

|   |      | 5.2.4   | Benefits                           | 120 |

|   | 5.3  | The M   | IDL+ Grouper                       | 121 |

|   |      | 5.3.1   | Syntax                             | 121 |

|   |      | 5.3.2   | Semantics                          | 122 |

|   |      | 5.3.3   | 8-Bit Microprocessor               | 123 |

|   |      | 5.3.4   | Benefits                           | 125 |

|   | 5.4  | Impro   | ovements to MDL+ code              | 125 |

| 6 | Res  | earch   | done with MDL+                     | 127 |

|   | 6.1  | Exam    | ples                               | 128 |

|   |      | 6.1.1   | 8-Bit Microprocessor               | 129 |

|   |      | 6.1.2   | Polynomial Evaluator               | 133 |

|   |      | 6.1.3   | Other Examples                     | 137 |

|   | 6.2  | Gener   | al Purpose Computing Architectures | 137 |

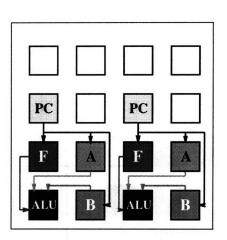

|   |      | 6.2.1   | 8-Bit Microprocessor               | 138 |

|   |      | 6.2.2   | 32-Bit Microprocessor              | 138 |

|   |      | 6.2.3   | MIMD                               | 142 |

|   |      | 6.2.4   | VLIW                               | 145 |

|   |      | 6.2.5   | SIMD                               | 149 |

|   |      | 6.2.6   | ASIC                               | 150 |

|   | 6.3 | Other  | CGRAs                      | 150 |

|---|-----|--------|----------------------------|-----|

|   |     | 6.3.1  | Eliminating Level-2 wires  | 150 |

|   |     | 6.3.2  | Unregistered Level-2 Wires | 151 |

|   |     | 6.3.3  | No level-1 wires           | 151 |

|   |     | 6.3.4  | No diagonal lines          | 152 |

|   |     | 6.3.5  | No length-2 lines          | 153 |

|   |     | 6.3.6  | Other Experiments          | 156 |

|   | 6.4 | Questi | ions about MATRIX          | 156 |

|   |     | 6.4.1  | Level-2 lines              | 156 |

|   |     | 6.4.2  | Level-1 lines              | 158 |

|   |     | 6.4.3  | Inputs to BFU ports        | 159 |

|   |     | 6.4.4  | OR Plane                   | 159 |

|   |     | 6.4.5  | Control                    | 160 |

|   |     | 6.4.6  | Other Questions            | 161 |

| 7 | Com | clusio | . 1                        | 163 |

| ( |     |        |                            |     |

|   | 7.1 |        |                            | 163 |

|   |     | 7.1.1  | Code Generating MDL+       | 163 |

|   |     | 7.1.2  | MDL+'s Grammar             | 166 |

|   |     | 7.1.3  | Output and Error Messages  | 170 |

|   | 7.2 | New I  | nsights                    | 176 |

|   |     | 7.2.1  | Manual Placement           | 177 |

|   |     | 7.2.2  | How to use MDL+            | 179 |

|   |     | 7.2.3  | MATRIX's Strong Points     | 181 |

|   | 7.3 | Future | e Work                     | 182 |

|   |     | 7.3.1  | Basic MDL+                 | 182 |

|   |     | 7.3.2  | Driver                     | 184 |

|   |     | 7.3.3  | Router                     | 186 |

|   |     | 7.3.4  | Placer                     | 186 |

|   |     |        | Grouper                    | 188 |

|              | 7.3.6 High-Level Synthesis              | 190 |

|--------------|-----------------------------------------|-----|

|              | 7.3.7 CGRAs                             | 191 |

| A            | MDL+ version 1.0 Grammar                | 193 |

| в            | MDL+ Man Pages                          | 197 |

| С            | MDL+ Globally Reserved Words            | 201 |

| D            | 8 Bit Microprocessor implemented in MDL | 205 |

|              | D.1 MDL                                 | 205 |

|              | D.2 MDL+1.1                             | 211 |

|              | D.3 MDL+1.2                             | 212 |

|              | D.4 MDL+1.3                             | 213 |

|              | D.5 MDL+1.4                             | 215 |

| $\mathbf{E}$ | Full MDL+ Grammar                       | 217 |

# List of Figures

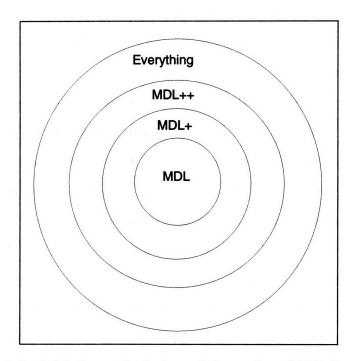

| 2-1  | A Mathematical view of the various MDL Languages          | 25 |

|------|-----------------------------------------------------------|----|

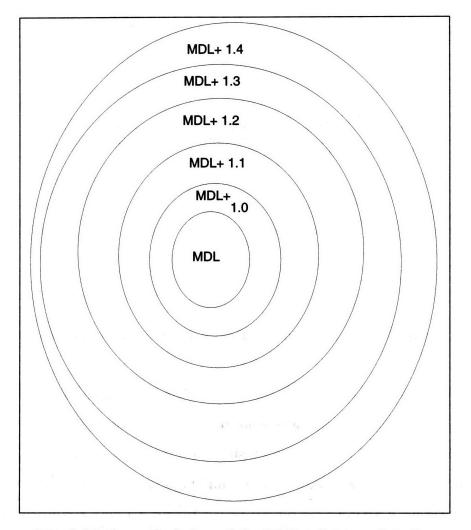

| 2-2  | A Mathematical view of the MDL+ Intermediate Languages    | 27 |

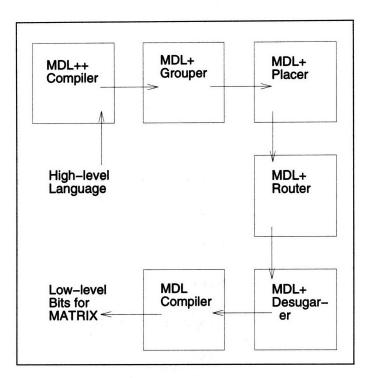

| 2-3  | A Block Diagram of the proposed MDL++ Compiler            | 28 |

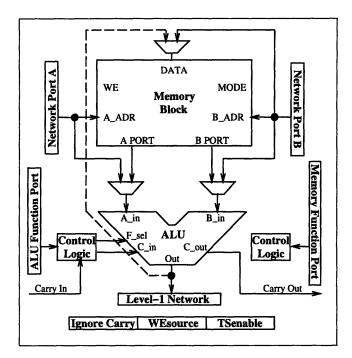

| 3-1  | MATRIX Basic Functional Unit                              | 33 |

| 3-2  | Level 1 Network Connections                               | 34 |

| 3-3  | Level 2 Network Connections                               | 35 |

| 3-4  | MATRIX Network Switch Architecture - BFU Cell             | 36 |

| 3-5  | Function Port Architecture                                | 37 |

| 3-6  | BFU Control Logic                                         | 38 |

| 3-7  | Distributed PLA                                           | 39 |

| 4-1  | Source code that does not type-check                      | 50 |

| 4-2  | Typical error message for code that does not type-check   | 50 |

| 4-3  | Sample Bitvec Definition                                  | 63 |

| 4-4  | BFU Control Logic                                         | 71 |

| 4-5  | Four Ways to define a simple C/R II value                 | 73 |

| 4-6  | Nine ways to define a Port                                | 77 |

| 4-7  | Sample BFU Ports definition                               | 80 |

| 4-8  | Sample BFU Definition                                     | 83 |

| 4-9  | Sample Error Message for over-shifting a non-DC BFU       | 86 |

| 4-10 | One BFU replicated 36 times by placing Layouts in Layouts | 87 |

| 4-11 | A typical Connect                                         | 89 |

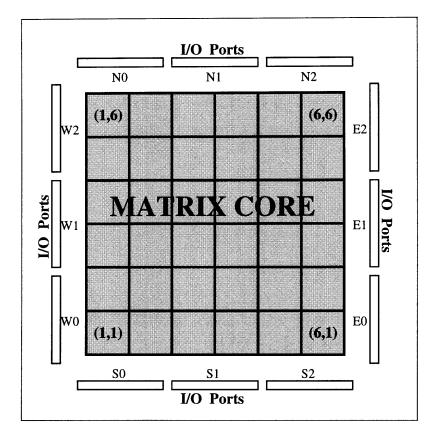

| 4-12 | Block Diagram of a MATRIX Chip with IOport names          | 93 |

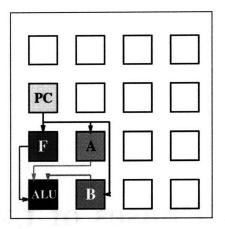

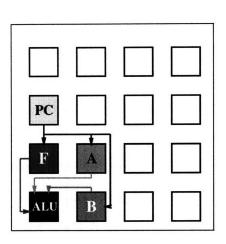

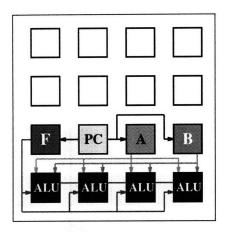

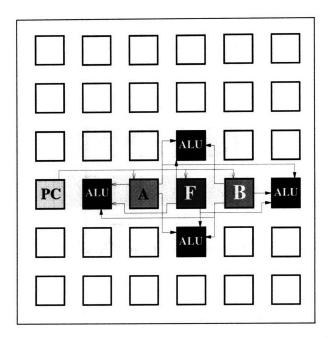

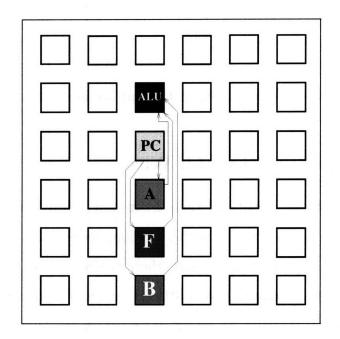

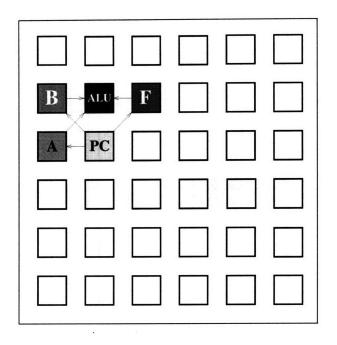

| 5-1   | 8 Bit Microprocessor on MATRIX                                        | 106         |

|-------|-----------------------------------------------------------------------|-------------|

| 5-2   | PC definition in MDL+1.1                                              | 107         |

| 5-3   | I-store definition in MDL+1.1                                         | 108         |

| 5-4   | Definitions of A, B, and F in MDL+1.1                                 | 109         |

| 5 - 5 | Definition of ALU in MDL+1.1                                          | 110         |

| 5-6   | Definition of Layout in MDL+1.1                                       | 110         |

| 5-7   | Definition of Layout in MDL+1.3                                       | 120         |

| 5-8   | Definition of Memory Objects in MDL+1.4                               | 124         |

| 5-9   | Definition of ALU Object in MDL+1.4                                   | 124         |

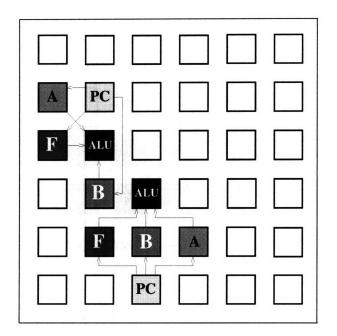

| 6-1   | 8 Bit Microprocessor on MATRIX, placed by a human                     | 129         |

| 6-2   | 8 Bit Microprocessor on MATRIX, automatically placed with mdl -2 $$ . | 132         |

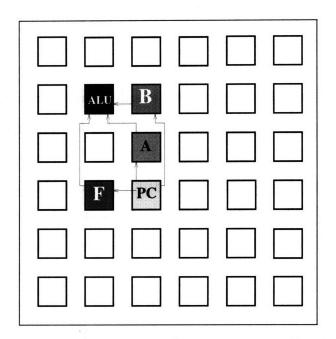

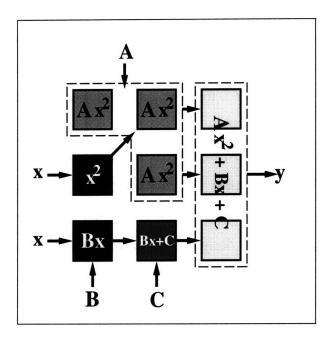

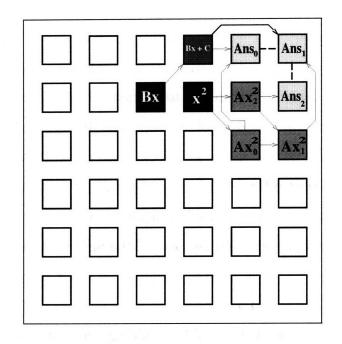

| 6-3   | Polynomial Evaluator designed by a human                              | 134         |

| 6-4   | Polynomial Evaluator as placed by the compiler                        | 136         |

| 6-5   | 32 Bit Microprocessor on MATRIX, placed by a human                    | 1 <b>39</b> |

| 6-6   | 32 Bit Microprocessor on MATRIX, automatically placed with mdl -2 $$  | 140         |

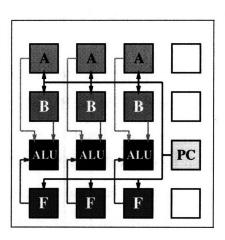

| 6-7   | MIMD Architecture on MATRIX, placed by a human                        | 14 <b>3</b> |

| 6-8   | MIMD Architecture on MATRIX, automatically placed with mdl -2         | 144         |

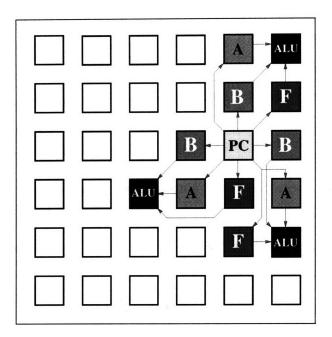

| 6-9   | VLIW Architecture on MATRIX, placed by a human                        | 145         |

| 6-10  | VLIW Architecture on MATRIX, automatically placed with mdl -2         | 147         |

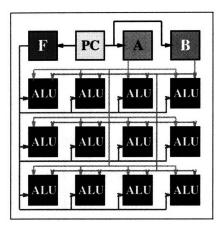

| 6-11  | SIMD Processor on MATRIX                                              | 149         |

| 6-12  | 8-bit microprocessor routed without level-1 lines                     | 152         |

| 6-13  | 8-bit microprocessor routed without diagonal level-1 wires            | 153         |

| 6-14  | 8-bit microprocessor routed without length-2 level-1 wires            | 154         |

| 6-15  | VLIW architecture routed without length-2 level-1 wires               | 155         |

| 7-1   | Examining an MDL+ verilog output file                                 | 174         |

| 7-2   | MDL+ code that does not make sense                                    | 184         |

# List of Tables

| 4.1  | String meanings in (const String) structure       | 53 |

|------|---------------------------------------------------|----|

| 4.2  | Strings in Static Source Structures               | 54 |

| 4.3  | Strings defining Selection Values                 | 59 |

| 4.4  | Strings defining Enable Values                    | 60 |

| 4.5  | Quick Summary of Types of Constants               | 61 |

| 4.6  | Quick Summary of Constants                        | 62 |

| 4.7  | Values in a Bitvec                                | 63 |

| 4.8  | Quick Summary of Bitvecs                          | 64 |

| 4.9  | Meaning of l2_d1 and l2_d2                        | 66 |

| 4.10 | Quick Summary of BFU Networks                     | 66 |

| 4.11 | Flags allowed in BFU Configs                      | 67 |

| 4.12 | Sources for Left and Right Flags                  | 69 |

| 4.13 | Quick Summary of BFU Configs                      | 69 |

| 4.14 | Control argument keywords and associated hardware | 70 |

| 4.15 | ReduceII Arguments                                | 72 |

| 4.16 | ReduceII Bit-Desc Legal Arguments                 | 72 |

| 4.17 | Quick Summary of BFU Controls                     | 74 |

| 4.18 | Quick Summary of BFU Powers                       | 75 |

| 4.19 | Ways to define a Value of a Port                  | 76 |

| 4.20 | Ways to define a Constant Number, for TScycle     | 78 |

| 4.21 | Quick Summary of Ports                            | 78 |

| 4.22 | Names for BFU Ports                               | 79 |

| 4.23 | Quick Summary of BFU Ports                        | 80 |

| 4.24 | Quick Summary of Memories                               | 81  |

|------|---------------------------------------------------------|-----|

| 4.25 | Quick Summary of BFUs                                   | 84  |

| 4.26 | Ways to define a Constant Number for Layout Coordinates | 85  |

| 4.27 | Quick Summary of Layouts                                | 87  |

| 4.28 | Quick Summary of Connects                               | 89  |

| 4.29 | Quick Summary of IOports                                | 91  |

| 4.30 | Quick Summary of Chips                                  | 94  |

| 4.31 | MDL+ Constructs                                         | 95  |

| 5.1  | Length of 8-bit microprocessor implementations          | 126 |

| C.1  | Global Keywords in MDL+, part 1 of 2                    | 202 |

| C.2  | Global Keywords in MDL+, part 2 of 2                    | 203 |

# Chapter 1

## Introduction

Continuing advances in semiconductor technology have greatly increased the amount of processing that can be performed by single-chip general purpose computing devices. In addition, the relatively slow increase of inter-chip communication bandwidth requires that modern high performance devices use as much of their potential on-chip processing power as possible. This results in large, dense ICs and a large design space for general purpose computing architectures.

There are several ways of viewing this design space, one way being in terms of granularity. Designers have the option of building very large processing units, or many smaller ones, in the same space. Traditional architectures are either very coarse grain, such as microprocessors, or very fine grain such as FPGAs (Field Programmable Gate Arrays). Both have their own advantages and disadvantages.

Very coarse grain devices, such as microprocessors, incorporate very few large processing units which operate on wide data-words. Each unit is hardwired to perform a small set of instructions on these data-words. Usually each unit is optimized for a different set of instructions, such as integer and floating point, and the units are generally hardwired to operate in parallel. The hardwired nature of these units allows them to very rapidly perform their instructions. In fact, a great deal of area on modern microprocessor chips is dedicated to cache memories in order to support a very high rate of instruction issue. This allows these devices to efficiently handle very dynamic instruction streams. Unfortunately, because microprocessors and other coarse-grain computing devices are highly optimized for simple, wide-word, dynamic instructions, they are relatively inefficient when performing other kinds of operations. For example, many cycles are required to build up a complex operations which are not part of the pre-selected instruction set, out of the processor's instructions. In addition, when performing short-word operations, a large amount of the device's processing power is not utilized.

On the other end of the design space, very fine grain devices, such as FPGAs, incorporate a large number of very small processing elements. These elements are arranged in a configurable interconnect network so that larger structures can be built out of them. The configuration data used to define the functionality of the processing units and network can be thought of as a very large, semantically powerful, instruction word. Nearly any operation can be described, and mapped to hardware. In general, this allows these devices to perform any particular operation faster than a coarse-grain, microprocessor-like, device.

However, the size of this "instruction word" creates a number of problems with fine-grain devices. First of all, reloading this instruction takes a relatively long time, making dynamic instruction streams very difficult for these devices. Secondly, if the operation being performed is, in fact, a wide word operation, a great deal of this "instruction word" must be dedicated to re-describing the operation for each of the small processing elements. Thus, fine grain processing elements are also not equipped to take advantage of a large number of common computing operations.

The increasing available silicon area means that it is now possible to build a large number of intermediate-grain processing elements. MATRIX (*Multiple ALU Architecture with Reconfigurable Interconnect Experiment*) [MD96] is the first such Coarse Grain Reconfigurable Architecture (CGRA) exploiting the regularity and rapid instruction issue features of coarse-grain units, but still allowing these units to be connected in an application-specific manner. This means that it is capable of deploying its coarse-grain resources, such as memory and processing, in a way that takes advantage of the opportunities for optimization present in any given problem.

Another way to view the design space is by the way in which the resources of the

chip are being reused. Designers have the option of building processing units which can be quickly reused in time, changing the operation they perform each cycle, or many smaller ones which will not change what they do as quickly, but will make use of all of the space on the chip.

Very coarse-grain devices, such as microprocessors, although they do waste a lot of area (such as an FPU during an application that only does integer arithmetic), reuse the complete ability of the chip each cycle, by doing an entirely new operation. Very fine-grain devices, such as FPGAs, have small hard-wired units which do not change their operation often, but there are usually tens of thousands of these units on a single chip, all of which can be doing useful operations in parallel at the same time, thus all of the spatial resources of the chip are being used. Chips that are using all of the temporal resources of the chip can not run faster than their slowest operation, and can not use their wasted area to parallelize a problem. Thus, they will not be fast, but they will not take up a lot of space. On the other side, chips that are using all of their spatial resources can run as quickly as the application dictates, but will spread out in area while parallelizing the application in order to compensate for using generalized fine-grain units instead of instruction-specific hardware (e.g. a multiplier). Thus, they will use a lot of space but will run quickly.

This space thus constitutes a view of the basic space-time tradeoff. CGRAs can, after fabrication time, allocate parts of the chip to a microprocessor-like implementation for a part of an application that does not require high-throughput, while using more space for the parts of the application that do require high-throughput by using FPGA-like implementations. This means that CGRAs can make better space-time tradeoffs on a per-application basis by deploying a lot of its space resources when faced with high-throughput constraints, and using its time resources to save on space by reusing some of its area through time when faced with low-throughput constraints.

In this thesis, we study only the CGRA MATRIX, and attempt to apply our knowledge to CGRAs and this entire space. Since MATRIX is a means of combining elements of different architectures, there should be an intermediate language expressible in terms of certain architectures which compiles to MATRIX. While other group members have designed the actual layout for MATRIX, and a verilog simulation of it, this thesis will design this intermediate language as well as the tools to compile it down, and investigate high-level synthesis possibilities for MATRIX.

The first step in this process is specifying this new intermediate language, the new MATRIX Description Language (MDL+), to succeed the old MATRIX Description Language (MDL). Chapter 2 discusses the high-level motivations for designing MDL+, and the mathematical view of MDL+ as a member of a family of intermediate languages, such that it is a step on the road towards a high-level language which is easily compiled down for CGRAs using high-level synthesis techniques.

Once the framework for the design of MDL+ is set, chapter 3 will describe the actual MATRIX chip in sufficient detail to allow for a complete specification of the MDL+ language. Chapter 4 will then go into great detail about the syntax and semantics of MDL+, as well as describing the effects of the MDL+ compiler's Automatic Driving Phase, and providing a basic coverage of the interfaces and error reporting mechanisms of the new MDL+ compiler.

Chapter 5 will go on to discuss the intelligent phases of the MDL+ compiler which can automatically group high-level functionality into MATRIX constructs, place MATRIX constructs on a MATRIX chip, and route the interconnect between these units on a MATRIX chip. Through some discussion of how these phases of the compiler were designed and how they act, we will begin to understand how to better program for MATRIX, how to design CGRAs to be easily programmed, and how a high-level synthesis compiler might compile high-level code to an MDL+ backend.

Chapter 6 will then attempt to learn more about these issues by using the MDL+ compiler to study both MATRIX and MDL+. This will include implementing example applications in MDL+, examining various general-purpose computing architectures modeled in MDL+, and studying the effects of modifying the backend of the MDL+ compiler.

Finally, Chapter 7 will summarize the benefits of MDL+ and the MDL+ compiler over the previous state-of-the-art, as well as discussing what we have learned about programming for CGRAs and about designing CGRAs. It will end by suggesting directions for future work.

The most interesting material is the research that culminates in new heuristics for designing coarse-grain reconfigurable architectures and for using these architectures, including ideas about how to place and route for them. This material is located in chapter 6 and the second half of chapter 7.

### Chapter 2

### The MDL Family of Languages

This chapter is intended to convey the big picture of what MDL+ is about. This extends into the motivation behind MDL+ including the desires for an eventual language MDL++, and leads to an understanding of both the way MDL+ is implemented and the way it is explained in this document. Finally, understanding this view of MDL+ should enable people to understand the abstraction layers available when programming in MDL+ as well as the ways to take advantage of this power. We start with a brief description of the mathematical ideal (section 2.2) and quickly progress through the anatomy of an MDL+ compiler (section 2.3) to suggestions for how to program using the power of MDL+. (section 2.4) This section should provide the motivation and high-level understanding that will assist with the later chapters on the syntax and semantics details of MDL+. (chapters 4,5)

#### 2.1 Background

Before beginning the meat of this chapter, we provide a brief background of the languages and compiler phases that we will be referring to. They were all mentioned in chapter 1, and will be discussed in much more detail in later chapters, but this section is intended to provide enough detail about each until it itself is discussed.

MDL - This is the original Matrix Description Language, first introduced in [Esl95]. MDL is basically just a hardware description language for the MATRIX chip. MDL was quickly designed and a compiler was developed for it as a quick hack. Both the language and compiler were developed as a first-cut implementation. The language was a good start, but not able to support much functionality due to the amount of time put into the compiler. The language was also never completely specified. The MDL compiler eventually got most of the bugs worked out of it, but is probably still fairly buggy. It needs more power and flexibility, it does not have a sufficient interface for error reporting, and was never well documented. Reading through some of the MDL compiler's code verifies that it was a quick-hack project.

**MDL+** - This is the programming language developed for this thesis. It attempts to clean up both the specification of MDL and the implementation of the MDL compiler, as well as adding many nice programming features that MDL lacked or did not implement correctly, and adding higher-level programming possibilities. It is intended to be able to serve, with only slight changes, as a front-end to a compiler for various CGRAs besides MATRIX, and as a back-end to a compiler which performs high-level synthesis on a high-level language. Several of the ideas for improving MDL given in [Mat96b] have been incorporated into MDL+. Specification of the basic MDL+ language will be given in chapter 4.

MDL++ - This name is being reserved for the possible occurrence of a truly high-level compiler for MATRIX or other CGRA. MDL++ will be used throughout this thesis to describe an unspecified high-level language such as C or Silage, perhaps developed with MATRIX in mind, and the associated compiler which would turn this high-level code into configuration bits for MATRIX. Topics relating to MDL++ will be discussed in chapters 5 and 6, and a summary of suggestions for the design and implementation of MDL++ will be given in section 7.3.6.

Automatic Driving Phase - There are many interconnect wires on a MATRIX chip, and some must not be driven at any given time in order to conserve power and decrease heat. This phase of the MDL+ compiler determines whether each line is used by an MDL+ design, and might turn some wires on or off. The driver will be discussed in section 4.3.

Automatic Routing Phase - It is possible to specify an MDL+ design such that two units know that they are communicating with each other, but they do not know which of the many interconnect wires they are using. This phase of the MDL+ compiler sets both of those units so that they are communicating over a specific wire instead of merely knowing which unit they are communicating with. Once this is done, the driving phase can set used wires to be driven and others to be turned off. The router will be discussed in section 5.1.

Automatic Placing Phase - It is possible to specify in MDL+ that a unit should be on a chip, but not specify where on the chip that unit should be placed. This phase of the MDL+ compiler puts such units at specific locations on the chip. Once this is done, the routing phase can figure out which wires can and will be used to communicate with the unit. The placer will be discussed in section 5.2.

Automatic Grouping Phase - It is possible to specify in MDL+ that a chip should contain a higher-level object that does not precisely correspond to a physical unit that exists in the MATRIX hardware. This phase of the MDL+ compiler expresses such units as pieces of actual MATRIX hardware, and combines them to some extent, so that, for example, one basic unit on MATRIX might have one part of it acting as a logical register between two logical-objects, and also have another part of it acting as a logical memory unit. Once this is done, the placing phase can figure out where to put the actual MATRIX basic units on the chip. The grouper will be discussed in section 5.3.

High-Level Synthesis - This is the added functionality of the MDL++ compiler over the MDL+ compiler, or the process of turning a high-level language like C or Silage into a more hardware-oriented description. While high-level synthesis has gathered more definitions in the literature, this is the one we are referring to when we use the term in this thesis.

#### 2.2 An Abstract view of MDL languages

When beginning the planning stages for MDL+, several objectives naturally come to mind:

- **Programming Extensibility** It would be desirable to be able to use MDL code with the MDL+ compiler. In fact, it would be best if we could interlink pieces of MDL code with pieces of MDL+ code, for example have a legal MDL+ design where an MDL unit interacts with an MDL+ unit in the same chip layout.

- Multi-level code It would also be advantageous to possess the ability to let users enter code at many levels – even given the power of an automatic grouper, placer, and router, the user might have specifically tightly designed a certain subpart of the cell, and want it placed in a specific part of the chip or even routed exactly as specified. Thus, we want to provide the user access to MDL+ without automatic features, MDL+ with a router, MDL+ with a router and placer, and a completely automatic MDL+ with a grouper. Upon reviewing many projects and papers on high level synthesis (such as [RP90, GR94, WC95, CHM91, Wak91, NON91, HDDW93, MCG+90, LND+91, CSW93, RvSC+93]), it becomes clear that this is a key aspect of a high-level chip compiler.

- Human Interactions It would be best if human interaction could occur in both directions, receiving information from the compiler at each stage and giving it to the compiler at each stage. This means that in addition to being able to tell the compiler where you want particular units placed, you should be able to ask the compiler how the chip looked just before it was placed, so that you can try to then place by hand.

Given these objectives we decided to design a family of MDL languages, each being a superset of the previous ones, all based on MDL. Thus, any MDL code will be legal in any MDL+ intermediate language, and MDL+ code will be allowed in MDL++, but not necessarily in MDL. Finally, MDL++ is a subset of  $\Sigma^*$  (Everything). This "MDL view of the Universe" is shown in figure 2-1.

Figure 2-1: A Mathematical view of the various MDL Languages

Once we have decided on such a worldview, and given our objectives, it seems a natural decision to specify MDL+ as a family of languages that are strictly subsets of each other, all being supersets of MDL and all being subsets of MDL++.<sup>1</sup> We assign these MDL languages version numbers to correspond to the versions of the MDL+ compiler releases. Given that each language is a superset of the previous ones, each version of the compiler will be completely backwards-compatible, which was an implicit desire in our Programming Extensibility objective.

MDL+ version 1.0 is the same as MDL except that it is much easier to program in, essentially a language which could be desugared into the MDL Kernel. MDL+ 1.1 is a small step ahead, adding minor functionality which we no longer considered "just better MDL" but rather actually extensions to MDL. In practice, it is difficult to decide which basic improvements belong in MDL+1.0 and which should be considered additions available in MDL+1.1. Thus, we group all extensions besides the Automatic Driving Phase, and consider them to be in MDL+1.0 for practical discussions. Then,

<sup>&</sup>lt;sup>1</sup>Keep in mind through this discussion that MDL++ has never been specified, and might never be specified. This is just a suggestion for it.

the sole addition to the MDL+ compiler for version 1.1 becomes the Automatic Driving Phase. MDL+1.1 is then considered "basic MDL+" and it is this language that is discussed in chapter 4.

MDL+ 1.2 is a version of the compiler in which routing can be done automatically, and thus the language MDL+ 1.2 is one where explicit routing information can be omitted. MDL+ 1.3 can then omit placing information, and MDL+ 1.4 actually adds new constructs which can be defined (math-functional constructs instead of physical-functional constructs) which the MDL+1.4 compiler then automatically groups together into physical units that are available on MATRIX. These extensions to MDL+ are discussed in chapter 5. All of the MDL+ languages fit onto a "Bullseye of Languages" that is the middle piece of the above worldview. (Figure 2-2)

Designing the languages such that each one is a superset of the previous ones is natural, and thus easy, because each compiler does more automatically than the previous ones, allowing the user to either use new higher-level constructs (more stuff, so a superset) or allows the user to omit more information (more possibilities allowed, less constrained, so a superset). In short, the more the compiler does, the more the options the user has, and since we never remove any possibilities the user now has a superset of the possible programs that he can use in the new language.

#### 2.3 The Anatomy of the MDL+ compiler

Now that we have a good idea of how the various MDL+ languages will be related, in a mathematical sense, we need to specify how the compiler will be written. The mathematical definition gives us a clear idea of possible intermediate languages for the MDL+ compiler, namely the MDL+ 1.0 - MDL+ 1.4 languages. This is basically the direction we proceeded in. Since the compiler has an internal state that is not the lisp-like MDL+ code, it will not actually be storing these intermediate languages, but it will have internal state that will have a one-to-one mapping to these languages, and thus have the ability to print out the intermediate code as a user would understand it at any point. Although this code will lack the nice human-designed hierarchy of

Figure 2-2: A Mathematical view of the MDL+ Intermediate Languages

Figure 2-3: A Block Diagram of the proposed MDL++ Compiler

the original code, it still enables us to achieve our Human Interactions objective from above.

This design brings us to the picture of the MDL++ compiler shown in figure 2-3. Note that the output at each stage is not only corresponding to a legal intermediate-MDL+ code, but to all previous codes, since they were supersets of this intermediate language. However, these phases of the compiling process are not all just desugaring into some kernel of MDL+, but rather the compiler is actually automatically working on the code and adding new detail (without a unique choice for which detail), for example in the grouper, placer, and router pieces.

Of course, this figure is just a high-level view of the compiler as the actual MDL+ compiler does not make use of the MDL compiler. Nevertheless, the MDL+ compiler has a code generator which (while being better than the MDL compiler) could function as an MDL compilers' code generator. Similarly, MDL+ has a parser and scanner that can parse a superset of MDL, and thus could parse MDL.

#### 2.4 Multi-level MDL+ Programming

Proceeding through chapters 4 and 5, they will start by explaining the "inner" languages, that are subsets of the others, and then work outwards until they have explained all of MDL+. In this way we will progress forwards through the languages (simple to complex) and backwards through the phases of compilation (last to first). On a very real level, understanding of all intermediate languages is essential to the writing of good efficient MDL+ code.

By Multi-level programming we mean that we can achieve the Multi-level Code objective from above. That is, MDL+ code can include code from all intermediate languages, and thus some of the code might completely specify a piece of the chip while other code might just ask the compiler to place an ALU in one of the units somewhere on the chip and connect it to other ALUs, whichever units they should fall in.

For applications which are either very important to optimize or just not being compiled to a state acceptable to the programmer, there also becomes a whole other way to view Multi-level programming. By describing the MDL+ compiler the way that we have, we have enabled the user to get into the guts of the compiler's work at each level. Thus, an ambitious multi-level programmer can write multi-level code (as described in the last paragraph) and then tell the MDL+ compiler to group it and print out the resulting MDL+1.3 code. He can then re-group the pieces which he does not like the automatic grouping of manually and run the MDL+ compiler on this modified output, telling it to only run the placer and output MDL+1.2 code, and so on. In this way, the programmer can view some of the compiler's automated actions as suggestions, while allowing the compiler complete control over the aspects that the programmer does not care about, is not capable of doing on his own, or is content with.<sup>2</sup>

It is now clear how all of the objectives which we sought are realized by this implementation of MDL+, and the reader is ready to proceed through the next few

<sup>&</sup>lt;sup>2</sup>In professorial lingo, the compiler has become a grad student.

chapters secure enough in the big picture to understand the details.

## Chapter 3

# MATRIX

Before proceeding to the specification of the basics of MDL+ we take a break to discuss the hardware present on a MATRIX chip. This discussion of the theoretical basis for CGRAs and the actual hardware on MATRIX provides an ability to understand what the various constructs of MDL+ correspond to. This thesis is not actually about MATRIX, but since this thesis is about compiling for CGRAs and MATRIX, a lot of background about MATRIX is necessary before being able to understand the work that we did. This chapter provides that background, so that the next chapter can resume a discussion of the work actually done for this thesis. For further clarification of material in this chapter, see the thesis that proposed the idea [DeH96], the original paper to introduce MATRIX [MD96], and the MATRIX Micro-Architecture specification [Mir95a].

Much of the basic description of MATRIX in this chapter is taken directly from [Mir95b]. Many of the figures are from [Mir95b] and [Mir95a]. All of this other material was produced for Reinventing Computing and is used with permission of the authors.

#### **3.1** Architecture Overview

MATRIX attempts to bridge the gap between microprocessors and FPGAs, such as those offered by Xilinx. [Xil94] The best way to achieve this is by examining the way in which the two computing machines limit and specify their operations. [DeH95] Microprocessors place strict limits on their sets by specifying them in advance at fabrication time. The set is often limited to less than 256 instructions and therefore require very little "configuration data" (the actual instruction word - often 8 bits or less). FPGAs on the other hand, have a large amount of configuration data (up to 30 KBytes per configuration on some of the larger parts), but have an infinite instruction set which is not fixed at fabrication time. MATRIX, therefore, aims to limit its instruction set, but not absolutely fix it, at fabrication time. It should also reduce the amount of configuration data required to specify each instruction, which will help make each instruction much faster and allow for rapid instruction issue rates.

This is accomplished by creating a microprocessor-like basic block, consisting of a Memory and fixed ALU (Arithmetic Logic Unit), and connecting them in a reconfigurable mesh. Therefore, while each unit has an easy-to-specify configuration, the combination of many such elements allows for a great deal of flexibility.

#### **3.2** Basic Unit

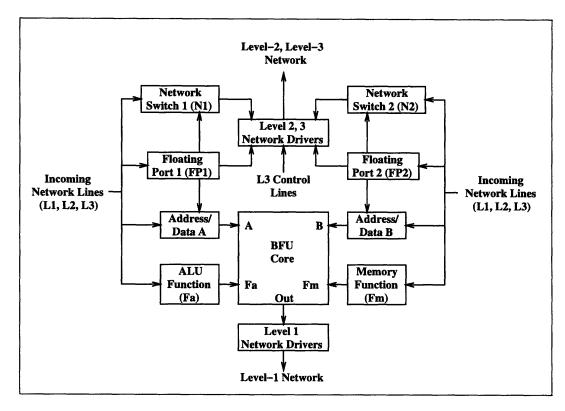

The Basic Functional Unit (BFU) of MATRIX is the coarse grain building block out of which more complex processing units can be built. It primarily consists of a memory block and basic ALU. Figure 3-1 shows the block diagram for a BFU cell.

The main BFU memory is a 256 word by 8 bit wide memory block, which is arranged to be used in either single or dual port modes. In dual port mode, the memory size is reduced to 128 words in order to be able to perform both read operations without increasing the read latency of the memory. In both modes this read operation takes place during the first half of the clock cycle and the values are latched for the rest of the cycle. Write operations take place on the second half of the cycle. This allows a BFU to perform register-file like operations such as A op  $B \rightarrow A$  in one cycle.

The MATRIX ALU is a basic 8 bit arithmetic logic processing unit. It is capable of performing the following operations:

• Pass

Figure 3-1: MATRIX Basic Functional Unit

- Logic Operations AND, OR, XOR

- Shifts Left and Right, with and without carry

- Add

- Multiply

With optional input inversion this also allows NOT, NOR, NAND, and subtraction.

Several adjacent blocks can also be composed to form wider-word ALU's. For example, four basic units can perform a 32-bit operation. The blocks can also be configured so that they can serve as a pure memory, pure ALU, or an ALU/memory (ALU/register file) combination.

Every input to the BFU is registered. This means that every BFU will be in its own pipeline stage which allows for highly pipelined systems.

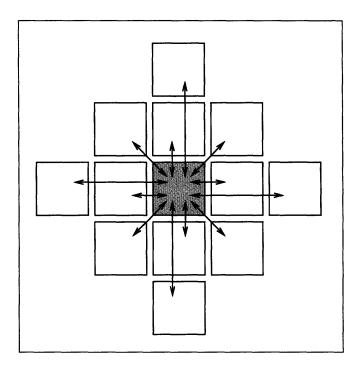

Figure 3-2: Level 1 Network Connections

#### **3.3** Interconnect Network

The MATRIX network consists of three levels of interconnect structuring: a regular neighbor mesh, longer switchable lines, and long broadcast lines.

On the first level, output of every BFU is passed to its nearest neighbors in all directions, its neighbors 2 cells away in the cardinal directions, and itself. As a result every cell receives 13 Level-1 inputs. This network is intended to provide fast connections between tightly packed cells. Figure 3-2 shows the connections on the Level-1 network.

The second level provides length-4 broadcast lines along rows and columns of BFUs. Level-2 switches could operate in two modes. In one, the data passing through the switch would be registered, creating an extra pipeline stage in the network. This would be useful for synchronization. In the other mode, data would be passed without registering. This would allow for longer chains of network connections to be built. The possible number of links in these chains would depend on particular implementations of this design as well as the internal clock speed, but probably be as long as

Figure 3-3: Level 2 Network Connections

three or four links. Due to the reduction in time to fabricate the MATRIX chip, as well as simplicity in design, the option of not registering level 2 lines has not been implemented in the current version of MATRIX, but it is still unclear whether it would have been worth implementing. We will, by using the MDL+ compiler, discuss whether the inability to leave level-2 lines unregistered has significantly hurt the ability to automatically route MATRIX.

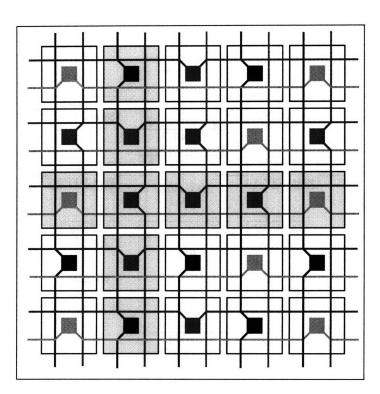

The BFUs on the main diagonal drive horizontal level-2 lines, and every other BFU drives in the same direction, creating a checkerboard pattern. Each BFU drives two level-2 lines, and can view all eight level-2 lines passing over it. Figure 3-3 shows the level-2 connections on a five by five subgrid of BFUs.

The MATRIX level-3 network is intended to carry data long distances as rapidly as possible. It consists of 4 shared network lines spanning every MATRIX row and column. Each BFU cell gets to drive up to 4 inputs onto the level-3 network. The delay across level-3 is one clock cycle per step, with steps at this level being up to a full-chip long. Thus it is possible to get from any BFU to any other BFU in a

Figure 3-4: MATRIX Network Switch Architecture - BFU Cell

MATRIX array in 2 clock cycles.

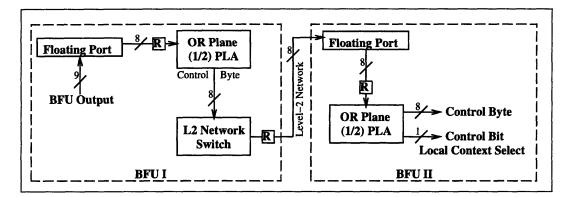

#### **3.4** Network Ports

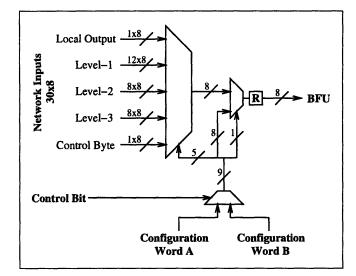

The network is connected to the BFUs through the network ports, as shown in Figure 3-4. It is in these ports that much of the flexibility of the MATRIX architecture is found.

A typical port is shown in Figure 3-5. The port is controlled by a 9 bit configuration word. This word can be interpreted in two ways, based on the value of the 9th bit. In *Static-Value* (Constant) mode, the lower eight bits of the configuration word are passed directly to the BFU. This allows the port's value to be fixed to a pre-programmed value. In the other mode, *Static-Source*, the lower 5 bits of the configuration word select from the 30 incoming lines and the value on this line is propagated to the BFU. In this mode, the BFU can be controlled by another BFU,

Figure 3-5: Function Port Architecture

or from an external source.

For the Address/Data ports and network ports, a third mode is allowed: Dynamic Source. In this mode the value coming from another network switch, the Floating Port on the same side of the BFU (see figure 3-4), can be used to be select from the 30 incoming network lines. Thus, the port's value can be fixed by the configuration word, come from a fixed source, or come from a source that can be selected on a cycle by cycle basis.

While three modes on 30 input lines gives MATRIX a lot of flexibility, the ports need to be very large in order to accommodate this many input lines and very large MUXs. The BFU would be a lot smaller if less inputs were available, thus providing more BFUs per chip. One goal of this thesis is to compile down our intermediate representation to BFUs while watching to see how many inputs are really needed per port, in order to determine if some of the current flexibility is not useful, or not as efficient as having several more smaller BFUs.

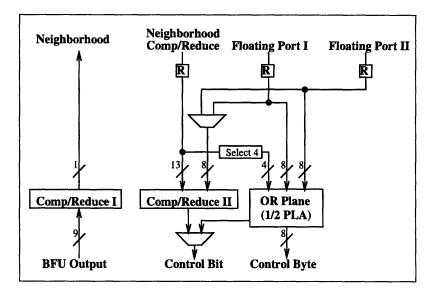

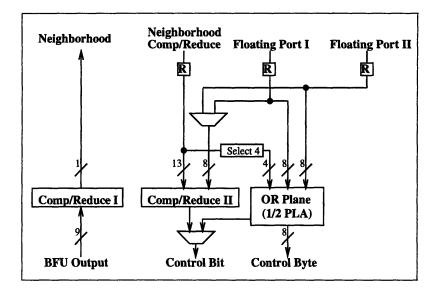

Figure 3-6: BFU Control Logic

# 3.5 Control

There are three portions of control logic in each MATRIX BFU, as shown in figure 3-6. First is Compare/Reduce I which compares the local ALU output to a given pattern and outputs a bit to every BFU which receives the level-1 output from the local BFU. Second, there is Compare/Reduce II which can compare any of the BFU's neighbors' Compare/Reduce I outputs and either of the floating ports, and outputs one bit. Third, there is the OR plane which can choose for input any four of the neighborhood Compare/Reduce I values and both of the floating port inputs, and can output 9 bits. Either the high bit from the OR plane output or the Compare/Reduce II bit can determine the local context of the BFU for the next cycle.

This control logic can probably be improved. The OR-plane is useful because it is the only thing on a MATRIX chip which can compose any arbitrary bit-level logic when combined with a second OR plane to form a PLA, as shown in figure 3-7. However, it takes up a lot of area, and is very complicated to test, and is therefore being left out of the initial design of MATRIX. One goal of this thesis will be to determine its usefulness, and whether it should be added to the next chip design. Similarly, we will explore other logic options, such as changing the Compare/Reduce networks,

Figure 3-7: Distributed PLA

not broadcasting Compare/Reduce I as widely, or changing the entire control logic scheme.

# **3.6** Deployable Resources

The ability of one BFU to control another is one of the main fundamental advantages of MATRIX's coarse-grain architecture. For larger primitive units, there are not enough on a single die to make this kind of self-control interesting. For smaller cells, one cell is not large enough to generate the control information for other cells. Thus, it is only at this intermediate granularity that it becomes possible to deploy a chip's resources at this level of flexibility. We thus mention this aspect of MATRIX before completing our discussion of MATRIX and this chapter.

In terms of MATRIX, deployable resources means that every BFU can be configured to serve whatever function it is most needed for. Depending on the type of architecture MATRIX is imitating at the time, BFUs will be allocated to different functions.

Examples of how MATRIX can be configured to imitate various architectures, thus deploying its resources in different ways, will be given in chapter 6 where in addition to discussing MATRIX's ability to implement these architectures, we will discuss MDL+'s ability to compile them. In addition to compiling versions of several existing general purpose computing architectures, that chapter will discuss ways in which MDL+ and MATRIX can deploy resources on an application-specific ASIC-type basis. The earlier

part of the chapter will include several ASIC-type MDL+ designs for MATRIX.

Thus, we will give a lot of evidence that MATRIX's resources are truly deployable, in a way that cannot be achieved by very-coarse, or very-fine grain systems. Designers simply need to decide what kind of processing style suits their needs, and then descriptions of those architectures (or ASIC-like descriptions) can be compiled automatically into an application which will run on MATRIX, deploying resources to support the designers' preferred style. Developing this software is a large part of this thesis, and we therefore return to discussion of MDL+ with the next chapter.

# Chapter 4

# MDL+ as Better MDL

This chapter describes the basic syntax and semantics of the MDL+ language that corresponds to configuration details that are actually loaded onto the chip. Thus, it will be describing how MDL+ includes the functionality of MDL, and what basic forms of syntactic sugar MDL+ offers. This chapter will not discuss the aspects of the MDL+ compiler which are at a fundamentally higher level, such as the automatic routing, placement, and grouping that the compiler can do. Those aspects, as well as the syntactic elements of MDL+'s grammar needed to support them, are discussed in Chapter 5.

The first part of this chapter is devoted to explaining the basics behind MDL+. The next part discusses the additions to MDL+ that are more than just cleaning up MDL, but not actually intelligent phases of the compiler, namely MDL+'s automatic driving phase. The end of this chapter is devoted to explaining the basic output modes and compiler options that MDL+ provides, in order to make this chapter complete and sufficient to enable the reader to write an MDL+ source file and then compile and use it himself. For the complete grammar defined in this chapter, see Appendix A.

# 4.1 Language Basics

MDL+ is a lexically scoped call-by-value language using a LISP-style syntax. MDL+ uses a LISP-like syntax for several reasons. It is easier to parse, seems to fit the problem in that the language constructs actually correspond to physical resources, and because MDL used a LISP-like syntax and it is easiest on MDL programmers if we change the appearance of the language as little as possible.

The actual layout of an MDL source file is very simple: it is a list of successive definitions. These definitions are read by the compiler in-order, and thus are read in the environment defined by the definitions above the current one in the input file. If any variables are defined above the current definition in the file, they are thus bound in the current defining-environment, and so they can be used by the current definition. Since MDL+ is lexically-scoped, they will be assumed to mean whatever they were defined as in the file at the point above their use that is nearest their use. Any places where variables are used in a more dynamically-scoped way will be explicitly mentioned when the construct is explained.

### 4.1.1 Basic Statement Structure

Since this is a LISP-like syntax, each definition is enclosed in parenthesis. Each definition is a definition of a specific type of construct, and thus begins with a statement that indicates which type of construct it is defining, such as **def-bfu** or **def-port**. Since each definition is defining a specific instance of that type, the instance must be named, and this name is always the second item listed, just after the **def-** item. Finally, prior to the end parenthesis, the construct is defined with appropriate arguments. These are discussed for each construct in the next section. Often it will be allowed for these arguments to be omitted entirely, producing the default item of that construct type bound to the appropriate name for future definitions to use.

# 4.1.2 Identifiers

The name given to an instance of some construct type must be a legal identifier, which probably includes anything that it might have been named. Specifically, it must start with a letter (lowercase or capital), an underscore (\_), a colon (:), a period (.), a hyphen (-), a forward slash (/), a dollar sign (\$), a less-than sign (<), or a greater than sign (>). Any subsequent characters can be any character that could have started the identifier, but they can also be digits.

It is recommended that names be constrained to letters and digits but it does not have to be so. Since MDL+ is context-insensitive where identifiers are concerned, using an uppercase version of a letter yields the identical effect of using the lowercase version of that letter.

# 4.1.3 Numbers

Whenever a number is required in an MDL+ file, it can either be represented by a sequence of digits which will be interpreted as a decimal number, or precede a sequence of hexadecimal digits with 0x or 0X which will be interpreted as a hexadecimal number.

# 4.1.4 Compare/Reduce Numbers

Besides decimal and hexadecimal numbers, MDL+ will also recognize Compare/Reduce-Numbers or rednumbers. They should be prefixed with a **0r** or **0R** and each character or bit of the number must be a **0**, **1**, **x**, or **f**. These letters are case insensitive, and an **x** means that the bit compared against can be either a 0 or a 1, while an **f** means to always fail. These numbers are only for use with the Compare/Reduce control-system of MATRIX and are not allowed most places where normal numbers and hexadecimal numbers are allowed. These numbers are also known as rednums.

### 4.1.5 Don't Cares

One concept that will appear throughout MDL+ is that of *Don't Cares*, or *DCs*. Basically, whenever there is a configuration value or argument that could be entered for some construct in MDL+ that the programmer does not care about at all, he can enter "DC" in the MDL+ code instead, or omit the argument entirely. For specific usage options, see the part of the next section that deals with the specific construct that is of interest, since sometimes there are limited options, in order to clean up unnecessary aspects of the grammar a bit. Usually, everything can either be omitted entirely, or its values filled in with Don't Cares.

# 4.1.6 Copying Constructs

It is almost always permissible to define a construct with only one argument, where that argument is either DC or the name of an instance of the same type of construct which is defined in the current environment. Thus, for almost any legal type, it could be substituted in the following code for *mytype*, thus producing two legal copies of the type in the environment, both completely unspecified.

(def-mytype a dc)

(def-mytype b a)

At the point of the MDL+-code just after these two lines, a and b would both be bound in the environment to completely unspecified (not caring) instances of the type replacing mytype. Since MDL+ definitions are all passed arguments call-by-value, a and b would refer to separate but identical instances, and not be merely aliases of each other.

### 4.1.7 Inheritance

Another recurring theme in MDL+ is that of inheritance. With DCs, the ability to rearrange and omit a lot of the MDL+ code, and inheritance, MDL+ files are much shorter, more manageable, easier to write, and easier to understand than MDL files

used to be. Inheritance is not as pervasive in MDL+ as DCs are in that not every construct can inherit from other constructs of its type. But the more useful examples do have inheritance. For example, a BFU can be defined as being exactly the same as another already-defined BFU, except for some explicit differences. Since the parent BFU is evaluated at the time of definition, in a lexically-scoped manner, changes to the parent BFU later in the source file will not affect the child BFU at all. Thus, it might be best to view inheritance in MDL+ as copying an old instance of the type to the new instance and then specifying changes to it.

This other view is not only more accurate, but it also provides insight into other possibilities for how to use inheritance in MDL+ that a traditional view might not encourage. For example, in a BFU definition, the changes to the parent BFU can be specified prior to the parent BFU being named. In that case, the new BFU is formed by first specifying a new implicit BFU from the new specifications and then treating it as the parent of the actual explicitly-defined parent, and inheriting in reverse-order. This will be explained further when there is a basis for understanding the specifics, once the BFU has been discussed, in the next section.

# 4.1.8 Reserved Words

MDL+ has two types of reserved words that will thus be interpreted with special meanings: Globally reserved words and locally reserved words. Globally reserved words are special everywhere in an MDL+ file and thus can not be used as identifiers. Locally reserved words are only special in specific contexts and thus are fine for use in most cases. All globally reserved words are listed in appendix C, while locally reserved words should be obvious for each context.

### 4.1.9 Lists

There are many parts of the MDL+ grammar that call for lists. Sometimes these are sequences which are being defined, such as the sequence of all memory cells for a BFU. Other times, each element of the list is intended to convey more information about the configuration of a single item being defined. In this case, it is possible for the configuration information from some of the list to contradict with information from other elements of the list. When there are contradictions, the later elements (right-most) will take precedence over the earlier elements (left-most). However, any pieces of the earlier definition which are not contradicted by the later definitions will remain.

For example, saying that the last two bits of a number are "01" followed by saying that the second to last bit of the number is "1" will be understood as saying that the last two digits of the number are "11". In general, this is the way the compiler will understand items of configuration at least as large as a single number, while any information smaller than a single number (a piece of a number) will actually be completely replaced by later references. If our example had been the number 1 and then the number 2, the compiler would understand the list as just the number 2.

# 4.1.10 Ordering Directions

There is a convention throughout MDL+ and MATRIX programming in general of an implicit ordering on the opposite cardinal directions. South or down is "less than" or "comes before" north or up. Similarly, west or left is less than or comes before east or right. This convention is prevalent in many elements of the syntax and semantics of MDL+, as explained in the next section.

# 4.1.11 Going Beyond MATRIX

Proceeding through the explanations of basic MDL+ in this chapter, there will be several elements for which configuration is provided even though they do not exist on the MATRIX hardware. These are generally elements that could have been used in MATRIX, but were taken out of the design at some point either to conserve area on the chip or to reduce the amount of time until the chip could be fabricated. They have been included in MDL+ because they might be useful for simulation of hypothetical chips, as well as a desire to be compatible with MDL source code.

# 4.1.12 Definitions

Here we define many words that will be used a lot in the upcoming section to describe aspects of MDL+. All of them should seem to fit with their definitions fairly naturally, but they do mean more in the context of MDL+ than they would in standard language.

- Construct This is a datatype for MDL+. In MDL+ code, there can be definitions of constructs, which would then leave an instance of that construct in the environment. They generally correspond directly to hardware on MATRIX, but not always. The only types in MDL+ that are not constructs are simple types: Numbers, strings, rednumbers, and Don't Cares. Examples are *BFUs* and *Memories*.

- Instance A specific example of a construct. After definition of a construct, there is an instance of the type in the environment. Two instances of a construct are always unique and not aliases of each other.

- Constructor A globally reserved word in MDL+ that is used to indicate the beginning of the definition of some construct. After that definition, there will be a new instance of that construct. Each construct has its own constructor. Examples are *def-bfu* and *def-mem*.

- Structure A description of a piece of the grammar of MDL+. This is a sequence of words and parenthesis that explain how a certain amount of the MDL+ syntax is used. Some of the words will need to be written in the MDL+ file exactly as they are in the structure, and some are arguments that will need to be replaced. The only other notation used in structures is Kleene closure. There may be multiple structures allowable in MDL+ to do the same thing: One structure for defining BFUs is (def-bfu Name Old) where Name is an argument that is the string which names the BFU being defined, and Old is an argument that is the string which names an already defined BFU. A second structure for defining BFUs is (def-bfu Name DC) where Name is the same

kind of argument as above. Structures listed in the text will always be boldfaced.

- **Basic Structure** All constructs in MDL+ can be defined with two structures such as those listed above for BFUs, one to copy an old instance of the same type and one to create a completely unspecified instance of the type. Clearly, these are not a sufficient set of structures. The basic structure is the structure that includes all alternatives besides these two for defining a given construct. It is considered basic because it is the only one that the language could not do without.

- Keyword Many basic structures will be of the form (Keyword Stuff) where Keyword will need to be replaced by a specific string that is either a global or local reserved word, and Stuff will need to be replaced by something special to the construct. The word replacing Keyword for one of these constructs is considered its keyword because it identifies the type of definition that the program is making. Constructs can have no keywords, one keyword, or many keywords.

- Argument This is a word in a structure that is not meant to be used exactly as written in the MDL+ code, but rather to be replaced with something else, perhaps something described by its own structure.

- Default If it is possible to define a construct with only a constructor and a new name inside a pair of parenthesis, then the default for that construct is whatever instance such a definition would produce. If not, then the construct can still be said to have a default if it is possible to define it with the basic structure of only a sole keyword inside a pair of parenthesis.

- **Replacing** This means that one thing will get completely eliminated and another put in its place. When A is replaced by B, the result is always exactly the same as B. This word is used in conjunction with *overriding* in order to be more specific about the behavior of inheritance and lists in MDL+.

- Overriding This means that one thing will use its parts which are specified to replace those parts in another thing. When A is overridden by B, the result has in common with B every piece of B which was specified, and in common with A any piece of information that was not specified in B. When a child inherits from a parent, the child overrides the parent, as right-most elements of lists override left-most elements of lists.

- Reverse Inheritance Whenever inheritance is allowed in MDL+, the parent may also be listed after the definition of the child in which case the parent overrides the child instead of the child overriding the parent.

- Full Inheritance This refers to a situation in which the parent may be listed at any point in the child's definition, and multiple parents may be listed. The items listed later always override the items listed earlier. Whenever inheritance is available in MDL+, full inheritance is available.

# 4.1.13 Type Checking

MDL+ is a type-checking compiler, and will thus halt with an error message if a name is used which is currently bound to an instance of a type which is not one of the types allowable in the place that the name was used. For example, the first local context of the A port of a BFU must be set to either the name of another BFU (a string that is the name of another BFU)<sup>1</sup> or to a constant value. Thus, if it is given a variable that is of type chip, the compiler will halt, since the user program did not type-check.

For example, consider the code in figure 4-1. The first line defines a chip named a and the remaining lines attempt to define a bfu named b which has the first local context of its A port defined to be that chip named a. It could have defined the A port value to be a number, e.g. 8, or the name of a constant variable, or even another BFU, but not a chip. (See the explanations of BFUs (4.2.11), constants (4.2.1), and

<sup>&</sup>lt;sup>1</sup>The syntax for this case actually includes more than just the string, e.g. "(static bfuname)"

```

(def-chip a)

(def-bfu b

(ports

(aport a)

)

)

```

Figure 4-1: Source code that does not type-check.

```

Parse Error:

```

need a constant or aluobj, you have an identifier that has been defined to be something else. Only constants and aluobjs can be used here. If your ID is a BFU, you might want to wrap it in a (static) if you meant to use it, automatically routed, as static source. Bad ID: A Last Line Read: 4

Figure 4-2: Typical error message for code that does not type-check.

chips (4.2.15) to avoid any confusion and completely understand this.) Thus, trying to run this code through the MDL+ compiler would cause it to halt with the message in figure 4-2.

### 4.1.14 Output

One of the things that is often most mysterious when learning a new programming language is how to get any output out of it. In the case of MDL+, it is clear that there are no statements other than definitions for the environment, so it is especially unclear how the compiler will know to output something. In fact, if an input file does not complete any chip definitions, the compiler will parse the input, and if it is correct, the compiler will halt without outputting anything. However, when one or more chips are defined in an MDL+ file, the compiler will process them with its various automatic phases (discussed at the end of this chapter and in the next chapter) and then output each chip to its own file. The form of the output will depend on the command line arguments provided to the MDL+ compiler. It is illegal to define more than ten chips in any one MDL+ file, but there is not much reason why that would be done anyway.

The forms of output, and how to ask the compiler for them, will be discussed in much more detail in section 4.4 at the end of this chapter. At this point, all that is important is that if an MDL+ source file has a chip construct defined in it, then the compiler will be able to produce from it a configuration file which can be loaded onto a MATRIX chip to run the way the chip was specified in MDL+.

# 4.2 Language Constructs

The previous section provided a basic overview to the syntax and semantics of MDL+. As with most LISP-like languages, the basics are very simple and all of the functionality lies in the details of the primitives. In this case, the primitives correspond to the types of the language, or the various constructs. An instance of each type can be created and placed in the environment with an appropriate definition statement, as stated in the previous section, and then used later in the file.

All that is left is understanding each construct, which will correspond to some hardware on the actual MATRIX chip. This section will go into detail to explain each construct. After reading about any construct, it should be a simple matter to write an MDL+ file that uses that construct.

### 4.2.1 Constants

Constants are the lowest level type that MDL+ has. (Numbers, Rednumbers, and name strings are not types.) There are many different kinds of constants and they are used in many different kinds of other situations. Many times, using one kind of constant in a situation intended for another kind of constant will be a mistake, but MDL+'s type-checking will not catch these errors, because as far as the compiler is concerned all constants are equally appropriate for any places that need constants. The benefit to this is that there are times when it might be desirable to use one kind of constant in a place where a different kind is desired, and the compiler will not stop you. Constants are the lowest-level type in MDL+ and very useful because they are basically just numbers. The difference between a constant and a number are twofold: Constants can be bound to names and stored in the environment whereas numbers can not be, and constants can also be DC, meaning that it does not matter what number the constant represents, whereas numbers are just integers.