## Managing Scheduled Routing With A High-Level Communications Language

by

Christopher D. Metcalf

B.S., M.S., Computer Science Yale University, 1988

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

#### at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

#### SEPTEMBER 1997

© Massachusetts Institute of Technology 1997. All rights reserved.

A. 1 Λ Department of Electrical Engineering and Computer Science August 19, 1997 < - T Certified by ..... Stephen A. Ward Professor of Electrical Engineering and Computer Science Thesis Supervisor Accepted by ..... Arthur C. Smith Chairman, Departmental Committee on Graduate Students 1 1 1 1 C 1 OCT 291997

#### Managing Scheduled Routing With A High-Level Communications Language

by

Christopher D. Metcalf

Submitted to the Department of Electrical Engineering and Computer Science on August 19, 1997, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

#### Abstract

One of the most critical issues in multiprocessors today is managing the communications among processors. This thesis addresses the programming of systems (such as the NuMesh) that handle routing via high-speed reprogrammable scheduled routers on each node. A portable 'communications language', COP, used to express communications requirements, is presented.

Using scheduled routers to control data motion through the network has two advantages. First, by performing offline path scheduling for messages based on information extracted from the application, latency and congestion can be improved. Second, by removing the need for online decision making, such routers can run at extremely high speeds, further decreasing latencies and increasing performance.

Simple communication patterns known at compile time are relatively easy to schedule. However, data-dependent communications present more of a challenge. The compiler makes tradeoffs among different compilation techniques based on information in the communication program, including communication type and predicted traffic, as well as knowledge of the system size and layout. Further, the compiler chooses dynamically how to break up an application's communications into sequential phases, using communication relationships expressed in the input language. The compiler generates code that efficiently handles changing phases and ensuring data integrity while doing so.

This thesis shows that certain classes of applications, such as those that suffer from congestion with dynamic routers, show a significant decrease in run-time routing cycle count when using scheduled routing. Furthermore, reprogrammable scheduled routers are shown to provide a relatively general solution to application communication needs; applications with uncongested or data-dependent traffic are found to take approximately the same number of routing cycles, yielding a decrease in overall runtime given the potentially high cycle-speed of scheduled routers.

Thesis Supervisor: Stephen A. Ward Title: Professor of Electrical Engineering and Computer Science

### Acknowledgments

My years at the Laboratory for Computer Science have given me a remarkable opportunity to work with and learn from a range of bright and interesting people. This thesis draws upon that background not just for technical issues, but as a standard to live up to.

Steve Ward, my thesis supervisor, provided an important part of the support for this thesis. As well as starting the NuMesh project, he encouraged me to explore issues that were a little more fundamental and a little less mainstream, and both directed and participated in the chaotic and productive group meetings out of which came many of the most interesting results of the NuMesh project.

Thanks are also due to the other two members of my thesis committee, Gill Pratt and Frans Kaashoek. Their insistence on keeping the big picture visible, making the experimental framework of the results clear, and being precise in drawing conclusions, helped to make the thesis as readable as it is.

The other graduate students in the NuMesh group, along with the Alewife and CVA members of the overall Computer Architecture Group, gave me much of the day-to-day social and intellectual life of the lab. In particular, I would like to thank Dave Shoemaker for great collaboration and for refusing to allow me to ignore hardware, Pat LoPresti for helping me sound out ideas on languages and scheduled routing as well as putting up with continuous Tadpole bug reports, and Anne McCarthy for her competence, warmth, and supportive fire-fighting. My officemate Kirk Johnson was a source of many an interesting conversation, late night systems hacking, and friendly support. Thanks also to Frank Honoré, Russ Tessier, John Nguyen, and John Pezaris for many interesting times.

Thanks to the people who volunteered their time to read through drafts of this thesis and volunteer suggestions, Michael Littman and Joe Morrison, and Dave Shoemaker.

My parents provided me with encouragement throughout my thesis, giving me perspective from the other side of the Ph.D. fence and letting me know I was in their thoughts as I passed the various milestones of the thesis path.

Finally, and most importantly, thanks to my wife, Elaine, without whom I'm not sure I would have made it through—and without whom I certainly wouldn't have started at MIT when I did! Her support and encouragement were a large part of what kept me going; her advice helped keep me focussed on making progress week by week; and her shared happiness at every milestone passed was a joy. Just as important, even at times when my thesis didn't seem to be going the direction I wanted it to, her presence in my life provided a fundamental sense of balance and happiness.

## Contents

| 1 | Intr                           | oductio                    | n                                          | 11   |  |  |  |

|---|--------------------------------|----------------------------|--------------------------------------------|------|--|--|--|

|   | 1.1                            | Contri                     | butions of the Research                    | 12   |  |  |  |

|   | 1.2                            | Benefi                     | its of Scheduled Routing                   | . 14 |  |  |  |

|   |                                | 1.2.1                      | Cycle Speed                                | 14   |  |  |  |

|   |                                | 1.2.2                      | Hotspot Avoidance                          | 14   |  |  |  |

|   |                                | 1.2.3                      | In-Router Algorithms                       | 16   |  |  |  |

|   |                                | 1.2.4                      | Stream Prioritization                      | 17   |  |  |  |

|   |                                | 1.2.5                      | Header Traffic                             | 17   |  |  |  |

|   |                                | 1.2.6                      | Non-Cartesian Networks                     | 17   |  |  |  |

|   |                                | 1.2.7                      | Faulty Networks                            | 19   |  |  |  |

|   |                                | 1.2.8                      | Multiple Applications                      | 19   |  |  |  |

|   | 1.3                            | Drawb                      | backs to Scheduled Routing                 | 19   |  |  |  |

|   | 1.4                            | Schedu                     | uled Routing                               | 20   |  |  |  |

|   |                                | 1.4.1                      | Scheduling Virtual Finite State Machines   | 20   |  |  |  |

|   |                                | 1.4.2                      | Flow Control in Scheduled Routing          | 22   |  |  |  |

|   |                                | 1.4.3                      | Router Reprogramming                       | 23   |  |  |  |

|   |                                | 1.4.4                      | Other Characteristics of Scheduled Routing | 23   |  |  |  |

|   | 1.5                            | Thesis                     | Outline                                    | 24   |  |  |  |

| 2 | The Communications Language 22 |                            |                                            |      |  |  |  |

|   | 2.1                            | Motiva                     | ation                                      | 25   |  |  |  |

|   | 2.2                            | Expres                     | ssing Communications as Operators          | 26   |  |  |  |

|   | 2.3                            | Suppo                      | rting Phases                               | 28   |  |  |  |

|   |                                | 2.3.1                      | Choosing Optimal Phase Boundaries          | 28   |  |  |  |

|   |                                | 2.3.2                      | Expressing Time                            | 29   |  |  |  |

|   | 2.4                            | Group                      | ing Operators Together                     | 30   |  |  |  |

|   |                                | 2.4.1                      | Multiple Operators                         | 30   |  |  |  |

|   |                                | 2.4.2                      | Continuing Operators                       | 30   |  |  |  |

|   |                                | 2.4.3                      | Multiple Threads of Control                | 31   |  |  |  |

|   | 2.5                            | Comm                       | nunicating in Subsets of the Mesh          | 31   |  |  |  |

|   | 2.6                            | Expressing Run-Time Values |                                            |      |  |  |  |

|   | 2.7                            | .7 Computational Model     |                                            |      |  |  |  |

|   |                                | 2.7.1                      | The I/O Functions                          |      |  |  |  |

|   |                                | 2.7.2                      | The Load Function                          |      |  |  |  |

|   |                                | 2.7.3                      | COP/HLL Integration Example                | 35   |  |  |  |

|   | 2.8             | Extens  | ibility                                                                                 |

|---|-----------------|---------|-----------------------------------------------------------------------------------------|

|   | 2.9             |         | le COP Code                                                                             |

|   | 2.10            |         | anguage Design Issues                                                                   |

|   |                 |         | Message Streaming                                                                       |

|   |                 |         | Exposing I/O Wait Time                                                                  |

|   |                 |         | Hidden State                                                                            |

|   |                 | 2.10.4  | Loop and Branch Prediction                                                              |

|   |                 | 2.10.5  | Schedule Generation                                                                     |

|   |                 |         | Message Passing or Shared Memory?                                                       |

|   | 2.11            |         | ary                                                                                     |

| 3 | Dolo            | ted Wo  | rk 43                                                                                   |

| 3 | <b>Xela</b> 3.1 |         |                                                                                         |

|   | 5.1             |         |                                                                                         |

|   |                 | 3.1.1   | The Gabriel Project                                                                     |

|   |                 | 3.1.2   | OREGAMI/LaRCS                                                                           |

|   |                 | 3.1.3   | The PCS Tool Chain         45           The OCS D         47                            |

|   |                 | 3.1.4   | The CrOS Project         47           61         100 0000000000000000000000000000000000 |

|   |                 | 3.1.5   | Chaos and PARTI                                                                         |

|   |                 | 3.1.6   | Other Communication Languages                                                           |

|   | 3.2             |         | led Routing Architectures                                                               |

|   |                 | 3.2.1   | iWarp                                                                                   |

|   | • •             | 3.2.2   | GF11                                                                                    |

|   | 3.3             |         | led Communication                                                                       |

|   |                 | 3.3.1   | Agrawal-Shukla                                                                          |

|   |                 | 3.3.2   | Bianchini-Shen                                                                          |

|   |                 | 3.3.3   | Other Scheduling Work                                                                   |

| 4 | Man             | aging D | Pata Dependency 52                                                                      |

|   | 4.1             | Operate | or Implementations                                                                      |

|   |                 | 4.1.1   | Approaches to Data Dependency                                                           |

|   |                 | 4.1.2   | Implementation Types                                                                    |

|   |                 | 4.1.3   | Meta-Implementations                                                                    |

|   | 4.2             | Online  | Scheduled Routing                                                                       |

|   |                 | 4.2.1   | Implementation                                                                          |

|   |                 | 4.2.2   | Resource Allocation                                                                     |

|   |                 | 4.2.3   | Future Extensions                                                                       |

| 5 | Mon             | oging N | Iultiple Phases   64                                                                    |

| 5 | <b>5</b> .1     | 0 0     | uing Operators                                                                          |

|   | 5.1             | 5.1.1   |                                                                                         |

|   |                 | 5.1.1   | Simple Continuation                                                                     |

|   |                 | 5.1.2   | 1                                                                                       |

|   | 5.2             |         |                                                                                         |

|   | 5.4             | 5.2.1   | ng Phases                                                                               |

|   |                 | 5.2.1   | -                                                                                       |

|   |                 | J.4.4   | Determining Which Operators are Terminating                                             |

|   |      | 5.2.3   | Barriers for Phase Termination                       |

|---|------|---------|------------------------------------------------------|

|   |      | 5.2.4   | Alternate Subset Specifiers                          |

|   | 5.3  | Inter-P | hase Wire Constraints                                |

|   |      | 5.3.1   | Finding 'Live' Communications Edges                  |

|   |      | 5.3.2   | Allowing Write Reuse with Barriers                   |

|   |      | 5.3.3   | Other Wire-Reuse Considerations                      |

|   |      | 5.3.4   | Dependency Analysis to Minimize 'Live' Edges         |

|   | 5.4  | Manag   | ing a Scheduled Router as a Cache                    |

|   |      | 5.4.1   | Caching for Router Schedules                         |

|   |      | 5.4.2   | Caching for Router VFSMs                             |

|   |      | 5.4.3   | Runtime Cache Management                             |

|   | 5.5  | Finding | g Load Operators                                     |

|   |      | 5.5.1   | Choosing a Load Operator for a Phase                 |

|   |      | 5.5.2   | Associating Multiple Phases with a Load Function     |

| 6 | The  | Compil  | er Search Engine 86                                  |

|   | 6.1  | -       | le Threads of Control with Scheduled Routing         |

|   |      | 6.1.1   | Restricting the Set of Nodes for Routing             |

|   |      | 6.1.2   | Deriving Spatial Extent Information                  |

|   |      | 6.1.3   | Restructuring COP Parallelism with Spatial Extents   |

|   |      | 6.1.4   | Sequential Descendants of Parallel Groups            |

|   | 6.2  | Search  | ing the Implementation Space                         |

|   |      | 6.2.1   | The Search Model                                     |

|   |      | 6.2.2   | Structuring the Phase Tree                           |

|   |      | 6.2.3   | Picking Implementations for Phases                   |

|   |      | 6.2.4   | Closing a Phase                                      |

|   |      | 6.2.5   | Computing Timings for an Implementation Set          |

|   |      | 6.2.6   | A Cost Metric for Stream Bandwidths                  |

|   | 6.3  | Stream  | Routing                                              |

|   |      | 6.3.1   | Basic Stream Router Interface                        |

|   |      | 6.3.2   | Stream Router Cost Function                          |

| 7 | Bacl | k-End I | mplementations 104                                   |

|   | 7.1  |         | led-Routing Backend                                  |

|   |      | 7.1.1   | The NuMesh Hardware                                  |

|   |      | 7.1.2   | NuMesh Phase-Changing Restrictions                   |

|   |      | 7.1.3   | The NuMesh Stream Router                             |

|   |      | 7.1.4   | Cost Function Constraints for NuMesh                 |

|   |      | 7.1.5   | NuMesh Caching Restrictions                          |

|   | 7.2  | Dynam   | nic-Routing Backend                                  |

|   |      | 7.2.1   | Disambiguating Messages                              |

|   |      | 7.2.2   | Dependency Analysis for Interface Address Allocation |

|   |      | 7.2.3   | Supporting Virtual Interface Addresses               |

|   |      |         |                                                      |

| 8 | Rest | lts 11                                   | .7 |  |

|---|------|------------------------------------------|----|--|

|   | 8.1  | Experimental Methodology                 | 7  |  |

|   |      | 8.1.1 Compilation                        | 7  |  |

|   |      | 8.1.2 Simulation                         |    |  |

|   |      | 8.1.3 Data Collection                    |    |  |

|   | 8.2  | Communication Kernels                    | -  |  |

|   |      | 8.2.1 Hotspot Avoidance: Results         |    |  |

|   |      | 8.2.2 In-Router Algorithms: Results      |    |  |

|   | 8.3  | Data-Dependent Communications Techniques |    |  |

|   |      | 8.3.1 Latency                            |    |  |

|   |      | 8.3.2 Bandwidth                          |    |  |

|   |      | 8.3.3 Online Scheduled Routing           |    |  |

|   | 8.4  | Application Benchmarks                   |    |  |

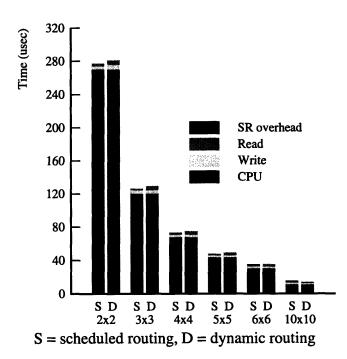

|   |      | 8.4.1 Matrix Multiplication              |    |  |

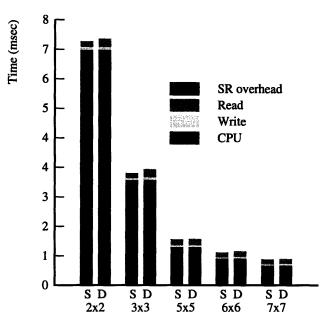

|   |      | 8.4.2 Gaussian Elimination               | ,9 |  |

| 9 | Con  | lusions 13                               | 1  |  |

| 1 | 9.1  | Managing Multiple Phases                 |    |  |

|   | 9.2  | Managing Data Dependency                 |    |  |

|   | 9.3  | The Compiler Search Engine               |    |  |

|   | 9.4  | COP                                      |    |  |

|   | 9.5  | Future Work                              |    |  |

|   |      |                                          |    |  |

| A | COI  |                                          |    |  |

|   | A.1  | Primitive COP Operators                  |    |  |

|   | A.2  | Compound COP Operators                   |    |  |

|   | A.3  | Optional Operator Arguments              |    |  |

|   | A.4  | (runtime)                                |    |  |

|   | A.5  | COP Grouping Constructs                  |    |  |

|   | A.6  | Predefined COP Variables and Functions   |    |  |

|   | A.7  | COP Extensibility                        |    |  |

|   | A.8  | Sample COP Idioms                        | .7 |  |

| B | One  | rator Implementations 14                 | 8  |  |

|   | B.1  | Implementations                          |    |  |

|   | B.2  | Generating Reduction Trees               |    |  |

|   |      |                                          |    |  |

# **List of Figures**

| 1-1 | Bitreversal on a small mesh                                         |

|-----|---------------------------------------------------------------------|

| 1-2 | Scheduled paths for bitreversal on a small mesh                     |

| 1-3 | Bitreversal routing (dynamic vs. scheduled routing)                 |

| 1-4 | Diamond-lattice scheduled routing                                   |

| 1-5 | A virtual state machine transferring data                           |

| 1-6 | VFSM schedules on a small mesh                                      |

| 1-7 | Data movement on a small mesh                                       |

| 1-8 | NuMesh transfer actions                                             |

| 2-1 | Broadcast abstraction                                               |

| 2-2 | A high-level view of code generation                                |

| 2-3 | Simple application code                                             |

| 2-4 | COP output for simple application                                   |

| 2-5 | Final HLL code for node zero                                        |

| 2-6 | COP code for matrix multiplication                                  |

| 2-7 | COP code for Gaussian elimination 39                                |

| 3-1 | Gabriel code for an FFT star                                        |

| 3-2 | LaRCS code for the n-body problem                                   |

| 3-3 | A simple PCS program                                                |

| 3-4 | CrOS code for a parallel prefix                                     |

| 5-1 | Dependency graph for simple COP fragment                            |

| 6-1 | Simple abstract multi-threaded code example                         |

| 6-2 | Simple disjoint parallel example                                    |

| 6-3 | COP disjoint example                                                |

| 6-4 | One possible way to handle disjoint COP                             |

| 7-1 | NuMesh hardware architecture                                        |

| 7-2 | NuMesh datapath                                                     |

| 7-3 | Dependency graph for simple COP fragment                            |

| 7-4 | Address allocation graph for simple COP fragment                    |

| 7-5 | Dependency graph for simple COP loop with deterministic routing 115 |

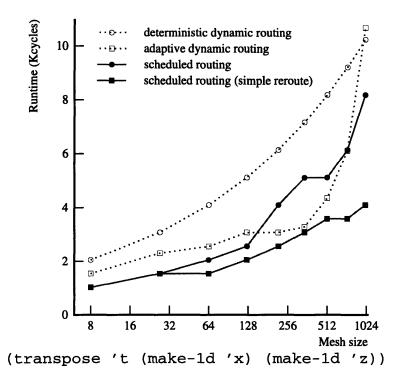

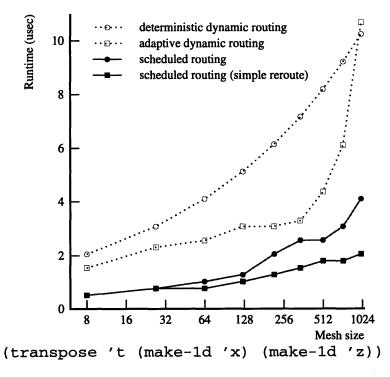

| 8-1 | Comparative performance for transpose (cycles)                      |

| 8-2 | Comparative performance for transpose (wall-clock time)             |

•

| 8-3  | Comparative performance for bitreverse (wall-clock time)                 |

|------|--------------------------------------------------------------------------|

| 8-4  | Prefix times (one-word prefix, cycles)                                   |

| 8-5  | Prefix times (mesh size 64, cycles)                                      |

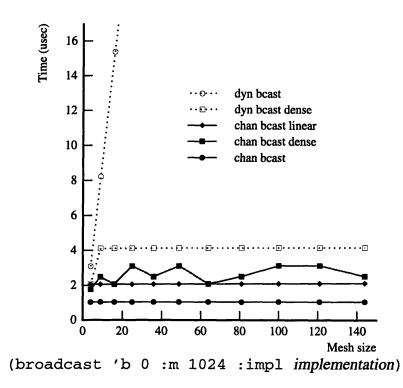

| 8-6  | Broadcast implementations (one word, wall-clock time)                    |

| 8-7  | Broadcast implementations (1024 words, wall-clock time)                  |

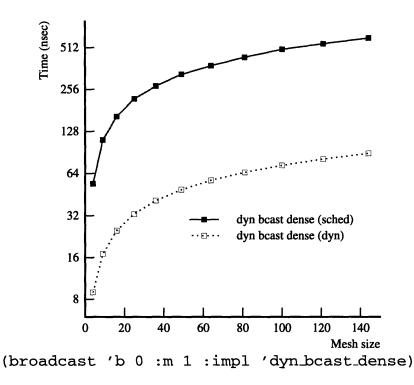

| 8-8  | Online broadcast with dynamic vs. scheduled routing, wall-clock time 127 |

| 8-9  | Matrix multiplication comparison, wall-clock time                        |

| 8-10 | Gaussian elimination comparison, wall-clock time                         |

| A-1  | COP code for specifying nearest-neighbor connections                     |

## **List of Tables**

| 4.1        | Interface functions for operator implementations |

|------------|--------------------------------------------------|

|            | Barrier techniques for safe phase termination    |

| 7.1        | NuMesh VFSM sources and destinations             |

| 8.2<br>8.3 | Instrumentation categories for elapsed time      |

|            | Pre-defined COP variables                        |

## Chapter 1

## Introduction

One of the most critical issues in multiprocessors today is managing the communications among processors. Traditionally, communication in multiprocessors was a major bottleneck, as was the case for the early Intel multiprocessors [37], for example. More modern machines (e.g. recent Cray machines [36]) have much higher-speed interfaces and networks; furthermore, recent work in communication techniques is helping to lower or mask latencies further (e.g. active messages [66] and rapid context switching [1, 61]). Communications, however, can still be a serious performance constraint.

Two approaches to reducing latency and increasing bandwidth are possible. One is to reduce cycle times in the network, thus moving data through the network more quickly, and directly improving both latency and bandwidth. The other is to make more intelligent use of the existing bandwidth in the network, such that the useful bandwidth can be increased and message latency better controlled (typically by providing guarantees of maximum latency). Both approaches can be applied at once by using a simple network processing element (with correspondingly fast switching times), running a reprogrammable scheduled router—essentially a simple finite state machine—to control data motion. In this thesis, this technique is referred to as *reprogrammable scheduled routing*; this class of routers is represented by the NuMesh router [68, 58, 59, 57]. Essentially, routing decisions are made offline (when the application is compiled), and at run time the routers simply execute repetitive schedules that handle all data transfers.

Pre-scheduling communications through the network has several clear advantages. Primarily, it allows for the routing scheduler to choose message paths to maximize specific user criteria (such as throughput and latency). Without some form of pre-scheduling, decisions can only be made based on local criteria; furthermore, routing hardware can only make decisions optimized for what the hardware designer thought was important. More importantly, without pre-scheduling, a router has no ability to look ahead to see what messages will be arriving shortly; it is a strictly "online" solution. Routing schedulers can examine the entire application's communication structure before generating schedules for the routers, and therefore represent a more general "offline" solution. Additionally, the more complex hardware needed for traditional data-dependent decisions can not achieve the short cycle time that is possible in principle with a highly-pipelined finite state machine. However, there are several limitations to the picture presented thus far.

Firstly, it is usually true that an application's communications are not completely deducible

at compile time. For example, an application may have a broadcast that is performed along all the columns of a matrix, but the exact row may be unknown. At run time, all the processors may know who is broadcasting—or perhaps only the broadcasting processor will know. Using the communications language presented in this thesis,  $COP^1$ , an application can specify everything that is known about communication patterns at compile time: compile-time constant components, restrictions on what dimensions are used or what nodes are involved, whether all the nodes have full information on the needed pattern or not, and so forth. Furthermore, each communication *operator* (*e.g.*, broadcast or parallel prefix) can be tagged with information that the compiler can use to optimize the implementation: message size, number of messages expected to be sent, and maximum desired bandwidth, for example.

Given the information presented by the language, the compiler has a wide range of implementation options for data-dependent communication operations. If only a few router schedules are needed to handle the possible operand values for the operator, the compiler may include them all, along with run-time selection code. Or, if including multiple schedules is infeasible, it may make sense to simply allocate all the possible paths statically, and use only the relevant ones at run time. For more dynamic, but bandwidth-intensive communications, the compiler may choose to include code to compute the desired schedules at run time. Or, in the most dynamic situations, the compiler may fall back on generating code to perform online routing, using nearest-neighbor connections to forward messages through the mesh.

Secondly, it may be the case that an application is composed exclusively of communications whose source and destination can be uniquely deduced at compile time, but that there are simply too many such communications streams. A typical application will often move through a range of communication and computation *phases*; each phase will have its own static communications graph, and merging all the schedules into one global application schedule may result in greatly decreased bandwidth available on each stream. This thesis examines how to specify, implement, and optimize the use of phases at the router level, by coordinated reprogramming of the routers during the execution of the program.

Finally, it is important to support the notion of multiple threads of control in the program. An application may have different components that are running unrelated code at times during its execution. It is important to support this in the communication language, since otherwise the ability of the application to change phases to match changing communication requirements would be greatly constrained. For example, an application may want to divide the mesh into subcomponents, each of which runs independent loops several phases in length. Without a notion of 'disjoint components' it would be necessary to either synchronize all the phase changes, or combine all the communications into a single phase; either way would seriously limit the amount of bandwidth that could be scheduled for each communication.

## **1.1 Contributions of the Research**

The primary contribution of this research is demonstrating the effectiveness of a scheduled router on a range of dynamic and multi-phase applications. The results demonstrate its ability to generate better cycle counts for some classes of applications, and similar cycle counts

<sup>&</sup>lt;sup>1</sup>The <u>Communication OP</u>erators language

(and thus presumably faster wall-clock time) for other, arbitrary applications. Similarly, the provided results demonstrate that reprogrammable scheduled routing is a relatively general solution for routing. A secondary contribution is the design of a language that expresses the communication requirements of an application, in a way that simultaneously separates communication from computation, yet still provides sufficient semantic information to guide a routing compiler in producing efficient scheduled routing code.

Within this domain, this thesis contributes a variety of specific techniques for reprogrammable scheduled routers that allow for specific functionality or that improve performance.

- A wide variety of approaches for implementing a given communications operator, particularly when the operator involves data-dependent communications.

- An implementation of a virtual online router that allows for arbitrary communications to be issued by the application when absolutely necessary.

- Techniques for managing 'continuing operators' extending across multiple phases, without losing data from the continuing operators during phases changes, and without compromising other operators at phase-switch time.

- Algorithms for determining how to switch a node safely from running one phase to running another, without losing data in the current phase.

- Algorithms for determining what times are safe to communicate between nodes, given the possible presence of neighboring nodes that have not changed phases synchronously.

- A model for treating the router as a *cache* of currently-active scheduling information, handling such issues as optional phases (or phases selected at run time), as well as managing cache placement for groups of resources simultaneously.

- An algorithm for placing router-updating code in the application that allows for nodes uninvolved in a subset to nonetheless support communications for that subset.

- An approach for partitioning a mesh such that different threads of control can run independently, based only on which nodes are included in each communication operator and whether groups of operators are specified as running sequentially or in parallel.

- An algorithm for choosing how to partition a program optimally into communication phases, and simultaneously how to implement each communication operator most effectively.

Using these techniques, two backends for the COP compiler have been implemented, one for traditional dynamic routing and one for a reprogrammable scheduled router (NuMesh). Comparisons of the two backends are presented, examining the performance of the communications generated in each case.

This research does not include two critical components of scheduled routing. The first component is the process used to extract a communication-language program from a high-level language such as Fortran. The second component is the process used to schedule a single phase of static streams on a mesh. The research falls, in a sense, between the two levels, interfacing a high-level language to a low-level scheduling router.

## 1.2 Benefits of Scheduled Routing

Before proceeding further with the material, let us look more closely at scheduled routing itself, which can be dramatically superior to conventional routing in a number of different ways. Until now, it has been fairly difficult to access this functionality for all but a limited selection of applications.

#### 1.2.1 Cycle Speed

One of the most significant advantages of scheduled routing is that it allows all routing decisions to be made offline, and thus out of the critical path at run time. Consider a typical routing decision made by a dynamic router: it must read a word from another node, examine the header of the node for its destination (and possibly adaptive-routing information), and choose a neighbor node (or virtual channel) to send it to. These decisions, which are in the critical path for message latency, take time. Pipelining techniques can be applied to this decision-making to reduce cycle times and increase bandwidth, but the latency for message transfer remains the same.

Furthermore, as is discussed in Section 1.4, a scheduled router can avoid all round-trip handshakes when doing flow-controlled data transfers. This allows scheduled routing to perform flow control within a single inter-node transfer time. Larger buffers and asynchronous flow-control signals can be used to avoid round-trip handshakes for dynamic routers as well, but this is costly in terms of pin resources and/or buffer management.

In [2], a comparison of dynamic routers is given, breaking down all the components of the cost. A simple deterministic router's cycle time is quoted at 9.8 ns, with a simple planaradaptive router taking 11.4 ns. In [56], Shoemaker uses these component estimates to derive an estimate for the cycle time of a scheduled router using the same technology. He finds that the NuMesh scheduled router's cycle time is constrained only by the time for a single cross-node transfer, 4.9 ns. This is 50% of the deterministic router's clock period, and 43% of the simple adaptive router's. Improved signaling techniques or pipelining the cross-node transfer itself would decrease this cycle time even further with only minimal effect on the techniques used for scheduled routing.

#### 1.2.2 Hotspot Avoidance

One important advantage of scheduled routing is its ability to make full use of a network's internal bandwidth when presented with data patterns that normally cause hotspotting in the network. For example, a bit-reversal routing can be efficiently distributed across the bisection by precomputing the paths that all the data will follow. Less-structured communication can also be routed cleverly so as to avoid problems from contention in the network. In general, when using all the scheduled streams at full bandwidth, the only time that communications will run slower than the actual path distance between nodes is when the network bandwidth needed is inadequate, not just because of contention artifacts.

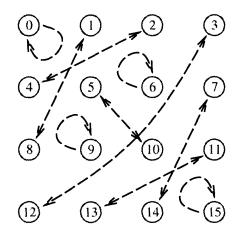

Figure 1-1 shows a simple communication pattern that demonstrates this problem. Each node transfers data to the node whose number is the bit-reversal of its own number; thus node 2 (binary 0010) transfers its data to node 4 (binary 0100). When transferring data using standard

Figure 1-1: Bitreversal on a small mesh

dynamic-routing schemes, messages will tend to saturate particular links in the mesh. For example, using e-cube routing (where messages travel first in the x dimension, then the y), all the data from the top and bottom rows will flow using along the links on the edges of the mesh, using none of the central links. As the mesh grows (particularly for 3D meshes), the problem gets worse. With scheduled routing, good paths can be found for all the communications; Figure 1-2 shows possible scheduled paths for the  $4 \times 4$  example.

Figure 1-2: Scheduled paths for bitreversal on a small mesh

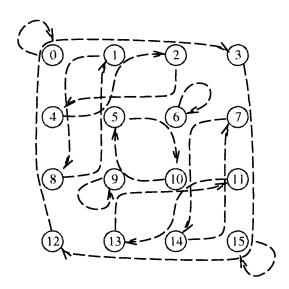

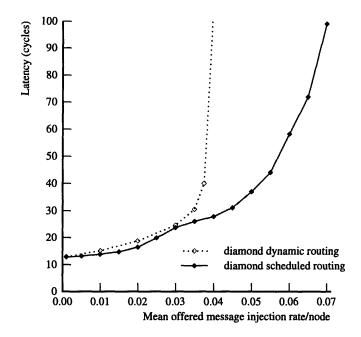

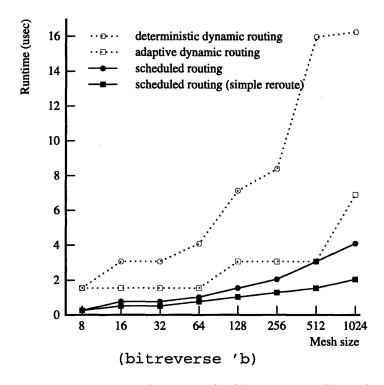

Figure 1-3 shows the results of a simple benchmark for bitreversal using different routing techniques. 512 data words are transferred between each pair of nodes with bitreversed addresses. Regular e-cube dynamic routing is shown, as is a simple adaptive routing technique from [21], and a scheduled-routing algorithm. The scheduled-routing algorithm schedules a route for all the streams at compile time by rerouting streams one at a time until it finds a good path, using only per-link bandwidths to determine legal routes. The dynamic routing cycle counts are gathered by simulation, and the scheduled routing cycle counts by scheduling a path

and deriving the number of cycles a message takes to flow across the paths given the allocated bandwidths.

Figure 1-3: Bitreversal routing (dynamic vs. scheduled routing)

The graph shows that the latency (expressed in cycles) for the two dynamic routing techniques is worse than for scheduled routing, and rising faster as the graph grows larger. Adaptive routing comes close in cycle count to scheduled routing, but to do that it must pay a price in router complexity and resulting slower cycle times.

#### **1.2.3** In-Router Algorithms

Beyond raw routing speed, however, scheduled routing offers the ability to build something of the structure of the algorithm into the network without compromising the speed of message delivery.

Consider the parallel prefix operation, for example. It takes an array of values  $a_0, ..., a_{n-1}$  and an operator  $\otimes$ , and returns, on each node k, the value  $a_0 \otimes a_1 \otimes ... \otimes a_k$ . Any associative operation can be used for  $\otimes$ : add (integer or FP), OR, AND, XOR, MIN, MAX, *etc.*, as well as any user-defined operation; operands can be of any length. One well-known use of parallel prefix is the carry-lookahead adder. On a scheduled router, the prefix implementation can be partly expressed in the router, with nodes multicasting partial sums to all their descendants in the prefix tree with a single message send. As a result, there is no extra overhead in the processor from having to resend the data to its children, and the processor simply does the minimum number of reads and writes to the network necessary to provide arguments to the prefix operation being computed.

Other complex communication structures can also be built in the router to take data where it is generated and deliver it to where it is needed without requiring complex multicast setups in the processor, or requiring processors to forward data within the mesh. For example, data can be scattered and gathered within the mesh by constructing the router code to deliver the first word on a given stream to its processor and route the remainder of the message to a neighbor processor. Conversely, a stream could be set up that took data from its processor and forwarded it, then reconfigured automatically to take data from its neighbor only. Such operations on a traditional online-routed machine require multiple messages, each with its own setup time and header overheads.

#### **1.2.4 Stream Prioritization**

Scheduled routing can also be useful in situations where different streams of message traffic have different bandwidth needs. By preallocating differing amounts of schedule time to each stream, bandwidth is divided as necessary for efficient application performance, even when all the streams are being driven full-out: the higher-bandwidth streams don't crowd out the lower-bandwidth streams, nor do a number of lower-bandwidth streams combine to reduce the required bandwidth on one higher-bandwidth stream. Message prioritizing in traditional online routing systems is similar to this approach, but does not offer as fine a degree of control over the relative bandwidth needs of a collection of streams.

As an example, consider a rendering engine that generates images in real time using internode communications. Periodically, the system may change to a different image by distributing a large data set to all the nodes. However, the time-critical communications between the nodes as they render the last few frames of the image should not be compromised by the high-volume data set for the next image being downloaded into the mesh.

Similarly, it is also possible to tune a stream's latency to meet application needs. A given stream may be low bandwidth, but may want to run with as little latency as possible. This need can be met by appropriate scheduling, without compromising the ability of high-bandwidth streams to run at their full designated bandwidth.

#### **1.2.5 Header Traffic**

All online routing algorithms require some form of overhead associated with each message, typically in the form of a message header of one or two words holding the destination address, length, and so forth [18]. Offline-routed messages generally require no packet headers, since the message is identified by the scheduled time of transmission rather than by any data that it carries with it. In applications that send a large number of short messages, the headers can constitute a noticeable percentage of the total traffic carried, and avoiding their use can increase the bandwidth available to data.

As a simple example, consider an example where communications are typically messages with four data words; in this case, a dynamic router would add an additional word, increasing traffic in the mesh by 20%. All things being equal, a scheduled router would see 20% better bandwidth, along with improved latency.

#### **1.2.6** Non-Cartesian Networks

Not all networks are as easy to route for as the Cartesian network; there, the e-cube algorithm easily achieves 100% of the bisection bandwidth on random traffic (consider two random nodes

on opposite sides of a bisection; the probability of a message between them using any particular link in the bisection is equal to that for any other bisection link). Irregular networks may be convenient to build based on component availability or, for dedicated nodes, for predicted bandwidth needs among nodes. Such networks are extremely difficult to handle using online routing algorithms, since the route from one node to another may not lead through any obvious path.

Even regular topologies may be hard to get maximum performance from with online algorithms. For example, the diamond lattice network [63, 52] is an appealing network topology, with isomorphic 3D connectivity but only four neighbors for each node; this allows a simpler crossbar and more pins per I/O port for pin-limited packages. However, the diamond lattice suffers from the fact that using exclusively shortest path connections prevents the network from achieving 100% of its bisection bandwidth. In fact, no known online algorithm is able to provide full bandwidth across the bisection on the diamond lattice. Accordingly, scheduled routing can serve as an enabling factor for exploring the potential of non-Cartesian networks.

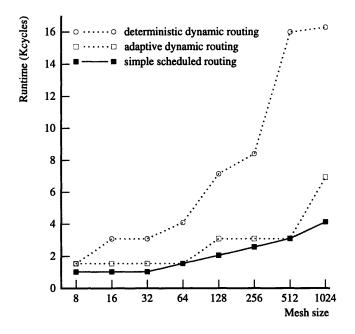

Figure 1-4 shows the difference in achievable bandwidth in a diamond-lattice network between traditional online routing and a version of scheduled routing. The graph depicts random traffic; the diamond-lattice mesh simulated is of size 455 (a 7-ary 4-diamond), with length-4 messages. The online algorithm is a suitably modified version of the Cartesian network's oblivious e-cube algorithm. As before, cycle counts are gathered by simulation of dynamic algorithms and a simple computation from scheduled bandwidths for the schedule router.

Figure 1-4: Diamond-lattice scheduled routing

The graph shows that the dynamic routing algorithm hits a maximum throughput limit around 0.04 mean offered messages per node (that is, the point when each node has a 4% chance of injecting a message on each cycle). By contrast, the scheduled algorithm continues to provide throughput (though with growing latency) up to 0.07, the largest mean offered rate per node shown.

#### 1.2.7 Faulty Networks

Scheduled routing also allows faulty networks to be used efficiently. For a network with components that are faulty at compile-time, the same arguments apply here as discussed in the previous section. A network test can be performed before an application begins to run, and dead nodes and links can be worked around in the schedule.

If links or nodes die during the program execution, a low-bandwidth stream can be provided to notify all the nodes of the failure and switch to a checkpointing mode to dump the application state before rebuilding the communications graph and continuing. More sophisticated approaches can also be built into a runtime system that knows what communication operations a given node or stream is involved in, and can instruct neighboring nodes (using a low-bandwidth stream) to modify their schedules to accommodate the extra bandwidth demands on them caused by a neighboring dead node or stream.

### **1.2.8 Multiple Applications**

While current research in scheduled routing has assumed multiprocessors with a single application at a time, this restriction is not absolute. Multiple applications and multiple users can share a scheduled network by allocating portions of each router to each application. The network will be timesliced along with the applications themselves, with a context switch on the processor accompanied by a context switch of the scheduled router. Direct access to the physical hardware would be mediated by some combination of hardware support (as in FUGU [47]) and operating-system support (as is done in the Exokernel [22]). The resulting multitasking system should provide similar gains to each process as could be found on a single-tasking system, though for each additional task, the smaller amount of router memory available per-task would cause extra reload time (as is discussed in Section 5.4).

## 1.3 Drawbacks to Scheduled Routing

Unfortunately, scheduled routing is not a panacea, and some applications will be unlikely to benefit from simple scheduled routing.

High-bandwidth applications that require primarily short-lived, highly-dynamic communications are not well-suited to scheduled routing. All three qualifiers are important to this limitation, however:

- When applications are low-bandwidth, it is easy to create multiple streams at compile time and choose among them at run time.

- When the connections are long-lived, extra setup time can be expended to create appropriate routing schedules and still benefit from high cycle speeds and low contention.

- Lastly, when communications are constant, or data-dependent in a structured manner, the scheduled router can support them directly at full speed.

Only when all of the above qualifiers are true does communication using scheduled routing become slower than dynamic routing; in this case scheduled routing must use a form of dynamic routing, as discussed in Section 4.2. Applications with little or no compile-time knowledge of the *order* of communications are problematic in the same way as applications with short-lived dynamic communications. The notion of communication phases is dependent on being able to separate communications into sets, each with some temporal locality. If an application has a large number of possible communication streams, the result is much like the application with short-lived dynamic communications, just expressed somewhat differently.

While the thesis explicitly ignores the issue of converting high-level language inputs into structured communications, this process can be either helped or hindered by the choice of high-level language. Some languages, such as HPF [46] or Crystal [15], provide high-level communications operators; these operators easily allow for suitable communication schedules to be generated. Other languages, such as Mul-T [38] and Linda [14], have less emphasis on high-level operations and are harder to extract structured communications from.

For languages with lower-level primitives, the burden falls to the compiler to extract the necessary structured communications. As discussed above, if the compiler can only find short-lived, highly-dynamic communications in the language, the performance on a scheduled router will suffer. If the code only contains send and receive operations, or fork and join, the compiler must be relatively sophisticated to ascertain such things as a broadcast from a run-time source or a reduction.

One way to handle the problem of applications with dynamic communication characteristics is to include dynamic-routing hardware in the scheduled router. Doing so allows the compiler to schedule a certain amount of bandwidth to devote to dynamic routing; effectively, adding such support allows the hardware to support scheduled routing and dynamic routing both.

## **1.4 Scheduled Routing**

The previous section presented the benefits of scheduled routing at a high level. This section examines the basic mechanisms of scheduled routing in sufficient detail to understand the key ideas of the thesis. Chapter 7.1 discusses the specifics of the NuMesh implementation of scheduled routing in somewhat more detail.

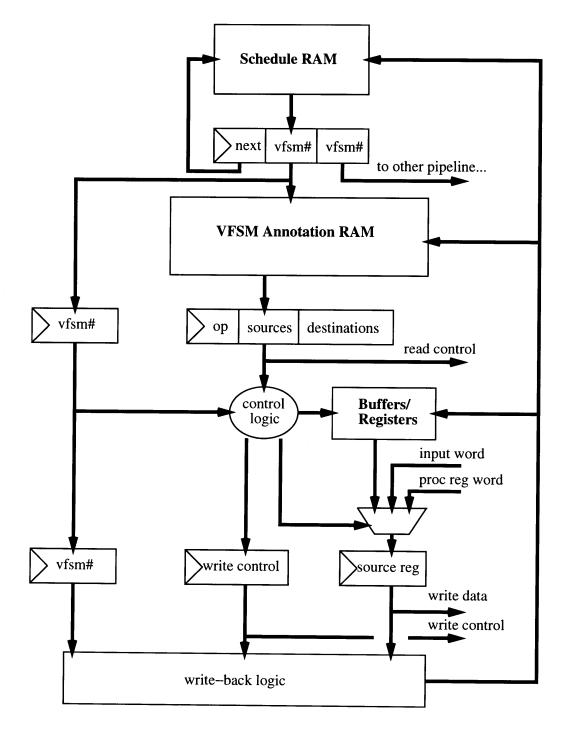

#### 1.4.1 Scheduling Virtual Finite State Machines

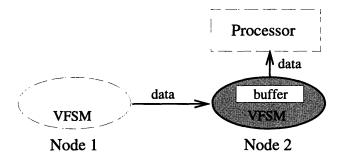

The fundamental unit of scheduled routing is the virtual finite state machine, or VFSM. A VFSM handles moving a particular stream of data through a particular node. It includes some buffering for that particular stream of data as well as annotations (called the VFSM's source and destination) that indicate where its data come from and go to. Figure 1-5 shows a simple VFSM for a stream of data moving from node one through node two's router to node two's processor. Linking together all the individual VFSM sources and destinations on each node yields an overall VFSM chain that moves the data from a stream's original source to its final destination; in the given example, the stream's source might be node zero, and its destination is node two.

If it was only necessary to move one stream of data through each node, a single VFSM could be used as a router. However, it is much more common to need to move several unrelated

Figure 1-5: A virtual state machine transferring data

streams of data through each processor. This can be accomplished by scheduling the VFSMs in some predefined sequence on a node, essentially time-slicing the router hardware into multiple virtual finite state machines (thus the 'V' in 'VFSM').

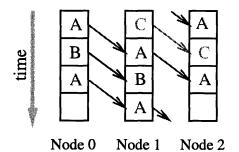

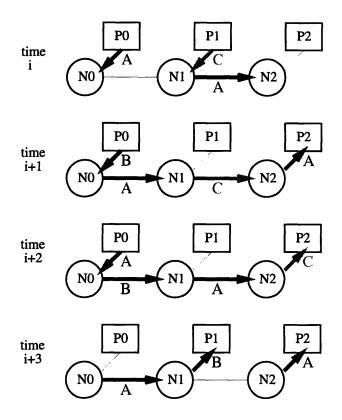

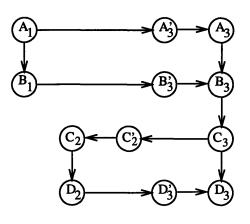

However, it is necessary to be able to differentiate two streams of data that just happen to pass between the same two nodes at some point. To do so, the VFSMs are scheduled globally, so that when a VFSM on one node does a write at a particular time, the VFSM that reads the same stream of data on the neighboring node is scheduled one clock cycle later. Figure 1-6 shows how VFSMs might be scheduled on three nodes (in a one-dimensional array), carrying three streams of data among them. Stream A, with bandwidth 0.5, carries data from nodes 0 to 2; streams B and C, with bandwidth 0.25, carry data from 0 to 1 and from 1 to 2, respectively. Each word of data moves through the mesh at one cycle per node; the number of times a given VFSM appears in a schedule corresponds to its allotted bandwidth.

Figure 1-6: VFSM schedules on a small mesh

Another representation of how scheduled routing is shown in Figure 1-7, which demonstrates which cycles data is carried across the wires in the mesh; router nodes are shown as circles, with their attached processors in boxes. In the example, a data word might start on node 0 on the VFSM for stream A when it's scheduled at time 0, get passed to node 1 at time 1, then passed to node 2 at time 2, where the last VFSM delivers data to the processor. A similar word leaving node 0 at time 1 must be associated with stream B, and will therefore be delivered by the VFSM for stream B on node 2 to the processor, instead of forwarded to node 3 as is true for stream A. Streams of data in a scheduled routing environment are thus bound tightly to a specific set of VFSMs on the nodes chosen to route them from their source to destination.

The nodes in the mesh are synchronized at boot time, and remain synchronized from then on. Each node runs its schedule repetitively, returning to the top of the schedule after running

Figure 1-7: Data movement on a small mesh

the VFSMs scheduled last in the schedule. Thus, if the schedule is of length k, the 3rd *timeslot* in the schedule will be run at time 3, 3 + k, 3 + 2k, and so on.

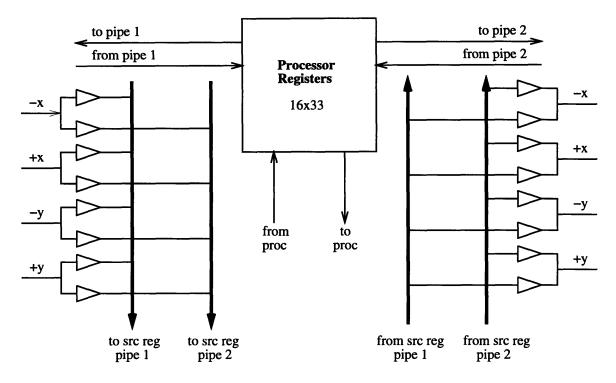

The discussion so far has assumed that the physical hardware is capable of only a single communication action per cycle. Multiple physical FSMs can be included on each node that are each independently timesliced by VFSMs. These physical FSMs are called *pipelines*, using terminology that reflects the implementation of the current NuMesh hardware. Each pipeline is capable of scheduling an independent VFSM for each cycle. Thus, on a given cycle there may be a simultaneous transfer by one pipeline of data from the +x to the -x directions, while another pipeline is transferring data from the processor to the +y direction. Co-scheduled VFSMs must have non-conflicting sources and destinations to avoid conflicts.

#### **1.4.2 Flow Control in Scheduled Routing**

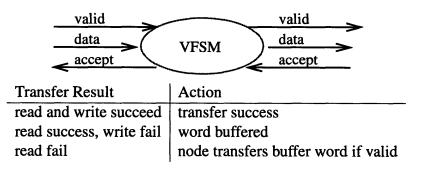

So far, it has implicitly been assumed that whenever data is ready to be transferred it can always be accepted by the destination. However, if the stream's destination processor is busy, and the source processor is attempting to write data into the mesh, the system must handle the potential for a backlog in the stream. This problem (known as the *flow control* problem) is handled by a synchronized exchange of control signals along with the data.

Whenever a valid data word can be written to a neighbor, the VFSM asserts the *valid* line to the remote reader and sends the data. When reading, a VFSM determines whether it has sufficient buffer space to accept another word of data, setting the *accept* line to the remote writer accordingly. After setting the accept line low, the reader will simply ignore any data

presented to it.

The difference from traditional online-routing schemes is that the accept line is driven by the reader at the same time as the valid line. Since the mesh is running schedules that are all offline-generated, a reader always knows when a writer is sending data, and it can generate an 'accept' during the same cycle as the data is written. This means that scheduled routing allows a single-cycle protocol for determining flow control.

When the writer VFSM discovers that the reader couldn't accept the data word, it queues the word in its buffer. The next time the writer is scheduled, it will set the accept line low for *its* writer, and attempt to transfer the buffered word instead of reading a new one. Figure 1-8 shows one VFSM with its incoming and outgoing control and data lines, and summarizes what actions it takes depending on the state of those lines. These actions happen in synchrony across the entire mesh every cycle; this choreography—scheduling which VFSMs run on each node at each cycle—determines how data moves through the mesh.

Figure 1-8: NuMesh transfer actions

#### 1.4.3 Router Reprogramming

The router may be updated under program control. Each scheduled router is assumed to have a schedule memory which can hold multiple schedules (of which only one is active). Each location in the router in which a schedule can be placed has some index associated with it. New schedules can be downloaded to the router by specifying the desired index and providing the schedule information. COP requires a router schedule memory large enough to hold at least two complete schedules, so it can load a new schedule into the router while the previous one continues to run.

Similarly, each router is assumed to have multiple VFSMs, of which only some are used in a given schedule. VFSMs can be used for the same operator in multiple schedules (as is discussed in Section 5.1); however, VFSMs can also be *reused* by changing the source and destination annotations associated with the VFSM, then using the VFSM in a new schedule. An index is associated with each VFSM that allows it to be referenced both for scheduling and for reprogramming its annotations.

#### 1.4.4 Other Characteristics of Scheduled Routing

**Processor Interface.** At each end of a stream of data, the router must deliver data to and from the processor itself. The interface between the two can be specified as just another flow-

controlled source or destination for the VFSMs. The architecture could require that the processor be synchronized to the mesh sufficiently to know that a data word in timeslot 5 belongs to a certain stream. However, to allow for a more general, asynchronous interface, multiple interface addresses are provided. The router can deliver data from stream A consistently to interface address 12; the processor can then read interface address 12 at its leisure to find data from stream A.

Scheduling Delays. Streams can also be delayed one or more cycles on a node. Normally, a VFSM is scheduled on a given cycle, reads the data from its specified source, then writes the data to the appropriate VFSM on the next node on the following cycle. However, global scheduling constraints may make it infeasible to schedule a stream on consecutive cycles in each node in its path. Accordingly, it may be necessary to delay a few cycles to find a suitable path. This can be done by allocating two VFSMs on a node to a stream. One reads from the neighbor node, then hands off to the other VFSM; the second VFSM, scheduled later, reads from the first one and then writes the data word to the destination node.

**Data Forking.** A data 'fork' allows a stream of data to be forked to two (or more) destinations within the router. This feature can be used to arrange a multicast stream that has multiple destinations. A data fork can be implemented by consecutively scheduling a set of VFSMs, the first of which is responsible for reading the data from the neighboring node, and each of which handles one of the destinations. Multiple data forks can be placed in a stream; this creates a distribution tree that can send the data to the destinations in an optimal manner.

### **1.5 Thesis Outline**

The rest of this thesis is organized as follows: Chapter 2 provides a brief overview of the communications language, COP, motivated by the demands of reprogrammable scheduled routing. Chapter 3 looks at related work in the field. Chapter 4 examines how to handle data-dependent communications with a scheduled router; Chapter 5 examines how to handle multiple phases of communications in an application using scheduled routing. Chapter 6 looks at the techniques used to search out optimal implementations and phases. Chapter 7 provides details of the two current backends of the COP compiler, one for the NuMesh reprogrammable scheduled router and one for traditional dynamic routers. Chapter 8 presents some comparative data on performance for the two backends. Finally, Chapter 9 presents the conclusions drawn from the research. Two appendices are also included, one giving more details of the COP language, and the other providing a list of operator implementations.

## Chapter 2

## **The Communications Language**

This chapter presents an overview of COP, the <u>C</u>ommunication <u>OP</u>erators language (think of a traffic cop directing the flow of network traffic). The language features presented here are motivated directly by the needs of scheduled routing, and are sufficient to place the related work in context. Later sections will include further discussions of language features as they are motivated; a full reference for the language can be found in Appendix A.

COP assumes a multiprocessor model of *nodes* interconnected in a network; each node has a processor (*e.g.*, a conventional off-the-shelf CPU) and a local memory. Each node includes a *router* that handles the connections among the nodes. A COP program expresses all the communications in an application from a processor-to-processor perspective. The application is thus completely freed from having to know how data is moved around within the network, and simply calls COP compiler-generated functions to perform all I/O.

The chapter begins by presenting some motivation for a separate communications language; Section 2.2 introduces COP 'operators'. Sections 2.3 and 2.4 discuss COP's support for phases as well as for grouping operators together. Restricting operators to subsets of the mesh is considered in Section 2.5, and expressing data-dependent communication in Section 2.6. Section 2.7 discusses the COP computational model, and Section 2.8 briefly outlines COP's extensibility. Finally, Section 2.9 gives some COP examples, and Section 2.10 discusses design issues for the language; a summary section concludes.

## 2.1 Motivation

Programming a scheduled-routing communications substrate requires a traditional language compiler to become substantially more complex. There are several simple approaches that can be taken to try to avoid some of this difficulty:

- Limit the application to a set of constant streams in a single phase. The introduction discussed why such a model is inadequate, but it does have the advantage that it is relatively straightforward to implement and requires no close coupling between the stream router and the high-level language (HLL) compiler.

- Create the necessary schedules by hand for each application (or perhaps by an applicationspecific compiler, similar to [4]), allowing for any necessary data-dependency and schedule-

switching by a close knowledge of the particular communications schedules created for that application. This solution, while allowing the necessary power for the given application, is insufficiently general.

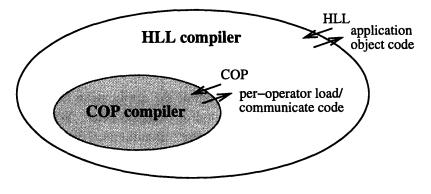

Instead, let us consider the more general compilation possibilities. While it would be possible for an application to handle all its I/O requirements internally, the COP language allows for a high-level language (HLL) compiler to specify the communications using COP instead and leave all the communication details to the COP compiler. This *split-language* approach separates the burden of offline communications generation from the usual, language-dependent compiler chores such as partitioning and placement. This separation of responsibility means that many HLL compilers can use COP, and COP can handle a variety of different hardware backends, so that M languages and N hardware backends require only M + N compilers rather than MN. Previous HLL compilers have not taken this approach because a dynamic router is a relatively trivial target for a communications compiler, unlike a reprogrammable scheduled router.

Partitioning the communication and the computation in this manner is a delicate balancing act. If too little information is provided to the communications compiler, the resulting application may not run as fast as possible, limited by its communications. On the other hand, if too much information is provided, the communications compiler requires a very closely-coupled interface to the HLL compiler, and becomes effectively tied to that compiler.

The remainder of this chapter presents the COP language; then, in the final section, the issue of separating the compilation of communications and computation is addressed again. For now, it is worth observing that COP is motivated additionally as a research vehicle, despite any potential drawbacks associated with its nature as a stand-alone communications language. Structuring the compiler around COP allows for an exploration of reprogrammable scheduled routing without the distraction of more routine compiler issues, and still offers insights into the mechanisms required for a compiler to target a scheduled router at any level of abstraction.

A *communication language* such as COP is distinguished from other languages by two key features:

- 1. It does not attempt to express an application's computation, leaving that to a separate compiler;

- 2. It is intended to be compiled rather than evaluated at run-time, thus providing a structured form of the actual application's communication needs.

COP, in fact, is not a language in the traditional sense of the word. A COP 'program' is fundamentally just a hierarchy of communications expressions; the language has no run-time variables or control structures. Since the input is evaluated in a Lisp environment, a wide variety of control structures are available at compile-time, but the Lisp environment basically functions as a macro language designed to make COP programs easier to specify.

## 2.2 Expressing Communications as Operators

A first question to ask for a language specifying communications is where to place the abstraction layer for the communication operations themselves. The communications compiler should have the freedom to implement communications patterns in an optimal manner. For example, consider the case where the application wants to perform a broadcast to the mesh from node zero (as shown in Figure 2-1). The best technique to use will depend on the size and topology of the mesh, the relative speed of the interface and the routers, and the capability of the routers, among other things. Some options for a broadcast include a direct multicast (for a scheduled router), sequential writes to each destination (for a dynamic router), a flood-fill technique (for a dense mesh), or a tree-broadcast technique.

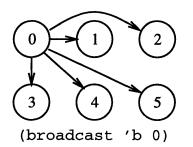

Figure 2-1: Broadcast abstraction

The application can not and should not attempt to determine which is the best way to perform the broadcast. Each technique requires the processors to interact differently with the mesh, so the application can't specify the broadcast semantics by simply listing a set of streams that it wants to use. Therefore, COP provides the necessary semantics by placing the abstraction barrier higher.

Accordingly, the basic unit of a COP program is taken to be the *operator*; each type of operator corresponds to a particular communication pattern. Operators range in complexity from a simple stream operator, expressing a single stream of data with source and destination known at compile time, to a prefix operator that performs a parallel prefix operator on the involved nodes. (The 'operator' framework has other advantages, which will be described throughout the chapter.)

An example operator follows; this one line is also an acceptable complete COP program (perhaps for an application that simply broadcasts work to clients who display the results locally):

#### (broadcast 'b 0)

The first argument to the operator gives the operator's *label*; this value is used to label the COP output for this operator (this issue is revisited later). The second argument, for a broadcast, specifies the source of the broadcast. The COP compiler can choose any of a variety of operator *implementations* for the broadcast, based on what will perform best in the particular context specified by the application and the target mesh. Additional *optional arguments* can be specified as annotations, giving information on approximate message count, maximum required bandwidth, and the like; these are introduced when motivated in the text, and enumerated in Section A.3.

A wide variety of global operator types are available in the COP library. Included among the set of operator types are stream, reduce, allreduce, prefix, broadcast, collect, barrier, cshift, eoshift, transpose, bitreverse, and permute. The stream operator is particularly noteworthy, as it allows arbitrary connections to be specified between pairs of nodes when no higher-level operator exists to describe the communication. Appendix A.1 describe all of the COP operator types in more detail.

Expressing communications as operators yields an additional advantage. As was discussed in Section1.2.3, scheduled routing allows for higher-level routing constructs to be executed (at least partly) within the routers themselves. The example used there, parallel prefix, expresses underlying semantics not readily reduced to simple, efficient communication primitives. By including such high-level operators as COP primitives, it becomes possible to portably access these features, increasing applications' performance on more capable routers without limiting the applicability of COP to simpler routers.

Additionally, the fact that scheduled routing requires *global* scheduling matches well with the use of *aggregate* high-level operators in COP. Since the routers' schedules must be controlled in a coordinated manner, aggregate operators that require global knowledge are an appropriate match.

The simple, one-line COP program above is used again in Section 2.7, where it is used to illustrate the interface between COP code and application code.

## 2.3 Supporting Phases

An important feature of any communications language is that it support phases: without such support, all the communications must be merged into a single phase. For scheduled routing, such merging would result in disastrously little bandwidth available to each operator, as all the operators would have to share the available scheduled bandwidth.

As is discussed in the next chapter, some existing communication languages support fixed, user-specified phases. That is, the communications language explicitly indicates the boundaries between phases. However, for the HLL compiler to attempt to derive phase boundaries is for it to take on itself the job of the communications compiler. Determining phase boundaries depends on message traffic, the effects of scheduling multiple operators in one phase, and the overhead for changing out of a phase with a given set of operators in it, among other things. Accordingly, making such decisions is beyond the scope of the HLL compiler.

It is also worth observing that since the notion of a 'phase' does not contribute much to compiling for a dynamic-routing target, it would be inappropriate to require phases to be specified in a language intended to be used for dynamic routing as well as scheduled routing.

#### 2.3.1 Choosing Optimal Phase Boundaries

When determining where to place the phase boundaries, the COP compiler must weigh a variety of factors. With scheduled routing, dedicating a single phase to an operator achieves the following goals:

- For a high-traffic operator, dedicating a single phase to it may be critical to achieve the necessary performance.

- Some operator implementations generate complete schedules for all the nodes (as is discussed more in Section 4.1), and therefore require a separate phase.

However, sharing a phase among a number of operators has several benefits

- It allows the operators in the phase to be used unpredictably by the application (as discussed in Section 2.4.1).

- It eliminates the overhead involved in changing phases between the operators.

- It reduces the footprint of a given set of operators in the router, thus allowing for more operators to be held in the router at once.

As a simple example, let us suppose it takes 20 cycles to switch from one phase to another for a given application and mesh. If there are two operators to schedule, the compiler can predict how long the communications for each phase will take when the operators are scheduled together or in separate phases. Let us suppose that, if scheduled in separate phases, each operator will get 0.667 bandwidth, whereas scheduled into a single phase together they will only get 0.500 bandwidth each. If each operator is used to send one message 50 words long, it will take 100 cycles per operator (200 total) if scheduled in the same phase, and 75 cycles (170 total, including 20 for phase change time) if scheduled in separate phases. Thus, the compiler will choose separate phases. If the messages were shorter (less than 40 words), a single phase holding both operators would be a better choice.

#### 2.3.2 Expressing Time

Accordingly, operators are grouped together simply by expressing that they are run sequentially (thus, whenever the application performs I/O on one of the operators in the group, it is guaranteeing that it has finished performing I/O on the earlier operators). Using this information, the COP compiler can determine where within a sequence of sequential operators to place phase boundaries (if any). For example, a broadcast to all the nodes, followed by a reduction, would be specified as

```

(sequential

(broadcast 'b 0)

(reduce 'r 0 'myfunc))

```

(The second and third arguments to the reduce specify respectively that the result should be left on node zero, and that the high-level application is supplying a function myfunc to combine values on each node.) The COP compiler can now choose whether to compile this construct to one phase or to two phases based on timing predictions.

If a series of operators will be used repetitively, the loop construct is used instead of sequential. A label for the loop is specified (as is done for operators), along with an approximate loop count. A loop construct indicates that the last phase in the loop may be followed by the first phase, which is (as is discussed later) important for correct phase changes on a scheduled router. Thus, if the broadcast and reduction were repetitively performed, the COP program might be given as

```

(loop '1 1000

(broadcast 'b 0)

(reduce 'r 0 'myfunc))

```

## 2.4 Grouping Operators Together

#### 2.4.1 Multiple Operators

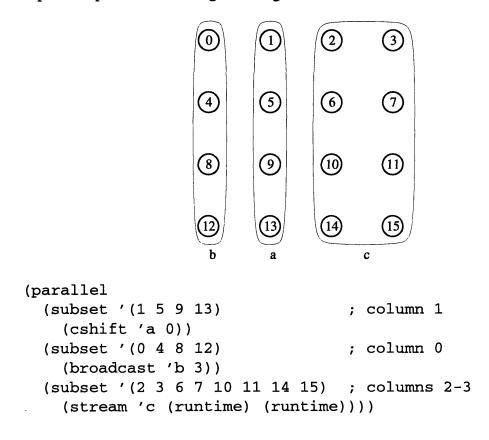

Of course, an application can't always guarantee that it will use operators sequentially, so a construct is needed in the language that indicates that a group of operators may be used in any order. This is expressed with the parallel construct. For example, if there are three specific 'root' nodes that broadcast at unpredictable times, the COP description might be

```

(parallel

(broadcast 'b0 0)

(broadcast 'b1 7)

(broadcast 'b2 12))

```

Operators appearing within a parallel construct must be scheduled into a single phase to allow the application to use them all unpredictably. The parallel construct is thus more restrictive than the sequential construct, since the COP compiler is free to treat a sequential as a parallel, but not the reverse.

An alternate form of the parallel command is available as a macro which can parameterize multiple instances of a parallel command. The doall command takes a variable specification (in the same form as a let statement, with list values for the variables), and converts it into a parallel command by concatenating the results of evaluating the body with the variables bound to all combinations of their list members in turn.

### 2.4.2 Continuing Operators