## Design and Modeling of a High Current Switching Regulator

by

Danielle Coffing

Submitted to the Department of Electrical Engineering and Computer Science

in partial fulfillment of the requirements for the degree of

Master of Engineering in Electrical Engineering and Computer Science

at the

### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

June 1997

© Danielle Coffing, MCMXCVII. All rights reserved.

The author hereby grants to MIT permission to reproduce and distribute publicly paper and electronic copies of this thesis document in whole or in part, and to grant others the right to do so.

Chairman, Department Committee on Graduate Theses

### Design and Modeling of a High Current Switching Regulator

by

Danielle Coffing

Submitted to the Department of Electrical Engineering and Computer Science on May 8, 1997, in partial fulfillment of the requirements for the degree of Master of Engineering in Electrical Engineering and Computer Science

#### Abstract

A design method for switching regulators using Matlab and Simulink has been developed. The Matlab script presented calculates the necessary bandwidth of the loop given the power distribution network characteristics and the maximum acceptable output voltage variation. The compensation network is then calculated for given characteristics of the output filter components. The script also analyzes the stability over the range of possible load currents. The transfer functions describing the system are loaded into a regulator model in Simulink so that transient simulations can be performed. This design method has been correlated with Spice and four breadboards. The design cycle time can be decreased by using Matlab to gain intuition for how parameter and component variation affect the stability and transient performance of the regulator. This method presented is then used to determine the necessary characteristics of the error amplifier and comparators used in the MC33470 design. Finally, the OTA and comparator designs are presented.

Thesis Supervisor: Martin F. Schlecht Title: Professor of Electrical Engineering

### Acknowledgments

I gratefully thank the following people who have given me their support on this thesis:

Doug Domke, operations manager, for the opportunity to do this project.

Bob Vyne, design manager; and Al Zahedi, product manager; for the thesis description, administrative and technical support and oversight, and overall guidance and direction.

The Intel program managers; Bob Dotson, project leader; Jeff Morud, applications; and Todd Manes, production and test; for providing detailed oversight and help on specific design and operational requirements.

Also, never-ending technical support from Tom Somerville, Tom Petty, Troy Stockstad, and Richard Griffith in design; Monty Palmer and Theron Barnes in layout; and Jaime Vargas in test.

Finally, Professor Schlecht, for his thoughtful explanations and valuable advice.

# Contents

| 1 | Introduction                                                   |                                                            |                                         |  |

|---|----------------------------------------------------------------|------------------------------------------------------------|-----------------------------------------|--|

|   | 1.1                                                            | Background                                                 | 14                                      |  |

|   | 1.2                                                            | Design Strategy                                            | 16                                      |  |

|   | 1.3                                                            | Thesis Organization                                        | 17                                      |  |

| 2 | Vol                                                            | tage Regulators                                            | 18                                      |  |

|   | 2.1                                                            | Switching versus Linear Regulators                         | 20                                      |  |

|   | 2.2                                                            | Switching Regulator Control Methods                        | 23                                      |  |

|   |                                                                | 2.2.1 Voltage Mode Control                                 | 24                                      |  |

|   |                                                                | 2.2.2 Peak Current Mode Control                            | 26                                      |  |

|   |                                                                | 2.2.3 Average Current Mode Control                         | 27                                      |  |

|   |                                                                |                                                            |                                         |  |

| 3 | Reg                                                            | gulator Top-Level Modeling                                 | 28                                      |  |

| 3 | <b>Reg</b><br>3.1                                              | gulator Top-Level Modeling Spice as a Control Systems Tool | <b>28</b><br>29                         |  |

| 3 |                                                                |                                                            |                                         |  |

| 3 | 3.1                                                            | Spice as a Control Systems Tool                            | 29                                      |  |

| 3 | 3.1                                                            | Spice as a Control Systems Tool                            | 29<br>30                                |  |

| 3 | 3.1                                                            | Spice as a Control Systems Tool                            | 29<br>30<br>30                          |  |

| 3 | <ul><li>3.1</li><li>3.2</li><li>3.3</li></ul>                  | Spice as a Control Systems Tool                            | 29<br>30<br>30<br>46                    |  |

|   | <ul><li>3.1</li><li>3.2</li><li>3.3</li></ul>                  | Spice as a Control Systems Tool                            | 29<br>30<br>30<br>46<br>47              |  |

|   | <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>Dev</li> </ul> | Spice as a Control Systems Tool                            | 29<br>30<br>30<br>46<br>47<br><b>49</b> |  |

|          |      | 4.1.3   | Development of Matlab Script to Determine Loop Bandwidth  |     |

|----------|------|---------|-----------------------------------------------------------|-----|

|          |      |         | Requirement                                               | 54  |

|          | 4.2  | Outpu   | at Filter and Power Devices                               | 58  |

|          |      | 4.2.1   | Modeling Output Filter and Power Devices                  | 59  |

|          |      | 4.2.2   | Effect of Load Current Variation on Output Filter Model   | 62  |

|          |      | 4.2.3   | Development of Matlab Script to Determine Effect of Power |     |

|          |      |         | Distribution Network and Load Current Variation           | 64  |

|          | 4.3  | Error   | Amplifier and Compensation                                | 71  |

|          |      | 4.3.1   | OTA and Operational Amplifier and Compensation Modeling   | 72  |

|          |      | 4.3.2   | Development of Matlab Script to Find Compensation Network | 82  |

|          |      | 4.3.3   | Determination of Amplifier Characteristics                | 88  |

|          | 4.4  | Input   | Filter Modeling                                           | 91  |

|          |      | 4.4.1   | Instability Problems Associated with the Input Filter     | 91  |

|          |      | 4.4.2   | Matlab Modeling to Predict Instability                    | 93  |

|          | 4.5  | Simuli  | ink                                                       | 96  |

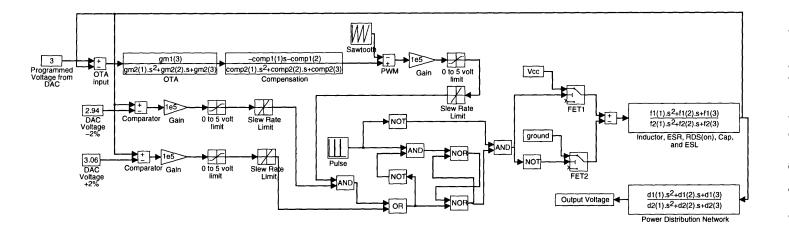

|          |      | 4.5.1   | Regulator Modeling in Simulink                            | 97  |

|          | 4.6  | Final   | script                                                    | 98  |

|          |      | 4.6.1   | Cost and Performance Optimization                         | 98  |

|          |      | 4.6.2   | Design Methodology Summary                                | 107 |

| <b>5</b> | Scri | pt Vei  | rification                                                | 109 |

|          | 5.1  | Verific | eation Procedure                                          | 109 |

|          | 5.2  | Bread   | boards                                                    | 112 |

|          |      | 5.2.1   | LTC1430 Breadboard Using AVX Capacitors                   | 113 |

|          |      | 5.2.2   | LTC1430 Breadboard Using Sanyo Oscon Capacitors           | 123 |

|          |      | 5.2.3   | LTC1430 Breadboard Using Nichicon Capacitors              | 131 |

| 6        | Reg  | ulator  | Design: MC33470                                           | 139 |

|          | 6.1  | Specif  | ications                                                  | 139 |

|          | 6.2  | Regula  | ator Parameter Extraction from Specifications             | 142 |

|          |      | 6.2.1   | Parasitic Values                                          | 142 |

|   |     | 6.2.2   | Output Filter Components                                      | 143 |

|---|-----|---------|---------------------------------------------------------------|-----|

|   |     | 6.2.3   | Regulator Output Impedance Requirement                        | 144 |

|   |     | 6.2.4   | Desired Phase Margin                                          | 145 |

|   |     | 6.2.5   | Operational Amplifier versus Operational Transconductance Am- |     |

|   |     |         | plifier (OTA)                                                 | 145 |

|   |     | 6.2.6   | Compensation Technique                                        | 146 |

|   | 6.3 | Matla   | b Script for MC33470 Design                                   | 146 |

|   | 6.4 | Simula  | ation Results and Design Requirements                         | 152 |

|   |     | 6.4.1   | Phase Margin and Stability                                    | 154 |

|   |     | 6.4.2   | Compensation Values and Slew Rate Requirement                 | 154 |

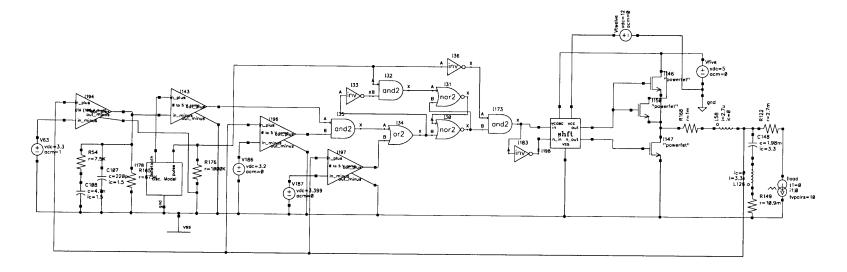

| 7 | Err | or Am   | plifier Design                                                | 157 |

|   | 7.1 | Ampli   | fier Topology and Technology Description                      | 157 |

|   | 7.2 | Input   | Differential Pair                                             | 160 |

|   |     | 7.2.1   | Common Mode Voltage Range                                     | 160 |

|   |     | 7.2.2   | Transconductance and Input Impedance                          | 162 |

|   | 7.3 | MOSE    | FET Modeling                                                  | 163 |

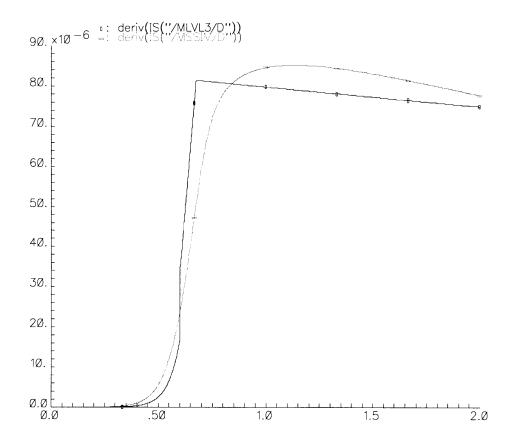

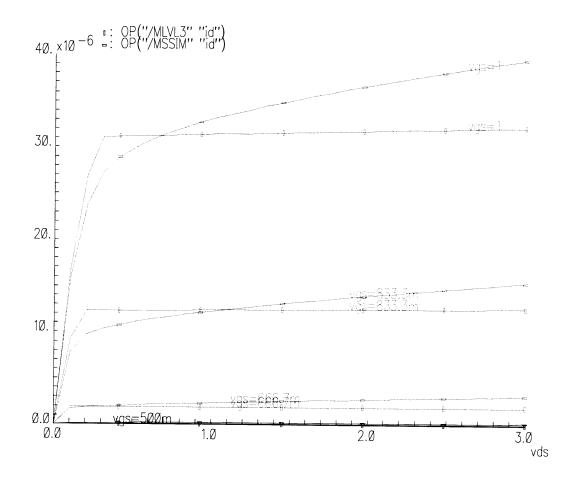

|   |     | 7.3.1   | Level 3 versus SSIM                                           | 163 |

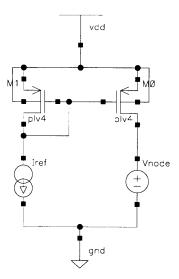

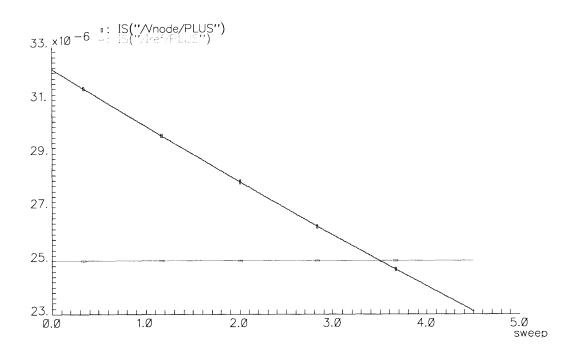

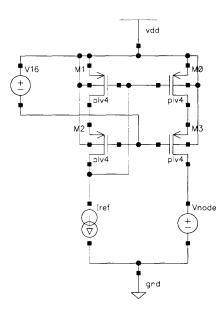

|   | 7.4 | Curren  | nt Mirrors                                                    | 168 |

|   |     | 7.4.1   | Drive Requirement and Slew Rate                               | 168 |

|   |     | 7.4.2   | Output Impedance and Cascoding                                | 169 |

|   |     | 7.4.3   | Output Signal Swing                                           | 172 |

|   |     | 7.4.4   | Input Common Mode Range Enhancement                           | 174 |

|   |     | 7.4.5   | Transconductance                                              | 175 |

|   | 7.5 | Biasin  | g                                                             | 176 |

|   | 7.6 | Design  | n Summary                                                     | 177 |

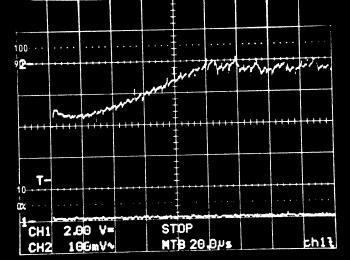

| 8 | Coa | arse Co | omparator Design                                              | 182 |

|   | 8.1 | Functi  | ional Description                                             | 182 |

|   | 8.2 | Desigr  | n Requirements                                                | 182 |

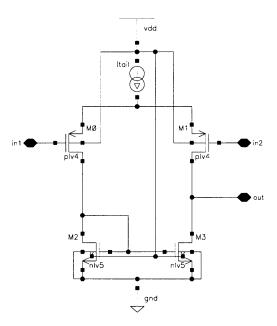

|   | 8.3 | Comp    | arator Architecture                                           | 183 |

|   | 8.4 | Simulation Results               | 185        |

|---|-----|----------------------------------|------------|

| 9 | Con | clusion                          | 190        |

|   | 9.1 | Summary                          | 190        |

|   | 9.2 | Conclusions                      | 190        |

|   | 9.3 | Future Work                      | 191        |

| Α | Mat | lab Script                       | 192        |

| в | Mot | orola MMSF5NO3HD Power FET Model | <b>224</b> |

# List of Figures

| 2-1 | Microprocessor supply voltage trend.                                    | 19 |

|-----|-------------------------------------------------------------------------|----|

| 2-2 | Microprocessor power dissipation trend                                  | 20 |

| 2-3 | Block diagram of a linear regulator.                                    | 21 |

| 2-4 | Switching regulator block diagram.                                      | 22 |

| 2-5 | a) Voltage mode control. b) Peak current mode control. c) Average       |    |

|     | current mode control                                                    | 25 |

| 3-1 | a) Switching regulator using an operational amplifer as the error am-   |    |

|     | plifier. b) Switching regulator using an operational transconductance   |    |

|     | amplifier as the error amplifier.                                       | 31 |

| 3-2 | Operational amplifier shown with input and feedback impedance net-      |    |

|     | works.                                                                  | 33 |

| 3-3 | Block diagram of an operational amplifier and feedback factor $\beta.$  | 34 |

| 3-4 | Frequency characteristics of an operational amplifier and compensation. | 39 |

| 3-5 | Block diagram of an error amplifier and compensation that includes      |    |

|     | the effect of the output impedance of the OTA.                          | 40 |

| 3-6 | Open loop transfer function of an OTA and compensation                  | 43 |

| 3-7 | Block diagram used in Matlab of the regulator using an a) operational   |    |

|     | amplifier and b) an OTA.                                                | 44 |

| 3-8 | Complete system transfer function for the example in Section $3.2.1$ .  | 45 |

| 4-1 | Power distribution network model.                                       | 51 |

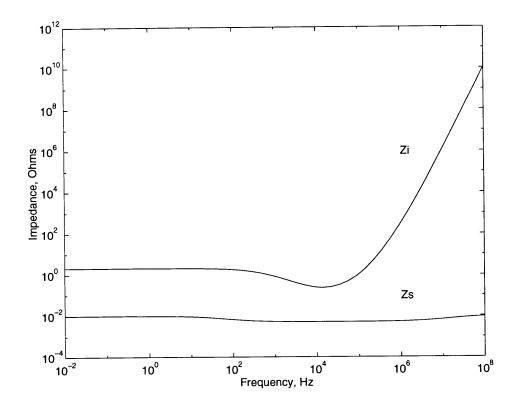

| 4-2 | Ouput impedance versus frequency plots generated by Matlab              | 57 |

| 4-3 | Model of the output filter used to find its transfer function           | 59 |

| 4-4  | Comparasion between output filter models with and without parasitics             |     |

|------|----------------------------------------------------------------------------------|-----|

|      | included                                                                         | 60  |

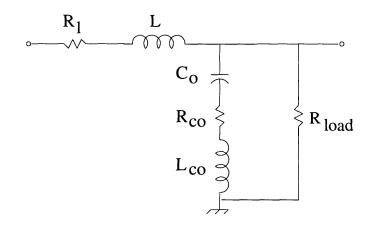

| 4-5  | Model of the output filter including the effective load resistance               | 63  |

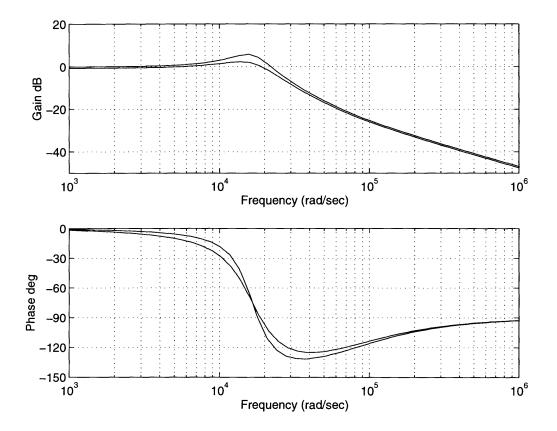

| 4-6  | Example of output filter characteristic change due to changing load              |     |

|      | current                                                                          | 65  |

| 4-7  | Model of the power distribution network used to find its transfer function.      | 66  |

| 4-8  | Using a) PSpice to verify the b) Matlab model of the power distribution          |     |

|      | network                                                                          | 69  |

| 4-9  | Comparison of output filter model with and without the power distri-             |     |

|      | bution network model                                                             | 70  |

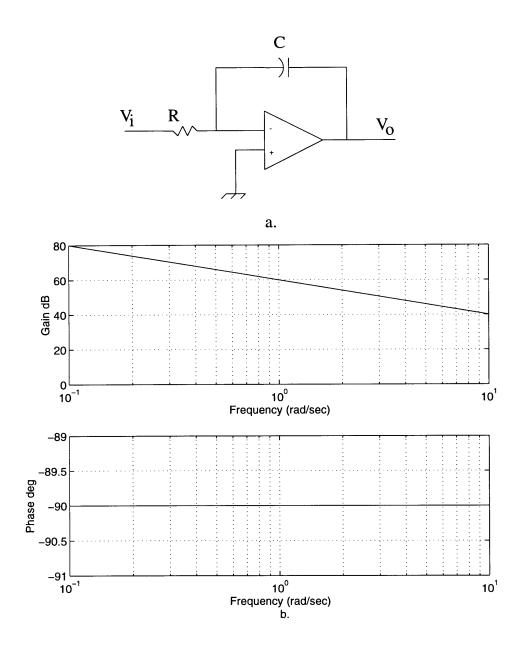

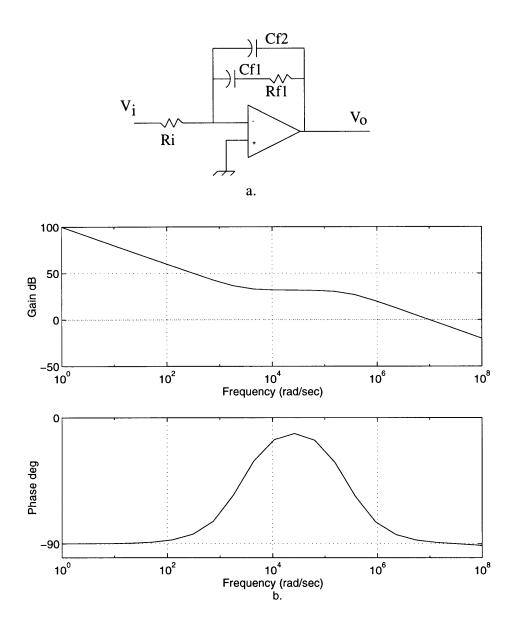

| 4-10 | a) Block diagram and b) typical Bode plot of a type I compensation               |     |

|      | scheme                                                                           | 73  |

| 4-11 | a) Block diagram and b) typical Bode plot of a type II compensation              |     |

|      | scheme                                                                           | 75  |

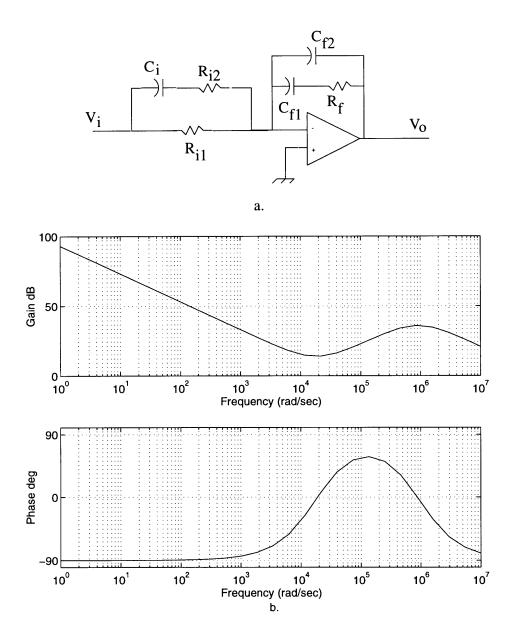

| 4-12 | a) Block diagram and b) typical Bode plot of a type III compensation             |     |

|      | scheme                                                                           | 77  |

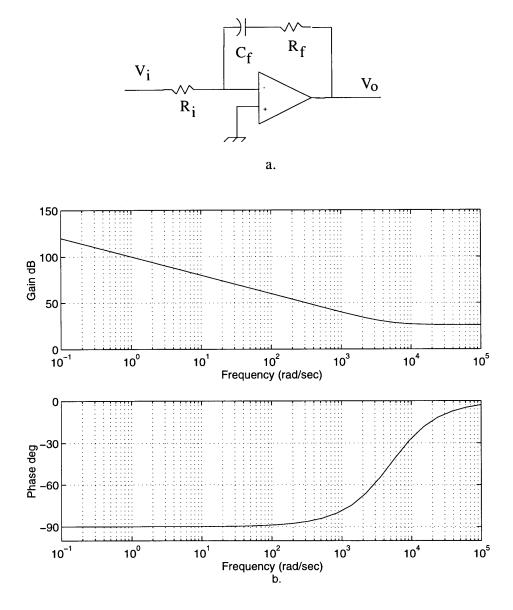

| 4-13 | a) Block diagram and b) typical Bode plot of a series RC compensation            |     |

|      | scheme                                                                           | 78  |

| 4-14 | Block diagram of a type I compensation scheme using an OTA. $\ldots$             | 80  |

| 4-15 | Block diagram of a type II compensation scheme using an OTA                      | 80  |

| 4-16 | Bode plot for type II compensation with $R_{out} = 100~{\rm k}\Omega$ and 10 M . | 81  |

| 4-17 | Series RC compensation using with an OTA                                         | 82  |

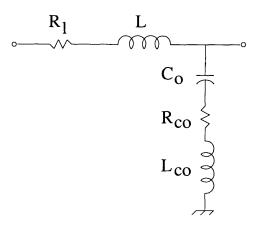

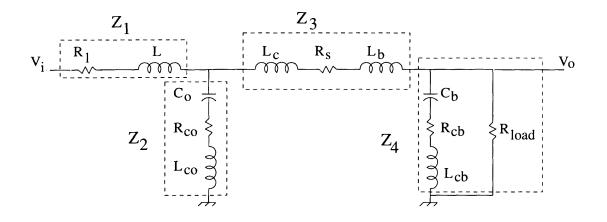

| 4-18 | Example of an input filter implementation                                        | 92  |

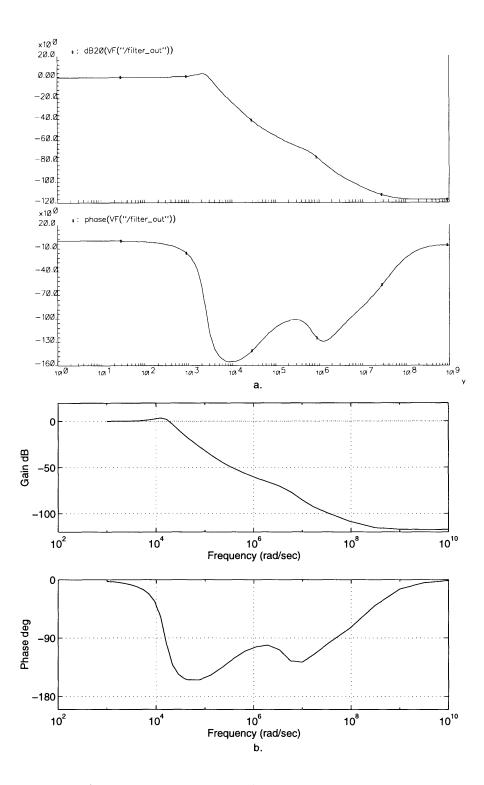

| 4-19 | Input impedance of the regulator and output impedance of the input               |     |

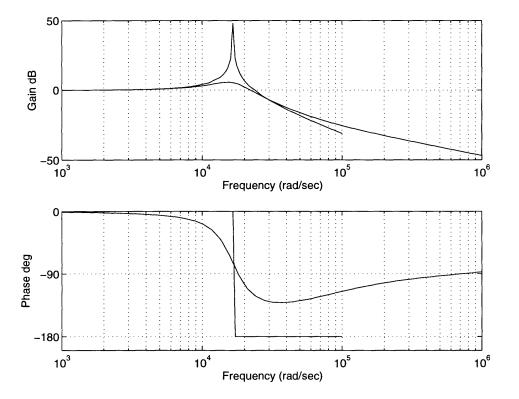

|      | filter                                                                           | 95  |

| 4-20 | Example of a Simulink model used in transient analysis.                          | 99  |

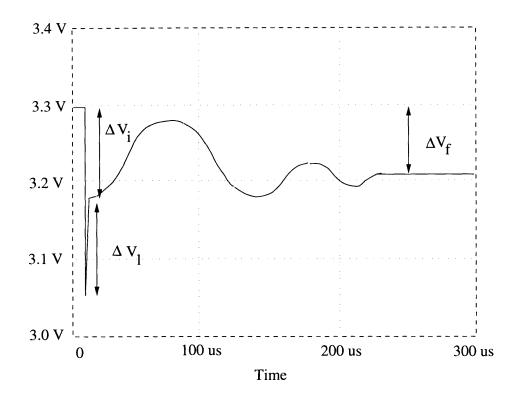

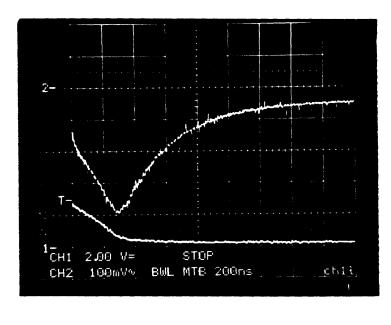

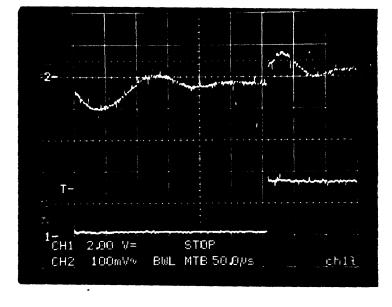

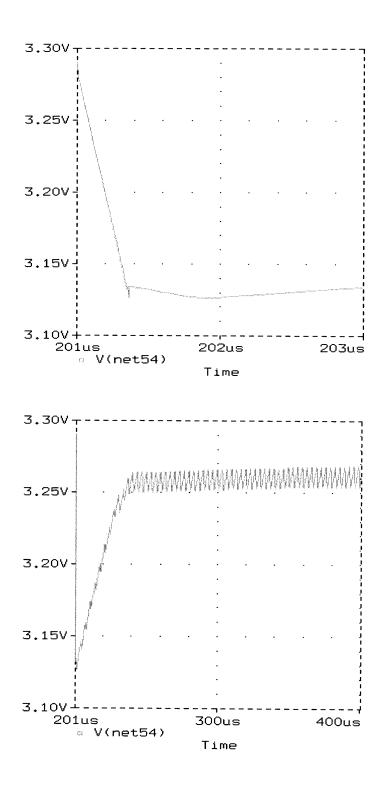

| 5-1  | Voltage transients caused by a load current step over a 500 ns time              |     |

|      | period                                                                           | 111 |

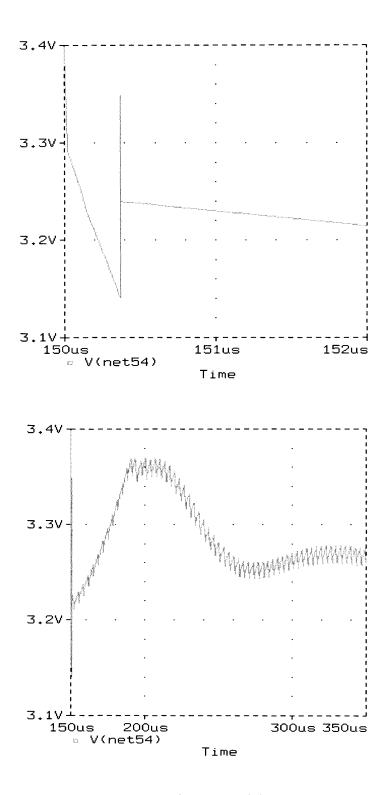

| 5-2  | Example voltage transient caused by a load current step over a 300 $\mu s$   |      |

|------|------------------------------------------------------------------------------|------|

|      | time period                                                                  | 112  |

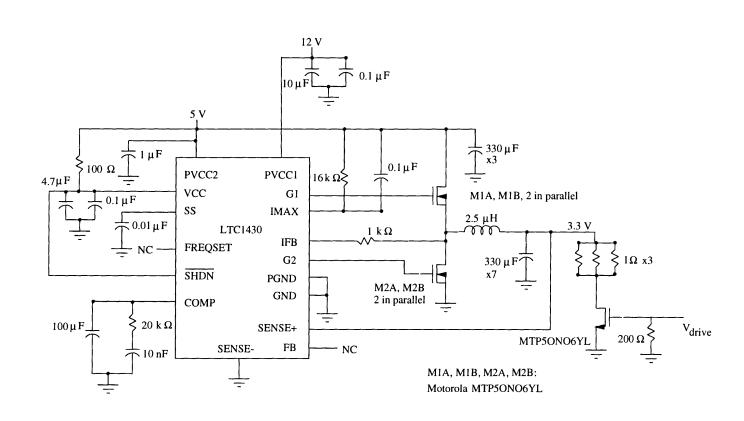

| 5-3  | LTC1430 breadboard using AVX capacitors                                      | 115  |

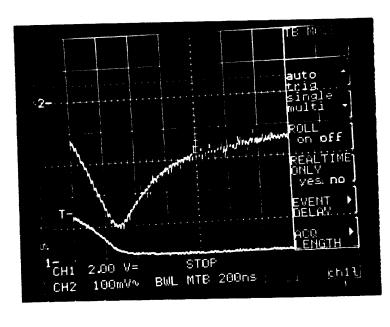

| 5-4  | Transient response of LTC1430 breadboard with AVX capacitors: a) $0$         |      |

|      | - 2 $\mu$ s. b) 0 - 200 $\mu$ s                                              | 116  |

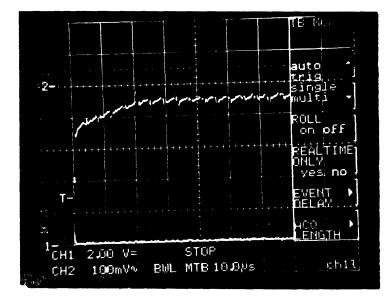

| 5-5  | Pspice schematic of the LTC1430 breadboard using AVX capacitors              | 118  |

| 5-6  | Pspice transient response of generated from Figure 5.5 for a) 0 - 2 $\mu s$  |      |

|      | and b) 0 - 200 $\mu$ s                                                       | 121  |

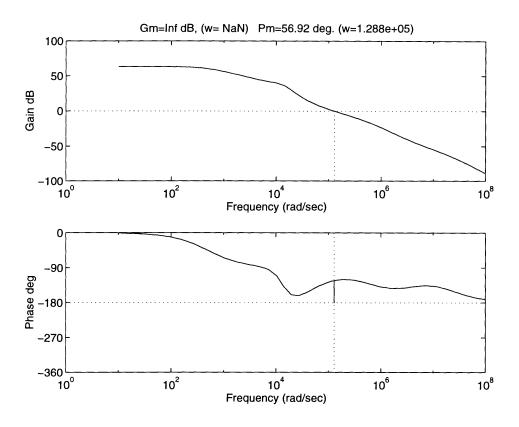

| 5-7  | Open loop response for breadboard with AVX capacitors generated              |      |

|      | with Matlab.                                                                 | 123  |

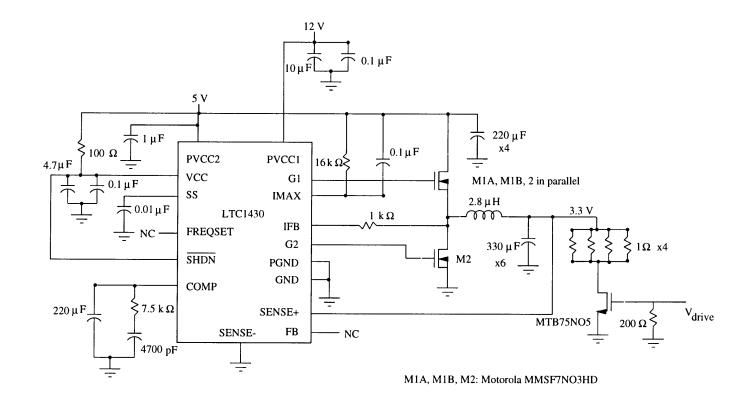

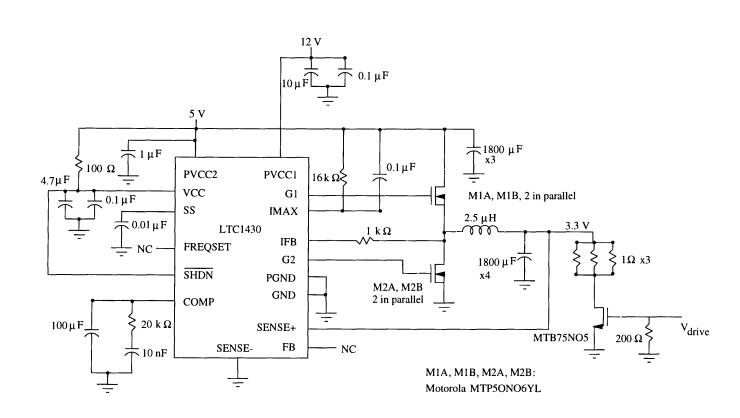

| 5-8  | LTC1430 breadboard using Sanyo Oscon capacitors                              | 125  |

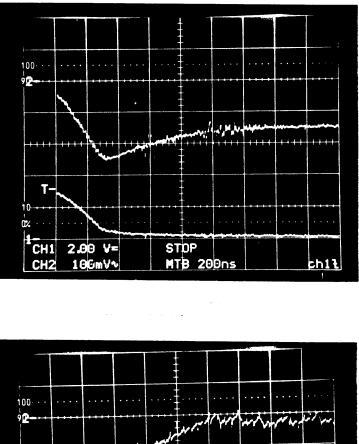

| 5-9  | Transient response of LTC1430 breadboard with Sanyo Oscon capaci-            |      |

|      | tors: a) 0 - 2 $\mu$ s. b) 0 - 500 $\mu$ s                                   | 126  |

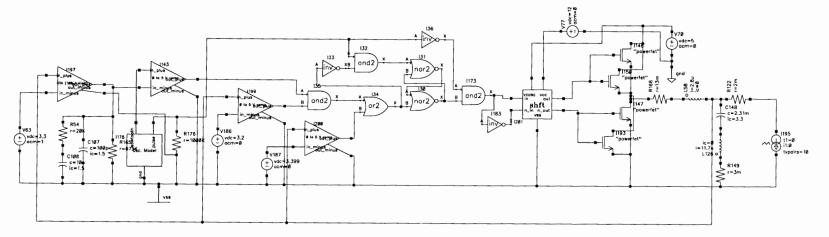

| 5-10 | Pspice schematic of the LTC1430 breadboard using Sanyo Oscon ca-             |      |

|      | pacitors                                                                     | 127  |

| 5-11 | Pspice transient response of generated from Figure 5.10 for a) 0 - 2 $\mu s$ |      |

|      | and b) 0 - 200 $\mu$ s                                                       | 128  |

| 5-12 | Open loop response for breadboard with Sanyo Oscon capacitors gen-           |      |

|      | erated with Matlab                                                           | 130  |

| 5-13 | LTC1430 breadboard using Nichicon capacitors.                                | 132  |

| 5-14 | Transient response of LTC1430 breadboard with Nichicon capacitors:           |      |

|      | a) 0 - 2 $\mu$ s. b) 0 - 200 $\mu$ s                                         | 133  |

| 5-15 | Pspice schematic of the LTC1430 breadboard using Nichicon capacitors         | .134 |

| 5-16 | Pspice transient response of generated from Figure 5.15 for a) 0 - 2 $\mu s$ |      |

|      | and b) 0 - 200 $\mu$ s                                                       | 135  |

| 5-17 | Open loop response for breadboard with Nichicon capacitors generated         |      |

|      | with Matlab.                                                                 | 137  |

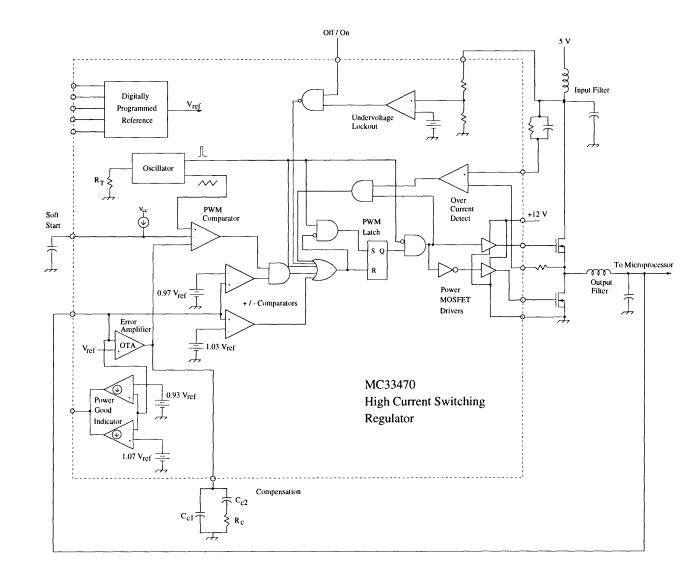

| 6-1  | Block diagram of the MC33470.                                                | 140  |

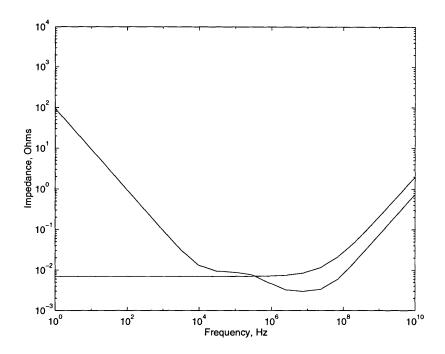

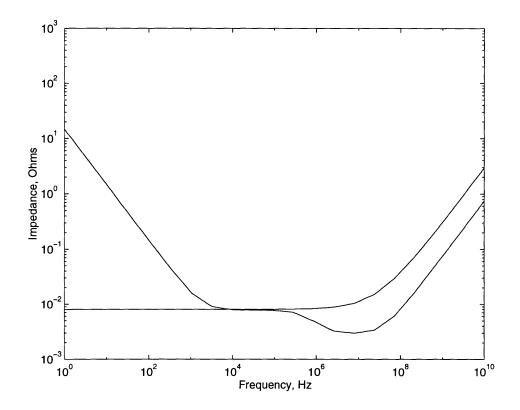

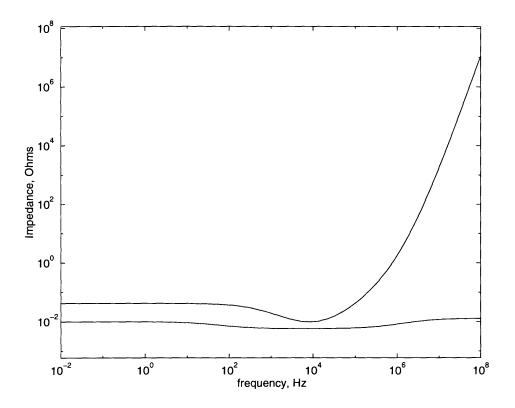

| 6-2  | Impedance curves for the regulator using Nichicon 1800 $\mu$ F capacitors.   | 149  |

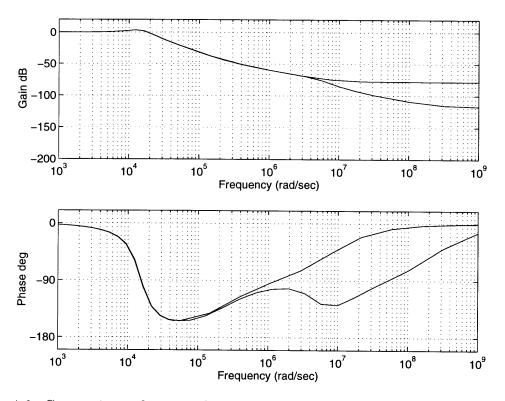

| 6-3  | Impedance curves to determine if the proposed input filter is acceptable            | e.152 |

|------|-------------------------------------------------------------------------------------|-------|

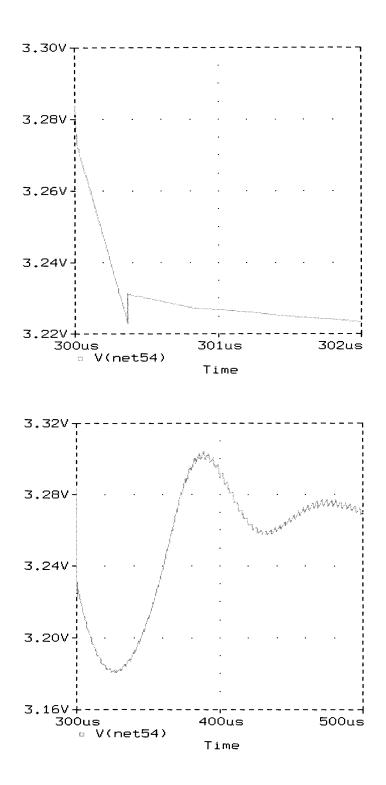

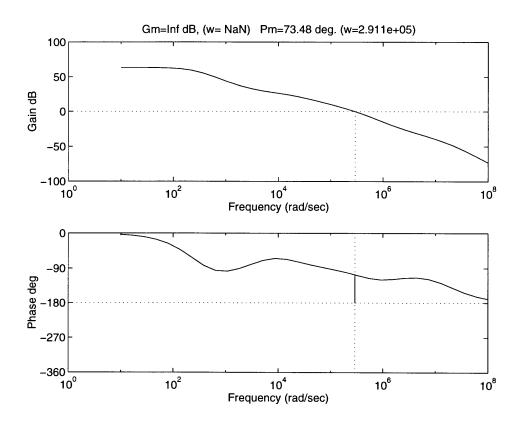

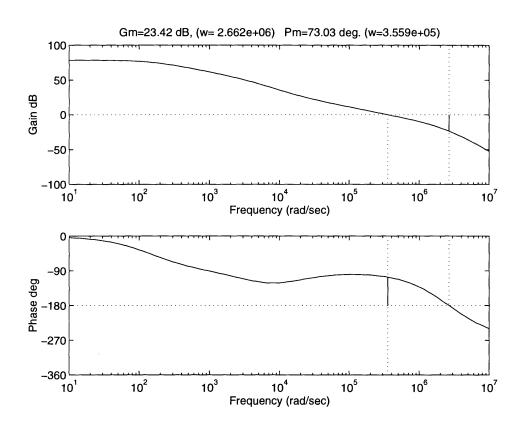

| 6-4  | Open loop system response generated by running the Matlab script                    | 153   |

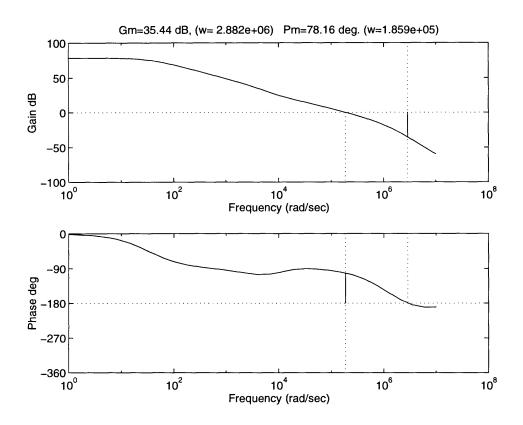

| 6-5  | Open loop system response with improved compensation values                         | 155   |

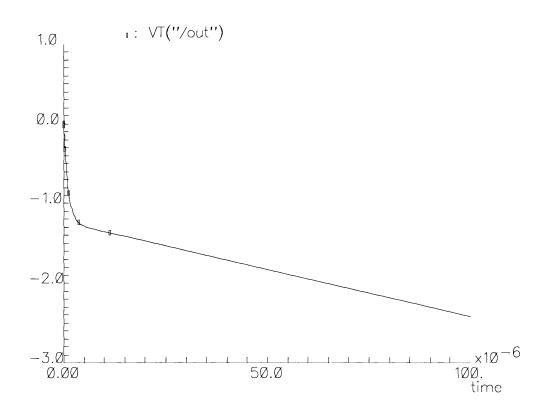

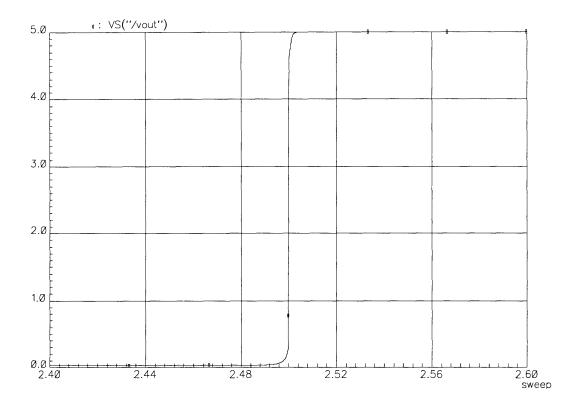

| 6-6  | Slew rate characteristic of the OTA output voltage with $C_{c1} = 100 \text{ pF}$ , |       |

|      | and $C_{c2} = 10 \text{ nF.}$                                                       | 156   |

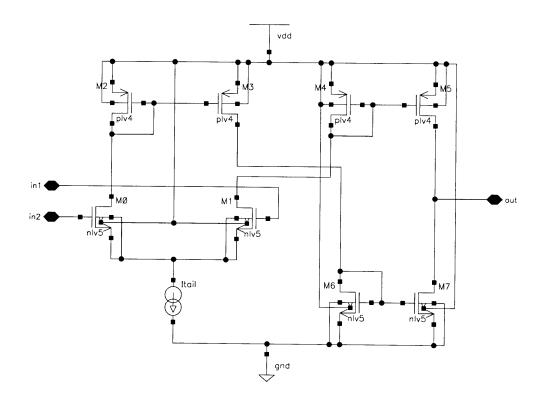

| 7-1  | Simplified architecture of the proposed OTA                                         | 158   |

| 7-2  | Common mode range limitations of a PMOS differential pair                           | 161   |

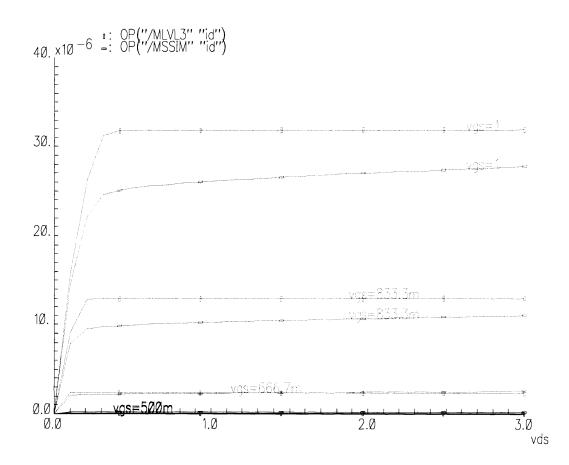

| 7-3  | Input characteristic comparison (NMOS, $V_{ds} = 100 \text{ mV}$ ): SSIM Level      |       |

|      | 6 versus Level 3                                                                    | 165   |

| 7-4  | Output characteristic comparison (NMOS, $L = 4$ UDR): SSIM Level                    |       |

|      | 6 versus Level 3.                                                                   | 166   |

| 7-5  | Output characteristic comparison (NMOS, $L = 12$ UDR): SSIM Level                   |       |

|      | 6 versus Level 3                                                                    | 167   |

| 7-6  | Simple PMOS mirror (L = 16 UDR)                                                     | 170   |

| 7-7  | Matching of simple mirror                                                           | 171   |

| 7-8  | Cascoded PMOS mirror with headroom extension (L = 8 UDR)                            | 171   |

| 7-9  | Matching of cascoded mirror.                                                        | 172   |

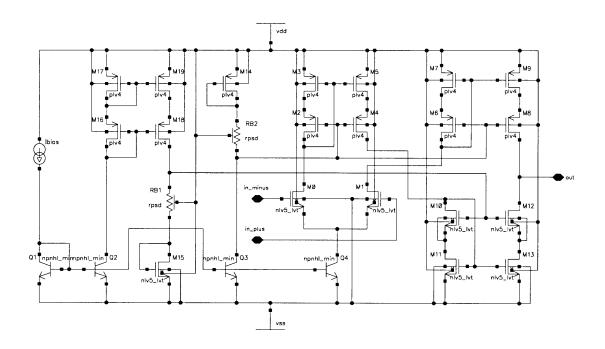

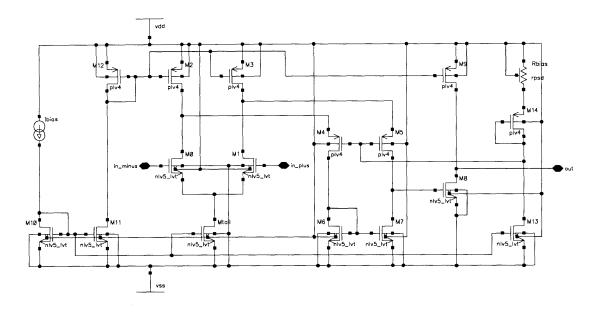

| 7-10 | Complete OTA schematic.                                                             | 173   |

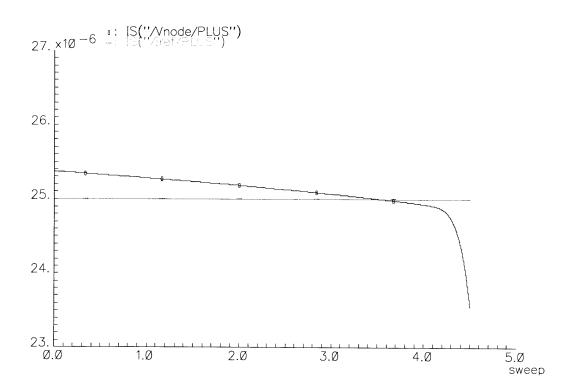

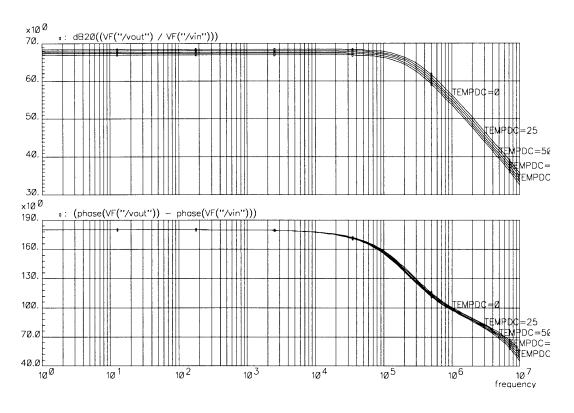

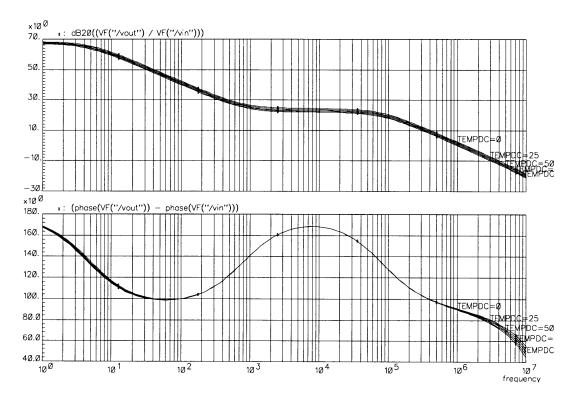

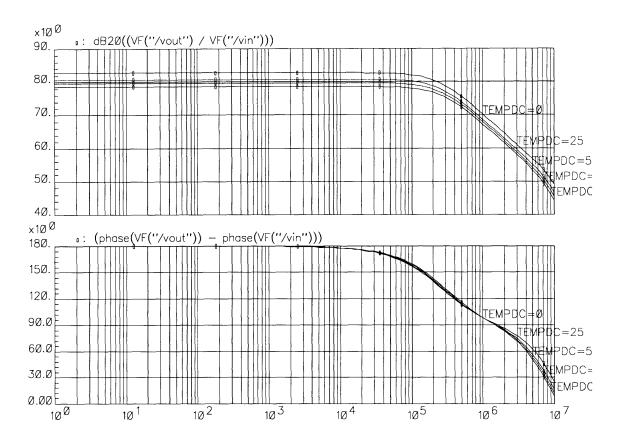

| 7-11 | Open Loop frequency response: uncompensated                                         | 178   |

| 7-12 | Open Loop frequency response: compensated.                                          | 178   |

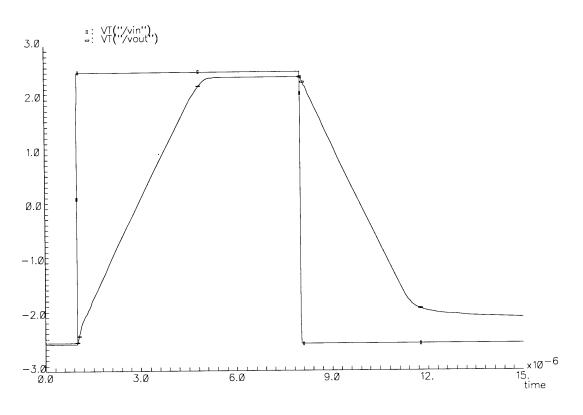

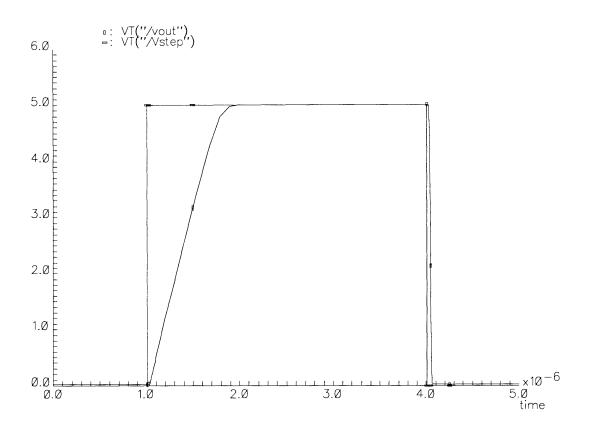

| 7-13 | Slew rate behavior.                                                                 | 179   |

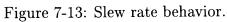

| 7-14 | Output signal swing capability.                                                     | 179   |

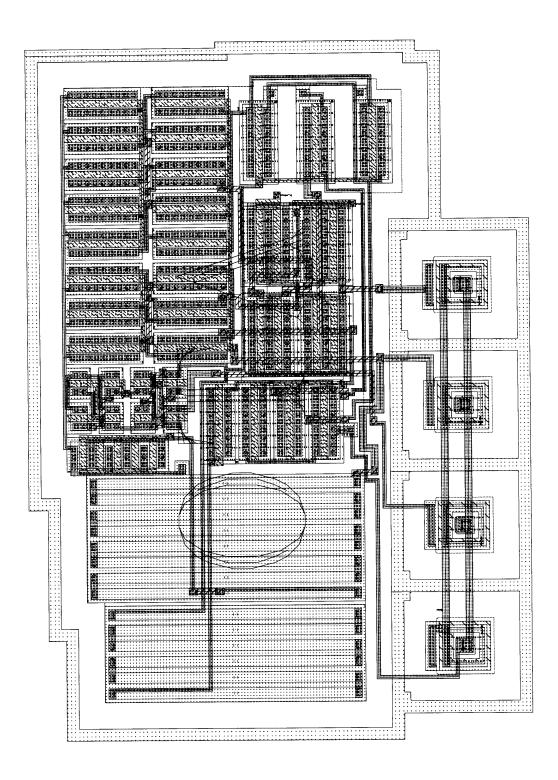

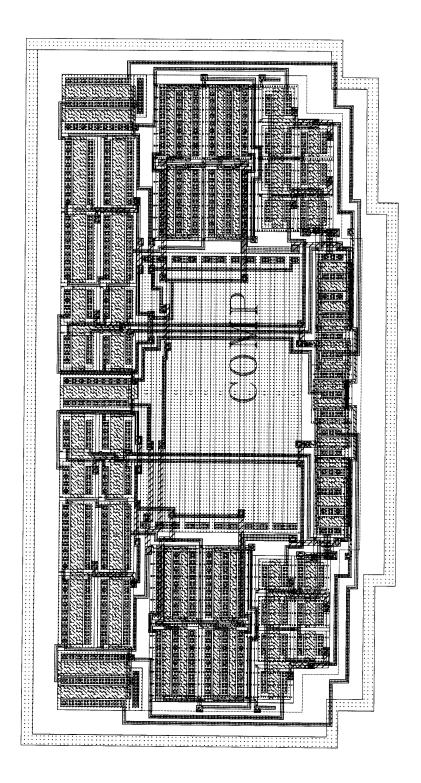

| 7-15 | Layout of the OTA: die size = $0.352 \times 0.253 \text{ mm}^2$                     | 180   |

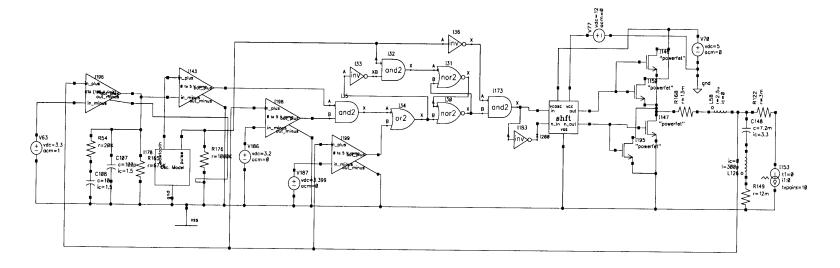

| 8-1  | Comparator schematic.                                                               | 184   |

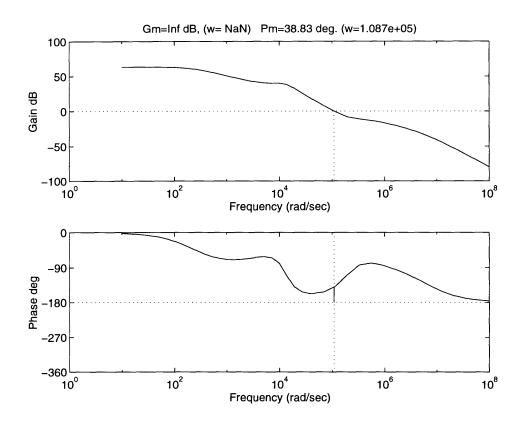

| 8-2  | Open loop frequency response.                                                       | 185   |

| 8-3  | Slew rate behavior: $C_{load} = 5$ pF                                               | 186   |

| 8-4  | Output signal swing capability.                                                     | 187   |

| 8-5  | Layout of dual comparators: die size = $0.382 \times 0.2 \text{ mm}^2 \dots \dots$  | 188   |

# List of Tables

| 2.1 | Summary of switching regulator control method by company   | 23  |

|-----|------------------------------------------------------------|-----|

| 7.1 | Performance requirements of the OTA needed for the MC33470 | 158 |

| 7.2 | Summary of OTA design.                                     | 181 |

| 8.1 | Summary of comparator design parameters.                   | 189 |

## Chapter 1

## Introduction

Microprocessors are moving towards lower operating voltages and higher current requirements [11, 34]. The lower operating voltages are necessary to limit the power dissipation caused by both the increase in clock speeds to greater than 200 MHz and the increasing number of transistors in each successive generation IC [13]. At the same time, the tolerance level for supply voltage variation is decreasing. This has created a market for high performance power supplies using voltage regulator ICs that can provide exceptional load regulation and stability while minimizing cost. Because each new generation of microprocessor requires a lower operating voltage, voltage regulators are being designed with an onboard digital-to-analog converter (DAC) to increase flexibility and enhance long term usability [13, 15]. The regulator IC also contains a pulse width modulator (PWM), logic, and an error amplifier, but the power FETs, compensation network, and output inductor and capacitor are all external. Because the external components are chosen by the user, a list of possible component values should be provided as part of the total regulator design solution. These values will give the user guidelines as to what choices would provide the best transient response and stability to meet the performance requirements of the particular application while staying within a certain price range. Simulation problems can occur in both creating these guidelines and designing the basic system regulator.

This thesis will focus on two aspects of the regulator design problem. First, a design methodology will be developed using Matlab that avoids many of the typical

simulation problems. Secondly, the design parameters extracted using this methodology will be used to design the error amplifier and comparators needed for the regulator. This thesis work will be conducted at the Amplifier and Power group of Motorola's Logic and Analog Technologies Group in Tempe, Arizona. A standard switching regulator targeting the microprocessor market will be designed. This buck regulator will use a 5 V input voltage to provide an output voltage between 1.8 and 3.5 V, programmed by an integrated 5-bit DAC in 50 mV increments below 2.1 V and 100 mV increments above 2.1 V. The regulator will maintain the output voltage to within  $\pm$  5% of its nominal value during a transition between no load and maximum load of 14 A. This  $\pm$ 5% window includes variations due to both the voltage reference and the load transient effects. The regulator IC has to be able to slew at 30 A/ $\mu$ s at the output pins which drive the external power devices.

Due to the large current demands, the regulator must be very efficient to reduce power dissipation. The regulator must have an efficiency rating of at least 80% at maximum rated load current and a minimum of 40% at low load conditions. To protect itself and the microprocessor it powers, the regulator must provide several protective functions. First, it needs to power down if the output voltage goes more than 15% higher than desired. Secondly, if the load current increases beyond a specified level, the regulator needs to provide a constant current that will not damage the IC. The goal of this design is to provide all of the above functionality and versatility and yet cost less than the currently favored discrete linear regulator.

#### **1.1 Background**

As microprocessor technologies and architectures become more advanced, the amount of supply voltage variation that they can tolerate becomes more restrictive. This results in a more complex voltage regulator design, including, but not limited to, the use of nested control loops, more complex error amplifiers, and extra logic in an attempt to improve transient performance. The additional features required can make simulating the voltage regulator system much more difficult. At the same time, increasing complexity makes top level system simulations more important since there can now be more opportunities for errors to occur.

Simplification of the top level schematic can help Spice<sup>1</sup> simulation convergence problems as well as dramatically improve run time performance. These simplifications include using macromodels to represent some subcircuits. For example, a comparator can be modeled as a differential input high gain block with the output limited between ground and the power supply.

For this thesis work, two simulation packages, PSpice and MCSpice, were available. MCSpice is Motorola's internal version of Spice. Neither package alone provides a complete design solution. Top level behavioral modeling and system simulation is adequately supported in PSpice, but is not fully implemented in the most recent version of MCSpice. For transistor level simulation, MCSpice uses an advanced, proprietary SSIM MOSFET model. However, PSpice still relies on an antiquated Level 3 MOS model. This model drastically overestimates both output impedance and moderate inversion transconductance. A more efficient and reliable design tool is necessary to increase system level understanding and to address transistor level design issues.

Along with the simulation problems mentioned above, the designer also must address the problem of deciding which control mode to use in the regulator design. Currently, three control modes are commonly used in the industry for switching regulators. However, these modes are not compatible with each other, utilizing different board layouts, compensation techniques and external components. As each successive microprocessor generation requires more stringent power supply controls, the use of voltage regulator modules will become prevalent and one control method will more than likely become the industry standard. Therefore, the competition needs to be surveyed so that the right control method can be chosen which will lead to the highest probability of project success.

<sup>&</sup>lt;sup>1</sup>Spice stands for Simulation Program with Integrated Circuit Emphasis

### **1.2** Design Strategy

This project has three main goals. First, the switching regulator IC must be less expensive than other regulator ICs currently available. This dictates how large the die area can be and what sort of package can be used. The limit on die size advocates the use of the simplest possible solution to reduce the area needed. However, the regulator also needs to be well designed so that it can provide reasonable performance with a variety of external components. This will allow the customer to choose the most cost effective solution for their application. Secondly, the regulator must be completely compatible with similar products already commercially available so that each regulator will have comparable performance for the same external components. Finally, the regulator design must be completed quickly so that it can reach the market in time to be designed into microprocessor power supplies.

The first objective is to understand the system level issues and use this understanding to develop a software algorithm to assist in the regulator design. This algorithm should be generic enough to allow it to be used with future regulator design programs. The first part of the software to assist with the switching regulator design is a Matlab program, or "script". This script will allow the system level design of a switching regulator to be interactive. It should also provide almost instantaneous feedback on system performance when any key parameter, either external or internal to the system, is modified. For example, the script should be able to calculate the necessary compensation values to meet the loop bandwidth specification and desired system phase margin. Also, it should be able to model the effect of the error amplifier characteristics on the loop performance and find the total cost of the external components used. The second part of the software used in the design process will be Simulink. Simulink allows transient responses to be simulated using Matlab transfer functions.

The Matlab algorithm developed will provide information on the effects of the subsystem parameters on the regulator performance. For example, changing the open loop gain of the error amplifier will affect the phase margin and transient response of the regulator and the designer needs to know if this change will be significant. Once these effects are understood, the error amplifier and comparator specifications can be determined. The second objective of this thesis is to determine these specifications and use them to design the comparators and error amplifier. Because the project goals include designing a regulator controller IC that is completely compatible with competitors' parts and completing the design as quickly as possible, developing a Matlab design method is necessary.

### **1.3** Thesis Organization

This thesis is organized as follows. Chapter 2 will present an overview of linear and switching regulators and the three most commonly used control methods for switching regulators. Chapter 3 will describe Matlab and the advantages of using it to understand a regulator system in the frequency domain. A simple frequency domain model of the regulator will also be derived in this chapter. Chapter 4 will develop a more detailed regulator model that accounts for parasitic component values and second order effects. A Matlab script will be developed that allows the regulator design process to be interactive and gives the designer an intuitive feel for how parameter variations affect the stability of the regulator.

In Chapter 5, the Matlab design methodology will be verified using PSpice and three breadboards built with similar regulator ICs. Chapter 6 will use the Matlab script to understand the design issues involved in Motorola's high current switching regulator, the MC33470, and extract subsystem parameters. Chapter 7 will describe the error amplifier design process using the parameters provided by the Matlab script. Chapter 8 will describe the requirements of the maximum and minimum comparators and their design process. Finally, the conclusion will be presented in Chapter 9.

## Chapter 2

## Voltage Regulators

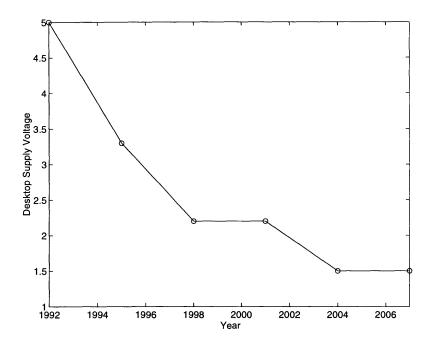

Voltage regulators can be used to provide microprocessors with a well-controlled power supply at the desired operating voltage from a pre-existing supply. Each successive microprocessor generation requires a lower operating voltage and higher supply current. The trend in power supply voltage is shown in Figure 2.1 [18]. The drop in the supply voltage has been driven by two requirements. First, each new microprocessor generation contains an ever-increasing number of transistors. The Pentium<sup>®</sup> Pro<sup>1</sup>, for example, has 5.5 million transistors. To allow such a large number of transistors to be integrated onto a single integrated circuit, minimum device spacing and size has decreased. Therefore, lower supply voltages are needed to keep the electric field from exceeding the dielectric breakdown of these high integration technologies. Second, decreasing the supply voltage decreases the power dissipation in the IC for a given drain current and clock frequency. The dynamic power dissipation is given as

$$P_{dyn} = \frac{1}{2} V_{dd}^2 C_l f_{clk}$$

(2.1)

As clock frequencies continue to increase, higher supply currents are required to account for an increase in parasitic, oxide and junction capacitances associated with these very high density integrated circuits. Therefore, even though the supply voltage has decreased over time, the power dissipation has increased dramatically due to

ı

<sup>&</sup>lt;sup>1</sup>Pentium is a registered trademark of Intel Corp.

Figure 2-1: Microprocessor supply voltage trend.

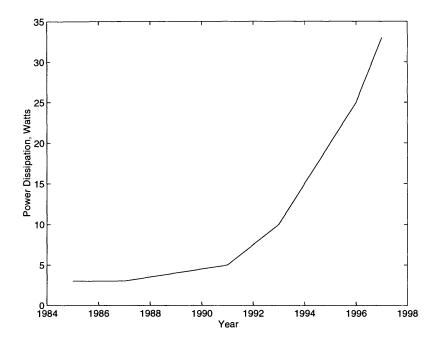

the increasing clock speeds, supply current, and number of transistors. The power dissipation trend is shown in Figure 2.2 [18].

Because microprocessors have moved to lower operating voltages and higher supply currents, the demands placed on regulator efficiency and regulation tolerance have become more restrictive. In the past, regulator efficiency was not as critical because the total power dissipation was low enough that it did not cause excessive heating in the power supply unit. However, regulator efficiency can no longer be ignored as modern microprocessors approach power dissipation levels in excess of 25 W. Also, as microprocessor supply voltages decrease, the relative tolerance of the regulated voltage does not. For example, a 3.3 V,  $\pm 5\%$  supply would require the regulator to maintain the nominal voltage within a 330 mV tolerance window. However, for a supply voltage of 1.8 V, this  $\pm 5\%$  tolerance requirement has reduced the same window to just 180 mV [9]. Therefore, as the supply voltage decreases, the voltage regulator needs to be able to control the output voltage more accurately to ensure that the microprocessor performs properly and provides long term reliability.

Figure 2-2: Microprocessor power dissipation trend.

### 2.1 Switching versus Linear Regulators

In the past, if power dissipation was secondary to cost and complexity, microprocessor power dissipation levels were low enough to allow discrete linear regulators to be used to convert from the 5 volt supply to the microprocessor supply voltage [26].

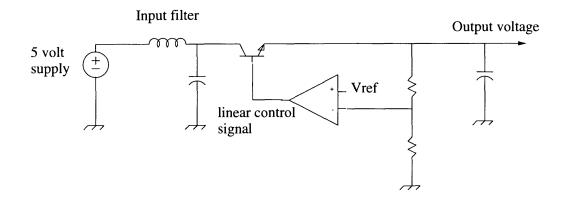

A simplified block diagram of a linear regulator is shown in Figure 2.3 [1]. The regulator uses an error amplifier to compare the output voltage to a reference voltage. The amplifier then generates a control signal proportional to the error between the desired and actual output voltages. This linear control signal drives a pass transistor at some point between saturation and cutoff so that the correct amount of supply current is supplied to the load to keep the output voltage at the correct value. An input filter can be used to prevent rapid changes in load current from affecting the 5 volt supply. The output filter is used to reduce the ripple in the output voltage due to large load current changes.

The principle advantage of using a linear regulator is that it can have fewer components than a switching regulator and can therefore be less expensive. However, for applications in which efficiency is a critical design goal, a linear regulator may not be

Figure 2-3: Block diagram of a linear regulator.

appropriate. The linear control signal generated by the error amplifier tends to keep the pass transistor biased such that a voltage drop always exist between its collector and emitter (or drain and source). This differential voltage can be as high as several volts. The power dissipation in the pass transistor, which represents as much as 95% of all the efficiency loss in a linear regulator, is given as the differential voltage times the load current. As microprocessor operating voltages decrease and supply current requirements increase, this power dissipation increases.

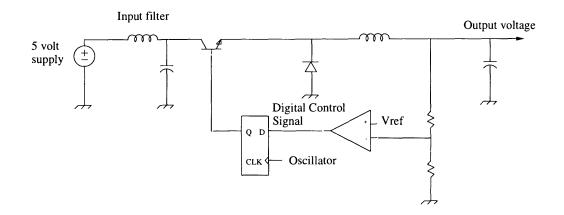

Switching regulators, in general, can achieve a much higher efficiency rating than a linear regulator. Historically, this has come at the expense of additional components and increased circuit complexity. However, modern, low cost process technologies have reduced both the cost of the regulator IC and the associated peripheral components, making it a very attractive alternative for power supply designers. A simplified block diagram of a switching regulator is shown in Figure 2.4. The output voltage is compared to a reference voltage and a digital signal is produced by a comparator to indicate whether the output voltage is above or below the reference voltage. If the output voltage is too low, the comparator enables the oscillator signal to drive the pass transistor. The oscillator signal is a square wave that cycles between ground and the input supply voltage. This ensures that the transistor is always either in saturation or cutoff. In saturation, the voltage from collector to emitter is very low, and therefore the power dissipation is low. In cutoff, the current through the transistor

Figure 2-4: Switching regulator block diagram.

is very low, and again the power dissipation in the transistor is low. If the output voltage is too high, the comparator disables the oscillator signal and the transistor is kept in the cutoff region. Because no current is being supplied to the load, the load current being removed from the output filter capacitor will reduce the output voltage. Once it falls below the reference voltage, the comparator will again enable the oscillator drive to the pass transistor.

Three common topologies for switching regulators are buck, boost, and flyback [8]. Each of these topologies is capable of operating in both discontinuous and continuous modes. The discontinuous mode refers to the situation in which the current though the inductor goes discontinuous during part of the clock cycle. This changes the location of the poles and zeros in the output filter and therefore changes the system stability. In the continuous mode, the current in the inductor is never zero. Whether the regulator operates in discontinuous mode or continuous mode is determined by the external components, specifically whether a FET or diode is used between the coil and ground. Since the external components, in general, are chosen by the customer, an understanding of these two situations is required.

| Vendor      | Part Number | Control Method              |

|-------------|-------------|-----------------------------|

| Unitrode    | UC3570      | Voltage                     |

| Unitrode    | UC3886      | Average Current             |

| Linfinity   | LMX1600A    | Proprietary (VRM Only)      |

| MicroLinear | ML4900      | Voltage                     |

| Raytheon    | RC5042      | Voltage/Current             |

| Cherry      | CS5150      | Proprietary (Dual Feedback) |

| Maxim       | MAX797      | Peak Current                |

| Elantec     | EL7560/61   | Peak Current                |

| Linear Tech | LTC1553     | Voltage                     |

Table 2.1: Summary of switching regulator control method by company

### 2.2 Switching Regulator Control Methods

Several different switching regulator control methods exist that can be utilized to provide the level of performance needed. However, due to differences in compensation techniques, packaging and external components, the control methods are not compatible. Therefore, to be competitive in the microprocessor power supply market, proper selection of the control method most widely used by other vendors and preferred by customers becomes critical. The information available on high current switching regulator ICs from throughout the industry was examined and three regulator control methods were found to dominate. These methods are voltage mode control, average current mode control, and peak current mode control. Information on eight switching regulator control ICs designed for high end microprocessors, including the Intel Pentium<sup>®</sup> Pro, was collected and a summary of part numbers and the control mode used is provided in Table 2.1 [4, 6, 10, 16, 17, 19, 20]. This benchmark survey helps to illustrate the diversity of switching regulator controller architectures currently available. Without a clear industry standard, each control mode must be examined in detail. The next sections outline the benefits, and disadvantages, of each control mode in an effort to determine the most appropriate choice for this design program.

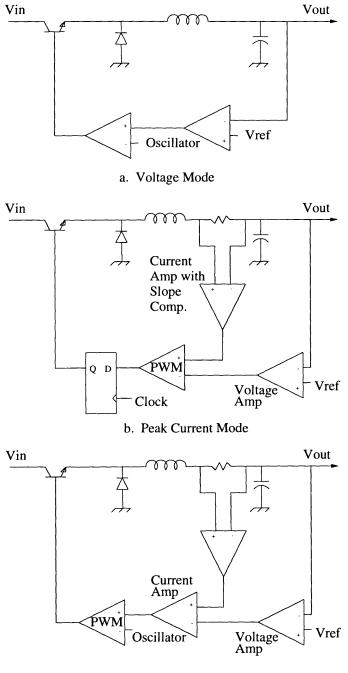

#### 2.2.1 Voltage Mode Control

Voltage mode control was the first method developed for use in switching regulators [7]. A simplified schematic of a voltage mode controlled regulator is shown in Figure 2.5a [18]. The duty cycle of the control waveform is generated by comparing the error signal to a sawtooth waveform using the pulse width modulator (PWM) comparator. The error amplifier signal is determined solely by comparing the output voltage to the reference voltage. Because only one control signal is used to determine the duty cycle of the waveform applied to the power FET devices, voltage mode control is the simplest control method. This simplicity means that few external components are required, and the internal IC design consumes less die area, allowing this control method to be, in general, the least expensive solution. In addition, the stability analysis and simulation modeling can be performed more easily than for control methods using multiple control loops.

However, with this simplicity comes some disadvantages [18]. For voltage mode control, the two poles due to the output filter need to be compensated directly. This is accomplished by adding positive phase, or a "phase boost" at the double pole location. This compensation technique causes the loop bandwidth of the regulator to be limited if an acceptable phase margin is to be maintained. Likewise, the phase margin of the system can be very sensitive to variations in the components used with this compensation method. Any variation of the filter capacitor ESR,  $R_{DSon}$  of the power FETs, ESR of the inductor, or compensation component values can change the system phase margin by several degrees, resulting in a change in the transient performance of the regulator. Also, instability can be caused by adding an input filter if the impedance of the filter is chosen incorrectly.

c. Average Current Mode

Figure 2-5: a) Voltage mode control. b) Peak current mode control. c) Average current mode control.

Unlike current mode control techniques, the current limiting functionality is not inherent in this control method and must be added separately. Finally, the gain due to the PWM is a function of the input voltage and oscillator peak to peak voltage. If the input voltage changes, the resulting loop bandwidth and gain will change, again effecting the transient performance of the regulator [17].

#### 2.2.2 Peak Current Mode Control

A block diagram of peak current mode control is shown in Figure 2.5b [18]. This control method generates a control signal by comparing the inductor current to the output voltage. The slope of the inductor current is given by Eq. 2.2.

$$\Delta I = \frac{v_{in} - v_{out}}{L} \tag{2.2}$$

This inductor current has a sawtooth shape similar to that generated by the oscillator used in voltage mode control. However, unlike the constant slope of the oscillator waveform, the slope of the current waveform varies as a function of input and output voltages. This results in a constant loop gain and bandwidth which is independent of the magnitude of the input voltage. Also, because both the current in the inductor and the output voltage are being sensed, rather than just the output voltage, the compensation needed to account for the output filter frequency response is simplified. This results in an additional feedback loop requirement, but serves to minimize the effect of the pole from the output filter inductor [17]. Under normal regions of operation only one pole affects the stability of the system and therefore the compensation is greatly simplified, allowing a higher bandwidth to be achieved.

Peak current mode control has an additional advantage. The current limiting function is automatically provided by the additional current feedback loop. Peak current mode control also has some disadvantages. First, the current loop has low gain, which is further reduced as the current through the output filter inductor becomes discontinuous. Also, this control mode is more die area intensive due to the need for a current amplifier and related circuitry. In addition, the stability analysis becomes more complicated than voltage mode control because two loops need to be considered, rather than just one. Finally, the system becomes unstable at duty cycles greater than 50% unless slope compensation techniques are employed [3, 7, 14, 24, 31]. This instability is well documented in the literature and can be avoided, but the necessary compensation increases circuit complexity and cost.

#### 2.2.3 Average Current Mode Control

An average current mode control loop is shown in Figure 2.5c [18]. This method is similar to the peak current control method, except that another amplifier has been added. This high gain amplifier, referred to as the current amplifier, generates an output signal based on the current through the inductor and the error signal from the error amplifier. This has the effect of comparing the desired output current to the actual output current which allows it to have the fastest response to changes in load current of the three control methods presented here. This control method is more complicated than the peak current control method due to the extra amplifier needed, but it has the advantage of not needing slope compensation for situations in which the duty cycle exceeds 50%. As with peak current control, average current control has been well documented [6, 7, 18, 24] and design strategies have been developed to maximize its performance. This control method was a proprietary technique developed by Unitrode and remains underutilized in the industry.

After consultation with potential customers and experts in the field, the decision was made to design this high current switching regulator using voltage mode control. This type of control would provide relative simplicity, market compatibility and a robust level of performance, all at minimal cost. This thesis will concentrate solely on the design and modeling of this type of buck regulator with the understanding that the principles and ideas presented here can be used with other architectures and control methods.

## Chapter 3

## **Regulator Top-Level Modeling**

Although voltage mode has been chosen as the control method of choice due in part to its relative simplicity, the regulator top-level modeling and simulation can still present problems using traditional approaches. The ability to perform top-level modeling is important for several reasons. First, large high integration systems, such as switching regulator, are generally designed using a top down approach with a number of designers each responsible for their own subsystem, or functional block. A top level simulation provides each designer not only with subsystem performance parameters which are not immediately obvious from the system specification, but also with information regarding interactions between each subsystem. For example, in a switching regulator, variations in the magnitude of the output filter capacitor can have a rather profound effect on the soft start circuit biasing value. Secondly, a top level simulation allows a designer to gain an understanding of how a variation in an external component can effect overall system performance. For example, variations in the equivalent series resistance (ESR) of the output filter capacitor can dramatically effect the phase margin of the system. Finally, these simulations can be used to quickly confirm top level system functionality.

### 3.1 Spice as a Control Systems Tool

IC designs are often done on a transistor level with Spice. However, the transient response of a large system such as a regulator can take many hours to simulate. Also, the combination of a mixed-mode circuit, and one or more feedback loops can cause the simulation to either not find a bias point or worse, find a bias point which is inaccurate. To further complicate matters, bias and supply currents in a high current switching regulator can differ by as much as six orders of magnitude. This can cause a myriad of problems in circuit simulators that are unaccustomed to simulating such a wide range of simulataneous operating conditions. For example, the load current may be as high as 10 or 12 amps, yet biasing circuits for the error amplifiers, comparators and other analog circuits are typically in the range of 10 to 20 microamps.

Efforts by the designer to assist or correct Spice simulation problems through adjustment of tolerance values can often lead to inconclusive results. The designer is left with no indication from the simulator if the algorithm in the simulation engine failed due to a mathematical difficulty, or whether the system itself is unstable. Also, Spice is not generally regarded as a controls system design tool. However, systems on a chip are increasingly oriented toward integration of complex control functions where knowledge of system stability and stability margin are critical to the success of the project.

One alternative approach using Spice is to create a simplified model minus the nonlinear components such as the logic circuitry, power FETs, comparators and pulse width modulator. With this model, state space averaging could be utilized to find the open loop frequency response of the system. However, even if these simulations converge and are valid, an excessive amount of time is required to complete the analysis due to the size of the system, making it a challenge for the designer to gain intuition regarding the system performance. Therefore, it becomes difficult for a recommendation to be made to the customer about the external components necessary to get the best regulator performance for the lowest price. In an effort to decrease simulation time, macromodeling or behavioral modeling can be used instead of transistor level simulation. In an effort to solve a majority of the problems presented here, an approach has been developed for this project using a commercially available software tool specifically engineered for control systems analysis.

## 3.2 Using Matlab and Simulink as Control Systems Tools

Matlab is a mathematical software package that is used for matrix manipulation and graphical representation of data. The Matlab control system toolbox and Simulink, a graphical user interface for manipulating system transfer functions and performing system transient simulations, are used along with the basic Matlab functions in this project.

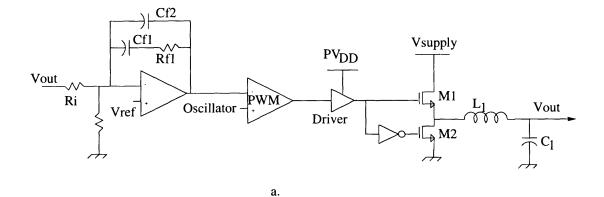

#### **3.2.1** Basic Regulator Modeling

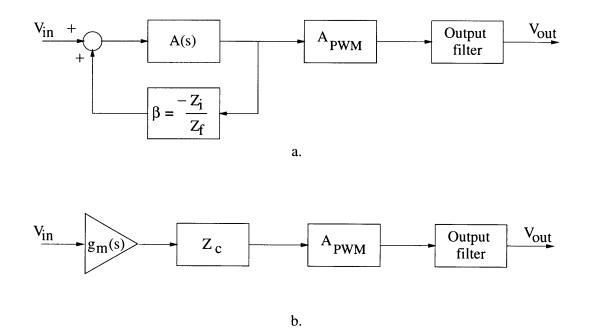

In designing a system such as a switching regulator, the most important advantage of using Matlab over transistor level modeling is found in the frequency response plots that can be generated. In order to find the frequency characteristics of a particular regulator, a model needs to be derived. This can be done by separating the regulator into smaller subsystems, or functional blocks, and finding the transfer function for each. Each block is then recombined into a top level schematic. Once the frequency characteristics are generated for each block in the switching regulator, these characteristics can then be used to determine the output filter components, the necessary compensation values, and the gain bandwidth product of the error amplifier to ensure stability and the desired phase margin is achieved. A basic switching regulator, using an operational amplifier as the error amplifier and employing voltage mode control, is shown in Figure 3.1a. Figure 3.1b shows the same regulator with an operational transconductance amplifier (OTA) used as the error amplifier.

To express the system in terms of a transfer function, the first step is to remove the nonlinear elements by using state space averaging [25, 27, 36]. For example,

Figure 3-1: a) Switching regulator using an operational amplifer as the error amplifier. b) Switching regulator using an operational transconductance amplifier as the error amplifier.

the power FET driver applies either a logic 1 (represented as  $PV_{DD}$  in Figure 3.1) or ground (logic level 0) to the gate of the top power FET (M1) which biases the device either completely off ( $V_{gs} < V_{th}$ ) or into conduction ( $V_{gs} > V_{th}$ ). Therefore, the node connecting the two power FETs (the source of M1 and the drain of M2) is either close to  $V_{supply}$  or to ground. The output filter, which includes the inductor  $L_1$  and capacitor  $C_1$ , is an impedance divider. The input voltage to this impedance divider can be expressed as ( $V_{supply}$ )D where D is the duty cycle generated by the PWM. This input voltage is the average voltage applied to the output filter. As the duty cycle increases, M1 is on for a longer period of time and the input filter sees a higher average voltage. This analysis applies to the regulator with either an OTA or operational amplifier because the functionality of the output filter, PWM, power FETs, and FET driver remains the same. For now, it will be assumed that both  $L_1$  and  $C_1$  are ideal and that the power FETs have zero on-resistance. The transfer function between the FET driver and the output voltage is shown in the following equation.

$$H(s) = \frac{Z_c}{Z_l + Z_c} \tag{3.1}$$

Letting  $Z_c = \frac{1}{Cs}$  and  $Z_l = Ls$ , the transfer function reduces to Eq. 3.2.

$$H(s) = \frac{1}{LCs^2 + 1}$$

(3.2)

In the following chapter, the model will be expanded to include effects of parasitic elements and non-ideal components. In Matlab, a transfer function can be described as a ratio of two vectors, one for the numerator and one for the denominator, with the coefficients of each vector arranged in descending order of the power of the complex variable s. For example, the previous transfer function could be written as num=[1] and den=[LC 0 1]. Therefore, this relationship allows the power FETs, FET driver, and PWM to be eliminated in order to express this system in terms of a single transfer function.

The output voltage of the error amplifier is proportional to the duty cycle of the regulator. However, this model has so far neglected the gain due to the PWM and

Figure 3-2: Operational amplifier shown with input and feedback impedance networks.

oscillator. The output of the error amplifier, regardless of which amplifier architecture is chosen, is compared to a sawtooth waveform to generate a digital signal whose pulse width determines the duty cycle. The smaller the range of the oscillator waveform, the less the output of the error amplifier is required to swing for a given input. This results in higher loop gain. The gain due to the PWM is therefore given as

$$A_{PWM} = \frac{V_{supply}}{\Delta V_{oscil}} \cdot e^{-j(2\pi f)T/2}$$

(3.3)

where the peak-to-peak value of the oscillator sawtooth voltage is given by  $V_{oscil}$  [18]. T is the period associated with the switching frequency. The term  $e^{-j(2\pi f)T/2}$  represents the phase delay due to the PWM. The transfer function derivations described thus far are valid for systems employing an operational amplifier or OTA (Figure 3.1a or 3.1b). However, frequency domain modeling of the error amplifier is strongly dependent on the type of amplifier architecture chosen.

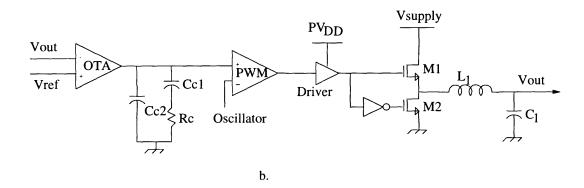

The operational amplifier and its compensation can be drawn as shown in Figure 3.2. The reference voltage for the regulator is attached to the positive terminal of the operational amplifier, which is small signal ground. Nodal analysis provides us with the following relationships:

$$\frac{V_{in} - V_x}{Z_{in}} + \frac{V_o - V_x}{Zf} = 0$$

(3.4)

$$V_o = AV_x \tag{3.5}$$

Figure 3-3: Block diagram of an operational amplifier and feedback factor  $\beta$ . where A is a function of frequency. Solving for  $V_o/V_{in}$  gives

$$\frac{V_o}{V_{in}} = \frac{-A}{\frac{Z_{in}}{Z_f}(A-1) - 1}$$

(3.6)

Assuming  $A - 1 \simeq A$ , Eq. 3.6 reduces to

$$\frac{V_o}{V_{in}} = \frac{A}{1+A\beta} \tag{3.7}$$

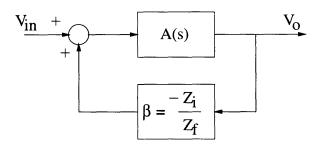

where  $\beta$  is  $-Z_{in}/Z_f$ . Therefore, the operational amplifier and compensation can be modeled as a block diagram as shown in Figure 3.3. Depending on the compensation used,  $Z_{in}$  may be a single resistor or some combination of resistors and capacitors. Likewise,  $Z_f$  may be a single capacitor or a combination of several passive components.

Once the transfer functions of  $Z_i$ ,  $Z_f$ , and A have been found, Matlab can automatically find the complete numerical transfer function of Figure 3.3 with the command feedback, which calculates the closed loop transfer function given the feedback factor and the plant transfer function [29]. An example of this modeling process can be illustrated with the error amplifier configuration shown in Figure 3.1a. The input impedance  $R_i$  is assumed to be 1 k $\Omega$ , the feedback resistor  $R_f$  is 5 k $\Omega$ , and the feedback capacitors are  $C_{f1} = 5600$  pF and  $C_{f2} = 4700$  pF. Solving symbolically,

$$Z_i = R_i \tag{3.8}$$

and

$$Z_f = \frac{1}{C_{f2}s \parallel (R_f + \frac{1}{C_{f1s}})}$$

(3.9)

A simplified expression for  $Z_f$  can be given as:

$$Z_f = \frac{R_f C_{f1} s + 1}{s(R_f C_{f1} C_{f2} s + C_{f1} + C_{f2})}$$

(3.10)

When vectors representing transfer functions are defined, the convention is used that a 1 at the end of the variable name indicates the numerator and a 2 represents the denominator variable. For example, h1 would be the numerator of H(s) and h2 would be the denominator of H(s). An example of how Matlab is used to manipulate these transfer functions into the form shown in Figure 3.3 is provided below:

```

% feedback component values

```

- >> rf=5000;

- >> cf1=5600e-12;

- >> cf2=4700e-12;

- >> ri=1000;

| 1.0e-07 | *    |     |   |

|---------|------|-----|---|

| 0.0000  | 0.10 | 030 | 0 |

The feedback factor shown in Figure 3.3 is given as  $Z_i/Z_f$ . This can be expressed using Matlab by using the **series** command. This command takes two transfer functions and calculates the equivalent transfer function for their series combination. Therefore,  $Z_i/Z_f$  can be expressed as the series combination of  $Z_i$  and  $1/Z_f$ , or in Matlab, as **series**(zi1, zi2, zf2, zf1). To account for the situation where the feedback factor contains a higher order numerator than denominator, which is not allowed in Matlab, a high frequency pole is added to the transfer function. From a practical standpoint, this high frequency pole can be ignored, but from a mathematical standpoint, it causes the order of the numerator to be the same as that of the denominator, satisfying the Matlab criteria. Adding this pole to the feedback factor is the same as adding a zero to  $Z_f$ . Instead of writing

$$Z_{f1} = R_f C_{f1} s + 1 \tag{3.11}$$

$Z_{f1}$  can be written as

$$Z_{f1} = (R_f C_{f1} s + 1)(\frac{1}{f_h} s + 1)$$

(3.12)

where  $f_h$  is the location of the high frequency zero in rads/sec. This technique is illustrated below:

% high frequency zero

>> fh=1e9;

% compute new feedback factor

```

>> [comp1,comp2]=series(zi1,zi2,zf2,zf1)

comp1 =

1.0e-04 *

0.0000    0.1030    0

comp2 =

0.0000    0.0000    1.0000

```

To complete the error amplifier model shown in Figure 3.3, the open loop transfer function of the operational amplifier needs to be defined. If the operational amplifier is assumed to have a very high low frequency gain and a single dominant pole, the gain as a function of frequency can be described as

$$A(s) = \frac{A}{\frac{1}{f_p}s + 1}$$

(3.13)

where  $f_p$  is the dominant pole location and A is the low frequency gain. For illustration, if we let A = 100,000 and  $f_p = 20$  rad/sec, the open loop characteristic of the operational amplifier can be modeled in Matlab as shown below:

```

% low frequency gain

>> a=1e5;

```

```

% dominant pole location (in rad/sec)

>> fp=20;

```

```

% A(s)

>> a1=[a]

a1 =

100000

>> a2=[1/fp 1]

a2 =

0.0500      1.0000

```

Now the model for the operational amplifier and its associated compensation network shown in Figure 3.3 is complete. The transfer function for the entire system can now be found using the **feedback** command. The first two variables passed to the feedback command are the numerator and denominator coefficients of the plant. The second set of variables is the numerator and denominator coefficients of the feedback factor. The fifth variable indicates whether positive or negative feedback should be used.

```

% plot transfer function

>> bode(op1,op2)

```

The bode command plots the frequency characteristics of the operational amplifier and compensation with the result shown in Figure 3.4. The compensation values were chosen for illustration purposes only. In this example, it can be seen that only 20° of positive phase was added. If this was insufficient for a particular design, a simple iteration of the subsystem component and parameter values could be performed to optimize the amount of phase addition and its location. The high frequency zero added to  $Z_f$  can also be seen in Figure 3.4. If this zero occurred at a low enough frequency that it impacted the accuracy of the model, its effect can easily be minimized by redefining the variable  $f_h$  to a larger value and having Matlab recalculate the transfer function coefficients.

The transfer function of an operational transconductance amplifier (OTA) can be

Figure 3-4: Frequency characteristics of an operational amplifier and compensation.

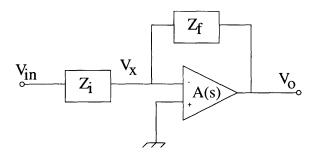

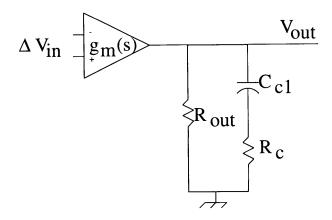

derived in a manner similar to that just described for an operational amplifier. The principle difference between the two derivations stems from the differences in compensation methods used. The compensation for the operational amplifier results in a closed feedback loop around the amplifier and contained within the outer regulator loop. The OTA compensation, however, is referenced to ground. Therefore, the only feedback path around the OTA is the regulator loop itself.

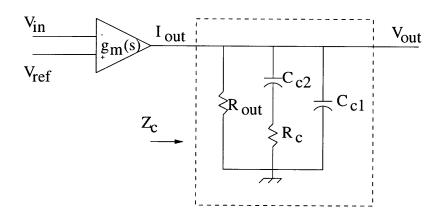

An OTA provides an output current proportional to the input differential voltage. This relationship is given by

$$I_{out} = g_m \Delta v_{in} \tag{3.14}$$

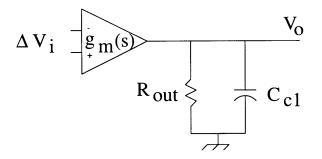

where the transconductance of the amplifier,  $g_m$ , is a function of frequency. The output current is converted to a voltage that is applied to one input of the PWM comparator. The conversion is performed by the compensation components and the output impedance of the OTA. Because the compensation network contains capacitive elements between the output of the OTA and ground, the output impedance of the

Figure 3-5: Block diagram of an error amplifier and compensation that includes the effect of the output impedance of the OTA.

OTA determines the DC gain. This gain is given by

$$A_v = g_m R_{out} \tag{3.15}$$

where  $R_{out}$  is the output impedance of the OTA. The output voltage of the OTA and compensation network, modeled as shown in Figure 3.5, is given by

$$V_{out} = I_{out} Z_c \tag{3.16}$$

where  $Z_c$  is the impedance of the compensation network in parallel with the output impedance of the OTA. Substituting Eq. 3.14 into Eq. 3.16, the transfer function of the OTA and compensation network is found to be

$$\frac{V_{out}}{V_{in}} = g_m Z_c \tag{3.17}$$

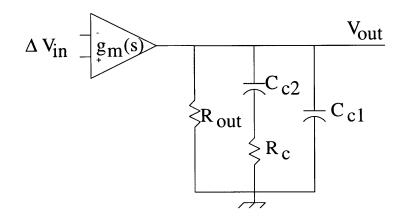

An example of modeling the OTA with Matlab can be illustrated using the compensation network shown in Figure 3.1b. The compensation values are assumed to be as follows:  $C_{c1} = 100 \text{ pF}$ ,  $C_{c2} = 10 \text{ nF}$ , and  $R_c = 20 \text{ k}\Omega$ . Also, the output impedance of the OTA is assumed to be 1 M $\Omega$  with a transconductance of 1 m $\Omega^{-1}$  at low frequencies. The OTA is assumed to have a single dominant pole at a frequency of  $w_p = 10^6$  rad/sec. Therefore, the transconductance of the OTA can be modeled as

$$G_m = \frac{g_m}{\frac{1}{w_p}s + 1} \tag{3.18}$$

The compensation network and output impedance can be modeled by

$$Z_c = R_{out} \parallel (R_c + \frac{1}{C_{c2}s}) \parallel \frac{1}{C_{c1}s}$$

(3.19)

Manipulation and simplification of Eq. 3.19 provides the following relationship for the current to voltage conversion network:

$$Z_{c} = \frac{sC_{c2}R_{c}R_{out} + R_{out}}{s^{2}C_{c1}C_{c2}R_{out}R_{c} + s(R_{out}C_{c2} + R_{out}C_{c1} + C_{c2}R_{c}) + 1}$$

(3.20)

Matlab can be used to find the numerical representations of these transfer functions as shown.

- % compensation values

>> cc1=100e-12;

- >> cc2=10e-9;

- >> rc=20e3;

```

% output impedance of OTA

>> rout=1e6;

```

% transconductance

>> gm=1e-3;

% dominant pole location

>> wp=1e6;

```

% compute gm(s)

>> gm1=[gm]

```

```

gm1 =

1.0000e-03

>> gm2=[1/wp 1]

gm2 =

0.0000 1.0000

```

% current to voltage conversion network

>> zc1=[cc2\*rc\*rout rout]

zc1 =

200 1000000

>> zc2=[cc1\*cc2\*rout\*rc rout\*cc2+rout\*cc1+cc2\*rc 1]

zc2 =

0.0000 0.0103 1.0000

```

% plot transfer function

>> bode(ota1,ota2)

```

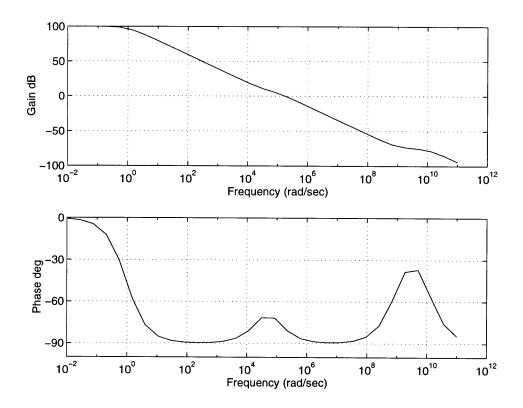

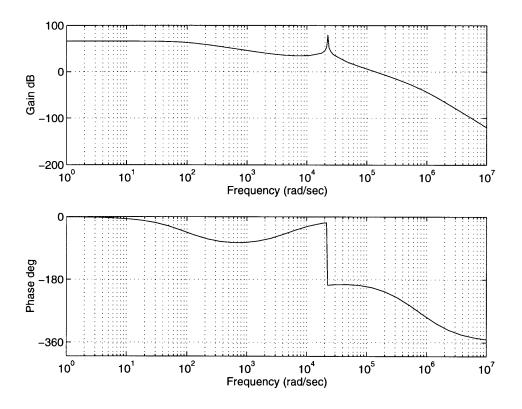

An example of the open loop transfer function of the OTA with compensation network is shown in Figure 3.6.

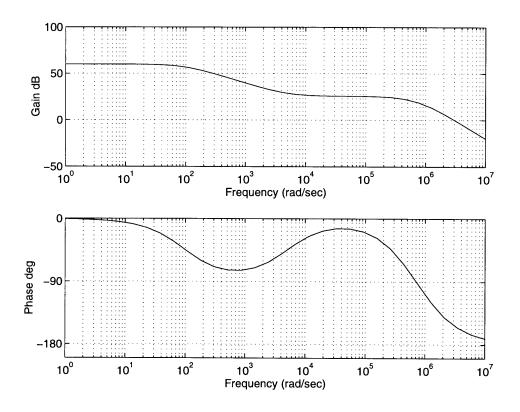

After each section of the regulator has been modeled in the frequency domain, the subsystems can be combined as shown in Figure 3.7 to find the complete open loop transfer function of the system. Figure 3.7a shows the model of a regulator using an operational amplifier as the error amplifier while Figure 3.7b shows an OTA used as

Figure 3-6: Open loop transfer function of an OTA and compensation.

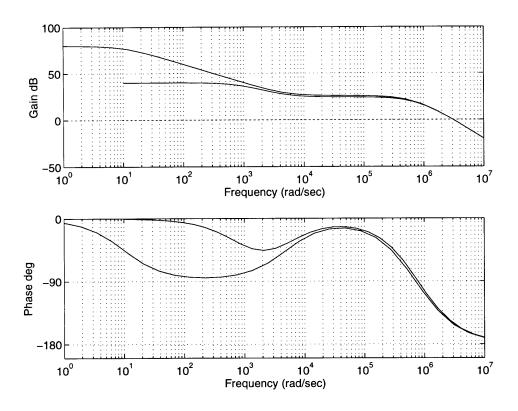

the error amplifier. After the transfer functions for each block have been determined, the complete transfer function can be found using the Matlab series command. Assuming an effective PWM comparator gain of 2, an output filter capacitor of 1000  $\mu$ F, an output filter inductor of 2  $\mu$ H, and that the OTA described above is used, the complete system function can be found as shown below.

Figure 3-7: Block diagram used in Matlab of the regulator using an a) operational amplifier and b) an OTA.

f2 =0.0000 0 1.0000 >> bode(f1,f2) % pwm gain >> pwm=2; >> f1=f1\*pwm f1 =2  $\ensuremath{\texttt{\%}}$  compute complete system transfer function >> [r1,r2]=series(ota1,ota2,f1,f2) r1 = 1.0e+03 \* 0 0 0 0 0.0004 2.0000

Figure 3-8: Complete system transfer function for the example in Section 3.2.1.

r2 =

| 0.0000 | 0.0000 | 0.0000 | 0.0000 | 0.0103 | 1.0000 |

|--------|--------|--------|--------|--------|--------|

|--------|--------|--------|--------|--------|--------|

### % plot system transfer function

### >> bode(r1,r2)

The complete system transfer function for this example is shown in Figure 3.8. At the frequency at which the magnitude crosses 0 dB, or a gain of 1, the phase is already more negative than  $-180^{\circ}$  which indicates the system is unstable when in a unity gain feedback configuration. At this point, the designer would be faced with another iteration to determine which parameter, or parameters, caused the system to be unstable. This is neither efficient nor elegant. The design methodology presented thus far needs to be improved to allow greater flexibility in the iterative process.

### 3.2.2 Matlab Scripts

We now have a basic tool for determining the effects of changing key design parameters on the stability of the regulator system. However, redefining these parameters to iterate towards an optimum design solution is both cumbersome and vulnerable to errors. In addition, the assumption that each designer be familiar with Matlab does not exploit the full advantage of the tool. Both of these issues can be avoided by developing a Matlab program, or "script" to assist in the regulator design process. The script will implement an algorithm that allows the system level design to be interactive, requiring only that the designer enter key design parameters when prompted. No detailed understanding of the inner workings of the script, or knowledge of the Matlab tool is required. The algorithm should be fairly generic to allow its use with future switching regulator design programs. The script will also provide almost instantaneous feedback on system performance when any key design variable, whether it be internal to the IC or associated with an external component, is modified. Also, Matlab can be used to automatically calculate compensation values to ensure system stability. A simple example of a Matlab script is shown below.

```

% scriptexample.m

```

```

% This script plots the transfer function of an LC filter.

l=input([blanks(5) 'Enter inductor value (in uH): --> ']);

l=l*1e-6;

c=input([blanks(5) 'Enter capacitor value (in uF): --> ']);

c=c*1e-6;

f1=[1]

f2=[1*c 0 1]

bode(f1,f2)

title('LC filter')

```

This script prompts the user for capacitor and inductor values and then calculates and plots the transfer function of an LC filter. Matlab also supports control flow statements, such as for and while loops, as well as if statements, allowing the iterative design process to be automatic and self contained. As the model for the switching regulator becomes more involved, including the addition of passive device parasitics and other non-idealities, this design methodology will become more of a necessity than a convenience.

### 3.3 Expanding the Regulator Model in Matlab

The regulator model developed thus far is very simplistic, accounting only for first order effects of the output filter, error amplifier and compensation, and PWM gain. To create a more viable representation of the regulator, several important design variables need to be incorporated into the regulator model, including output filter and board parasitics, power FET transfer characteristics, error amplifier limitations and effects due to input filter components.

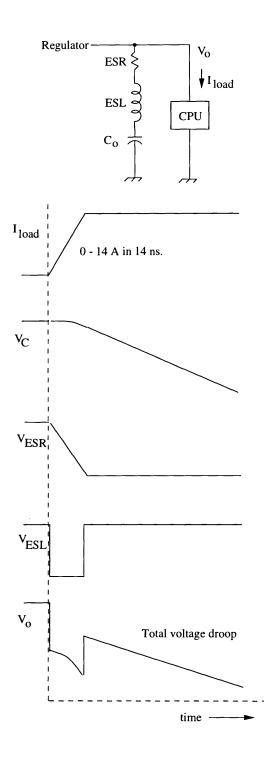

Possibly the most important effect on system stability is that contributed by the parasitics of the output filter components. The two primary modeling concerns are the equivalent series resistance (ESR) and equivalent series inductance (ESL) of the output filter capacitor. These non-idealities are especially important for two reasons. First, since the output filter can see load current changes of more than 10 amps in a very short period of time, the magnitude of ESR and ESL can prove to be the limiting factor in how well the regulator IC can maintain transient load regulation [12]. Secondly, the ESR and ESL each contribute a zero to the output filter transfer function which can dramatically change the phase margin of the system. The output filter inductor also has an ESR which can effect the system phase margin and needs to be modeled.

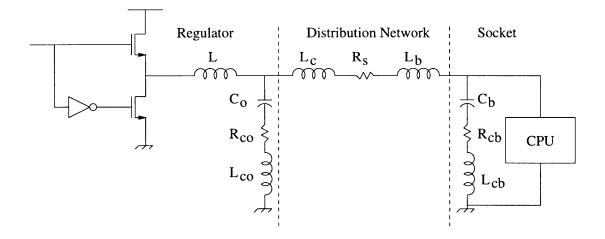

The interconnect between the voltage regulator output filter and the microprocessor itself contains parasitic resistance and inductance that needs to be included in the system model. In addition, the microprocessor socket contains a number of bypass capacitors to ensure that high frequency, high load current changes do not result in a loss of load regulation. These components are part of the power distribution network and are included in the higher order model. The simple model represents the power FETs as ideal switches with zero onresistance. The magnitude of the channel impedance, or  $R_{DSon}$ , of the actual power FET is on the same order as the ESR of the output filter capacitor and therefore must be included. Also, the error amplifier, whether it be an operational amplifier of OTA, was assumed to have a single pole response. However, higher frequency, non-dominant poles do exist and may have an effect on system stability. In addition, if an OTA is used, the model should account for variations in output impedance with frequency.

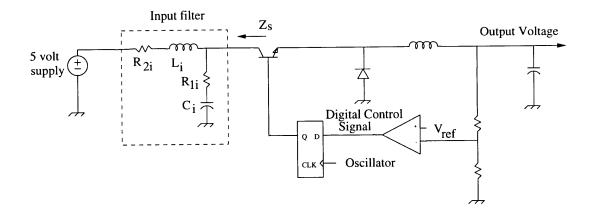

Finally, some applications require that the input supply voltage be isolated from the regulator system using an LC filter. The filter components and associated parasitics need to be included in the complete model due to the effect it may have on the system transfer function.

Developing an accurate and concise model for a switching regulator power supply is a laborious process. However, the benefits of such a model, from rapid determination of system phase margin to accurate prediction of load regulation capability, is invaluable to the success of any regulator design program.

As the model begins to evolve using state space averaging techniques and validated assumptions, its complexity warrants the use of the Matlab design methodology. Used in conjunction with Simulink and the available Spice simulation engines, complete system level understanding and circuit level performance requirements will avail itself to members of the design team. Chapter 4 begins a more detailed analysis of this design methodology and outlines more specifically the additional factors necessary to complete the higher order model.

## Chapter 4

# Developing a Regulator Design Methodology using a Matlab Script

Matlab has been shown to be a very useful tool that can be used to quickly determine the frequency response and stability information of a regulator system for various combinations of design parameters. Also, the ability to write a script in Matlab allows the interface to be more intuitive, simple to use, and reduces errors that could occur if large numbers of commands had to be entered by hand. A script allows the system level design of a switching regulator to be interactive. It can also provide almost instantaneous feedback on system performance when any key parameter, either external or internal to the system, is modified. To use Matlab most effectively, a more detailed model of the regulator needs to be derived. This model can be used to develop a methodology to reduce regulator design time and increase the likelihood of initial project success.

### 4.1 **Power Distribution Network**

A modern high performance microprocessor, like the Intel Pentium B Pro, can have a change in load current from a minimum of 0 amps to a maximum of 14 amps at a rate