## Commercialization of Germanium Based Nanocrystal Memory

by

## Kian Chiew Seow

B.Eng., (Electrical Engineering) National University of Singapore, 2006

## SUBMITTED TO THE DEPARTMENT OF MATERIALS SCIENCE AND ENGINEERING IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

## MASTER OF ENGINEERING IN MATERIALS SCIENCE AND ENGINEERING

## AT THE

## MASSACHUSETTS INSTITUTE OF TECHNOLOGY

#### SEPTEMBER 2007

## © 2007 Massachusetts Institute of Technology All rights reserved

| Signature of       |                                                                  |

|--------------------|------------------------------------------------------------------|

|                    | · · ·                                                            |

| Autnor:            | · · · · · · · · · · · · · · · · · · ·                            |

|                    | Department of Materials Science and Engineering                  |

|                    | July 23, 2007                                                    |

|                    | July 25, 2007                                                    |

|                    |                                                                  |

| Certified          |                                                                  |

| by:                |                                                                  |

| •                  | Carl V. Thompson                                                 |

|                    | •                                                                |

|                    | Stavros Salapatas Professor of Materials Science and Engineering |

|                    | Thesis Supervisor                                                |

|                    |                                                                  |

| Accepted           |                                                                  |

|                    |                                                                  |

| by:                |                                                                  |

|                    | Samuel M. Allen                                                  |

|                    | POSCO Professor of Physical Metallurgy                           |

|                    | Chair, Departmental Committee on Graduate Students               |

|                    | Chan, Departmental Committee on Oracuate Students                |

| CHUSETTS INSTITUTE |                                                                  |

|                    |                                                                  |

|                    | ARCHIVES                                                         |

| SEP 2 4 2007       | AKUTIT                                                           |

|                    |                                                                  |

|                    |                                                                  |

| IBRARIES           |                                                                  |

## Commercialization of Germanium Based Nanocrystal Memory

By

#### Kian Chiew Seow

## Submitted to the Department of Material Science and Engineering On August 1, 2007 in Partial Fulfillment of the Requirements of the Degree of Master of Engineering in Material Science and Engineering

#### ABSTRACT

This thesis explores the commercialization of germanium-based nanocrystal memories. Demand for smaller and faster electronics and embedded systems supports the development of high-density, low-power non-volatile electronic memory devices. Flash memory cells designed for ten years of data retention require the use of a thick tunneling oxide. This compromises writing and reading speed as well as endurance. A smaller device size can be achieved and speed and can be improved by decreasing the oxide thickness. However, significant charge leakage will occur if the oxide is too thin, which will reduce the data retention time dramatically. This imposes a limit to the amount by which the oxide thickness can be decreased in conventional devices. Research has shown that by incorporating nanocrystals in the tunnel oxide, charge traps are created which reduce charge leakage and improve endurance through charge-storage redundancy. By replacing the conventional floating gate memory with one using Si or Ge nanocrystals, the nonvolatile memory exhibits high programming speed with low programming voltage and superior retention time, and yet is compatible with conventional silicon technology.

This thesis provides an analysis of competing technologies, an intellectual property analysis, costs modeling as well as ways to improve nanocrystal memories in order to compete with other forms of emerging technologies to replace conventional Flash memories.

Thesis Supervisor: Carl V. Thompson Title: Stavros Salapatas Professor of Materials Science and Engineering

12 ANORA

. . 2 .

#### ACKNOWLEDGEMENTS

This thesis would not have materialized with the help, guidance and support of many people. First and foremost, I would like to thank Prof. Carl Thompson from the Massachusetts Institute of Technology (MIT) and Prof. Choi Wee Kiong from the National University of Singapore (NUS) for their guidance. I would also like to thank Prof Chim Wai Kim from NUS for lending me literature pertaining to nanocrystal memories.

I would also like to thank Dr. Vincent Ho and Mr Chin Khee Yeap from the semiconductor industry for providing me with estimated figures for the costs models.

The administrative officers from the Singapore-MIT alliance (SMA) office as well as the Department of Material Science and Engineering (DMSE) Office are also a great help. Special thanks to Ms Jocelyn Sales and Ms Juliana Chai for their assistance and help rendered throughout my entire course of studies.

In addition, I would also like to thank Roy, Zhengfei, Hongpeng and Zhihao from the Microelectronics Lab in the National University of Singapore for the time spent with me in discussing technical aspects pertaining to nanocrystal memories.

This thesis would also not be possible without the support of my fellow coursemates from the Singapore-MIT alliance program and the Massachusetts Institute of Technology, my housemates as well as my friends.

I would like to thank my family for having stood by me for all 26 years of my life. Last but not least, I would like to give my warmest thanks to professors in MIT and NUS who have taught me, and anyone who is not mentioned here but has helped me in one way or another.

## Contents

| 1. | Introduction                                        |    |

|----|-----------------------------------------------------|----|

|    | 1.1 History of Non-volatile Memory Structures       | 10 |

|    | 1.2 Working Principles of Conventional Flash Memory | 13 |

|    | 1.3 Current and Future Non-volatile Memories        | 16 |

|    | 1.4 Nanocrystal Memory                              | 22 |

|    | Chapter 1 References                                | 23 |

| 2. | Nanocrystal Memory                                  |    |

|    | 2.1 Nanoceystal Memory Device                       | 27 |

|    | 2.2 Synthesis of Germanium Nanocrystals             | 30 |

|    | 2.3 Characterization of Nanocrystals                | 33 |

|    | 2.4 Charge Storage in Nanocrystal Memory Devices    | 34 |

|    | 2.5 Optimum Nanocrystal Size                        | 43 |

|    | 2.6 Comparison of Different Nanocrystal Memory      | 48 |

|    | 2.7 Hetero-nanocrystal Memory                       | 50 |

|    | 2.8 Comparison between NC Memory and other          | 57 |

|    | Flash Replacement Technologies                      |    |

|    | 2.9 Multi-bit Schemes                               | 62 |

|    | Chapter 2 References                                | 62 |

| 3. | Market and Intellectual Property Analysis                |    |

|----|----------------------------------------------------------|----|

|    | 3.1 Market Overview                                      | 75 |

|    | 3.2 Market Growth                                        | 79 |

|    | 3.3 Competitors                                          | 83 |

|    | 3.4 Intellectual Property                                | 84 |

|    | 3.5 Market and Intellectual Property Analysis Conclusion | 86 |

|    | Chapter 3 References                                     | 86 |

| 4. | Cost Modeling                                            |    |

|    | 4.1 Chip Industry Trends                                 | 90 |

|    | 4.2 Cost Model of Building a Fabrication Plant           | 94 |

|    | 4.3 Cost Modeling Conclusions                            | 96 |

|    | Chapter 4 References                                     | 97 |

| 5. | Conclusions                                              |    |

.

99

# **List of Figures**

Г

| Figure 1.1: Schematic of a Floating Gate Device                                                                                                                                                                                                                                                         | 12 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.2: (Top) NOR Flash Memory and Wiring on Silicon. (Bottom))<br>NAND Flash Memory and Wiring on Silicon.                                                                                                                                                                                         | 15 |

| Figure 1.3: (Left) Schematic Comparison between a Floating Gate<br>Structure and a SONOS Structure (Right) A Transmission Electron<br>Microscopy (TEM) Image of the SONOS Structure                                                                                                                     | 18 |

| Figure 1.4: Schematic of Phase Change Memory                                                                                                                                                                                                                                                            | 20 |

| Figure 1.5: A MRAM Cell During Read (Above) and Write (Below)<br>Operations                                                                                                                                                                                                                             | 22 |

| Figure 2.1: Schematic of Silicon Nanocrystal Based Memory                                                                                                                                                                                                                                               | 28 |

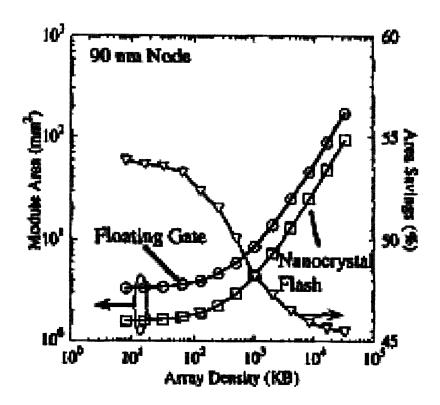

| Figure 2.2: Memory module size for both conventional floating gate<br>NVM and nanocrystal based NVM showing approximate factor of two<br>reduction for nanocrystal b Figure 2.3: Schematic illustration of the<br>density of supercritical particles as a function of time after quenching<br>based NVM | 30 |

| Figure 3.2: Schematic illustration of the density of supercritical particles as a function of time after quenching                                                                                                                                                                                      | 31 |

| Figure 2.4: C–V hysteresis loops for various annealed MOS capacitors.<br>The inset is a schematic of the MOS memory structure based on silicon nanocrystals                                                                                                                                             | 35 |

| Figure 2.5: Long-term charge retention characteristics in various annealed MOS capacitors, measured using the constant-capacitance method at the flat-band point                                                                                                                                        | 36 |

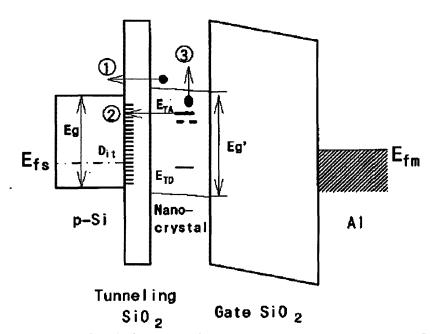

| Figure 2.6: Energy band diagram of the MOS memory structure at flat-<br>band condition for electron tunneling processes in the retention mode<br>after injecting electrons                                                                                                                              | 37 |

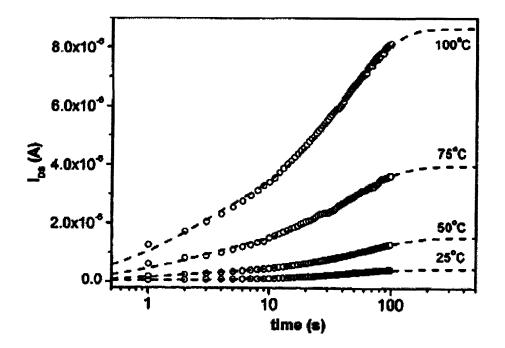

| Figure 2.7: Drain current $(I_{DS})$ transient at a read voltage of 5V after a write operation at 15V for 20s.                                                                                                                                                                                          | 40 |

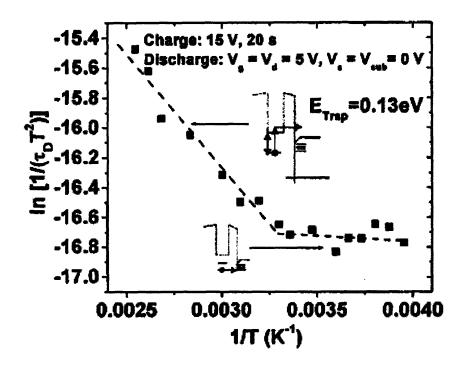

| Figure 2.8: Inverse of discharging time constant $(\frac{1}{\tau_D})$ divided by the square of the temperature plotted against the inverse of T.                                                                                                                                                        | 41 |

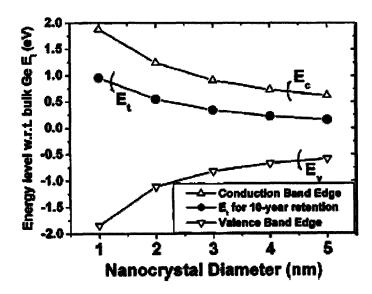

| Figure 2.9: Trap energy level required for 10 year charge retention performance vs nanocrystal diameter.                                                                                                                                                                                                | 42 |

.

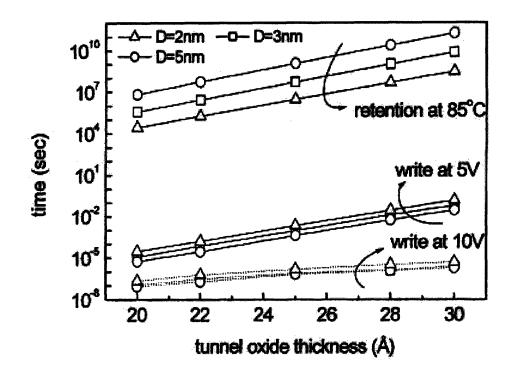

| Figure 2.10: Retention characteristics at various tunnel oxide thicknesses and the Ge nanocrystal size on device performance                                                                                                                                                                   | 45 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

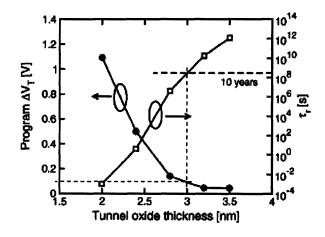

| Figure 2.11: Plot of threshold voltage shifts $\Delta V_T$ and retention period $\tau_r$ as a function of tunnel oxide thickness                                                                                                                                                               | 45 |

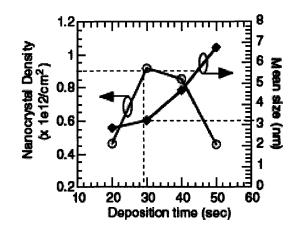

| Figure 2.12: Nucleation curve of nanocrystal deposited by CVD on $SiO_2$ showing the evolution of nanocrystal density and size with deposition time.                                                                                                                                           |    |

| Figure 2.13: Ordered Array of Nanocrystals                                                                                                                                                                                                                                                     | 48 |

| Figure 2.14: (Left) The schematic cross sectional of Ge/Si heteronanocrystal memory half cell. (Right) The valence band diagram for (a) hole writing (b) retention and (c) erasing.                                                                                                            | 51 |

| Fig 2.15: Fabrication of ordered nanocrystal array using porous alumina<br>using a two step anodization process. The first anodization serves as a<br>template for ordered hole formation in the second anodization.                                                                           | 52 |

| Fig 2.16: Formation of heteronanocrystals using porous alumina.                                                                                                                                                                                                                                | 53 |

| Figure 2.17: High magnification view of Ge nanodot array fabricated using alumina membrane.                                                                                                                                                                                                    | 54 |

| Figure 2.18: Ordered formation of silicon nanocrystals using diblock copolymers                                                                                                                                                                                                                | 55 |

| Figure 2.19: Schematic for formation of vertical blocks of polystyrene.                                                                                                                                                                                                                        | 55 |

| Figure 2.20: Interfacial energies $\gamma_{Sf}$ and $\gamma_{Mf}$ as a function of f. $\gamma_{Sf} = \gamma_{Mf}$ at $f \sim 0.6$ (0.6 styrene and 0.4 PMMA).                                                                                                                                  | 56 |

| Figure 2.21: Atomic force microscopic phase images. Images are from thin films of $P(S-b-MMA)$ symmetric diblock copolymer with a random copolymer anchored either a) to the substrate only or b) to the substate and air surface. Insets indicate the orientation of the lamellar morphology. | 57 |

| Figure 2.22: Cell Sizes of Different Memory Technology Nodes in the ITRS                                                                                                                                                                                                                       |    |

| Figure 2.23: Schematic of double gate nanocrystal memories with ultrathin body structure                                                                                                                                                                                                       |    |

| Figure 2.24: Energy band diagram in retention just after a write pulse                                                                                                                                                                                                                         | 62 |

| Figure 2.25: Schematic on the use of discrete traps for charge storage to realise a dual bit memory cell                                                                                                                                                                                       | 63 |

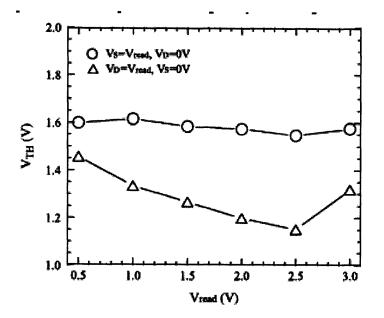

| Figure 2.26: Difference of threshold voltage between the read with drain<br>and with source after programming by channel hot electron with high<br>drain bias                                                                                                                                  | 64 |

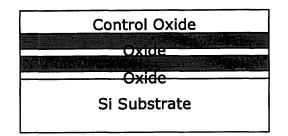

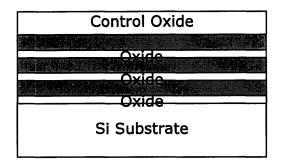

| Figure 2.27: Two and three layer schematics of multilevel nanocrystal                                                                                                                                                                                                                          | 65 |

| memories.                                                                                                                                                                                                                                                                                     |     |

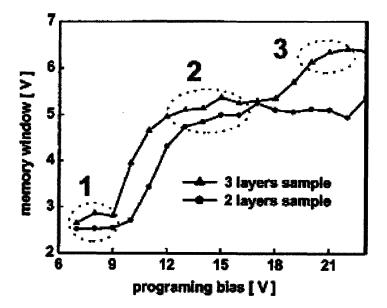

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 2.28: The dependence of the memory window on programming voltage. There are three apparent stages observed for the three layer samples, and two stages for the layer samples                                                                                                           | 65  |

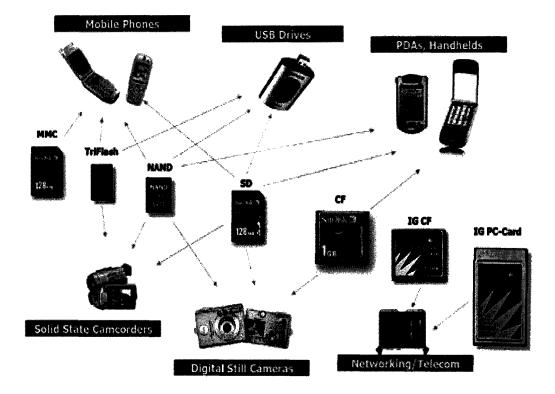

| Figure 3.1: Some Applications for NAND Flash                                                                                                                                                                                                                                                  | 77  |

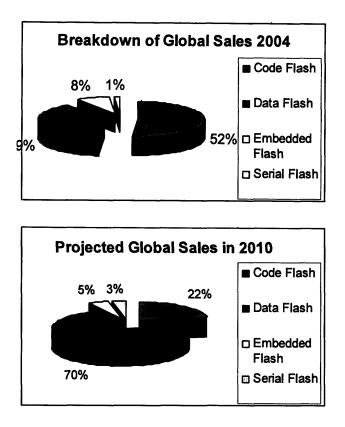

| Figure 3.2: (Top) Breakdown of global sales of flash memory in 2004 (Bottom) Projected global sales in 2010.                                                                                                                                                                                  | 78  |

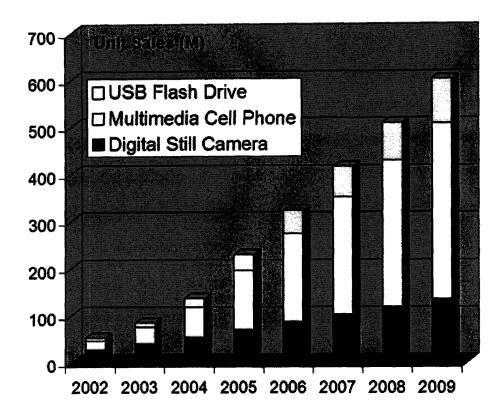

| Figure 3.3: Projection of unit shipments of mobile electronic products with flash memory.                                                                                                                                                                                                     | 79  |

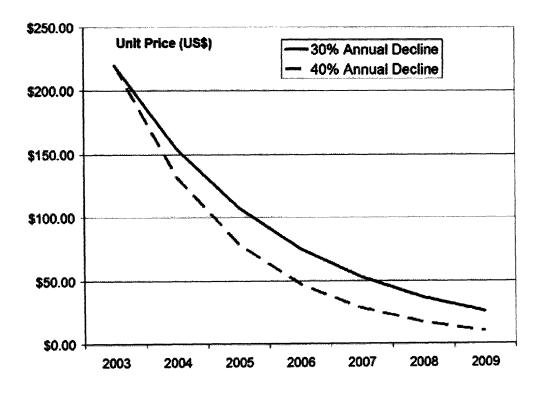

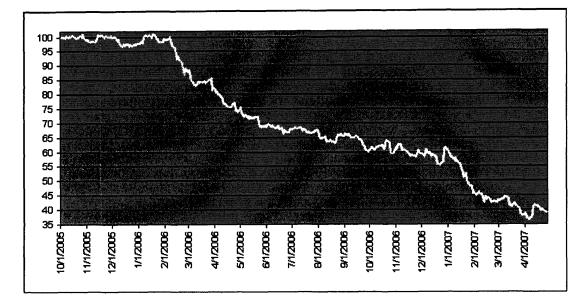

| Figure 3.4: Projection of price of a 1 GB thumbdrive                                                                                                                                                                                                                                          | 80  |

| Figure 3.5: Price-weighted index comprised of the average retail price of 1GB Universal Serial Bus (USB) Flash Memory. The index is normalized to a base value of 100 as of October 1, 2005. The price index shows a 40% drop for a period of 1 year and a 65% drop for a period of 18 months | 81. |

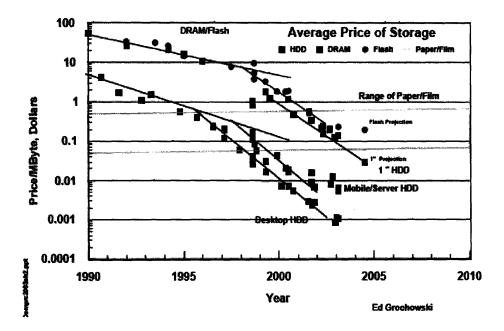

| Figure 3.6: Price per megabyte of hard disk drives, dynamic random access memory, flash                                                                                                                                                                                                       | 82  |

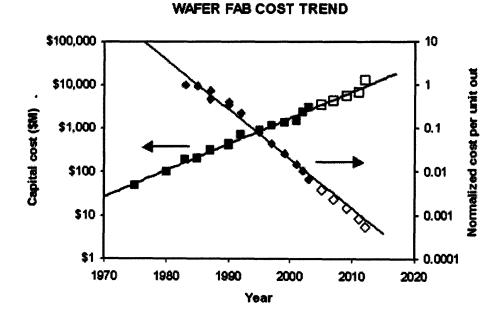

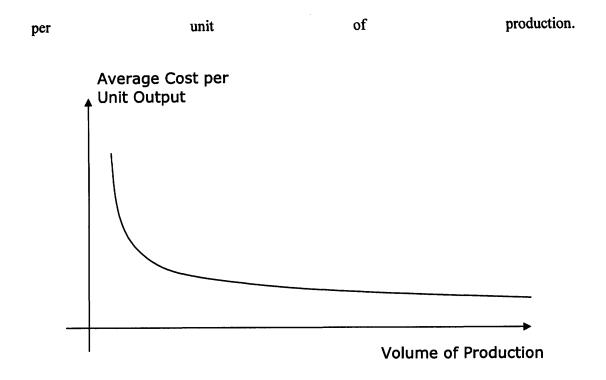

| Figure 4.1: Capital costs and normalized cost per unit output over the years                                                                                                                                                                                                                  | 91  |

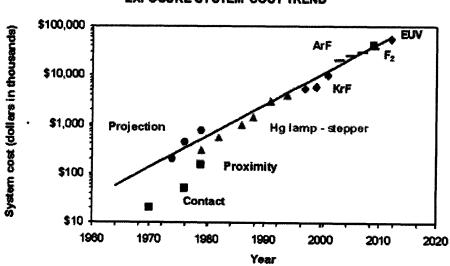

| Figure 4.2: Exposure system costs trend                                                                                                                                                                                                                                                       | 91  |

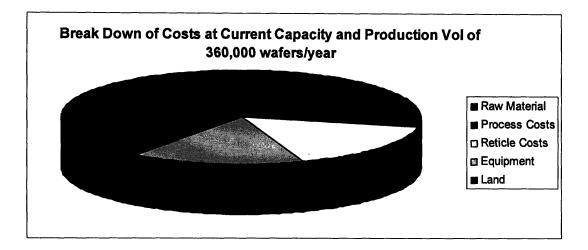

| Figure 4.3: Wafer cost breakdown for a 300mm logic wafer. Much of the costs come from depreciation of building and equipment costs, followed by costs of raw materials and other consumables                                                                                                  | 92  |

| Figure 4.4: Average cost curve of a typical Flash manufacturer.                                                                                                                                                                                                                               | 93  |

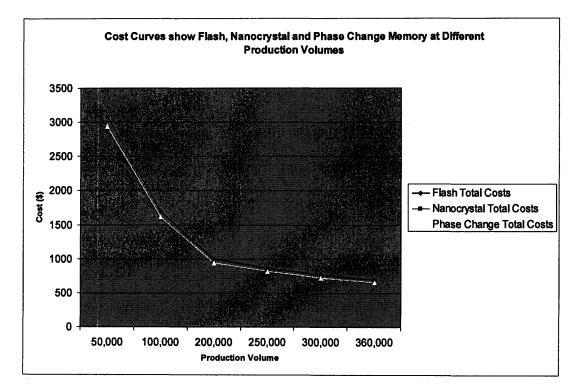

| Figure 4.5: Simulated cost curves for plant with annual production of 360,000.                                                                                                                                                                                                                | 95  |

| Figure 4.6: Simulated Breakdown of costs for a plant with capacity and annual production of 360,000 wafer per annum                                                                                                                                                                           | 96  |

# **List of Tables**

| Table 2.1 Mask adders required to integrate nanocrystal based non volatile memory into a standard CMOS flow compared against conventional non volatile memory | 29 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 2.2: Different Types of Memory Technologies                                                                                                             | 59 |

| Table 3.1: Major memory technologies and companies with research on                                                                                           | 83 |

| Table 3.2: Selected patents relevant to fabrication of nanocrystal based memory devices                                                                       | 84 |

| Table 4.1: 2005 Rankings Top Suppliers of Flash Memories                                                                                                      | 94 |

| Table 4.2: Parameters used in cost analysis                                                                                                                   | 94 |

## **Chapter 1: Introduction**

Demand for smaller and faster electronics and embedded systems supports the development of high-density, low-power non-volatile electronics. Flash memory cells designed for ten years of data retention require the use of a thick tunneling oxide. This compromises writing and reading speed as well as endurance.

A smaller device size can be achieved and speed and can be improved by decreasing the oxide thickness. However, significant charge leakage will occur if the oxide is too thin and this reduces the data retention time dramatically. This imposes a limit to the amount by which the oxide thickness can be decreased in conventional devices.

Research has shown that by incorporating nanocrystals in the tunnel oxide, charge traps are created which reduce charge leakage. By replacing the conventional floating gate memory with one using Si or Ge nanocrystals, the nonvolatile memory exhibits high programming speed with low programming voltage, superior retention time and yet is compatible with conventional silicon technology.

In addition, nanocrystal based memories are also more resistant to defects in the tunnel oxide. In conventional Flash cells, when there is a defect in the tunnel oxide, charges stored in the floating gate will leak away, rendering the cell unusable. However,

for nanocrystal memories, a defect in the tunnel oxide will only affect the charges stored in neighboring nanocrystals. As a result, nanocrystal based memories would normally be able to function properly as long as the defect remains small and isolated.

#### 1.1 History of Non-volatile Memory Structures

Memory can be classified as two main types: volatile and non-volatile. Volatile memory loses its data after the supply current is turned off. Examples of this type of memory include static random access memory (SRAM) and dynamic random access memory (DRAM). Non-volatile memory retains its data even when it is not powered. The main types of non-volatile memory include Electrically Erasable Programmable Read Only Memory (EEPROM,) Erasable Programmable Read Only Memory (EPROM) and Flash (also called Flash EEPROM).

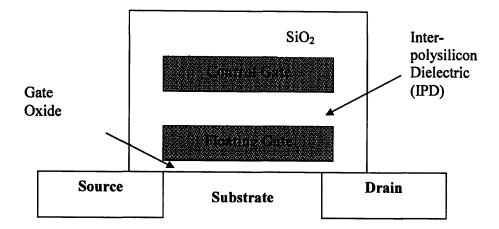

Kahng and Sze proposed the first non-volatile floating gate memory in 1967. A conventional Metal Oxide Semiconductor Field Effect Transistor was modified to include an embedded metal floating gate as illustrated in Fig 1.1. The floating gate device looks like an n-channel Metal Oxide Semiconductor Field Effect Transistor (MOSFET) except that it has two gates: the floating gate and the control gate. The floating gate is able to store charges that were injected from the substrate through the thin tunneling oxide. The storage of charges changes the threshold voltage of the MOSFET and allows logic '0' and '1' to be represented.<sup>1</sup>

A schematic of a floating gate device is as illustrated below:

Figure 1.1. Schematic of a Floating Gate Device

In this type of memory, electrons are transferred from the substrate to the floating gate by tunneling through the thin layer of silicon dioxide. Storage of charges in the floating gate can be adjusted between high and low levels to represent '1' and '0'. The charges are retained even when the power is switched off.

In 1970, Frohman-Bentchkowsky demonstrated a floating polysilicon gate. The electrons were injected through a thick gate oxide to the floating silicon gate and removed using ultraviolet (UV) irradiation. This was also known as Electrically Programmable Read Only Memory (EPROM).

In 1980, an Electrical Erasable Programmable Read-Only Memory (EEPROM) utilizing tunneling write/erase was developed by Intel. The Floating Gate Tunneling Oxide (FLOTOX) technology proposed by Intel utilizes two transistors (a select transistor and a memory transistor) to achieve selective bit programming through Fowler-Nordheim (FN) tunneling. The select gate transistor is used to select or deselect floating gate transistors for programming or erasing. The die size was further increased to include error correction/redundancy circuitry, making them much larger than EPROMs.<sup>2</sup>

A single transistor EEPROM cell combining hot electron programming and FN tunneling erase was introduced in the 1980s. This new generation of EEPROMs does not have the select transistor and could only be erased by resetting the devices on the entire chip or a large portion of the chip. This generally sets all bits in the block to 1. Starting with a freshly erased block, any location within that block can be programmed. However, once a bit has been set to 0, only by erasing the entire block can it be changed back to 1. This chip is known as the Flash EEPROM. A smaller cell size can be achieved compared to the normal EEPROM. This can be further scaled down by using a thinner gate dielectric. However, of the gate oxide gets too thin, there will be current leakage problems, causing data retention issues. This limits the scalability of the minimum dimension of the memory cell.<sup>3-5</sup>

## 1.2 Working Principles of Conventional Flash Memory

13

Conventional state of the art Flash memory stores information in floating gates transistors similar to that illustrated in Figure 1. Traditionally, each transistor or cell holds one bit. However, newer Flash systems can hold multiple bits and are called multi level cell devices. As mentioned earlier, information is stored inside the floating gate by trapped electrons.

In a NOR flash cell, the floating gate is programmed by placing a large voltage at the control gate. Electrons are sucked up and deposited at the floating gate via a process called hot electron injection (HEI). In order to erase, a large negative voltage is supplied at the gate and the electrons tunnel out by Fowler-Nordheim (FN) Tunneling. The high voltage required is generated using an on chip charge pump. Most modern NOR flash memory components are divided into erase segments, usually called either blocks or sectors. All of the memory cells in a block must be erased at the same time. NOR programming, however, can generally be performed one byte or word at a time. On the other hand, NAND flash memory uses tunnel injection for writing and tunnel release for erasing.

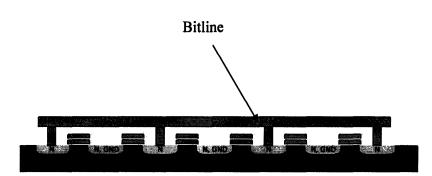

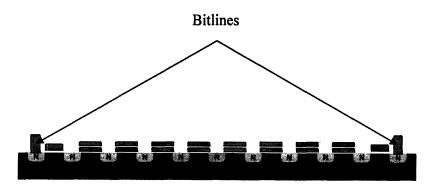

In NOR cells, the source or drain of the transistors are connected to a single bitline in parallel. In NAND cells, the memory cells are connected from a single bitline in series. This is as illustrated in Figure 1.2. The wordline, connected to the control and floating gate, is stacked above the silicon substrate. Adjacent transistors share the same source/drain.

Figure 1.2: (Top) NOR Flash Memory and Wiring on Silicon. (Bottom)) NAND Flash Memory and Wiring on Silicon.<sup>6</sup>

The parallel configuration of NOR Flash enables random access of data, enabling fast read speed. Hence, NOR flash is ideal for applications which are frequent read-only or perform-read operations such as code storage. NAND Flash enjoys higher cell density for a given technology node. This translates to smaller chip size, lower cost-per-bit and faster write/erase speed through programming blocks of data. Hence, NAND is ideal for applications such as data storage which requires low cost, small size and which rewrites data frequently.<sup>7-9</sup>

## 1.3 Current and Future Non-volatile Memories

Flash memory is the dominant form of non-volatile memory in the market. In recent years, there has been a drastic increase in demand for portable electronic devices such as cellular phones, digital cameras and thumb drives. In addition, new markets for flash memories are emerging. As prices fall, Flash memories are now able to compete with magnetic and optical storage media, especially in areas where users are willing to pay a premium for speed and performance<sup>10-15</sup>. Both developments contribute to skyrocketing demand for Flash Memory.

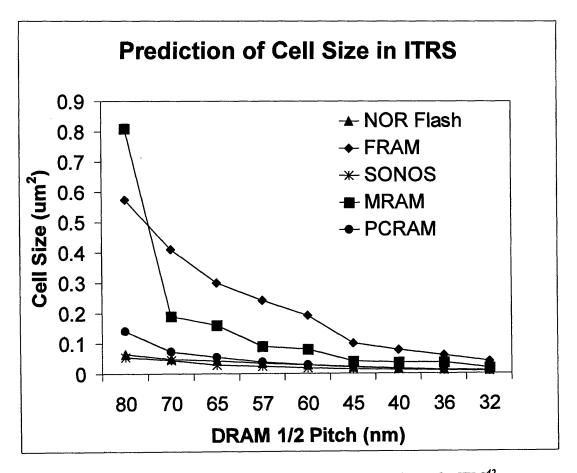

Great efforts have been carried out to make Flash memory cells smaller and more portable and at the same time faster and with lower power consumption. However, there is a limit to which cell size can be scaled down. Current flash memory technology is expected to be replaced or undergo some radical changes in the not-so-distant future<sup>16-18</sup>. There has been intense research interest into the various options available and various new technologies have been mooted as potential successors to conventional Flash technology. The major forerunners include Silicon Oxide Nitride Oxide Semiconductor (SONOS), Ferro-electric Random Access Memory (FRAM), Magnetic Random Access Memory (MRAM) and phase change memory (PCRAM). Predictions of their attributes have been listed in the International Technology Roadmap for Semiconductors (ITRS)<sup>19</sup>. They are touted to be potential successors to conventional memory. A brief description of their working principles is given below while a more in depth comparison between them and nanocrystal based memories will be given in Chapter 2.

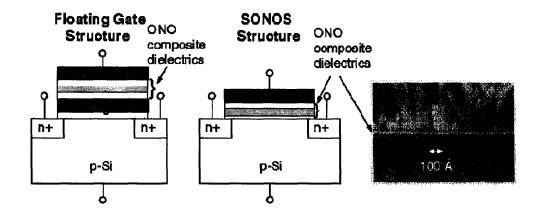

## 1.3.1 Silicon Oxide Nitride Oxide Semiconductor (SONOS)

Silicon Oxide Nitride Oxide Semiconductor (SONOS) "cells" consist of a standard n-channel MOS transistor with additional layers of insulators on the gate. These include the oxide layer (~2 nm), a silicon nitride layer (~5 nm), and a second oxide layer (5-10nm). SONOS is similar to Flash Memory. However, it relies on the charge trapping mechanism in which electrons are trapped in the nitride layer. SONOS offers a lower power usage, improved cycling endurance, reduction in process complexity and elimination of drain-induced turn-on. The SONOS memory device is more scalable than the floating gate flash memory since the equivalent oxide thickness (EOT) of the gate stack is thinner in the SONOS memory than in the floating gate memory.<sup>21</sup> Moreover, current manufacturing processes are simpler compared to flash manufacturing processes as they only require four additional non-critical masking steps over the basic logic processes (flash floating gate requires eleven additional processes).<sup>22</sup> Also, the trapped nitrides do

not leak away easily and hence SONOS is more radiation hard than conventional Flash whose thin tunneling oxide is easily damaged by large ionizing doses, leading to charge leakage.<sup>23</sup>

Figure 1.3: (Left) Schematic Comparison between a Floating Gate Structure and a SONOS Structure (Right) A Transmission Electron Microscopy (TEM) Image of the SONOS Structure.<sup>20</sup>

#### 1.3.2 Ferroelectric Random Access Memory (FeRAM)

A ferroelectric memory cell consists of a ferroelectric capacitor and a MOS transistor. It is similar to the storage cell of a DRAM. However, the material between the capacitor's electrodes has a high dielectric constant and can be polarized by an electric field. When an external electric field is applied across a dielectric, the dipoles tend to align themselves with the field direction, as a result of small shifts in the positions of atoms and shifts in the distributions of electronic charge in the crystal structure. This type of material is known as a ferroelectric material. Contrary to its name, this type of material does not necessarily have to contain iron. The polarization remains even when the electric

field is removed and remains until it gets reversed by an opposite electrical field. This makes the memory non-volatile. The polarity and quality of stored data is dependent on the direction and strength of the remnant polarization after the electric field is removed. Ferroelectric memories can be written much faster than EEPROMs and operating voltages are relatively small. FeRAM is also radiation hard.<sup>18</sup> Today's FRAM uses lead zirconate titanate (PZT); other materials are being considered. The main developer of FRAM is Ramtron International. The main drawback of FRAM is incorporating ferroelectric materials into current silicon manufacturing processes.<sup>24</sup> The International Technology Roadmap for Semiconductors (ITRS) also highlighted that continued scaling of the stack capacitor would be challenging and FRAM production is sensitive to processing conditions and temperatures.<sup>19</sup>

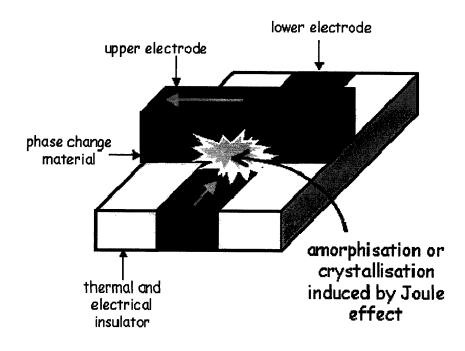

#### 1.3.2 Phase Change Random Access Memory (PCRAM)

Phase Change Memory (PCRAM) comprises of a transistor and a resistor made from chalcogenide material alloys (eg.  $Ge_2Sb_2Te_5$ ) commonly used in rewritable compact disks. Electrical charges are used to convert the phase of the material from crystalline, which is conductive, to amorphous, which is resistive, vice versa. This is accomplished though Joule heating. In this way, the resistance state of the material can be used to represent logic '0' and '1'. Multi-state operations can also be achieved by programming the cell to intermediate values. The energy required for phase transformation also decreases with cell size, encouraging memory scaling. Erasable thermal phase change recording at a storage density of 3.3Tb inch<sup>-2</sup> has been shown and Samsung has produced a working prototype of PCRAM that is comparable to the size of NOR Flash<sup>25-26</sup>. Issues include reducing the reset current as cell size scales while maintaining writing capability and reducing thermal cross-talk at higher densities<sup>18,28</sup>.

Figure 1.4. Schematic of Phase Change Memory<sup>54</sup>

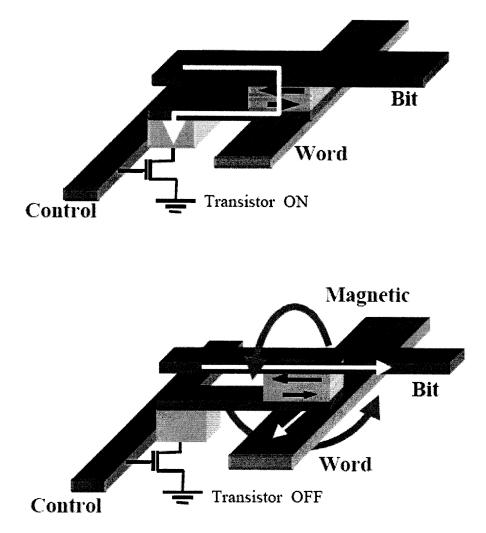

## 1.3.4 Magnetic Random Access Memory (MRAM)

In Magnetic Random Access Memory, the information is stored as the magnetization direction of ferromagnetic elements. In MRAM, the elements are formed from two ferromagnetic plates, each of which can hold a magnetic field, separated by a thin insulating layer. It utilizes the tunneling magnetoresistive (TMR) effect. The tunneling energy for electrons that are spin-aligned with both magnetic layers is less than that for electrons that are spin-aligned with only one layer. When the orientation of

both magnetic layers is the same, spin-aligned electrons have a higher probability of tunneling through the insulating layer. When the magnetic orientations of the layers are opposed, the tunneling probability of both spin-up and spin-down electrons is reduced. Due to the magnetic tunnel effect, the electrical resistance of the cell changes depending on the orientation of the fields in the two plates. Two plates having the same polarity indicate a logic state of "0", while two plates of opposite polarity indicates a logic state of "1" as resistance is higher. Another type of MRAM consists of two ferromagnetic plates separated by a magnetic, non metallic spacer layer. This utilizes the giant magnetoresistive (GMR) effect. Free electrons are generated 'spin-up' and 'spin-down' in equal proportions. When the orientation of both magnetic layers is parallel, only one type of electron is retarded. When the magnetic orientations of the layers are anti-parallel, both spin-up and spin-down electrons suffer retardation. In this way, resistance is varied to give logic "0" and "1". For both methods, one of the two plates is commonly fixed to one polarity and the other's field will change to match that of an external field<sup>29-31</sup>. Issues with future development of MRAM includes disturbance from neighbouring cells, stability issues concerning the tunneling barrier and the free layer with increased scaling<sup>18, 31-33</sup>.

21

Figure 1.5. A MRAM Cell During Read (Above) and Write (Below) Operations<sup>34</sup>

## 1.4 Nanocrystal Memory

Another area of active research is the use of nanocrystals to replace a single floating gate as storage sites. This is similar to the use of nitride traps in SONOS memory. It is

easy to integrate nanocrystal based memories into current CMOS processes. It also has several other advantages. This will be discussed further in the next chapter.

#### References

- D. Kahng and S.M.Sze "A floating gate ad its application to memory devices," Bell Syst. Tech. J., vol 46, p.1288, 1967

- Jitu J. Makwana, Dieter K. Schroder "A non-volatile memory overview," <u>http://aplawrence.com/Makwana/nonvolmem.html</u>

- B.H. Koh *et al.* "Traps in germanium nanocrystal memory and effect on charge retention: modeling and experimental measurements," J. of Appl Phys, vol 97, p.124305, 2005

- Min She and Tsu-Jae King, "Impact of crystal size and tunnel dielectric on semiconductor nanocrystal memory performance," IEEE Trans. On Electron Devices, vol 50, no 9, p. 1934, 2003

- Ya-Chin King, Tsu-Jae King and Chenming Hu, "MOS Memory Using Germanium Nanocrystals Formed by Thermal Oxidation of Si<sub>1-x</sub> Ge<sub>x</sub>," IEEE Electron Devices Meeting, p. 115, 1998

- 6. Wikipedia, "Flash Memory," <u>www.wikipedia.com.</u>

- Electronic Information Online, "Flash Memory Devices" <u>http://www.electronics-</u> manufacturers.com/info/computers-and-laptops/flash-memory-devices.html

- Toshiba, "NAND vs NOR Flash Memory Technology Overview" <u>http://www.chips.toshiba.com</u>

- Electronics Design, Strategy, News, "What is the difference between NAND and NOR Flash?" <u>http://www.edn.com/article-partner/CA6319916.html</u>

- 10. Michelle Kessler, "Demand for Flash Memory Skyrockets." <u>http://www.usatoday.com/money/industries/technology/2005-09-18-flash-</u> <u>memory\_x.htm</u>

- Michael Kanellos, "SanDisk drops prices with new flash drives." EETimes Encyclopedia

http://news.com.com/SanDisk+drops+prices+with+new+flash+drive/2100-1041\_3-6166983.html

- 12. Chris Preimesberger, "Hot Flash: 'Flashtops' Take On the Memory Market." eWeek.com <u>http://www.eweek.com/article2/0,1895,2008089,00.asp</u>

- 13. John Walko, "SanDisk targets gruvi music card at mobiles." EETimes Encyclopedia

http://www.eetimes.com/showArticle.jhtml;jsessionid=ENNZMSCPVD3ZUQSN DLOSKH0CJUNN2JVN?articleID=171201249

- 14. Dov Moran, "Progenitor of the USB Flash Drive," EETimes <u>http://www.eetimes.com/showArticle.jhtml;jsessionid=ENNZMSCPVD3ZUQSN</u> <u>DLOSKH0CJUNN2JVN?articleID=174401544</u>

- 15. Theo Valich, "Flash will Kill BluRay ad HD DVD," http://www.theinquirer.net/default.aspx?article=36930

- 16. Michael Kenellos, "Is Flash Fried?" CNet News.com http://news.com.com/Flash+forward/2009-1040\_3-994240.html

- Aaron Theon and Jean Pierre Leburton, "Towards Single-Electronics," IEEE

2002

- Betty Prince, "Trends in Scaled and Nanotechnology Memories," Memory Strategies International, IEEE, 2005

- 19. The International Technology Roadmap for Semiconductors 2006 Update, Process Integration, Devices and Structures <u>http://www.itrs.net/Links/2006Update/FinalToPost/04\_PIDS2006Update.pdf</u>

- 20. Jiankang Bu and Marvin H. White, "Design Considerations in Scaled SONOS Non-volatile Memory Devices" <u>http://klabs.org/richcontent/MemoryContent/nvmt\_symp/nvmts\_2000/presentatio</u> ns/bu white sonos lehigh\_univ.pdf#search=%22SONOS%20memory%22

- 21. Min She, "Semiconductor Flash Memory Scaling" pHD dissertation, 2003.

- 22. C.T. Swift et al, "An Embedded 90nm SONOS non-volatile memory utilizing hot electron programming and uniform tunnel erase," IEEE Electron Devices Meeting, p 927, 2002.

- 23. Dennis A. Adams, David Mavis, James R.Murray and Marvin H.White, "SONOS Non Volatile Memory Semiconductor Memories for Space and Military Applications."

http://klabs.org/richcontent/MemoryContent/nvmt\_symp/nvmts\_2000/papers/ada ms\_d.pdf

24. Wikipedia, "Ferroelectric RAM," http://en.wikipedia.org/wiki/Ferroelectric\_RAM 25. Samsung. "Samsung Introduces the Next Generation of Non-Volatile Memory – PRAM,"

http://samsung.com/PressCenter/PressRelease/PressRelease.asp?seq=20060911\_0 000286481

- 26. Hendrik et al. "Ultra-high-density phase-change storage and memory," Nature Vol 5, 383, 2006.

- 27. PC-RAM Project Home Page http://www.projects.ex.ac.uk/pcram/

- Yun Sheung Shin. "Non-volatile Memory Technologies for Beyond 2010," 2005

Symposium for VLSI Circuits Digest of Technical Papers, 2005

- 29. IBM, "IBM Research News", http://www.research.ibm.com/resources/news/20001207\_mramimages.shtml

- 30. Phillips Password Magazine, "MRAM- Magnetic Memory Goes Solid State", http://www.research.philips.com/password/archive/12/mram.html

- 31. S. Tehrani et al, "Progress and Outlook for MRAM Technology", IEEE Transactions on Magnetics, Vol 35, No 5,p 2814, 1999

- 32. Johan Akerman, "Towards a Universal Memory", Science Vol 308, p508, 2005.

- W.J. Gallagher et al. "Recent Advances in MRAM Technology, " IEEE <u>VLSI</u> Technology, p72-73 2005. (VLSI-TSA-Tech).

- 34. J.P. Nozieres, "Magnetic random access memories (MRAM): a truly universal memory?" Unpublished Paper

## **Chapter 2: Nanocrystal Memory**

Nanocrystal memory has been an area under intense research since Tiwari et al. demonstrated a Si nanocrystal memory that uses direct tunneling into three dimensionally confined nanocrystals for bi-stability in the conduction of a transistor channel<sup>1,2</sup>. Since then, memory effects of materials such as Germanium<sup>3-8</sup> and transition metals such as Au, Ag, W, Pt and Sn<sup>9-13</sup> have been investigated by various research groups worldwide.

#### 2.1 Nanocrystal Memory Device

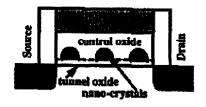

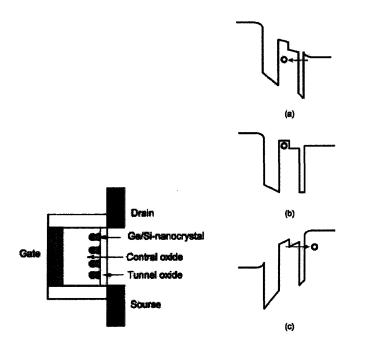

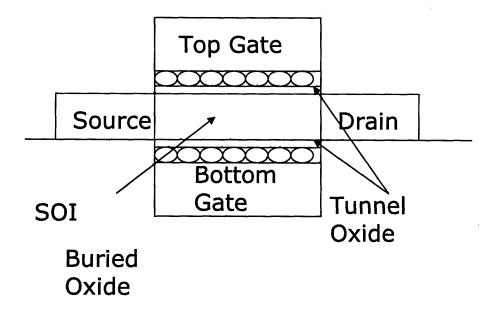

The memory devices demonstrated by Tiwari et al. are based on a Flash memory structure (consisting of a MOSFET as illustrated in Figure 1) with floating islands of silicon nanocrystals embedded in the gate oxide. This is illustrated in Figure 4. By using electrically isolated charge storage sites, charge leakage via localized oxide defects is reduced and a superior retention time can be achieved. As a result, a thinner tunneling oxide can be employed. This relaxation in the tunneling oxide constraint results in smaller operating voltages as well as lower power dissipation than current Flash EEPROM. It also brought about faster programming and at low operating voltage via direct tunneling mechanisms.<sup>1,2</sup> Nanocrystal based memories are also more resistant to defects in the tunnel oxide. In addition, nanocrystal based memories are less complex to manufacture than conventional Flash memory. Conventional

memory requires 11 additional mask adders over the basic CMOS process while nanocrystal memory requires only 4. The reduction in complexity is due to the elimination of process steps to satisfy the high voltage requirements in conventional Flash memory. The removal of high voltage requirements in nanocrystal memory also enable nanocrystal memory to scale better than conventional Flash memory. This is evident from Figure 2.2. Germanium as well as metal-nanocrystal-based transistors work similarly to silicon nanocrystal memory.

Figure 2.1: Schematic of Silicon Nanocrystal Based Memory

| Process Step                                                                                                                                                                                                                                                                           | Logic | Floating Gate                                                         | Nanocrystal                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------------------------------------------------------|------------------------------------------|

| Process Step<br>Isolation Formation<br>High Voltage Wells<br>NVM Array Well (1Mask)<br>Tunnel Oxidation<br>Floating Gate Deposition/Patterning<br>ONO/Nanocrystal Dep./Patterning<br>Low Voltage Wells<br>OGO Wells                                                                    | Logic | Floating Gate<br>•<br>2 masks<br>1 mask<br>•<br>1 mask<br>1 mask<br>• | Nanocrystal<br>•<br>1mask<br>1 mask<br>• |

| High Voltage Oxidation/Patterning<br>OGO Oxidation Patterning<br>Low Voltage Oxide Growth<br>Gate Deposition<br>NVM Stack Patterning<br>NVM Source Hole Implant<br>NVM Drain Implant<br>Gate Patterning<br>High Voltage LDD Implants<br>OGO LDD Implants<br>S/D and Backend Processing | •     | •<br>1 mask<br>1 mask<br>1 mask<br>1 mask<br>2 masks<br>•             | 1 mask<br>•<br>1 mask<br>•               |

| Masking Step Adder                                                                                                                                                                                                                                                                     |       | +11                                                                   | +4                                       |

Taken from:

R. Muralidhar et al, "A 6V Embedded 90nm Silicon Nanocrystal Non-volatile Memory", IEEE Int Conf, 31, 2004

Table 2.1 Mask adders required to integrate nanocrystal based non volatile memory into a standard CMOS flow compared against conventional non volatile

memory<sup>14</sup>

Figure 2.2: Memory module size for both conventional floating gate NVM and nanocrystal based NVM showing approximate factor of two reduction for nanocrystal based NVM<sup>14</sup>

## 2.2 Synthesis of Germanium Nanocrystals

There are numerous ways of synthesizing germanium nanocrystals. These include cosputtering<sup>5-7</sup>, chemical vapour deposition<sup>15-17</sup>, ion implantation<sup>3,4</sup>, sol gel techniques<sup>18</sup> oxidation and reduction of SiGe films<sup>19</sup> and molecular beam epitaxy<sup>20</sup>.

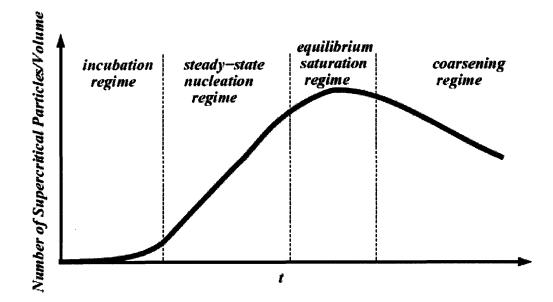

Figure 2.3: Schematic illustration of the density of supercritical particles as a function of time after quenching.<sup>21</sup>

Figure 2.3 shows a schematic illustration of the density of supercritical particles as a function of time after quenching. It can be observed that there are 4 stages of growth; namely, incubation, steady-state nucleation, equilibrium saturation and coarsening. In the incubation regime prior to the nucleation stage, the incubation time can be obtained by extrapolating the steady-state nucleation slope to zero density. In the nucleation stage, the steady-state nucleation rate can be predicted from the slope of the curve in this steady-state regime. Nanocrystals form by nucleation and growth. The density of the particles peaks in the equilibrium saturation regime. Subsequently, coarsening or ripening of the particles occurs, where a decrease in the particle density is observed. In this stage, the supersaturation of the matrix with respect to the solute atoms is sufficiently small to make nucleation of new particles unlikely. Ostwald ripening (coarsening) of nanocrystals will then occur.

The nanocrystal size is usually controlled by time and annealing temperature. In the coarsening phase, the Lifshitz-Slyozov theory of coarsening in alloys is normally used to describe the time evolution of the sizes of the particles of a phase coarsening by mass transfer among particles in a matrix. The Lifshitz-Slyozov-Wagner (LSW) theory predicts the rate of coarsening in alloys. It states that at large times t, the critical dimension  $x_c$  tends asymptotically to depend on time as  $t^{1/3}$ . At the same time, the degree of supersaturation correspondingly falls as  $t^{-1/3}$  and the number of grains as  $t^{-1}$ . Large particles grow while smaller ones shrink at the coarsening stage due to the Gibbs Thomson effect. The Gibbs-Thomson effect relates the curvatures of the spherical grains (represented by  $r_1$  and  $r_2$ ) to their corresponding activities (represented by  $a_1$  and  $a_2$ ) and hence solubilities in solution by the following equation:

$$RT\ln(\frac{a_2}{a_1}) = 2V_m\sigma[\frac{1}{r_2} - \frac{1}{r_1}]$$

R and T are the molar constant and the temperature, respectively.  $V_m$  represents the molar volume of a certain phase and  $\sigma$  represents the interfacial energy between two phases. The difference in the solute concentrations for different curvature particles

sets up a concentration gradient that drives diffusion of matter from the smaller to the larger particles  $^{21,22}$ .

The material in which Ge nanocrystals are embedded is usually  $SiO_2$  although other types of materials such as  $Al_2O_3$  are also investigated in research projects<sup>23</sup>.

#### **2.3 Characterization of Nanocrystals**

A variety of structural, optical and electrical techniques are commonly used to characterize Ge nanocrystals.

For structural characterization, transmission electron microscopy (TEM) is commonly used. It enables the size distribution, the spatial distribution, shape and defect structure of the nanocrystals to be studied. X-ray photoelectron spectroscopy is commonly used to investigate the chemical bonds that are present while Raman spectroscopy is used to determine the crystallinity and size of the nanocrystals. In addition, secondary ion spectroscopy (SIMS) allows a quantitative depth profiling of the elements in a sample.

The most commonly used characterization method is photoluminescence (PL) spectroscopy, especially in the study of quantum confinement effects. For electrical

methods, capacitance-voltage (C-V), capacitance-time (C-t) and current-voltage (I-V), measurements can be made to characterize the charge storing capability of nanocrystal-based transistor devices.

## 2.4 Charge Storage in Nanocrystal Memory Devices

There is an argument going on in the research community on the way in which nanocrystals store charge. It has been suggested that the charges are stored at the conduction band <sup>1,2,24</sup> or at deep traps <sup>7,8,25</sup>. Recent research indicates that charges are more likely linked to interfacial traps. Y.Shi et al. has highlighted that the band edge of a Si nanocrystal is higher than that of the substrate due to three dimensional quantum confinement effects. As a result, any electrons stored in the conduction band can easily tunnel back to the substrate. This cannot account for the observation of long retention times. He proposed that the injected electrons are stored at deep trapping sites.

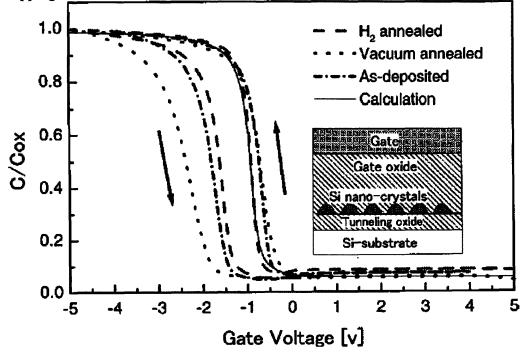

Figure 2.4: C-V hysteresis loops for various annealed MOS capacitors. The inset is a schematic of the MOS memory structure based on silicon nanocrystals<sup>25</sup>.

In order to investigate the effect of traps on charge storage, Shi et al. annealed various MOS capacitors in an H<sub>2</sub> ambient at 430 °C and in vacuum at 700 °C. The former process effectively decreased the number of interface traps by H-passivation, and the latter resulted in a high density of interface traps, especially P<sub>b</sub> centers. Figure 2.4 shows the C-V characteristics for the treated samples as well as the as deposited ones. The device annealed in vacuum exhibited the largest V<sub>fb</sub> shift as it has the highest trap density. The minimum V<sub>fb</sub> shift is observed for the H<sub>2</sub> annealed device having the lowest trap density. This means that more charges are stored in the nanocrystals synthesized by annealing in vacuum rather than in H<sub>2</sub>.

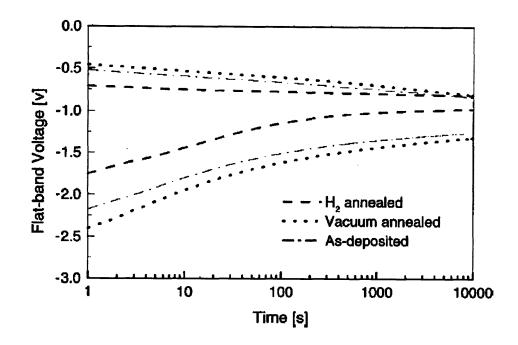

Figure 2.5: Long-term charge retention characteristics in various annealed MOS capacitors, measured using the constant-capacitance method at the flat-band point  $^{25}$ .

Figure 2.5 shows the long-term charge storage characteristics of various devices where the changes in the net charge stored in nanocrystals are proportional to the shifts of the  $V_{fb}$  obtained under constant-capacitance conditions. The fastest rate of electron loss is observed for the vacuum-annealed device while the H<sub>2</sub>-annealed device has the slowest electron-loss rate. Therefore, a higher rate of charge loss is obtained for a device with a higher density of traps. Furthermore, the temperature dependence of the charge storage characteristics shows that the charge-loss rate decreases slightly when the temperature changes from 300 K to 80 K. This implies

that thermal activation is not dominant for the charge-loss processes in the tested samples.

Figure 2.6: Energy band diagram of the MOS memory structure at flat-band condition for electron tunneling processes in the retention mode after injecting electrons<sup>25</sup>.

Based on the above experimental results, Shi et al proposed a model whereby an injected electron will first fill up the empty states in deep trap levels prior to filling up shallower trap levels. There are two mechanisms in which electrons can be detrapped and lost to the silicon substrate. The first is direct tunneling from the traps to the interface states at the SiO<sub>2</sub>/Si interface (process 2). Charge loss by this mechanism can be reduced by reducing number of interface states. The second is the indirect process involving the thermal detrapping of electrons to the conduction band (process 3) and then tunneling back to the substrate (process 1). A deeper trap level is

desirable for suppressing this kind of thermal activation. Shi et al. concluded from the experimental observation of charge loss rates on interface trap density and temperature that process 2 determines the long term charge retention in the samples. He further notes that the traps and defects at the internal/surface of nanocrystals and the interface states at the SiO<sub>2</sub>/Si substrate play different roles in the charge-loss process. The traps and defects at the internal/surface of a nanocrystal determine the amount of charge that can be stored. On the other hand, a smaller number of the interface states in the Si/SiO<sub>2</sub> interface would effectively result in a lower tunneling rate and longer retention time <sup>25</sup>.

Chen et al also concluded that at least some of the electrons are stored in traps after comparing experimental results with simulation data generated by another research group  $^{8,26}$ .

Unlike Shi et al<sup>25</sup>, King<sup>27</sup> and Koh et al.<sup>28</sup> note a significant temperature dependence in their Ge nanocrystal memory samples. Like Shi, they demonstrated that the memory devices lose their memory effect after annealing in a hydrogen ambient, thus showing that charges are stored in the interfacial traps rather than in the conduction band. Koh et al <sup>28</sup> found good agreement of experimental data with simulations (Figure 2.6). The simulated data was based on the temperature dependent Shockley-Read-Hall (SRH) relationship developed by McWhorter et al. <sup>29</sup>. The thermal equilibrium emission constant of electrons can be derived as

38

$$e_n = AT^2 \exp(-qE_t/kT),$$

where k is the Boltzmann constant, q is the electronic charge, T is the temperature,  $E_t$  is the trap energy level measured with respect to the conduction edge of the nanocrystal and A is the temperature independent constant which can be expressed as

$4\sqrt{\frac{6\sigma_e gk^2m}{(\pi\hbar^2)^{3/2}}}$ . m is the effective mass of the electron, g is the degeneracy and

h is Planck's constant. Also, the drain current during the discharge phase is modeled as

$$I_{DS(transient)} = q \{ n_1 [1 - \exp(-\lambda_1 t)] + n_2 [1 - \exp(1 - \exp(-\lambda_2 t)] \},\$$

where  $n_1 + n_2 = n$  and n is the total number of nanocrystalline Ge charging sites.  $\lambda_1$ and  $\lambda_2$  represent the discharging rate constants for the two different discharging mechanisms.

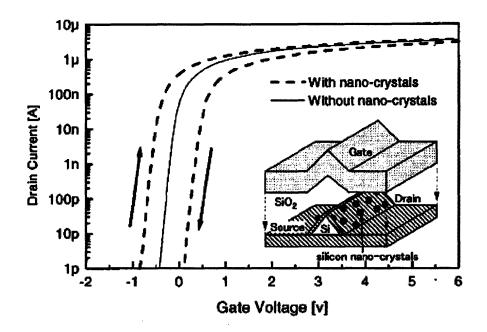

Figure 2.7: Drain current  $(I_{DS})$  transient at a read voltage of 5V after a write operation at 15V for 20s. The symbols represent the measured data and the lines are fitted data from a simulation. The increase in  $I_{DS}$  for higher temperatures could be explained by the larger carrier mobility and the higher intrinsic carrier concentration of the substrate.<sup>28</sup>

By performing transient drain current ( $I_{DS}$ ) measurements, the trap energy levels (E<sub>t</sub>) can be extracted. This is done by performing transient drain current measurements at different temperatures and calculating the discharging time constant ( $\tau_D$ ).  $\tau_D$  is defined as the time corresponding to 90% of the  $I_{DS}$  at steady state, when the drain current gradually returns to steady state value. The electrons which are detrapped during the discharge phase increase the drain current over its steady state value. Figure 2.8 indicates that for the samples, below 307.7K, the discharging process is relatively temperature insensitive, which corresponds to Process 2 (direct tunneling from the traps to the interface states at SiO<sub>2</sub>/Si interface) as described by Shi et al. Above 307.7K, Process 1 + 3 (indirect process involving the thermal detrapping of electrons to the conduction band and then tunneling back to the substrate) is more dominant and the discharging process shows a strong temperature dependence.<sup>28</sup>

Figure 2.8: Inverse of discharging time constant  $(\frac{1}{\tau_D})$  divided by the square of the temperature plotted against the inverse of T. The graph is plotted based on the calculations given by  $R_D \propto e_n = AT^2 \exp(-qE_1/kT)$ .  $R_D$  is the rate of discharge.<sup>28</sup>

Based on the above research observations, the following conclusions can be made:

- The discharge process is dominated by Process 1 + 3 at high temperatures and Process 2 at low temperatures.

- At low temperatures, decreasing the interface state at SiO<sub>2</sub>/Si substrate interface will improve retention time.<sup>25</sup>

3. At high temperatures, controlling the deep level traps is crucial to increase the retention duration of the memory device. Engineering the trap energy level can be carried out by manipulating the material of the host matrix, doping with impurities or changing the material of the tunnel oxide. The last method is based on the assumption that the trap sites in the nanocrystals responsible for charge storage are close to the Si substrate and such trap sites are affected by the close proximity to the tunnel barrier. Koh et al were able to prove this by showing that that nc-Ge/Al<sub>2</sub>O<sub>3</sub> has higher activation energies and hence deeper trap levels than nc-Ge/SiO<sub>2</sub>. <sup>28</sup> Other than methods involving increasing trap levels, retention time can also be increased by increasing the tunnel barrier, such as using germanium/silicon (Ge/Si) heteronanocrystals, which will be discussed later.

Figure 2.9: Trap energy level required for 10 year charge retention performance vs nanocrystal diameter. The Ge band-gap widening due to quantum confinement effect is also indicated. The conduction and valence bands edges at the boundaries of the

widened Ge band gap are given by  $E_c$  and  $E_v$ .  $(E_c - E_i) = (E_i - E_v) = 0.33 eV$  in bulk Ge,  $E_i$  is the midgap energy of Ge.<sup>28</sup>

Figure 2.9 illustrates the trap energy required to meet the 10 year requirement taking into account quantum size effects<sup>28</sup>. We can see from Figure 2.9 that as the size of nanocrystals decrease,  $E_c-E_t$  increases, and deeper level traps are required. As the size of the nanocrystals decreases, the barrier height is lower and it is easier for the electrons to leak through the tunnel barrier. In order to compensate for this, deeper-level traps are required.

It is important to note that there is a tradeoff between read/write speeds and voltages with retention time. The thicker the tunnel oxide, the longer the retention time, the lower the operating speeds and the higher the voltages required. By improving retention time through other means, such as trap level engineering, read/write voltages can be decreased and operating speeds improved by decreasing the oxide barrier. Hence, other attributes such as operating speeds and voltages are inextricably linked to retention time.

### 2.5 Optimum Nanocrystal Size

There is also a tradeoff between the reliability/memory window with the retention time/programming speed. Generally, there is a need to fabricate nanocrystals as small

as possible in order to increase memory window and to reduce stress induced leakage during retention to improve reliability.

However, when the nanocrystals decrease, retention time is degraded as quantum confinement effects become significant. Confinement effects are strongly dependent on nanocrystal diameter and scales inversely with the square of nanocrystal diameter. In addition, coulomb blockage effects of small nanocrystals decrease tunneling probabilities and reduce programming speed. Coulomb charging effects are inversely proportional to the nanocrystal diameter. The two effects are evident from Figure 2.10. Retention time degrades as nanocrystal diameter decrease from 5nm to 2nm. Also, programming time is faster for 5nm diameter nanocrystals compared to 2nm diameter nanocrystals.

Neglecting effects of stress-induced leakage, we will attempt to estimate the largest nanocrystals that satisfy the minimum memory window requirements. The larger the size of the nanocrystals, the smaller the quantum confinement and coulomb blockage effects.<sup>30-32</sup>

Figure 2.10: Retention characteristics at various tunnel oxide thicknesses and the Ge nanocrystal size on device performance<sup>30</sup>

Figure 2.11: Plot of threshold voltage shifts  $\Delta V_T$  and retention period  $\tau_r$  as a function of tunnel oxide thickness.<sup>31</sup>

Referring to Figure 2.11, for a ten year retention period, a tunnel oxide thickness of 3nm is required. This corresponds to a  $\Delta V_T$  of around 0.1V. This value can be used in the following equation

$$\Delta V_T = -R\frac{Q'}{C'},$$

where R is a factor correcting for the non uniform coverage of the area by discrete nanocrystals (assumed to be 0.4), Q' is the total charge density stored and C' is the nanocrystal-gate capacitance per unit area.<sup>32</sup> Also,

$$C'=\frac{\varepsilon}{t},$$

where  $\varepsilon$  is the dielectric constant of the interpoly silicon oxide dielectric and is given by  $3.9 \times 8.854 \times 10^{-12} F/m$  and t is the interpoly silicon oxide thickness (assumed to be 6nm).<sup>32</sup> Assuming that one nanocrystal on average stores one charge,

$$Q' = -Ne = -\frac{C' \times \Delta V_T}{R} = \frac{5.755 \times 10^{-3} \times 0.1}{0.4}$$

$$N = 9 \times 10^{15} / m^2 = 9 \times 10^{11} / cm^2$$

N is the nanocrystal density ( $N = 9 \times 10^{15} / m^2 = 9 \times 10^{11} / cm^2$ ) and e is the electronic charge given by  $1.6 \times 10^{-19} C$ .<sup>32</sup>

Figure 2.12: Nucleation curve for nanocrystal deposited by CVD on  $SiO_2$  showing the evolution of nanocrystal density and size with deposition time.<sup>33</sup>

Based on the above assumptions, the optimum nanocrystal size is 3nm. However, it must be noted that the optimum size is determined by factors such as the tunnel and interpoly oxide thickness as well as the method in which the nanocrystals are deposited (the nucleation curves for other methods of deposition, such as sputtering, may differ from that of CVD).

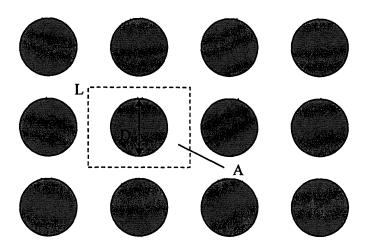

Figure 2.13: Ordered Array of Nanocrystals

If the nanocrystals are deposited in an ordered array as shown above, then

$$A = \frac{1}{N} = 1.11 \times 10^{-16} m^2$$

$$L = \sqrt{A} = 1.05 \times 10^{-8} m$$

Assuming that the spacing between the nanocrystal is equal to the nanocrystal diameter, then

$$D = \frac{L}{2} = 5.27 \times 10^{-9} m = 5.27 nm$$

## 2.6 Comparison of Different Nanocrystal Memories

The earliest work on quantum-dot Flash memories concentrated on nanocrystalline silicon (nc Si) as a replacement for the floating gate. Since then, numerous groups have proposed using nanocrystalline germanium (nc Ge) and metal dots such as Au, Ag, W, Pt, and Sn <sup>9-13</sup>. The main advantages of using metal nanodots include a higher density of states around the Fermi Level, making them more immune to Fermi Level fluctuations caused by contamination and ensuring tighter threshold voltage control, and the creation of an asymmetrical barrier by engineering the work function and thus inducing a smaller barrier for writing and a larger barrier for retention. The potential well of the metal nanocrystals can be carefully engineered to yield a small barrier for writing and a large barrier for retention. The use of different types of metal nanocrystals with different work functions opens the possibility of changing the barrier height by 2eV.<sup>9</sup> However, the introduction of metal nanodots to current silicon processing technology is a great challenge. It is well known that the presence of contaminants vastly affects the performance of the transistor and an in-depth feasibility study needs to be undertaken before metal nanodots can be introduced to the baseline CMOS process. <sup>10</sup> Also, most of the advantages of metal nanocrystals revolve around improving the retention time. This can be achieved through other means using semiconductor nanocrystal memories also as highlighted above.

There are no in-depth experimental studies comparing the performance of silicon and germanium nanocrystal memory devices. However, researchers have pointed out some theoretical advantages of Ge nanocrystals over Si. Ge has a smaller bandgap

49

compared to Si, which results in a higher confinement barrier for retention similar to metal nanocrystals.<sup>34</sup> Retention time could also be improved, especially if electrons detrap by Process 1+3 as highlighted above.

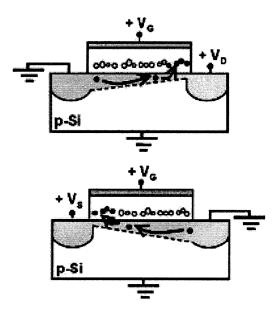

#### 2.7 Hetero-nanocrystal Memory

A novel MOSFET memory storage cell using Ge/Si hetero-nanocrystals has been proposed<sup>35</sup>. Simulation results show that the hetero-nanocrystals have superior charge retention capability compared to Ge and Si nanocrystals alone. Ge has a smaller bandgap than Si and by introducing a Si interface around the nanocrystal, it would create an additional barrier height at the Ge/Si interface which makes it harder for electrons to leak out. A staircase potential well is created and charges will have to pass through both the potential barrier of Si nanocrystal and the tunnel barrier before it can leak out. During writing and erasing, the movement of charges is mainly affected by only the potential barrier of the tunnel oxide under the proper bias. Hence, the retention time could be prolonged remarkably while the writing and erasing time could be held to be approximately the same order of magnitude.<sup>35</sup>

Figure 2.14: (Left) The schematic cross sectional of Ge/Si heteronanocrystal memory half cell. (Right) The valence band diagram for (a) hole writing (b) retention and (c) erasing. It is the effect of the compound barrier that prolongs the retention time of device evidently.<sup>35</sup>

Two ways in which heteronanocrystal memories can be fabricated are: (1) using porous alumina and (2) using diblock copolymers.

,

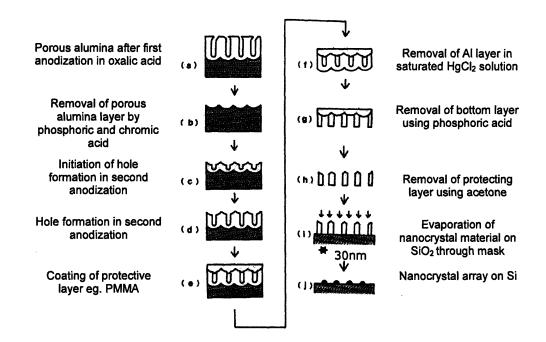

Fig 2.15: Fabrication of ordered nanocrystal array using porous alumina using a two step anodization process. The first anodization serves as a template for ordered hole formation in the second anodization.<sup>36</sup>

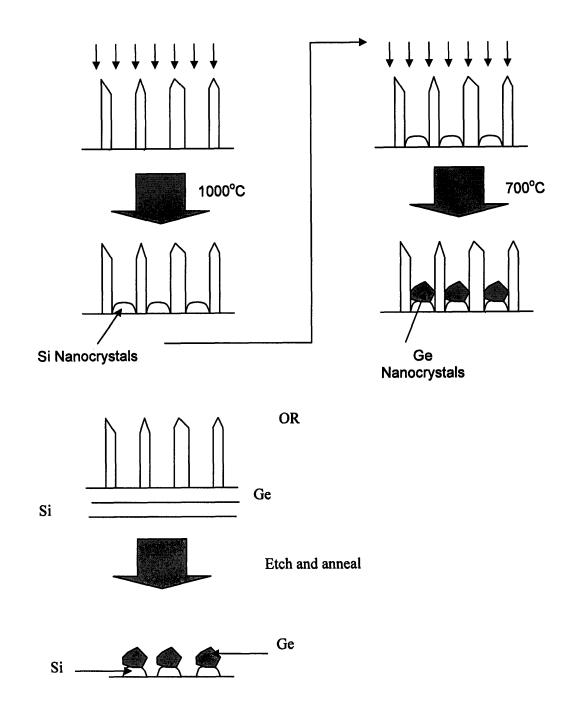

Fig 2.16: Formation of heteronanocrystals using porous alumina.

Fig. 2.15 illustrates one of the methods for fabricating porous alumina membranes. The fabricated alumina membrane can then be used for the ordered

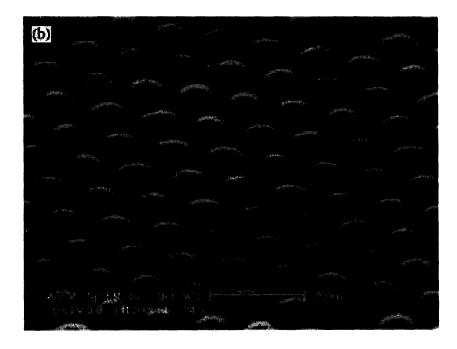

deposition of heteronanocrystals or serve as masks for etching as shown in Figure 2.16. Experiments carried out using Ge nanodots show a highly ordered array.<sup>37</sup>

Figure 2.17: High magnification view of Ge nanodot array fabricated using alumina membrane.<sup>37</sup>

Diblock copolymers have been used for the ordered deposition of Si nanocrystals.<sup>38</sup> It is likely that these could be extended to heteronanocrystals.

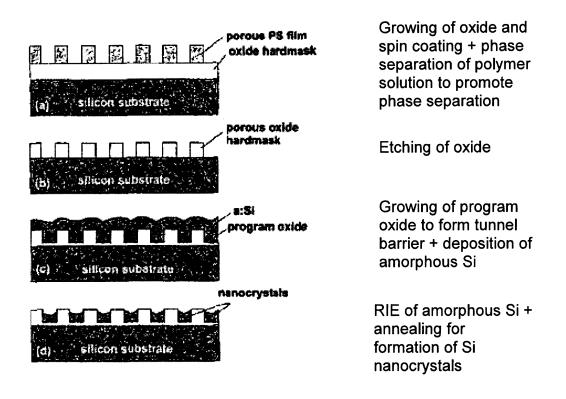

Figure 2.18: Ordered formation of silicon nanocrystals using diblock copolymers.<sup>38</sup>

Figure 2.19: Schematic for formation of vertical blocks of polystyrene.<sup>39</sup>

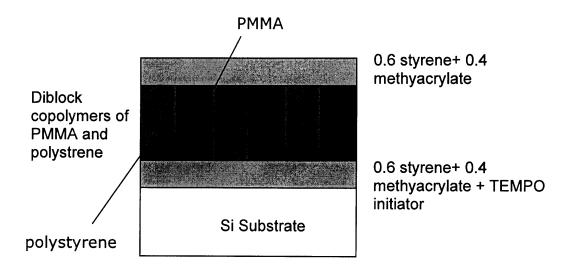

In order to form vertical blocks of polystyrene, a copolymer solution comprised of 0.6 styrene and 0.4 methylacrylate is first coated onto the silicon substrate and on top of the copolymers. At this proportion, the interfacial energy of styrene and the solution is equal to the interfacial energy of polymethylacrylate (PMMA) and the solution, resulting in vertical columns of styrene and methyacrylate being self assembled. If the copolymer solution is not applied, methylacrylate will preferentially wet the surface over styrene and horizontal blocks will result. If the top surface is not coated, an inverted 'U' shape, as shown in Fig 2.21, will develop.

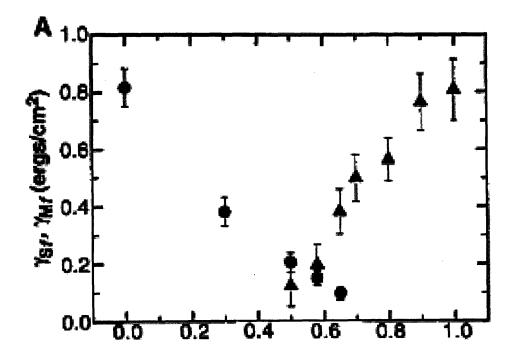

Figure 2.20: Interfacial energies  $\gamma_{Sf}$  and  $\gamma_{Mf}$  as a function of f.  $\gamma_{Sf} = \gamma_{Mf}$  at  $f \sim 0.6$  (0.6 styrene and 0.4 PMMA).<sup>40</sup>

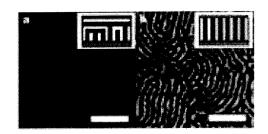

Figure 2.21: Atomic force microscopic phase images. Images are from thin films of P(S-b-MMA) symmetric diblock copolymer with a random copolymer anchored either a) to the substrate only or b) to the substate and air surface. Insets indicate the orientation of the lamellar morphology.<sup>41</sup>

The TEMPO initiator shown in Fig. 2.19 binds the polymer solution to the silicon oxide through –OH functional groups on the TEMP initiator. The polystyrene film can then function as masks for deposition or etching as indicated in Figure 2.16.

# 2.8 Comparison between NC Memory and other Flash Replacement Technologies

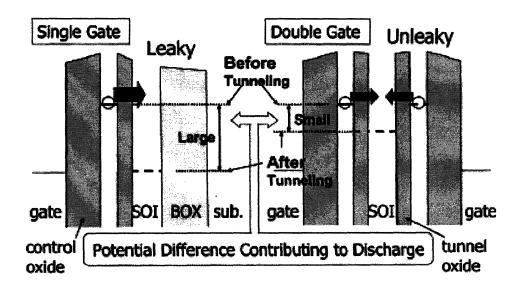

In the International Technology Roadmap for Semiconductors (ITRS) 2006 Update, the predictions for cell sizes of the different memory technologies are as illustrated in figure 2.22. At the 80nm technology node, MRAM is ~16 times the cell size and FRAM is ~12 times the cell size of Flash Memory. In the near future, Flash and the closely related SONOS memories are still expected to have the highest chip densities. A flash memory /SONOS memory cell consists of only one transistor. An FRAM cell consists of a transistor and a capacitor while a MRAM cell consists of a transistor and a magnetic tunnel junction. PCRAM consists of one chalcogenide and a transistor/diode. From the ITRS, it seems like it will take some time and effort for FRAM and MRAM technologies to catch up with flash/SONOS. On the other hand, nanocrystal-based memories are expected to face fewer difficulties in scaling as the architecture is similar to conventional Flash memories. Sizes comparable or less than (due to elimination of high voltage requirement structures) conventional Flash memories are expected.

Figure 2.22: Cell Sizes of Different Memory Technology Nodes in the ITRS<sup>42</sup>

58

| Memory       | Flash-  | Flash   | FRAM        | MRAM      | PCRAM    | SONOS   | NC      |

|--------------|---------|---------|-------------|-----------|----------|---------|---------|

| Туре         | NOR     | NAND    |             |           |          |         | Memory  |

| Endurance    | 1.00E+5 | 1.00E+5 | 1.00E+13    | >3.00E+16 | 1.00E+12 | 1.00E+7 | 1.00E+7 |

| (Erase/Write | 2       |         |             |           |          |         |         |

| Cycles)      |         |         |             |           |          |         |         |

| Data         | 20      | 20      | 10          | >10       | >10      | 20      | 20      |

| Retention    |         |         |             |           |          |         |         |

| Read/        | 2/10    | 2/18    | 1.5/1.5     | 3.3/3.3   | 0.4/1    | 2/5.5   | 1/6     |

| Program      |         |         |             |           |          |         |         |

| Voltage (V)  |         |         |             |           |          |         |         |

| Read Time    | Fast    | Fast    | Fast/Medium | Fast      | Medium   | Fast    | Fast    |

| Per Bit      | ~10ns   | ~50ns   | 30-60ns     | 5-70ns    | 70ns     |         |         |

| Write Time   | Low     | Low     | Medium      | Fast      | Medium   | Low-    | Medium  |

| Per Bit      | ~2 ms   | ~0.4ms  | 30-60ns     | 5-70ns    | 100-     | Medium  | <10µs   |

|              |         |         |             |           | 500ns    | 10µs    |         |

| Erase Time   | Low     | Medium  | Medium      | Fast      | Medium   | Medium  | Low-    |

| Per Bit      | ~900 ms | ~2.0ms  | 30-60ns     | 5-70ns    | 100-     | ~1ms    | Medium  |

|              |         |         |             |           | 500ns    |         | <100ms  |

| Mask         | 11      | 11      | 2           | 3         | 5        | 4-7     | 4       |

| Adders to    |         |         |             |           |          |         |         |

| CMOS logic   |         |         |             |           |          |         |         |

| e Charge       |

|----------------|

| ling Tunneling |

|                |

| Table 2.2: Different T | ypes of Mem | ory Technologies <sup>43-5</sup> |

|------------------------|-------------|----------------------------------|

|------------------------|-------------|----------------------------------|

Table 2.2 compares some of the key attributes of nanocrystal memory with other forms of memories. Care must be taken when making comparisons as most of the emerging memories such as MRAM and nanocrystal memories are manufactured on older technology nodes compared to conventional Flash. Others such as PCRAM have not been mass manufactured at the time of writing and performances can only be compared based on research papers as well as press releases.