### A Design for an RGB LED Driver with Independent PWM Control and Fast Settling Time

by

Awo Dede O. Ashiabor

Submitted to the Department of Electrical Engineering and Computer Science

in Partial Fulfillment of the Requirements for the Degree of

Master of Engineering in Electrical Engineering and Computer Science

at the Massachusetts Institute of Technology

May, 2007 [June 1007] ©2007 Massachusetts Institute All rights reserved

| Author       | ·                |                                    |                                       |

|--------------|------------------|------------------------------------|---------------------------------------|

|              | Department of El | ectrical Engenvert                 | May 25, 2007                          |

| Contified by |                  | (                                  | • • • •                               |

| Certified by |                  | [John 7111y, Senio<br>VI-A Company | Design Engineer]<br>Thesis Supervisor |

| Certified by | <u></u>          |                                    | ·                                     |

|              |                  | ·                                  | vid Perreault]،<br>is Supervisor،     |

| Accepted by  | <u> </u>         | د<br>Professor of Elect            | Arthur C. Smith                       |

|              | Chairman         | , Department Committee c           |                                       |

|              |                  |                                    |                                       |

|              |                  |                                    |                                       |

# A Design for an RGB LED Driver with Independent PWM Control and Fast Settling Time

By Awo Dede O. Ashiabor

Submitted to the Department of Electrical Engineering and Computer Science on May 28, 2007, in partial fulfillment of the requirements for the degree of Master of Engineering in Electrical Science and Engineering.

#### Abstract

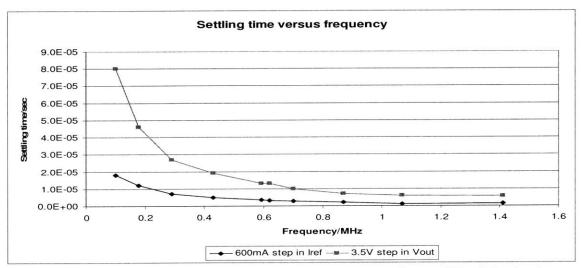

A small sized and efficient method to power RGB LEDs for use as backlights in flat panel displays is explored in this thesis. The proposed method is to drive a parallel switched connection of LEDs with a single Average Mode Controlled buck regulator. Specifications for the switching regulator and control circuitry are described. The application circuit demonstrates current settling times between  $7\mu s$  and  $30\mu s$  at a switching frequency of 290kHz. Current settling is improved at higher switching frequencies, with settling times approaching a  $2\mu s$  to  $4\mu s$  range at 1MHz switching.

M.I.T. Thesis Supervisor: Prof. David Perreault VI-A Company Thesis Supervisor: John Tilly (Linear Technology Corporation)

## **Table of Contents**

| 1.  | Introdu     | uction                                                   | 7  |

|-----|-------------|----------------------------------------------------------|----|

|     | a.          | Display Technologies of Today                            | 7  |

|     | b.          | The use of LEDs in Displays                              | 9  |

|     | с.          | About this Thesis                                        |    |

|     |             | i. Minimizing the settling time of a Multiple LED driver |    |

|     |             | ii. Other performance criteria                           |    |

|     |             | iii. Thesis Organization                                 |    |

| 2.  | Overv       | iew of Design Strategies                                 |    |

|     | a.          | Theoretical Solutions                                    |    |

|     | b.          | Commercial Solutions                                     |    |

| 3.  | Syster      | ns and Specifications                                    | 28 |

| 4.  | Desig       | n and Simulation                                         |    |

|     | a.          | Average Current Mode Controlled LED Driver               |    |

|     | b.          | Improvements to ACMC Controlled LED Driver               |    |

|     | с.          | Modeling of External Components                          |    |

| -   | d.          |                                                          |    |

| 5.  |             | g                                                        |    |

|     | a.          |                                                          |    |

|     |             | i. Settling time                                         |    |

|     | 1           | ii. Efficiency                                           |    |

|     | D.          | Performance on Breadboard                                |    |

|     |             | i. Settling time                                         |    |

|     | 0           | ii. Efficiency                                           |    |

| 6   |             | Solution Integration in I.C                              |    |

| 0.  | conci<br>a. | Summary                                                  |    |

|     | a.<br>b.    | •                                                        |    |

|     | о.<br>С.    | Future Work                                              |    |

|     | с.<br>d.    | Acknowledgements                                         |    |

| 7.  |             | pgraphy                                                  |    |

| 8.  |             | idix I                                                   |    |

| 9.  |             | ndix II                                                  |    |

|     |             | ndix III                                                 |    |

| - 0 | rr••        |                                                          |    |

# **Table of Figures**

| <b>1.1:</b> DLP incorporating the fast current settling multiple LED driver                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------|

| <b>1.2:</b> Fast settling output current allows faster frequency, a higher refresh rate and better contrast pictures on DLP screen            |

| <b>1.3:</b> Traditional Multiple LED driver has distinct drivers encapsulated into one chip7                                                  |

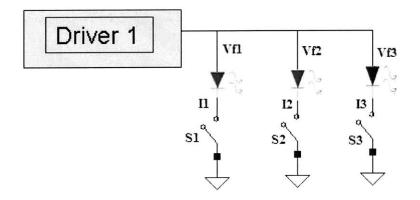

| 1.4: Proposed Multiple LED driver with one output port serving multiple LEDs7                                                                 |

| <b>2.1:</b> Proposed Multiple LED driver with one output port serving multiple LEDs9                                                          |

| <b>2.2:</b> 2-phase Buck converter                                                                                                            |

| <b>2.3:</b> Waveforms of the 2-phase Buck converter                                                                                           |

| 2.4: Basic structure and operation of FRDB converter                                                                                          |

| <b>2.5:</b> Average Current Mode buck regulator15                                                                                             |

| <b>2.6:</b> The principal difference between this current mode regulator and the voltage mode circuit is in the source of the modulating ramp |

| 2.7: LEDs driven by separate converters                                                                                                       |

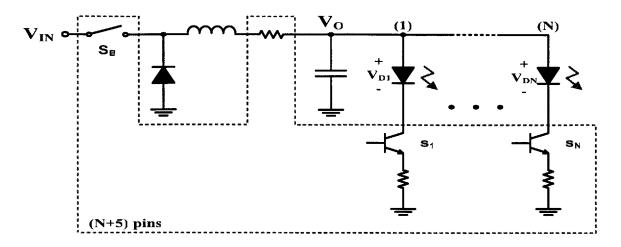

| <b>2.8:</b> Parallel topology20                                                                                                               |

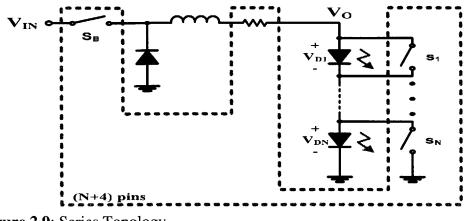

| <b>2.9:</b> Series Topology                                                                                                                   |

| <b>3.1:</b> Multiple LED driver                                                                                                               |

| 4.1a: Schematic of Average Current Mode Controlled LED Driver                                                                                 |

| <b>4.1b:</b> Block diagram describing system during a reference current step                                                                  |

| <b>4.1c:</b> Block diagram describing system during a load step                                                                               |

| <b>4.2:</b> Transfer function of PWM comparator                                                                                               |

| <b>4.3</b> : Bode plot of open-loop buck and ACMC compensated open-loop gain30                                                                |

| <b>4.4</b> : LED current settles to 5% of final value in 7µs in response to a reference current step                                          |

| <b>4.5</b> : Transient response to a step in output current. Output current settles within 27µs to 5% of final value                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>4.6:</b> For a 2.4A step in output current, settling time is 80µs32                                                                                                                                      |

| <b>4.7:</b> The critical inductance design scheme keeps the small signal settling time at $7\mu$ s 34                                                                                                       |

| <b>4.8:</b> After applying the critical inductance technique, the settling time for large output reference current steps improves from 80µs to 73µs                                                         |

| <b>4.9</b> After applying the critical inductance rule, the output current settling time stays at 27µs                                                                                                      |

| <b>4.10:</b> The anti-windup circuit reduces large reference current step settling time from 73µs to 22µs                                                                                                   |

| <b>4.11:</b> Slowly ramping up the reference current also reduces settling time from 73µs to 24µs                                                                                                           |

| <b>4.12:</b> For a 2.4A reference current step, reducing output inductor to 20µH lowers the settling time further to 17µs                                                                                   |

| <b>4.13</b> : Switching at 1MHz results in a 2µs settling time for a 600mA step in reference current                                                                                                        |

| <b>4.14:</b> And for a 2.4A step in reference current, settling time is 4µs42                                                                                                                               |

| <b>4.15</b> : At 1MHz switching, output current settling time is 7µs43                                                                                                                                      |

| <b>5.1:</b> PCB board of initial design                                                                                                                                                                     |

| <b>5.2:</b> Full circuit schematic of the prototype system                                                                                                                                                  |

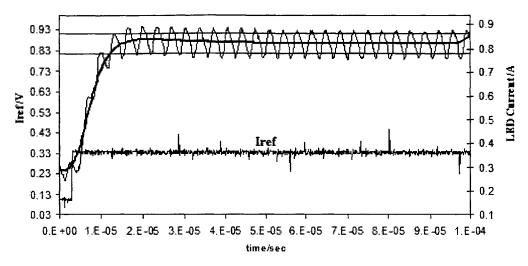

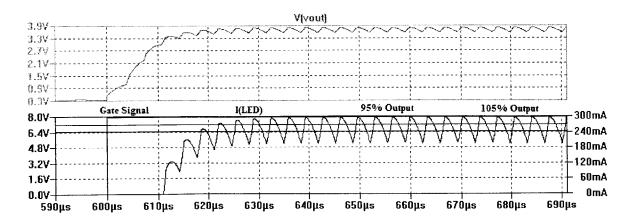

| <b>5.3:</b> The large ripple on the output current makes it difficult to spot the 5% settling time. After smoothing output current with a moving average, settling time is easily read off plot as $9\mu$ s |

| 5.4: RGB LEDs produce a white color                                                                                                                                                                         |

| 5.5: RGB LEDs produce a green color                                                                                                                                                                         |

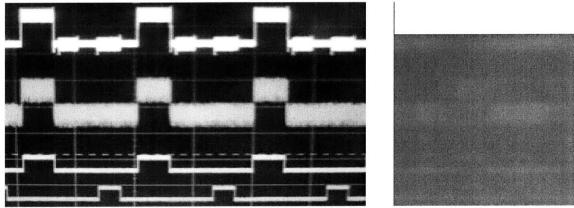

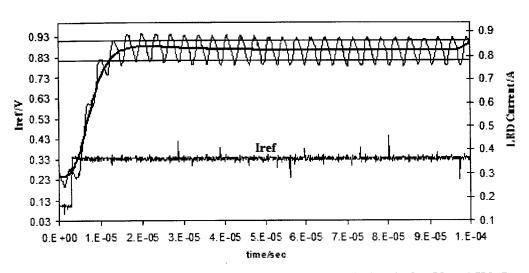

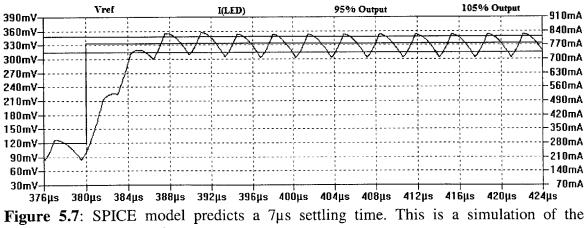

| <b>5.6</b> : Transient performance of breadboard circuit for a reference current step55                                                                                                                     |

| 5.7: SPICE simulation of experiment of Figure 5.655                                                                                                                                                         |

| 5.8: Breadboard circuit yields a 30µs load step settling time                                                                                                                                               |

| <b>5.9</b> : SPICE simulation of experiment of Figure 5.856                               |

|-------------------------------------------------------------------------------------------|

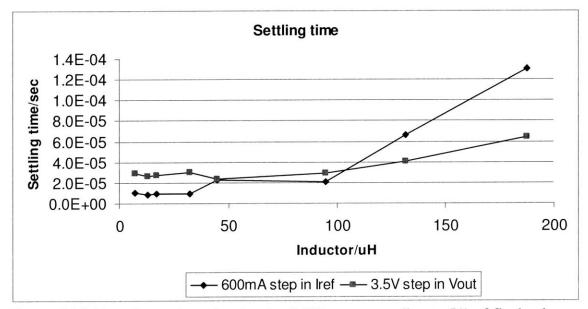

| 5.10: Experimental results showing LED current settling time versus inductor size57       |

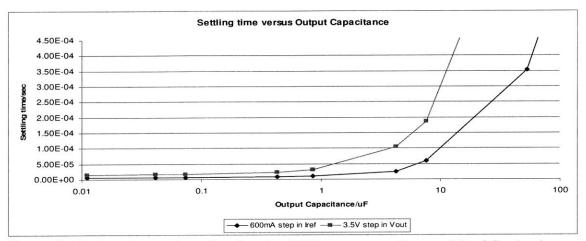

| 5.11: Experimental results showing LED current settling time versus output capacitor size |

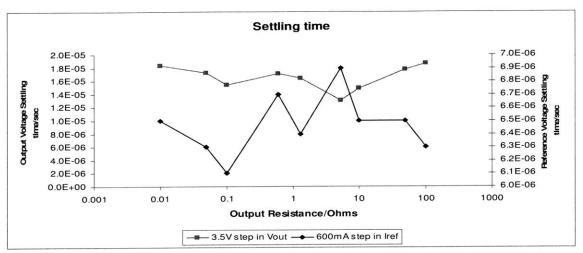

| 5.12: Experimental results showing LED current settling time vs output resistor size60    |

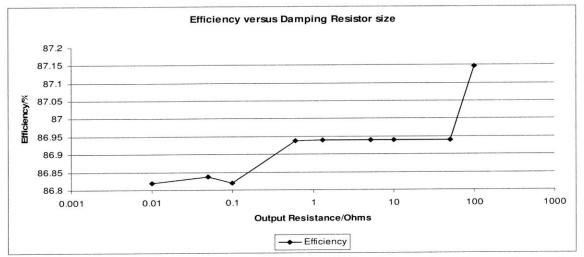

| 5.13: Experimental results showing efficiency versus output resistor size60               |

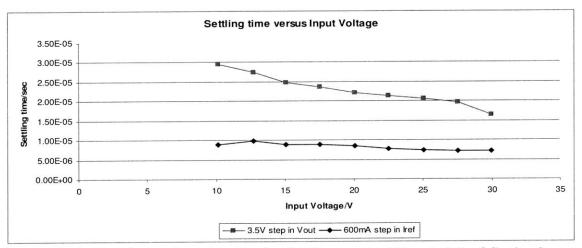

| 5.14: Experimental results showing LED current settling time versus input voltage61       |

| <b>5.15:</b> Experimental results showing LED current settling time vs frequency62        |

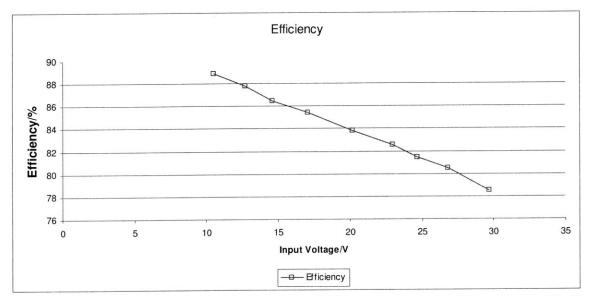

| <b>5.16:</b> Experimental results showing efficiency vs. input voltage                    |

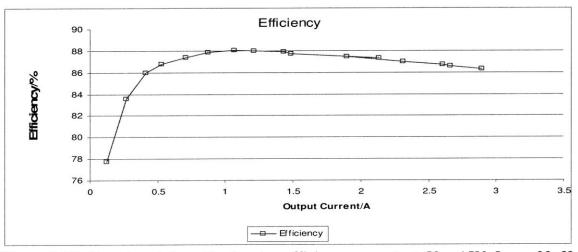

| <b>5.17:</b> Experimental results showing efficiency versus output current                |

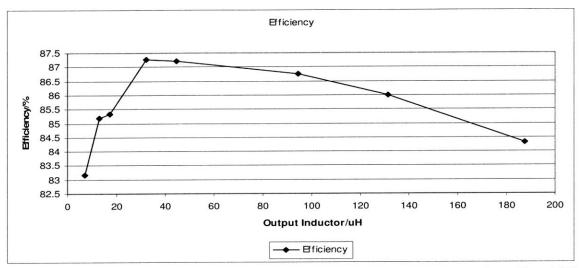

| <b>5.18</b> : Experimental results showing efficiency vs inductor size                    |

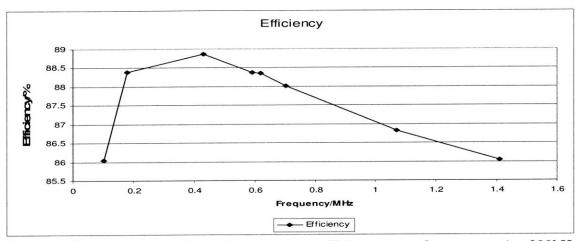

| <b>5.19:</b> Experimental results showing efficiency vs frequency                         |

# **List of Tables**

| 2.1: Tradeoffs of Theoretical solutions           | 18 |

|---------------------------------------------------|----|

| <b>2.2:</b> Tradeoffs of commercial solutions     | 21 |

| 3.1: Specifications for Multiple LED Driver       | 23 |

| 4.1: Summary of design choices and settling times | 44 |

| 5.1: Prototype operating parameters               | 51 |

| 5.2: Specifications for Multiple LED Driver       | 53 |

# **Chapter 1 - Introduction**

#### a. Display Technologies of Today

Flat panel televisions are no longer a luxury item. Today, the average television store can boast of an eclectic stock of High Definition (HD) televisions, Liquid Crystal Display (LCD) televisions, Plasma Screen televisions and Digital Light Processing (DLP) televisions, to name a few. Sales of flat screen TVs alone hit a \$17 billion figure in 2005, and are projected to continue on an upward trend. This boom in the television business is only a microcosm of a greater innovation in the display industry. Besides TV sets, we enjoy very fine, life-like pictures off minute screens in PDAs, cell phones and other tiny consumer portables. These novel displays are expected to permeate business areas too; there is good reason to believe that medical imaging devices will be upgraded to these sharper displays, and so will computers, spectroscopes, microscopes, 3-D visual displays, holographic storage devices, and professional photographic devices.

The new display technologies make up for the deficiencies of CRT technology such as its bulkiness and poor contrast in large screens. These innovative screens also deliver digital television which CRT cannot provide. Though the new screens are all improvements to the CRT screen, they each have their own setbacks, and as a result, it is still early to select one technology as the overall best. That is why we still see many types of flat screens on the market. We discuss a number of these screen technologies below. Thin, lightweight and silent, LCD screens run on low power and provide good text contrast. They also offer a wide viewing angle and low electromagnetic radiation. What's more, since 1999, the prices of LCD sets have been declining steadily, largely, as a result of improvement in the LCD manufacturing process. The negative aspects of LCD technology include poor image contrast. LCD technology cannot create rich black colors. Its inherent fixed resolution, limited peak brightness, caused by the fixed brightness of the backlight, and its notorious motion blur makes the viewing experience less than heavenly. The size-cost ratio unfortunately remains prohibitively high, even though this ratio is on a downward trend.

Plasma screens also have many advantages comparable to the LCD: wide viewing angle, as well as a flat and compact shape. Moreover, there is no flicker effect<sup>1</sup> in plasma screens. Additionally, its architecture has no need for a backlight or a projection of any kind, making for very thin (albeit heavy) devices. Plasma screens also emit rich colors that the LCD screens cannot match. That said, they do not come cheap.

The advantages of DLP technology include its light weight, high gamut of color, and excellent contrast ratios. Unfortunately, DLP screens require at least 12" - 24" depth. This renders the monitors bulky. Furthermore, in single chip DLP systems, there is the potential of having the "Rainbow Effect". This problem is unique to DLP. A rainbow forms briefly in the viewer's peripheral vision. It occurs when viewers rapidly shift their focus from a very bright area to a dark area.

<sup>&</sup>lt;sup>1</sup> Flicker is visible fading between image frames displayed on cathode ray tube (CRT) based monitor.

#### The use of LEDs in Displays

It is reported that replacing the fluorescent backlight with LEDs corrects the "rainbow effect" in DLP TVs [1]. Other screen manufacturers like Samsung and Acer are also installing LEDs as backlights in LCD screens, to improve (dynamic) contrast ratios and thereby enrich color production. Compared to CCFL backlit LCDs, LCD panels with LED backlights can easily be divided into subsections. The brightness of each subsection is controlled independently to produce many levels of brightness and with it, a high contrast ratio. LEDs also eliminate the warm-up time and color instability of screens since they have an instant turn-on. An additional advantage to consumers is that LEDs have longevity.

#### **b.** About this Thesis

## i. Minimizing the settling time of a Multiple LED driver

The intention here is to design a compact and cheap way to drive LEDs for use in flat panel displays. The key feature of this compact, cheap LED driver is its fast current settling. Allow me to explain why this property is important.

If one could develop a single affordable and small-size LED driver that could drive many types of LEDs, i.e. LEDs of different current ratings and forward voltages, one could eliminate many LED drivers in the display, replacing them with a single circuit that switches among several LEDs. In order for this multiple LED driver to be useful, the output current must settle to its nominal value quickly. There is no point in using a multiple LED driver if the current settles slowly. This is because the colors of the different LEDs will reach the requisite hue slowly. If the colors settle slowly such that we have to cycle through these LEDs at a frequency lower than 100Hz, the eye will be unable to blend the distinct colors. The ability to blend colors to form a wider spectrum of colors is lost. Evidently such an LED driver is inappropriate for lighting applications.

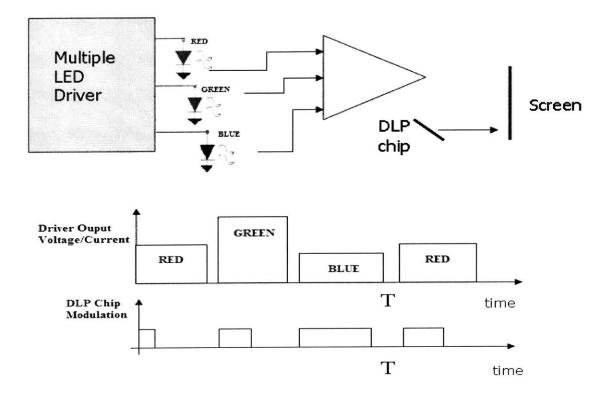

In the DLP screen for example, a driver could drive RGB LEDs in the backlight. In a given cycle (at a frequency higher than a 100Hz), the driver turns on the red LED for 30% of the time, the green LED for another 30% and the blue LED another 30%. Because the red, green and blue LEDs may require different forward voltages and current, our multiple fast settling LED driver must reset its output current and voltage quickly each time we switch between the LEDs. See Figure 1.1. When the red, green and blue lights reach the DLP chip, they are pulse-width modulated. The red light may hit the DLP chip first and is reflected onto the screen for the required amount of time to illuminate the right amount of red light. The green light may hit the DLP chip next and may be reflected for a different duration. If the red color is reflected onto the screen longest, the resultant color appears reddish, if the blue light is reflected for the longest duration within a cycle, the resultant color appears bluish, and so on.

**Figure 1.1:** DLP incorporating the fast-current-settling multiple LED driver. Output voltage and output current are reset whenever we shift between LEDs. In the first cycle, a dominant bluish color is produced.

This technology is suitable only if the RGB currents settle fast, otherwise as Figure 1.2 depicts, we cannot cycle through the three primary colors at a rate faster than a 100Hz. The human eye will see the distinct red, green and blue colors, rather than one integrated color [2].

Figure 1.2: Fast settling output current allows faster frequency, a higher refresh rate and better contrast pictures on DLP screen.

The benefits of using our small-size inexpensive multiple LED driver in DLP screens are plentiful. First, we eliminate the color wheel and all the mechanical circuitry involved in combining color. We shrink the size of the DLP screen as a consequence. We can also guarantee a longer life for the screen due to the longevity of LEDs. The screen runs on lower power because one, LEDs are more efficient than white lamps and two, because we eliminate the color wheel. The color wheel in DLP TV wastes a lot of energy in its operation. To create non-white colors, it filters out the unwanted color components of the white light. The light components that are filtered out are wasted in the form of heat energy. Also, if the output current settles very quickly, we can cycle through the LEDs at a frequency much higher than 100Hz. DLP manufacturers claim that there are many advantages associated with operating at higher frequencies [3]. That is why we place enormous emphasis on the fast current settling characteristic of our multiple LED driver.

## ii. Other performance criteria

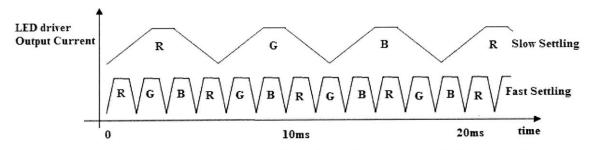

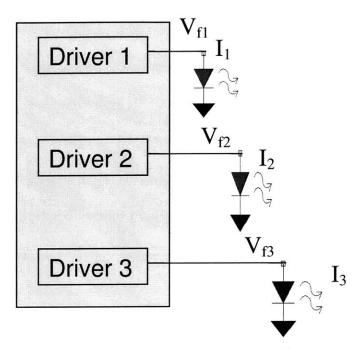

Traditionally, what we term as a multiple LED driver is in fact several distinct LED drivers packaged into one chip. This multiple driver is characterized by several distinct output ports illustrated by Figure 1.3. The idea is that if we could create a real multiple driver, that is, a driver with one output port serving multiple LEDs, we size down the LED driver and possibly its cost by a great margin. Compare the traditional multiple LED driver in Figure 1.3 to the proposed multiple LED driver of Figure 1.4.

Figure 1.3: Traditional Multiple LED driver has distinct drivers encapsulated into one chip.

Figure 1.4: Proposed Multiple LED driver with one output port serving multiple LEDs.

In addition to a smaller sized solution, we seek a driver that is efficient and beats the efficiency or at least matches the efficiency of existing lighting solutions. The more efficient the system, the less costly it is to operate, since it expends less energy. The efficiency of the system also impacts the size of the solution. A grossly inefficient

lighting system will demand larger heat sinks and will make the screen very bulky and unattractive for use in flat panel displays.

We see this fast current settling multiple LED driver playing a major role in all applications that require fast settling multiple output currents. Its use is not limited to display applications.

### iii. Thesis organization

Chapter 2 of this thesis presents an overview of several design strategies and considerations for multiple LED drivers.

Chapter 3 presents the specifications of the multiple LED driver.

Chapter 4 is a rigorous discussion of the design selected for the implementation of the multiple LED driver.

Chapter 5 describes methods used to test a prototype built from discrete components and presents a summary of the results obtained on the bench.

Chapter 6 summarizes the concepts learned from this thesis and proposes future work.

Chapter 7 is a bibliography of references cited in this thesis

Appendix I contains the circuit description in SPICE.

Appendix II contains the MATLAB code used to simulate the circuit.

Appendix III contains the PCB board layout of the prototype and the Bill of Materials.

## **Chapter 2- Overview of Design Approaches**

#### a. Theoretical Solutions

There are a number of recommendations pertaining to fast transient DC/DC converters which apply to the design of the multiple LED driver of Figure 1.4, repeated here as Figure 2.1. In recent years, some designers have proposed means of increasing the bandwidth of the systems and some have even proposed changing the inherent topologies of the converters. We discuss a few of these schemes: switching at higher frequencies, multi-phase converters, the fast response double buck converter (FRDB), the average current mode control scheme and the peak current mode control method. In the next few pages, we examine each proposition closely to select the most suitable scheme for the work at hand - a compact and efficient fast current multiple LED driver.

Figure 2.1: Proposed Multiple LED driver with one output port serving multiple LEDs.

#### Switching at higher frequencies

A high switching frequency means that the control loop of the system is able to correct errors more rapidly. The output current as a result will settle to the correct value quickly. Another benefit of switching at a higher frequency is a reduction in the output ripple. This means that one can get away with smaller and inexpensive filtering devices at the output node. Indeed, these advantages do not come at zero cost. Higher switching frequencies cost efficiency. Since some components' switch power loss are proportional to frequency, higher switching frequency translates to higher power losses. Also, when one switches at a higher frequency, one runs into noise coupling issues and the layout design is greatly complicated.

#### **Multi-phase converters**

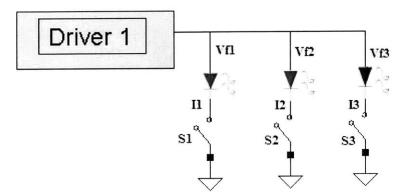

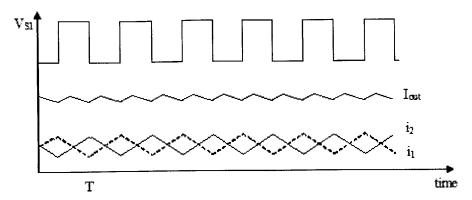

Multi-phase converters work by interleaving more than one distinct converter operating out of phase with each other [4], [5]. The purpose is to reduce ripple on the output without using massive filtering elements at the output stage, which slow down the settling of the output current. By avoiding big inductors and capacitors, the output responds more quickly to changes in the system than it would otherwise. Multi-phase converters produce low output ripple and fast settling current. It is for among these reasons that the multi-phase synchronous buck converter has become the dominant topology for microprocessors [6]. Figure 2.2 below shows a two-phase buck converter.

Figure 2.2: 2-phase synchronous buck converter. Adapted from [7].

Consider the two-phase converter of Figure 2.2. Assuming that the size of the inductors L1 and L2 are the same, and that the gate signals  $VS_1$  and  $VS_2$  are exactly 180 degrees out of phase, and that the system is operating near 50% duty cycle, the current through L1 and L2 will resemble that drawn in Figure 2.3. As shown in the picture, the resultant output current has only small ripple, with a fundamental frequency of twice the switching frequency of each power stage. For constant total energy storage, interleaving N stages reduces ripple current by a factor greater or equal to N and increases fundamental ripple frequency by a factor of N [4], [5].

Figure 2.3: Waveforms of the 2-phase synchronous buck converter.

This implies in turn that the designer can generate an output current having a given ripple with reduced inductors and capacitors as compared to a single power stage. Moreover, because the individual inductors are small, one can slew the operating current quickly compared to a single buck converter with the same ripple current. Additionally, because we now have essentially two buck stages, we spread the power consumption across more converters. This distribution allows the chip to withstand larger total power consumption.

One problem with the multi-phase converters is that we add another layer of complication. That is to say, we have to carefully synchronize the gate signals to avoid an open at the input, significant delays, and uneven power sharing [8]. Our layout is also made complex. In this thesis, we focus on a single-phase design, but recognize that a multi-phase approach may be valuable in some applications.

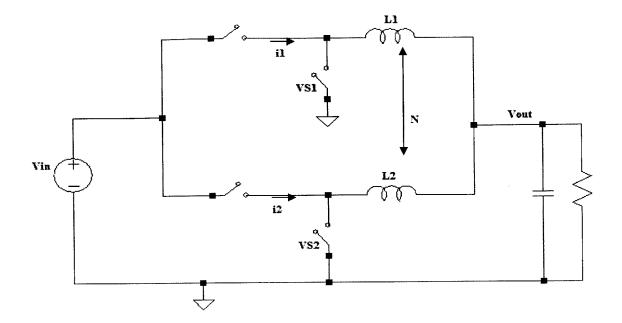

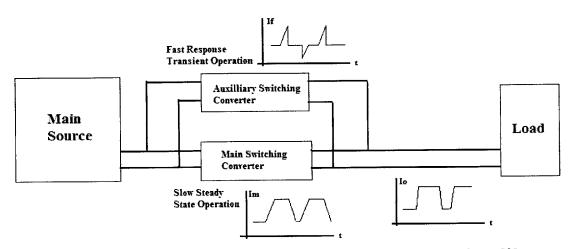

#### Fast transient response dc/dc converter

Reference [9] considers a "Fast transient response" dc/dc converter. The fast transient response dc/dc converter is very similar to the 2-phase converter in that it employs two power stages. The difference is that while all the converter stages in a multi-phase

converter are identical, converters of the fast transient buck are not identical. The two converter stages in the "fast transient response" converter have different functionalities. The linear or main buck converter operates like a typical buck converter. The novel addition is the second "auxiliary" stage. What does it do? Because the output filter is a low pass filter, it removes all high frequency components at the output. By so doing, it limits fast transitions at the output. The purpose of the auxiliary stage is to inject extra current to speed up such transitions at the output, while maintaining low output ripple. See Figure 2.4 for a block diagram of the circuit.

Figure 2.4: Basic structure and operation of FRDB converter. Adapted from [9]

The sum of the filtered output of the buck stage plus the injected current from the nonlinear converter provides a fast transient, low ripple response at the output. In principle, if the two power stages operate independently of each other, there is no stability issue if each control loop is independently stable.

It should be recognized that the control of the auxiliary converter is not trivial. How much current should it inject or take out during a step of the output current? Since our application calls for a variable output current step, the control of the auxiliary converter must be dynamic as well – a nontrivial exploit. For reasons of complexity, this design strategy is not considered further.

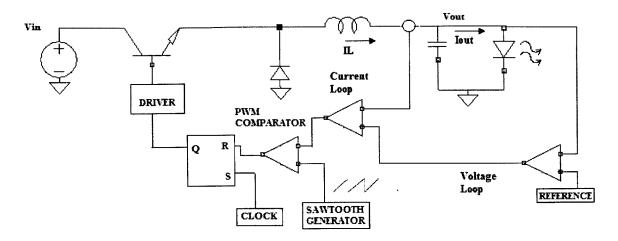

#### **Average Current Mode Control**

We have held a discussion of a few relevant topologies. Let us describe how the control scheme can influence the transient response of the driver. We first take a look at the Average Current Mode Control, (ACMC) [10]. ACMC is popular for its simple feedback technique. The control consists of two loops. There is a fast internal current feedback loop and a slower voltage feedback loop. The fast current feedback circuit measures a low-pass filtered version of the inductor current and compares it to an error signal generated by the slower voltage error amplifier. The signal from the current error amplifier is fed to a PWM comparator whose other input is a sawtooth ramp. This PWM comparator produces a pulsating signal. The duty ratio of the slowers to modulate the output power. When output current is too low, the duty ratio of the pulse increases; as a result, the converter switch stays on for a longer time period, and consequently, the output power ramps up. When output current is too high, the converse occurs. Via this feedback, the circuit maintains output voltage and current at the prescribed value.

**Figure 2.5**: In this Average Current mode buck regulator, the error signal and a modulating ramp form a pulse-width modulator, which controls the buck switch.

In order to generate fast transient responses and accurate output, the control path is made fast by proper dynamic compensation of the (current) error amplifier. By providing full state feedback (of both inductor current and capacitor voltage) better dynamics are achievable than can be obtained with a voltage feedback alone.

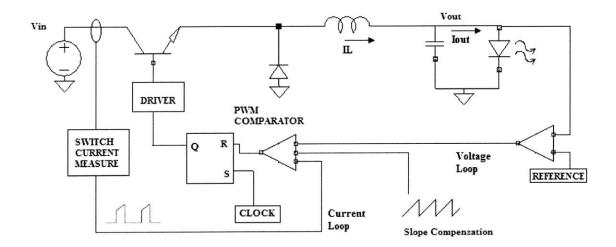

#### **Peak Current Mode Control**

Similar to ACMC, under Peak Current Mode Control (PCMC) one utilizes feedback of both inductor current and capacitor voltage to improve dynamic performance. What differentiates the two modes is the origin of the modulating ramp. Under PCMC, the modulating ramp is a signal proportional to the buck switch current, or equivalently, the inductor current. Each cycle, the switch is turned on, and then turned off when the inductor (or switch) current reaches a peak value set by the voltage loop. An additional modification is that a compensating ramp is also sometime required to prevent subharmonic oscillations [11].

Figure 2.6: The principal difference between this current mode regulator and the voltage mode circuit is in the source of the modulating ramp. Adapted from [10].

Evidently, for PCMC to run correctly, it requires an accurate yet fast measurement of the inductor current to create the modulating ramp signal. This measurement is no trivial feat. One could capture the buck switch current. The mechanism draws on the fact that when the buck switch is on, the inductor current equals the switch current. Other measurement choices include placing a sense resistor in series with the inductor, a current sense transformer across the on-resistance of the switch, or a current mirror circuit coupled to the switch. Each of these methods requires a level shift to transpose the measured signal down to the ground reference for application to the PWM comparator, since the buck regulator modulating switch is floating. None of the switch's terminals is connected to ground. The source terminal of the switch is either at the input voltage potential when the switch is on or at approximately 0.7V when off.

One perceived advantage of Average Current Mode Control over Peak Current Mode control is noise sensitivity. As the comparator is driven from the wide-bandwidth current sense, there is the potential for noise to trigger the PWM comparator. Under Average Current Mode control, only a low pass filtered version of the current is sent to the PWM comparator, providing noise immunity. Conversely, however, Peak Current Control provides "instant" pulse-by-pulse current limiting, where Average Current Mode Control does not.

Another advantage of Average Current Mode Control over Peak Current Mode Control is accuracy. Since the output current is exponentially dependent on the output voltage in the LED driver application, it is extremely important that the reference voltage setting the output voltage is precise. Furthermore, because the multiple LED driver of Figure 2.1 is designed to drive many LEDs of different forward voltages, over different currents, the output voltage is expected to step to several different values. Thus, the reference voltage must accurately predict the output voltage needed for the many LED types and output currents. In order to keep the control scheme for the driver of Figure 2.1 simple, a single (current) loop control method is considered in which one directly regulates the average output current. Both the ACMC and PCMC if used, will be stripped of its voltage loop entirely. A one (current) loop ACMC control without the voltage loop, still regulates the average output current with remarkable accuracy. However, PCMC without its voltage loop, regulates the *peak* output current. Additional circuitry needs to be added to remove the peak to average current error. This supplementary circuit further complicates the PCMC control circuitry.

#### **Table summarizing tradeoffs**

| Property\Topology           | Multi-phase                                 | FRDB     |

|-----------------------------|---------------------------------------------|----------|

| Transient Response          | Fast                                        | Fast     |

| Efficiency                  | Moderate                                    | Moderate |

| Ripple Current              | Depends on number of phases and duty cycle. | Low      |

| External<br>Component count | High                                        | High     |

| Die size                    | Big                                         | Big      |

| Total cost                  | High                                        | High     |

| Property\Control  | ACMC without voltage loop | PCMC without voltage loop |

|-------------------|---------------------------|---------------------------|

| Transient         | Fast                      | Fast                      |

| Response          |                           |                           |

| Noise sensitivity | Low                       | High                      |

| Accuracy          | High                      | Low                       |

Table 2.1: Tradeoffs of theoretical solutions.

Considering our evaluation of the solutions at hand, it appears that the most likely successful candidate is a single synchronous buck power stage employing average current mode control. The reason behind this choice is that a single buck power stage will enable the basic approach to be tested out with the greatest simplicity. This could be extended (e.g. to a multiphase interleaved design) later if higher performance is deemed necessary. ACMC provides the best combination of precision, fast transient response and low noise.

### **b.** Commercial Solutions

Here are some examples of ways that manufacturers design power converters to generate multiple fast settling currents.

#### Separate topology

One solution in industry is to drive the individual LEDs with separate converters from one power supply. There are n converters for n LEDs. Each converter provides the right amount of current to its corresponding LED. This topology does not demand fast settling currents, since the LEDs are on the entire time that the driver is on. The problem with this solution is that the size of the die is large and numerous inductors are required. Consequently, it is an expensive solution.

Figure 2.7: LEDs driven by separate converters.

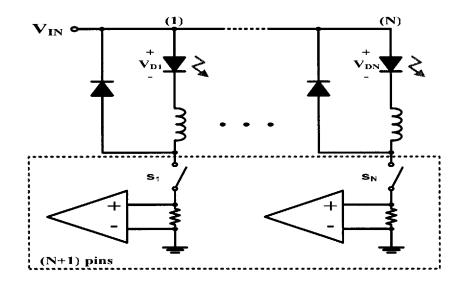

#### **Parallel topology**

Here, one buck stage serves one distinct output node connected to multiple LEDs. The output voltage is modulated, but the different currents are set by the resistors added onto the LED strings. The resistor size controls the voltage across the LED, and by so doing, it fixes the LED current.

Figure 2.8: Parallel topology

Gate signals sent to switches  $S_1$  through to Sn turn the LEDs on and off almost instantaneously. Because the parallel topology uses fewer elements than the separate topology, it is a much smaller and less costly solution. It is moderately efficient. The power wasted by the resistor ballasts aggregate to a significant sum that raises concern.

#### Series topology

Like the parallel topology, the series topology has one main converter stage. However unlike in Figure 2.8, the LEDs are connected in series. There are n switches. Each is connected in parallel with one LED. When a switch turns on, the diode is shorted out and is turned off. One big challenge here is the switch implementation. It will require level shifting since only one switch is referenced to ground. All the others are referenced to a varying voltage. Even though the die size appears smaller than that of the separate topology, the complicated switching circuitry increases the die size considerably, and renders the series topology expensive and large. It is relatively efficient because no power is wasted through ballast resistors. Unfortunately, the current running through any two LEDs cannot be different.

Figure 2.9: Series Topology.

#### **Table summarizing tradeoffs**

|                    | Separate Topology | Parallel Topology | Series Topology  |

|--------------------|-------------------|-------------------|------------------|

| Transient Response | Fast              | Fast              | Moderate         |

| Efficiency         | High              | Moderate          | High             |

| External Component | High              | Low               | Moderate         |

| Count              |                   |                   |                  |

| Die size           | Control big       | Control small     | Control moderate |

|                    | Switch small      | Switch big        | Switch big       |

| Total cost         | High              | Low               | Moderate         |

| Individual LED     | Yes               | Yes               | No               |

| Current Adjustable |                   |                   |                  |

Table 2.2: Tradeoffs of commercial solutions.

The parallel topology appears to be the best suited to our purpose.

In conclusion, an ACMC approach with a parallel topology without the ballasted current sources may best answer our quest. A one loop, current loop ACMC will be used. This is because we expect the output voltage to vary a lot as we switch between several LEDs and also vary the output current. This makes it difficult to pin an output reference voltage for the voltage loop.

# **Chapter 3 - Systems and Specifications**

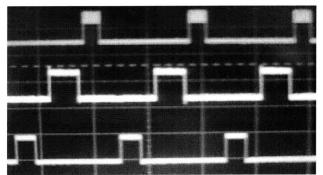

Given the tradeoffs described in the preceding chapter, the best compromise between speed, size, cost and efficiency is to operate a single central control switch with one output node that sources several LEDs. These LEDs will be individually controlled with separate pulse signals (PWM). Since the different LEDs may require different DC output currents, the reference voltage that sets the output current will be pulsed to different voltages any time we switch between LEDs. The control circuit will adopt the single current loop Average Current Mode Control, which we shall loosely refer to as the Average Current Mode Control (ACMC).

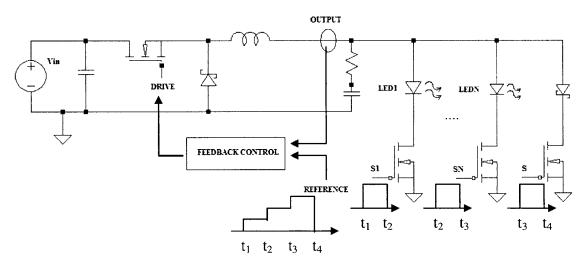

Figure 3.1: Multiple LED driver

The gate signals S1 to SN and S do not have significant overlap. However, because they are being switched at a very fast frequency, the eye averages the independent colors into one color. Signal S turns on the Schottky when none of the LEDs are on. By using a Schottky we waste less power during the turn off time at the output because the Schottky

has a low forward voltage. (One could select a different device or just use a "shorting" fet to tradeoff loss for output voltage deviation.)

Below is a set of practical electrical operating conditions at which we expect the multiple LED driver to meet. These requirements are based on commercial requests.

| PARAMETER             | MIN  | TYP | MAX  | UNITS |

|-----------------------|------|-----|------|-------|

| Input Voltage         | 10   | 15  | 30   | V     |

| Settling time         | 1    | 10  | 30   | μs    |

| Switching Frequency   | 0.15 | 0.6 | 2    | MHz   |

| Switch Duty Cycle     | 0    |     | 95   | %     |

| Output Current        | 0    |     | 3    | A     |

| Output Current ripple |      |     | 150  | mA    |

| Output regulation     |      | 1   | 4    | %     |

| Quiescent Current     |      | 5   | 6    | mA    |

| Reference Voltage     | 0    |     | 1.25 | V     |

| Efficiency            | 85   | 92  |      | %     |

## **Multiple LED Driver**

Figure 3.2: Specifications for Multiple LED Driver

# **Chapter 4 - Design and Simulation**

Because of time constraints, the circuit is designed and implemented using discrete components instead of in an integrated circuit. There is good reason to believe that the results obtained from the breadboard will provide great insight into a design on transistor level. This section explores how to achieve fast settling time with an ACMC controlled multiple LED driver based on a synchronous buck. Some suggestions to improve the settling time are also presented. This is followed by a discussion on the limitations of these design choices.

#### a. Average Current Mode Controlled LED Driver

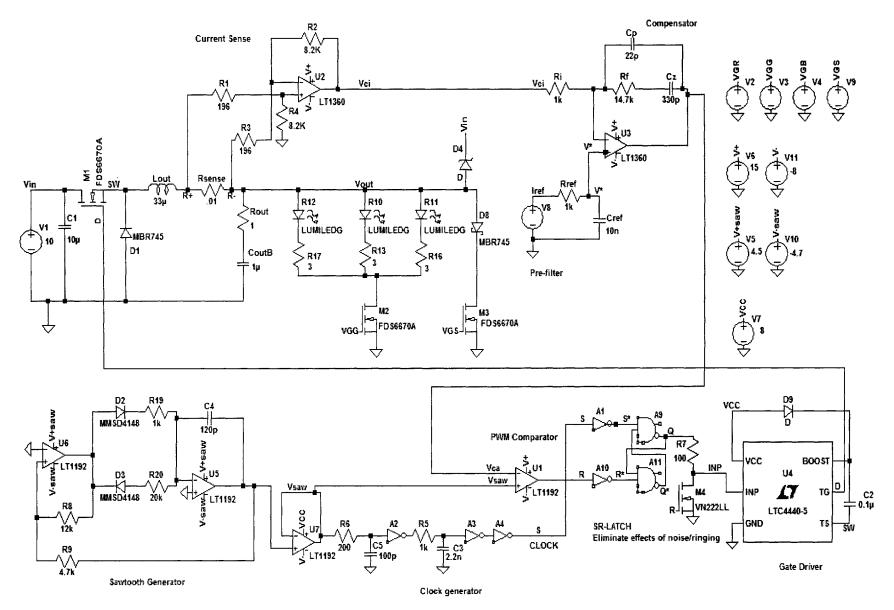

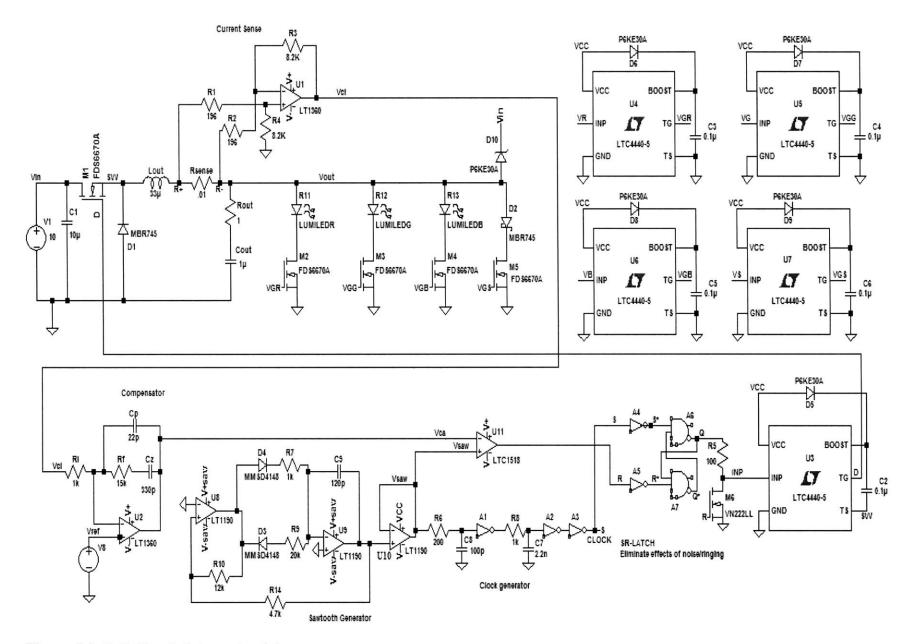

Shown in Figure 4.1a is the simulation schematic of an ACMC controlled multiple LED driver. The output stage of the buck is a simple low-pass LC filter. The driver is designed for fast transient response at a 290 kHz switching frequency without exceeding the ripple specification (maximum 150mA peak to peak output current ripple). Specific circuit values and tradeoffs will be discussed in the following text.

Figure 4.1a: Schematic of Average Current Mode Controlled LED Driver. See Appendix I for circuit description in SwitcherCAD.

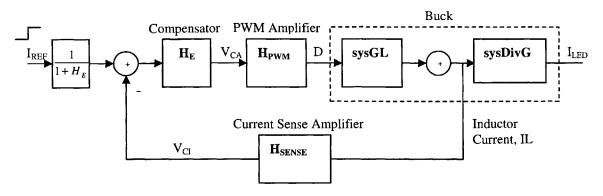

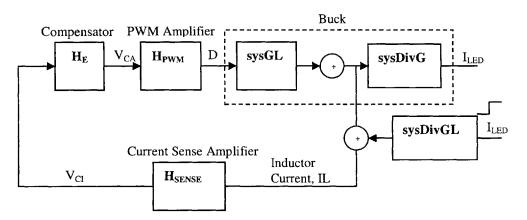

**Figure 4.1b:** Block diagram of Average Current Mode controlled multiple LED driver. This circuit is for a step in reference current. See Appendix II for block descriptions in MATLAB.

**Figure 4.1c:** Block diagram of Average Current Mode controlled multiple LED driver. This circuit is for a step in the load. See Appendix II for block descriptions in MATLAB.

Figure 4.1b shows the control block diagram of the system. I<sub>REF</sub> sets the output current.

The inductor current sensed by

$$H_{\text{SENSE}} = Rsense * \frac{R2}{R1}$$

gives  $V_{\text{CI}}$ , which is compared to

$I_{REF}$  at the compensator. The difference is multiplied by the compensator transfer

function

$$H_E(s) = \frac{sR_fC_z + 1}{R_i[s(C_z + C_p) + s^2R_fC_zC_p]}$$

, where s= j $\omega$ . The output of the

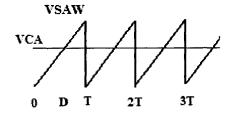

compensator,  $V_{CA}$ , is sent to the PWM comparator, approximated as  $f_{SW}^*V_{SAW}$ , where fsw is the switching frequency and Vsaw, the amplitude of the sawtooth signal. The

approximation  $H_{PWM}$  stems from the assumption that  $V_{CA}$  is a DC signal. Suppose this assumption is accurate, as Figure 4.2 below illustrates, the duty cycle D can be

approximated as

$$V_{CA}/(V_{SAW}*f_{SW})$$

since  $\frac{V_{CA}}{D} = \frac{V_{SAW}}{T}$ .

Figure 4.2: Assuming VCA is a constant, the transfer function of the PWM comparator can be linearized.

The next block models operation of the buck converter. At the buck, the duty cycle

multiplies sysGL

$$\approx \frac{V_{IN}/R_{OUT}}{s^2 * L_{OUT} * C_{OUT} + s * \frac{L_{OUT}}{R_{OUT}} + 1}$$

to give the inductor current. A fraction

of the inductor current determined by sysDivG =  $\frac{1 + s * C_{OUT} * R_{OUT}}{1 + s * C_{OUT} * (R_{OUT} + R_{LED})}$ , flows into

the LED.  $R_{LED}$  is the dynamic resistance of the LED. For our purposes, the value of the dynamic resistance is in the range of 0.02 $\Omega$  and 0.6  $\Omega$ .

Figure 4.1c shows a linearized model of the system during a load switch. Arguably, this model is flawed in many respects, however it provides an insight into the dynamics of the system during a load switch. The assumption is that the dynamic resistance of the LED and the output voltage are almost constant such that sysGL and sysDivG remain constant during the load switch. The idea behind the model in Figure 4.1c is that when the load switches from an LED to another diode of a different forward voltage, the output current

will jump or drop instantaneously primarily because of the exponential relationship between the output voltage and output current. This is valid if we assume the output voltage remains relatively constant at time t=0 when the load steps. This change in output current is reflected in the inductor current via sysDivGL, a current division of the output

current. SysDivGL =

$$\frac{sR_{OUT}C_{OUT} + 1}{s^2 L_{OUT}C_{OUT} + sR_{OUT}C_{OUT} + 1}$$

In seeking the "fastest" transient response, we mean the fastest 5% settling of the output current to, one, steps in the reference current, characterized by a step in  $I_{REF}$  in Figure 4.1a and 4.1b, and two, a load (or LED) switch at the output. Solving for the settling time exactly involves very involved non-linear calculations. In order to avoid detailed computation, we design for the highest possible bandwidth and a decent phase margin, a phase margin in the vicinity of 60° using linearized models and MATLAB as a tool. With the aid of SPICE simulations the settling time is calculated more accurately.

While filtering out ripple at the output, we jeopardize our mission to achieve a high bandwidth. The large filtering components we select for the output ripple attenuation present low frequency poles to the system. Without any dynamic compensation, these low frequency poles drag the bandwidth of the system to a low frequency too. The role of the compensator is to provide sufficient drive to compensate for these low frequency poles. The consequence is a higher bandwidth and faster settling. However, it needs to be recognized that the control authority to rapidly slew the output is limited by the inductor size, input and output voltages, and allowable duty ratio (0 to 1). The compensator not only adjusts the dynamics of the buck output but increases the gain and desensitizes the system to changes in system parameters such as input voltage, output voltage and component values. With this compensation scheme, the buck stage parameters have limited impact on the small-signal bandwidth, though large signal changes are still (slewrate) limited by the components. For simplicity, however, the design of the power stage and the controller are decoupled and designed sequentially. These design decisions are then studied and revisited where needed.

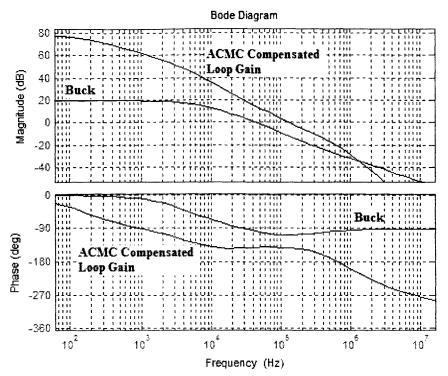

#### **Initial Design**

The output stage of the buck is constructed using a  $33\mu$ H inductor and a  $1\mu$ F capacitor in series with a  $1\Omega$  damping resistor. This initial design adequately filters out the output ripple. Figure 4.3 confirms that this choice of output filter attenuates output ripple sufficiently. But the small-signal bandwidth is fairly low, meaning that the transient response of the open-loop buck is not fast.

Figure 4.3: Bode plot of open-loop buck (= sysGL\*sysDivG) and ACMC compensated open-loop gain (= sysHE\*sysHPWM\*sysGL\*sysDivG) from MATLAB. ACMC Compensation shifts bandwidth from 5kHz to 110kHz. The values used in the converter and compensator are  $\frac{1.373e^{-39}s^7 + 2.72e^{-33}s^6 + 1.676e^{-27}s^5 + 3.3e^{-22}s^4}{9.245e^{-45}s^8 + 1.374e^{-38}s^7 + 6.948e^{-33}s^6 + 1.263e^{-27}s^5 + 3.432e^{-23}s^4}$ and  $\frac{1.848e^{-17}s^8 + 4.035e^{-23}s^7 + 2.999e^{-29}s^6 + 9.026e^{-34}s^5 + 9.029e^{-39}s^4}{(1.128e^{-38}s^{15} + 4.527e^{-29}s^{14} + 6.826e^{-20}s^{13} + 4.599e^{-11}s^{12} + 0.01186s^{11} + 1.457e^5s^{10} + 4.931e^{11}s^9 + 5.348e^{17}s^8 + 2.388e^{23}s^7 + 4.085e28s6 + 1.131e33s5 + 1.09e36s4)$ respectively. The computation of these transfer functions is indexed in Appendix II.

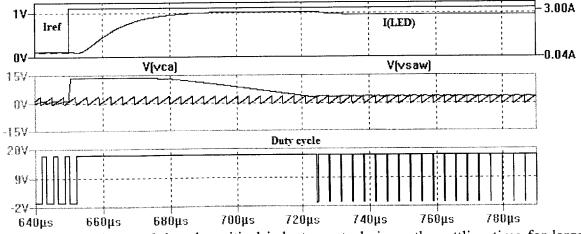

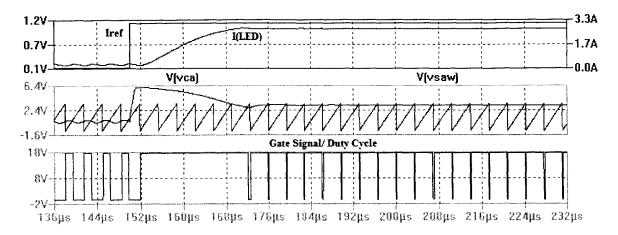

ACMC modifies the slow small-signal behavior of the open-loop buck regulator by injecting a zero before the switching frequency. This compensation is implemented as a type II compensator. With the driver powered by a 10V input voltage and switching at 290kHz, the result is a 7 $\mu$ s settling time response to a step in reference current (at a constant 1 $\Omega$  load), and a 27 $\mu$ s settling time when we change the load from a Schottky diode to an LED having an approximately 3.9V drop at approximately 250mA output current. Figures 4.4 and 4.5 illustrate the current settling of the RGB driver.

**Figure 4.4**: LED current settles to 5% of final value in  $7\mu$ s in response to a reference current step. Upward settling time and downward settling time both equal  $7\mu$ s.

Figure 4.5: Transient response of output current when load is changed from a Schottky to an LED of approximately 3.9V drop. Output current settles within  $27\mu s$  to 5% of final value.

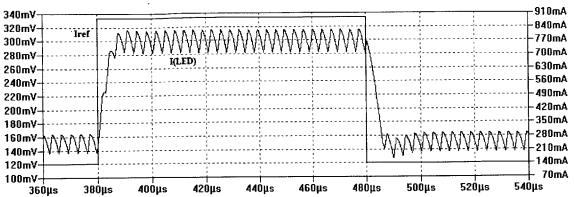

Since the RGB driver is to be used under varying duty cycle operations, it is important that the settling time remain reasonable for all possible reference current step amplitudes. We subject the driver to a 10% to 90% step in reference current and examine the current settling. With this large reference current step, the settling time deteriorates considerably. This phenomenon occurs for reference current steps greater than 0.9A. As Figure 4.6 depicts, this slow reference current settling stems from duty cycle saturation. When the reference current makes a huge jump suddenly, the system falls out of small signal operation. Consequently, the settling time is no longer determined by the small signal bandwidth of the system, but rather, the settling time is dominated by a large signal slew rate, which is closely related to the passive component values.

settling time worsens dramatically. For a 2.4A step in output current, settling time is  $80\mu$ s compared to  $7\mu$ s when reference current steps by 500mA.

In summary, settling time is 7µs in response to small reference current steps, 80µs in response to large reference current steps and 27µs when load is changed from a Schottky of approximately 0.2V drop to an LED of approximately 3.9V drop.

## **b.** Improvements to ACMC Controlled LED Driver

We now explore the limitations of the initial design. Armed with an understanding of where the limitations stem from, we can improve the settling time by fine-tuning our initial design or introducing different solutions that resolve the limitations of the initial design.

#### Improving small reference current step settling

The first item for improvement is the small reference current step settling time. In [12], P-L. Wong et al. (2002) describe a design method, critical inductance design, as a means to design a fast transient and efficient converter. The authors of *Critical inductance in voltage regulated modules* claim that in a fast DC/DC converter, there exists a critical inductance above which the transient response of the converter is drastically degraded. The idea behind the critical inductance is that as long as one avoids duty cycle saturation, by limiting inductor size to the "critical inductance", the converter exhibits superior transient performance compared to other conventional design methods such as the continuous conduction mode (CCM) or quasi-square wave (QSW) design. Typically, the critical inductance design solution yields a faster transient response in comparison to the other design schemes, and where the transient responses are comparable, the critical inductance technique offers lower output ripple. The authors of [12] define the critical inductance, L<sub>CRIT</sub> as the largest inductor that permits the largest needed change in duty

cycle.

$$L_{CRIT} = \frac{\Delta D_{MAX} * V_{IN} * \pi / 2}{\Delta I_{OUT} * \omega_{BW}}$$

;  $\Delta D_{MAX}$  is the maximum change in duty cycle,  $\Delta I_{OUT}$

is the corresponding change in output current,  $V_{IN}$  is the input voltage and  $\omega_{BW}$  is the bandwidth.

Given that our application calls for a  $\Delta D_{MAX} \approx 0.95$ ,  $\Delta I_{OUT} \approx 2.85A$ ,  $\omega_{BW} = 2\pi * 29 \text{kHz}$  at  $V_{IN} = 10 \text{V}$ ,  $L_{CRIT}$  calculates to be a 29µH inductor.

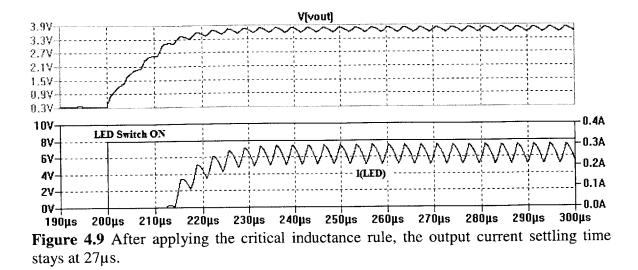

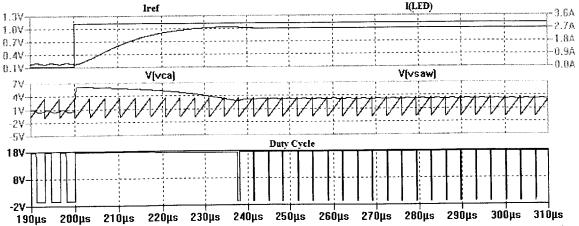

With  $L_{OUT}$  at 29µH, the output capacitance is set at 1µF, so as to meet the ripple specification. The damping resistor is maintained at 1Ω. The small reference current step settling time stays at 7µs and the output current settling time stays at 27µs. Meanwhile,

for large reference current steps, the settling time reduces from  $80\mu s$  to  $73\mu s$ . Figures 4.7 through to 4.9 illustrate these results.

Figure 4.7: The critical inductance design scheme keeps the small signal settling time at  $7\mu$ s.

Figure 4.8: After applying the critical inductance technique, the settling time for large output current steps improves from  $80\mu s$  to  $73\mu s$ .

The critical inductance design method does not improve the small reference current step settling time. This raises the question as to whether the  $29\mu$ H inductor is the true critical inductance. Suppose  $7\mu$ s is the optimal small reference current step settling, it implies that the critical inductance is not  $29\mu$ H but rather is an inductance equal or greater than  $33\mu$ H. For, with a  $33\mu$ H inductor, we still managed to avoid duty cycle saturation.

## Improving large reference current step settling

Although the critical inductance design method is said to prescribe an inductor size such that duty cycle saturation is avoided, contrary to expectations, Figure 4.8 points out that the saturation problem persists for large reference current steps, even after the conservative critical inductance design. This apparent controversy is resolved by examining the root cause of the duty cycle saturation. It turns out that the duty cycle saturation observed in Figure 4.8 is not directly related to the output inductor size. The saturation here is different from that which is referred to by [12]. This saturation arises from the slewing of the integrating capacitors at the compensator. As Figure 4.8 depicts,

when the reference current steps, signal  $V_{CA}$ , the compensator output voltage, swings to the supply rail immediately. Afterwards, the large integrating capacitors slow down the slew of  $V_{CA}$ . It takes over 70µs slewing down to meet with the sawtooth signal,  $V_{SAW}$ . Even at time 680µs, 30µs after the reference current steps, the duty cycle wrongfully remains at 100%, although the output current has overshot its target - all because the slow slewing  $V_{CA}$  is still well above the sawtooth.

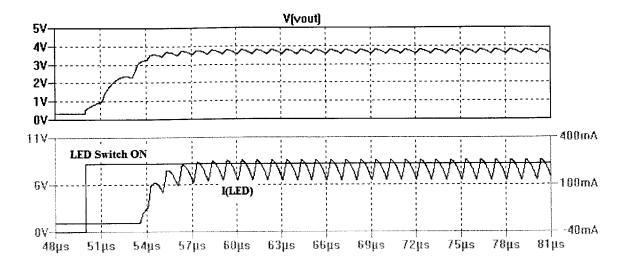

One workaround is to add on an anti-windup circuit [13]. Two zener diodes connected back to back across the compensator capacitor Cp serve to clamp the integration error of the compensator, and prevent  $V_{CA}$  from hitting the rails. Similarly, the amplitude of the sawtooth can be increased to reduce the voltage potential between the supply rails and the sawtooth. When a 4.7V zener anti-windup circuit is added,  $V_{CA}$  clamps at 4.7V. The settling time drops down to 22µs. This settling time is much better than the settling time attained by the initial design and the settling time attained by the "critical inductance" circuit. This improved settling is captured in Figure 4.10.

Figure 4.10: The anti-windup circuit reduces large reference current step settling time from  $73\mu$ s to  $22\mu$ s.

An equally efficient remedy is to filter the reference current (or voltage) with a low pass filter. The compensator sees a smoother jump in the reference current (or voltage), and so does not provide needless gain that sends the output current overshooting its target. Figure 4.11 shows that by smoothing the large reference current step, the delay caused by the slewing of the integrating capacitors is truncated to 28µs.

Figure 4.11: Slowly ramping up the reference current also reduces settling time from  $73\mu s$  to  $28\mu s$ .

Figures 4.10 and 4.11 beg the question as to whether we can shrink the duty cycle saturation time further, possibly to zero microseconds. We expect that by using a smaller output inductor, we can use smaller integrating capacitors, and as a result speed up the slew of the integrating capacitors. This argument implies that reducing the output inductance should improve the large reference current step settling. Former observations of the large reference current step confirm this argument. Without an anti-windup circuit, when the output inductor is at  $29\mu$ H, the large reference current step settling time is  $73\mu$ s and at  $33\mu$ H the settling time is  $80\mu$ s. We combine the positive effects of using an anti-windup and using a lower output inductor size, and run the driver with an anti-windup

circuit and a  $20\mu$ H inductor. The saturation time reduces to  $17\mu$ s, pushing the large reference current step settling time to  $17\mu$ s. See Figure 4.12. The small reference current step settling time of the driver still remains at  $7\mu$ s. The output current settling time also remains at  $27\mu$ s.

**Figure 4.12:** For a 2.4A reference current step, reducing output inductor to  $20\mu$ H lowers the settling time further to  $17\mu$ s.

Unfortunately, we cannot blindly reduce the output inductor size, because there is a minimum inductance needed to keep the driver stable. This minimum inductance is the minimum inductance needed to keep the slope of the inductor current as seen at the input of the PWM comparator from exceeding the slope of the sawtooth signal [10]. Hence,

$$\frac{V_{OUT}}{L_{OUT}} * sysHsense(j\omega_{SW}) * sysHE(j\omega_{SW}) \le V_{SAW} * f_{SW}; sysHsense and sysHE are the$$

amplification at the current sense amplifier and compensator respectively. Therefore,

$$L_{OUT} \ge \frac{V_{OUT} * sysHsense (j\omega_{SW}) * sysHE(j\omega_{SW})}{V_{SAW} * f_{SW}}$$

. For the present system, this

represents  $L_{OUT} \ge 20 \mu H$ .

Combining this minimum inductance criterion with the maximum inductance constraint provides a range of output inductor sizes that yield the minimum reference current step settling time. Any inductor within this range offers excellent small reference current step settling, while the minimum in the range provides the best large reference current step settling and real estate savings.

$$\frac{V_{OUT} * sysHsense(j\omega_{SW}) * sysHE(j\omega_{SW})}{V_{SAW} * f_{SW}} \le L_{OUT} \le \frac{\Delta D_{MAX} * V_{IN} * \pi/2}{\Delta I_{OUT} * \omega_{BW}}$$

(4.1).

For our values, we find  $20\mu H \le L_{OUT} \le 29\mu H$

#### **Improving load step settling**

Altogether, the techniques discussed so far have improved the reference current step settling. The settling time in response to a load step, on the other hand, appears to stick around  $27\mu s$  for output inductors sized between  $20\mu H$  and  $33\mu H$ . Why is this? A second pertinent question is, if the same control circuitry controls the output current (or more correctly the inductor current) during reference current steps and during load steps, why is the output current step response not as fast as the reference current step response?

In answer to the second question, we compare the block diagram of the system in Figure 4.1b to that illustrated in Figure 4.1c. The loop transfer function to the two step inputs,  $I_{REF}$  and load are not the same. While the reference current goes through a prefilter labeled 1/(1+sysHE) before entering the closed loop, any disturbance to the output current due to a load switch is first treated by sysDivGL. Since these two blocks are not identical, we do not expect the same transient response to the two step inputs.

Now, to why the output current step response sticks around  $27\mu s$ . A few simulation runs reveal that the load settling performance derails with higher output inductance and/or higher output capacitance. For example, with the output inductor at  $72\mu H$ , the output current settles within 140 $\mu s$ . This slow down is because high output capacitors and high output inductors push the poles of sysDivGL to very low frequencies. These low frequency poles contribute to the slow responses to output current steps.

All these statements have been made with the assumption that the small signal model of Figure 4.1c accurately describes the system when the output current steps. Arguably, this assumption is flawed, since the LEDs are not linear devices. When we switch LEDs the descriptions of sysGL and sysDivG change. One reason is because the output voltage moves during the transition. SysGL is defined under the assumption that the output voltage stays fixed. Secondly, the buck model changes during the output voltage only swings within an order of magnitude, and the fact that the dynamic resistances of the LEDs are all fairly low, mean sysGL and sysDivG remain unchanged to some degree. Secondly, if one adds on a resistor in series to the output capacitor, a resistor whose value is much less than all the dynamic resistances of the LEDs, then this added on resistor dominates the output resistance, sysGL and sysDivG are more robust when the load steps, and the small signal model applied does convey some truth about the behavior of the circuit.

Another reason for adding on the resistor in series to the output capacitor is to lower the peaking of the output current when we step from a high forward voltage LED to a low forward voltage LED. SPICE simulations show that a 1 $\Omega$  resistor serves the purpose quite dutifully. Additionally, the efficiency of the system remains almost unchanged after this modification.

In summary, low output inductors and low output capacitors improve the output current settling time. Ripple specifications together with stability issues and reference current step settling specifications do not permit us to reduce the output inductor and/or output capacitor too low. Since the objective is to achieve both excellent current step settling and output current step settling, we resort to the output inductor range set by equation

4.1;

$$\frac{V_{OUT} * sysHsense(j\omega_{SW}) * sysHE(j\omega_{SW})}{V_{SAW} * f_{SW}} \le L_{OUT} \le \frac{\Delta D_{MAX} * V_{IN} * \pi/2}{\Delta I_{OUT} * \omega_{BW}}$$

One must not jump to the smallest inductor in the range, as this may call for a very high output capacitor in order to meet output ripple specifications. The high output capacitor will derail the settling and defeat the purpose of picking a low output inductor.

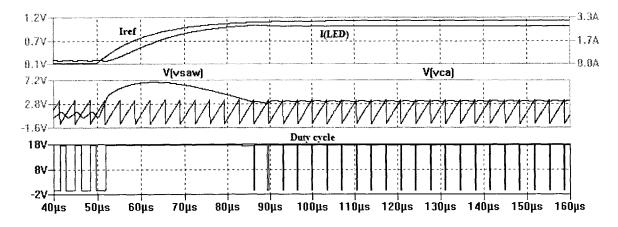

#### **Higher switching Frequency**

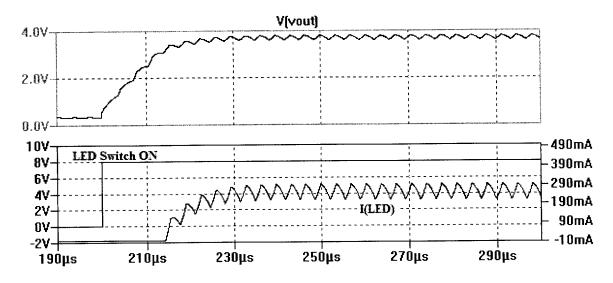

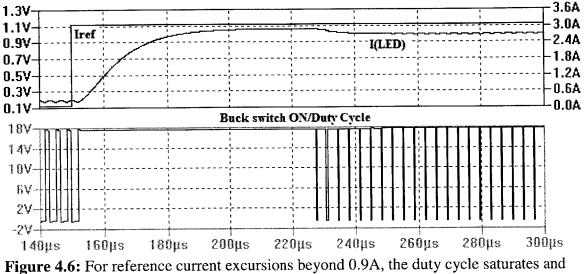

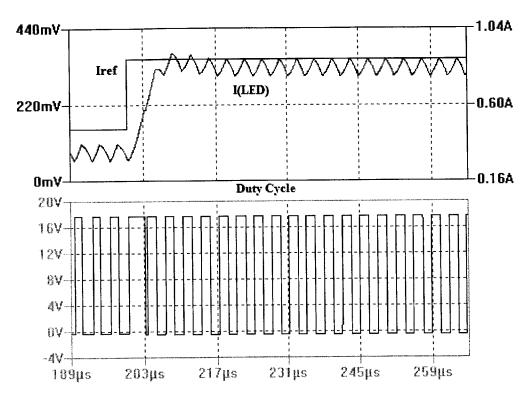

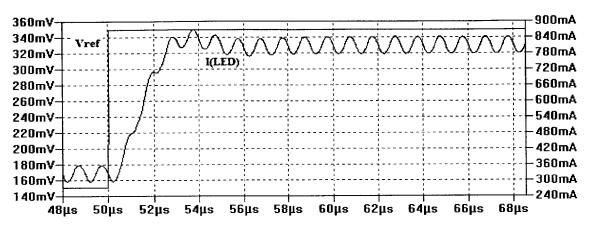

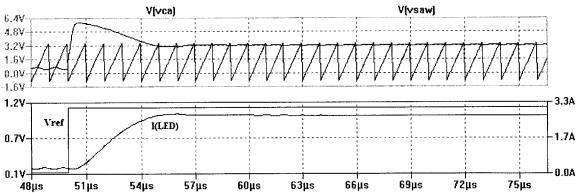

The preceding sub-chapters seem to imply that we cannot improve upon the 7 $\mu$ s small signal settling and the 27 $\mu$ s output current settling at 290kHz switching. The only alternative left to shrink the settling times is to scale the entire design up in frequency. Scaling the frequency by a factor of 3 to 970kHz, sets the reference current step settling time at 2.5 $\mu$ s, the 2.4A reference current step at 6 $\mu$ s and the output current step at 9 $\mu$ s. With a 2 $\mu$ s reference current settling time target, we run the circuit at 1MHz, and indeed

we achieve a 2us for a 600mA step in output current. At 1MHz, the 2.4A reference current step, settles within  $4\mu$ s and the load settling time measures to be  $7\mu$ s. See Figures 4.13 through to 4.16.

**Figure 4.13**: Switching at 1MHz results in a 2µs settling time for a 600mA step in reference current. This simulation uses circuit values  $V_{IN}=10V$ ,  $L_{OUT} = 5.8\mu$ H,  $C_{OUT} = .29\mu$ F,  $R_{OUT} = 1\Omega$  and compensator values Ri=1k, Rf = 15k, Cp = 6.38pF, Cz=95.7p and a 4.7V zener anti-windup circuitry.

**Figure 4.14:** And for a 2.4A step in reference current, switching at 1MHz yields a 4µs settling time. This simulation uses circuit values  $V_{IN}=10V$ ,  $L_{OUT} = 5.8\mu$ H,  $C_{OUT} = .29\mu$ F,  $R_{OUT} = 1\Omega$  and compensator values Ri=1k, Rf = 15k, Cp = 6.38pF, Cz=95.7p and a 4.7V zener anti-windup circuitry.

**Figure 4.15**: At 1MHz switching, output current settling time is 7 $\mu$ s. This simulation uses circuit values V<sub>IN</sub>=10V, L<sub>OUT</sub> = 5.8 $\mu$ H, C<sub>OUT</sub> =.29 $\mu$ F, R<sub>OUT</sub> = 1 $\Omega$  and compensator values Ri=1k, Rf = 15k, Cp = 6.38pF, Cz=95.7p and a 4.7V zener anti-windup circuitry.

# Summary of design choices and settling times

|                                                                                                                                                           | Settling time/µs                      |                                       |                           |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------------------------------|---------------------------|--|

| Circuit:<br>V <sub>IN</sub> =10V                                                                                                                          | Small<br>Reference<br>Current<br>Step | Large<br>Reference<br>Current<br>Step | Output<br>Current<br>Step |  |

| Initial design: $f_{SW}=290$ kHz<br>$L_{OUT} = 33\mu$ H, $C_{OUT}=1\mu$ F, $R_{OUT}=1\Omega$<br>Cp=22pF, Cz=330pF                                         | 7                                     | 80                                    | 27                        |  |

| Critical inductance : $f_{SW}=290$ kHz<br>$L_{OUT} = 29\mu$ H, $C_{OUT} = 1\mu$ F, $R_{OUT} = 1\Omega$<br>cCp=22pF, Cz=330pF                              | 7                                     | 73                                    | 27                        |  |

| Zener Anti-windup/ Prefilter: $f_{SW}$ =290kHz<br>L <sub>OUT</sub> = 29 $\mu$ H, C <sub>OUT</sub> =1F, R <sub>OUT</sub> = 1 $\Omega$<br>Cp=22pF, Cz=330pF | 7                                     | 22/28                                 | 27                        |  |

| Zener Anti-windup: $f_{SW}=290$ kHz<br>$L_{OUT} = 20\mu$ H, $C_{OUT} = 1\mu$ F, $R_{OUT} = 1\Omega$<br>Cp=22pF, Cz=330pF                                  | 7                                     | 17                                    | 27                        |  |

| Higher switching frequency: 970kHz<br>$L_{OUT} = 6.7\mu$ H, $C_{OUT} = .33\mu$ F, $R_{OUT} = 1\Omega$<br>Zener Anti-windup<br>Cp=7.3pF, Cz=110pF          | 2.5                                   | 6                                     | 9                         |  |

| Higher switching frequency: 1MHz<br>$L_{OUT} = 5.8\mu$ H, $C_{OUT} = .2\mu$ F, $R_{OUT} = 1\Omega$<br>Zener Anti-windup<br>Cp=6.38pF, $Cz=95.7p$ F        | 2                                     | 4                                     | 7                         |  |

Table 4.1: Summary of design choices and settling times

#### **Conclusion -** Settling time

1. For small signal reference current steps, an inductor size within the range specified by equation 4.1,  $\frac{V_{OUT} * sysHsense(j\omega_{SW}) * sysHE(j\omega_{SW})}{V_{SAW} * f_{SW}} \le L_{OUT} \le \frac{\Delta D_{MAX} * V_{IN} * \pi/2}{\Delta I_{OUT} * \omega_{BW}}, \text{ offers}$

the minimum settling time in response to both reference current and output current steps.

- 2. For fast large reference current step settling, the smallest inductor size in the range should be selected. An anti-windup circuit also improves the large reference current step settling. If the designer can cook up an anti-windup circuit that always keeps the integration capacitors from hitting the supply rails, the large reference current step settling will equal the small reference current settling time and would not be a topic needing special attention.

- 3. The load step settling time is improved by restricting inductor size and output capacitor size to low values. The best output current settling time is also achieved by selecting an inductor size  $L_{OUT}$  such that  $\frac{V_{OUT} * sysHsense(j\omega_{SW}) * sysHE(j\omega_{SW})}{V_{SAW} * f_{SW}} \leq L_{OUT} \leq \frac{\Delta D_{MAX} * V_{IN} * \pi/2}{\Delta I_{OUT} * \omega_{BW}}$

- 4. Adding a low resistor in series to the output capacitance serves to keep the transfer function of the buck system relatively constant under different LEDs. It also serves to lower the peaking of the output current when one switches from an LED of a high forward voltage to an LED of a lower forward voltage. Adding on a damping resistor has no impact on the settling times.

- 5. Scaling the circuit up in frequency improves all settling times.

6. In our application since we step both the reference current and the load step settling at the same time, we are ultimately concerned with the maximum of the two settling times. The initial design of the output stage of the buck – a  $33\mu$ H inductor connected to a  $1\Omega$  resistor in series with a  $1\mu$ F output capacitor yields the best overall settling time with reasonable efficiency, since we are using a reasonably large inductor.

#### Efficiency

Power is lost primarily through the conduction losses of the switch mosfets M1, MS1 to MSN and MS and the catch diode. The sense resistor, the ESR of the inductor and ESR of the output capacitor also contribute to the power losses. Furthermore, the switching losses of the mosfets and gate driver circuits also add to the inefficiency of the system.

The capacitor and inductor in the circuit also burn power via their parasitic resistance. The capacitor values used in the circuit are less than  $1\mu$ F, as a result, we expect them to be of the ceramic type, to have negligible ESR and to burn negligible power. Because of this argument, the capacitors are modeled without ESR in SPICE. The on-resistance of the inductor is also neglected in simulation because the on-resistance of the inductor is very specific to the inductor: its shape, size and other manufacturing conditions. It is therefore unreasonable to fix the on-resistance of the inductor in simulation.

Since the ESR of the capacitors and the on-resistance of the inductor are always kept at zero in simulation, it is not surprising that the efficiency measured in simulation is almost constant across the design schemes proposed.

$$Efficiency = \begin{pmatrix} \frac{1W}{1.7W} = 59\%; I_{out} = 0.36A \\ \frac{25W}{26.1W} = 95\%; I_{out} = 2.7A \end{pmatrix}$$

It must be noted that the true efficiency is lower since all of the controller power consumption is not accounted for here. The other reason is that the inductor and capacitors are also modeled without any parasitic resistance.

# c. Modeling of External Components

As indicated earlier the capacitors and inductors are modeled as ideal components. The inductor is modeled as a pure inductor. It has neither parasitic resistance nor parasitic capacitance. In the same vein, the capacitor is modeled as a pure capacitor. It has neither parasitic resistance nor parasitic inductance. The consequence is that the efficiency estimated from simulation is higher than it will be on breadboard. That being said, because we expect the capacitors to be of the ceramic type with very low ESR, by ignoring the capacitors' ESR only negligible errors are introduced to the SPICE simulation results.

The amplifiers and gate drivers are selected from the LTC SwitcherCAD library. A few modifications are added to the models to make them more realistic. One such modification is limiting the output current of the operational amplifiers in the circuit to their true maximum output current.

# d. Modeling of Power Dissipation

The efficiency measurements are made by averaging power dissipated at the input and at the sawtooth generation circuit as input power. Output power is calculated by averaging power dissipated by the LED alone.

# **Chapter 5 – Testing**

Testing the design solutions proposed in Chapter 4 on the bench allows us to validate the computer models and conclusions drawn. Since the models are as accurate as we make them, performance in simulation may deviate from real life performance if the models are inaccurate. Measurements on the bench should give a more realistic picture of solutions proposed.

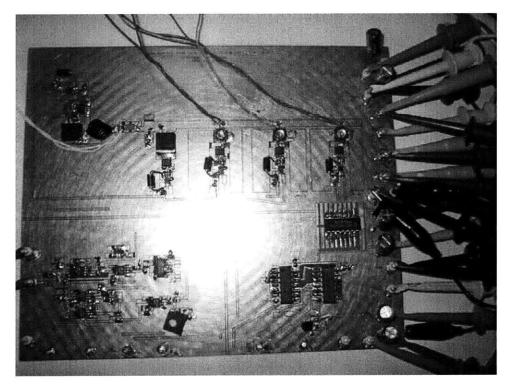

A picture of the breadboard of the initial solution is displayed below in Figure 5.1.

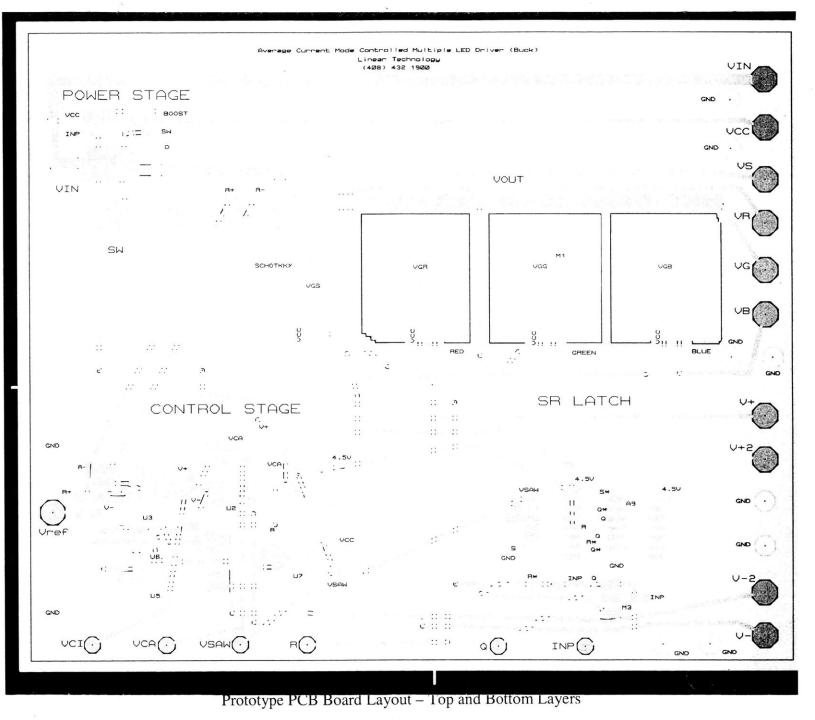

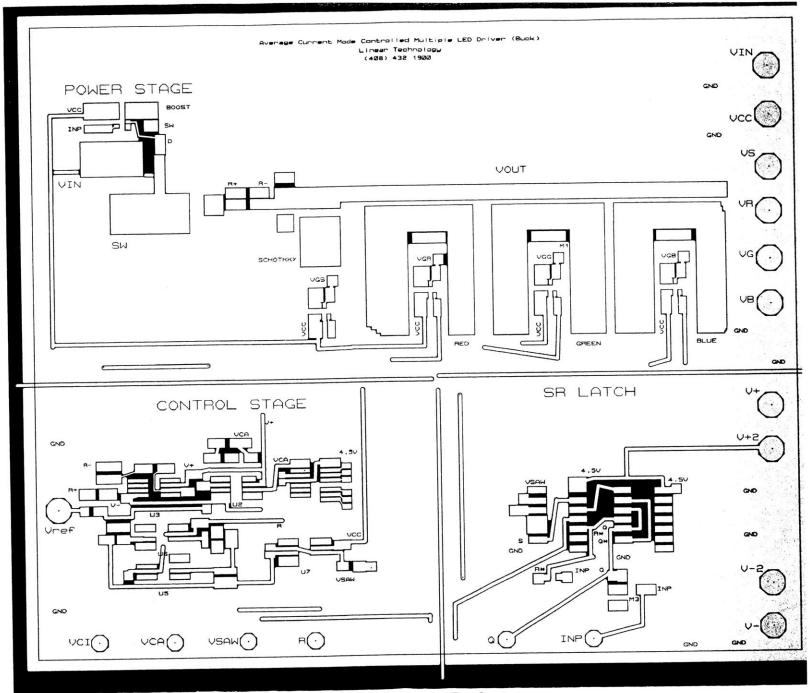

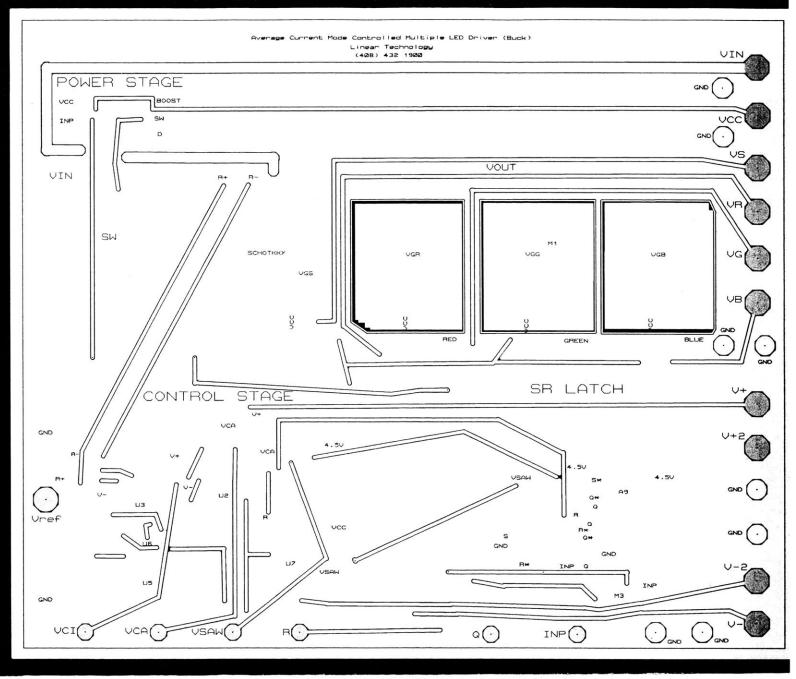

Figure 5.1: PCB board of initial design. The PCB board layout and Bill of Materials are indexed in Appendix III

Figure 5.2: Full Circuit Schematic of the prototype system

| Operating parameter                     | Value                                                                                                                                     |  |  |  |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Input voltage, V <sub>IN</sub>          | 10V- 30V                                                                                                                                  |  |  |  |

| Switching frequency                     | 101kHz, 179kHz, 290kHz, 430kHz,                                                                                                           |  |  |  |

|                                         | 592kHz, 620kHz, 702kHz, 870kHz,                                                                                                           |  |  |  |

|                                         | 1.07MHz, 1.41MHz                                                                                                                          |  |  |  |

| Output Inductor, L <sub>OUT</sub>       | <ul> <li>7.1μH, 12.9μH, 17.2μH, 32.2μH, 44.9μH,</li> <li>94.7μH, 131.5μH, 187.3μH</li> <li>(All inductors are of type D03316P)</li> </ul> |  |  |  |

|                                         |                                                                                                                                           |  |  |  |

|                                         |                                                                                                                                           |  |  |  |

| Output Capacitor, C <sub>OUT</sub>      | 11nF, 41nF, 74nF, 430nF, 852nF, 4.25μF, 7.53μF, 52.93μF, 97.16μF                                                                          |  |  |  |

|                                         |                                                                                                                                           |  |  |  |

| Output Resistor, R <sub>OUT</sub>       | $0.01\Omega, 0.05\Omega, 0.1\Omega, 0.6\Omega, 1.3\Omega, 5.2\Omega,$                                                                     |  |  |  |

|                                         | 10Ω, 50Ω, 100.6Ω                                                                                                                          |  |  |  |

| Load                                    | MBR74 Schottky                                                                                                                            |  |  |  |