# **ENERGY SCALABILITY OF ON-CHIP INTERCONNECTION**

# **NETWORKS**

by

THEODOROS K. KONSTANTAKOPOULOS

Diploma ECE, University of Patras, Greece, 2000 M.S. EECS, Massachusetts Institute of Technology, 2002

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Electrical Engineering and Computer Science

at the

## MASSACHUSETTS INSTITUTE OF TECHNOLOGY

June 2007

© Massachusetts Institute of Technology, 2007. All Rights Reserved.

Author ..... Department of Electrical Engineering and Computer Science May 25, 2007

Certified by .....

Anant Agarwal, Professor Department of Electrical Engineering and Computer Science Thesis Supervisor

Accepted by ..... Arthur C. Smith

Chairman, Department Committee on Graduate Students

# ENERGY SCALABILITY OF On-Chip Interconnection NETWORKS

by

THEODOROS K. KONSTANTAKOPOULOS

Submitted to the Department of Electrical Engineering and Computer Science on May 25, 2007, in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering and Computer Science

### ABSTRACT

On-chip interconnection networks (OCN) such as point-to-point networks and buses form the communication backbone in multiprocessor systems-on-a-chip, multicore processors, and tiled processors. OCNs consume significant portions of a chip's energy budget, so their energy analysis early in the design cycle becomes important for architectural design decisions.

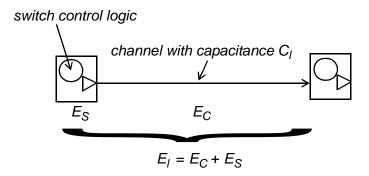

Although innumerable studies have examined OCN implementation and performance, there have been few energy analysis studies. This thesis develops an analytical framework for energy estimation in OCNs, for any given topology and arbitrary communication patterns, and presents OCN energy results based on both analytical communication models and real network traces from applications running on a tiled multicore processor. This thesis is the first work to address communication locality in analyzing multicore interconnect energy and to use real multicore interconnect traces extensively. The thesis compares the energy performance of point-to-point networks with buses for varying degrees of communication locality. The model accounts for wire length, switch energy, and network contention. This work is the first to examine network contention from the energy standpoint. The thesis presents a detailed analysis of the energy costs of a switch and shows that the estimated values for channel energy, switch control logic energy, and switch queue buffer energy are 34.5pJ, 17pJ, and 12pJ, respectively.

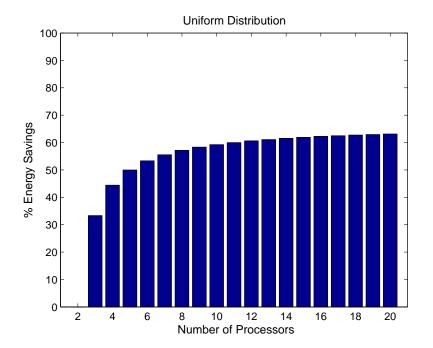

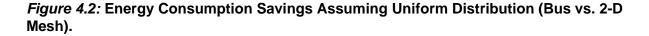

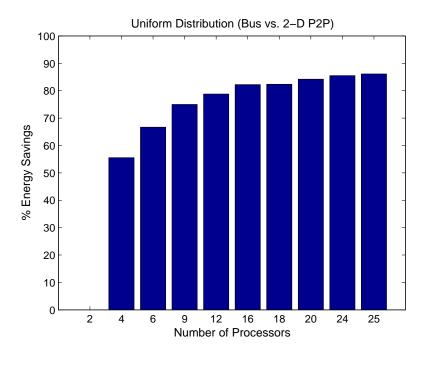

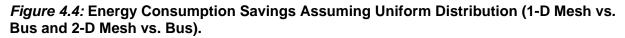

The results suggest that a one-dimensional point-to-point network results in approximately 66% energy savings over a bus for 16 or more processors, while a two-dimensional network saves over 82%, when the processors communicate with each other with equal likelihood. The savings increase with locality. Analysis of the effect of contention on OCNs for the Raw tiled microprocessor reports a maximum energy overhead of 23% due to resource contention in the interconnection network.

Thesis Supervisor: Anant Agarwal Title: Professor of Electrical Engineering and Computer Science

## Acknowledgments

I feel privileged to have worked with so many talented people during my time at MIT. I would have never achieved any of this without the support, guidance, and direction from my advisor, Prof. Anant Agarwal. His supervision helped me move many academic steps ahead. Working with him has been a great intellectual experience. Anant was great in making me look at the big picture in times where I was lost in the details of research. My research has greatly benefited from his technical guidance and his steady stream of enthusiasm.

I would also like to thank Prof. Anantha Chandrakasan and Prof. Arvind for serving as members of my committee. They were always there for me when I needed them. They provided valuable feedback on my thesis and helped with the clarity of the presentation from the view of an external reader.

Many thanks to all the members of the Raw group. I have spent a lot of time with them working in different projects, also doing things outside research. Several people have contributed directly to the work in this thesis and I would like to point out their contribution. Paul Johnson ran the benchmarks and provided me with the trace information that I used in the thesis for the model validation. Jason Miller has been an extremely helpful labmate and officemate. He was always there to answer all my questions on the Raw microprocessor. His help is greatly appreciated. Jonathan Eastep spent a significant amount of his time going over my thesis and providing valuable feedback on all aspects of it. He has been extremely helpful in pointing out ways to present the results of my research in a more clear and straightforward way.

Special thanks to my good friend Duke Xanthopoulos for providing valuable feedback on many aspects of the thesis. Our discussions have really helped me all this time. Petros Boufounos has been there for me whenever Matlab was giving me nightmares. Paul-Peter

Sotiriadis has been very helpful in the initial parts of my research when I first started thinking about the models and the framework.

I couldn't thank more my parents for everything they have done for me. They have always been encouraging me to try different things in life, respecting my decisions and helping me achieve my goals. I am extremely grateful for that. All members of my family have been extremely supportive; they were a constant force of strength all seven years I spent at MIT.

Throughout my life at MIT, I was privileged to meet so many people that I could call my friends. Anna has been a great support all this time and she was there to help me bring some balance in my life. A lot of people had a positive impact in my life: Aggelos, Angelina, Anna, Anna, Christina, Christina, Duke, Eleftheria, Giorgos, Kostas, Margarita, Maria-Katerina, Nikolas, Nikol, Pavlos, Petros, Ramin, Sebastien, Thodoros, Vasilis, Yiannis, Yiannis.

Last but not least, I would like to thank all the MIT faculty and the administrative stuff for doing a perfect job in providing excellent standards of education and a very intellectually stimulating environment.

# TABLE OF CONTENTS

| Chapte | r 1 Intro | oduction                                 | 17 |

|--------|-----------|------------------------------------------|----|

| 1.1    | Contri    | butions                                  | 24 |

| 1.2    | Thesis    | Roadmap                                  | 27 |

|        |           |                                          |    |

| Chapte | r 2 Bac   | kground                                  | 31 |

| 2.1    | The R     | aw Microprocessor [1]                    | 32 |

|        | 2.1.1     | Overview and Design Philosophy           | 32 |

|        | 2.1.2     | The Processing Core                      | 33 |

|        | 2.1.3     | Communication Networks                   | 34 |

|        | 2.1.4     | Raw Implementation                       | 35 |

|        | 2.1.5     | Energy Summary                           | 36 |

| 2.2    | Tiled /   | Architectures                            | 37 |

|        | 2.2.1     | The Stanford Smart Memories Project [26] | 37 |

|     |        | 2.2.2   | The UWM Multiscalar [30]                             |    |

|-----|--------|---------|------------------------------------------------------|----|

|     |        | 2.2.3   | The U. of Washington WaveScalar [28]                 | 39 |

|     |        | 2.2.4   | The UT-Austin TRIPS architecture [29]                | 40 |

|     |        | 2.2.5   | The UC Davis Synchroscalar [31]                      | 41 |

|     | Sum    | mary    |                                                      | 41 |

| ••• |        |         |                                                      |    |

| Cr  | -      |         | amework for Energy Analysis                          |    |

|     | 3.1    |         | / Analysis Framework                                 |    |

|     | 3.2    |         | ad Model                                             |    |

|     | 3.3    |         | terconnection Model                                  |    |

|     | 3.4    |         | o-Point Interconnection Network Model                |    |

|     | 3.5    | Traffic | Distributions                                        | 48 |

|     |        | 3.5.1   | Communication Energy Cost                            | 48 |

|     |        | 3.5.2   | Uniform Distribution                                 | 49 |

|     | 3.6    | Energy  | Comparison of the Two Systems                        | 51 |

|     | 3.7    | Localiz | ed Traffic Distributions                             | 54 |

|     |        | 3.7.1   | Linear Decay                                         | 55 |

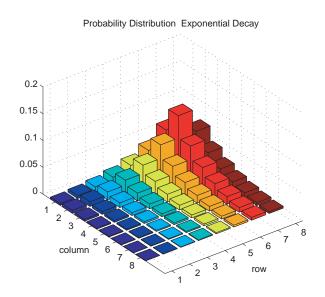

|     |        | 3.7.2   | Exponential Decay                                    | 57 |

|     |        | 3.7.3   | Step Distribution                                    | 59 |

|     |        | 3.7.4   | Truncated Linear Decay                               | 61 |

|     |        | 3.7.5   | Truncated Exponential Decay                          | 63 |

|     |        | 3.7.6   | Savings Comparison for Different Distributions       | 64 |

|     | Sum    | mary    |                                                      | 66 |

|     |        |         |                                                      |    |

| Ch  | napter | 4 Two-  | Dimensional Interconnection Networks                 | 69 |

|     | 4.1    | Interco | nnection Network Model for 2-D Systems               | 69 |

|     | 4.2    | Comm    | unication Energy Cost                                | 71 |

|     | 4.3    | Uniforr | n Distribution                                       | 73 |

|     | 4.4    | Energy  | Comparison of a 2-D Network with 1-D Network and Bus | 74 |

|     | 4.5    | Localiz | ed Traffic Distributions                             | 77 |

|     |        | 4.5.1   | Uniform Distribution                                 | 80 |

|     |        | 4.5.2   | Linear Decay                                         | 80 |

|     |        | 4.5.3   | Exponential Decay                                    | 81 |

|     |        | 4.5.4   | Step Distribution                                    | 81 |

|     |        |         | •                                                    |    |

|     |              | 4.5.5    | Truncated Linear Decay                                  | 82  |

|-----|--------------|----------|---------------------------------------------------------|-----|

|     |              | 4.5.6    | Truncated Exponential Decay                             | 82  |

|     | Sum          | mary     |                                                         | 83  |

|     |              |          |                                                         |     |

| Ch  | -            |          | rgy Savings and Model Validation Using Network Traces   |     |

|     | 5.1          |          | rk Traces                                               |     |

|     | 5.2          | Trace    | Communication Statistics                                | 89  |

|     | 5.3          | Energ    | y Savings                                               | 90  |

|     | 5.4          |          | Validation                                              |     |

|     | Sum          | mary     |                                                         | 97  |

| Ch  | antor        | · 6 Swit | ch Energy and Wire Length                               | 00  |

| CII | артеі<br>6.1 |          | n Energy                                                |     |

|     | 6.2          |          | n Energy and Varying Wire Lengths                       |     |

|     | 6.3          |          | Order Dimension Mapping                                 |     |

|     | 6.4          | Ŭ        | ation of Matrices D and H                               |     |

|     | 6.5          |          | y Comparison for High-Dimensional Networks              |     |

|     |              |          |                                                         |     |

|     | Sum          | mary     |                                                         |     |

| Ch  | apter        | · 7 Con  | tention Energy Analysis for Multi-Dimensional Networks  | 111 |

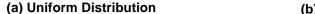

|     | 7.1          | Switch   | n Model                                                 | 111 |

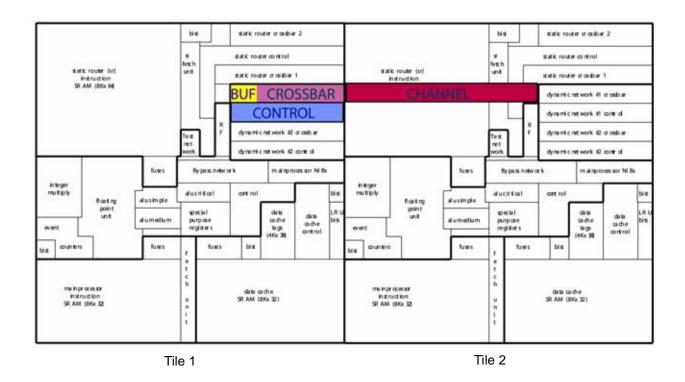

|     | 7.2          | Life of  | a Message in the Network                                | 115 |

|     | 7.3          | Calcul   | ation of Contention Probability                         | 119 |

|     |              | 7.3.1    | Contention Probability In One-Dimensional Networks      | 128 |

|     |              | 7.3.2    | Contention Probability In Bus-Based Networks            | 129 |

|     | 7.4          | Energ    | y Consumption Assuming Uniform Distribution             | 131 |

|     | 7.5          | Energ    | y Consumption Using Network Traces                      | 135 |

|     | Sum          | mary     |                                                         | 142 |

|     |              |          |                                                         |     |

| Ch  | apter        | 8 Futu   | ıre Work                                                | 145 |

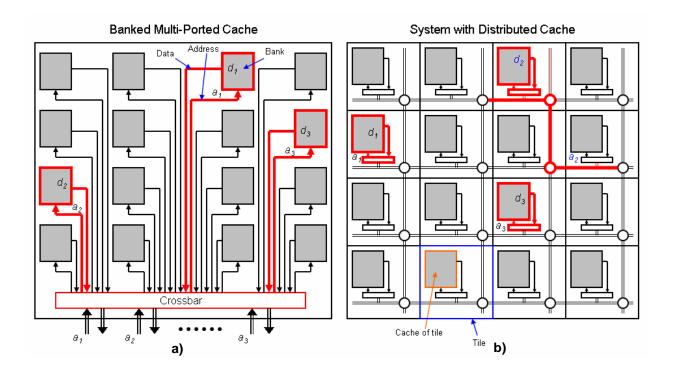

|     | 8.1          | Advan    | tages of Distributed vs. Centralized Hardware Resources | 145 |

|     |              | 8.1.1    | Cache Architecture                                      | 146 |

|     |              | 8.1.2    | Energy Savings for Distributed Caches                   | 148 |

|     | 8.2          | Netwo    | rk Topologies                                           | 151 |

| 8.3    | Traces                                              | 151 |

|--------|-----------------------------------------------------|-----|

| 8.4    | Technology Scaling Effect                           | 152 |

| 8.5    | Energy Performance of Tiled Processor Architectures | 154 |

| Chapte | 9 Related Work                                      | 155 |

| Chapte | 10 Conclusions                                      | 161 |

| Nomen  | clature                                             | 165 |

| Append | ix A Calculation of Energy Costs                    | 169 |

| A.1    | Link Capacitance Energy Cost Estimation             | 169 |

| A.2    | Crossbar and Control Logic Energy Cost Estimation   | 171 |

| A.3    | Input Queue Buffer Energy Cost                      | 172 |

| Append | ix B Communication Patterns in Raw Applications     | 177 |

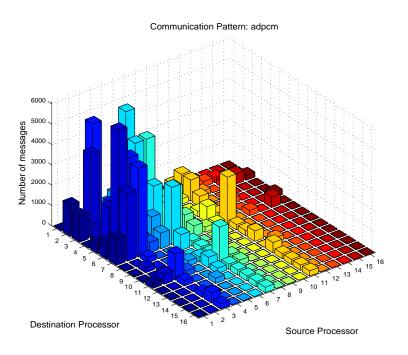

| B.1    | APDCM                                               | 178 |

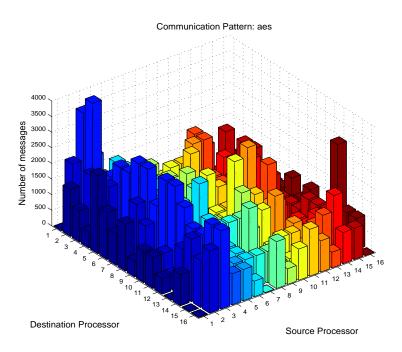

| B.2    | AES                                                 | 178 |

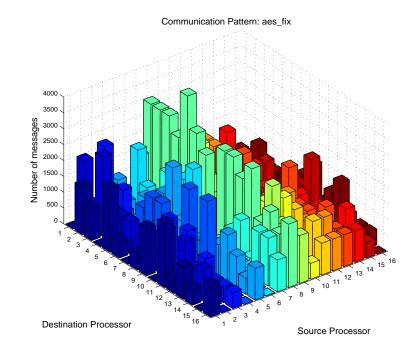

| B.3    | AES_FIX                                             | 179 |

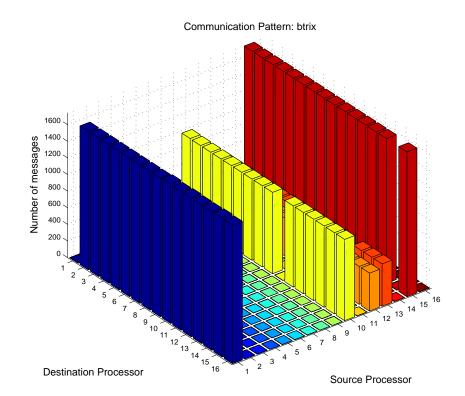

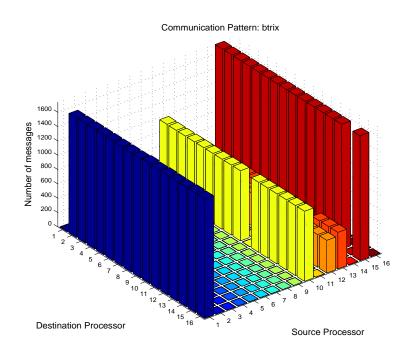

| B.4    | BTRIX                                               | 179 |

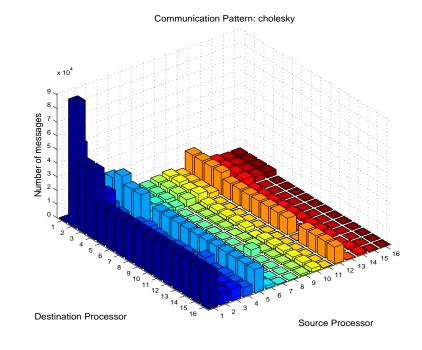

| B.5    | CHOLESKY                                            | 180 |

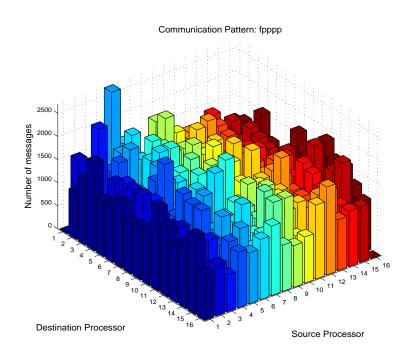

| B.6    | FPPPP                                               | 180 |

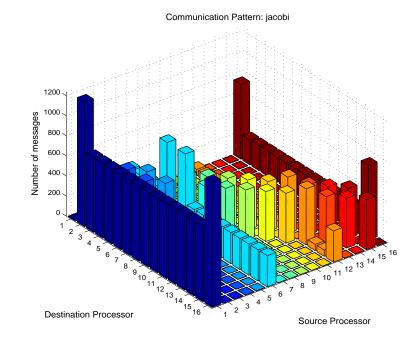

| B.7    | JACOBI                                              | 181 |

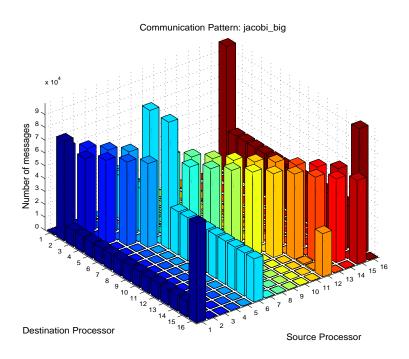

| B.8    | JACOBI_BIG                                          | 181 |

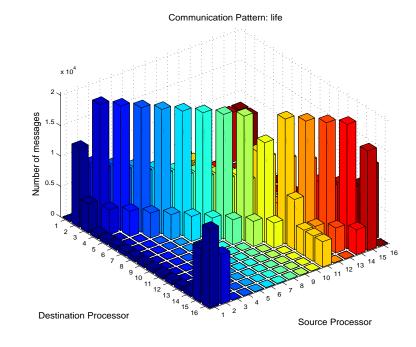

| B.9    | LIFE                                                | 182 |

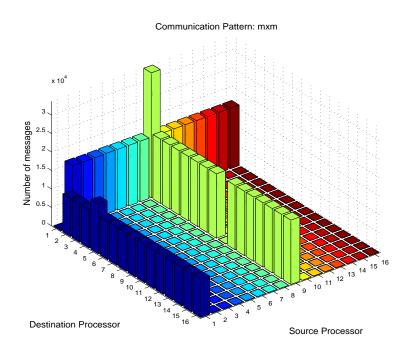

| B.10   | MXM                                                 | 182 |

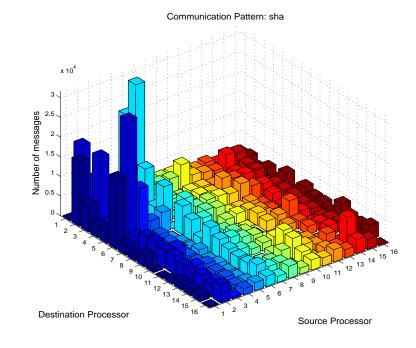

| B.11   | SHA                                                 | 183 |

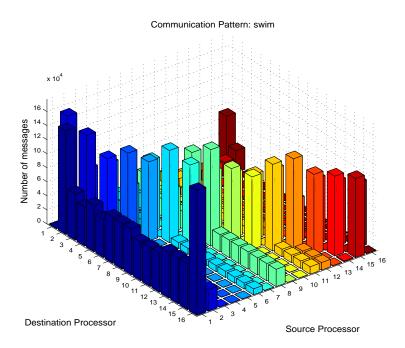

| B.12   | SWIM                                                | 183 |

| B.13   | TOMCATV                                             | 184 |

| B.14   | VPENTA                                              | 184 |

| _      |                                                     |     |

|        | ix C Three-Dimensional Interconnection Networks     |     |

| C.1    | Interconnection Energy for 3-D Systems              |     |

| C.2    | Uniform Distribution                                | 187 |

# LIST OF FIGURES

# Chapter 1

| Fig. 1.1: Transistor Trend [20]. Number of transistors used in microprocessors over the | Э  |

|-----------------------------------------------------------------------------------------|----|

| last twenty five years 1                                                                | 8  |

| Fig. 1.2: Frequency Trend [20]. Reported operating frequency for different              |    |

| microprocessors over the last twenty five years 1                                       | 9  |

| Fig. 1.3: Power Trend[20]. Reported microprocessor power consumption over the last      |    |

| twenty five years                                                                       | 20 |

# Chapter 2

| Fig. 2.1: The Raw Microprocessor. A Raw processor consists of a 2-D array of uniform    | nly  |

|-----------------------------------------------------------------------------------------|------|

| replicated tiles, each containing a MIPS-style processor and two types of network route | ers  |

| to connect it to the neighboring tiles.                                                 | . 33 |

| Fig. 2.2: Raw Die Photo                                                                 | . 36 |

#### Chapter 3

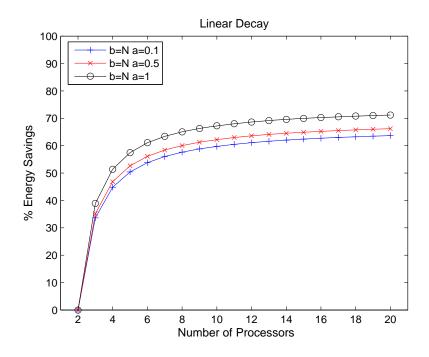

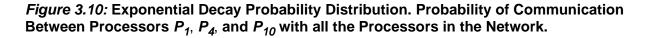

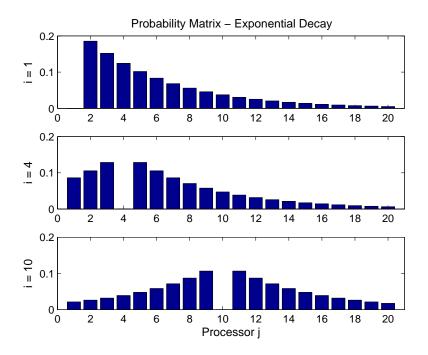

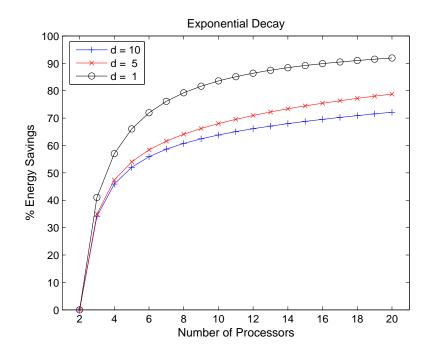

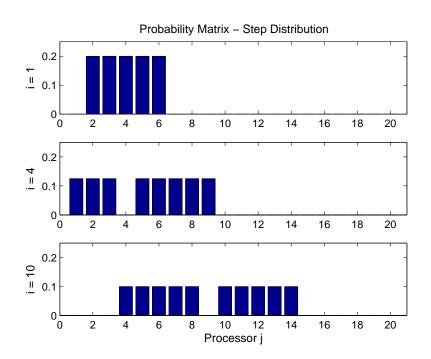

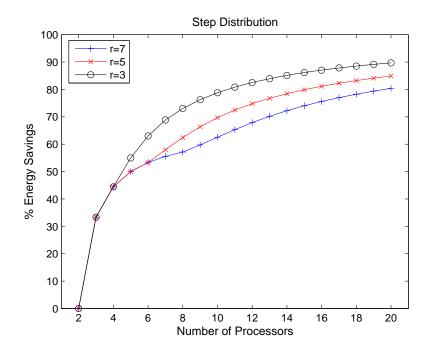

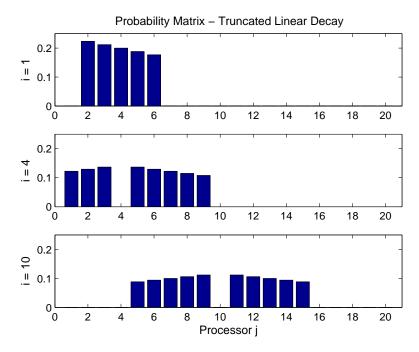

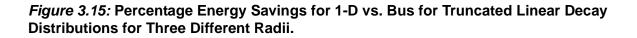

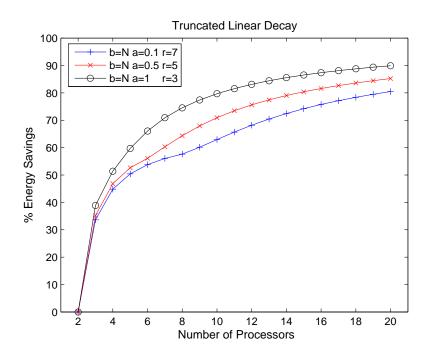

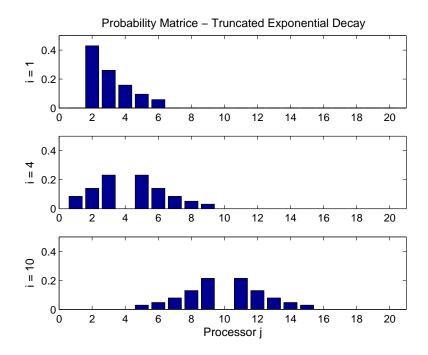

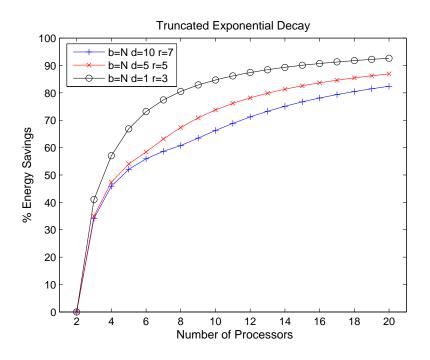

Fig. 3.6: Energy Costs for a Network Hop. The total energy consists of the energy dissipated in the link that connects two neighboring processors and the energy dissipated in the switch.52 Fig. 3.8: Linear Decay Probability Distribution. Probability of Communication Between Fig. 3.9: Percentage Energy Savings for 1-D vs. Bus for Linear Decay Distributions for Three Fig. 3.10: Exponential Decay Probability Distribution. Probability of Communication Between Fig. 3.11: Percentage Energy Savings for 1-D vs. Bus for Exponential Decay Distributions for Fig. 3.12: Exponential Decay Probability Distribution. Probability of Communication Between Fig. 3.13: Percentage Energy Savings for 1-D vs. Bus for Step Distributions for Three Different Radii......61 Fig. 3.14: Truncated Linear Decay Probability Distribution. Probability of Communication Fig. 3.15: Percentage Energy Savings for 1-D vs. Bus for Truncated Linear Decay Distributions for Three Different Radii......62

| Fig. 3.16: Truncated Exponential Decay Probability Distribution. Probability of    |    |

|------------------------------------------------------------------------------------|----|

| Communication between Processors P1, P4, and P10 with all the Processors in the    |    |

| Network                                                                            | 63 |

| Fig. 3.17: Percentage Energy Savings for 1-D vs. Bus for Truncated Exponential Dec | ay |

| Distributions for Three Different Radii                                            | 64 |

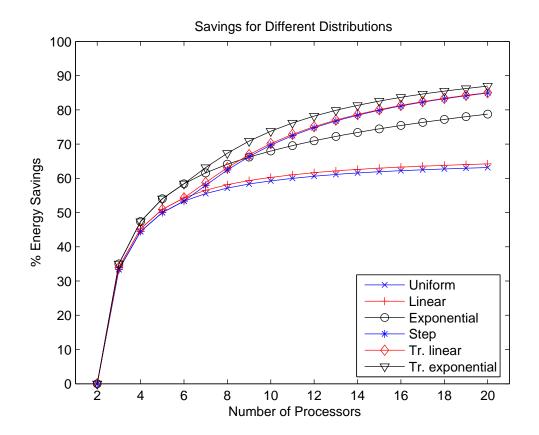

| Fig. 3.18: Savings Comparison for All Distributions                                | 65 |

# Chapter 4

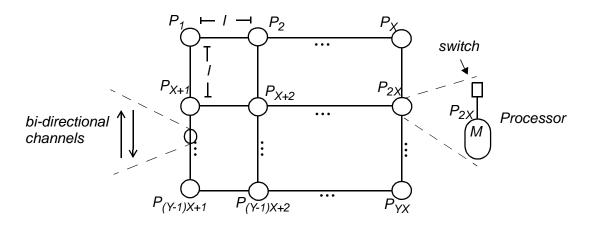

| Fig. 4.1: 2-D Point-to-Point Network Model: N Processors, each transmitting M data   |

|--------------------------------------------------------------------------------------|

| words on a 2-D mesh network. There are X processors in each row and Y processors in  |

| each column                                                                          |

| Fig. 4.2: Energy Consumption Savings Assuming Uniform Distribution (Bus vs. 2-D      |

| Mesh)76                                                                              |

| Fig. 4.3: Energy Consumption Savings Assuming Uniform Distribution (1-D Mesh vs. 2-  |

| D Mesh77                                                                             |

| Fig. 4.4: Energy Consumption Savings Assuming Uniform Distribution (1-D Mesh vs.     |

| Bus and 2-D Mesh vs. Bus) 80                                                         |

| Fig. 4.5: Energy Consumption Savings Assuming Linear Distribution (1-D Mesh vs. Bus  |

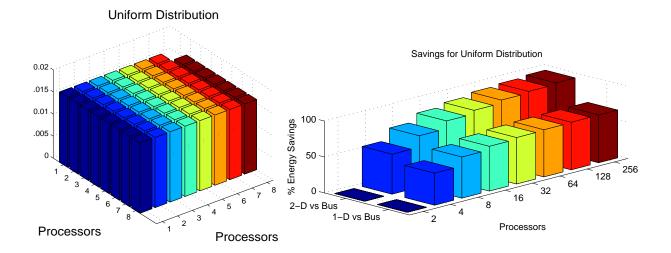

| and 2-D Mesh vs. Bus)                                                                |

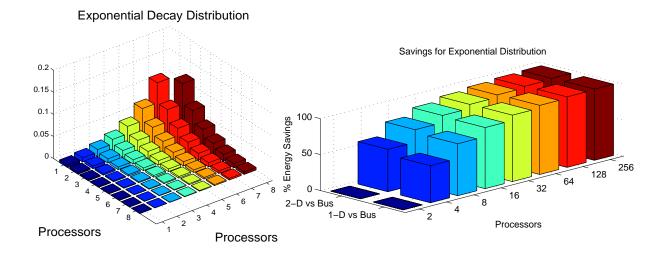

| Fig. 4.6: Energy Consumption Savings Assuming Exponential Distribution (1-D Mesh vs. |

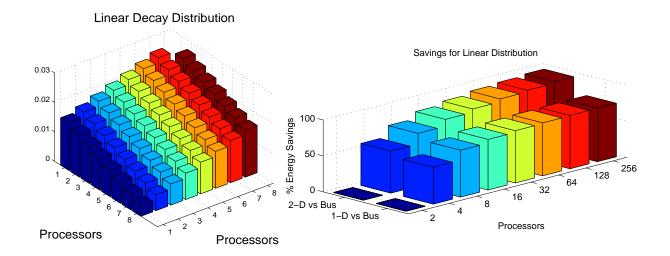

| Bus and 2-D Mesh vs. Bus)                                                            |

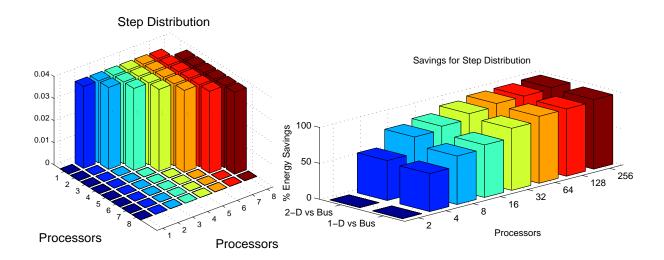

| Fig. 4.7: Energy Consumption Savings Assuming Step Distribution (1-D Mesh vs. Bus    |

| and 2-D Mesh vs. Bus)                                                                |

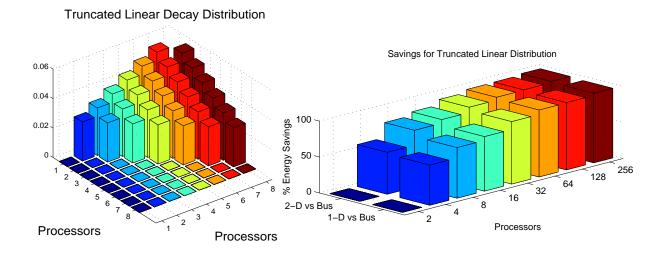

| Fig. 4.8: Energy Consumption Savings Assuming Truncated Linear Distribution (1-D     |

| Mesh vs. Bus and 2-D Mesh vs. Bus)                                                   |

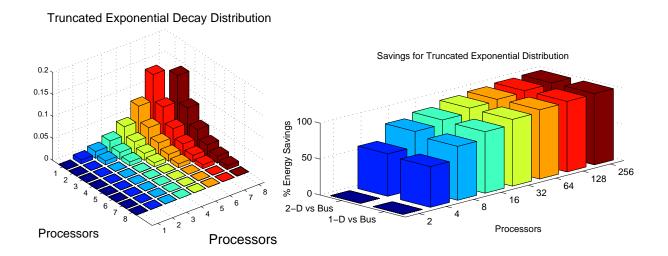

| Fig. 4.9: Energy Consumption Savings Assuming Truncated Exponential Distribution (1- |

| D Mesh vs. Bus and 2-D Mesh vs. Bus)                                                 |

# Chapter 5

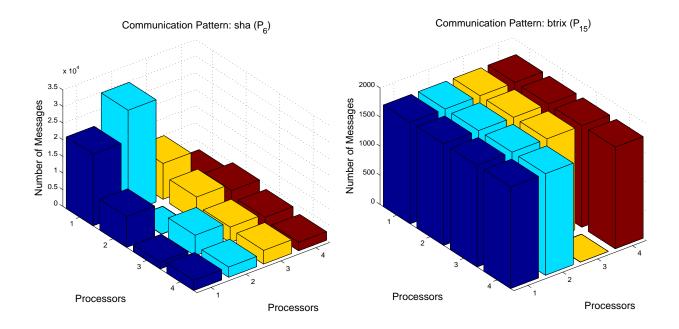

| Fig. 5.1: Number of Messages Transferred from One Processor to Other Processors   | in |

|-----------------------------------------------------------------------------------|----|

| the Network for sha and btrix                                                     | 88 |

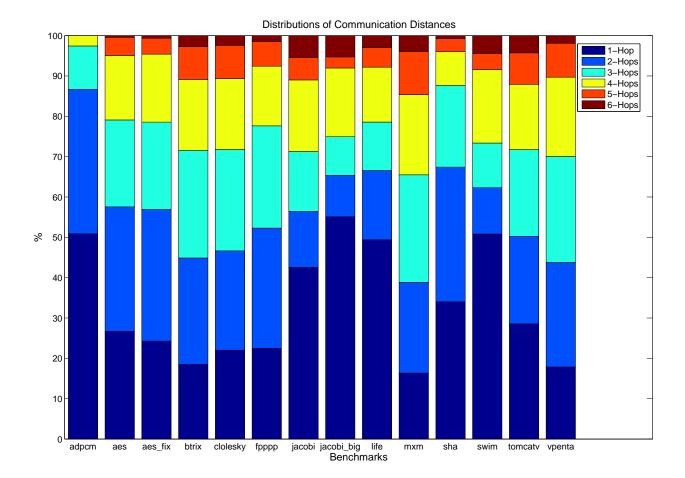

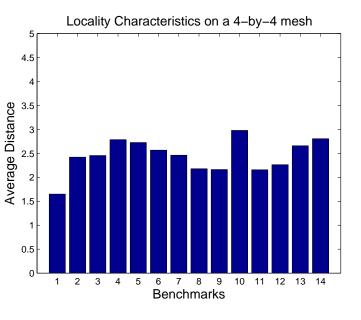

| Fig. 5.2: Distributions of Communication Patterns for All Applications.           | 90 |

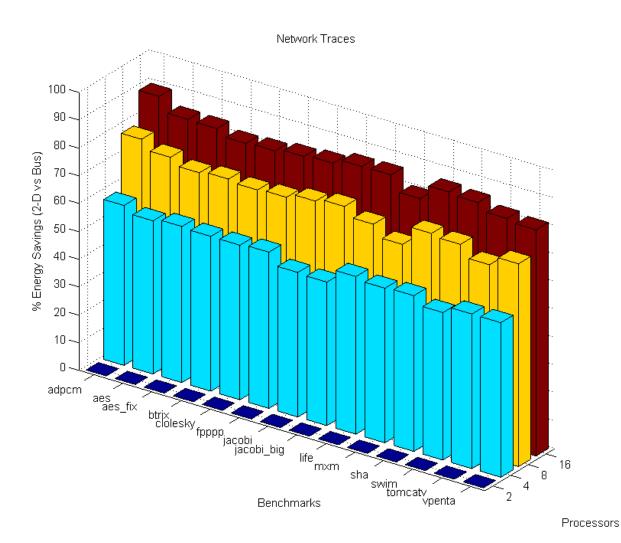

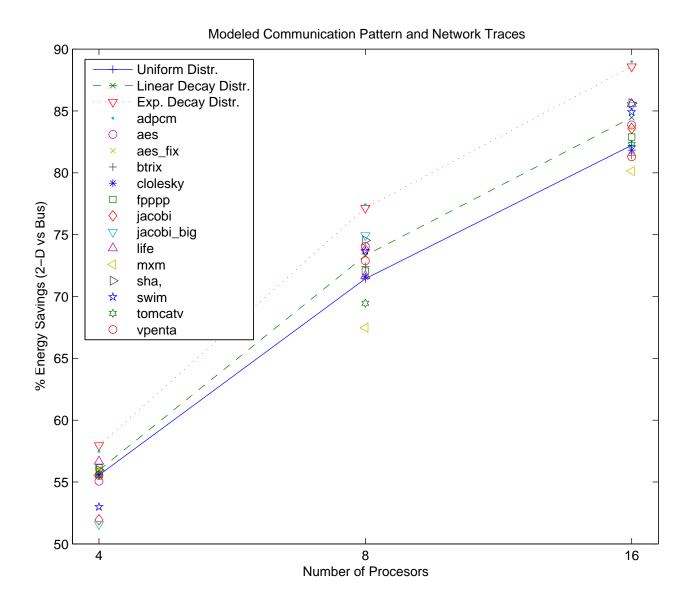

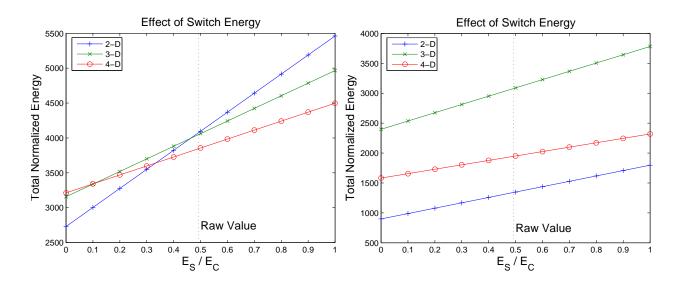

| Fig. 5.3: Savings Over Different Numbers of Tiles for the 14 Applications when No |    |

## Chapter 6

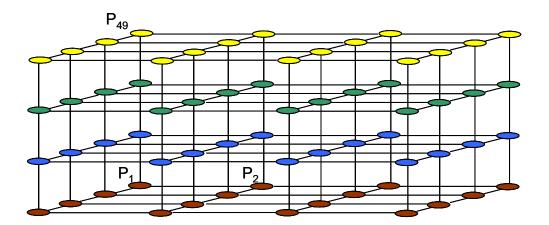

| Fig. 6.1: 64-Tile System Implemented in Three Dimensions. There are 4 Process   | sors in Each |

|---------------------------------------------------------------------------------|--------------|

| Dimension                                                                       | 102          |

| Fig. 6.2: Mapping of the 64 Tiles Into Two Dimensions. The Logical Distance Ber | tween P1 and |

| P49 is 3 Hops and the Physical Distance is 12 "Physical Hops"                   | 103          |

| Fig. 6.3: Energy Comparison for 2-D, 3-D and 4-D Networks with 256 Nodes        | 107          |

### Chapter 7

| Fig. 7.1: Typical Microarchitecture of An On-Chip Network Switch for 2-D Mesh112                    |

|-----------------------------------------------------------------------------------------------------|

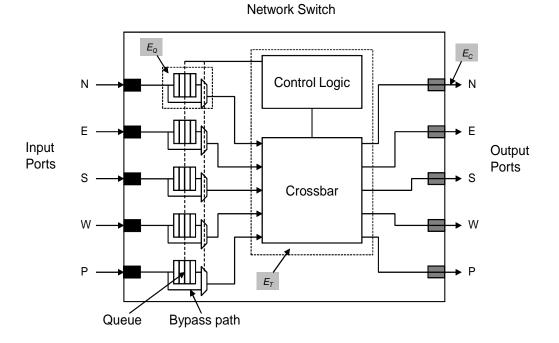

| Fig. 7.2: Physical Placement of the Crossbar, the Control Circuitry, the Input Queue Buffer, the    |

| Channels for the Dynamic Network in Raw114                                                          |

| Fig. 7.3: Expected Energy Consumption of a Message for One Network Hop117                           |

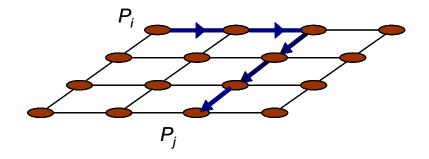

| Fig. 7.4: Example of a Message Route on a 2-D Network118                                            |

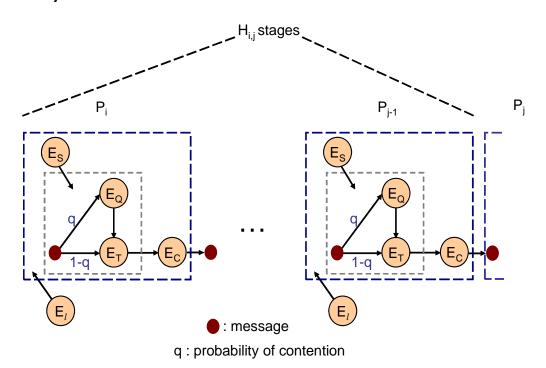

| Fig. 7.5: Process Describing the Total Expected Energy Cost for Moving a Message from Pi to         |

| Pj119                                                                                               |

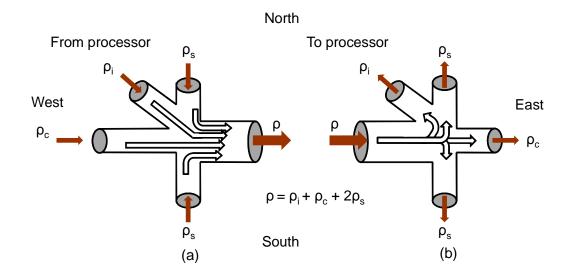

| Fig. 7.6: Channel Utilization at a Switch. The channel utilization r is composed of three           |

| components: ri (messages generated/consumed by the node processor), rc (messages                    |

| continuing to this direction through the switch), and rs (messages switching to this direction at   |

| the switch). (a) shows how r is composed and (b) shows how r is decomposed122                       |

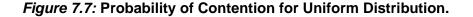

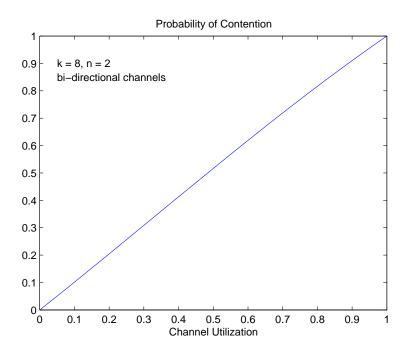

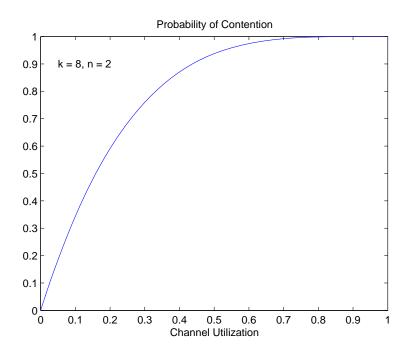

| Fig. 7.7: Probability of Contention for Uniform Distribution124                                     |

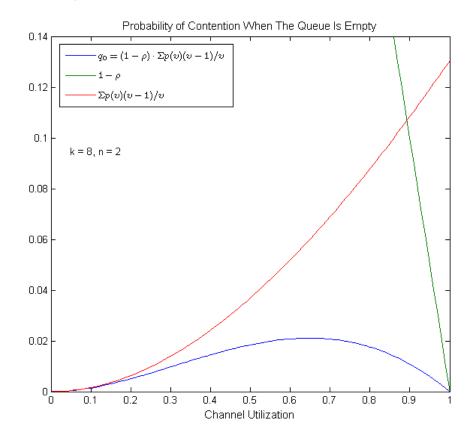

| Fig. 7.8: Probability of Contention for Uniform Distribution when the Queue is Empty.125            |

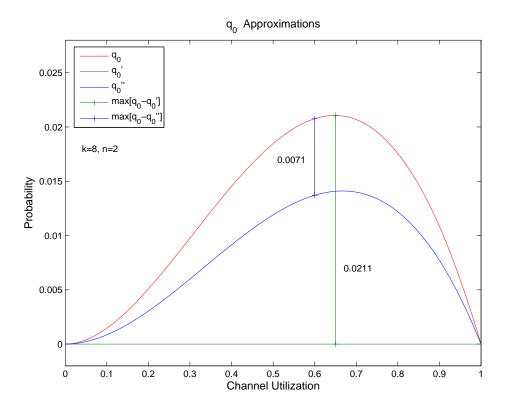

| Fig. 7.9: Approximations of the Probability of Contention when the Queue is Empty for Uniform       |

| Distribution127                                                                                     |

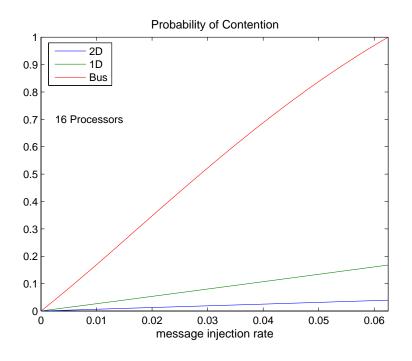

| Fig. 7.10: Probability of Contention for a Two- and One-Dimensional Network, and a Bus-Based        |

| System131                                                                                           |

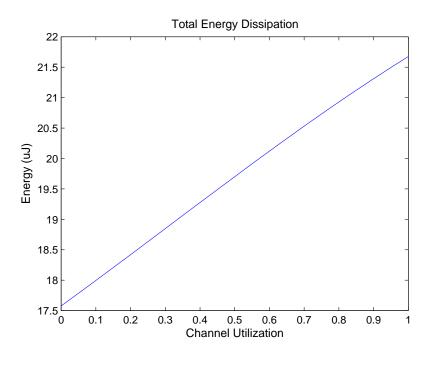

| Fig. 7.11: Total energy consumption in a 8-by-8 system for different values of channel utilization. |

| Each processors transmits 1000 words and processors communicate with equal likelihood with          |

| each other1                                                                             | 33 |

|-----------------------------------------------------------------------------------------|----|

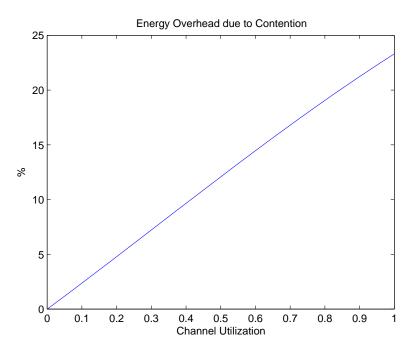

| Fig. 7.12: Energy Overhead due to Contention for the Uniform Distribution               | 35 |

| Fig. 7.13: Probability of Contention for Uniform Distribution in the Raw Static Switch. |    |

| 136                                                                                     |    |

#### Chapter 8

#### Appendix A

| Fig. A.1: Message Path from the East Output of a Tile to the Switch Input Port of the    |

|------------------------------------------------------------------------------------------|

| Neighboring Tile on the East 170                                                         |

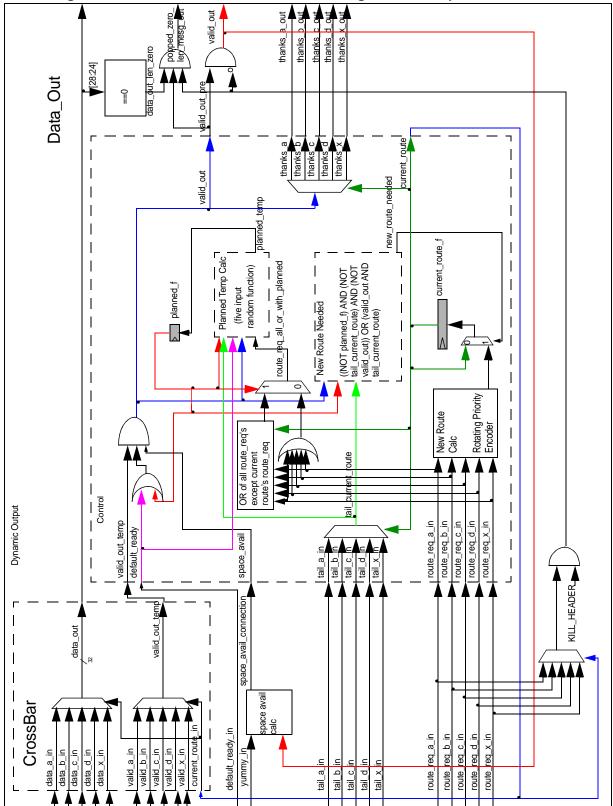

| Fig. A.2: Schematic of Dynamic Output Block. The block includes the CrossBar block,      |

| control logic for the CrossBar and for the control signal to the input block 174         |

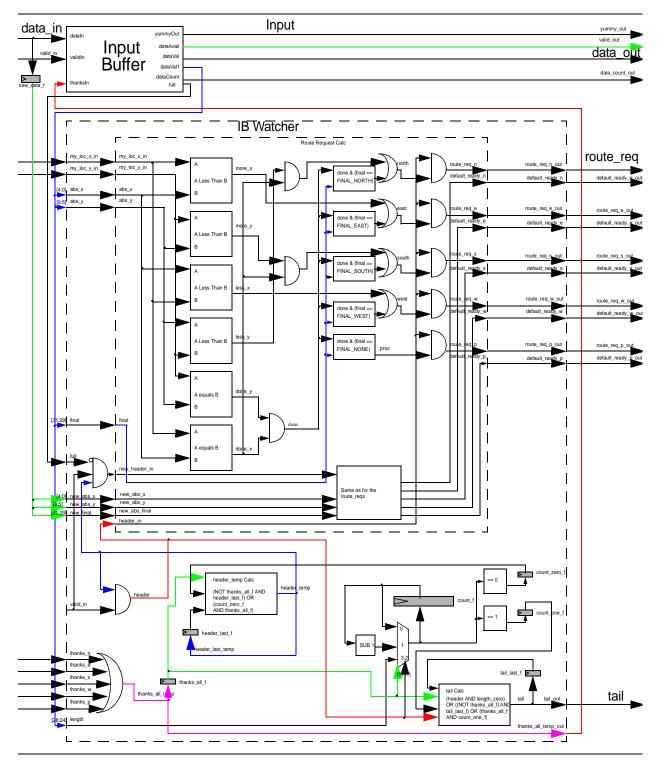

| Fig. A.3: Schematic of Dynamic Input Block. The block includes the Input Buffer, control |

| logic for the Input Buffer and the generation of route_req and tail signals 175          |

#### Appendix B

| Fig. B.1: Communication Pattern: adpcm    | 178 |

|-------------------------------------------|-----|

| Fig. B.2: Communication Pattern: aes      | 178 |

| Fig. B.3: Communication Pattern: aes_fix  | 179 |

| Fig. B.4: Communication Pattern: btrix    | 179 |

| Fig. B.5: Communication Pattern: cholesky | 180 |

| Fig. B.6: Communication Pattern: fpppp      | .180 |

|---------------------------------------------|------|

| Fig. B.7: Communication Pattern: jacobi     | .181 |

| Fig. B.8: Communication Pattern: jacobi_big | .181 |

| Fig. B.9: Communication Pattern: life       | .182 |

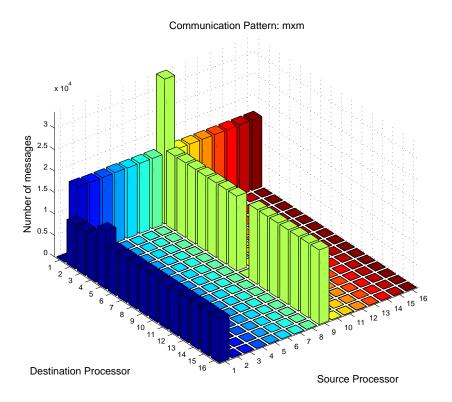

| Fig. B.10: Communication Pattern: mxm       | .182 |

| Fig. B.11: Communication Pattern: sha       | .183 |

| Fig. B.12: Communication Pattern: swim      | .183 |

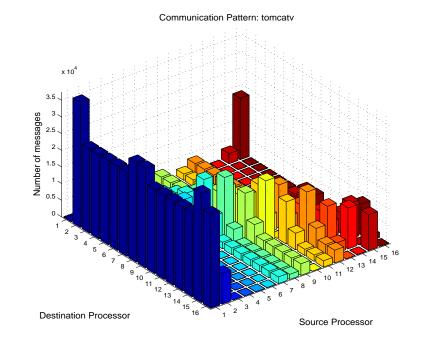

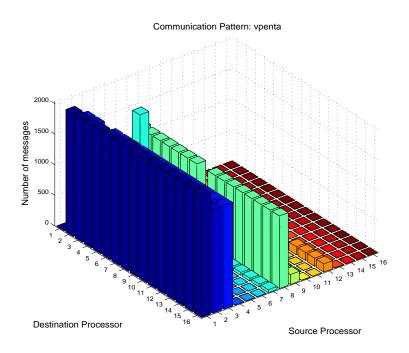

| Fig. B.13: Communication Pattern: tomcatv   | .184 |

| Fig. B.14: Communication Pattern: vpenta    | .184 |

|                                             |      |

# Appendix C

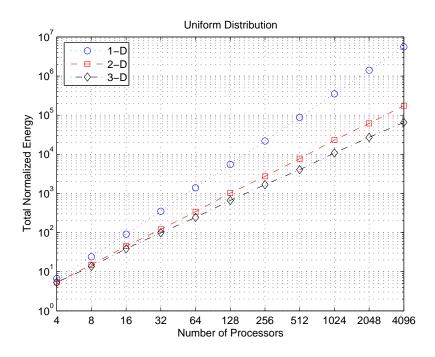

| Fig. C.1: Normalized Energy - Uniform Distribution for 1-D, 2-D and 3-D mesh netw | vorks with |

|-----------------------------------------------------------------------------------|------------|

| same numbers of processors.                                                       | 188        |

# **CHAPTER 1**

# INTRODUCTION

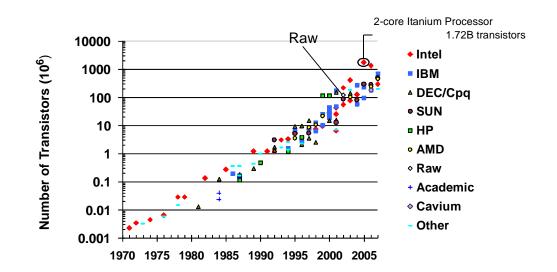

Microprocessor performance has increased dramatically in the last three decades. Moore's Law predicted that the number of transistors in integrated circuits would double every eighteen months. Fig. 1.1 illustrates Moore's Law [22]. The minimum feature size in production integrated circuits has continued on an exponential decline since the first integrated circuit appeared. Moreover, the average selling price per transistor has fallen over six orders of magnitude in the last thirty years [23]. The graph reveals that Moore's Law still holds, despite the escalating technological challenges, which means that the availability of transistors and resources will grow for microprocessor designers. Previously, computer designers have taken advantage of these resources largely to build systems with centralized structures such as superscalar and pipelined processors with caches, due to the simpler programming model compared to systems with distributed structures.

*Figure 1.1:* Transistor Trend [20]. Number of transistors used in microprocessors over the last twenty five years.

Source: ISSCC Proceedings 1971-2007

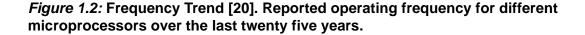

Contrary to the transistor trend shown in the previous graph, the operating frequency trend (Fig. 1.2) reveals that the frequency has reached a maximum in 2004 [21], with the exception of IBM's Power6 microprocessor [59]. Moreover, predictions for the operating frequency in future microprocessors indicate that it has leveled off. The perception of building deeper and more complex pipelines for complex superscalar machines has been mainly driving the microprocessor industry, leading to the increase in the operating frequency.

Power and energy consumption issues, however, have become a limiting factor in modern processors and make the need for different directions in computer architecture imminent. Power and wire constraints will drive processors to explicitly parallel modular architectures ([63], [10]). These constraints have led to the development of several research projects aiming to explore scalable designs such as the MIT Raw microprocessor [1], the Stanford Smart Memories project [26], the Stanford Merrimac-Streaming Supercomputer [27], the MIT Scale project [25], the U. of Wisconsin Multiscalar [30], the UW WaveScalar [28], the UT Austin TRIPS [29], the UC Davis Synchroscalar [31].

Source: ISSCC Proceedings 1971-2007

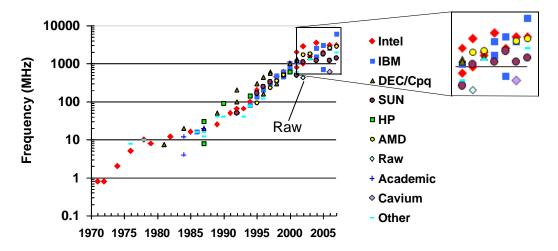

Modern superscalar processors with large out-of-order instruction issue widths, register renaming units, multi-level caches, and other performance-enhancing features have begun to yield diminishing returns on performance. An even more important issue than the operating frequency wall is the tremendous amount of power that such structures typically consume, giving rise to today's power-hungry commercial processors ([9], [15], [16], [17]). The power in modern microprocessors reached a barrier in 2000, as Fig. 1.3 clearly shows. This graph presents the reported power dissipation of microprocessors in the last twenty-five years.

Power consumption and wire delays have limited the continued scaling of centralized systems [63], while making multicore architectures increasingly popular. To emphasize the above statement, Intel cancelled the next step in the Pentium 4 processor line (code name Tejas) in 2004 because of power issues, and they are refocusing on multicore processors to hit new power and performance targets. They have recently announced [49] an 80-tile network-on-chip architecture with a processing engine on each tile. All the major semiconductor companies follow this trend toward multicore solutions; this trend will continue all the way to tiled processor

*Figure 1.3:* Power Trend[20]. Reported microprocessor power consumption over the last twenty five years.

Source: ISSCC Proceedings 1971-2007

architectures as it is one of the most power efficient ways to exploit technology scaling. Tiled architectures use point-to-point interconnection networks for data communication; this thesis shows that point-to-point networks is an energy efficient way to communicate data in systems with multiple cores.

A number of recent studies have shown that implementing architectures that attempt to break up large centralized structures into smaller, more localized ones seems to be an effective way to alleviate both the performance and power scaling issues. Taylor et al. [2] demonstrated that the long wire delay caused by these large centralized structures is effectively mitigated by a tiled architecture. Additionally, Zyuban and Kogge [6] address the above-mentioned power issues by proposing a distributed architecture that is inherently lower-power without compromising performance, while showing that centralized superscalar architectures, even when optimized for energy efficiency, are inherently energy-inefficient.

Tiled processor architectures have been proposed as a way to allow the performance of highperformance microprocessors to scale along with processor designers' exponentially-increasing transistor budgets. They are distributed processor architectures aimed at exploiting fine-grain concurrency, even from a single programmer-specified thread. Tiled architectures reduce power by breaking up computation into multiple independent tasks, which can potentially decrease power consumption without sacrificing performance [7]. They typically incorporate a number of tiles that are replicated across the chip and connected via an on-chip network, thus simplifying VLSI design complexity. Furthermore, intelligent compilers exploit data locality, allowing computation to be scheduled and positioned in such way that communication costs are low, thereby reducing overall power consumption.

Wire delays, power limitations, and complexity limitations are moving VLSI processor designs towards tiled architectures. Tiled processor architectures attempt to mitigate these issues by organizing the processor resources in a more power-efficient manner. For instance, they typically distribute large caches and register files across the chip, keeping the size of each individual structure small. Compilers optimized for and targeted toward tiled architectures exploit data locality and localized computation and can eliminate heavy network activity for operand communication across tiles.

As the demand for on-chip bandwidth between different processing elements in multicore systems scales up, point-to-point interconnection networks are becoming a necessity for on-chip communication. Riding this wave, as the number of processing elements scale up in multicore and tiled processor architectures, the study of on-chip interconnection networks (OCN) — the medium for processor-to-processor or memory communication — becomes extremely important. Although network performance has been extensively studied previously (e.g., [13], [51], [52], [12], [53]), the power and energy of OCNs have not been explored as rigorously. As the energy consumption in OCNs increases [54], energy estimation tools that can provide a comparison of different architectures and applications for various network traffic patterns early in the design cycle become extremely useful to the computer architect.

This thesis proposes an energy analysis framework for on-chip interconnection networks that can serve as a basis to model (a) multi-dimensional point-to-point networks or buses that transfer data between processors, (b) OCNs that connect distributed resources such as caches on chip, or for that matter (c) networks that communicate data between different components, such as ALUs and register files.

This work shows that point-to-point interconnection networks have significant energy advantages over bus-based networks. Our framework demonstrates how energy savings depend on the number of nodes in the network and the degree of communication locality. We present our analysis for a one-dimensional point-to-point network and a bus-based network and show that the one-dimensional OCN results in approximately 66% energy savings over a bus for 16 or more processors, even when the communication patterns are uniformly distributed.

Increasing the network dimensionality to two dimensions results in additional energy savings. We show that for uniformly distributed communication patterns moving from one to two dimensions results in energy savings of  $O(\sqrt{N})$ , where *N* is the number of processors in the system. Applications that exhibit communication locality result in significantly greater energy savings. As an example, the results that use the analytical model and are confirmed with traces of real benchmarks show that the energy of a 2-D OCN can be 10 times lower than that of a bus for 16 processors when the applications show communication locality (e.g., ADPCM), and about 5 times lower better when there is poor locality (e.g., btrix).

With the advent of tiled architectures [1], [26], [28], [56], [31], compilers become increasingly responsible for balancing computational parallelism and communication locality. As such, the resulting communication patterns of applications produce widely differing on-chip network energy consumption. Using network traces from a set of benchmarks compiled and run on a tiled processor, we quantify the degree to which applications with greater communication locality are more energy-efficient.

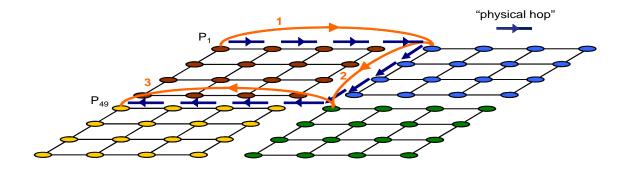

The concept of communication locality is increasingly important in two-dimensional realizations of on-chip networks. The importance occurs because there is a significant trade-off between the energy savings that result from the smaller logical distance between processors and the increased energy dissipation due to the greater wire lengths [12] and hence greater capacitance between processors, as the higher dimensions are mapped into the plane. We investigate this trade-off by comparing the total energy consumption of systems with the same number of processors but with a different dimensionality. For example, we show that for a chip with 256 processing cores, a 2-D mesh is more energy efficient than a 3-D OCN under the condition that the energy of the switch logic is no greater than 0.5 times the energy of a network channel connecting a pair of physically adjacent cores.

Communication locality depends on the examining benchmark as well as on the partitioning and placement of data on the different tiles of the system. Early-stage energy and power estimation of multicore chips is extremely important in providing compilers information in determining the most efficient code partitioning and data and instruction placement across the cores.

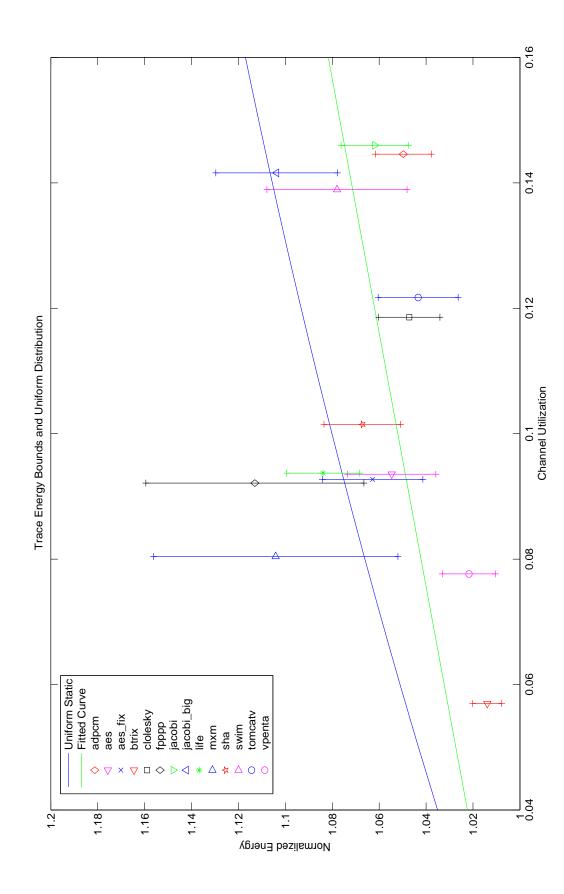

Network contention of network resources results in message delays and increased energy dissipation in the switch, when messages are written into queueing buffers waiting to be serviced by a specific output port. This thesis examines the effect of contention on the energy dissipated in interconnection networks. We derive a closed-form solution for the energy for various channel utilization values assuming processors communicate to each other with equal likelihood. We used energy estimates for the energy dissipated in the interconnection networks in the Raw microprocessor to quantify the energy overhead and showed that the maximum amount of additional overhead paid is 23.3%. Additionally, using network traces we estimate the lower and upper bounds for the energy dissipation in the communication network for the different applications that we examine.

#### **1.1 Contributions**

This thesis proposes a practical analytical model to describe the energy characteristics of onchip networks, demonstrating the importance of computation-communication locality and providing a simple framework for application experts, architects, compilers, and run-time systems to reason about energy-centric properties of their codes and systems.

We demonstrate the use of probability distributions to model various network traffic patterns and show, using these distributions as well as network traces, that the energy dissipation in onchip point-to-point networks is inversely proportional to the distance that messages travel in the network. The examination of the communication characteristics of network traces from applications running on a tiled multicore processor suggests that probability distributions is an effective and accurate way of modeling on-chip traffic patterns. Therefore, our framework can be used to estimate the energy consumption in on-chip interconnection networks without running the applications.

We present a contention energy analysis and derive a set of closed-form equations for the probability of contention in buses, one-, and two-dimensional networks. The analysis suggests that in point-to-point networks the most important and common source of contention for new messages entering a network switch is messages in the switch waiting to be serviced. We show that there is an upper limit on the energy cost expended due to contention and calculate this cost for a tiled multicore processor as 23%.

We estimate the energy dissipation of the different components in the switch using extracted capacitance values from the layout of a tiled processor. We follow the path of a message from the output of one tile to the output of the neighboring one and estimate the energy dissipation in the channels that connect the two tiles, the logic circuitry that generates the control signals required for routing the message from the switch input to the output, and the input queue buffer where the message is stored when it suffers contention.

This thesis differs from previous work on energy analysis of OCNs [36], [39], [41], [42], by making the following unique contributions:

#### (1) Energy Analysis Framework

This work proposes an energy analysis framework for on-chip interconnection networks that can serve as a basis to model: (a) multi-dimensional point-to-point networks or buses that transfer data between processors; (b) OCNs that connect distributed resources such as on-chip caches; or for that matter (c) networks that communicate data between different components such as ALUs and register files.

We develop a framework for the energy analysis of OCNs that can be used with any topology (buses, tori, meshes, etc.) and arbitrary communication patterns (uniform, truncated exponential, patterns measured from a real workload, etc.).

We present a set of probability distributions to model various traffic patterns that closely match the communication characteristics of various benchmarks. These distributions can be used to represent any level of locality among the processors in the system and have a true point-to-point nature.

We propose the use of the analytical framework to compare the energy performance of a centralized multi-bank cache organization (or any centralized structure for that matter) to a tiled architecture that arranges cache memories across the total chip area.

#### (2) Extensive Use of Real Network Traces

In the analysis, we extensively use real network traces from benchmarks running on the Raw microprocessor to compare the energy performance of OCNs and to validate the analytical model. Using both the analytical model and network traces, we quantify the positive impact of communication locality on the energy dissipated in the on-chip interconnection network.

If we can estimate what the communication among tiles would look like, we can model these communication patterns and have interconnection network energy reports using our framework without running the applications and recording the network traces. Benchmark simulation can be expensive and not extremely useful if the designers are in the phase where they are making architectural decisions.

#### (3) Contention Energy Analysis

We analyze the effect of contention on OCNs to the total energy consumption and propose message scheduling advice that reduces the energy overhead of network delays. We derive a closed-form solution for the energy dissipation on the network for various values of channel utilization and calculate the energy overhead of contention on the total energy dissipation in point-to-point interconnection networks.

Additionally, using information collected from applications running on the Raw multicore processor we present upper and lower bounds of the energy dissipated on the raw network for scalar operand communication.

#### (4) Network Hardware Components Energy Estimates

The thesis presents a detailed analysis of the energy costs of a switch. We follow a low level approach in our methodology based on capacitance values from the Raw microprocessor dynamic networks. For wiring and metal capacitance values, we use the extracted capacitance values generated by the IBM ChipEdit capacitance extractor tool for the final layout of the Raw microprocessor. For the cell input and output capacitances we use the values provided by IBM for their cells in the SA-27E process. We show that the measured

values for channel energy, switch control logic energy, and switch queue buffer energy are 34.5pJ, 17pJ, and 12pJ, respectively.

#### (5) Network Switch Analysis

We investigate the effect on energy of two-dimensional realizations of high-order networks (three- and four-dimensional networks) and examine the effect of switch energy and wire lengths under various traffic pattern assumptions, highlighting the trade-offs between the logical and physical distance between processors in the system.

We examine how the choice of the most energy-aware network topology is based on the communication locality inherent on the application by comparing the total energy consumption of a two-, three, and four-dimensional network for applications that exhibit different locality characteristics.

#### (6) Analysis Results Comparing Buses, 1-D, and 2-D Networks

The framework compares the energy of buses, 1-D, and 2-D point-to-point networks, including the impact of wire lengths and related capacitance, and communication locality. We quantify the energy savings moving from bus-based architectures to point-to-point topologies for applications that exhibit no communication locality, as well as other applications with various levels of locality.

## 1.2 Thesis Roadmap

The remainder of the thesis is organized as follows:

Chapter 2 gives a background on the MIT Raw Microprocessor and presents other existing tiled processor architectures.

- Chapter 3 describes our energy analysis framework and presents an analysis of the energy advantages moving from a bus-based system to a one-dimensional point-to-point interconnected system. We present two simple interconnection models and investigate the power performance for various communication patterns. We derive closed-form equations that describe the energy savings of the point-to-point networks compared to bus-based systems and investigate the effect of locality of communication on the total energy dissipation. In our analysis, we use different probability distributions to model various locality characteristics for the traffic patterns on the interconnection network.

- Chapter 4 moves the analysis of Chapter 3 to two-dimensional interconnection systems. We analyze the communication costs for a uniform and for various localized traffic patterns. We provide formulas that explain the relation between the energy dissipated on a two-dimensional point-to-point interconnection network and onedimensional point-to-point networks as well as bus-based systems.

- Chapter 5 provides a validation of our model using network traces from benchmarks running on the Raw [1] microprocessor for different tile configurations. We examine the different locality characteristics of the network traces and their effect on the total energy dissipated.

- **Chapter 6** examines the energy characteristics of high-dimensional networks. We enhance our model to accommodate any realization of high-order networks, after they are mapped into a two-dimensional substrate. We investigate the effect of the logical and physical distances between two processors on the total energy for communication, assuming traffic patterns that allow localized and non-localized communication.

- **Chapter 7** presents an analysis of the effects of network contention to the total energy dissipation in on-chip interconnection networks. In our analysis we use energy costs for

major components of a network router, that are based on an actual fabricated switch, the network switch of the Raw microprocessor. We calculate the probability of contention on a specific output port assuming different channel utilization patterns. Furthermore, we provide energy estimates for the total energy consumption on the interconnection network, taking into account the probability of contention on every node of the system assuming a uniform distribution for the communication among processors. We extend our analysis to provide upper and lower bounds of the energy consumption in the Raw networks for different benchmarks running on a 16-tile configuration.

- **Chapter 8** describes possible future directions of this study.

- Chapter 9 presents the related work on high-level power and energy estimation tools and describes the differences between each work compared to the work presented in this thesis.

- Chapter 10 concludes the thesis.

- **Appendix A** describes the methodology for estimating the energy costs for the various components of the network switch for the Raw microprocessor. These energy costs are used in the contention analysis in Chapter 7.

- **Appendix B** presents graphs with the communication patterns evident in the applications that we examine in this thesis.

- **Appendix C** presents an analysis for the energy estimation for a point-to-point network implemented in three dimensions.

# **CHAPTER 2**

# BACKGROUND

The energy analysis of interconnection networks has a direct application to tiled processor architectures. With process scaling and increasing number of cores in multicore systems, pointto-point interconnection networks are becoming a necessity for on-chip communication, as the demand for on-chip bandwidth between different processing elements scales up.

This chapter presents existing tiled processor architectures that can utilize our framework to perform high-level calculations on the energy dissipated on the interconnection networks. We examine the following multiprocessor projects: the MIT Raw microprocessor [1], the Stanford Smart Memories project [26], the U. of Wisconsin Multiscalar [30], the UW WaveScalar project [28], the UT Austin TRIPS [29], and the UC Davis Synchroscalar project [31]. The reader familiar with the Raw microprocessor and tiled processor architectures can proceed to Chapter 3.

The first challenge of tiled architectures [34] is to determine the best allocation of silicon resources among the computing, memory and communication needs. The second challenge is determining the granularity and the number of the tiles of the system. Addressing these problems calls for several models. The optimal balancing and evaluation of all the design trade-offs require an architecture model, an application model as well as a cost model.

### 2.1 The Raw Microprocessor [1]

This section describes the MIT Raw Microprocessor. Raw is a research architecture design undertaken by the MIT Raw research team and was fabricated by IBM. We provide a more detailed description of Raw compared to the other tiled processor architectures, because in future chapters we will be using some of its network components for energy characterization as well as network trace information collected from various benchmarks running on the Raw microprocessor.

The network traces provide relevant information on the traffic volume, distance, and locality of communication. They are not particular reflective of contention.

#### 2.1.1 Overview and Design Philosophy

The Raw architecture exposes the details of the hardware to the programmer (or the compiler) making parallelism explicit, instead of using expensive hardware structures to hide the true nature of the processor. For example, the software should specify separate instruction streams for each functional unit.

Additionally, Raw eliminates large, centralized structures for the purpose of scalability. In traditional superscalar processors, the area and delay of structures like bypass networks and register files grow with the square or cube of the issue width. As these structures grow, the wires within them grow to the point that a signal can no longer traverse them in a single clock cycle. In that case, additional pipeline stages should be added or the clock frequency must be reduced.

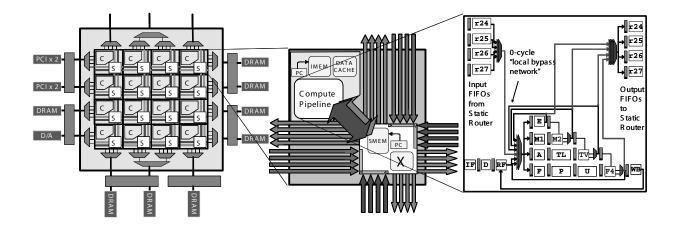

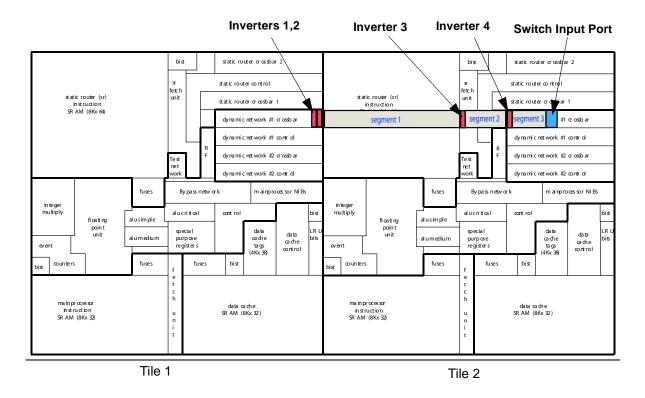

*Figure 2.1:* The Raw Microprocessor. A Raw processor consists of a 2-D array of uniformly replicated tiles, each containing a MIPS-style processor and two types of network routers to connect it to the neighboring tiles.

Raw on the other hand retains only the essential hardware, enabling the placement of many more functional units on chip than a superscalar can. Using distributed computational elements, the Raw architecture addresses scalability.

Besides the advantages of scalability and efficient use of die area, a Raw processor is significantly cheaper and easier to build than a monolithic superscalar. All of the tiles are identical and relatively simple. The effort required to build a Raw processor is essentially the same as that required to build a single tile.

#### 2.1.2 The Processing Core

Fig. 2.1<sup>1</sup> illustrates the basic architectural characteristics of Raw. The tiles are interconnected by four 32-bit full-duplex on-chip networks, consisting of over 12,500 wires. Two of the networks are static (routes are specified at compile time) and two are dynamic (routes are specified at run time). Each tile is connected only to its four neighbors. Every wire is registered at the input to its destination tile, which means that the longest wire in the system is no greater than the length or

<sup>1.</sup>Reproduced with permission from Michael Taylor

width of a tile. The tile is sized so that a signal travels through a small amount of logic and across the tile in one clock cycle. This property ensures high clock speeds, and the continued scalability of the architecture.

The Raw chip is divided into an array of 16 identical uniformly-replicated programmable tiles. A tile contains an 8-stage, in-order, single-issue MIPS-style processing pipeline, a 4-stage singleprecision pipelined FPU, a 32KB data cache, two types of communication routers, static and dynamic, and 32KB and 64KB of software-managed instruction caches for the processing pipeline and static router respectively. These tiles are general purpose in nature and each can run its own independent instruction stream.

The exposed ISA allows parallel applications to exploit all of the chip resources, including gates, wires and pins. While obviously conducive to data- and task-level parallelism, Raw supports instruction level parallelism by spreading computation across cores and scheduling operands over the low-latency static networks. The Raw compiler can do this automatically managing the effect of wire delays by orchestrating both scalar and stream data transport.

#### 2.1.3 Communication Networks

The Raw processor has four 32-bit bi-directional on-chip mesh networks. There are two types of networks, *static* and *dynamic*. The two static networks are statically scheduled and explicitly managed. The two dynamic networks are routed dynamically at run-time.

#### Static Networks

The static networks provide a low-latency, high-bandwidth connection between the tiles. They are intended for known communication that can be statically scheduled at compile time. The static router can be directly programmed to control the flow of data on the static networks.

Each static network provides a 32-bit full-duplex network link between each tile processor, its next neighbor, and the other static network. These networks are register-mapped and integrated

into the bypass network in each processing pipeline. This results in high-speed communication on the static network with an ALU-to-ALU latency of 3 cycles, between two neighboring tiles.

In the thesis we will be using trace information from the static networks for different benchmarks running on Raw. Those traces are for operand communication between tiles. There is an approximate cost of 504pJ [42] due to cache accesses but in our analysis we will not account cache energy.

#### **Dynamic Networks**

The second type of communication network on Raw is dynamic. There are two completely separate identical dynamic networks: the MDN (memory dynamic network) and the GDN (general dynamic network). The dynamic networks handle traffic which is not statically predictable such as cache misses, external interrupts, and data dependent communication patterns. The MDN is used for accessing on-chip resources including memory, the interrupt controller, and I/O devices. In contrast, the GDN may be used freely by an application. Since GDN usage is unrestricted, there is the potential for it to deadlock due to overflow of receive buffers, but the GDN has deadlock recovery mechanism.

The dynamic networks are dimension-ordered, wormhole-routed networks. Each message on the dynamic network consists of a header word with information about the message and up to 31 data words. Information specified in the header work includes the message length and type, as well as the destination tile. The messages travel in the network first in the X dimension and then in the Y dimension, causing the routers along the path to create a worm-hole for the remaining message. The routers forward the remaining words of a message until the whole message has passed by. Then, they are free to examine their input buffer queues to start servicing other messages.

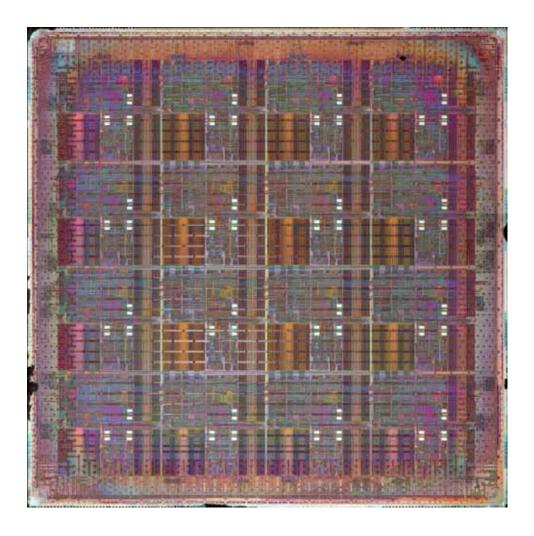

#### Figure 2.2: Raw Die Photo

#### 2.1.4 Raw Implementation

The Raw multicore processor was implemented in IBM's 180nm, 6-layer copper, CMOS 7SF standard-cell ASIC process. The choice of 16 tiles was determined by the die size available. The die area is 18.2mm X 18.2mm, although the tiles take up only 16mm X 16mm of this area. The larger die size was necessary to accommodate the column grid array (CGA) package in order to achieve a higher pin count. The package has 1657 total pins of which 1080 pins are available for use as high speed transceiver logic (HTSL) I/O pins. Fig. 2.2 shows a die photo of the entire 16 tile Raw processor.

#### 2.1.5 Energy Summary

Kim et al. [42] present measurements of energy consumption in the Raw microprocessor. In their study they show that on idle state (when the clock is grounded) the chip draws a leakage current of 28mA and dissipates 45mW.

Additionally, they examined the average current of an application with average instruction mix running on a single Raw tile, which showed that the compute power consumes a very small fraction of the power compared to the clock power. Therefore, they concluded that implementing clock-gating at the tile-level is highly desirable for tiled architectures.

The work in [42] continued examining the energy costs of communication over the two types of network in the Raw multicore processor. The measured numbers for the static and dynamic networks are 85pJ and 90pJ, respectively. Both numbers are measured for a maximum toggle-rate per word; consecutive words injected to network would cause the channel lines to alternate on every cycle, so these values correspond to the maximum energy dissipation per cycle. This thesis describes a methodology in Appendix A that calculates the average and maximum energy costs per hop for the dynamic network; these values are 51.5pJ and 89pJ, respectively.

A more detailed discussion of the microprocessor can be found in [1], [2], [3], [19], [63].

## **2.2 Tiled Architectures**

In this section we present a brief overview of other academic projects on tiled processor architectures.

#### 2.2.1 The Stanford Smart Memories Project [26]

The Stanford Smart Memories project is a research effort to design a single-chip computing element which provides configurable hardware support for diverse computing models and maps efficiently to future wire-limited VLSI technologies. Smart Memories is a partitioned, explicitly parallel, reconfigurable architecture for use as a future universal computing element. Finding a

single topology that fits well with all applications, which have different communication patterns and memory needs, is very difficult. With Smart Memories the appearance of the on-chip memory, interconnection network, and processing elements is tailored to better match the application requirements.

There are 64 tiles on a Smart Memories chip. Each tile contains processing, memory and communication resources. The tile processor is a 64-bit processor and the instruction and data accesses are interleaved on to tile crossbar on alternate phases of the clock. Four tiles form a quad. The 16 quads communicate over a global network. The intra-quad interconnect has four 64-bit phase-pipelined broadcast buses, which can be statically or dynamically allocated.

Smart Memories is designed to efficiently support different programming models to allow applications be programmed and run in the model that gives the best performance and programming ease. Different programming models are supported in the Smart Memories system by reconfiguring memory system to provide the memory access requirements for each model. The three major programming models are: the shared memory, multi-thread mode [48], the streaming mode, and the transactional coherence and consistency model.

#### 2.2.2 The UWM Multiscalar [30]

Multiscalar processors use an aggressive implementation paradigm for extracting large quantities of instruction level parallelism from ordinary high-level language programs. A single program is divided into a collection of tasks by a combination of software and hardware. The tasks are distributed to a number of parallel processing units which reside within a processor complex. Each of the parallel processing elements operates on its task using its own program counter and physical copy of the single logical register file. Register results are dynamically routed among the many parallel processing units with the help of compiler-generated masks.

Memory accesses may occur speculatively without knowledge of preceding loads or stores. Addresses are disambiguated dynamically, many in parallel, and processing waits only for true data dependencies. Data dependencies are resolved by a combination of hardware and software, with hardware being given more responsibility compared to currently used instruction level parallelism paradigms.

#### 2.2.3 The U. of Washington WaveScalar [28]

WaveScalar is a dataflow instruction set architecture and execution model designed for scalable, low-complexity/high-performance processors. The WaveScalar ISA is designed to run on an intelligent memory system. Each instruction in a WaveScalar binary executes in-place in the memory system and explicitly communicates with its dependents in dataflow fashion. Conceptually, a WaveScalar binary is the dataflow graph of an executable and resides in memory as a collection of intelligent instruction words. Each instruction word is intelligent, because it has a dedicated functional unit. In practice, since placing a functional unit at each word of instruction memory is impractical, an intelligent instruction cache called a WaveCache, holds the current working set of instructions and executes them in place.

WaveScalar architectures cache instructions and the values they operate on in a WaveCache, a simple grid of "alu-in-cache" nodes. By co-locating computation and data in physical space, the WaveCache minimizes long wire, high-latency communication.

The WaveCache is a grid of approximately 2K processing elements (PEs) arranged into clusters of 16. Each PE contains logic to control instruction placement and execution, input and output queues for instruction operands, communication logic, and a functional unit. Each PE also contains buffering and storage for 8 different instructions, bringing the total WaveCache capacity to 16 thousand instructions, which is equivalent to a 64KB instruction cache in a modern RISC machine. The input queues for each input require only one write and one read port and as few as

2 entries per instruction, or 16 entries total. The input queues are indexed relative to the current wave and a small, multi-ported RAM holds full-empty bits for each entry in the input queues. Matching logic accesses and updates the bits as new inputs arrive, obviating the need for content addressable memories.

Within a cluster, the processing elements communicate via a set of shared buses. Tiles within the same cluster receive results at the end of the clock cycle in which they were computed. Cluster size is one of the key architectural parameters of the WaveCache. Larger clusters require more wires and more area for intra-cluster communication, while smaller clusters increase intercluster communication costs.

For inter-cluster communication, the WaveCache uses a dynamically routed on-chip network. Each hop in the network crosses one cluster and takes a single cycle.

### 2.2.4 The UT-Austin TRIPS architecture [29]

The TRIPS architecture is an example of an Explicit Data Graph Execution (EDGE) architecture that supports a static placement, dynamic issue (SPDI) execution model. EDGE architectures, unlike RISC and CISC instruction sets, explicitly encode dependencies into individual instructions. This encoding permits dataflow-like execution without the hardware overheads of conventional out-of-order processors, in which the hardware must reconstruct dependences on the fly.

The TRIPS architecture is hierarchical with a system composed of multiple TRIPS chips, and each chip composed of multiple processing and memory elements. A TRIPS chip includes 8 processors, a collection of on-chip secondary memory arrays, and off-chip channels to external DRAM and other TRIPS chips. Each processor employs a Grid Processor Architecture consisting of an 8x8 array of ALUs, a local register file, local instruction and data caches, and control circuits. Both the grid processor and the memory arrays are configurable to enable efficient

execution of multiple program domains. The chip also includes a sensor network and a small embedded monitor processor to dynamically detect application behavior and changes in system behavior. This information is fed back to the runtime system, the application, and the compiler for on-line optimization.

TRIPS programs are compiled into graphs of predicated hyperblocks, each of which is represented internally as a dataflow graph, with instructions communicating directly though instruction-encoded dependences. Each hyperblock has a set of input and output registers, which is how communication occurs between them. The TRIPS architecture supports up to a maximum of eight 128-instruction hyperblocks executed on a processor core simultaneously, thus enabling a 1,024 instruction window.

### 2.2.5 The UC Davis Synchroscalar [31]

Synchroscalar is a tile-based architecture for embedded processing. It is designed to provide the flexibility of DSPs while approaching the power efficiency of ASICs. This goal is achieved by providing high parallelism and voltage scaling while minimizing control and communication costs. Specifically, Synchroscalar uses columns of processor tiles organized into statically-assigned frequency-voltage domains to minimize power consumption. Furthermore, while columns use SIMD control to minimize overhead, data-dependent computations can be supported by extremely flexible statically-scheduled communication between columns.

## Summary

This chapter presented a brief overview of current academic tiled processor architecture projects. The most common feature of tiled architectures is the distribution of the silicon resources across the chip area. The lack of centralized control and centralized structures enables scalability for these designs.

Another major common characteristic of tiled architectures is the desire for data locality for improved performance and power dissipation savings. However, it is obvious from examining the diversity of the projects presented, that there is no "best" allocation of computing, memory or communication resources. The diversity of applications along with architectural trade-offs and design costs determine how VLSI resources are distributed.

# **CHAPTER 3**

# **A FRAMEWORK FOR ENERGY ANALYSIS**

This chapter develops a framework for energy analysis in on-chip interconnection networks. We present an analysis of two simple processor interconnection models, a bus-based model and a point-to-point network model. Initially we develop our model for a one-dimensional mesh network (we examine two-dimensional and higher-dimensional networks in Chapter 4 and Chapter 6) and present the advantages of point-to-point interconnection network systems compared to busbased systems in terms of energy consumption, assuming different network traffic characteristics.

We present the workload model and the two interconnection models. Then we describe the network traffic patterns that we apply to the point-to-point model. For each pattern we calculate the total communication energy and compare it with the energy consumed in the bus-based model. We derive closed-form equations that describe the energy savings of the point-to-point

model assuming a uniform communication distribution (when processors communicate with equal likelihood) and investigate the effect of locality of communication on the total energy dissipation.

## 3.1 Energy Analysis Framework

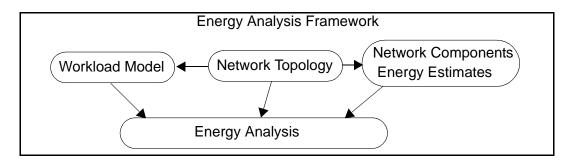

Fig. 3.2 describes the energy analysis framework that we propose.

*Figure 3.1:* Energy Analysis Framework. The framework considers the network topology, the workload model, and energy estimates of the network components to calculate the energy dissipated in the interconnection network.

The framework takes into account the topology and size of the interconnection network (mesh, ring, torus etc. and the number of processors), the workload model (number of messages sent by each processor in the network and traffic patterns in the network), and estimates of the energy of the network components (energy expended in the channels and the switch) to calculate the energy dissipation in the interconnection network.

The network topology also feeds the workload model and the network hardware energy estimates components of the framework. For example, processors might not communicate frequently if they are not physically located close to each other. Additionally, the number of processors in a bus-based system affects the total energy cost for accessing the bus.

## 3.2 Workload Model

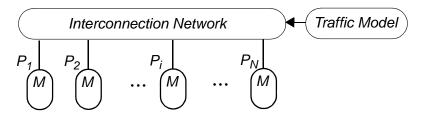

Fig. 3.2 describes our workload model.

*Figure 3.2:* Workload Model. There are *N* processors in the network. Each processors wants to transmit *M* data words. The processor communication patterns are specified by the traffic model.

Our system consists of N processors ( $P_1, ..., P_N$ ). The N processors are connected with an interconnection network. Our model does not exclude traffic patterns with unequal loads; however, we assume here for simplicity that each processor wants to transmit M data words as messages<sup>1</sup>. The M data words have as their destination other processors of the system. Applications that run on the system result in different data communication among processors. The different communication patterns are described by the traffic model.

# **3.3 Bus Interconnection Model**

Fig. 3.3 depicts a simple bus-based machine model that we use in this analysis.

# *Figure 3.3:* Bus-Based Model. There are *N* processors in the system. Each processor wants to transmit *M* data words.

In the bus model, when a processor transmits a data word, the data is available throughout the entire length L of the bus. The bus width is assumed to be a data word. After all the processors

<sup>1.</sup>We will mention how to model unequal traffic patterns, but will not analyze it in detail.

have sent their data, the total energy consumption  $E_{BUS}$  on the bus will be given by

$$E_{BUS} = M \cdot N \cdot E_L, \qquad 3.1$$

where  $E_L = \frac{1}{4}C_L V_{DD}^2$  is the average energy cost of accessing the bus,  $C_L$  is the total capacitance of the bus, and  $V_{DD}$  is the supply voltage.

The total energy supplied by an inverter for a low to high transition is  $C_L V_{DD}^2$  [11]. Half of it is stored on the bus line as electrical capacitive energy and the remainder is dissipated as heat in the inverter output resistance. If the bus line is high, then no additional energy is required from the inverter to pull it high.

If the bus line is high and the inverter pulls it low, then there is no additional energy supplied by the inverter, but the stored energy on the bus line  $(C_L V_{DD}^2/2)$  is dissipated as heat in the inverter pull-down. If the bus line is low and the inverter pulls it low then there is no exchange of energy. The average of these cases is  $C_L V_{DD}^2/4$ . Even with repeaters, the total energy remains the same and only the bus delay changes.

### 3.4 Point-to-Point Interconnection Network Model

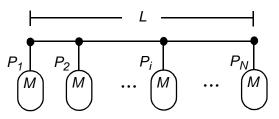

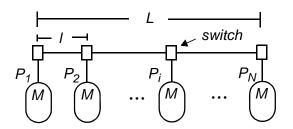

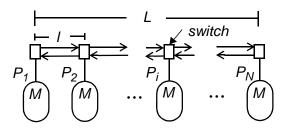

Fig. 3.4 shows the point-to-point model, where N processors are interconnected with a onedimensional mesh network.

The total length of the bus is split into N-1 segments, each having length l and capacitance  $C_l$ ; the width of each segment is also assumed to be a data word. When processor  $P_i$  wants to send data to processor  $P_j$ , the data are available only at the segments that connect  $P_i$  with  $P_j$ , and each switch is responsible for re-transmitting the data or sending them to the attached processor.

*Figure 3.4:* Point-to-Point Interconnection Network Based Model. There are *N* processors in the network. Each processor wants to transmit *M* data words. The switch is responsible for re-transmitting the data or sending them to the attached processor.

We will derive the general form for energy for any point-to-point network, and then specialize for a one-dimensional network.

The total energy  $E_{P2P}$  when all processors have transmitted their data in any point-to-point network is given by

$$E_{P2P} = \sum_{i=1}^{N} \sum_{j=1}^{N} E_{i,j},$$

3.2

where  $E_{i,j}$  is the energy consumption due to transmitting of all data words that have as source processor  $P_i$  and destination processor  $P_j$ . The total energy as well as  $E_{i,j}$  depend on the processor communication pattern. Eq. 3.2 applies to any one-, two- or high-dimensional point-topoint network. It is clear that  $E_{i,j} = 0$ , if  $P_i$  never sends a message to  $P_j$ .

For the remaining analysis, we assume that the network is bi-directional and that there are no end-around connections (Fig. 3.5). In other words, there are separate word-wide physical channels in both directions.

## **3.5 Traffic Distributions**

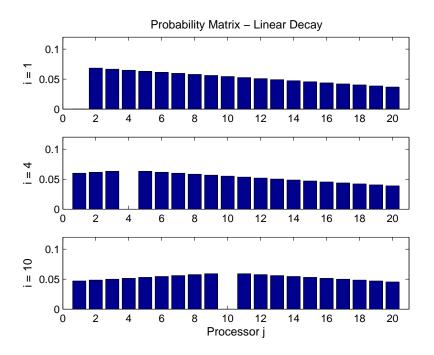

We examine six different probability distributions (uniform, linear decay, exponential decay, step, truncated linear decay, and truncated exponential decay) to model the traffic of the data for each processor. We investigate the effect of these network traffic distributions on the energy consumption for the point-to-point network model. We want to observe non-localized communication patterns, as well as localized ones. To model traffic patterns with various locality characteristics, we apply distributions that allow communication among all processors (linear decay and exponential decay), as well as distributions that allow communication, truncated linear decay, and truncated exponential decay).

In Chapter 5 we incorporate into our framework traffic patterns taken from benchmarks running on the Raw microprocessor. At this point, our analysis ignores contention; doing so works in favor of the energy dissipation of the bus-based system; we show in Chapter 7 that contention in bus-based system is significantly greater compared to the contention in point-topoint networks. Even under the assumption of no contention, we will show that the energy efficiency of point-to-point networks is significant compared to bus-based systems.

### 3.5.1 Communication Energy Cost

If  $E_i$  is the energy cost of accessing a channel for one network hop and  $p_{i,j}^{1}$  is the probability that processor  $P_i$  communicates with processor  $P_j$  for a given data word, the expected energy cost  $E_{i,j}$  of communicating data from processor  $P_i$  to processor  $P_j$ , for this network model, is given by

<sup>1.</sup>We define the probability  $p_{i,j}$  as the probability that processor  $P_i$  communicates with processor  $P_j$ , where  $p_{i,j}$  satisfies  $\sum_{j=1}^{N} p_{i,j|i=I} = 1$ ,  $p_{i,j} = 0$  for i = j, and I = 1, 2, ...N. The set of  $p_{i,j}$  defines a communication probability matrix p.

$$E_{i,j} = M \cdot p_{i,j} \cdot E_l \cdot H_{i,j}, \qquad 3.3$$

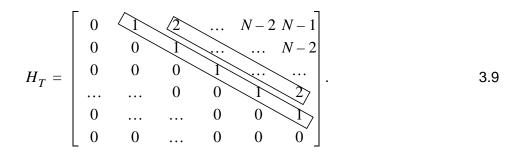

where each element  $H_{i,j}$  (Eq. 3.4) shows the number of hops the data make when transmitted from processor  $P_i$  to processor  $P_j$ . The expected number of messages that  $P_i$  sends to  $P_j$ under the communication pattern described in the probability matrix p is  $M \cdot p_{i,j}$ . We assume that the probability  $p_{i,j}$  is independent and identical for each data word sent from  $P_i$  to  $P_j$ . For a one-dimensional network matrix with no end-around connections H is given by

$$H = \begin{bmatrix} 0 & 1 & 2 & \dots & N-2 & N-1 \\ 1 & 0 & 1 & \dots & \dots & N-2 \\ 2 & 1 & 0 & 1 & \dots & \dots \\ \dots & \dots & 1 & 0 & 1 & 2 \\ N-2 & \dots & \dots & 1 & 0 & 1 \\ N-1 & N-2 & \dots & 2 & 1 & 0 \end{bmatrix}.$$

3.4

For localized communication patterns, the communication probability  $p_{i,j}$  for two processors in Eq. 3.3 decreases as the distance between the two processors increases.

Our analysis assumes that each processor wants to transmit M data words, which implies equal traffic loads. Our framework can model unequal traffic loads; to do so we modify Eq. 3.3 as

$$E_{i,j} = M_i \cdot p_{i,j} \cdot E_l \cdot H_{i,j}, \qquad 3.5$$

where *M* is a vector and each element  $M_i$  holds the number of messages that  $P_i$  wants to transmit. In this case, the expected number of messages that  $P_i$  sends to  $P_i$  is  $M_i \cdot p_{i,j}$ .

#### 3.5.2 Uniform Distribution

If there is no sense of communication locality in our system, a processor communicates with any other processor with equal probability. Therefore, in any point-to-point network, each message is equally likely to make (1, 2,..., N-1) hops. So we can replace the communication probability  $p_{i,j}$  of Eq. 3.3 with

$$p_{i,j} = \frac{1}{N-1}$$

, for  $i \neq j$ , 3.6

and get the following equation for the expected energy cost  $E_{i,j}$  for the communication between processors  $P_i$  and  $P_j$ :

$$E_{i,j} = \frac{M}{N-1} \cdot E_l \cdot H_{i,j}.$$

3.7

The total expected energy cost of transmitting the data assuming uniform distribution (from Eq. 3.2) is

$$E_{P2P} = \sum_{i=1}^{N} \left( \sum_{j=1}^{N} E_{i,j} \right) = \frac{M}{N-1} \cdot E_{l} \cdot \sum_{i=1}^{N} \sum_{j=1}^{N} H_{i,j}.$$

3.8