## Architectural and Compiler Support for Strongly Atomic Transactional Memory

by

C. Scott Ananian

M.Sc Electrical Engineering and Computer Science,

Massachusetts Institute of Technology, 1999;

B.S.E. Electrical Engineering,

Princeton University, 1997.

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering and Computer Science at the Massachusetts Institute of Technology.

May 25, 2007

Copyright 2007 Massachusetts Institute of Technology.

All rights reserved.

| Author         |                                                           |

|----------------|-----------------------------------------------------------|

|                | Department of Electrical Engineering and Computer Science |

|                | May 25, 2007                                              |

| Certified by . |                                                           |

|                | Martin Rinard                                             |

|                | Professor of Computer Science and Engineering             |

|                | Thesis Supervisor                                         |

| Accepted by    |                                                           |

|                | Arthur C. Smith                                           |

|                | Chairman, Department Committee on Graduate Theses         |

Architectural and Compiler Support for Strongly Atomic Transactional

Memory by C. Scott Ananian

Submitted to the

Department of Electrical Engineering and Computer Science

May 25, 2007

In partial fulfillment of the requirements for the Degree of Doctor of Philosophy

in Electrical Engineering and Computer Science.

#### **Abstract**

Transactions are gaining ground as a programmer-friendly means of expressing concurrency, as microarchitecture trends make it clear that parallel systems are in our future. This thesis presents the design and implementation of four efficient and powerful transaction systems: APEX, an object-oriented software-only system; UTM and LTM, two scalable systems using custom processor extensions; and HYAPEX, a hybrid of the software and hardware systems, obtaining the benefits of both.

The software transaction system implements strong atomicity, which ensures that transactions are protected from the influence of nontransactional code. Previous software systems use weaker atomicity guarantees because strong atomicity is presumed to be too expensive. In this thesis strong atomicity is obtained with minimal slowdown for nontransactional code. Compiler analyses can further improve the efficiency of the mechanism, which has been formally verified with the SPIN model-checker.

The low overhead of APEX allows it to be profitably combined with a hardware transaction system to provide fast execution of short and small transactions, while allowing fallback to software for large or complicated transactions. I present UTM, a hardware transactional memory system allowing unbounded virtualizable transactions, and show how a hybrid system can be obtained.

Thesis Supervisor: Martin Rinard

Title: Professor of Computer Science and Engineering

#### Acknowledgments

I would like to thank my advisor Martin Rinard for his infinite patience, and for his guidance and support. I would like to thank Tom Knight for pointing me in the direction of transactional memory many years ago, and Charles Leiserson, Bradley Kuszmaul, Krste Asanović, and Sean Lie for the opportunity to collaborate on our hardware transactional memory research.

A list of thanks would not be complete without my "officemates" (real or virtual) who made my years at LCS and CSAIL so enjoyable: Maria-Cristina Marinescu (#2), Radu Rugina (#3), Darko Marinov (#5), Brian Demsky (#6), Alex Salcianu (#7), Karen Zee (#8), Patrick Lam (#10), Viktor Kuncak (#11), Amy Williams (#13), and Angelina Lee (who somehow has no number).

My mother, Cyndy Bernotas, waited a long time for this thesis to be complete. My brother, Chris Ananian, profited by the delay and became the first Dr. Ananian—but didn't rub it in too much. Jessica Wong and Kathy Peter put up with my indefinite studenthood. Thank you.

C. Scott Ananian Cambridge, Massachusetts May 2007

## Contents

| 1 | Inti | roduct  | ion                                           | 13 |

|---|------|---------|-----------------------------------------------|----|

|   | 1.1  | The ri  | ising challenge of multicore systems          | 13 |

|   | 1.2  | Advar   | ntages of transactions                        | 14 |

|   | 1.3  | Unlim   | lited transactions                            | 15 |

|   | 1.4  | Strong  | g atomicity                                   | 17 |

|   | 1.5  | Summ    | nary of contributions                         | 17 |

| 2 | Tra  | nsactio | onal programming: The good, bad, and the ugly | 21 |

|   | 2.1  | Four    | old things you can't (easily) do with locks   | 21 |

|   | 2.2  | Four r  | new things transactions make easy             | 24 |

|   | 2.3  | Some    | things we still can't (easily) do             | 31 |

| 3 | Des  | igning  | a software transaction system                 | 33 |

|   | 3.1  | Findir  | ng transactions                               | 33 |

|   | 3.2  | Design  | n goals                                       | 39 |

|   |      | 3.2.1   | Weak vs. strong atomicity                     | 39 |

|   |      | 3.2.2   | Object-oriented vs. flat TM                   | 39 |

|   |      | 3.2.3   | Tolerable limits for object expansion         | 40 |

|   |      | 3.2.4   | Reads vs. writes                              | 42 |

|   |      | 3.2.5   | The big idea: Waving FLAGs                    | 43 |

|   | 3.3  | Specif  | Tying the basic mechanism                     | 43 |

|   |      | 3.3.1   | Object structures                             | 44 |

|   |      | 3.3.2   | Operations                                    | 47 |

#### CONTENTS

| 4 | $\mathbf{Ape}$ | eX implementation: Efficient software transactions | 57  |

|---|----------------|----------------------------------------------------|-----|

|   | 4.1            | The FLEX compiler infrastructure                   | 57  |

|   | 4.2            | Transforming synchronization                       | 61  |

|   |                | 4.2.1 Method transformation                        | 61  |

|   |                | 4.2.2 Analyses                                     | 63  |

|   |                | 4.2.3 Desugaring                                   | 64  |

|   | 4.3            | Runtime system implementation                      | 65  |

|   |                | 4.3.1 Implementing the Java Native Interface       | 66  |

|   |                | 4.3.2 Preprocessor specialization                  | 68  |

|   | 4.4            | Limitations                                        | 71  |

|   |                | 4.4.1 Static fields                                | 72  |

|   |                | 4.4.2 Coarse-grained LL/SC                         | 72  |

|   |                | 4.4.3 Handling subword and multiword reads/writes  | 74  |

|   |                | 4.4.4 Condition variables                          | 76  |

|   | 4.5            | Additional optimizations                           | 80  |

| 5 | Ape            | eX performance                                     | 83  |

|   | 5.1            | Performance limits for nontransactional code       | 84  |

|   | 5.2            | Full application benchmarks                        | 93  |

|   |                | 5.2.1 Nontransactional check overhead              | 93  |

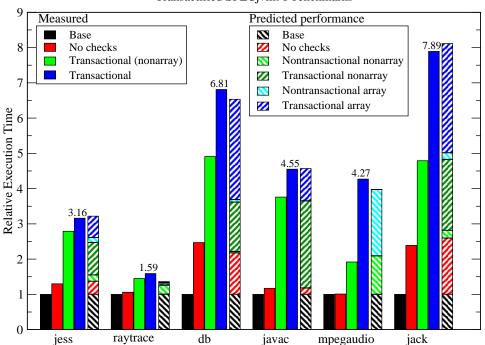

|   |                | 5.2.2 Transaction overhead                         | 99  |

|   | 5.3            | Performance recommendations                        | .03 |

| 6 | Arr            | ays and large objects 1                            | 07  |

|   | 6.1            | Basic operations on functional arrays              | .08 |

|   | 6.2            | A single-object protocol                           | 10  |

|   | 6.3            | Extension to multiple objects                      | 11  |

|   | 6.4            | Lock-free functional arrays                        | 16  |

|   | 6.5            | Performance of functional array implementations    | 24  |

#### CONTENTS

| 7 | Trai           | sactions in hardware: Unbounded Transactional Mem- |

|---|----------------|----------------------------------------------------|

|   | $\mathbf{ory}$ | 129                                                |

|   | 7.1            | The UTM architecture                               |

|   |                | 7.1.1 New instructions                             |

|   |                | 7.1.2 Rolling back processor state                 |

|   |                | 7.1.3 Memory state                                 |

|   |                | 7.1.4 Caching                                      |

|   |                | 7.1.5 System issues                                |

|   | 7.2            | The LTM architecture                               |

|   | 7.3            | Evaluation                                         |

|   |                | 7.3.1 Scalability                                  |

|   |                | 7.3.2 Overhead                                     |

|   |                | 7.3.3 Overflows                                    |

|   | 7.4            | A hybrid transaction implementation                |

| 8 | Cha            | lenges 151                                         |

|   | 8.1            | Performance isolation                              |

|   | 8.2            | Progress guarantees                                |

|   | 8.3            | The semantic gap                                   |

|   | 8.4            | I/O mechanisms                                     |

|   |                | 8.4.1 Forbidding I/O                               |

|   |                | 8.4.2 Mutual exclusion                             |

|   |                | 8.4.3 Postponing I/O                               |

|   |                | 8.4.4 Integrating do/undo                          |

|   | 8.5            | OS interactions                                    |

|   | 8.6            | Recommendations for future work                    |

| 9 | Rela           | ted work 163                                       |

|   | 9.1            | Nonblocking synchronization                        |

|   | 9.2            | Efficiency                                         |

|   | 9.3            | Transactional memory systems                       |

|   | 9.4            | Language-level approaches to synchronization       |

#### CONTENTS

| 10           | Cor   | nclusion                                   | 173   |

|--------------|-------|--------------------------------------------|-------|

| $\mathbf{A}$ | Mo    | del-checking the software implementation   | 175   |

|              | A.1   | Promela primer                             | . 177 |

|              | A.2   | Spin model for software transaction system | . 179 |

| В            | Cor   | npiler and runtime system configurations   | 197   |

| Bi           | bliog | graphy                                     | 201   |

# List of Figures

| 2.1  | Destructive linked-list traversal                              | 25 |

|------|----------------------------------------------------------------|----|

| 2.2  | A simple backtracking recursive-decent parser                  | 27 |

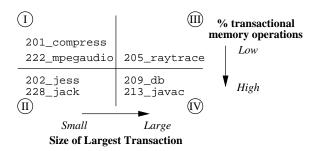

| 3.1  | Transactification of SPECjvm98 benchmark suite                 | 35 |

| 3.2  | Classification of SPECjvm98 benchmarks into quadrants based    |    |

|      | on transaction properties.                                     | 35 |

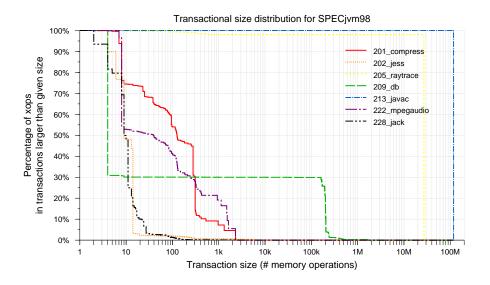

| 3.3  | Distribution of transaction size in the SPECjvm98 bench-       |    |

|      | mark suite.                                                    | 38 |

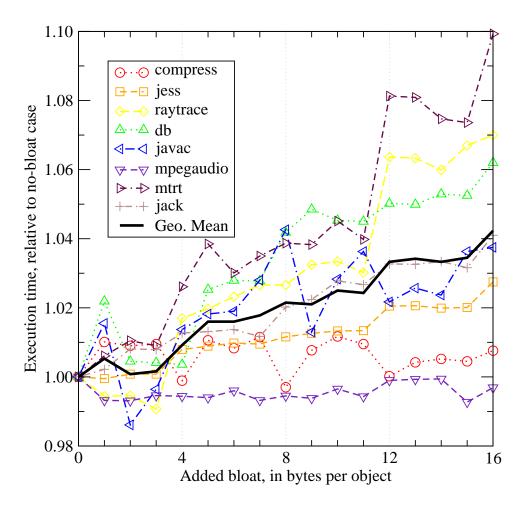

| 3.4  | Application slowdown with increasing object bloat for the      |    |

|      | SPECjvm98 benchmark applications                               | 41 |

| 3.5  | Comparison of loads and stores inside transactions for the     |    |

|      | SPECjvm98 benchmark suite, full input runs                     | 42 |

| 3.6  | Implementing software transactions with version lists          | 45 |

| 3.7  | Declaring objects with version lists in Promela                | 46 |

| 3.8  | Promela specification of nontransactional read and write op-   |    |

|      | erations                                                       | 48 |

| 3.9  | First half of the field copy-back routine.                     | 50 |

| 3.10 | Final portion of the field copy-back routine                   | 51 |

| 3.11 | Promela specification of transactional read and write opera-   |    |

|      | tions                                                          | 53 |

| 3.12 | The per-object version-setup routine for transactional writes. | 54 |

| 3.13 | The per-field copy-through routine for transactional writes    | 55 |

#### LIST OF FIGURES

| 4.1  | speed comparison of exception return techniques for SPECJVIII96 |     |

|------|-----------------------------------------------------------------|-----|

|      | benchmarks                                                      | 60  |

| 4.2  | Software transaction transformation.                            | 61  |

| 4.3  | A portion of the Java Native Interface                          | 67  |

| 4.4  | Specializing transaction primitives by field size and object    |     |

|      | type (readwrite.c)                                              | 69  |

| 4.5  | Specializing transaction primitives by field size and object    |     |

|      | <pre>type (readwrite-impl.c)</pre>                              | 70  |

| 4.6  | Specializing transaction primitives by field size and object    |     |

|      | type (preproc.h).                                               | 70  |

| 4.7  | Static field transformation.                                    | 72  |

| 4.8  | Nontransactional write to small (subword) field                 | 76  |

| 4.9  | Drop box example illustrating the use of condition variables    |     |

|      | in Java                                                         | 77  |

| 5.1  | Counter microbenchmark to evaluate read- and write-check        |     |

|      | overhead for nontransactional code                              | 85  |

| 5.2  | C implementation of read checks for counter microbenchmark.     | 85  |

| 5.3  | C implementation of write checks for counter microbenchmark.    | 86  |

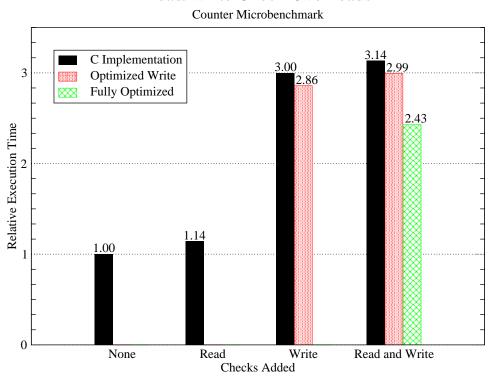

| 5.4  | Check overhead for counter microbenchmark                       | 88  |

| 5.5  | PowerPC assembly for counter microbenchmark with write          |     |

|      | checks                                                          | 90  |

| 5.6  | Optimized PowerPC assembly for counter microbenchmark           |     |

|      | with both read and write checks.                                | 91  |

| 5.7  | Check overhead as percentage of total dynamic instruction       |     |

|      | count                                                           | 92  |

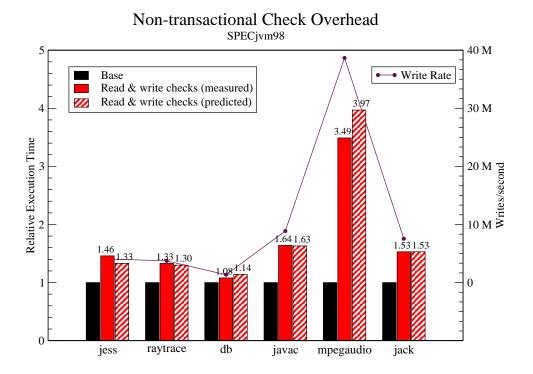

| 5.8  | Nontransactional check overhead for SPECjvm98                   | 94  |

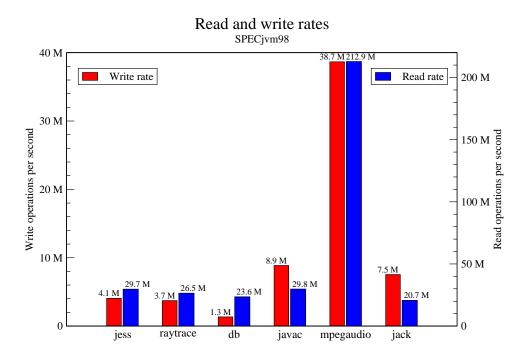

| 5.9  | Read and write rates for SPECjvm98                              | 95  |

| 5.10 | Actual versus predicted nontransactional check overhead         | 96  |

| 5.11 | Number of false flags read/written in SPECjvm98 benchmarks.     | 96  |

| 5.12 | Transaction overhead for SPECjvm98                              | .00 |

#### LIST OF FIGURES

| 5.13 | Transaction, call, and nontransactional read and write rates      |     |

|------|-------------------------------------------------------------------|-----|

|      | for SPECjvm98 benchmarks.                                         | 103 |

| 5.14 | Transaction performance model inputs for SPECjvm98 bench-         |     |

|      | marks                                                             | 104 |

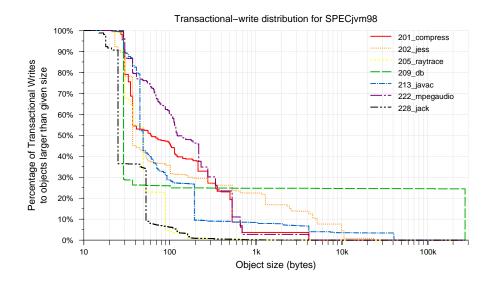

| 6.1  | Proportion of transactional writes to objects equal to or smaller |     |

|      | than a given size                                                 | 108 |

| 6.2  | Implementing nonblocking single-object concurrent operations      |     |

|      | with functional arrays                                            | 110 |

| 6.3  | Data structures to support nonblocking multiobject concur-        |     |

|      | rent operations.                                                  | 112 |

| 6.4  | READ and READT implementations for the multiobject pro-           |     |

|      | tocol                                                             | 113 |

| 6.5  | WRITE and WRITET implementations for the multiobject              |     |

|      | protocol                                                          | 114 |

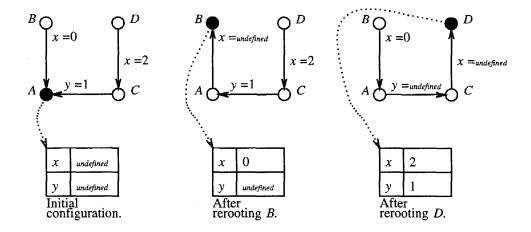

| 6.6  | Shallow binding scheme for functional arrays                      | 117 |

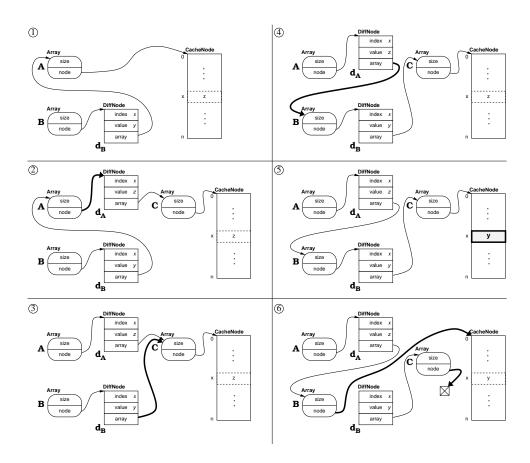

| 6.7  | Atomic steps in FA-Rotate(B)                                      | 120 |

| 6.8  | Implementation of lock-free functional array using shallow        |     |

|      | binding and randomized cuts (part 1)                              | 121 |

| 6.9  | Implementation of lock-free functional array using shallow        |     |

|      | binding and randomized cuts (part 2)                              | 122 |

| 6.10 | Array reversal microbenchmark to evaluate performance of          |     |

|      | functional array implementations                                  | 124 |

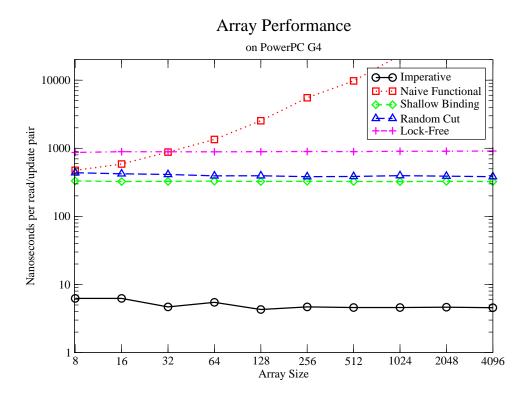

| 6.11 | Functional array performance on an array reversal microbench-     |     |

|      | mark                                                              | 126 |

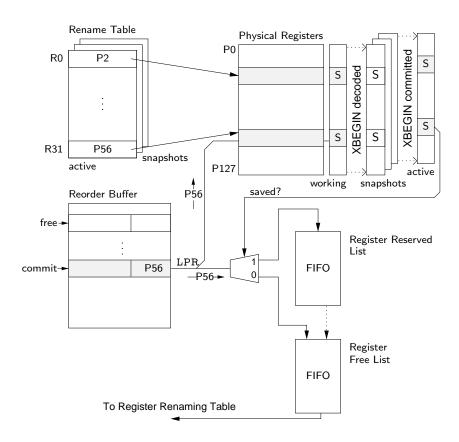

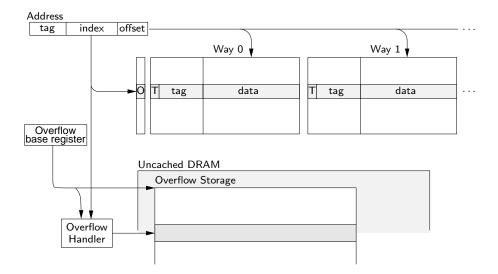

| 7.1  | UTM processor modifications                                       | 134 |

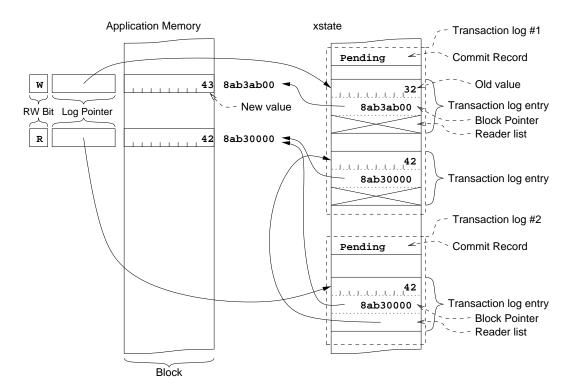

| 7.2  | The xstate data structure.                                        | 135 |

| 7.3  | LTM cache modifications.                                          | 141 |

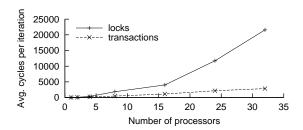

| 7.4  | Counter performance on UVSIM                                      | 143 |

| 7.5  | SPECjvm98 performance on a 1-processor UVSIM simulation.          | 147 |

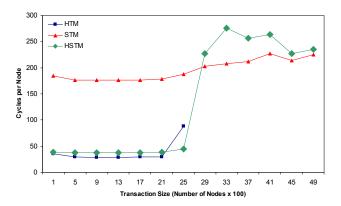

| 7.6  | Hybrid performance on simple queue benchmark                      | 147 |

#### LIST OF FIGURES

| 9.1 | A directory object in Emerald, illustrating the use of monitor  |     |

|-----|-----------------------------------------------------------------|-----|

|     | synchronization                                                 | 169 |

| 9.2 | A simple bank account object illustrating the use of the atomic |     |

|     | modifier                                                        | 170 |

Teen Talk Barbie (apocryphal)

## Chapter 1

## Introduction

How can we fully utilize the coming generation of parallel systems? The primitives available to today's programmers are largely inadequate. *Transactions* have been proposed as an alternative to the existing mechanisms for expressing concurrency and synchronization, but current implementations of transactions are either too limited or too inefficient for general use. This thesis presents the design and implementation of efficient and powerful transaction systems to help address the challenges posed by current trends in computing hardware.

## 1.1 The rising challenge of multicore systems

Processor technology is nearing its limits: even though transistor quantities continue to grow exponentially, we are now unable to effectively harness those vast quantities of transistors to create speedier single processors. The smaller transistors yield relatively slower signal propagation times, dooming attempts to create a single synchronized processor from all of those resources. Instead, hardware manufacturers are providing tightly integrated multicore systems which integrate multiple parallel processors on one chip.

The widespread adoption of parallel systems creates problems: how can we ensure that operations occur in an appropriate order? How can we

ensure certain operations occur *atomically*, so that other components of the parallel system only observe data structures in well-defined states?

Atomicity in shared-memory multiprocessors is conventionally provided via mutual-exclusion *locks* (see, for example, [93, p. 35]). Although locks are easy to implement using test-and-set, compare-and-swap, or load-linked/store-conditional instructions, they introduce a host of difficulties. Protocols to avoid deadlock when locking multiple objects often involve acquiring the locks in a consistent linear order, making programming with locks errorprone and introducing significant time and space overheads in the resulting code. The granularity of each lock must also be explicitly chosen, as locks that are too fine introduce unnecessary space and time overhead, while locks that are too coarse sacrifice attainable parallelism (or may even deadlock). Every access to a shared object must hold some lock protecting that object, regardless of whether another thread is actually attempting to access the same object.

## 1.2 Advantages of transactions

Transactions are an alternative means of providing concurrency control. A transaction can be thought of as a sequence of loads and stores performed as part of a program which either commits or aborts. If a transaction commits, then all of the loads and stores appear to have run atomically with respect to other transactions. That is, the transaction's operations are not interleaved with those of other transactions. If a transaction aborts, then none of its stores take effect and the transaction may be restarted, with some mechanism to ensure forward progress.

By structuring concurrency at a high level with transactions, human programmers no longer need to manage the details required to ensure atomicity. A full mental model of the global concurrency structure must be kept in mind when writing synchronization code, which programmers have difficulty correctly maintaining. The simpler "global atomicity" guaranteed

under the transactional model eliminates potential errors and simplifies the conceptual model of the system, making future modifications safer as well.

The transaction primitives presented in this thesis can exploit optimistic concurrency, provide fault tolerance, and prevent delays by using nonblocking synchronization. Although transactions can be implemented using mutual exclusion (locks), our algorithms utilize nonblocking synchronization [40, 54, 56, 65, 73] to exploit optimistic concurrency among transactions. Nonblocking synchronization offers several advantages; from the system builder's perspective the principle advantage is fault tolerance. In a traditionally constructed system, a process that fails or pauses while holding a lock within a critical region can prevent all other processes from making progress. It is in general not possible to restore locked data structures to a consistent state after such a failure. Nonblocking synchronization offers a graceful solution, as non-progress or failure of any one thread does not affect the progress or consistency of other threads or the system.

Implementing transactions using nonblocking synchronization offers performance benefits as well. When mutual exclusion is used to enforce atomicity, page faults, cache misses, context switches, I/O, and other unpredictable events may result in delays to the entire system. Nonblocking synchronization allows undelayed processes or processors to continue to make progress. In real-time systems, the use of nonblocking synchronization can prevent priority inversion in the system [60], although naive implementations may result in starvation of low-priority tasks (see Section 8.2 for a discussion).

#### 1.3 Unlimited transactions

The *transactional memory* abstraction [49, 50, 63, 81, 87, 89], has been proposed as a general and flexible way to allow programs to read and modify disparate primary memory locations as a single operation (atomically), much as a database transaction can atomically modify many records on disk.

#### CHAPTER 1. INTRODUCTION

Hardware transactional memory (HTM) supports atomicity through architectural means, whereas software transactional memory (STM) supports atomicity through languages, compilers, and libraries. I will present both software and hardware implementations of the transaction model.

Researchers of both HTM and STM commonly express the opinion that transactions need never touch many memory locations, and hence it is reasonable to put a (small) bound on their size [49, 50]. For HTM implementations, they conclude that a small piece of additional hardware—typically in the form of a fixed-size content-addressable memory and supporting logic—should suffice. For STM implementations, some researchers argue additionally that transactions occur infrequently, and hence the software overhead would be dwarfed by the other processing done by an application. In contrast, this thesis supports transactions of arbitrary size and duration. Just as most programmers need not pay any attention to the exact size and replacement policy of their system's cache, programmers ought not concern themselves with limits or implementation details of their transaction system.

My goal is to make concurrent and fault-tolerant programming easier, without incurring excessive overhead. This thesis advocates unbounded transactions because neither programmers nor compilers can easily cope when an architecture imposes a hard limit on transaction size. An implementation might be optimized for transactions below a certain size, but must still operate correctly for larger transactions. The size of transactional hardware should be an implementation parameter, like cache size or memory size, which can vary without affecting the portability of binaries.

In Chapter 7 I show how a fast hardware implementation for frequent short transactions can gracefully fail over to a software implementation designed to efficiently execute large long-lived transactions. The hybrid ap-

<sup>&</sup>lt;sup>1</sup>For example, [49, section 5.2] states, "Our [HTM] implementation relies on the assumption that transactions have short durations and small data sets"; while the STM described in [50] has quadratic slowdown when transactions touch many objects: performance is O((R+W)R), where R and W are the number of objects opened for reading and writing, respectively.

proach allows more sophisticated transaction models to be implemented, while allowing a simpler hardware transaction mechanism to provide speed in the common case.

#### 1.4 Strong atomicity

Blundell, Lewis, and Martin [17] distinguish between *strongly atomic* transaction systems, which protect transactions from interference from non-transactional code, and *weakly atomic* transaction systems which do not afford this protection. Nearly all current software transaction systems are weakly atomic, however, despite the pitfalls thus opened for the unwary programmer, because of the perceived difficulty in efficiently implementing the required protection.

Strong atomicity is clearly preferable, as the programmer will inevitably overlook some nontransactional references to shared data; we wish to preserve correctness in this common case. Blundell et al. point out that programs written for a weakly atomic model (to run on a current software transaction system, say) may deadlock when run under strong atomicity (for example, on a hardware transaction system). The transaction systems considered in this thesis preserve the correct atomic behavior of transactions even in the face of unsynchronized accesses from outside the transaction.

### 1.5 Summary of contributions

In summary, this thesis makes the following contributions:

• I provide efficient implementations of *strongly atomic* transaction primitives to enable their general use. My experiments have not

<sup>&</sup>lt;sup>2</sup>There are some systems which use type systems to disallow nontransactional access to objects with a "shared" type [45, 50, 84], but to my knowledge all systems which allow (or cannot prevent) access to shared objects from nontransactional code do so unsafely [26, 31, 44, 51, 53, 87].

#### CHAPTER 1. INTRODUCTION

shown an overhead of more than 150% in real applications, although proper compiler support should reduce that worst case considerably.

- The transaction primitives presented in this thesis can exploit optimistic concurrency, provide fault tolerance, and prevent delays by using nonblocking synchronization.

- This thesis proposes systems which can support transactions of arbitrary size and duration, sparing the programmer from detailed knowledge of the system's implementation details.

- I present both software and hardware implementations of the transaction model. The software transaction system runs real programs written in Java; I discuss the practical implementation details encountered. The hardware transaction systems require only small changes to the processor core and cache.

- I show how a fast hardware implementation for frequent short transactions can gracefully fail over to a software implementation designed to efficiently execute large long-lived transactions.

In Chapter 2 I provide some concurrent programming examples that illustrate the limitations of current lock-based methodologies. I also provide examples illustrating the uses (some novel) of a transaction system, and conclude with a brief caution about the current limits of transactions.

In Chapter 3 I present the design of APEX, an efficient software-only implementation of transactions. Software-only transactions can be implemented on current hardware, and can easily accommodate many different transaction and nesting models. Software transactions excel at certain long-lived transactions, where the overhead is small compared to the transaction execution time. An early version of APEX was published as [4]. I conclude by presenting a microbenchmark that demonstrates the performance limits of the design.

In Chapter 4 I discuss the practical implementation of APEX. I present details of the compiler analyses and transformations performed, as well as solutions to problems that arise when implementing Java. I then present benchmark results using real applications, discuss the benefits and limitations revealed, and describe how the limits could be overcome.

Chapter 6 explores one such limitation in depth, describing how large arrays fit into an object-oriented transaction scheme. I present a potential solution to the problem based on fast functional arrays.

In Chapter 7 I present LTM and UTM, hardware systems that enable fast short transactions. The transaction model is more limited, but short committing transactions may execute with no overhead. The additional hardware is small and easily added to current processor and memory system designs. This portion of the chapter is joint work with Krste Asanović, Bradley C. Kuszmaul, Charles E. Leiserson, and Sean Lie, and has been previously published as [6, 7].

At the end of the chapter, I present HYAPEX, a *hybrid* transaction implementation that builds on the strengths of simple hardware support while allowing software fallback to support a robust and capable transaction mechanism. Unlike the extended hardware scheme, the transaction model is still easy to change and update; the hardware primarily supports fast small transactions and conflict checking in the common case. I discuss some ways compilers can further optimize software and hybrid transaction systems. These opportunities may not be available to pure-hardware implementations.

In Chapter 8 I discuss remaining challenges to the use of ubiquitous transactions for synchronization, and present some ideas toward solutions. Chapter 9 discusses related work, and my final chapter summarizes my findings and draws conclusions.

#### CHAPTER 1. INTRODUCTION

You have a hardware or a software problem.

Service manual for Gestetner 3240

## Chapter 2

# Transactional programming: The good, bad, and the ugly

Before diving into the design of an efficient transaction system, I motivate the transactional programming model by presenting four common scenarios that are needlessly difficult using lock-based concurrency. I then present four novel applications that a transactional model facilitates. To ground the discussion in reality, I conclude by enumerating a few cases where transactions may *not* be the best solution.

## 2.1 Four old things you can't (easily) do with locks

Locks engender poor modularity and composability, an inability to deal gracefully with asynchronous events, and fragile and complex safety protocols that are often expressed externally to their implementations. These limitations of locks are well-known [52]. I present four common tasks which locks make unnecessarily difficult: making localized changes to synchronization, performing atomic operations on containers, creating a thread-safe double-ended queue, and handling asynchronous exceptions.

#### CHAPTER 2. TRANSACTIONAL PROGRAMMING

#### Tweak performance with localized changes

Preventing deadlocks and races requires global protocols and non-local reasoning. It is not enough to simply specify a lock of a certain granularity protecting certain data items; the order or circumstances in which the lock may be acquired and released must also be specified globally, in the context of all locks in the system, in order to prevent deadlocks or unexpected races. This requirement prevents the programmer from easily tuning the system using localized changes: every small change must be re-verified against the protocols specified in the whole-program context in order to prevent races and/or deadlock.

Furthermore, this whole-program protocol is not typically expressed directly in code. With common programming languages, acquire/release ordering and guarantees must be expressed externally, often as comments in the source code that easily drift out of sync with the implementation. For example, in [6] we counted the comments in the Linux filesystem layer, and found that about 15% of these relate to locking protocols; often describing global invariants of the program which are difficult to verify. Many reported kernel bugs involve races and deadlocks.

#### Atomically move data between thread-safe containers

Another common programming pitfall with locks is their non-composability. For example, given two thread-safe container classes implemented with locks, it is impossible to safely compose the get function of one with the put function of the other to create an atomic move. We must peek inside the implementation of the containers to synthesize an appropriate locking mechanism for such an action—for example, to acquire the appropriate container, element, or other locks on both containers—and even then, we need to resort to some global lock ordering to guard against deadlock. Modularity must be broken in order to synthesize the appropriate composed function, if it is possible at all.

#### 2.1. FOUR OLD THINGS YOU CAN'T (EASILY) DO WITH LOCKS

In the Jade programming language, Rinard presents a partial solution using "implicitly synchronized" objects [83, p14]. Lock acquisition for each module is exposed in the module's API as an executable "access declaration." Operation composition is accomplished by creating an access declaration for the composed operation which invokes the appropriate access declarations for the components. The runtime system orders the lock acquisitions to prevent deadlock. This process suffices for conservative mutual exclusion, but pre-declaration makes it difficult to express optimistic locking protocols, where one or more locks are only rarely required.

Transactions do not suffer from the composability problem [45]. Because transactions only specify the atomicity properties, not the locks required, the programmer's job is made easier and implementations are free to optimistically synchronize in any way that preserves atomicity.<sup>1</sup>

#### Create a thread-safe double-ended queue

Herlihy suggests creating a thread-safe double-ended queue using locks as "sadistic homework" for computer science students [52]. Although double-ended queues are a simple data structure, creating a scalable locking protocol is a non-trivial exercise. One wants dequeue and enqueue operations to complete concurrently when the ends of the queue are "far enough" apart, while safely handling the interference in the small-queue case. In fact, the solution to this assignment was a publishable result, as Michael and Scott demonstrated in 1996 [75].

The simple "one lock" solution to the double-ended queue problem, ruled out as unscalable in the locking case, is scalable and efficient for nonblocking transactions [52, 56].

<sup>&</sup>lt;sup>1</sup>Section 2.2 presents a concrete example.

#### CHAPTER 2. TRANSACTIONAL PROGRAMMING

#### Handle asynchronous exceptions

Properly handling asynchronous events is difficult with locks, because it is impossible to safely go off to handle the event while holding an arbitrary set of locks—and it is impossible to safely drop the locks. The solution implemented in the Real-Time Specification for Java [19] and similar systems (see [71, section 9]) is to generally forbid asynchronous events within locked regions, allowing the programmer to explicitly specify certain points within the region at which execution can be interrupted, dropping all locks in order to do so. Maintaining the correctness in the face of even explicitly declared interruption points is still difficult.

Transactional atomic regions handle asynchronous exceptions gracefully, by aborting the transaction to allow an event to occur.

#### 2.2 Four new things transactions make easy

I present four examples in this section, illustrating how transactions can support fault tolerance and backtracking, simplify locking, and provide a more intuitive means for specifying thread-safety properties. I first examine a destructive traversal algorithm, showing how a transaction implementation can be treated as an exception-handling mechanism. I show how a variant of this mechanism can be used to implement backtracking search. Using a network flow example, I then show how the transaction mechanism can be used to simplify the locking discipline required when synchronizing concurrent modifications to multiple objects. Finally, I show an existing race in the Java standard libraries (in the class java.lang.StringBuffer). "Transactification" of the existing class corrects this race.

#### Destructive traversal

Many recursive data structures can be traversed without the use of a stack by using pointer reversal. This technique is widely used in garbage collectors,

```

// destructive list traversal.

void traverse(List 1) {

List last = null, t;

/* zip through the list, reversing links */

for (int i=0; i<2; i++) {

do {

if (i==0) visit(1); // visit node

t = 1.next;

1.next = last;

last = 1;

1 = t;

} while (l!=null);

l = last;

// now do again, backwards. (restoring links)

}

}

```

Figure 2.1: Destructive linked-list traversal.

and was first demonstrated in this context by Schorr and Waite [86]. An implementation of a pointer-reversal traversal of a simple singly-linked list is shown in Figure 2.1.

The traverse() function traverses the list, visiting nodes in order and then reversing the next pointer. When the end of the list is reached, the reversed links are traversed to restore the list's original state.

Of course, I have chosen the simplest possible data structure here, but the technique works for trees and graphs—and the reader may mentally substitute their favorite hairy update on a complicated data structure.

In normal execution, the data structure is left complete and intact after the operation. But imagine that an exception or fault occurs inside the visit() method at some point during the traversal: an assertion fires, an exception occurs, the hardware hiccups, or a thread is killed. Control may leave the traverse() method, but the data structure is left in shambles. What is needed is some exception-handling procedure to restore the proper state of the list. This handler can be manually coded with Java's existing try/catch construct, but the exception-handling code must be tightly-coupled to the traversal if it is going to undo the list mutations.

#### CHAPTER 2. TRANSACTIONAL PROGRAMMING

Instead, I can provide a non-deterministic choice operator, try/else, and write the recovery code at a higher level as:

```

try {

traverse(list);

} else { // try-else construct

throw new Error();

}

```

The try/else block appears to make a non-deterministic choice between executing the try or the else clause, depending on whether the try would succeed or not. This construct can be straightforwardly implemented with a transaction around the traversal, always initially attempting the try. Exceptions or faults cause the transaction to abort; when it does so all the heap side-effects of the try block disappear.

#### Backtracking search

Introducing an explicit fail statement allows us to use the same try/else to facilitate backtracking search. Backtracking search is used to implement practical<sup>2</sup> regular expressions, parsers, logic programming languages, Scrabble-playing programs [9], and (in general) any problem with multiple solutions or multiple solution techniques.

As a simple example, let us consider a recursive-decent parser such as that shown in Figure 2.2. We don't know whether to apply the sum() or difference() production until after we've parsed some common left prefix. We can use backtracking to attempt one rule (sum) and fail out of it inside the eat() method, in the process undoing any data structure updates performed on this path, and then attempt the other possible production.

#### Optimistic synchronization

Let's now turn our attention now to parallel codes, the more conventional application of transaction systems. Consider a serial program for computing

<sup>&</sup>lt;sup>2</sup>As opposed to the limited regular expressions demonstrated in theory classes which are always neatly compiled to deterministic finite automata [33].

```

char buffer[];

int pos;

void eat(char token) {

if (buffer[pos++] != token)

fail;

int expr() {

try {

return sum();

} else {

return difference();

}

int sum() {

int a = number();

eat(ADD);

int b = number();

return a+b;

}

int difference() {

int a = number();

eat(MINUS);

int b = number();

return a-b;

}

```

Figure 2.2: A simple backtracking recursive-decent parser, using transactional try/else/fail.

#### CHAPTER 2. TRANSACTIONAL PROGRAMMING

network flow (see, for example, [24, Chapter 26]). The inner loop of the code pushes flow across an edge by increasing the "excess flow" on one vertex and decreasing it by the same amount on another vertex. One might see the following Java code:

```

void pushFlow(Vertex v1, Vertex v2, double flow) {

v1.excess += flow; /* Move excess flow from v1 */

v2.excess -= flow; /* to v2.

*/

}

```

To parallelize this code, one must preclude multiple threads from modifying the excess flow on those two vertices at the same time. Locks provide one way to enforce this mutual exclusion:

This code is surprisingly complicated and slow compared to the original. Space for each object's lock must be reserved. To avoid deadlock, the code must acquire the locks in a consistent linear order, resulting in an unpredictable branch in the code. In the code shown, I have required the programmer to insert an id field into each vertex object to maintain a total ordering. The time required to acquire the locks may be an order of magnitude larger than the time to modify the excess flow. What's more, all of this overhead is rarely needed! For a graph with thousands or millions of vertices, the number of threads operating on the graph is likely to be less than a hundred. Consequently, the chances are quite small that two different threads actually conflict. Without the locks to implement mutual exclusion, however, the program would occasionally fail.

Software transactions (and some language support) allow the programmer to parallelize the original code using an atomic keyword to indicate that the code block should appear to execute atomically:

This atomic region can be implemented as a transaction, and with an appropriately nonblocking implementation, it will scale better, execute faster, and use less memory than the locking version [6, 40, 44, 49, 73, 87]. From the programmer's point of view, I have also eliminated the convoluted locking protocol which must be observed rigorously everywhere the related fields are accessed, if deadlock and races are to be avoided.

Further, I can implement atomic using the try/else exception-handling mechanism I have already introduced:

```

for (int b=0; ; b++) {

try {

// atomic actions

} else {

backOff(b);

continue;

}

break; // success!

}

```

I non-deterministically choose to execute the body of the atomic block if and only if it will be observed by all to execute atomically. The same linguistic mechanism I introduced for fault tolerance and backtracking provides atomic regions for synchronization as well.

#### Bug fixing

The existing *monitor synchronization* methodology for Java, building on such features in progenitors such as Emerald [16, 61], implicitly associates

<sup>&</sup>lt;sup>3</sup>See Section 9.4.

#### CHAPTER 2. TRANSACTIONAL PROGRAMMING

an lock with each object. Data races are prevented by requiring a thread to acquire an object's lock before touching the object's shared fields. The lack of races is not sufficient to prevent unanticipated parallel behavior, however.

Flanagan and Qadeer [29] demonstrated this insufficiency with an actual bug they discovered in the Sun JDK 1.4.2 Java standard libraries. The java.lang.StringBuffer class, which implements a mutable string abstraction, is implemented as follows:

```

public final class StringBuffer ... {

private char value[];

private int count;

...

public synchronized

StringBuffer append(StringBuffer sb) {

...

A: int len = sb.length();

int newcount = count + len;

if (newcount > value.length)

expandCapacity(newcount);

// next statement may use stale len

B: sb.getChars(0, len, value, count);

count = newcount;

return this;

}

public synchronized int length() { return count; }

public synchronized void getChars(...) { ... }

}

```

The library documentation indicates that the methods of this class are meant to execute atomically, and the synchronized modifiers on the methods are meant to accomplish this.

The append() method is *not* atomic, however. Another thread may change the length of the parameter sb (by adding or removing characters) between the call to sb.length() at label A and the call to sb.getChars(...) at label B. This non-atomicity may cause incorrect data to be appended to the target or a StringIndexOutOfBoundException to be thrown. Although the calls to sb.length() and sb.getChars() are individually atomic, they do not compose to form an atomic implementation of append().

Replacing synchronized with atomic in this code gives us the semantics we desire: the atomicity of nested atomic blocks is guaranteed by the

atomicity of the outermost block, ensuring that the entire operation appears atomic.

Both the network flow example and this StringBuffer example require synchronization of updates to more than one object. Monitor synchronization is not well-suited to this task. Atomic regions implemented with transactions can be used to simplify the locking discipline required to synchronize multiobject mutation and provide a more intuitive specification for the desired concurrent properties. Further, the StringBuffer example shows that simply replacing synchronized with atomic provides a alternative semantics that may in fact correct existing synchronization errors. For many Java programs, the semantics of atomic and synchronized are identical; see Section 8.3.

#### 2.3 Some things we still can't (easily) do

The transaction mechanism presented here is not a universal replacement for all synchronization. In particular, transactions cannot replace mutual exclusion required to serialize I/O, although the needed locks can certainly be built with transactions. The challenge of integrating I/O within a transactional context is discussed in Section 8.4. Large programs—the Linux kernel, for example—have been written such that locks are never held across context switches or I/O operations, however. Transactions provide a complete solution for this limited form of synchronization.

Blocking producer-consumer queues, or other options that require a transaction to wait upon a condition variable, may introduce complications into a transaction system: transactions cannot immediately retry when they fail, but instead must wait for some condition to become true. Section 4.4.4 describes some solutions to this problem, ranging from naive (keep retrying and aborting with exponential backoff until the condition is finally true) to clever; the clever solutions require additional transaction machinery.

#### CHAPTER 2. TRANSACTIONAL PROGRAMMING

Easy things should stay easy, hard things should get easier, and impossible things should get hard.

Motto for Perl 6 development

## Chapter 3

# Designing a software transaction system

In this chapter I detail the design of APEX, a high-performance software transaction system. I first present a methodology for isolating likely transactions from benchmarks. I then describe the system goals, and use quantitative data from benchmarks to buttress the design choices. I formalize an implementation meeting those goals in the modeling language Promela. The correctness of this implementation can be model-checked using the SPIN tool; the details of this effort are in Appendix A.

After outlining the design of APEX in this chapter, Chapter 4 discusses its practical implementation.

## 3.1 Finding transactions

One of the difficulties of proposing a novel language feature is the lack of benchmarks for its evaluation. Although there is no existing body of code that uses transactions, there is a substantial body of code that uses Java (locking) synchronization. This thesis utilizes the FLEX compiler [3] to substitute atomic blocks (methods) for synchronized blocks (methods) in order to evaluate the properties Java transactions are likely to have. The

#### CHAPTER 3. DESIGNING A SOFTWARE TRANSACTION SYSTEM

semantics are not precisely compatible: the existing Java memory model allows unsynchronized updates to shared fields to be observed within a synchronized block, while such updates are never visible to a transaction expressed with an atomic block. Despite the differences in semantics, the automatic substitution of atomic for synchronized does, in fact, preserve the correctness of the benchmarks I examine here.

The initial results of this chapter explore the implications of exposing the transaction mechanism to user-level code through a compiler. I compiled the SPECjvm98 benchmark suite with the FLEX Java compiler, modified to turn synchronized blocks and methods into transactions, in order to investigate the properties of the transactions in such "automatically converted" code. FLEX performed method cloning to distinguish methods called from within transactions, and implemented nested locks as a single transaction around the outermost.<sup>2</sup> I instrumented this transformed program to produce a trace of memory references and transaction boundaries for analysis. I found both large transactions (involving millions of cache lines) and frequent transactions (up to 45 million of them). We will show that these properties are not unusual for typical applications.

The SPECjvm98 benchmark suite represents a variety of typical Java applications that use the capabilities of the Java standard library. Although the SPECjvm98 benchmarks are largely single-threaded, they contain synchronized code within the thread-safe Java standard libraries which is transformed into transactions. Because in this evaluation I am looking at transaction properties only, the multithreaded 227\_mtrt benchmark is identical to its serialized version, 205\_raytrace. For consistency, I present only the latter.

<sup>&</sup>lt;sup>1</sup>The Java 5.0 revision of the Java memory model [68-70] narrows the semantic gap. The full memory model includes details—such as volatile fields—which I do not treat in this work. Section 8.3 discusses the challenges involved in automatic transactification, and [41] contains a fuller discussion of the interactions between transactions and high-level memory models.

<sup>&</sup>lt;sup>2</sup>See Section 4.2 for more details on this transformation.

|                         | total         |              | transactional | biggest             |

|-------------------------|---------------|--------------|---------------|---------------------|

| program                 | memory ops    | transactions | memory ops    | ${\it transaction}$ |

| 201_compress            | 2,981,777,890 | 2,272        | <0.1%         | 2,302               |

| $202_{-} \mathrm{jess}$ | 405,153,255   | 4,892,829    | 9.1%          | 7,092               |

| 205_raytrace            | 420,005,763   | 4,177        | 1.7%          | 7,149,099           |

| 209_db                  | 848,082,597   | 45,222,742   | 23.0%         | 498,349             |

| 213_javac               | 472,416,129   | 668          | 99.9%         | 118,041,685         |

| 222_mpegaudio           | 2,620,818,169 | 2,991        | < 0.1%        | 2,281               |

| 228_jack                | 187,029,744   | 12,017,041   | 34.2%         | 14,266              |

Figure 3.1: Transactification of SPECjvm98 benchmark suite: resulting transaction counts and sizes, compared to total number of memory operations (loads and stores). These numbers represent full input size runs.

Figure 3.2: Classification of SPECjvm98 benchmarks into quadrants based on transaction properties.

#### CHAPTER 3. DESIGNING A SOFTWARE TRANSACTION SYSTEM

Figure 3.1 shows the raw sizes and frequency of transactions in the transactified SPECjvm98 suite. Because the run times of the benchmarks are roughly comparable, transaction count is also an indicator of transaction rate. Figure 3.2 proposes a taxonomy for Java applications with transactions, grouping the SPECjvm98 applications into quadrants based on the number and size of the transactions that they perform. Applications in Quads II and IV require an efficient transaction implementation, because they contain many transactional operations. Quads III and IV contain at least some large transactions, which pose difficulties for currently proposed hardware transactional memory schemes. We now examine the benchmarks in each quadrant to determine why its program logic caused it to be classified in that quadrant.

Quad I applications perform few (up to about 2000) small transactions. These applications include 201\_compress, an implementation of gzip compression, and 222\_mpegaudio, an MP3 decoder. Both of these applications perform inherently serial tasks. They perform quite well with locks, and would likely execute with acceptable performance even with a naive software implementation of transactions, as long as the impact on nontransactional operations was minimal.

Quad II applications perform a large number of small transactions. The expert system 202\_jess falls in this category, as does the parser generator 228\_jack and small input sizes of 209\_db, a database. These benchmarks perform at least an order of magnitude more transactions than Quad I applications, and all of the transactions are small enough to comfortably fit the known hardware transactional memory schemes [49, etc], if one were to be implemented.

Quad III includes 205\_raytrace, a ray-tracing renderer. A small number of transactions are performed, but they may grow large. Existing bounded

<sup>&</sup>lt;sup>3</sup>The canonical run times used for computation of the Spec ratio range from 380 to 1175 seconds. Sorted by run time: 202\_jess, 380 s; 213\_javac, 425 s; 228\_jack, 455 s; 227\_mtrt, 460 s; 209\_db, 505 s; 222\_mpegaudio, 1100 s; 201\_compress, 1175 s.

hardware transactional schemes do not suffice. The large transactions may account for a large percentage of total memory operations, which may make software schemes impractical.

Finally, Quad IV applications such as 209\_db and the 213\_javac Java compiler application perform a large number of transactional memory operations with at least a few large transactions.

The 213\_javac Java compiler application and the large input size of the 209\_db benchmark illustrate that some programs contain *extremely* large transactions. When 213\_javac is run on its full input set, it contains 4 huge transactions, each of which contains over 118 million transactional memory operations. Closer examination reveals that the method Javac.compile(), which implements the entire compilation process, is marked as synchronized: the programmer has explicitly requested that the entire compilation occur atomically.

The large transactions in Quad III and IV may be, as in this case, a result of overly coarse-grained locking, but my goal is to relieve the programmer from the burden of specifying correct atomic regions of smaller granularity. Performance may benefit from narrowing the atomic regions, but execution with coarse regions should be possible and not prohibitively slow.

The 209\_db benchmark suffers from a different problem: at one point the benchmark atomically scans an index vector and removes an element, creating a potentially large transaction if the index is large. The size of this index is correlated in these benchmarks with the input size, but it need not be: a large input could still result in a small index, and (to some degree) vice-versa.

A similar situation arises in the java.lang.StringBuffer code shown in Section 2.2: a call to the synchronized sb.getChars() method means that the size of the transaction for this method grows like the length of the parameter sb. In other words, the transaction can be made arbitrarily large by increasing the length of sb; or, equivalently, there is no bound on transaction size without a bound on the size of the string sb.

Figure 3.3: Distribution of transaction size in the SPECjvm98 benchmark suite. The x-axis uses a logarithmic scale.

Any transaction system that allows the programmer free reign over specifying desired transaction and/or atomicity properties will result in some applications in each of these categories. Large transactions, for example, are a side-effect of modularity: when a cross-module call occurs inside a transaction, the abstraction boundary prevents precise knowledge of the memory accesses implicitly included. Existing hardware transactional memory schemes only efficiently handle relatively short-lived and small transactions (Quad I or II), although they are efficient for these transactions. Object-based transaction systems can asymptotically approach that efficiency for long-lived transactions; the existence of which is shown in Figure 3.3, which plots the distribution of transaction sizes in SPECjvm98 on a semi-log scale.

These initial results indicate that real applications can be transactified with modest effort, yielding significant gains in concurrency. In other work [6] we have shown that a factor of 4 increase in concurrency can be obtained by doing nothing more than converting locks to transactions. Since the

transactified applications may contain large transactions, prior proposed hardware support for transactions is inadequate.

### 3.2 Design goals

In this section I briefly describe the desired properties of the APEX software transaction system: strong atomicity, object-orientation, low bloat, and fast reads. Where possible I justify these desiderata using quantitative data obtained from analyses of the SpecJVM98 benchmarks, which I implemented using the FLEX Java compiler framework.

### 3.2.1 Weak vs. strong atomicity

As previously discussed in Section 1.4, strongly atomic transaction systems protect transactions from interference from nontransactional code, while weakly atomic transaction systems do not afford this protection. Consider unsynchronized code directly altering the length field of the String-Buffer class, the example discussed in Section 2.2. In a weakly atomic system, an unsynchronized decrement to the count field between labels A and B in StringBuffer.append() on page 30 causes a StringIndexOutOfBound-Exception to be thrown in the call to getChars() at label B. This exception should never be thrown by an atomic execution of StringBuffer.append().

Current software transaction systems implement only weak atomicity because of the assumed expense of implementing strong atomicity. The APEX system achieves strong atomicity without adding excessive overhead, so that correct operation is assured even despite concurrent nontransactional operations on locations involved in a transaction.

### 3.2.2 Object-oriented vs. flat TM

The APEX transaction system, unlike most current proposals [44, 49] (including the UTM and LTM hardware systems presented in Chapter 7), uses

an "object-oriented" design. Much contemporary research is focused on implementing a flat (transactional) memory abstraction in software, primarily because flat systems side-step the large object issues presented in Chapter 6. The object-oriented approach, however, offers several benefits:

Efficient execution of long-running transactions. As discussed briefly in Sections 9.2 and 9.3, flat word-oriented transaction schemes typically require overhead proportional to the number of words read/written in the transaction, even if these locations have been accessed before inside the transaction. Object-oriented schemes impose a cost proportional to the number of objects touched by the transaction—but once the cost of "opening" those objects is paid, the transaction can continue to work indefinitely upon those objects without paying any further penalty. Object-oriented schemes are thus seen to be more efficient for long-running transactions.

Preservation of optimization opportunities. Furthermore, transaction-local objects can be identified (statically or dynamically) and creation/updates to these objects can be done without any transaction tax at all. Word oriented schemes discard the high-level information required to implement these optimizations.

I contend that the problems with previous object-oriented schemes can be solved while preserving the inherent benefits of an object-oriented approach, and the current thesis presents one such solution.

### 3.2.3 Tolerable limits for object expansion

An object-oriented transaction scheme requires transaction state information about each object. In APEX, this information is added directly to the objects, to eliminate indirection cost. I measured the slowdown caused by various amounts of object "bloat" to determine reasonable bounds on the size of this extra information. Figure 3.4 presents these results for the

Figure 3.4: Application slowdown with increasing object bloat for the SPECjvm98 benchmark applications.

CHAPTER 3. DESIGNING A SOFTWARE TRANSACTION SYSTEM

|                      | transactional | transactional |

|----------------------|---------------|---------------|

| program              | memory ops    | stores $\%$   |

| 201_compress         | 50,029        | 26.2%         |

| $202_{	extsf{jess}}$ | 36,701,037    | 0.6%          |

| 205_raytrace         | 7,294,648     | 23.2%         |

| 209_db               | 195,374,420   | 6.3%          |

| 213_javac            | 472,134,289   | 22.9%         |

| 222_mpegaudio        | 41,422        | 18.6%         |

| $228_{-}$ jack       | 63,912,386    | 17.0%         |

Figure 3.5: Comparison of loads and stores inside transactions for the SPECjvm98 benchmark suite, full input runs.

SPECjvm98 applications; I determined that two words (eight bytes) of additional storage per object would not impact performance unreasonably. This amount of bloat causes a geometric mean of 2% slowdown on these benchmarks.

### 3.2.4 Reads vs. writes

I also measured the number and types of reads and writes for the SpecJVM98 benchmarks. Figure 3.5 shows that transactional reads typically outnumber transactional writes by at least 4 to 1; in some cases reads outnumber writes by over 100 to 1.4 It is worthwhile, therefore, to make reads more efficient than writes. In particular, since the flag-overwrite technique discussed in Section 3.2.5 requires us to allocate additional memory to store the "real" value of the field, I wish to avoid this process for transactional reads, reserving the extra allocation effort for transactional writes.

<sup>&</sup>lt;sup>4</sup>The typical ratio roughly matches the 3:1 average observed in Hennessy and Patterson [46, pp. 105, 379].

### 3.2.5 The big idea: Waving FLAGs

I would like nontransactional code to execute with minimal overhead, but transactions should still appear atomic to nontransactional code. My basic mechanism is loosely based on the distributed shared memory implementation of Scales and Gharachorloo [85]. I pick a special "flag" value, and "cross-out" locations currently involved in a transaction by overwriting them with the flag value. Reading or attempting to overwrite a flagged value indicates to nontransactional code that exceptional processing is necessary; all other nontransactional operations proceed as usual. The flagged field either is currently involved in an active transaction, belongs to a committed or aborted transaction and requires copy back, or indicates a "false flag", a field with a true value equal to the flag value (see page 46).

This technique explicitly allows safe access to fields involved in a transaction from nontransactional code, which provides strong atomicity, a design goal of the system.

# 3.3 Specifying the basic mechanism

I now present algorithms that have these desired properties. The APEX algorithms provide strongly-atomic object-oriented transactions with low bloat and fast reads. Further, the APEX algorithms are completely nonblocking, which allows good scaling and proper fault-tolerant behavior. Specifically, one faulty or slow processor cannot hold up the remaining good processors.

I implement the synchronization required by the APEX algorithms using load-linked/store-conditional instructions. I require a particular variant of these instructions that allows the location of the load-linked to be different from the target of the store-conditional. This variant is supported on many chips in the PowerPC processor family, although it has been deprecated in version 2.02 of the PowerPC architecture standard.<sup>5</sup> This disjoint location

<sup>&</sup>lt;sup>5</sup>Version 2.02 of the PowerPC architecture standard says, "If a reservation exists but the storage location specified by the stwcx. is not the same as the location specified

capability is essential to allow us to keep a finger on one location while modifying another: a poor man's "Double Compare And Swap" instruction.

I describe the APEX algorithms in the Promela modeling language [57], which I used to allow mechanical model checking of the race-safety and correctness of the design. Portions of the model have been abbreviated for this presentation; the full Promela model is given in Appendix A, along with a brief primer on Promela syntax and semantics.

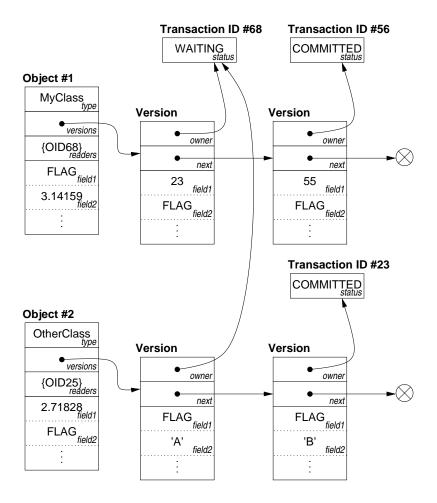

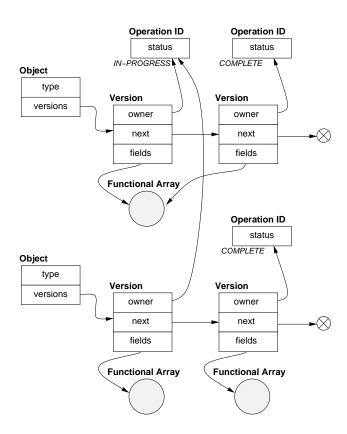

### 3.3.1 Object structures

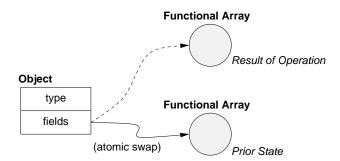

Figure 3.6 illustrates the basic data structures of the APEX software transaction implementation. Objects are extended with two additional fields. The first field, versions, points to a singly linked list of object versions. Each one contains field values corresponding to a committed, aborted, or inprogress transaction, identified by its owner field. There is a single unique transaction object for each transaction.

The other added field, readers, points to a singly linked list of transactions that have read from this object. Committed and aborted transactions are pruned from this list. The readers field is used to ensure that a transaction does not operate with out-of-date values if the object is later written

by the Load And Reserve instruction that established the reservation...it is undefined whether [the operand is] stored into the word in storage addressed by [the specified effective address]" and states that the condition code indicating a successful store is also undefined in this circumstance [58, p 25]. The user manual for the MPC7447/7457 ("G4") PowerPC chips states, however, "The stwcx. instruction does not check the reservation for a matching address. The stwcx. instruction is only required to determine whether a reservation exists. The stwcx. instruction performs a store word operation only if the reservation exists," [32, Section 3.3.3.6] which is the behavior we require. I believe version 1.10 of the PowerPC Architecture specification required this behavior, although I have not been able to locate a copy to confirm this requirement. The Cell architecture specification follows version 2.02 of the PowerPC specification, although it adds cache-line reservation operations that can also be used to implement our algorithm for reasonably-sized objects aligned within cache lines; see [98] for an implementation of Java I created that observes the appropriate alignments.

Figure 3.6: Implementing software transactions with version lists. A transaction object consists of a single field *status*, which indicates if it has COMMITTED, ABORTED, or is WAITING. Each object contains two extra fields: *readers*, a singly-linked list of transactions that have read this object; and *versions* a linked list of version objects. If an object field is FLAG, then the value for the field is obtained from the appropriate linked version object.

```

#define FLAG 202 /* special value to represent 'not here' */

typedef Object {

byte version;

byte readerList; /* we do LL and CAS operations on this field */

pid fieldLock[NUM_FIELDS]; /* we do LL operations on fields */

byte field[NUM_FIELDS];

};

typedef VersiOn { /* 'Version' misspelled because SPIN #define's it. */

byte owner:

byte next;

byte field[NUM_FIELDS];

};

typedef ReaderList {

byte transid;

byte next;

mtype = { waiting, committed, aborted };

typedef TransID {

mtype status;

};

```

Figure 3.7: Declaring objects with version lists in Promela. The byte datatype encodes pointers. The fieldLock field assists in the implementation of the load-linked/store-conditional pair of operations in Promela.

### nontransactionally.

There is a special flag value, here denoted by FLAG. It should be an uncommon value, i.e. not a small positive or negative integer constant, nor zero. In my implementation, I have chosen the byte OxCA to be the flag value, repeated as necessary to fill out the width of the appropriate type. The semantic value of an object field is the value in the original object structure, unless that value is FLAG, in which case the field's value is the value of the field in the first committed transaction in the object's version list. A "false flag" occurs when the application wishes to "really" store the value FLAG in a field. To do so we create a fully-committed version attached to the object and store FLAG in that version, as well as in the object field.

Figure 3.7 declares these object structures in Promela.

### 3.3.2 Operations

I support transactional read/write and nontransactional read/write as well as transaction begin, transaction abort, and transaction commit. Transaction begin simply involves the creation of a new transaction identifier object. Transaction commit and abort are simply compare-and-swap operations that atomically set the transaction object's status field appropriately if and only if it was previously in the WAITING state. The simplicity of commit and abort are appealing: the APEX algorithm requires no complicated processing, delay, roll-back or validate procedure to commit or abort a transaction.

I could support nontransactional read and write (that is, reads and writes that take place outside of any transaction) by creating a new short transaction that encloses only the single read or write. Since nontransactional accesses to objects can be frequent, I provide more efficient implementations with the same semantics.

I now present the operations one-by-one.

### Nontransactional read

The readNT function performs a nontransactional read of field f from object o, putting the result in  $\nu$ . In the common case, the only overhead is to check that the read value is not FLAG. If the value read is FLAG, however, we copy back the field value from the most-recently committed transaction (aborting all other transactions) and try again. The copy-back procedure notifies the caller if this is a "false flag", in which case the value of this field really is FLAG. We pass the kill\_writers constant to the copy-back procedure to indicate that only transactional writers need be aborted, not transactional readers. All possible races are confined to the copy-back procedure, which I describe on page 49.

The top of Figure 3.8 specifies the nontransactional read operation in Promela.

```

inline readNT(o, f, v) {

:: v = object[o].field[f];

:: (v!=FLAG) -> break /* done! */

:: else

fi;

copyBackField(o, f, kill_writers, _st);

if

:: (_st==false_flag) ->

v = FLAG;

break

:: else

fi

od

}

inline writeNT(o, f, nval) {

:: (nval != FLAG) ->

:: atomic {

if /* this is a LL(readerList)/SC(field) */

:: (object[o].readerList == NIL) ->

object[o].fieldLock[f] = _thread_id;

object[o].field[f] = nval;

break /* success! */

:: else

fi

/* unsuccessful SC */

copyBackField(o, f, kill_all, _st)

:: else -> /* create false flag */

/* implement this as a short *transactional* write. */

/* start a new transaction, write FLAG, commit the */

/* transaction; repeat until successful. */

/* Implementation elided. */

fi;

}

```

Figure 3.8: Promela specification of nontransactional read and write operations.

### Nontransactional write

The writeNT function performs a nontransactional write of new value nval to field f of object o. For correctness, we must ensure that the reader list is empty before we do the write. I implement this check with a load-linked/store-conditional pair, which is modeled in Promela slightly differently, ensuring that the write only succeeds so long as the reader list remains empty.<sup>6</sup> If it is not empty, we call the copy-back procedure (as in readNT), passing the constant kill\_all to indicate that both transactional readers and writers should be aborted during the copy-back. The copy-back procedure leaves the reader list empty.

If the value to be written is actually the FLAG value, things get a little bit trickier. This case does not occur often, and so the simplest correct implementation is to treat this nontransactional write as a short transactional write, creating a new transaction for this one write, and attempting to commit it immediately after the write. This implementation is slow, but adequate for this uncommon case.

The bottom of Figure 3.8 specifies the nontransactional write operation in Promela.

### Field Copy-Back

Figures 3.9 and 3.10 present the field copy-back routine. We create a new version owned by a pre-aborted transaction which serves as a reservation on the head of the version list. We then write to the object field with a load-linked/store-conditional pair if and only if our version is still at the head of the versions list.<sup>7</sup> This addresses the major race possible in this routine.

<sup>&</sup>lt;sup>6</sup>A standard CAS would not suffice, as the load-linked targets a different location than the store-conditional.

<sup>&</sup>lt;sup>7</sup>Again, a CAS does not suffice.

```

inline copyBackField(o, f, mode, st) {

_nonceV=NIL; _ver = NIL; _r = NIL; st = success;

/* try to abort each version. when abort fails, we've got a committed

* version. */

do

:: _ver = object[o].version;

:: (_ver==NIL) ->

st = saw_race; break /* someone's done the copyback for us */

:: else

fi;

/* move owner to local var to avoid races

* (owner set to NIL behind our back) */

_tmp_tid=version[_ver].owner;

tryToAbort(_tmp_tid);

:: (_tmp_tid==NIL || transid[_tmp_tid].status==committed) ->

break /* found a committed version */

fi;

/* link out an aborted version */

assert(transid[_tmp_tid].status==aborted);

CAS_Version(object[o].version, _ver, version[_ver].next, _);

/* okay, link in our nonce. this will prevent others from doing the

* copyback. */

if