## Data Acquisition System for Quality Tests of the ATLAS Muon Endcap Trigger Chambers.

Jacek Wasilewski

July 2002

#### Data Acquisition System for Quality Tests of the ATLAS Muon Endcap Trigger Chambers.

MSc Dissertation of Jacek Wasilewski, Technical University of Łódź

#### Abstract of the dissertation

The ATLAS The Collaboration is building a general-purpose pp detector which is design to exploit the full discovery potential of the high energy proton-proton interaction Large Hadron Collider (LHC) at CERN.

The LHC offers a large range of physics opportunities, among which the origin of mass at the electroweak scale is a major focus of interest for ATLAS. The detector optimization is therefore guided by physics issues such a sensitivity to the largest possible Higgs mass range.

The Thin Gap Chambers (TGCs) are detectors designed to detect the high transverse momentum muons in the endcaps of the ATLAS detector. The short response time of the TGCs makes it an ideal trigger system for selecting interesting events in the highly packed environment of the LHC accelerator.

The TGCs are designed and built in Weizmann Institute and are tested at the Tel-Aviv University and at the Technion.

The subject of this dissertation is the design and operation of the data acquisition system, which serves to automatize the procedure of testing the performance of the TGC detector, before are to be installed in the ATLAS experiment.

#### **Dissertation Committee**

#### Chair

Professor Andrzej Napieralski, Department of Microelectronics and Computer Science at Technical University of Łódź, Poland.

#### Supervisor

Mgr Zbigniew Kulesza, Department of Microelectronics and Computer Science, Technical University of Łódź, Poland. Dr Erez Etzion, School of Physics and Astronomy, Tel-Aviv University, Israel.

#### Acknowledgements

I would like to thank Prof. Andrzej Napieralski and mgr Zbigniew Kulesza for giving me this unique opportunity to join the research program of the Tel Aviv group during the preparation of my dissertation. This allowed me to have a hands-on experience with the VME standard and its application to data acquisition systems. I am grateful to Dr Erez Etzion for hosting me at Tel Aviv University, introducing me into the activities of his laboratory and for providing professional help. I am also grateful to Prof. Halina Abramowicz for her support in this undertaking.

I am deeply indebted to my friends and colleagues from the lab., Meni Ben-Moshe and Jonatan Ginzburg for their daily professional and personal support. Without their company and help I would have been lost. I am also very appreciative of the support given to me by Dr Juliana Cohen. I am greatly indepted to Dr Yan Benhamu for showing me all kinds of new tricks to make my work more efficient and I will always remember the time we worked together, however short it was.

I also wish to express my thanks to Yoram Granitzky and Eduardo Warszawski from the Technion for their help with the hardware and software design. Thanks also go to Marcus Joos from CERN and to Galia Gilitz from the Weizmann Institute for their support with the VME software.

I cannot possibly name all the people who made my work easier and my stay in Israel more pleasant. But I thank them all from my heart.

I dedicate this dissertation to my parents. Without them I would have never achieved what I did.

## Table Of Contents.

| 1 | Introduction                                               | 8   |

|---|------------------------------------------------------------|-----|

|   | 1.1 The Large Hadron Collider                              |     |

|   | 1.2 A Toroidal LHC Apparatus                               |     |

|   | 1.2.1 Components of the ATLAS detector                     |     |

|   | 1.2.2 Moun chamber layout.                                 |     |

|   | 1.2.3 Trigger and data-acquisition system.                 |     |

|   | 1.3 Thin Gap Chamber.                                      |     |

|   | 1.3.1 Principle of operation of TGCs.                      | 14  |

|   | 1.3.2 TGC test bench                                       |     |

| 2 |                                                            |     |

|   | 2.1 The position measurement system                        |     |

|   | 2.1.1 The GassiPlex.                                       |     |

|   | 2.1.2 The V551B CAEN C-RAMS SEQUENCER.                     |     |

|   | 2.1.3 The two channels C-RAMS                              |     |

|   | 2.2 TGC readout scheme                                     |     |

|   | 2.2.1 The 128 channels Multihit Time to Digital Conversion |     |

|   | 2.2.2 The Amplifier Shaper Discriminator                   |     |

|   | 2.2.3 The ASD READOUT                                      |     |

|   | 2.2.4 The ASD TO TDC                                       |     |

|   | 2.2.5 The NIM to ECL translator.                           |     |

|   | 2.3 Trigger system.                                        |     |

|   | 2.4 Electronics general scheme.                            |     |

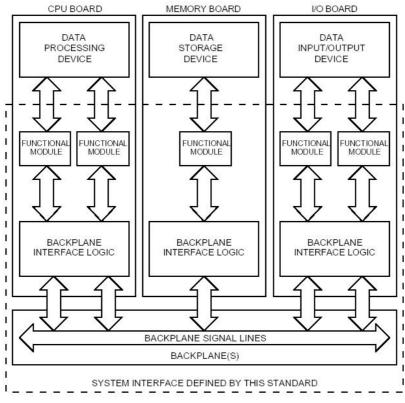

| 3 | VME Interface and functionality                            |     |

| 5 | 3.1 SEQUENCER                                              |     |

|   | 3.1.1 The SEQUENCER registers                              |     |

|   | 3.2 C-RAMS                                                 |     |

|   | 3.2.1 C-RAMS registers                                     |     |

|   | 3.3 TDC                                                    |     |

|   | 3.3.1 The TDC registers.                                   |     |

|   | 3.3.2 TDC programming procedure                            |     |

| 4 |                                                            |     |

| • | VME Software                                               |     |

|   | 4.1 Drivers                                                |     |

|   | 4.1.1 The memory mapping                                   |     |

|   | 4.1.2 The VMEbus error detections                          |     |

|   | 4.2 Online program structure                               |     |

|   | 4.2.1 The SEQUENCER setting                                |     |

|   | 4.2.2 The C-RAMS setting                                   |     |

|   | 4.2.3 The TDC setting                                      |     |

|   | 4.3 Pedestals and Thresholds                               |     |

|   | 4.4 The Data Acquisition program                           |     |

|   | 4.5 Data acquisition system monitoring                     |     |

| 5 | Results                                                    |     |

|   | 5.1 The timing of the Scintillators                        |     |

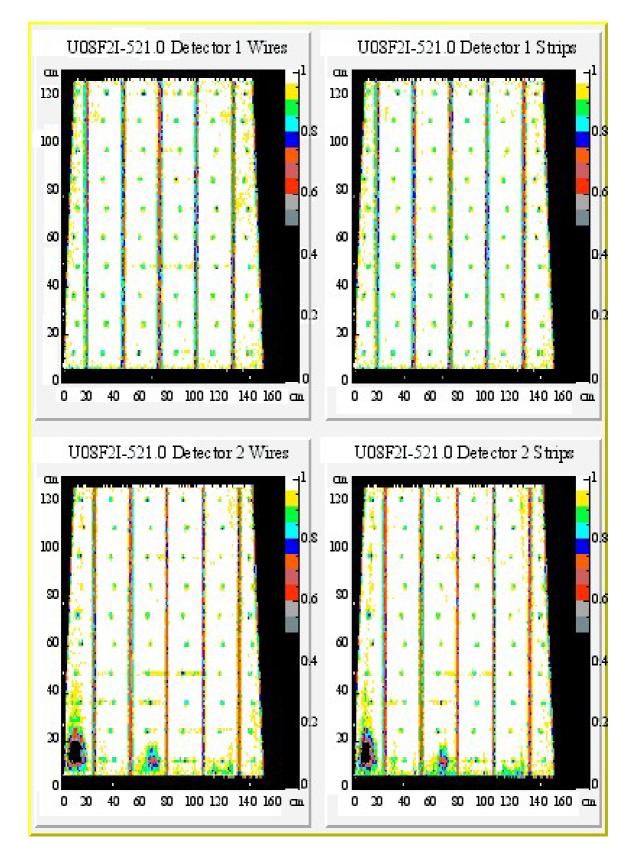

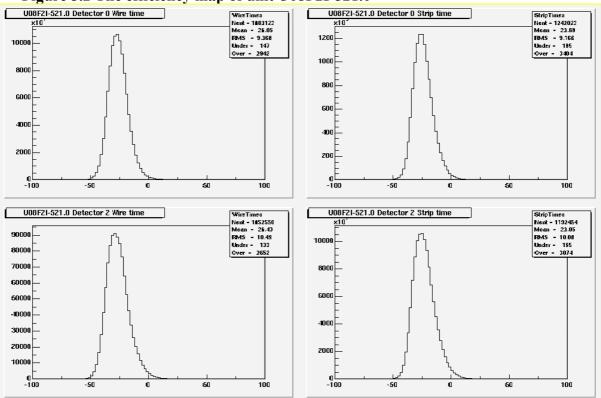

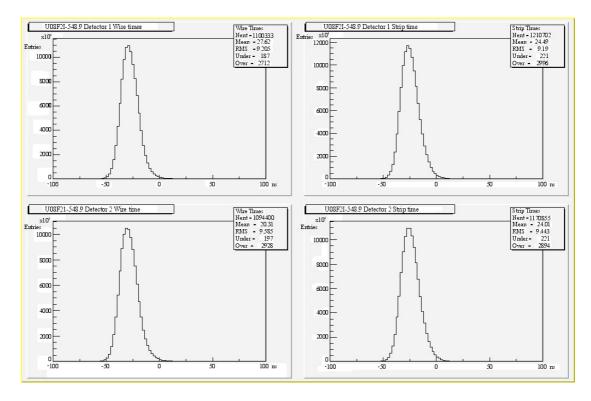

|   | 5.2 Example - The results of unit U08F2I-521.0             | 64  |

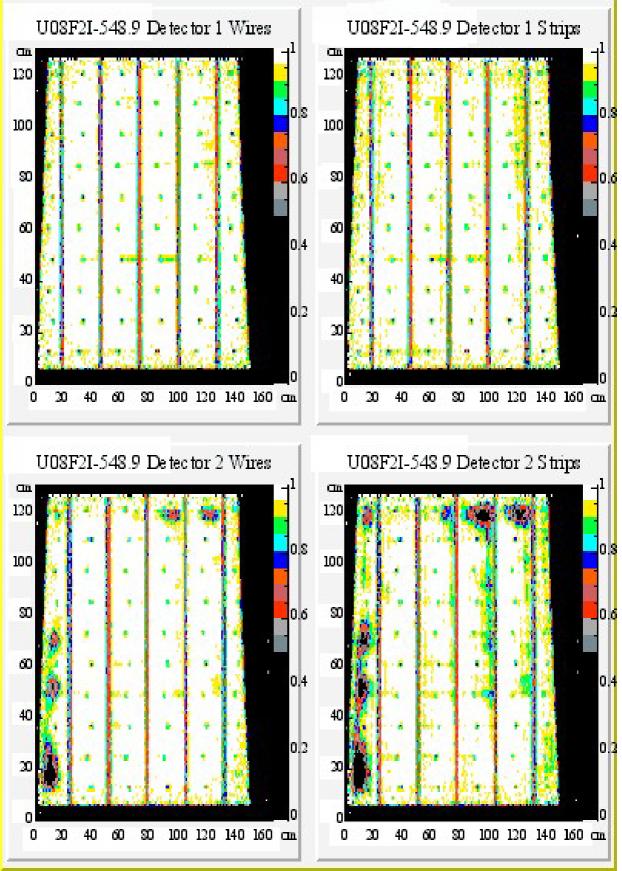

|   | 5.3 Another example - The result of unit U08F2I-548.9      | 67  |

| 6 | Summary                                                    | .68 |

| 7 Bibliography                                    | 69 |

|---------------------------------------------------|----|

| Appendix I: VMEBUS Specification                  |    |

| Appendix II: VMEbus Application Program Interface |    |

| Appendix III: A structure of binary output file   | 83 |

# List of figures.

| Figure 1.1 Overall layout of the ATLAS Detector                                          | 9    |

|------------------------------------------------------------------------------------------|------|

| Figure 1.2 Components of a Detector Atlas                                                |      |

| Figure 1.3 Three-dimensional view of the muon spectrometer instrumentation indicating th |      |

| areas covered by the four chamber technologies.                                          |      |

| Figure 1.4 Block diagram of the Trigger/DAQ system.                                      |      |

| Figure 1.5 Basic configuration of TGC                                                    |      |

| Figure 1.6 Electric field lines and potentials in a TGC.                                 | .13  |

| Figure 1.7 TGC structure showig anode wires, graphite cathodes, G-10 layers, and a read- | _    |

| out strip orthogonal to the wires.                                                       |      |

| Figure 1.8 Schematic diagram of cosmic ray telescope                                     |      |

| Figure 2.1 Functional block of a GassiChip                                               |      |

| Figure 2.2 The readout sequence of GassiPlex                                             |      |

| Figure 2.3 A typical distribution of the pedestal for one channel of the GassiChip       |      |

| Figure 2.4 Model v551B. The front panel.                                                 |      |

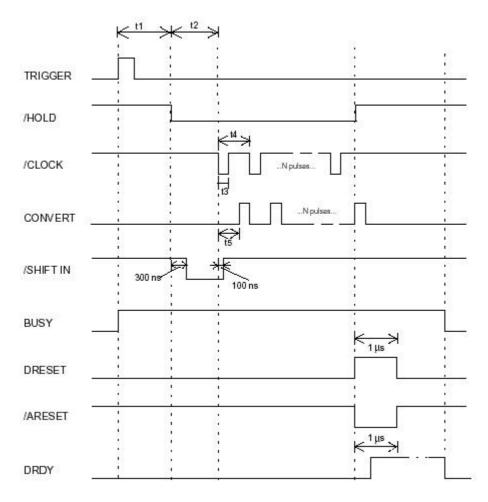

| Figure 2.5 Standard operation sequence.                                                  |      |

|                                                                                          |      |

| Figure 2.6 Model v550. The front panel.                                                  |      |

| Figure 2.7 Model v767. The front panel and Input connector pin assignment.               | . 24 |

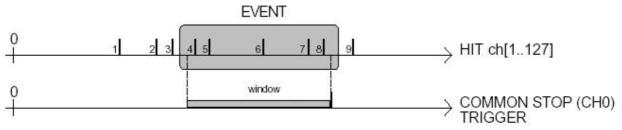

| Figure 2.8 Common Stop Emulation                                                         |      |

| Figure 2.9 Common Stop Sequence.                                                         |      |

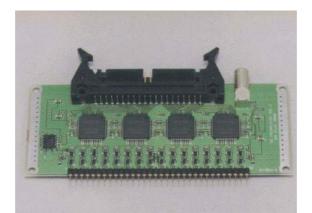

| Figure 2.10 The ASD board                                                                |      |

| Figure 2.11 Block diagram of the ASD chip.                                               |      |

| Figure 2.12 The signal propagations of ASD chip                                          |      |

| Figure 2.13 The ASDR top and back panel and the input connector pin assignment           |      |

| Figure 2.14 The TGC output signal from the ASDR                                          |      |

| Figure 2.15 The ASDTDC top panel and input connectors pin assignment.                    |      |

| Figure 2.16 The ASD TO TDC connections system layout.                                    | .30  |

| Figure 2.17 Schematic diagram of the trigger logical connection                          | .31  |

| Figure 2.18 Scheme of the trigger design                                                 |      |

| Figure 2.19 The TDC trigger (channel 1), signal from the TGC (channel 2) oscilogram      | . 32 |

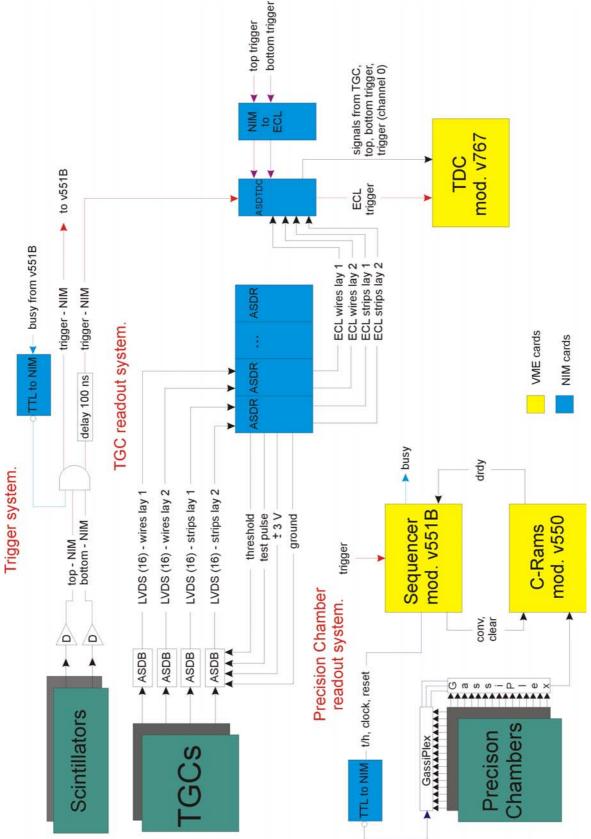

| Figure 2.20 The leyout of the readout system.                                            |      |

| Figure 2.21 The C-RAMS-SEQUENCER connections layout                                      |      |

| Figure 2.22 The ASDR-ASDTDC-TDC connections layout                                       | . 35 |

| Figure 3.1 SEQUENCER Status Register                                                     |      |

| Figure 3.2 SEQUENCER Number of Channels Register                                         |      |

| Figure 3.3 SEQUENCER T1 Register                                                         |      |

| Figure 3.4 SEQUENCER T2 Register                                                         |      |

| Figure 3.5 SEQUENCER T3 Register                                                         |      |

| Figure 3.6 SEQUENCER T4 Register                                                         |      |

| Figure 3.7 SEQUENCER T5 Register                                                         |      |

| Figure 3.8 C-RAMS Word Counter Register                                                  |      |

| Figure 3.9 Mod. v550 FIFO structure                                                      |      |

| Figure 3.10 C-RAMS Number of channels                                                    |      |

| Figure 3.11 C-RAMS Number of channels                                                    |      |

| Figure 3.11 C-RAMS Status Register<br>Figure 3.12 C-RAMS Pedestal/Threshold memories     |      |

|                                                                                          |      |

| Figure 3.13 TDC Output Buffer Data Structure                                             |      |

| Figure 3.14 TDC Status Register 1                                                        |      |

| Figure 3.15 TDC Status Register 2                                                        |      |

| Figure 3.16 TDC Control Register 2                                                       | .43  |

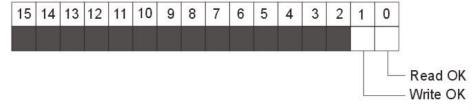

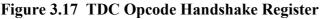

| Figure 3.17 TDC Opcode Handshake Register                                                  | ī |

|--------------------------------------------------------------------------------------------|---|

| Figure 3.18 TDC Opcode Register                                                            | í |

| Figure 3.19 Mod. V767 R/W operations: software logic blocks                                |   |

| Figure 3.20 Mod. V767 OPCODE Word                                                          |   |

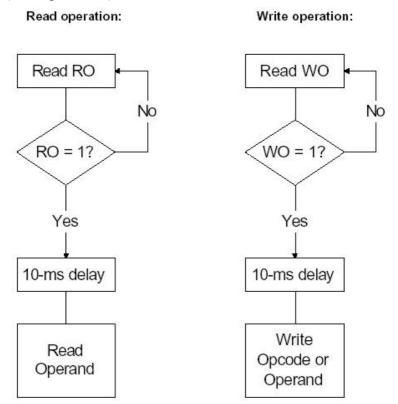

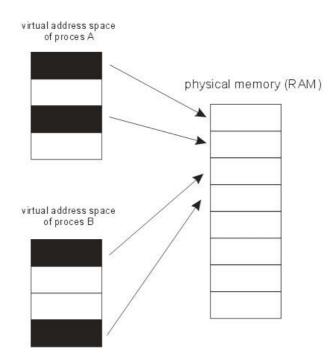

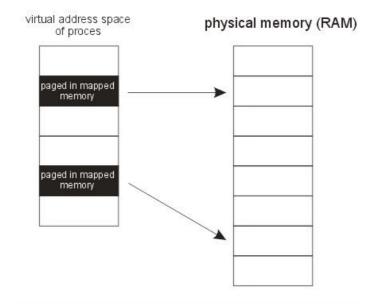

| Figure 4.1 Example of the relationship between the virtual address spaces of two processes |   |

| and physical memory                                                                        | ) |

| Figure 4.2 Mapping of the Virtual Memory                                                   | ) |

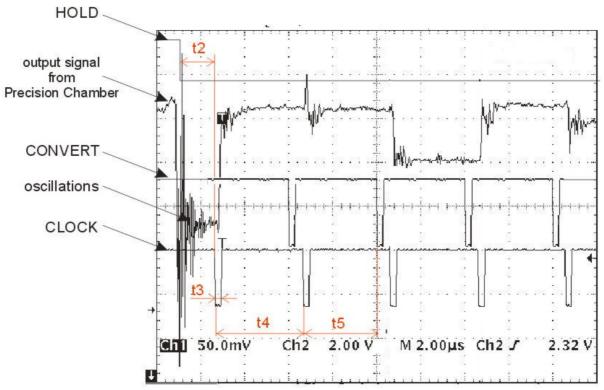

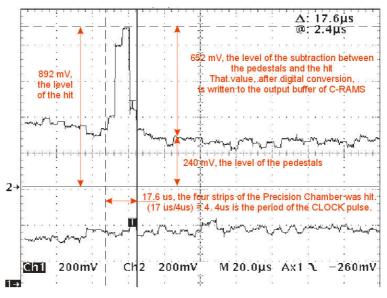

| Figure 4.3 The SEQUENCER timing oscilogram                                                 | ; |

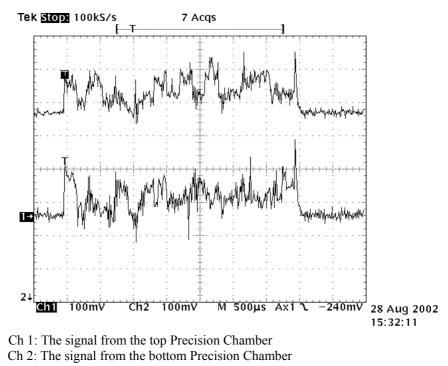

| Figure 4.4 The oscilogram of the signals from the Precision Chambers                       | ; |

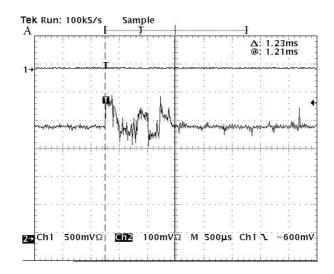

| Figure 4.5 The signal from the PC when the CLOck pulse is not passing all GassiChips 54    | ! |

| Figure 4.6 Readout sequence inside GassiChips                                              | ! |

| Figure 4.7 The back window width of the TDC                                                | ī |

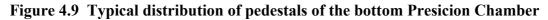

| Figure 4.8 Typical distribution of pedestals of top Presicion Chamber                      | ĵ |

| Figure 4.9 Typical distribution of pedestals of the bottom Presicion Chamber               | 7 |

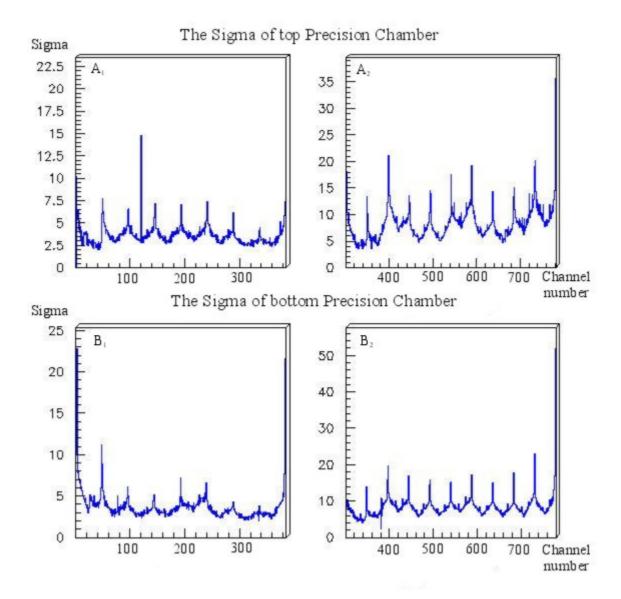

| Figure 4.10 The sigma for all channels of both Precision Chambers                          | ) |

| Figure 4.11 The example of the hit of the Precision Chamber                                | ) |

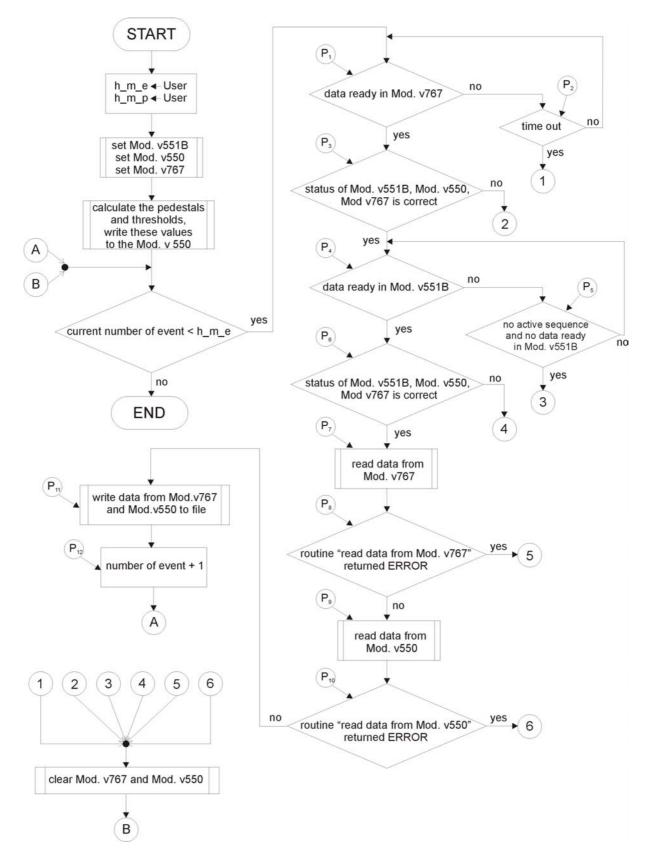

| Figure 4.12 The structure of data acquisition routine                                      | ) |

| Figure 4.13 Algoritm of the online code                                                    | ) |

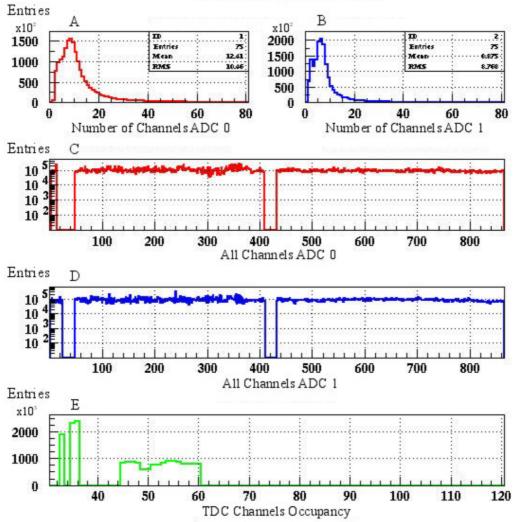

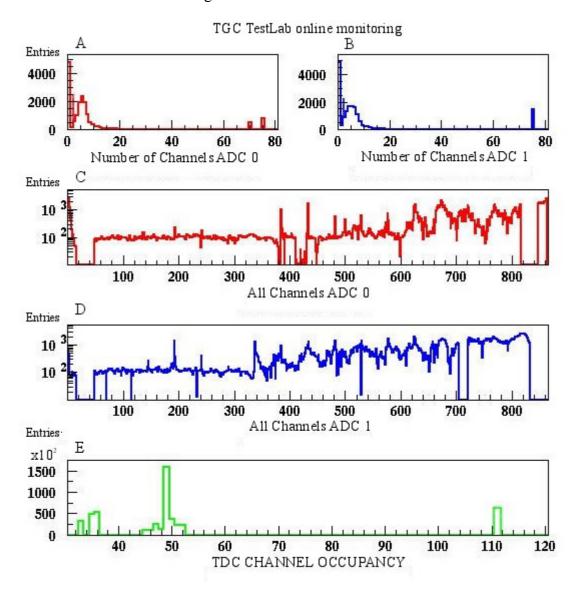

| Figure 4.14 The monitoring                                                                 | r |

| Figure 4.15 The monitoring                                                                 | , |

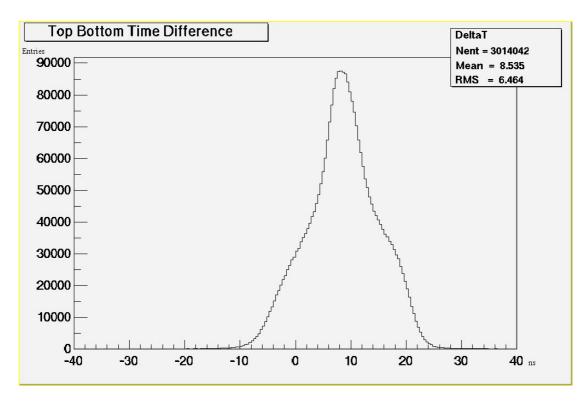

| Figure 5.1 The timing of the Scintillators                                                 | ; |

| Figure 5.2 The efficiency map of unit U08F2I-521.0                                         | ī |

| Figure 5.3 The timing of the unit U08F2I-521.0                                             | ī |

| Figure 5.4 The efficiency map of unit U08F2I-548.9                                         | 1 |

| Figure 5.5 The timing of the unit U08F2I-548.9                                             | ) |

# List Of Tables.

| Table 1.1. The LHC general parameters                        | 8  |

|--------------------------------------------------------------|----|

| Table 1.2 Principal TGC parameters.                          | 12 |

| Table 2.1 The inputs and outputs of the SEQUENCER            | 20 |

| Table 2.2 The inputs and outputs of the C-RAMS               | 23 |

| Table 2.3 The inputs and outputs of the TDC                  | 25 |

| Table 3.1 SEQUENCER Address Map                              | 36 |

| Table 3.2 C-Rams Address Map                                 | 39 |

| Table 3.3 Address Map for the TDC                            | 42 |

| Table 3.4 Mod. V767 OPCODE Words                             | 49 |

| Table 5.1 The efficiency of the unit U08F2I-521.0            | 65 |

| Table 5.2 The efficiency of the unit U08F2I-548.9            | 68 |

| Table AIII.1: The structure of the binary online output file | 84 |

## **1** Introduction

## 1.1 The Large Hadron Collider

The Large Hadron Collider (LHC) is a proton-proton (pp) collider designed to reach a centre of mass energy of 14 TeV and a luminosity of  $10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>. The design parameters of LHC are listed in Table 1.1. Typical of such a high energy accelerator is a beam crossing time of 25 ns with about 23 pp interactions per crossing.

The LHC is an unprecedented project, not only in terms of centre-of-mass energy and luminosity of the colloding beams, but also in terms of cost, complexity and size of the experiments for which it is designed. It is supported by strong physics motivation, which is to understand the origin elementary particle masses, and to search for physics beyond the Standard Model of fundamental interactions.

| LHC General Parameters                   |       |                                  |  |  |

|------------------------------------------|-------|----------------------------------|--|--|

| Energy at collision                      | 7     | TeV                              |  |  |

| Energy at injection                      | 450   | GeV                              |  |  |

| Dipole field at 7 TeV                    | 8.33  | Т                                |  |  |

| Coil inner diameter                      | 56    | mm                               |  |  |

| Distance between aperture axes (1.9 K)   | 194   | mm                               |  |  |

| Luminosity                               | 1 E34 | cm <sup>-2</sup> s <sup>-1</sup> |  |  |

| Beam beam parameter                      | 3.6   | 10 <sup>-3</sup>                 |  |  |

| DC beam current                          | 0.56  | A                                |  |  |

| Bunch spacing                            | 7.48  | М                                |  |  |

| Bunch separation                         | 24.95 | Ns                               |  |  |

| Number of particles per bunch            | 1.1   | 10 <sup>11</sup>                 |  |  |

| Normalized transverse emittance (r.m.s.) | 3.75  | μm                               |  |  |

| Total crossing angle                     | 300   | µrad                             |  |  |

| Luminosity lifetime                      | 10    | Н                                |  |  |

| Energy loss per turn                     | 7     | KeV                              |  |  |

| Critical photon energy                   | 44.1  | eV                               |  |  |

| Total radiated power per beam            | 3.8   | kW                               |  |  |

| Stored energy per beam                   | 350   | MJ                               |  |  |

| Filling time per ring                    | 4.3   | min                              |  |  |

Table 1.1. The LHC general parameters.

# 1.2 A Toroidal LHC Apparatus

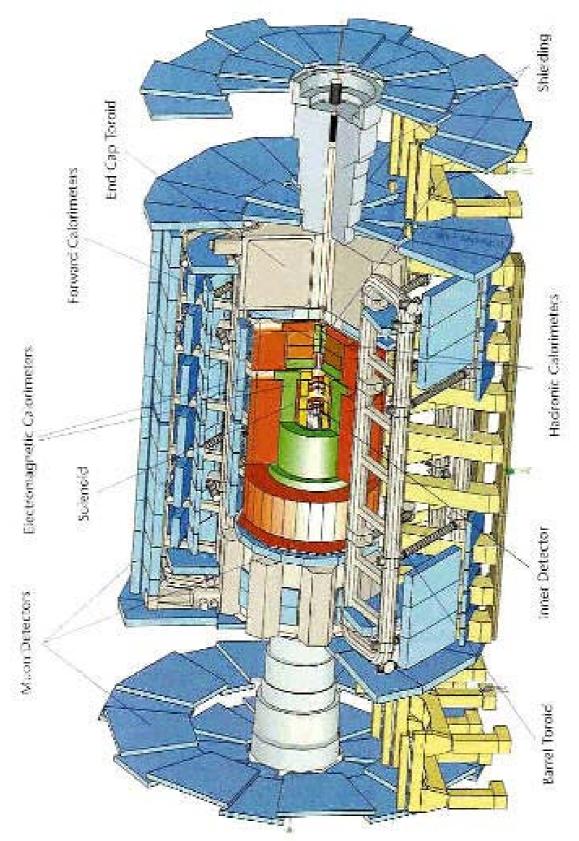

Figure 1.1 Overall layout of the ATLAS Detector

Two experiments have been proposed and approved to study pp interactions. One of them is the so called ATLAS experiment (ATLAS stands for A Toroidal LHC AparatuS) and one of its components, the forword muon trigger, is related to the work presented in this thesis. The overall ALTAS detector layout is shown in Figure 1.1. The basic criteria of the detector design  $[^1]$  include the following:

- very good electromagnetic calorimetry for electron and photon indentification and measurements;

- high-precision muon momentum measurements;

- large acceptance in pseudorapidity,  $\eta$ , where  $\eta = -\ln ctg \frac{\Theta}{2}$  and  $\Theta$  is the polar angle

of produced particles with respect to the beam line.

- triggering and measurement of particles with a low transverse-momentum,  $p_{T,}$  threshold;

### 1.2.1 Components of the ATLAS detector

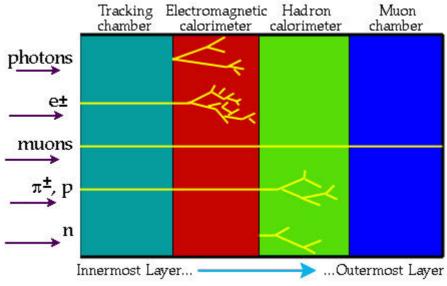

The reason that high energy detectors are divided into many components is that each component tests for a special set of particle properties. These components are stacked so that all particles go through the different layers sequentially. A particle will not be detected unless it either interacts with a given detector component in a measurable fashion, or decays into detectable particles.

Figure 1.2 Components of a Detector Atlas

An example of how various particles are detected is shown in Figure 1.2 As it happens, each particle type has its own "signature" in the detector.

- The trajectory of charged particles are detected in the tracking chambers.

- Photons and electorns are absorbed in the electromagnetic sections of the calorimeter.

- Strongly interacting particles like neutrons, protons and pions are absorbed in the hadron calorimeter.

- Characteristic of muons is that they interact very weekly with matter and their trajectories can be observed in tracking chambers (muon chambers) placed as the outermost layer.

#### **1.2.2** Moun chamber layout.

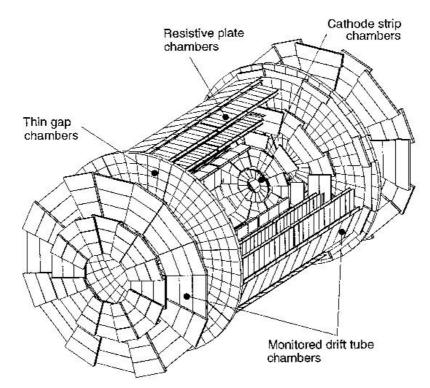

Figure 1.3 Three-dimensional view of the muon spectrometer instrumentation indicating the areas covered by the four chamber technologies.

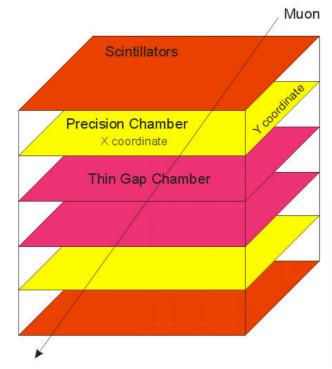

The overall layout of the muon chambers in the ATLAS detector is shown in Figure 1.3. For reasons of costs and detection efficiency, four different chamber technologies are used as indicated in the figure. The chambers are arranged such that particles from the interaction point traverse three stations of chambers. The barrel chambers form three cylinders concentric with the beam axis, at radii of about 5, 7.5 and 10 m. They cover the pseudorapidity range  $|\eta| < 1$ . The end-cap chambers cover the range  $1 < |\eta| < 2.7$  and are arranged in four disks at distances of 7, 10, 14 and 21 - 23 m from the interaction point, concentric with the beam axis. The trigger function in the end-caps is provided by first three discs, the three stations of Thin Gap Chambers (TGC). The three stations consist of 192 TGC units and 440,000 readout channels, and cover an area of 2900 m<sup>2</sup>.

#### 1.2.3 Trigger and data-acquisition system.

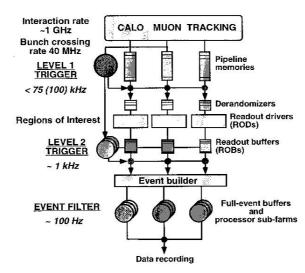

Figure 1.4 Block diagram of the Trigger/DAQ system.

The ATLAS trigger and the data-acquisition (DAQ) system is based on three levels of online event selection [<sup>3</sup>]. Each trigger level refines the decisions made at the previous level and, where necessary, applies additional selections criteria. Starting form an initial bunchcrossing rate of 40 MHz (interaction rate of  $\sim 10^9$  Hz at luminosity of  $10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>), the rate of selected events must be reduced to  $\sim 100$  Hz for permanent storage. While this requires an overall rejection factor of  $10^7$  against the so called 'minimum-bias' events, excellent efficiency must be retained for the rare new physics processes, such as Higgs boson production and decay, which will be searched for in ATLAS. Figure 1.4 shows a simplified functional view of the Trigger/DAQ system.

An essential requirement on the level 1 trigger is that it should uniquely identify the bunchcrossing of interest within the short (25 ns) bunch-crossing interval.

The TGCs were selected for the level one muon trigger becouse of their adequately short response time. The timing resolution of the system is such that there is a 99% efficiency for signals arriving within the 25ns gate.

#### 1.3 Thin Gap Chamber.

The parameters characterising a single TGC unit are given in Table 1.2.

| Gas gap                            | 2.8 mm                           |

|------------------------------------|----------------------------------|

| Anode wire pitch                   | 1.8 mm                           |

| Wire diameter                      | 50 μm                            |

| Wire potential                     | 3100 V                           |

| Gas mixture                        | $CO_2/n-C_5H_{12}(55\%/45\%)$    |

| Gas amplification                  | 106                              |

| Anode r/o pitch                    | 7.2-39.0 mm                      |

| Time resolution                    | >99% efficiently for 25 ns gate  |

| Rate capability                    | Tested at 30 kHz/cm <sup>2</sup> |

| Read-out strip width               | 14.6-49.1 mm                     |

| Total number of anode r/o channels | 280 000                          |

| Total number strip r/o channels    | 95 000                           |

Table 1.2 Principal TGC parameters.

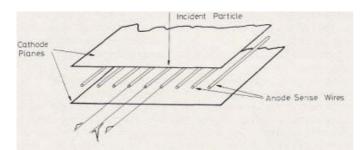

The TGC unit consists of a plane of equally spaced anode wires centered between two cathode planes as shown in Figure 1.5  $[^2]$ . The volume between two cathodes is field with a quenching gas.

Figure 1.5 Basic configuration of TGC.

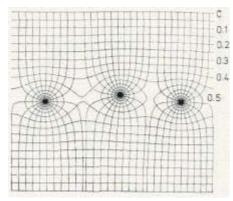

Figure 1.6 Electric field lines and potentials in a TGC.

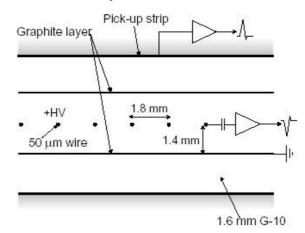

Figure 1.7 TGC structure showig anode wires, graphite cathodes, G-10 layers, and a read-out strip orthogonal to the wires.

Each wire sandwiched between two cathode planes acts as an independent proportional counter. The operating high voltage foreseen is 3.1 kV. The electric field configuration (see Figure 1.6) and the small wire distance provide for a short drift time and thus a good time resolution [<sup>2</sup>]. Except for the region very close to the anode wires, the field lines are essentially parallel and almost constant.

If electrons and ions are now liberated in the constant field region they will drift along the field lines toward the nearest anode wire and opposing cathode. Upon reaching the high field region, the electrons will be quickly accelerated to produce an avalanche. The positive ions liberated in the multiplication process then induce a negative signal on the anode wire.

The neighboring wires are also affected; however, the signals induced here are positive and of small amplitude as illustrated in Figure 1.7. In a similar manner, a positive signal is induced on the cathode. There is thus no ambiguity as to which wire is closest to the ionizing event.

## **1.3.1** Principle of operation of TGCs.

The TGCs are constructed in doublets and triplets. A TGC doublet is a unit which has two chambers. A TGC triplet has two chambers and one plane of wire between them. A chamber is a single layer of active detector element. For TGCs, this is a wire plane and its strips.

To obtain high granularity, good time resolution, high rate capabilities and ageing characteristics, a highly quenching gas that avoids streamers, while permitting a saturated operation is needed. This is achieved with a mixture of CO2–n-pentane (55%–45%), where the n-pentane plays the role of the quencher. No other gas that is less flammable has been found that provides the above performance.

### 1.3.2 TGC test bench

The TGC units are produced in the Weizmann institute in Israel and also in KEK in Japan and in China. There are three test benches to check the performance of TGC modules, two in Israel, in Technion and Tel-Aviv, and one in Kobe University in Japan. The purpose of this tests is too-fold. For each detector a detailed map of detection efficiency for the wires and strips is determined as well as their respective time resolution.

At the test site the TGC units pass the following steps of processing

- Preliminary checks

- Efficiency test

- Validation (Acceptance/Rejection)

A visual inspection of the incoming TGC units is performed to check that no damage was done to them during transport.

Figure 1.8 Schematic diagram of cosmic ray telescope.

The cosmic ray telescope is 2,2 m high, 1,6 m wide and 2,5 m long. There are 11 slots with a distance of 20 cm between them. The top and the bottom layers consist of scintillators planes. A signal in coincidence from the two planes signals the passage of a cosmic muon. The next layers from the bottom and from the top consist of the so called Precision Chambers (PC). The latter are made of TGC detectors which differ from the tested TGC chambers by their readout granularity. Their role is to accurately measure the positions where the muon crossed the chambers.

Accumulating events for a period of one week will permit a full mapping of the efficiency of each detector in the stack. The criteria for a good chamber is having 95% of its active area efficient at level of higher then 95% within a 25 nsec gate. If the unit failed the test it is removed from the test bench and returned to the Weizmann institute. After successfully passing this test, the detectors are flushed with CO<sub>2</sub>, sealed and prepared for the transportation to CERN.

In the following, we present the test bench for the TGC chambers as designed and built at Tel Aviv University. In the chapter two I am describing the hardware readout sytem, in the chapter three I am presenting the VME interface and functionality, the chapter four is describing the online software. The results of the testing are shown in the chapter five.

## 2 Readout system.

#### 2.1 The position measurement system

A Precision Chamber has similar construction as the TGC. The Precision Chamber has two orthogonal layers of strips which are built with the high granularity to provide a precise crossing moun position.

The readout system of the Precision Chamber is based on the C-Mos VLSI frontend chip GassiPlex, composed of four GassiPlex chips of 16 channels per one GassiBoard. A number, N, of chips can be "daisy chained", allowing the analog multiplexed outputs of N \* 16 channels to be sent on a single line to a VME-read out module. Unit such as CAEN Readout for Analog Multiplexed Signals (CRAMS) performing the digitalization and zero suppression of that analog signal sequence. The multiplexing and digitalization are two synchroneous operations operated by the same clock.

In case of a large number of channels, such a multiplexed scheme allows to minimize the number of expensive redout modules. The multiplexing frequency of 5 MHz allows a maximum data taking rate of a few hundred kHz for 16 channels.

#### 2.1.1 The GassiPlex.

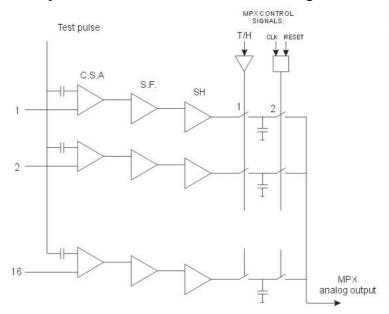

The single GassiChip consists of 16 channels as shown in Figure 2.1.

#### Figure 2.1 Functional block of a GassiChip

Each channel is composed of a charge sensitive amplifier (CSA), a switchable filter (SF), a shaping amplifier (SH) and Track/Hold stage (T/H).

The GassiChip is an ungated, then asynchronous, device, meaning that its inputs/outputs are always in a "live stage". Therefore, each output, or baseline, has to be kept at a constant DC-level in the absence of an input signal. That level is called "pedestal", evaluated in mV. Measuring the fluctuation of the pedestal level gives the noise level of that channel (in practice, as the sigma of a pedestal value distribution).

The shaping stage symmetries the pulse shape and allows a slight adjustment of the peaking time at 700 ns  $\pm$  100 ns via external bias resistor. That time is taken as a natural built-in delay used to wait for the external trigger decision.

In the operation mode, all the switches driven by the T/H stage are closed and those driven by the Multiplexed (MPX) stage open in the whole system. At the occurrence of an event, the capacitors associated with the hit channels are charged up by the corresponding detector currents. An external trigger signal, synchronous to that event, is used to generate a "HOLD" signal, sent to the whole system, in order to open all switches at a time corresponding to the peaking time of the shaping amplifier. Therefore, a charge particle crossing the detector leaves a signal in the strips close to the crossing point a signal which is larger then their pedestal level.

As long as the HOLD signal is kept active, the switches are open and the charges are freezed in the capacitors. As soon as the HOLD signal is released, the switches are closed and the charges is lost.

The decision for reading out an event (charges stored in the capacitors) is independent of the T/H operation. A train of MPX clock pulses is generated by an external device such as a SEQUENCER. The SEQUENCER allows adjusting the number and frequency of the clock pulses.

As soon as the clock train is over a RESET signal is sent to the GassiPlex, repositioning all the switches to their initial positions. That signal can be sent after the HOLD signal is released.

After the HOLD signal is generated, the trigger logic is vetoed by a BUSY signal to protect the whole system from taking new events. That protection is released by the SEQUENCER when all the tasks are terminated.

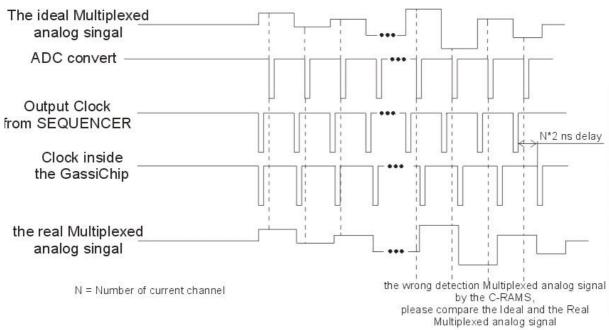

An example of the analog multiplexing train is shown in Figure 2.2. The clock train is sent also to the readout module where the digitization is performed. The digital conversion (and the suppression) of each analog step is done between two clock pulses, therefore:

- The ADC convert train must be synchroneous to the MPX clock train (same source). The SEQUENCER should give the possibility to manually adjust a delay between the 2 trains in order to enable the ADC conversion to be done in a stable part of each analog step.

- Although the two clock trains are issued from the same source, the MPX clock train is propagated trought all the GassiPlex chips to operate the MPX function.

Therefore, the train is accumulating a delay (2 ns per channel, 32 ns per chip) with respect to the ADC convert train. If the time between two clock pulses is too short, the synchronization requirement is lost after a certain number of clock pulses.

Figure 2.2 The readout sequence of GassiPlex.

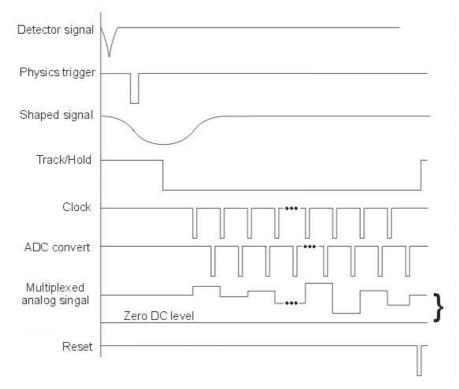

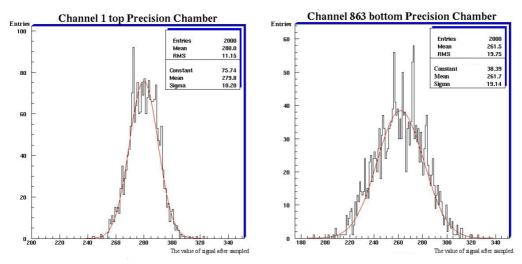

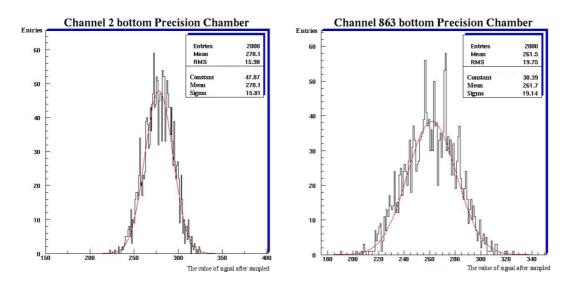

In order to define a threshold value for every channel, one has to measure all pedestals level, PED(i), their RMS (noise figure), and sigma SIG(i). The usual way is to calculate the threshold table as TH(i) = PED(i) + N\*SIG(i) where N is a selectable constant usually larger then three. In our case 2000 events are taken to calculate the threshold value. To minimize the noise level we choose to work with N equal to three. The threshold value for each channel is written to the pedestal and threshold memory of the C-RAMS [<sup>4</sup>]. The typical distribution of one channel of the PC is shown in Figure 2.3.

Figure 2.3 A typical distribution of the pedestal for one channel of the GassiChip.

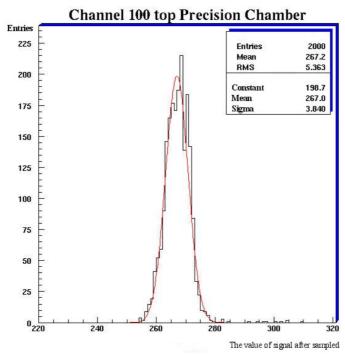

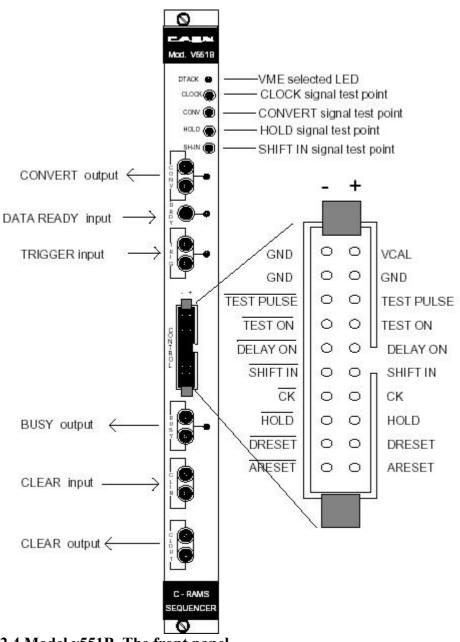

#### 2.1.2 The V551B CAEN C-RAMS SEQUENCER.

The V551B CAEN C-RAMS SEQUENCER (SEQUENCER) is a one-unit wide VME module that handles the Data Acquisition from multiplexing front-end chips, its front panel is shown in Figure 2. and its inputs outputs are described in the Table 2.1 [<sup>5</sup>]. The SEQUENCER has been developed to control the signals from/to the C-RAMS boards Mod. V550. A single SEQUENCER can control up to 19 C-RAMS modules in a complete VME crate, thus enabling the readout of 19\*(2\*2016) = 76608 multiplexed detector channels. The Mod. V551B is controlled via VME bus. The number N of detector channels to be read out by the C-RAMS can be programmed via VME up to 2047 (though the V550 C-RAMS can accept only 2016 detector channels). The multiplexing frequency can be set via VME from 100 kHz to 5 MHz, with programmable Duty Cycle. The delay between the multiplexing Clock signal and the Convert signal of the acquisition cards can be adjusted to wait for the settlement of the analog signal coming from the multiplexers. The delay between the TRIGGER and the HOLD signal and the delay between the HOLD and the Convertsion Cycles (CONVERT) are also programmable.

Figure 2.4 Model v551B. The front panel.

| Inputs     |                        |                      |           |  |  |

|------------|------------------------|----------------------|-----------|--|--|

| Signal     | Standard               | Active               | Connector |  |  |

| DATA READY | TTL                    | High                 | LEMO      |  |  |

| TRIG       | NIM                    | High                 | LEMO      |  |  |

| CLEAR IN   | NIM                    | High                 | LEMO      |  |  |

|            | Out                    | puts                 |           |  |  |

| CONVERT    | NIM                    | High                 | LEMO      |  |  |

| BUSY       | TTL                    | High                 | LEMO      |  |  |

| CLEAR OUT  | NIM                    | High                 | LEMO      |  |  |

| VCAL       | Analog Voltage         | Positive or negative | CONTROL   |  |  |

| TEST PULSE | TTL differential level | High                 | CONTROL   |  |  |

| TEST ON    | TTL differential level | High                 | CONTROL   |  |  |

| DELAY ON   | TTL differential level | High                 | CONTROL   |  |  |

| SHIFT IN   | TTL differential level | Low                  | CONTROL   |  |  |

| CLOCK  | TTL differential level | Low  | CONTROL |

|--------|------------------------|------|---------|

| HOLD   | TTL differential level | Low  | CONTROL |

| DRESET | TTL differential level | High | CONTROL |

| ARESET | TTL differential level | Low  | CONTROL |

#### Table 2.1 The inputs and outputs of the SEQUENCER.

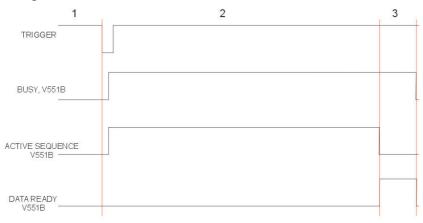

The readout sequence starts with an external or a VME TRIGGER. The BUSY becomes active, indicating that the module cannot accept another TRIGGER. The leading edge of the TRIGGER starts a monostable multivibrator circuit. After a t1 time programmable via VME the circuite activates the HOLD and the SHIFT IN signals. The HOLD signal is used to sample the signal at the output of the shapers at peaking time. Once the HOLD is asserted, a CLOCK cycles begins after a programmable t2 time. In the following readout sequence, N CLOCK and CONVERT pulses are generated. The number N of detector channels (between 1 and 2,047) can be programmed via VME. A CONVERT pulse follows each CLOCK pulse with a delay of t5 ns, programmable via VME.

The purpose of the delay is to wait for the relaxation of the analog signal coming from the multiplexers. The width of the active phase of the CLOCK and CONVERT pulses is t3 ns, programmable via VME. The V550 C-RAM accepts only CONVERT pulses with active phase  $\geq 100$  ns. The repetition period t4 of the CLOCK and CONVERT pulses (and consequently the multiplexing frequency) is programmable via VME. The CLOCK, CONVERT, HOLD and SHIFT-IN signals are available on four test points placed on the front panel. The active level of the test points is always high, disregarding of the normal level of the relevant signals on the front panel connectors.

With the last CONVERT pulse, the DRESET line (also the ARESET if enabled) becomes active for resetting the front-end circuitry. After the generation of the last CONVERT pulse, if none of the C-RAMS acquisition cards has asserted the DRDY signal the BUSY signal becomes inactive. Otherwise, when the DRDY raised (at least one channel has data ready), the BUSY signal remains high until all the C-RAMS FIFOs are read out, i.e. until the DRDY becomes inactive. An example of the sequence is shown in Figure 2..

Software controlled VETO is available as well. The VETO forces the V551B in a BUSY condition (no TRIGGER accepted).

Figure 2.5 Standard operation sequence.

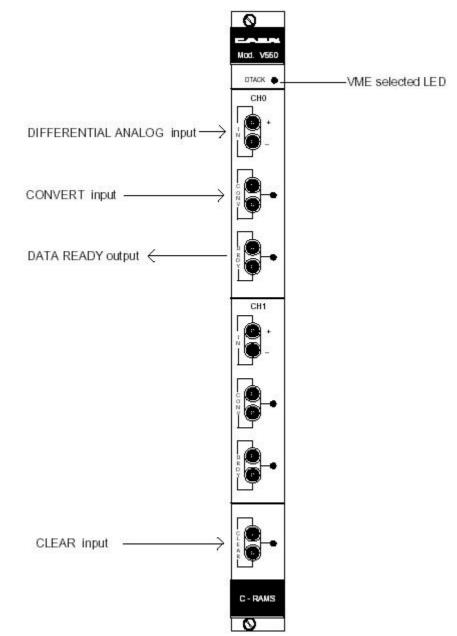

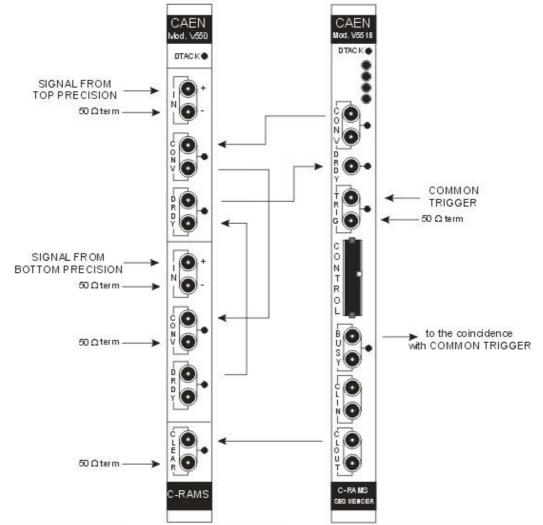

#### 2.1.3 The two channels C-RAMS

The two channels C-RAMS is a one-unit wide VME module housing two independent Analog to Digital Conversion blocks to be used for the readout of analog multiplexed signals coming from several front-end chips [6]. The front panel is shown in Figure 2. and its inputs, outputs are shown in Table 2.2.

Each block of the module accepts positive, negative or differential input signals, the signals are amplified and fed to an ADC. The module has the following features:

- Conversion rate up to 5 MHz.

- Differential input with selectable amplification.

- 10 bit linear conversion.

- Zero suppression and pedestal subtraction.

- Diagnostics and self-test capabilities.

With the occurrence of an external CONVERT signal, the input signal is sampled by the ADC and its digital value is compared to a threshold value. If the signal is over threshold, the pedestal is subtracted and the result is stored in an Output Buffer arranged in FIFO logic 2K x 32 bit. For this purpose each block of the module houses two memories for the storage of the thresholds and the pedestals of each detector channel. The pedestal and threshold values are independent for each channel and the pedestal/threshold memory, which is arranged in 2K x 24 bit, can be filled (or read) via the VME.

The number of N detector channels to be read between 32 and 2016 in steps of 32out is controlled via VME. At the end of a conversion cycle (N CONVERT pulses), with the last word stored in the FIFO, if there is data in the FIFO, the module channel goes into the Data Ready state signaling that the data must be read via VME. A positive open collector signal ("DRDY") is available for each channel on the front panel and is provided with two bridged connectors for daisy chaining. A fast CLEAR signal is also available for cycle abort.

It is possible to operate the module in a TEST mode (VME selectable) by simulating some input patterns, as if they were coming from the ADC.

Figure 2.6 The C-RAMS front panel.

| Inputs         |                    |         |        |           |               |

|----------------|--------------------|---------|--------|-----------|---------------|

| Signal         | Standard           | -       | Active | Connector | Minimum width |

| INPUT CHANNELS | Positive or differ | rential |        | LEMO      |               |

| CONVERT        | NIM                |         | High   | LEMO      | 100 ns        |

| CLEAR          | NIM                |         | High   | LEMO      | 50 ns         |

| Outputs        |                    |         |        |           |               |

| DATA READY     | TTL                | Hi      | gh     | LEMOI     |               |

|                |                    |         |        |           |               |

Table 2.2 The inputs and outputs of the C-RAMS

The module can be used to calculate the values of the thresholds and the pedestals. For this purpose the threshold/pedestal memory must be zeroed via the VME. In this way the zero suppression and pedestal subtraction functions are disabled and the words written in the FIFO are the true converted values. The readout is performed in the way already described above. The VME CPU can compute the mean values and the variances which is used to determine the thresholds and pedestals to be stored back in the threshold/pedestal memory. The Memory Owner bit (MO) of the status register is used to switch the pedestal & threshold memory access between the VME bus (MO=0) and the channels Control Logic. At power on, the memorized pedestal and threshold values are not specified, therefore the pedestal and threshold memory must be initialized by the user.

## 2.2 TGC readout scheme

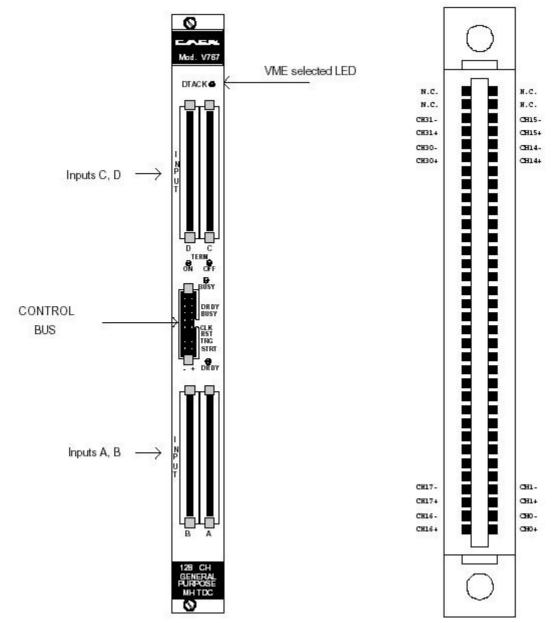

## 2.2.1 The 128 channels Multihit Time to Digital Conversion

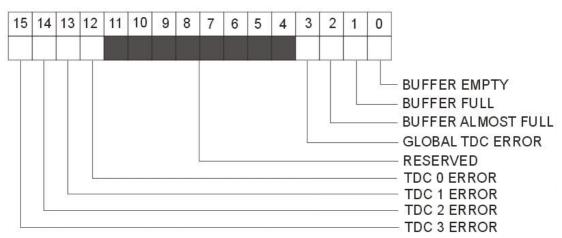

The 128 channels Multihit Time to Digital Conversin (TDC) is a one-unit wide VME module that houses 128 independent Time to Digital Conversion channels. The unit houses four such TDC chips [7].

The TDC is a General Purpose time-to-digital converter, with 32 channels per chip. The integrated circuit is developed as a full custom device in CMOS 0.7  $\mu$ m technology, allowing *Common Start* operations with a typical bin size of 0.8 ns. All channels can be enabled for the detection of rising and/or falling edges and for each channel there is a digital adjustment for the reset of any offsets and pedestals.

The data acquisition can be programmed in "EVENTS" (*Trigger Matching* with a programmable time window or *Start Gating* modes) or in "*Continuous Storage*" as well as the management of overlapping triggers. The *Common Stop* operation, though not existing in the chip itself, can be easily implemented on this board by assigning one of the 128 channels to a STOP signal and by an adequate programming of the trigger window.

The board houses a 32 kwords local memory FIFO buffer that can be read via the VME (as single data, Block Transfer and Chained Block Transfer) in parallel to the acquisition itself.

The programming is performed via a microcontroller that implements a high-level interface with the user in order to mask the board and the TDCs' hardware.

The unit accepts the following CONTROL signals (ECL differential) in common to all channels:

- START: a common START input;

- TRIGGER: a common TRIGGER input;

- RST: the RESET signal which allows to clear the buffers and reset the TDCs; upon programming, it can also reset other registers of the unit;

- CLOCK: providing an external Clock to the board.

The characteristics of the signals is shown in the Table 2.3.

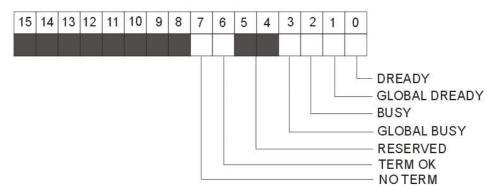

The status of unit is shown by the LEDs on the front panel:

- DTACK lights up each time the module generates the VME signal DTACK;

- DATA READY lights up when the Data Ready condition occurs;

- BUSY lights up when no more data can be written;

- TERM ON lights up when all the lines of the CONTROL bus are terminated;

- TERM OFF lights up when no CONTROL bus line is terminated.

Figure 2.7 The TDC front panel and Input connector pin assignment.

| Inputs                            |                           |                 |               |  |  |

|-----------------------------------|---------------------------|-----------------|---------------|--|--|

| Signal                            | Standard                  | Connector       | Minimum width |  |  |

| INPUT CHANNELS                    | ECL                       | Robinson Nugent | 10 ns         |  |  |

| CLOCK                             | ECL, (rising egde active) | Header 3M       | 25 ns         |  |  |

| RESET ECL, (active low)           |                           | Header 3M       | 25 ns         |  |  |

| TRIGGER ECL, (rising egde active) |                           | Header 3M       | 25 ns         |  |  |

| START ECL, (rising egde active)   |                           | Header 3M       | 10 ns         |  |  |

| Outputs                           |                           |                 |               |  |  |

| DRDY                              | ECL, active high          | Header 3M       |               |  |  |

| BUSY ECL, active high             |                           | Header 3M       |               |  |  |

|                                   |                           |                 |               |  |  |

### Table 2.3 The inputs and outputs of the TDC

The input connectors refers to following channels:

- Connector A refers to Channels 0 to 31.

- Connector B refers to Channels 32 to 63.

- Connector C refers to Channels 64 to 95.

- Connector D refers to Channels 96 to 127.

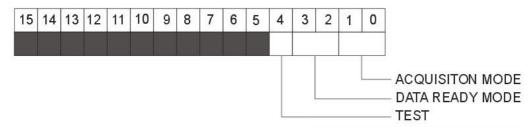

The TDC operation is based on the functionality of the CERN/ECP-MIC TDC chip. Five different module setups are selectable via software for different acquisition scenarios, namely:

- Stop Trigger Matching;

- Start Trigger Matching;

- Start Gating;

- Continuous Storage;

- Common Stop Emulation;

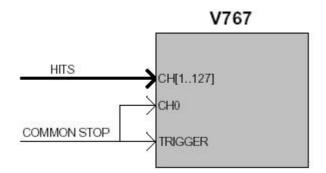

It is possible to switch from one operation mode to the other by simply resetting and reprogramming the module (with this operation the data in memory will be lost). Since the trigger is delayed and the input signals from the TGCs come before the trigger, common stop emulation is used. The TDC chips do not foresee the common stop operation. It is implemented with the scheme shown in Figure 2.8 :

Figure 2.8 Common Stop Emulation

The *Common Stop Emulation* is done by programming the board to a *Stop Trigger Matching*, with the trigger window ending and the occurrence of the trigger/stop signal (see Figure 2.9).

Figure 2.9 Common Stop Sequence.

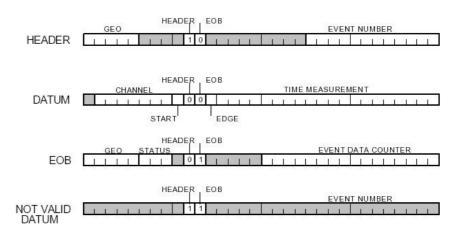

The stored data consist of: absolute time measurement (the zero time reference is represented by the RESET) ; the timing information of the STOP (T stop – T hit) which can be obtained by the software. The event is stored in the local buffer of the board with the following structure:

HEADER event number DATUM n.1 HIT time(4) DATUM n.2 HIT time(5) DATUM n.3 HIT time(6) DATUM n.4 HIT time(7) DATUM n.5 HIT time(8) DATUM n.6 STOP time EOB num. of data read = 6

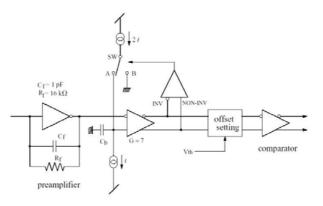

#### 2.2.2 The Amplifier Shaper Discriminator

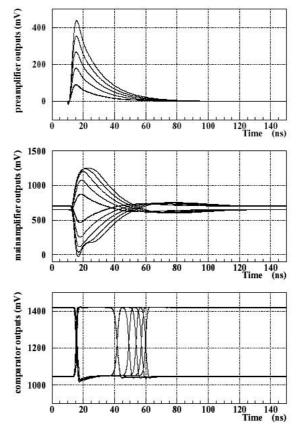

TGC signals from wire-groups and strips pass through an Amplifier Shaper Discriminator IC (ASD-IC) placed on ASD Boards which are housed inside the shielding boxes attached to each TGC unit. An ASD Board is shown in Figure 2.11. The ASD-IC uses SONY Analog Master Slice technology (bipolar). Each ASD-IC contains four channels. The scheme of the one single channel is shown in Figure 2...

The ADC measures the signal charge in a given time window following the initial threshold crossing. The signal charge is encoded into pulse width (this is demonstrated in Figure 2.).This charge information enable to increase the accuracy of the timing measurement by performing time slewing correction. Two modes of operation are provided. In one mode the ASD output gives the time over threshold information, i.e. signal leading and trailing edge timing. The other mode measures the leading edge time and charge and is considered as the default-operating mode [8].

Its outputs signals are conform to the Low Voltage Differential Signaling standard, LVDS, to assure drivability and immunity against noise and minimizing power.

The 16-ch ASD board (ASDB) was designed to receive wire and strip signals from the TGCs. Each board contains four ASD ICs with protection circuits and a test pulse circuit that receives a test pulse and distributes a charge impulse to each channel. The board design is common for all TGC chambers. LVDS logic signals from the ASDB are transmitted through a 20 twisted-pair cable and a preamplifier output through a LEMO type connector. DC power  $(\pm 3V)$ , ground, threshold voltage (common over a channel) and test pulse are supplied back to the ASDB via the same twisted-pair cable.

The circuit can successfully accept signals of 5 MHz or even higher frequencies.

Figure 2.110 The ASD board

Figure 2.11 Block diagram of the ASD chip.

Figure 2.12 The signal propagations of ASD chip.

The Figure 2. shows the shape of the signal as measured in three different place in the ASD chip. First plot show the signal shape in the preamplifier, main-amplifier output shape is shown in the second plot where the comparator output is drawen in the last figure.

#### 2.2.3 The ASD READOUT

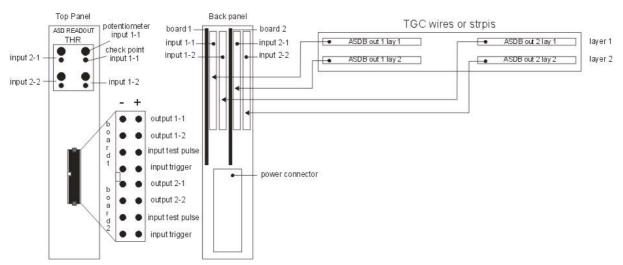

The signals from ASDB pass through an ASD READOUT (ASDR) NIM card. ASDR consists of two boards of two inputs each. Each board accepts signals from one TGC layer via 20 twisted-pair cable, however it can accept either wires signals or strips signals. Since the TDC accepts only the ECL standard signals, ASDR converts the LVDS input signals to the ECL format. Signals from one input are summed and that sum is the one single output of this board. The input-output connector, Header 3M type, 8+8 pins, is placed on the top panel. The structure of the pins is shown in Figure 2.. These output signals are transmitted through an 8-pair flat-pair cable to an ASD to TDC NIM card. The trigger and the test pulse are supplied back from the ASD to TDC via the same 8-pair flat-pair cable. The layout of ASDR is shown in Figure 2..

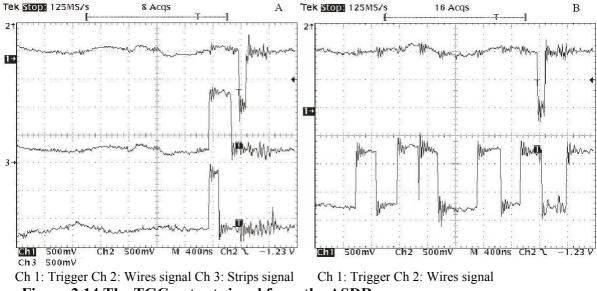

The ASDR provides the DC power, ground, test pulse and threshold voltage to the ASDB via the same 20-pair twisted-pair cable. User can set the threshold voltage on the front panel. Each input has its own potentiometer. It is possible to check the threshold value on the control points on the front panel. In our case the threshold of wires is set to -50 mV, whereas the strip threshold is set to 60mv (see Figure 2. A). The output signal is depend of the thresholds value, in the case of wrong values the signal would have noise and the offline code will not able to calculate the maps of efficiency and the timing correctly. It is illustrated in Figure 2. B.

Figure 2.13 The ASDR top and back panel and the input connector pin assignment.

Figure 2.14 The TGC output signal from the ASDR

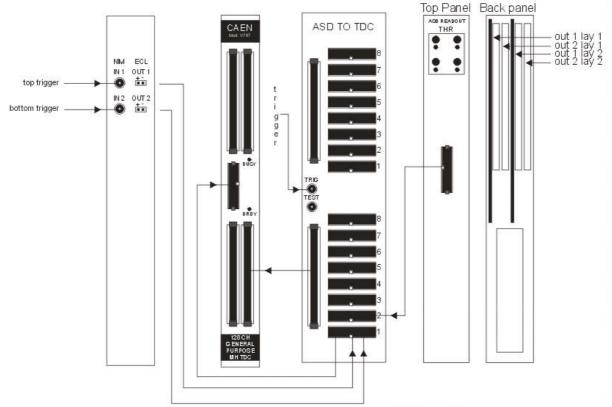

### 2.2.4 The ASD TO TDC.

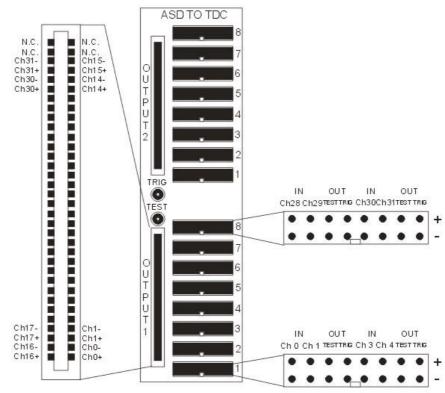

The ASDR output are transmitted to the ASD TO TDC (ASDTDC) NIM card through an eight pair flat-pair cable. The trigger and the test pulse are provided to the ASDR via the same flat cable. The bottom eight ASDTDC inputs refer to the first output and top eight ASDTDC inputs refer to the second output (see Figure 2.15).

Since the TDC input connectors are Robinson Nugent type (see Figure 2.7) thus ASDTDC changes only the type of connectors, from input connectors, Header 3M type, 8 + 8 pins, to the connector fitted the TDC. The input signals are transmitted to the output without any changes.

Figure 2.15 The ASDTDC top panel and input connectors pin assignment.

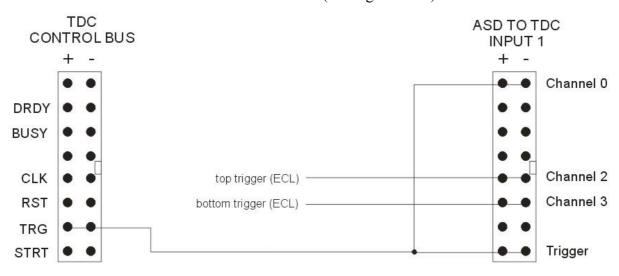

The ASDTDC card provides also the trigger to the TDC. The TDC trigger input is sent via the control bus of the TDC front panel (see Figure 2.7). That trigger has to be a standard ECL signal. The standard NIM trigger is connected to the LEMO connector on the ASDTDC front panel. The ASDTDC changes this trigger signal from NIM standard to the ECL standard. The ECL trigger is accessible from the trigger output in each input of the ASDTDC front panel. That trigger is connected to the TDC trigger input throught a special cable. Since the TDC is working in the *Common Stop Emulation* mode, the trigger is to be provided to channel zero of the selected TDC chip. It is done by the trigger connection from the first ASDTDC input to channel zero of the same fisrst input. The top and the bottom trigger signals are connected to the second and the third channel in the ASD TDC first input. This configuration provides the top and bottom triggers to the TDC, allowing the offline program to calculate the muon hit time in the scintillators (see Figure 2.16).

Figure 2.16 The ASD TO TDC connections system layout.

#### 2.2.5 The NIM to ECL translator.

The top trigger and the bottom trigger are connected to a NIM to ECL card. These output signals are connected to the second and the third channels of ASDTDC input one (see Figure 2.).

#### 2.3 Trigger system.

A charged particle (muon) which crosses the scintillator produces photon in the scintilating material. These photons are collected and amplified by Photomultiplier Tubes, which are attached at the ends of each scintillator. In this way a single analog signal is generated. All analog signals go to discriminators, where they are converted to a digital signal.

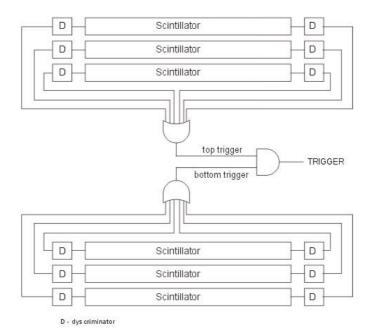

In our case eight scintillators are used, four at the bottom and four at the top of the cosmic ray telescope (see Figure 2.).

Figure 2.17 Schematic diagram of the trigger logical connection.

All signals from one couple of scintillators go to an OR logical gate. This signal represent the hit of that layer. The common trigger is made by an AND logical gate which takes a coincidence between the top and bottom layer signals.

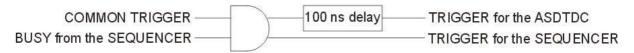

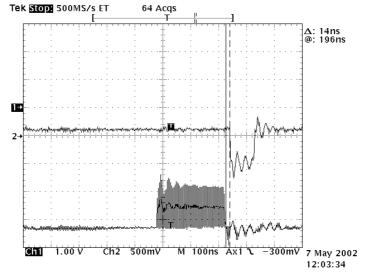

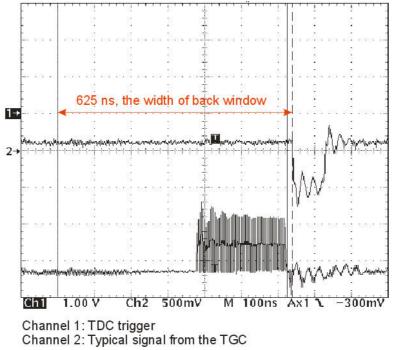

To prevent a trigger signal when the system is not ready an AND coincidence between the BUSY and COMMON TRIGGER is made. It means that triggers are not allowed when the system is reading data from chambers. Since the TDC is working in a *Common Stop Emulation* mode the trigger has to be delayed. Otherwise the signals from the TGC will not be in within the proper time window. We choose a delay 100 ns. The scheme of the trigger design is presented in Figure 2..

Figure 2.18 Scheme of the trigger design.

Figure 2.19 The TDC trigger (channel 1), signal from the TGC (channel 2) oscilogram.

The link between the TDC trigger and the signals from the TGC is shown in Figure 2.19. Without the 100ns delay the TDC trigger will be in the middle of the TGC signal and the TDC will report a TDC Chip Error (see § 3.3.1).

Figure 2.20 The leyout of the readout system.

To achieve synchronization between the C-RAMS and the SEQUENCER, the communication between these cards is done in the following way:

The TRIGGER is connected to the trigger input of SEQUENCER. With the occurrence of a TRIGGER signal the SEQUENCER starts generating the CLOCK, CONVERT, HOLD and BUSY signals.

To start taking data, a CONVERT signal is provided to the C-RAMS. The convert input of the C-RAMS is joined with the convert output of the SEQUENCER. The CLOCK and the CONVERT are synchronized at formation. After the train of CONVERT pulses the DRDY changes to high state indicating the presence of data in the output buffer. When the C-RAMS is in DRDY mode the generation of another CONVERT train pulses is prevented. To meet this condition, the DRDY is connected to the drdy input of the SEQUENCER. The BUSY of the SEQUENCER does not go low when the DRDY is high and the SEQUENCER does not accept any more triggers. The data, in the output buffer of C-RAMS, has to be read by a VME, otherwise the system will stop.

The output signals from the GassiPlexes cards are connected to the input channel of the C-RAMS. The C-RAMS has two input signals per one ADC channel, since the C-RAMS accepts a differential input signal. Since we use a positive signal, only one input channel is used. The second input has is terminated by a 50 $\Omega$  resistor. The C-RAMS sequence system layout is shown in Figure 2..

Figure 2.21 The C-RAMS-SEQUENCER connections layout.

To provide the signals from the TGCs chambers to the TDC the connections between the TGC, ASDR, ASTTDC and TDC is done in the following way:

The signals from the TGC are connected to the ASDR. The output signals go to the ASDTDC, the first input of ASDTDC is used to provide the triger, top and bottom trigger to the TDC. This input is connected to the TDC control bus. The trigger is connected to the LEMO input of this card as well. The output signals from ASDTDC go to the TDC. The layout of the connections is shown in Figure 2..

Figure 2.22 The ASDR-ASDTDC-TDC connections layout.

The layout of the electronics general scheme is shown in Figure 2...

## **3 VME Interface and functionality**

## 3.1 SEQUENCER

The C-RAMS has CR/CRS space of 254 bytes length. This space consists of the registers. User can read and write the data from them, the map of the registers is shown in Table 3.1 [5]. The Base Address can be changed by four internal rotary switches houses on two piggyback boards plugged into the main printed circuit.

The Base Address can be selected within the range:

| 0x00 0000 ÷ 0xFF 0000     | A24 mode |

|---------------------------|----------|

| 0x0000 0000 ÷ 0xFFFF 0000 | A32 mode |

| Address         | Register/Content           | Туре       |

|-----------------|----------------------------|------------|

| Base $+ 0xFE$   | Version & Series           | read only  |

| Base $+ 0 x FC$ | Manufacturer & module type | read only  |

| Base $+ 0xFA$   | Fixed code                 | read only  |

| Base $+ 0x18$   | Internal DAC               | write only |

| Base $+ 0x16$   | T5 Register                | read/write |

| Base $+ 0x14$   | T4 Register                | read/write |

| Base $+ 0x12$   | T3 Register                | read/write |

| Base $+ 0x10$   | T2 Register                | read/write |

| Base $+ 0x0E$   | T1 Register                | read/write |

| Base $+ 0x0C$   | Number of channels         | read/write |

| Base $+ 0x0A$   | Test Register              | read/write |

| Base $+ 0x08$   | Status Register            | read/write |

| Base $+ 0x06$   | Software Trigger           | read/write |

| Base $+ 0x04$   | Software Clear             | read/write |

| Base $+ 0x02$   | Interrupt Level            | write only |

| Base $+ 0x00$   | Interrupt Vector           | write only |

Table 3.1 SEQUENCER Address Map

## 3.1.1 The SEQUENCER registers

The following paragraphs are the registers description which are used by the online code.

#### 1. Clear Register

(Base address + 0x04, read/write)

A VME access to this location causes the following:

- 1. a pulse (500 ns) is generated on the CLEAR output;

- 2. a pulse (500 ns) is generated on the DRESET line of the CONTROL BUS;

- 3. a pulse (500 ns) is generated on the ARESET line of the CONTROL BUS;

- 4. if the conversion sequence is in progress, it is aborted and the BUSY output becomes not active

#### 2. Status Register

(Base address + 0x08, read/write)

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5  | 4 | 3  | 2  | 1 | 0  |

|----|----|----|----|----|----|---|---|---|---|----|---|----|----|---|----|

|    |    |    |    |    |    |   |   |   |   | AS | В | DY | AT | V | ID |

#### Figure 3.1 SEQUENCER Status Register

Figure 3.1 represents the bits structure of the Status register of the SEQUENCER Where:

ID – Internal Delay

- = 0 no Internal Delay;

- = 1 Internal Delay selected.

V – Veto

- = 0 no Veto state;

- = 1 Veto state.

AT – Auto Trigger

= 0 Normal mode;

- = 1 Auto Trigger mode.

- DY Data Ready (read only)

- = 0 no Data Ready;

- = 1 Data Ready.

- B Busy (read only)

- = 0 not Busy;

= 1 Busy.

AS – Active Sequence

- = 0 no Active Sequence;

- = 1 Active Sequence.

### 3. Number of channels register

### Figure 3.2 SEQUENCER Number of Channels Register

The structure of the Number of Channels Register is shown in Figure 3.2. The number of detector channels (0 - 2047) to be read out by the C-RAMS is programmed via this register (though the V550 C-RAMS is limited to 2016 detector channels)

### 4. T1 Register

(Base address + 0x0E, read/write)

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7  | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|---|---|----|---|---|---|---|---|---|---|

|    |    |    |    |    |    |   |   | T1 |   |   |   |   |   |   |   |

### Figure 3.3 SEQUENCER T1 Register

The T1 register is used to set the 8 bits T1 parameters (see Figure 3.3). It sets the delay between the Leading Edge of the TRIGGER and the HOLD assertion. The actual delay t1 (in nanosecond) is calculated as follows:

t1 = 500 + T1 \* 10 ns, where  $0 \le T1 \le 255$ .

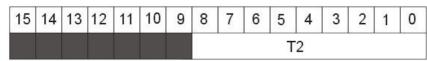

### 5. T2 Register

(Base address + 0x10, read/write)

### Figure 3.4 SEQUENCER T2 Register

In the T2 register one sets 9 bits T2 parameters (see Figure 3.4). It provides the t2 delay between the HOLD assertion and the start of the CLOC/CONVERT sequence. The actual delay t2 (in nanosecond) is calculated as follows:

t2 = 130 + T1 \* 20 ns, where  $10 \le T1 \le 511$ .

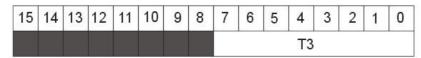

### 6. T3 Register

(Base address + 0x12, read/write)

### Figure 3.5 SEQUENCER T3 Register

The T3 register sets the 8 bits T3 parameters it is shown in Figure 3.5. It adjust the duration t3 of the active phase of the CLOCK and the CONVERT. The actual duration t3 (in nanosecond) is calculated as follows:

t3 = T3 \* 20 ns, where  $1 \le T3 \le T4 \le 255$ . This constraint (T3  $\le$  T4) follows automatically from the fact that the active phase of the CLOCK and CONVERT must be less their own period.

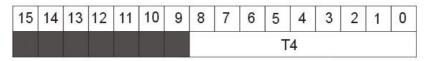

### 7. T4 Register

(Base address + 0x14, read/write)

### Figure 3.6 SEQUENCER T4 Register

The T4 register allows to set the 9 bits T4 parameters (see Figure 3.6). It defines the period t4 of both the CLOCK and the CONVERT sequence. The actual duration t4 (in nanosecond) is calculated as follows:

t4 = 20 + T4 \* 20 ns, where  $1 \le T4 \le 511$ .

### 8. T5 Register

(Base address + 0x16, read/write)

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|    |    |    |    |    |    |   |   |   |   | Т | 5 |   |   |   |   |

#### Figure 3.7 SEQUENCER T5 Register

The T5 register defines the 9 bits T5 parameters (see Figure 3.7). In Normal Mode (see Figure 3.1), it provides the delay t5 between the CLOCK and the relevant CONVERT. The actual delay t5 (in nanosecond) is calculated as follows: t5 = 40 + T5 \* 20 ns, where  $2 \le T5 \le 511$ .

# 3.2 C-RAMS

The CR/SCR space of this card has 24572 bytes length. The 4 international rotary switches houses on two pigyback boards plugged into the main printed circuit board fix the module's Base Address. The module can work in the A24 and A32 mode [6]. The Base Address can be selected in the range:

| A24 mode |

|----------|

| A32 mode |

|          |

The map of the registers is shown in Table 3.2.

| Pedestal/Threshold memory channel 1 | read/write                                                                                                                                                                                                                                                                                                     |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                     | read/write                                                                                                                                                                                                                                                                                                     |

|                                     | read/write                                                                                                                                                                                                                                                                                                     |

|                                     |                                                                                                                                                                                                                                                                                                                |

|                                     |                                                                                                                                                                                                                                                                                                                |

| Pedestal/Threshold memory channel 1 |                                                                                                                                                                                                                                                                                                                |

| Pedestal/Threshold memory channel 0 |                                                                                                                                                                                                                                                                                                                |

|                                     |                                                                                                                                                                                                                                                                                                                |

|                                     | read/write                                                                                                                                                                                                                                                                                                     |

|                                     |                                                                                                                                                                                                                                                                                                                |

| Pedestal/Threshold memory channel 0 |                                                                                                                                                                                                                                                                                                                |

| Version & Series                    | read only                                                                                                                                                                                                                                                                                                      |

| Manufactured & module type          | read only                                                                                                                                                                                                                                                                                                      |

| Fixed code                          | read only                                                                                                                                                                                                                                                                                                      |

| Test pattern channel 1              | write only                                                                                                                                                                                                                                                                                                     |

| Test pattern channel 0              | write only                                                                                                                                                                                                                                                                                                     |

| Word counter channel 1              | read only                                                                                                                                                                                                                                                                                                      |

| Word counter channel 0              | read only                                                                                                                                                                                                                                                                                                      |

| FIFO channel 1                      | read only                                                                                                                                                                                                                                                                                                      |

| FIFO channel 0                      | read only                                                                                                                                                                                                                                                                                                      |

| Module clear                        | write only                                                                                                                                                                                                                                                                                                     |

| Number of channels                  | read/write                                                                                                                                                                                                                                                                                                     |

| Status Register                     | read/write                                                                                                                                                                                                                                                                                                     |

| Interrupt Register                  | write only                                                                                                                                                                                                                                                                                                     |

|                                     | Pedestal/Threshold memory channel 0<br>Version & Series<br>Manufactured & module type<br>Fixed code<br>Fest pattern channel 1<br>Fest pattern channel 0<br>Word counter channel 0<br>Word counter channel 1<br>Word counter channel 0<br>FIFO channel 1<br>FIFO channel 1<br>FIFO channel 1<br>Status Register |

Table 3.2 C-Rams Address Map

### 3.2.1 C-RAMS registers

### 1. Word Counter Register

(Base address + 0x12, read only channel 1)

(Base address + 0x10, read only channel 0)

The Word counter registers have the following structure:

| 15 | 14 | 13 | 12 | 11 | 10 | 9    | 8     | 7     | 6     | 5      | 4      | 3      | 2    | 1     | 0   |

|----|----|----|----|----|----|------|-------|-------|-------|--------|--------|--------|------|-------|-----|

| ĺ  |    |    |    |    | Ni | umbe | erofo | overt | hresh | iold d | ata (N | lo. of | Data | in Fl | FO) |

Figure 3.8 C-RAMS Word Counter Register

### 2. FIFO Channel 0 and 1

(Base address + 0x0C, read only channel 1) (Base address + 0x08, read only channel 0)

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17   | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7  | 6   | 5    | 4   | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|------|----|----|----|----|----|----|----|---|---|----|-----|------|-----|---|---|---|---|

| 0  | V  |    |    |    |    |    |    |    |    |    | C  | ha | nn | el r | um | be | r  |    |    |    |    |   | С | ha | nne | el d | ata |   |   |   |   |

### Figure 3.9 C-RAMS FIFO structure

We can see the bits structure of the C-RAMS FIFO in Figure 3.. Where:

V – Validity bit :

- = 0 converted value is under pedestal;

- = 1 converted value is over pedestal.

- O Overange bit:

- = 0 no FADC overange;

- = 1 FADC overange.

### 3. Clear Module

(Base address + 0x06, write only)

A VME access to this location causes the following

- 1. Aborts the conversion process (if active);

- 2. clears the FIFOs;

- 3. clears the word counters.

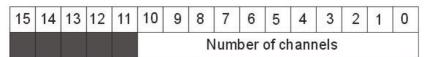

### 4. Number of channels

(Base address + 0x04, read/write)

This register allows programming the number of detector channels to be read out in 32 steps. This number ranges from 32 (DCN=1) to 2016 (DCN=63), DCN=0 means 1 detector channel only. Its structure is shown in Figure 3.11.

| 15 | 14 | 13 | 12 | 11            | 10 | 9 | 8 | 7 | 6 | 5   | 4    | 3   | 2    | 1 | 0 |

|----|----|----|----|---------------|----|---|---|---|---|-----|------|-----|------|---|---|

|    |    |    |    | DCN Channel 1 |    |   |   |   |   | DCN | l Ch | ann | el 0 |   |   |

Figure 3.110 C-RAMS Number of channels

### 5. Status Register

(Base address + %02, read/write)

The Status register contains information about the status and allows a few settings on the module.

| 15 | 14 | 13 | 12 | 11 | 10 | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1  | 0 |

|----|----|----|----|----|----|-----|-----|-----|-----|-----|-----|-----|-----|----|---|

|    |    |    |    |    |    | /F1 | /F0 | /H1 | /H0 | /E1 | /E0 | /D1 | /D0 | МО | Т |

Figure 3.131 C-RAMS Status Register

Figure 3.13 represents the bits structure, where:

```

T - Test mode.

```

- = 0 no Test mode;

- = 1 Test mode;

MO - Pedestal Threshold memory owner.

= 0 memory owned by VME;

= 1 memory owned by the Conversion logic;

/D0 - Channel 0 Data Ready bit, read only. = 0 data ready;

/D1 - Channel 1 Data Ready bit, read only. = 0 data ready;

- /E0 FIFO channel 0 empty bit, read only. = 0 empty;

- /E1 FIFO channel 1 empty bit, read only. = 0 empty;

- /H0 FIFO CHANNEL 0 half full bit, read only. = 0 half full;

- /H1 FIFO CHANNEL 1 half full bit, read only. = 0 half full;

- /F0 FIFO CHANNEL 0 full bit, read only. = 0 full;

- /F1 FIFO CHANNEL 1 full bit, read only. = 0 full;

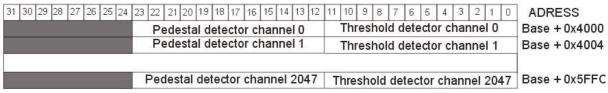

### 6. Pedestal and Threshold memories

(Base address + 0x2000...5FFE, read/write )

The pedestal and threshold memories are accessible via VME only if Memory owner bit is set to 0 (default mode).

They have the following structure which is shown in Figure 3.15:

|                           |                     | CHANNEL 0        |         |        |      |       |     |       |     |    |               |

|---------------------------|---------------------|------------------|---------|--------|------|-------|-----|-------|-----|----|---------------|

| 31 30 29 28 27 26 25 24 2 | 23 22 21 20 19 18 1 | 7 16 15 14 13 12 | 11 10 9 | 8 7    | 6    | 5     | 4 3 | 2     | 1   | 0  | ADRESS        |