## QuickStep:

## A System for Performance Monitoring and Debugging Parallel Applications on the Alewife Multiprocessor

by

Sramana Mitra

A.B., Computer Science and Economics Smith College, 1993

Submitted to the DEPARTMENT OF ELECTRICAL ENGINEERING AND COMPUTER SCIENCE in partial fulfillment of the requirements

for the degree of

### MASTER OF SCIENCE

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

February 1995

(c) 1995, Massachusetts Institute of Technology All rights reserved

| Signature of Author | :                 | /                                                         |

|---------------------|-------------------|-----------------------------------------------------------|

| -                   |                   | Department of Electrical Engineering and Computer Science |

|                     | ΛΛ                | 1 November 28, 1994                                       |

| Certified by:       |                   |                                                           |

|                     |                   | Anant Agarwal                                             |

|                     | ~                 | Associate Professor of Computer Science and Engineering   |

|                     | $\langle \rangle$ | Thesis Supervisor                                         |

| Accepted by:        |                   | Fradaria D. Margarthalan                                  |

|                     | (                 | Chairman, EECS Committee on Graduate Students             |

|                     |                   | Eng.                                                      |

|                     |                   | MASSACHUSETTS INSTITUTE<br>OF TECHNOLOGY                  |

|                     |                   | APR 13 1995                                               |

LIBRARIES

### QuickStep:

### A System for Performance Monitoring and Debugging Parallel Applications on the Alewife Multiprocessor

by

### Sramana Mitra

Submitted to the Department of Electrical Engineering and Computer Science on November 30, 1994 in partial fulfillment of the requirements for the Degree of Master of Science in Electrical Engineering and Computer Science

#### ABSTRACT

In Alewife, a large-scale multiprocessor with distributed shared memory, many sophisticated features have been incorporated to enhance performance. However for most parallel programs, the initial implementation usually produces sub-optimal performance. Alewife hardware offers features to monitor events that provide important information about program behavior. **QuickStep** is a tool that offers a software interface for monitoring such events and a graphical interface for viewing the results. The actual monitoring of the data takes place in hardware. This thesis will describe QuickStep's features and implementation details, evaluate the overhead due to the inclusion of the performance monitoring probes and look at case studies of parallel application optimization using QuickStep.

Thesis Supervisor: Anant Agarwal Title: Associate Professor of Computer Science and Engineering

## Acknowledgments

MIT would have been a very rough, unidimensional experience had it not been for ballroom dancing. I acknowledge first, therefore, dancing. I have named my system **QuickStep** after a dance that is fast and fun!

Of course, none of my work would have gained form if not for the constant guidance and influx of ideas from John Kubiatowicz. My deepest appreciation to Kubi, although I think I have successfully resisted his very convincing attempts to have me stay for a Phd. Thanks Kubi — indeed, it is flattering!

Thanks to my advisor — Professor Anant Agarwal — for giving me the high level direction. Thanks also for being extremely receptive and supportive of my long-term career goals and ambitions.

Ken and Don — my officemates have kept me in constant good humor. I could not have asked for better officemates. Thank you for making MIT warm for me.

I appreciate Ricardo Bianchini's help with the application chapter, as well as with the thesis in general.

Thanks to David Kranz, David Chaiken, Beng Hong Lim, Kirk Johnson and Rajeev Barua for the useful feedback and Silvina Hannono for the support.

Nate — my house-mate — has been a source of enormous comfort and friendship and Ellen has been there for me from day one (actually day negative something). My sincere appreciation to both.

Finally, thanks to all my friends from dancing and elsewhere for keeping me going.

To my parents: See you soon!

## Contents

| 1 | Intr                                                      | oduction                                                                                                                                                                                                                                                                                    | 9                                                  |  |  |  |  |  |

|---|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|--|--|--|--|

|   | 1.1                                                       | Performance Monitoring and Debugging Methods: Background                                                                                                                                                                                                                                    | 11                                                 |  |  |  |  |  |

|   |                                                           | 1.1.1 Static Analysis                                                                                                                                                                                                                                                                       | 11                                                 |  |  |  |  |  |

|   |                                                           | 1.1.2 Simulation                                                                                                                                                                                                                                                                            | 11                                                 |  |  |  |  |  |

|   |                                                           | 1.1.3 Emulation                                                                                                                                                                                                                                                                             | 11                                                 |  |  |  |  |  |

|   |                                                           | 1.1.4 Software Instrumentation                                                                                                                                                                                                                                                              | 12                                                 |  |  |  |  |  |

|   |                                                           | 1.1.5 Hardware Instrumentation                                                                                                                                                                                                                                                              | 13                                                 |  |  |  |  |  |

|   | 1.2                                                       | Goals of the Thesis                                                                                                                                                                                                                                                                         | 15                                                 |  |  |  |  |  |

|   | 1.3                                                       | Overview                                                                                                                                                                                                                                                                                    | 15                                                 |  |  |  |  |  |

| 2 | Feat                                                      | tures of QuickStep                                                                                                                                                                                                                                                                          | 16                                                 |  |  |  |  |  |

|   | 2.1                                                       | Timesliced Statistics                                                                                                                                                                                                                                                                       | 16                                                 |  |  |  |  |  |

|   | 2.2                                                       | Overall Statistics                                                                                                                                                                                                                                                                          | 18                                                 |  |  |  |  |  |

|   | 2.3                                                       | Network Usage Statistics                                                                                                                                                                                                                                                                    | 19                                                 |  |  |  |  |  |

|   | 2.4                                                       | Checkpoints                                                                                                                                                                                                                                                                                 | 20                                                 |  |  |  |  |  |

|   | 2.5                                                       | Additional Features                                                                                                                                                                                                                                                                         | 26                                                 |  |  |  |  |  |

| 3 | Imp                                                       | lementation                                                                                                                                                                                                                                                                                 | 27                                                 |  |  |  |  |  |

| C | 3.1                                                       | User Interface                                                                                                                                                                                                                                                                              | 27                                                 |  |  |  |  |  |

|   | J.1                                                       | Resource Allocation                                                                                                                                                                                                                                                                         |                                                    |  |  |  |  |  |

|   | 3.2                                                       | Resource Allocation                                                                                                                                                                                                                                                                         | 29                                                 |  |  |  |  |  |

|   |                                                           | Resource Allocation                                                                                                                                                                                                                                                                         | 29<br>29                                           |  |  |  |  |  |

|   |                                                           |                                                                                                                                                                                                                                                                                             |                                                    |  |  |  |  |  |

|   |                                                           | <ul> <li>3.2.1 Alewife's Performance Monitoring Architecture</li></ul>                                                                                                                                                                                                                      | 29                                                 |  |  |  |  |  |

|   |                                                           | <ul> <li>3.2.1 Alewife's Performance Monitoring Architecture</li></ul>                                                                                                                                                                                                                      | 29<br>30                                           |  |  |  |  |  |

|   |                                                           | <ul> <li>3.2.1 Alewife's Performance Monitoring Architecture</li></ul>                                                                                                                                                                                                                      | 29<br>30<br>31                                     |  |  |  |  |  |

|   | 3.2                                                       | <ul> <li>3.2.1 Alewife's Performance Monitoring Architecture</li> <li>3.2.2 Hardware Mask Configuration</li> <li>3.2.3 The Resource Allocator</li> <li>3.2.4 The Configuration File</li> <li>The Machine Side</li> </ul>                                                                    | 29<br>30<br>31<br>33                               |  |  |  |  |  |

|   | 3.2                                                       | <ul> <li>3.2.1 Alewife's Performance Monitoring Architecture</li> <li>3.2.2 Hardware Mask Configuration</li> <li>3.2.3 The Resource Allocator</li> <li>3.2.4 The Configuration File</li> <li>The Machine Side</li> <li>3.3.1 Data Collection and Reporting</li> </ul>                       | 29<br>30<br>31<br>33<br>36                         |  |  |  |  |  |

|   | 3.2                                                       | 3.2.1Alewife's Performance Monitoring Architecture3.2.2Hardware Mask Configuration3.2.3The Resource Allocator3.2.4The Configuration FileThe Machine Side                                                                                                                                    | 29<br>30<br>31<br>33<br>36<br>36                   |  |  |  |  |  |

|   | 3.2<br>3.3                                                | 3.2.1Alewife's Performance Monitoring Architecture3.2.2Hardware Mask Configuration3.2.3The Resource Allocator3.2.4The Configuration FileThe Machine Side                                                                                                                                    | 29<br>30<br>31<br>33<br>36<br>36<br>38             |  |  |  |  |  |

| 4 | <ul><li>3.2</li><li>3.3</li><li>3.4</li><li>3.5</li></ul> | 3.2.1Alewife's Performance Monitoring Architecture3.2.2Hardware Mask Configuration3.2.3The Resource Allocator3.2.4The Configuration FileThe Machine Side                                                                                                                                    | 29<br>30<br>31<br>33<br>36<br>36<br>38<br>40       |  |  |  |  |  |

| 4 | <ul><li>3.2</li><li>3.3</li><li>3.4</li><li>3.5</li></ul> | 3.2.1Alewife's Performance Monitoring Architecture3.2.2Hardware Mask Configuration3.2.3The Resource Allocator3.2.4The Configuration File3.2.4The Configuration FileThe Machine Side3.3.1Data Collection and Reporting3.3.2Instrumentation Overhead due to TimeSlicingPost-ProcessingSummary | 29<br>30<br>31<br>33<br>36<br>36<br>38<br>40<br>41 |  |  |  |  |  |

.

|   |      | 4.2.1 Example 1: Cached Reads                             | 42 |

|---|------|-----------------------------------------------------------|----|

|   |      | 4.2.2 Example 2: Remote Accesses                          | 43 |

|   |      | 4.2.3 Example 3: Timesliced Statistics                    | 43 |

|   | 4.3  | Summary                                                   | 47 |

| 5 | Case | e Studies Using QuickStep                                 | 49 |

|   | 5.1  | Case Study 1: MP3D                                        | 49 |

|   |      | 5.1.1 Description                                         | 49 |

|   |      | 5.1.2 Analysis Using QuickStep                            | 50 |

|   |      | 5.1.3 Summary                                             | 57 |

|   | 5.2  | Case Study 2: SOR                                         | 57 |

|   |      | 5.2.1 Description                                         | 57 |

|   |      | 5.2.2 Analysis Using QuickStep                            | 57 |

|   |      | 5.2.3 Summary                                             | 59 |

| 6 | Con  | clusions                                                  | 60 |

|   | 6.1  | Summary                                                   | 60 |

|   | 6.2  | Future Work                                               | 61 |

| A | Cod  | e Listings                                                | 63 |

|   | A.1  | Proc1: A Procedure Annotated with Checkpoints             | 63 |

|   | A.2  | Bench1.c: A Program for Validating Hit Ratios             | 64 |

|   | A.3  | Bench5.c: A Program for Validating Remote Access Patterns | 65 |

|   | A.4  | Bench11.c: A Program for Validating the Timesliced Mode   | 67 |

| B | Tabl | les for Graphs                                            | 69 |

. .

## **List of Tables**

| 2.1          | Data obtained from the raw data file for the classwise and single checkpoint graphs.           | 24 |

|--------------|------------------------------------------------------------------------------------------------|----|

| 2.2          | Data obtained from the raw data file for the checkpoint histogram                              | 25 |

| 4.1          | Results of running bench1.c on a 16-node Alewife machine                                       | 44 |

| 5.1          | Average data cache hit ratios for running the 3 versions of Mp3d on a 16-node Alewife machine. | 50 |

| 5.2          | Data distribution for running the 3 versions of Mp3d on a 16-node Alewife machine.             | 55 |

| 5.3          | Execution times for the three versions of SOR on a 16-node Alewife machine.                    | 59 |

| <b>B</b> .1  | Water on 16 processors: Per processor distribution of remote shared data accesses.             | 69 |

| <b>B</b> .2  | Water on 16 processors: Counts of packet headers passing through output queues.                | 70 |

| B.3          | Water on 16 processors: Histogram of distances of memory-to-cache input packets.               | 70 |

| <b>B.4</b>   | Orig Mp3d: Per processor distribution of remote distances travelled by read                    |    |

|              | invalidation packets                                                                           | 71 |

| B.5          | Mp3d: Per processor distribution of remote distances travelled by read invalidation            |    |

|              | packets                                                                                        | 71 |

| B.6          | MMp3d: Per processor distribution of remote distances travelled by read invali-                |    |

|              | dation packets.                                                                                | 72 |

| <b>B</b> .7  | Orig Mp3d: Average remote access latencies                                                     | 72 |

| <b>B.8</b>   | Mp3d: Average remote access latencies.                                                         | 73 |

| B.9          | MMp3d: Average remote access latencies.                                                        | 73 |

| <b>B</b> .10 | Orig Mp3d: Packet headers passing through output queue                                         | 74 |

| B.11         | Mp3d: Packet headers passing through output queue                                              | 74 |

| B.12         | MMp3d: Packet headers passing through output queue                                             | 75 |

| B.13         | ZGRID: Data cache hit ratios.                                                                  | 75 |

| B.14         | MGRID: Data cache hit ratios                                                                   | 76 |

| B.15         | CGRID: Data cache hit ratios.                                                                  | 76 |

# **List of Figures**

| 1.1 | An Alewife processor node.                                                                              | 10 |

|-----|---------------------------------------------------------------------------------------------------------|----|

| 1.2 | Flow chart of tuning the performance of an application using QuickStep                                  | 14 |

| 2.1 | The Alewife user interface with pull-down menus for selecting the different statistics to be monitored. | 17 |

| 2.2 | Water on 16 processors: Per processor data cache hit ratio.                                             | 18 |

| 2.3 | Water on 16 processors: Per processor distribution of remote shared data accesses [Table B.1].          | 19 |

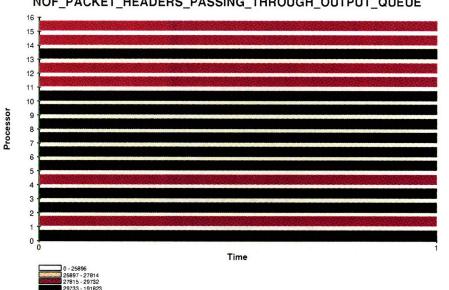

| 2.4 | Water on 16 processors: Counts of packet headers passing through output queues [Table B.2].             | 20 |

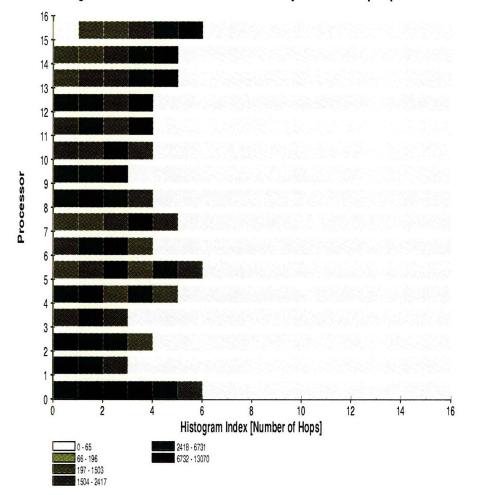

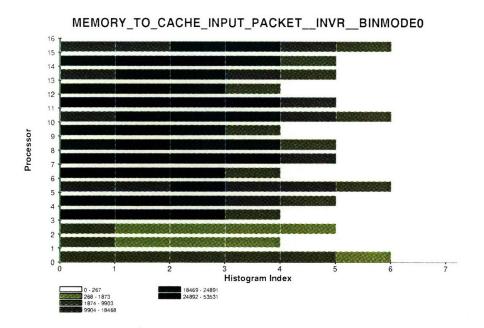

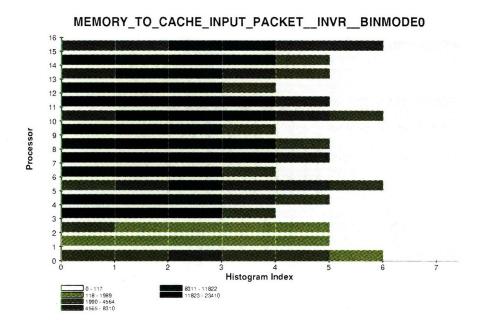

| 2.5 | Water on 16 processors: Histogram of distances of memory-to-cache input packets [Table B.3].            | 21 |

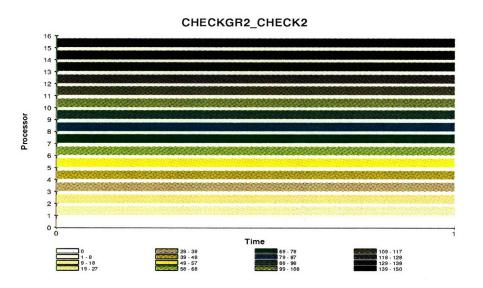

| 2.6 | Result of monitoring Checkgr2:Check2.                                                                   | 23 |

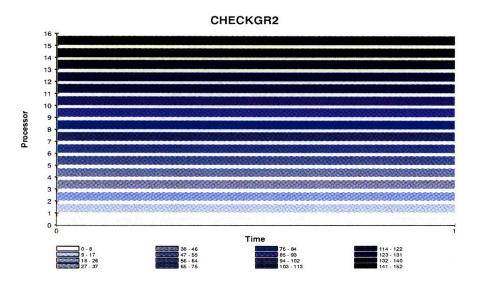

| 2.7 | Result of monitoring Checkgr2.                                                                          | 23 |

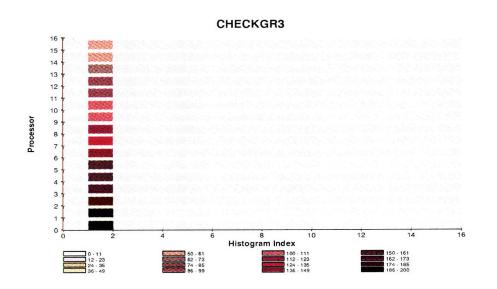

| 2.8 | Result of monitoring Checkgr3.                                                                          | 24 |

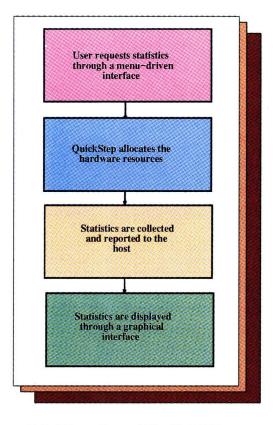

| 3.1 | Flow chart of the QuickStep system.                                                                     | 28 |

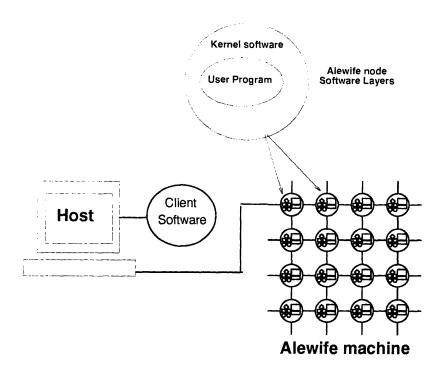

| 3.2 | Software layers in Alewife.                                                                             | 30 |

| 3.3 | Statistics counter mask fields.                                                                         | 32 |

| 3.4 | The configuration language.                                                                             | 34 |

| 3.5 | The operation keywords.                                                                                 | 35 |

| 3.6 | A sample configuration file.                                                                            | 37 |

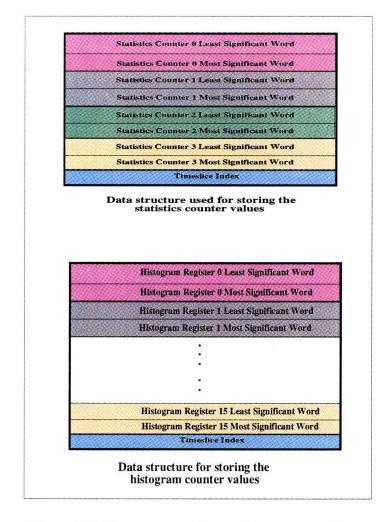

| 3.7 | Data structure for storing counter values.                                                              | 39 |

| 3.8 | Instrumentation overhead due to timeslicing: Monitoring timesliced data                                 | 40 |

| 2.0 | and instruction cache hit ratios for 3 applications.                                                    |    |

| 3.9 | Excerpt from a sample data file.                                                                        | 41 |

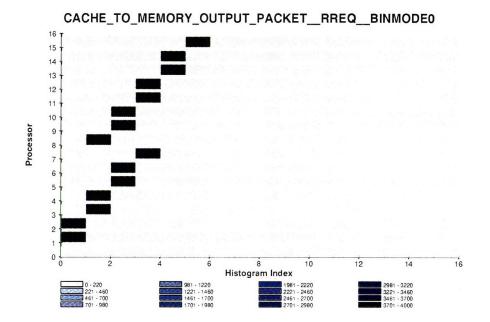

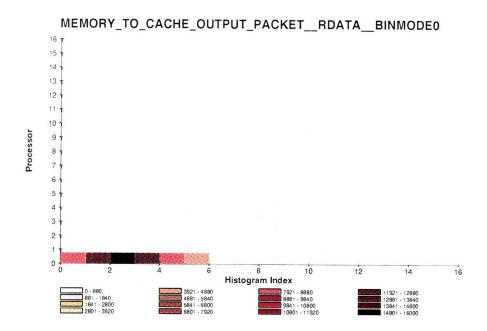

| 4.1 | Numbering scheme for the mesh of Alewife nodes.                                                         | 45 |

| 4.2 | Bench5.c on 16 processors: Per processor distribution of distances travelled                            |    |

|     | by RREQ packets going from caches of each processor to the memory of processor 0.                       | 45 |

| 4.3 | Bench5.c on 16 processors: Per processor distribution of distances travelled                            |    |

|     | by RDATA packets going from the memory of processor 0 to the caches of                                  |    |

|     | each processor.                                                                                         | 46 |

| 4.4  | Bench11.c on 8 processors: Per processor distribution of remote accesses    | 16 |

|------|-----------------------------------------------------------------------------|----|

|      | over time                                                                   | 46 |

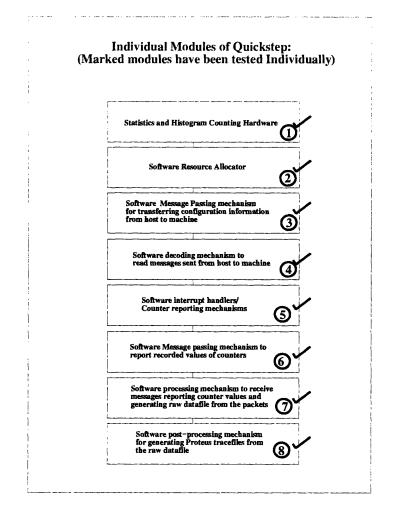

| 4.5  | Status of validation and testing of QuickStep.                              | 48 |

| 5.1  | Orig Mp3d: Per processor distribution of remote distances travelled by read |    |

|      | invalidation packets [Table B.4]                                            | 51 |

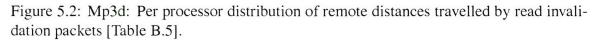

| 5.2  | Mp3d: Per processor distribution of remote distances travelled by read      |    |

|      | invalidation packets [Table B.5].                                           | 51 |

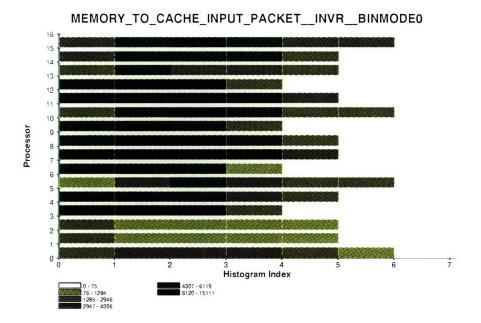

| 5.3  | MMp3d: Per processor distribution of remote distances travelled by read     |    |

|      | invalidation packets [Table B.6]                                            | 52 |

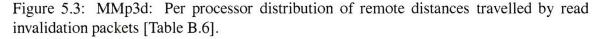

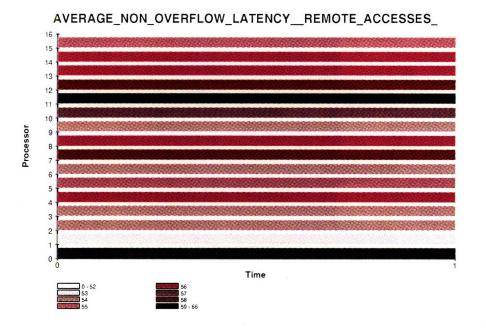

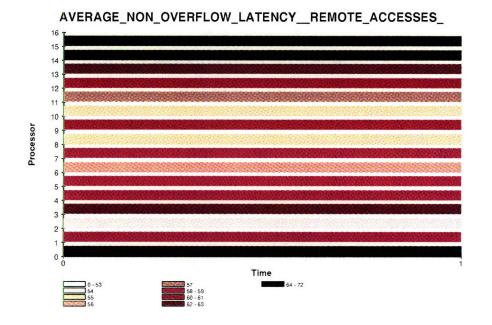

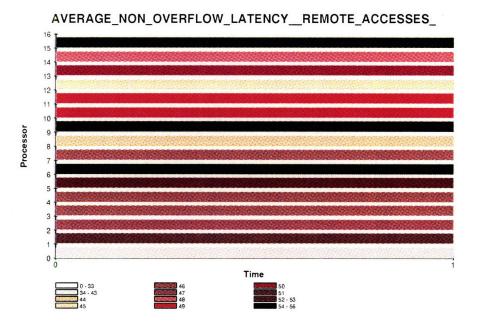

| 5.4  | Orig Mp3d: Average remote access latencies [Table B.7]                      | 53 |

| 5.5  | Mp3d: Average remote access latencies [Table B.8].                          | 53 |

| 5.6  | MMp3d: Average remote access latencies [Table B.9].                         | 54 |

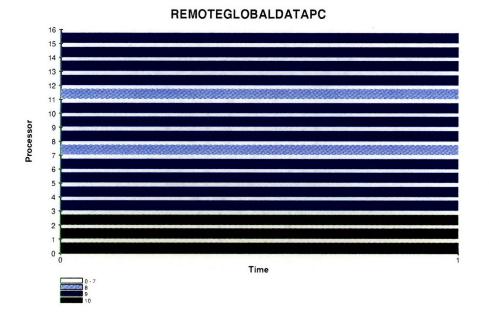

| 5.7  | Orig Mp3d: Percentage of remote global accesses.                            | 54 |

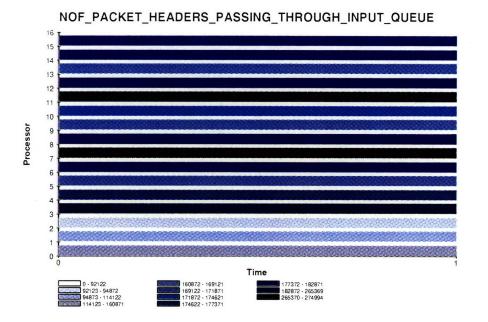

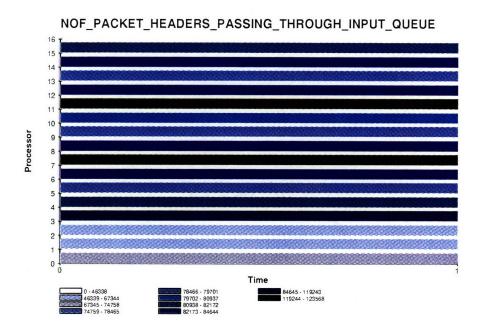

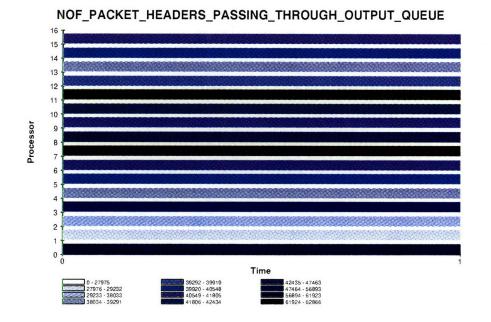

| 5.8  | Orig Mp3d: Packet headers passing through output queue [Table B.10].        | 55 |

| 5.9  | Mp3d: Packet headers passing through output queue [Table B.11].             | 56 |

| 5.10 | MMp3d: Packet headers passing through output queue [Table B.12]             | 56 |

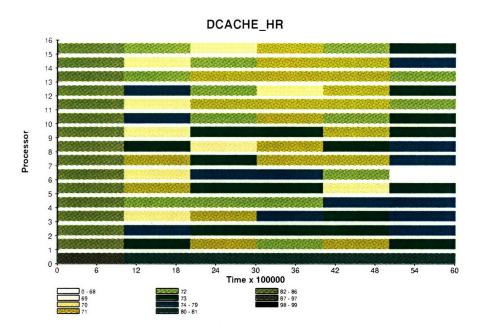

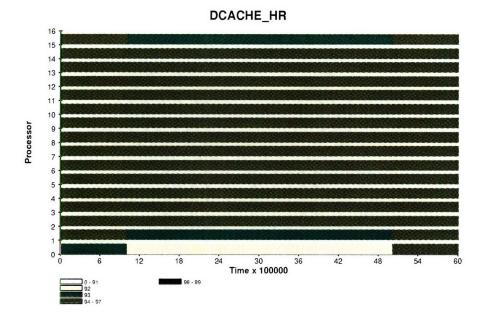

| 5.11 | ZGRID: Data cache hit ratios [Table B.13].                                  | 58 |

| 5.12 | MGRID: Data cache hit ratios [Table B.14].                                  | 58 |

| 5.13 | CGRID: Data cache hit ratios [Table B.15].                                  | 59 |

## Chapter 1

## Introduction

Even though the peak performance rating of multiprocessor systems has improved substantially over the past several years, the initial implementation of parallel applications almost never harnesses the full processing power. Performance bottlenecks abound and it is difficult for the programmer to keep track of all aspects of performance optimization. Consequently, there is the need for tools to assist in performance debugging.

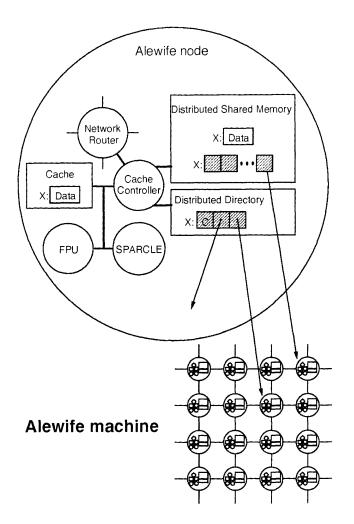

The Alewife machine is a large-scale multiprocessor with distributed shared memory built at the MIT Laboratory for Computer Science [1]. Alewife consists of a group of processing nodes connected by a two-dimensional mesh interconnection network. Each processing node consists of SPARCLE - a 33MHz processor, a floating point unit, 64Kbytes of static direct-mapped cache, 4 Mbytes of global shared memory, a network routing chip and a cache controller chip which enforces cache coherence between caches from different processing nodes, and provides a shared memory abstract view of distributed main memory (see Figure 1.1). Currently, the first batch of the Alewife *Communications and Memory Management Unit (CMMU)* chip is being tested by the members of the Alewife team and various software efforts in compiler and performance evaluation technology are in progress. **QuickStep** is one such project which explores the issue of performance debugging of parallel applications on the Alewife machine.

The Alewife CMMU has features to support performance monitoring in hardware. QuickStep utilizes these features to provide a performance monitoring and debugging platform.

Figure 1.1: An Alewife processor node.

## 1.1 Performance Monitoring and Debugging Methods: Background

Several efforts have been directed at identifying performance bottlenecks in parallel programs. The popular techniques are *Static Analysis, Simulation, Emulation, Hardware Instrumentation and Software Instrumentation* [10].

### 1.1.1 Static Analysis

Static analysis although fast, has limited applicability. The most extensive research in static analysis was done at the University of Illinois as a part of the Cedar multiprocessor project [16]. Static analysis involves predicting the performance of loops, counts of local and global memory references, estimates of MFLOPS, etc. based on simple models of instruction latencies and memory hierarchies. The Illinois project later went on to use more sophisticated techniques like exploiting compiler dependency analysis in the predictive models. However, the static analysis techniques are in general inaccurate and hence, are inadequate means of providing performance debugging solutions.

### 1.1.2 Simulation

Simulation is a slow but precise method. In execution driven simulation, a program is instrumented so that each operation causes a call to a routine which simulates the effects of that operation. While reasonably accurate, simulation is a very slow process and it is not even realistic to simulate the behavior of an entire large program. Therefore, simulation is hardly an effective tool for performance debugging. It is used more for detailed analysis of architectural tradeoffs and is important because it allows evaluation without real hardware. Simulation has been used extensively in the Stanford DASH [17] project, as well as in Alewife during the architectural design phase.

### 1.1.3 Emulation

Emulation is a method of hardware system debugging that is becoming increasingly popular. Field-programmable gate arrays have made possible an implementation technology that is ideal for full system prototyping, yet does not require the construction of actual silicon chips [23]. Emulation, also called Computer Aided Prototyping, combines CAE translation and synthesis software with FPGA technology to automatically produce hardware prototypes of chip designs from netlists. It enables concurrent debugging and verification of all aspects of a system including hardware, software and external interfaces, leading to a faster design cycle. Using emulation for performance debugging of applications, however, is not very common.

#### **1.1.4** Software Instrumentation

Software instrumentation is fast and flexible. Manually done, it involves instrumenting a program with write statements to print out special purpose information. More sophisticated tools involve automatic instrumentation. The common types of software instrumentation are accumulating an aggregate value (for example, time spent in a procedure) and tracing an event (a new trace event, usually time-stamped, is output each time it is executed). Software instrumentation, however, introduces inaccuracies due to their intrusive nature.

One of the earliest attempts at performance debugging in the sequential domain was *gprof* - an execution profiler that outputs data concerning execution timings in different routines [12]. Gprof monitors the number of times each profiled routine is called (*Call Count*) and the time spent in each profiled routine. The arcs of a dynamic call graph traversed by an execution of the program are also monitored and the call graph is built by post processing this data. The execution times are propagated along the edges of this graph to attribute times for routines to the routines that invoke them.

In the parallel world, a debugger called *Parasight* was developed at Encore Computer Corporation [2]. Parasight implements high-level debugging facilities as separate programs that are linked dynamically to a target program. Parasight was implemented on Multimax, a shared memory multiprocessor.

IPS is a performance measurement system for parallel and distributed programs that uses knowledge about the semantics of a program's structure to provide a large amount of easily accessible performance data and analysis techniques that guide programmers to performance bottlenecks [19]. IPS is based on the software instrumentation technique.

Quartz is another tool for tuning parallel program performance on shared memory multiprocessors. The principal metric in Quartz is *normalized processor time*: the total processor time spent in each section of the code divided by the number of other processors that are concurrently busy when that section of code is being executed.

Other related works can be found in [6], [7], [8] and [20]. A tool called *Memspy* is described in [18] that offers the additional feature of extremely detailed information to identify and fix memory bottlenecks. Memspy isolates causes of cache misses like cold

start misses, interference misses, etc. which is very useful.

Mtool is a software tool for analyzing performance loss by isolating memory and synchronization overheads [11]. Mtool provides a platform for scanning where a parallel program spends its execution time. The taxonomy includes four categories: Compute Time, Synchronization Overhead, Memory Hierarchy Losses, and Extra Work in Parallel Program (versus Sequential). Mtool is a fairly general implementation that runs on MIPS-chip based systems like DEC workstations, SGI multiprocessors and the Stanford DASH machine. Mtool's approach is distinct in that where most performance debugging tools lump the compute time and memory overhead together as "work", Mtool offers important information about the behavior of the memory system. Studies have shown that this is critical to optimizing the performance of parallel applications. Mtool is typically estimated to slow down programs by less than 10%.

#### **1.1.5 Hardware Instrumentation**

Hardware instrumentation involves using dedicated counters and registers to monitor events. Monitoring of events occurs in hardware and hence is virtually unintrusive. The biggest advantages of hardware instrumentation are its accuracy and speed.

The drawback of hardware instrumentation is that it is not widely available and it may not be as flexible as simulation. In our case, availability is not an issue since Alewife hardware was designed to support instrumentation counters. However, it is only possible to provide a finite amount of instrumentation support in hardware, so it is not as flexible as software. In Alewife, for example, we have 4 statistics counters that monitor a subset of all events. Therefore, only a finite set of events can be monitored during a single run. However, since runs can happen fast, multiple runs allow monitoring of larger sets of statistics. Furthermore, the event monitoring hardware was carefully architected so that most key events could be captured.

QuickStep takes a hybrid of hardware and software approaches and provides a friendly interface for viewing the data collected by the kernel. As is true for most hardware instrumentation based performance monitors, it is not trivial to directly port QuickStep to some other hardware platform. However, the concepts are general and portable. The features of QuickStep will include Gprof like execution profiling facilities, as well as means of monitoring memory system behavior and network traffic patterns.

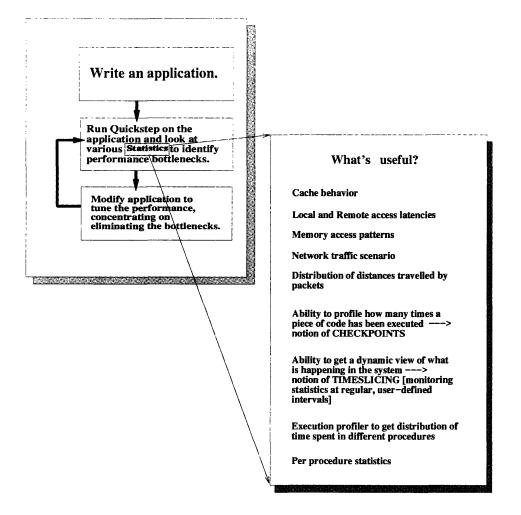

Figure 1.2: Flow chart of tuning the performance of an application using QuickStep.

### **1.2** Goals of the Thesis

The main goal of this work is to develop the QuickStep system with adequate features to provide a vehicle of further research on the Alewife machine. QuickStep provides a platform for monitoring cache and memory statistics, network statistics, various latencies and message frequencies, etc. for applications that are run on Alewife. It thus enables users to analyze the performance characteristics, bottlenecks and enhancement potentials and to accordingly fine-tune applications. Figure 1.2 shows a flow chart of tuning the performance of an application using QuickStep. It also shows what kind of statistics are useful for performance debugging. In principle, QuickStep is capable of providing all those features, although some of the profiling features have not been implemented yet.

The Alewife CMMU provides basic hardware support for monitoring events. 11% of the total chip area of the CMMU is dedicated to performance monitoring hardware. However, it is not possible to utilize this feature without a well-developed software interface which can handle the bit manipulations and produce comprehensible information. QuickStep provides this interface, as well as a graphical display environment for the information gathered.

### 1.3 Overview

The rest of this thesis proceeds as follows: Chapter 2 describes the features of QuickStep and illustrates the features that have been implemented so far with examples. This chapter also outlines other features that will be implemented in the next version of the system without too much modification of the existing model. Chapter 3 describes the principles followed in implementing QuickStep. Chapter 4 discusses the suite of programs used to test the validity of the system. Chapter 5 demonstrates the effectiveness of QuickStep by using it to analyze and optimize a few large parallel applications from the SPLASH suite. Finally, Chapter 6 summarizes the thesis.

## Chapter 2

## **Features of QuickStep**

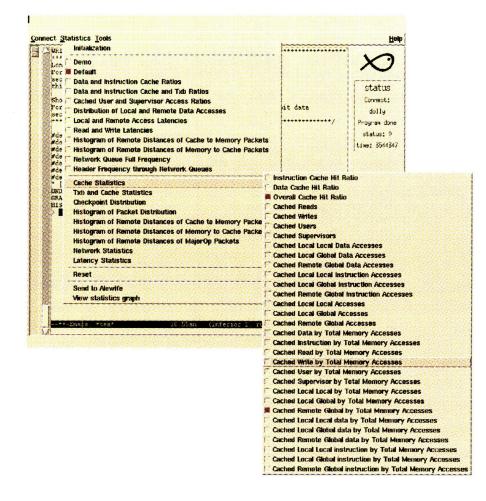

In QuickStep, the menu-driven interface through which different statistics are requested is a friendly environment [Figure 2.1]. This chapter describes the different classes of statistics that can be monitored and gives examples of sample outputs. Besides the major categories described here, the interface offers the additional facility of specifying pre-collated groups of statistics that are commonly used. The user can select one or more of these groups without having to look through the detailed menus. The groups are named in a self-explanatory way, for example, *Data and Instruction Cache Ratios, Distribution on Local and Remote Accesses, Read and Write Latencies, Header Frequency through Network Queues*, etc.

## 2.1 Timesliced Statistics

Statistics can either be recorded at the end of the run, or at regular intervals during the run. QuickStep provides both these options. allowing the user to get some amount of profiling information. Chapter 6 discusses the more elaborate profiling capabilities that will be provided in the next version of the system.

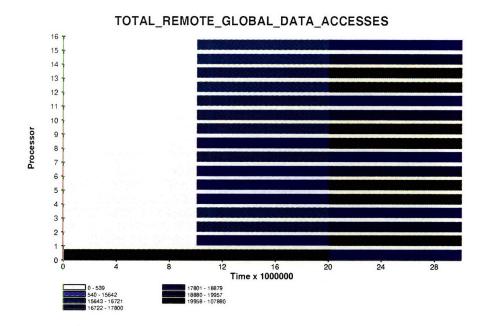

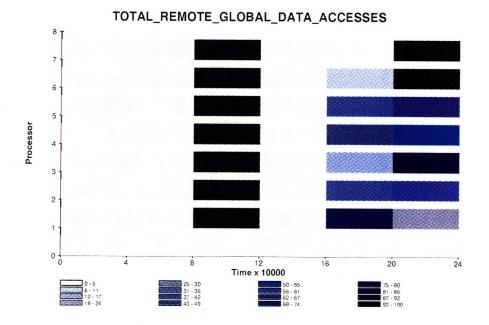

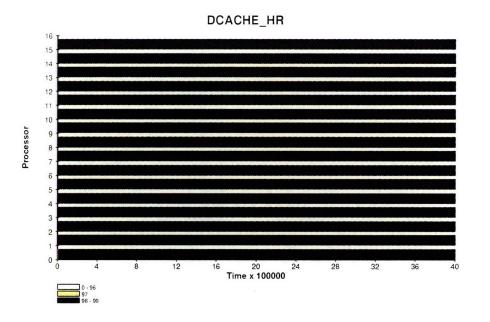

Figures 2.2 and 2.3 are examples of graphs obtained from the cache-statistics menu. The ratio figures on the graphs are rounded up to integers, however, if the user wants to look at more precise values, an easy-to-read raw datafile is available which provides figures upto 14 decimal places. Both the graphs have been obtained by running *Water* from the SPLASH suite on a 16-node Alewife machine, with timeslices of 10,000,000 cycles each. Since the data cache hit ratios are more or less uniform over time, the timeslice mode does not provide much extra information. Data cache hit ratios are uniformly 98-99% for all processors and timeslices, with the exception of the second timeslice of processor 0. However, in Figure 2.3 we see clearly how the access pattern changes over time. For

Figure 2.1: The Alewife user interface with pull-down menus for selecting the different statistics to be monitored.

Figure 2.2: Water on 16 processors: Per processor data cache hit ratio.

instance, during the first timeslice, all processors other than processor 0 are waiting for the initialization to be completed. Hence, the number of remote data accesses are low for all processors except processor 0. In the subsequent timeslices, all the processors are doing real computation, and the access pattern reflects activity.

When statistics are collected in the timesliced mode, program behavior is perturbed to some degree. Chapter 3 describes how the timesliced statistics are implemented and discusses perturbation due to instrumentation. When statistics are to be collected at regular intervals, the program has to stop running during the collection phases. This makes timesliced instrumentation intrusive and hence comparatively inaccurate. On the other hand, the timesliced mode does provide important information about program behavior over time.

## 2.2 Overall Statistics

Often, however, the user simply wants an overall summary statistic for the run. In such cases, the timesliced mode is turned off and the counter values are recorded at the end of the run. Figure 2.4 shows an example of a statistic gathered at the end of the run, ie. in the non-timesliced mode. It is possible to post-process data gathered in time-sliced mode

Figure 2.3: Water on 16 processors: Per processor distribution of remote shared data accesses [Table B.1].

to obtain the overall statistics. However, as discussed in the previous section, timesliced statistics perturb program behavior, while non-timesliced statistics do not. Furthermore, non-timesliced mode is naturally faster than the timesliced mode. As always, there is a trade-off between accuracy of statistics, perturbation of program and speed. Hence, we provide both timesliced and non-timesliced modes of collecting statistics.

## 2.3 Network Usage Statistics

Two types of hardware statistics yield histograms of values: *counts of packets* and *distribution of distances that packets have travelled*. The *counts of packets* mode watches network packets and whenever a packet appears in a designated direction (input or output), it is checked to see if it matches the class of packets that is being tracked. If so, then the corresponding histogram counter is incremented [Chapter 3]. This class of statistics is useful for tracking different classes of packets, especially from a low-level kernel programmer's point of view. Being able to track protocol packets, synchronization packets, boot packets, etc. can help a runtime system designer.

The distribution of distances mode increments histogram counters based on the number

NOF PACKET HEADERS PASSING THROUGH OUTPUT QUEUE

Figure 2.4: Water on 16 processors: Counts of packet headers passing through output queues [Table B.2].

of hops a packet of the specified class has travelled. Figure 2.5 gives an example of such a statistic. The y-axis has the processor number and the x-axis has the number of hops. The colors represent the numbers of packets in each category. This is very useful for debugging application performance because it provides a way of judging whether the application is showing good communication locality or not. Ideally, most of the communication ought to be nearest neighbor and if the remote distance histogram reflects that this is not the case, then the programmer can debug the application. It is easy to see the effect of debugging some aspect of a program by simply comparing histograms obtained from running different versions.

#### Checkpoints 2.4

Checkpoints are a set of useful debugging features offered by QuickStep. They are single cycle instructions that can be included at different points in a program and useful profiling information can be obtained by looking at the counts of the checkpoints. For instance, information can be obtained about how many times a procedure is called, or how often a particular section of code is executed.

Histogram of Remote Distances of Memory to Cache input packets

Figure 2.5: Water on 16 processors: Histogram of distances of memory-to-cache input packets [Table B.3].

To use the checkpoint facility of QuickStep the program being run needs to be annotated with the checkpoint instruction. This section gives an example of using checkpoints. The checkpoint instruction takes one argument, with two parts separated by a colon. The first part is the checkpoint group name and the second part is the checkpoint name. Checkpoint group is an abstraction which is used to group several checkpoints together. [A maximum of 16 checkpoints are allowed per group.] The argument translates to a 12-bit checkpoint address.

The three different checkpoint modes operate as follows:

- Classwise: In this mode, only the checkpoint group name to be tracked needs to be specified through the user interface. The address translation works such that the corresponding counter is incremented when the first 8 bits of the translated address matches a checkpoint.

- Single: In this mode, both the checkpoint group name and the checkpoint name to be tracked need to be specified through the user interface. The address translation works such that the corresponding counter is incremented when all 12 bits of the translated address matches a checkpoint.

- **Histogram**: In this mode, only the checkpoint group name to be tracked needs to be specified through the user interface. The histogram mode of checkpoint monitoring gives a distribution of accesses for checkpoints of a certain class.

Figures 2.6, 2.7 and 2.8 use the checkpoint features of QuickStep to monitor the procedure *Proc1* listed in Appendix A. *Proc1* is annotated with some checkpoints and when those checkpoints are tracked using QuickStep, the expected frequencies are obtained.

The procedure *Proc1* is started up on all 16 processors with arguments 10 and 200. Checkgr2:Check2 is monitored in Figure 2.6 and rightly comes out to be (10\*ProcessorId) on each processor. [The graph shows the ranges of frequencies and table 2.1 shows the exact numbers.]

Checkgr2 is monitored in Figure 2.7 and rightly comes out to be (10 \* ProcessorId + 2) on each processor. [The graph shows the ranges of frequencies, while table 2.1 shows the exact numbers.]

Checkgr3 is monitored in Figure 2.8 and rightly comes out to be 1 each for Check1 (Histogram Id = 0) and Check3 (Histogram Id = 2) and (200 - (10 \* ProcessorId)) for Check2 (Histogram Id = 1) on each processor. [The graph shows the ranges of frequencies and table 2.2 shows the exact numbers. Data for processors 0 through 6 only are represented in the table, but the rest of the data from the raw file have been verified to be consistent.]

Figure 2.6: Result of monitoring Checkgr2:Check2.

Figure 2.7: Result of monitoring Checkgr2.

| Processor Id | Checkgr2 | Checkgr2:Check2 |

|--------------|----------|-----------------|

| 0            | 2        | 0               |

| 1            | 12       | 10              |

| 2            | 22       | 20              |

| 3            | 32       | 30              |

| 4            | 42       | 40              |

| 5            | 52       | 50              |

| 6            | 62       | 60              |

| 7            | 72       | 70              |

| 8            | 82       | 80              |

| 9            | 92       | 90              |

| 10           | 102      | 100             |

| 11           | 112      | 110             |

| 12           | 122      | 120             |

| 13           | 132      | 130             |

| 14           | 142      | 140             |

| 15           | 152      | 150             |

Table 2.1: Data obtained from the raw data file for the classwise and single checkpoint graphs.

Figure 2.8: Result of monitoring Checkgr3.

| Processor Id | Checkgr3 | Histogram Id |

|--------------|----------|--------------|

| 0            | 1        | 0            |

| 0            | 200      | 1            |

| 0            | 1        | 2            |

| 1            | 1        | 0            |

| 1            | 190      | 1            |

| 1            | 1        | 2            |

| 2            | 1        | 0            |

| 2            | 180      | 1            |

| 2            | 1        | 2            |

| 3<br>3       | 1        | 0            |

| 3            | 170      | 1            |

| 3            | 1        | 2            |

| 4            | 1        | 0            |

| 4            | 160      | 1            |

| 4            | 1        | 2            |

| 5            | 1        | 0            |

| 5            | 150      | 1            |

| 5            | 1        | 2            |

| 6            | 1        | 0            |

| 6            | 140      | 1            |

| 6            | 1        | 2            |

Table 2.2: Data obtained from the raw data file for the checkpoint histogram.

## 2.5 Additional Features

The first major addition that is planned for the next version of QuickStep is a profiling feature. Currently, statistics gathering cannot be turned on or off in the middle of a run. However, this is a feature that would be of enormous usefulness. For instance, users of the QuickStep system have commented that it would be useful if a certain set of statistics could be computed on a per procedure basis. The statistics could be of various types: the amount of time spent in the procedure, the cache behavior and the network statistics for the procedure, etc.

This feature can be incorporated easily, by encoding the turning on and off of statistics counters into a function. Ideally, the user should be able to specify the name of the procedure and the statistics to be monitored. The compiler/linker would then incorporate the function in that procedure automatically, the process being transparent to the user.

Furthermore, there are several classes of statistics that the CMMU supports which have not been implemented in this version. These include synchronous trap statistics, hitmiss statistics, remote transaction statistics, memory controller statistics and transaction buffer statistics.

From a presentation point of view, we are currently using the Proteus *Stats* program as the display environment. Most of the data we are presenting would be easier to read in a 3-dimensional graphical display environment, which stats does not support. There is room for improvement in the way the statistics are represented through graphical displays.

## **Chapter 3**

## Implementation

In this chapter, we discuss the implementation details of the QuickStep performance monitoring system. Figure 3.1 shows a flow chart of the QuickStep system. This chapter is organized according to the flow chart as follows: We first describe the user interface in Section 3.1. Next, the Alewife architechtural support for performance monitoring and the resource allocation procedure are described in Section 3.2. Finally, the data collection and reporting is described in Section 3.3, and the graphical display is discussed in Section 3.4.

## 3.1 User Interface

The high-level interface for the QuickStep system is an integrated part of the general Alewife interface developed by Patrick Chan. Figure 2.1 shows a snapshot of the interface. It consists of menu items for:

- Connecting to the Alewife machine or to the NWO simulator (NWO is a simulator that has been developed as a part of the Alewife design process by David Chaiken)

- For selecting the statistics to monitor and display the graphical output of QuickStep

- For running *Parastat* a graphical monitor of the status of the individual nodes of the Alewife machine (also developed by David Chaiken)

The code for the interface is written in Tcl, an X-windows programming environment.

The user requests the statistics that he or she wants to monitor by clicking on the relevant menu items. The major classes of statistics that are currently offered are the following:

Figure 3.1: Flow chart of the QuickStep system.

- Cache Statistics

- Checkpoints for profiling

- Histograms of Remote Distances of cache to memory and memory to cache packets

- Network Statistics

- Latency Statistics for different types of memory accesses

This information is then passed on to the host[Figure 3.2] by selecting *Send to Alewife* from the *Statistics* menu. Internally, this transfer of information happens through the exchange of a message which is decoded by the host running QuickStep.

### **3.2** Resource Allocation

In this section, we first describe the hardware support that Alewife provides for performance monitoring. Then, we discuss the resource allocation problem, and how it is solved in QuickStep. We also describe the configuration file in which resource requirement information for different statistics are stored.

#### **3.2.1** Alewife's Performance Monitoring Architecture

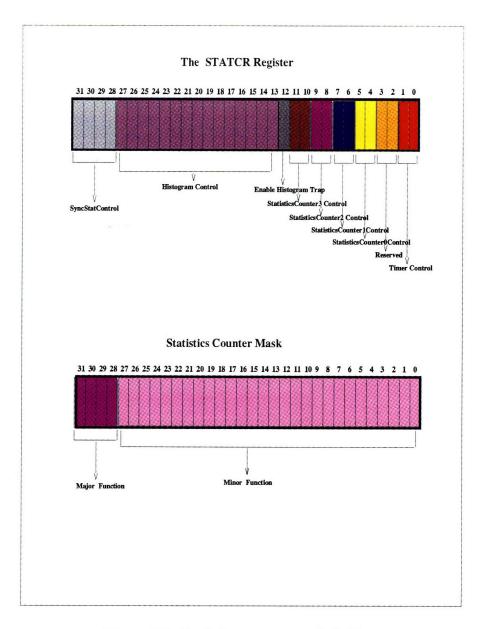

Alewife, being a vehicle for research in parallel computation, has several built-in features that assist in monitoring events like *data and instruction cache hit ratios, read accesses, write accesses, distances travelled by packets,* etc. In particular, the CMMU has 4 dedicated 32-bit statistics counters, and 16 20-bit histogram registers. The histogram registers are also counters that are incremented when certain events occur. The histogram registers monitor events like histograms of checkpoints, packet distributions and packet distances. The histogram control field of the statistics count different events. Each statistics counter is independently configured with a 32-bit event mask.

When an overflow of the statistics or histogram counters occurs, the hardware takes a trap. A 32-bit overflow counter for each statistics and histogram counter is implemented in software, which are then incremented. 64-bit resolution is thus achieved by extension into software.

The user interacts with the machine through the host (see Figure 3.2). The host is attached to processing node 15 of the mesh, and supports an interactive user interface.

Figure 3.2: Software layers in Alewife.

The user can boot the machine, load and run programs via this interface. The code for instrumenting the statistics gathering facility is included as a part of the Alewife kernel and the statistics monitoring mode is activated by adding features to the host interface. The Alewife kernel supports a message-passing interface [15] which is used to communicate between the host and the machine.

Alewife also supports a timer interrupt facility which is used to interrupt processors at specified times to collect statistics for a certain interval. This feature of the Alewife architecture is utilized in QuickStep to provide snapshot views of the behavior of a program over time, as described in Chapter 2.

### 3.2.2 Hardware Mask Configuration

As mentioned before, the CMMU has registers dedicated to monitor statistics. These registers are divided into two sets: the statistics counters and the histogram registers. Each set is controlled by one or more control registers. The statistics and histogram registers can work independently, or work together (to compute latency statistics).

The histogram registers are controlled as a single unit by the StatCR (statistics control) register. The registers work together as bins (except when computing latencies) to keep a

histogram of different events. Chapter 2 provides examples of this mode. The StatCR also controls other aspects of the statistics registers such as traps.

The counter registers work independently of each other and each has an associated 32 bit control register called its *mask*. These masks can be used to make the counters count a general set of events, or a subset of events. For instance, a counter can be set up to count cache hit ratios, or just data cache hit ratios.

Figure 3.3 shows the fields of the StatCR register and of a typical statistics counter mask. The *histogram control field* of the StatCR register holds the histogram mask, the *StatCounter0 Control, StatCounter1 Control, StatCounter2 Control and StatCounter3 Control* fields are responsible for enabling and disabling statistics counters 0 through 3.

The statistics counter masks have a 4-bit major function specifier and a 28-bit minor function specifier each. The major function specifier bits determine the class of statistics to be monitored (eg. checkpoints, network statistics, etc.) The minor function specifier fields determine the specifics within a class of statistics.

Let us look at a counter mask from the configuration file in Figure 3.6. 201EFF20 is the hexadecimal mask for counting number of cached data accesses. The major function specifier is 2, which represents the cache statistics. Bits 17 through 21 represent the type of processor request. Bit 21, for instance, denotes an instruction match. Since we are counting data accesses specifically, bit 21 is turned off. Bits 17 through 20 are read and write requests and are hence turned on. Bit 5 represents cached accesses and hence needs to be on. The rest of the bits are configured accordingly.

#### **3.2.3** The Resource Allocator

As mentioned before, the Alewife CMMU has only 4 statistics counters and 1 set of 16 histogram registers. Consequently, only a small number of events can be monitored during a single run. Hence, when the user requests a large number of statistics, several runs are needed to satisfy such requests. In such cases, allocation of counters need to take place across runs.

QuickStep has a resource allocator to take care of this task. Say, the user has requested 3 statistics: Data Cache Hit Ratios, Cached Unshared Data Accesses, Cached Local Shared Data Accesses and Cached Remote Shared Data Accesses. For Data Cache Hit Ratios we need 2 counters to count *number of cached data accesses* and *total number of data accesses*. For Cached Unshared Data Accesses we need 2 counters to count *number of cached unshared data accesses* and *total number of unshared data accesses*. For Cached Local Shared Data accesses we need 2 counters to count *number of cached Data accesses* we need 2 counters to count *number of cached local shared*

Figure 3.3: Statistics counter mask fields.

*data accesses* and *total number of local shared data accesses*. For Cached Remote Shared Data accesses we need 2 counters to count *number of cached remote shared data accesses* and *total number of remote shared data accesses*. That is a total of 8 events and 8 statistics counters are needed to compute them.

The resource allocator is intelligent enough to be able to figure out how many counters will be needed and how many runs will be required given the counter requirement. It can also eliminate duplicate events and optimize the number of runs required to satisfy the requested set of statistics. In this case, the resource allocator assigns *number of cached data accesses, total number of data accesses, number of cached unshared data accesses* and *total number of unshared data accesses* to the first run. The *number of cached local shared data accesses, total number of local shared data accesses, number of cached remote shared data accesses* are assigned to the second run.

The fact that all the requested statistics cannot be computed in one run due to limitations in the availability of hardware resources, implies, there is always a window of error. Hence, each statistic needs to be gathered several times and averaged over all data points to eliminate this effect. Since the hardware can only provide a finite set of resources, this effect is pretty much unavoidable.

### **3.2.4** The Configuration File

The information about what the mask values are for each event to be monitored is stored in a configuration file that is read by the resource allocator. The configuration file uses a configuration language described in Figure 3.4.

The operations that are to be performed on the counters to get the requested statistics are specified by the *CounterOperations* keyword. The specific operations that are allowed are described in Figure 3.5

#### **Example of a Configfile**

Figure 3.6 shows a sample configuration file with four records.

The first record provides the resource specifications for *Data Cache Hit Ratio* of statistics class *Cache Statistics*. The 2 counter masks provide mask-configurations for monitoring *the total number of cached data accesses* and *the total number of data accesses*. The record assumes that counter 0 will be monitoring the number of cached accesses and counter 1 will be monitoring the total number of accesses. The statistics that are reported if this record

|               | C                                                                                                                             |

|---------------|-------------------------------------------------------------------------------------------------------------------------------|

|               | ame of the statistic, with dots separating each menu subclass for<br>ne main user interface.                                  |

| CounterMas    | ks : Masks necessary for the relevant events;<br>represented as hexadecimal values (preceeded by #x)                          |

| CounterOpe    | ration: Operations to be performed on the counter values;<br>the set of operations allowed are described below                |

| HeaderStrin   | gs: Headers describing each statistic that is obtained by computing the result of each CounterOperation                       |

| HistogramM    | ask : Histogram Mask necessary for the relevant events;                                                                       |

| HistogramH    | eaderStrings : Headers describing the result of the<br>Histogram Operation                                                    |

| HistogramO    | peration : Currently, "Histogram" is the only operation allowed which reports the value of the histogram counters.            |

| TimeFlag :    | TimeFlag = 0 means timeslicing is not implemented,<br>TimeFlag = 1 means it is.                                               |

| Help: Des     | cribes the details of what are available as a part of the statistic                                                           |

| Accumulato    | r : Accumulator = 1 implies latency statistics are being computed,<br>and counter zero will need to be used as an accumulator |

| GroupNames    | S: Name of statistics group                                                                                                   |

| StatisticsNan | <b>nes</b> : If a statistics group has been defined, then the statistics constituting that group are referenced here          |

| EndRecord :   | An "EndRecord" is placed at the end of each statistics record                                                                 |

| EndOfFile :   | Needed at the end of the file                                                                                                 |

|               |                                                                                                                               |

|               |                                                                                                                               |

The Configfile reserved words are the following:

Figure 3.4: The configuration language.

### List of Operations allowed by the Configuration File Language

.....

| Value : | Takes 1 argument;<br>Reports value of the counter which is passed as the argument.                                                                                                                                                                            |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Div :   | Takes 2 arguments;<br>Reports result of dividing the value of the counter that is passed<br>as the first argument by the value of the counter that is passed<br>as the second argument.                                                                       |

| Sum :   | Takes multiple arguments;<br>Adds all the counter values that are passed as arguments.                                                                                                                                                                        |

| Mul :   | Takes multiple arguments;<br>Reports the product of all the counter values that are passed<br>as arguments.                                                                                                                                                   |

| Sub :   | Takes 2 arguments;<br>Reports the difference of the 2 counter values that are passed<br>as arguments.                                                                                                                                                         |

| DivMul  | : Takes 3 arguments;<br>Reports the result of multiplying the first argument (a number)<br>with the result of dividing the value of the counter that is passed<br>as the second argument by the value of the counter that is passed<br>as the third argument. |

|         | The Counter arguments are passed as numbers: 0, 1, 2 and<br>3 – referring to Counter 0, Counter 1, Counter 2, and<br>Counter 3.                                                                                                                               |

|         |                                                                                                                                                                                                                                                               |

Figure 3.5: The operation keywords.

12

is chosen by the user are specified by the header strings: *number of cached data accesses*, *total number of data accesses* and *data cache hit ratio*. The CounterOperation keyword gives the operations required to get those statistics. For example, the number of cached data accesses is the value of counter 0 and the total data accesses is the value of counter 1. The data cache hit ratio is obtained by dividing the value of counter 0 with that of counter 1 and multiplying the quotient by 100. TimeFlag = 1 implies that this statistic is available in the timesliced mode as well.

The other 3 records provide resource specifications for Cached Unshared Data Accesses, Cached Local Shared Data Accesses and Cached Remote Shared Data Accesses.

The configuration file is read by a parser which gets all the arguments related to the sets of statistics that have been requested. It then passes that information on to the resourceallocator, which determines the number of runs required and assigns the masks for each run.

Currently the configuration file is hand-generated, thereby leaving room for errors. In the next implementation of QuickStep, we would like to modify the configfile language somewhat, so as to allow for a more automated procedure for generating the configfile.

### **3.3** The Machine Side

Since all the resource allocation information is processed by the host, the task on the machine side is very simple. The host passes all the information for a particular run in a message to the machine. The machine (kernel) configures the statistics counter masks and the histogram control mask accordingly[Figure 3.3]. It also clears all the counters. If timesliced mode is requested, then the timer is programmed to go off at regular intervals. Finally, the counters are enabled at the beginning of the run. If timesliced mode is off, then statistics are gathered at the end of the run and the data is sent back in packets to the host.

#### 3.3.1 Data Collection and Reporting

When timeslicing is not used, the counter values are simply collected at the end of the run and sent back to the host in packets.

However, as described in Chapter 2, QuickStep offers the option of monitoring timesliced statistics. This feature is implemented by using a timer interrupt facility supported by the Alewife hardware. In our first implementation, the timesliced mode would cause an interrupt to happen at regular intervals. The interrupt handler would then disable all the

```

Name "Cache_Statistics.Data_Cache_Hit_Ratio"

CounterMasks #x201EFF20 #x201EFF3F

CounterOperation Value 0 Value 1 DivMul 100 0 1

HeaderStrings "#ofCachedDataAcc" "#ofDataAcc" "DCache-HR"

TimeFlag 1

Help "Offers 3 figures: Number of Cached Data Accesses,

Number of Total Data Accesses, and

Data Cache Hit Ratio"

EndRecord

Name "Cache_Statistics.Cached_Local_Local_Data_Accesses"

CounterMasks #x201EF320 #x201EF33F

CounterOperation Value 0 Value 1 DivMul 100 0 1

HeaderStrings "Cached Local-Local-Data Accesses"

"Total Local-Local-Data Accesses"

"Cached-Local-Local-Data"

TimeFlag 1

Help "Offers 3 figures: Cached Local-Local-Data Accesses,

Total Local-Local-Data Accesses, and

Cached Local-Local-Data Ratio"

Name "Cache_Statistics.Cached_Local_Global_Data_Accesses"

CounterMasks #x201EF520 #x201EF53F

CounterOperation Value 0 Value 1 DivMul 100 0 1

HeaderStrings "Cached Local-Global-Data Accesses"

"Total Local-Global-Data Accesses"

"Cached-Local-Global-Data"

"Cached-Local-Global-Data Accesses,

Total Local-Global-Data Accesses, and

Cached Local-Global-Data Ratio"

EndRecord

Name "Cache_Statistics.Cached_Remote_Global_Data_Accesses"

CounterMasks #x201EF920 #x201EF93F

CounterOperation Value 0 Value 1 DivMul 100 0 1

HeaderStrings "Cached Remote-Global-Data Accesses"

"Total Remote-Global-Data Accesses"

"Cached-Remote-Global-Data"

TimeFlag 1

Help "Offers 3 figures: Cached Remote-Global-Data Accesses,

Total Remote-Global-Data Accesses, and

Cached Remote-Global-Data Ratio"

EndRecord

```

-----

\_\_\_\_\_

Figure 3.6: A sample configuration file.

statistics and histogram counters and a packet reporting the counter/histogram information would be sent to the host. This protocol created a problem since whenever a large number of processors were involved, too many messages were going towards the host, thereby clogging up the network. We solved this problem by buffering the statistics counter values in arrays of structures (described in Figure 3.7). Note, the statistics counters are 32-bits in length and the histogram registers are 20-bits in length. However, additional overflow handling mechanism implemented in software provides 64-bit resolution for each register. Hence, when the counter values need to be stored, both the upper 32-bits and the lower 32-bits need to be recorded. The data-structures shown in Figure 3.7 demonstrate provisions for handling this task. We staggered the reporting of data to the host by ensuring that no two processors are reporting data during the same timeslice and thereby lightened the load on the network. The number of messages was reduced by sending large chunks of the array in a single message.

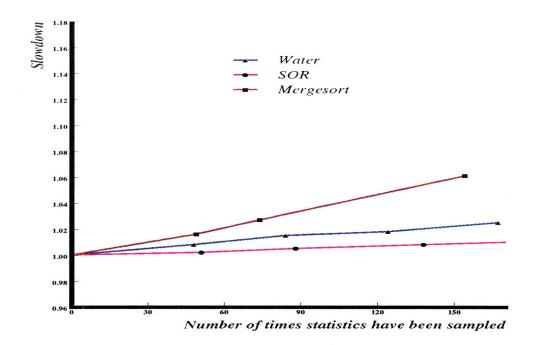

#### 3.3.2 Instrumentation Overhead due to TimeSlicing

Interrupting a program every so often is expected to perturb a program in terms of memory behavior, execution times, etc. We have done an experiment with perturbation characteristics regarding execution times. Figure 3.8 shows the results of the experiment. We ran 3 applications (namely, *Water, SOR* and *Mergesort*) first without timeslicing, and then timeslicing with decreasing intervals (ie. increasing number of times the system is interrupted). We found that the slowdown factor (ratio of execution time *with* timeslicing to execution time *without* timeslicing) is nominal for upto about 180 interruptions. It was not possible to get measurements with higher numbers of interruptions because the current network overflow software for Alewife cannot handle a higher degree of network congestion.

In our implementation of the timesliced mode of statistics gathering, we have faced some problems. When data reporting messages are sent to the host too often, the network clogs up. However, if very large buffers are used for storing the data, then the memory requirement on each processor limits the memory available to the application, and hence causes capacity misses, thereby deteriorating its performance. There are a couple of solutions to this problem:

- Increasing the memory on each node

- Adding I/O nodes to decrease network congestion

We expect these features to be available in later versions of Alewife.

Figure 3.7: Data structure for storing counter values.

Figure 3.8: Instrumentation overhead due to timeslicing: Monitoring timesliced data and instruction cache hit ratios for 3 applications.

### 3.4 Post-Processing

The data packets are received by the host and stored in memory until the end of the run. At the end of the run, they are output into a raw data file in a simple column format. A sample data file is given in Figure 3.9. The raw file is then processed to generate a binary file that is in the Proteus [5] trace file format, that can be viewed with a graphical interface supported by the Proteus Stats program. Chapter 2 shows examples of graphs obtained as outputs of the QuickStep system. The column headings from the raw data file are used to generate headings and menus for the graphs. The graphs give approximate ranges that are helpful as an easy-to-grasp summary. However, the datafile values are available if a user would like to look at more precise statistics. The *Index* column represents the processor number and the *timestamp* field represents the timeslice id. [In Figure 3.9, a small program was run on a 16-node Alewife machine and only overall statistics were gathered.]

| "Tota | l Local | -Local | -Data | Acce   | sse | 5 <sup>4 4</sup> | Cached-Lo | ocal-Lo | cal-I | ata <b>"</b> | Ind  | ex | Times | stamp |

|-------|---------|--------|-------|--------|-----|------------------|-----------|---------|-------|--------------|------|----|-------|-------|

| 331   | 332     | 99.6   | 98795 | 18072  | 288 | 331              | 332       | 99.6    | 8795  | 1807         | 2288 | 3  | 0     | -     |

| 330   | 331     | 99.6   | 97885 | 19637  | 463 | 330              | 331       | 99.65   | 7885  | 1963         | 7463 | 6  | 0     |       |

| 330   | 331     | 99.6   | 97885 | 519637 | 463 | 330              | 331       | 99.6    | 97885 | 1963         | 7463 | 9  | 0     |       |

| 332   | 333     | 99.6   | 99699 | 69969  | 969 | 332              | 333       | 99.6    | 9699  | 6996         | 9969 | 4  | 0     |       |

| 329   | 330     | 99.6   | 96969 | 69696  | 969 | 329              | 330       | 99.6    | 96969 | 6969         | 6969 | 7  | 0     |       |

| 329   | 330     | 99.6   | 96969 | 69696  | 969 | 329              | 330       | 99.6    | 96969 | 6969         | 6969 | 12 | 0     |       |

| 330   | 331     | 99.6   | 97885 | 19637  | 463 | 330              | 331       | 99.69   | 7885  | 1963         | 7463 | 10 | 0     |       |

| 331   | 332     | 99.6   | 98795 | 18072  | 288 | 331              | 332       | 99.6    | 8795  | 1807         | 2288 | 5  | 0     |       |

| 328   | 329     | 99.6   | 96048 | 63221  | 885 | 328              | 329       | 99.69   | 6048  | 6322         | 1885 | 13 | 0     |       |

| 328   | 329     | 99.6   | 96048 | 63221  | 885 | 328              | 329       | 99.69   | 96048 | 6322         | 1885 | 14 | 0     |       |

| 332   | 333     | 99.6   | 99699 | 69969  | 969 | 332              | 333       | 99.69   | 9699  | 6996         | 9969 | 2  | 0     |       |

| 327   | 328     | 99.6   | 95121 | 95121  | 95  | 327              | 328       | 99.69   | 5121  | 9512         | 195  | 15 | 0     |       |

| 331   | 332     | 99.6   | 98795 | 18072  | 288 | 331              | 332       | 99.69   | 8795  | 1807         | 2288 | 8  | 0     |       |

| 329   | 330     | 99.6   | 96969 | 69696  | 969 | 32 <b>9</b>      | 330       | 99.69   | 6969  | 6969         | 6969 | 11 | 0     |       |

| 333   | 334     | 99.7   | 00598 | 80239  | 52  | 333              | 334       | 99.70   | 0598  | 8023         | 952  | 1  | 0     |       |

| EndRe | cord    |        |       |        |     |                  |           |         |       |              |      |    |       |       |

|       |         |        |       |        |     |                  |           |         |       |              |      |    |       |       |

|       |         |        |       |        |     |                  |           |         |       |              |      |    |       |       |

|       |         |        |       |        |     |                  |           |         |       |              |      |    |       |       |

|       |         |        |       |        |     |                  |           |         |       |              |      |    |       |       |

. ....

Figure 3.9: Excerpt from a sample data file.

## 3.5 Summary

i I