### An Integrated Associative Processing System

by

### Frederick Paul Herrmann

S.B., Electrical Engineering S.B., Mathematics Massachusetts Institute of Technology (1987)

S.M., Electrical Engineering and Computer Science Massachusetts Institute of Technology (1989)

Submitted in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

#### in Electrical Engineering and Computer Science

at the

Massachusetts Institute of Technology

September, 1994

Signature of Author <u>Compartment of Electrical Engineering and Computer Science</u> July 28, 1994 Certified by <u>Professor Charles G. Sodini</u> NA . Thesis Supervisor Accepted by <u>Professor Frederic R. Morgenthaler</u> Chairman, Department Committee on Graduate Students © Massachusetts Institute of Technology, 1994 All rights reserved

#### An Integrated Associative Processing System

by

Frederick Paul Herrmann

Submitted to the Department of Electrical Engineering and Computer Science on July 28, 1994 in partial fulfillment of the requirements for the Degree of Doctor of Philosophy

#### Abstract

The design and implementation of an integrated associative processor is described. The chip is intended for use as a coprocessor in a system for accelerating pixel-parallel image processing tasks on desktop workstations and personal computers. Each of the chip's 256 processing elements includes 64 trits of three-state memory, a function generator, an activity register, and connections to a reconfigurable mesh network and a response resolution subsystem. The device-intensive design style makes extensive use of dynamic logic in dense pitch-matched circuits.

A novel dynamic associative memory cell supports fully-parallel match and write operations. The cell uses five MOS transistors, including two overlapping dual-gate devices available in double-polysilicon processes. The necessary sense and driver circuits are discussed, with particular attention to switching noise considerations.

The processing elements communicate over an Asynchronous Reconfigurable Mesh network which provides a mechanism for simultaneous broadcasting over multiple connected regions. The area-efficient implementation requires only one driver circuit per processing element. The network is readily extendible across chip boundaries, so that large arrays can be constructed with multiple chips.

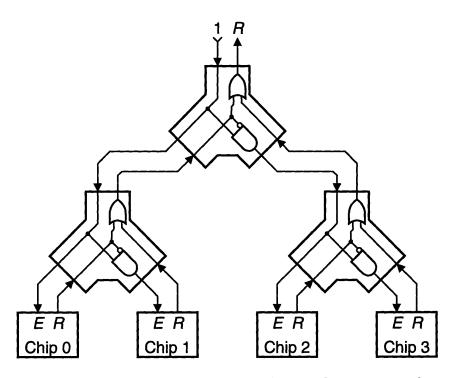

A new response resolution circuit is used to count and prioritize selected processing elements. A compact pass transistor chain is used within the confines of the array, and results from multiple arrays are combined in a tree structure.

Results are presented which verify the full functionality of all chip subsystems. The performance evaluation of the design is complicated by the fact that the chip was fabricated in a process other than that for which it was intended, but experimental results are shown to be consistent with measured process parameters. A 6-V supply is used to compensate for the high (2.1 V) second-polysilicon threshold voltages. Write and match instructions are performed in 175 ns, and 220 mW are dissipated in typical applications. The results of storage time experiments examining charge pumping, spooning, and leakage effects are presented.

A sample image processing application is demonstrated on a prototype system with four chips and 1024 processing elements. Several ideas for further work are discussed in the conclusion.

Thesis Supervisor:Charles G. SodiniTitle:Professor of Electrical Engineering

## Acknowledgements

I am grateful to my thesis advisor, Professor Charles Sodini, for his encouragement and guidance, both technical and personal. I have been privileged to be a member of his technically diverse research group, and I appreciate the opportunities I have had to broaden my experience under his supervision.

Jon Wade is gratefully acknowledged as my predecessor in the Smart Memory Project and as the inventor of the dynamic CAM cell upon which the cell used in this work is based. I learned a great deal while sharing office space with Jon, and I am particularly appreciative of his patience in going over the DBA design with me. Jeff Gealow brought a wealth of memory design knowledge to this same office, and I gratefully acknowledge his collaboration in the Associative Processing Project. I have enjoyed working with him on the system and software aspects of our projects, and I wish him and his circuits well.

I would like to acknowledge my readers, Professor Jon Allen and Professor Greg Papadopoulos, and thank them for their interest in this work. Their suggestions have helped me produce a better and more readable document.

I further acknowledge past and present members of the Associative Processing Project: Larry Hsu designed and built the system controller, which proved invaluable for chip testing. Chad Mikkelson was of great help to me in the lab, gathering most of the charge transfer data presented herein. Daphne Shih constructed the demonstration I/O system, and she is now working on a full-scale implementation. Keisuke Ishio designed the first cell test circuits; I thank him and Sharon Britton for sharing their real-world design experience. Thanks also to Phil Chu, John Maeda, Ahmed Mitwalli, and Shih-Jih Yao, all of whom contributed to the early associative processor software.

Craig Keast developed the MTL CCD-CMOS process and graciously accommodated the cell test circuits on his wafers. My thanks to him and to Jeff Gross, Kathy Krisch, and Joe Lutsky for answering my device questions, and to Ken Szajda for watching over my wafers in the ICL. I am also grateful to Steve Decker and Chris Umminger for help with measurements and much useful information, and to Curtis Tsai for convincing me that learning more about UNIX would be worthwhile.

I have greatly benefited from my association with the Vision Chip Project, and I appreciate their willingness to consider digital solutions. I particularly thank Professor John Wyatt for his leadership of the group and Professor Harry Lee for his always well-considered advice.

I was fortunate to accompany Prof. Sodini to UC Berkeley in the spring of 1990. Much of the architecture was still crystallizing during this period, and I thank Krste Asanović for his helpful comments on my partially formed ideas.

Pat Varley and Carolyn Zaccaria are skilled navigators of the M.I.T. bureaucracy, and I have been glad of their assistance on many occasions.

I appreciate the work of our computer system managers, both official and pro tempore: Vince Loh, Thomas Lohman, Giampiero Sciutto, and "Fletch" Freeman. I thank Professor Donald Troxel for access to the instructional laboratories, and I thank the MTL staff for fabrication, packaging, and measurement services.

A friend observes that nothing affects one's job satisfaction so much as the people with whom one works, and my experience confirms that this applies to grad school as well. This place abounds in talented graduate students and all-around good folks. Along with those already mentioned, I am glad to have known and worked with Michael Ashburn, Monica Choi, Kamyar Eshghi, Rod Hinman, Merit Hong, Jarvis Jacobs, Andrew Karanicolas, Jen Lloyd, Dave Martin, Vince McNeil, Ignacio McQuirk, Shujaat Nadeem, Ken O, Patrice Parris, Gee Rittenhouse, Julie Tsai, Bing Wang, and Paul Yu.

While at Berkeley I had the pleasure of meeting Eric Boskin, David Cline, Cormac Conroy, Dave Helman, and Sherry Lee. I remain grateful to them and the rest of the Cory Hall crowd for making me feel welcome and sparing me some space in front of a workstation.

I thank my parents for their unfailing love, support, and encouragement throughout my student career. Their prayers for me are truly appreciated. I also thank my in-laws for their kindness and for their patience with my nocturnal habits during these last difficult months.

Finally and most importantly, my thanks and love to Julie, who means everything to me.

This work was supported by grants from NSF and ARPA (Contract MP-9117724), Digital Equipment Corporation, and IBM. Integrated circuit fabrication was provided by MOSIS.

## Contents

| 1 | Inti                            | oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15                                            |

|---|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

|   | 1.1                             | An Image Processing System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 15                                            |

|   | 1.2                             | Associative Memories and Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 17                                            |

|   | 1.3                             | Comparison to Other Image Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 19                                            |

|   | 1.4                             | Organization of Thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 20                                            |

| 2 |                                 | Integrated Associative Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 23                                            |

|   | 2.1                             | Word Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 23                                            |

|   | 2.2                             | Interconnect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>28</b>                                     |

|   |                                 | 2.2.1 The Rectangular Mesh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 28                                            |

|   |                                 | 2.2.2 Asynchronous and Reconfigurable Communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 30                                            |

|   | 2.3                             | Response Resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 34                                            |

|   |                                 | 2.3.1 Chains for Prioritizing and Counting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 34                                            |

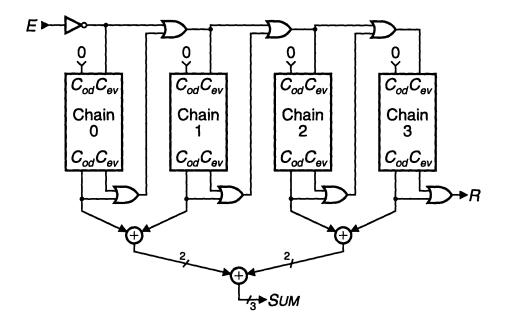

|   |                                 | 2.3.2 Prioritization with Multiple Chains                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 36                                            |

|   | 2.4                             | System Organization and Image I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 37                                            |

|   | 2.5                             | Controller Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 39                                            |

|   | 2.6                             | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 41                                            |

| 3 | Ass                             | ociative Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 45                                            |

|   | 3.1                             | Content Addressable Memory Cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 45                                            |

|   |                                 | 3.1.1 Static Cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 46                                            |

|   |                                 | 3.1.2 Dynamic Trit Cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 48                                            |

|   | 3.2                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 40                                            |

|   | 0.4                             | A Dynamic Associative Processor Cell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 40<br>52                                      |

|   | 3.2<br>3.3                      | A Dynamic Associative Processor Cell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                               |

|   |                                 | Match Sensing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 52                                            |

|   |                                 | Match Sensing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 52<br>56                                      |

|   |                                 | Match Sensing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 52<br>56<br>58                                |

|   | 3.3                             | Match Sensing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 52<br>56<br>58<br>59                          |

| 4 | 3.3<br>3.4<br>3.5               | Match Sensing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 52<br>56<br>58<br>59<br>61                    |

| 4 | 3.3<br>3.4<br>3.5               | Match Sensing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 52<br>56<br>58<br>59<br>61<br>63              |

| 4 | 3.3<br>3.4<br>3.5<br>The        | Match Sensing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 52<br>56<br>58<br>59<br>61<br>63<br><b>65</b> |

| 4 | 3.3<br>3.4<br>3.5<br>The<br>4.1 | Match Sensing .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . | 52<br>56<br>58<br>59<br>61<br>63<br><b>65</b> |

|              |                      | 70              |

|--------------|----------------------|-----------------|

|              | 4.4 Summary          | 72              |

| 5            | Experimental Results | 73              |

|              | -                    | 73              |

|              | 8                    | 75              |

|              |                      | 77              |

|              |                      | 78              |

|              | •                    | 81              |

|              |                      | 82              |

|              | -                    | 85              |

|              |                      | 87              |

|              |                      | 90              |

| 6            | Conclusion           | 93              |

| U            |                      | 93<br>93        |

|              |                      | 93<br>94        |

|              |                      | 94              |

|              | References           | 97              |

| Α            | Chip Data 10         | 07              |

|              | -                    | 07              |

|              | -                    | 12              |

| в            | MTL Process Data 1   | 15              |

| D            |                      | 10              |

| С            | Layout Design Rules1 | 17              |

| D            | Cell Design 12       | 21              |

| $\mathbf{E}$ | Schematic Diagrams   | 25              |

| 1.1          |                      | <b>2</b> 6      |

|              |                      | $\frac{20}{29}$ |

|              | 5                    | $\frac{1}{32}$  |

|              |                      | 35              |

|              |                      | $\frac{30}{46}$ |

|              |                      | 52              |

|              |                      | 62              |

| L.           |                      | 65              |

| $\mathbf{F}$ |                      | оэ<br>65        |

|              |                      | 05<br>66        |

|              | F.2 Arithmetic       | 00              |

# List of Figures

| 1.1  | Image processing system using array of associative processing elements    | 16 |

|------|---------------------------------------------------------------------------|----|

| 1.2  | RAM read and CAM search operations                                        | 17 |

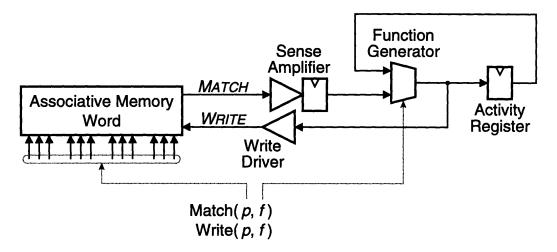

| 1.3  | Associative processing element                                            | 18 |

| 2.1  | Associative processing element with direct match-write feedback           | 24 |

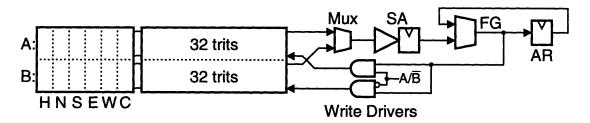

| 2.2  | Associative processing element with improved word logic                   | 25 |

| 2.3  | Processing element used on integrated associative processor               | 27 |

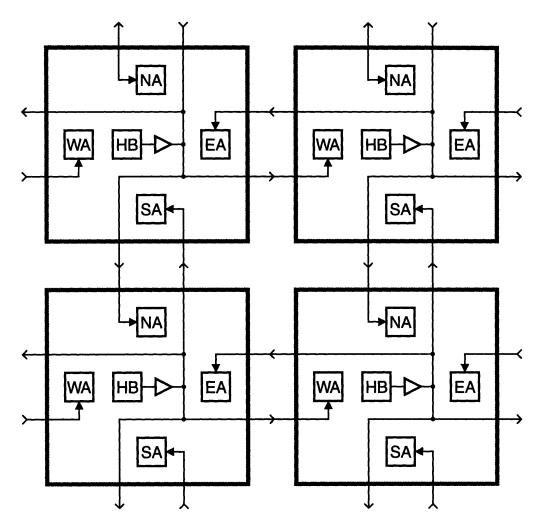

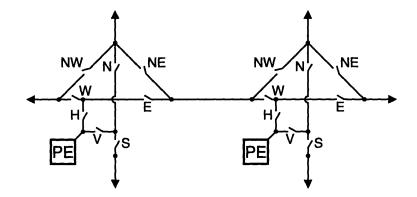

| 2.4  | Four processing elements with mesh connections                            | 29 |

| 2.5  | Polymorphic torus network                                                 | 31 |

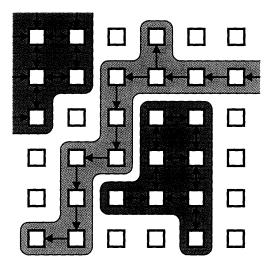

| 2.6  | Gated Connection Network switches for two PEs                             | 31 |

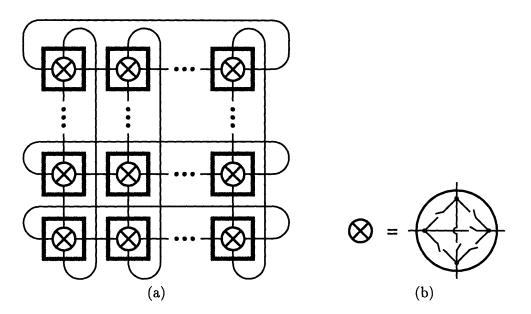

| 2.7  | Net configuration with two coteries and a unidirectional path             | 32 |

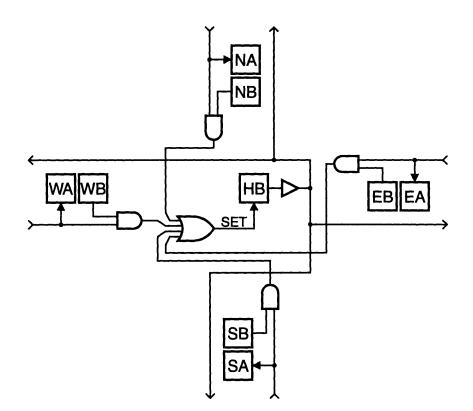

| 2.8  | Asynchronous reconfigurable mesh logic                                    | 33 |

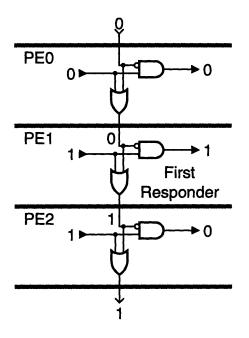

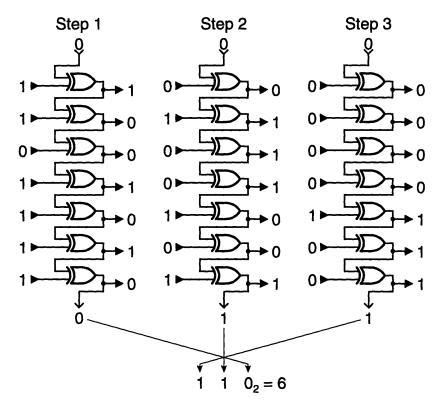

| 2.9  | Prioritizing chain of OR gates                                            | 35 |

|      | Counting responders with an XOR chain                                     | 35 |

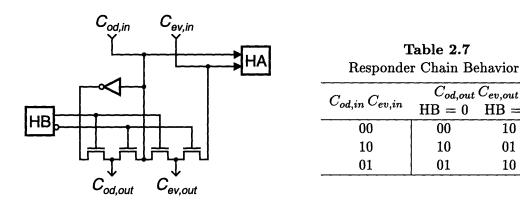

| 2.11 | Pass transistor logic for responder chain                                 | 36 |

|      | Response resolver with four chains                                        | 37 |

| 2.13 | Responder prioritization tree                                             | 38 |

| 2.14 | Multi-chip system organization                                            | 38 |

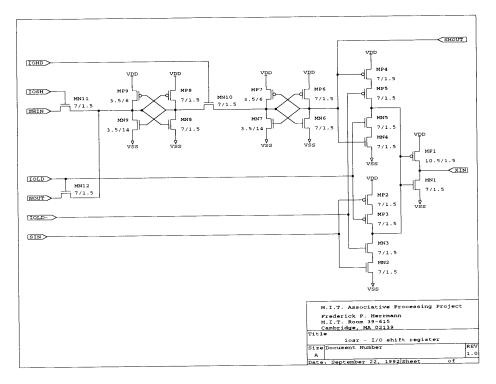

|      | Shift register for image I/O                                              | 40 |

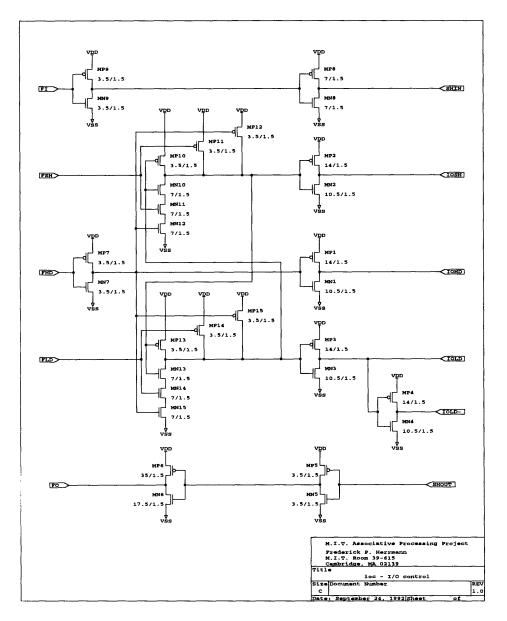

| 2.16 | System control path                                                       | 42 |

| 3.1  | First MOS CAM cell, by Igarashi et al.                                    | 46 |

| 3.2  | Improved static CAM cell by Kadota et al                                  | 47 |

| 3.3  | Static CAM cell by Ogura et al.                                           | 48 |

| 3.4  | Static CAM cell by Koo                                                    | 49 |

| 3.5  | Five-transistor dynamic CAM cell by Mundy                                 | 49 |

| 3.6  | Capacitance model of Mundy cell storage node                              | 51 |

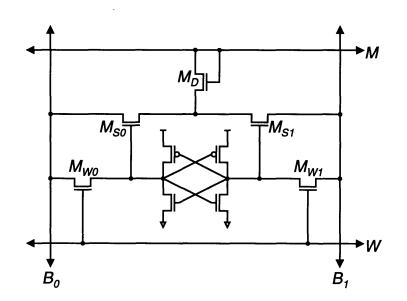

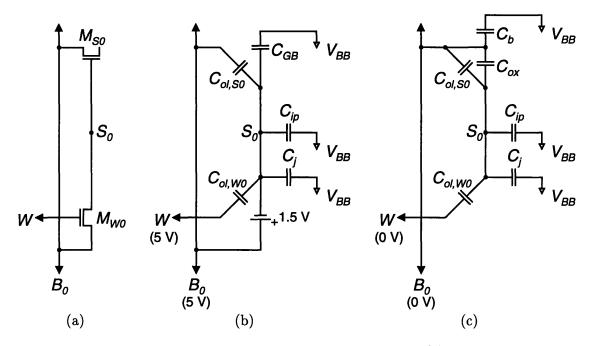

| 3.7  | Improved dynamic CAM cell using stacked capacitors                        | 52 |

| 3.8  | Improved dynamic CAM cell with crossed bit lines                          | 52 |

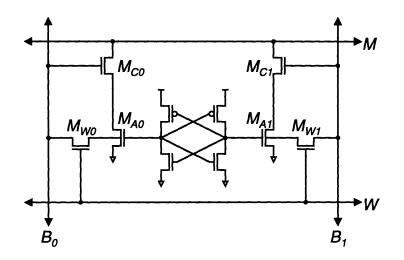

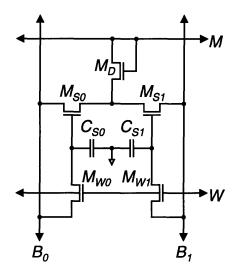

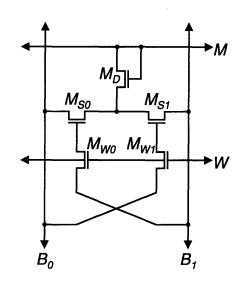

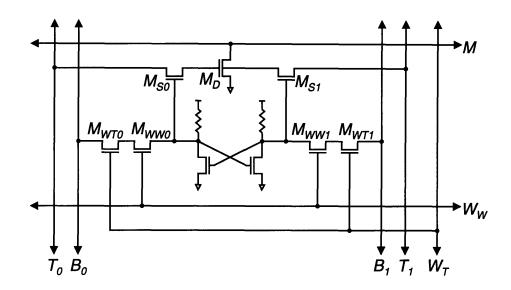

| 3.9  | Static associative processor cell                                         | 54 |

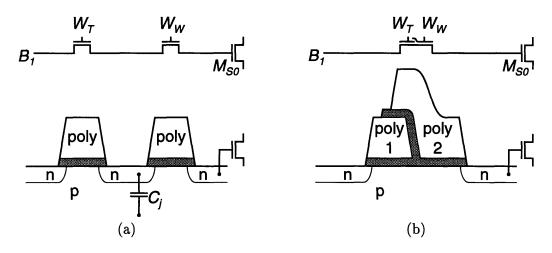

|      | Cross sections of write transistors                                       | 55 |

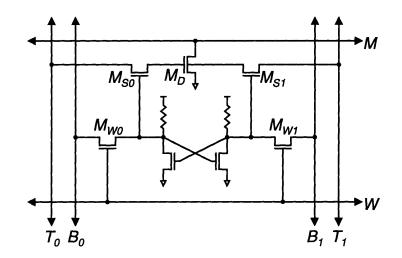

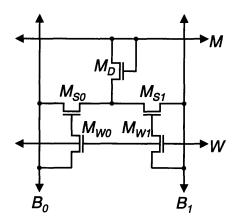

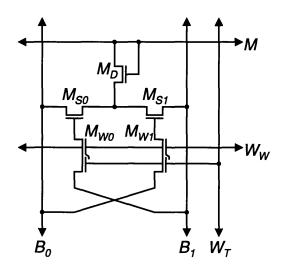

|      | New dynamic associative processor cell                                    | 55 |

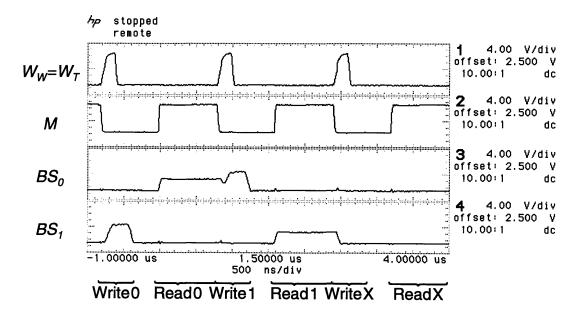

|      | Oscilloscope output of match operation                                    | 57 |

| 3.13 | Oscilloscope output of read operation                                     | 57 |

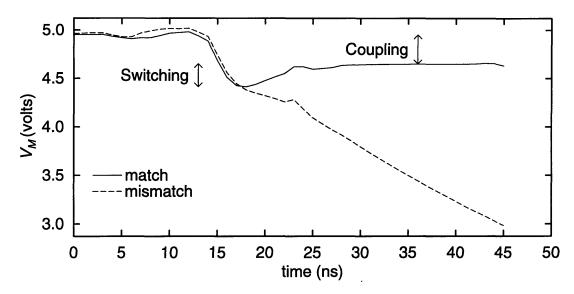

| 3.14 | Simulated match line potential with switching and coupling noise $\ldots$ | 58 |

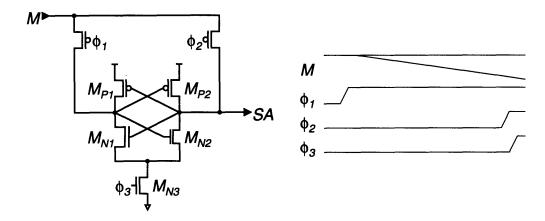

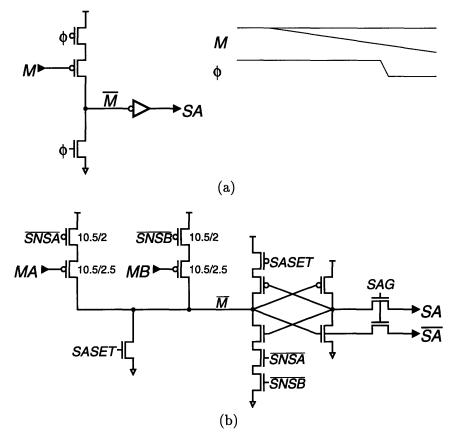

| 3.15       | Time-differential sense amplifier                          | • |   | • |   | <br>    |            | 59  |

|------------|------------------------------------------------------------|---|---|---|---|---------|------------|-----|

| 3.16       | Single-ended sense amplifier                               |   |   |   |   | <br>    |            | 60  |

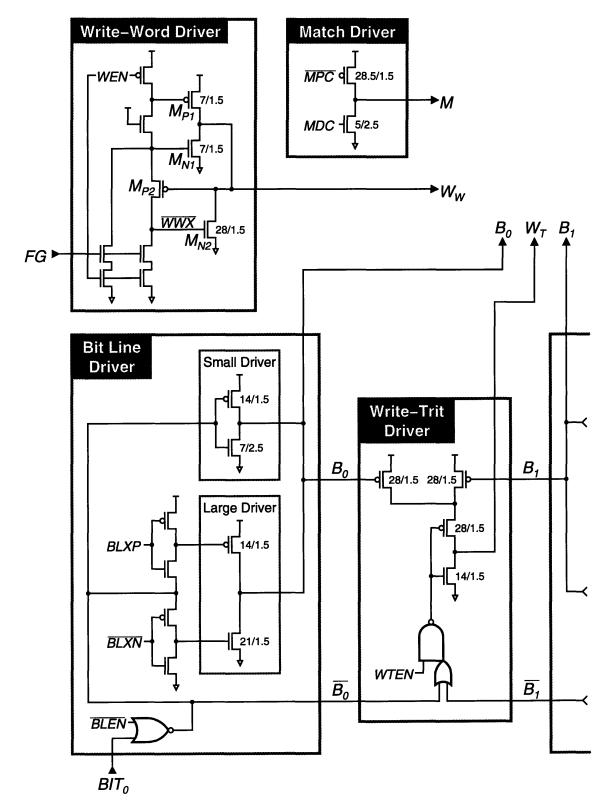

| 3.17       | Array driver circuits                                      |   |   |   |   | <br>    | . <b>.</b> | 62  |

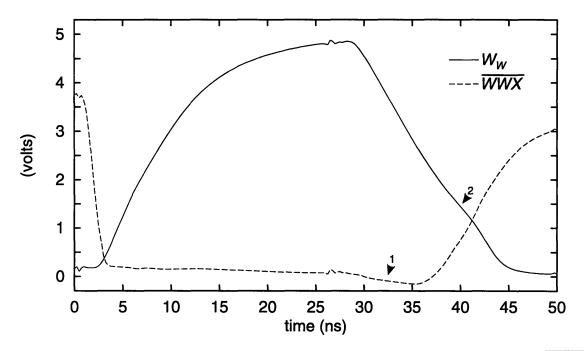

|            | Simulated write-word line potential                        |   |   |   |   |         |            |     |

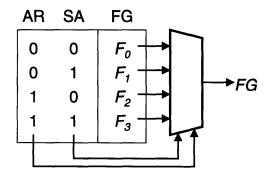

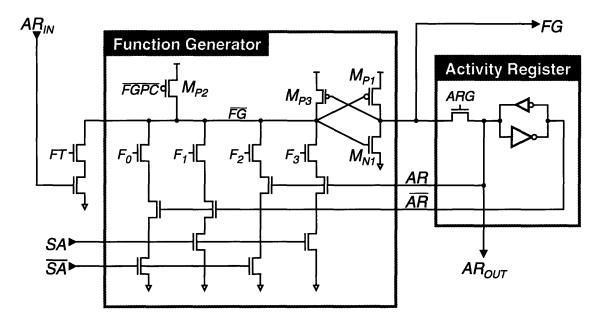

| 4.1        | Function generator as truth table selector                 |   |   |   |   | <br>    |            | 65  |

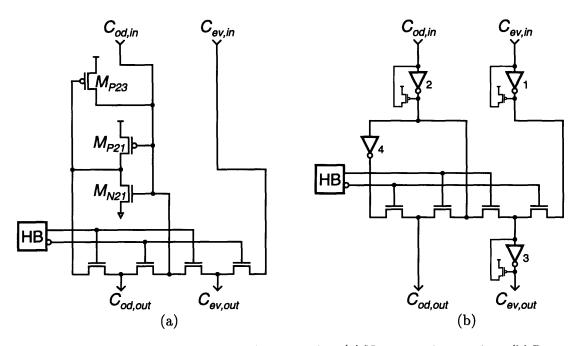

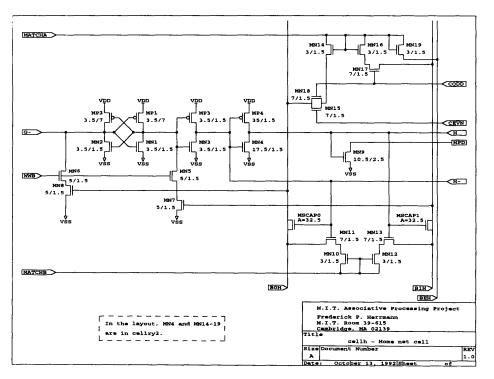

| 4.2        | Circuit implementation of word logic                       |   |   |   |   |         |            |     |

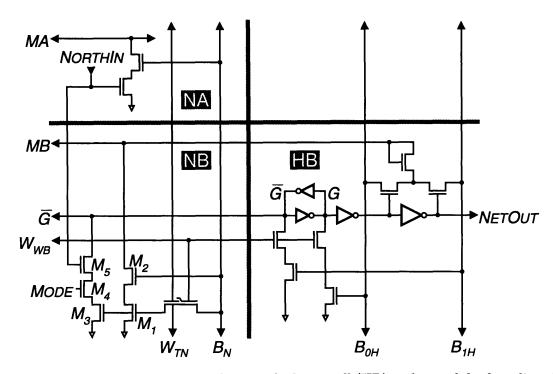

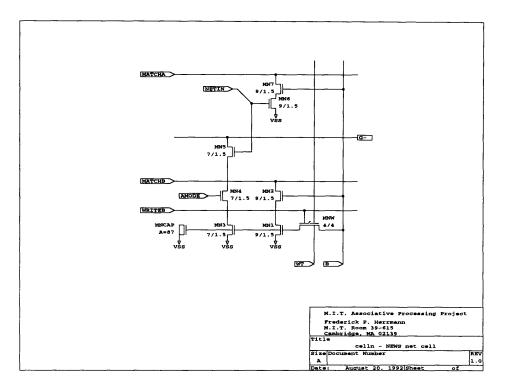

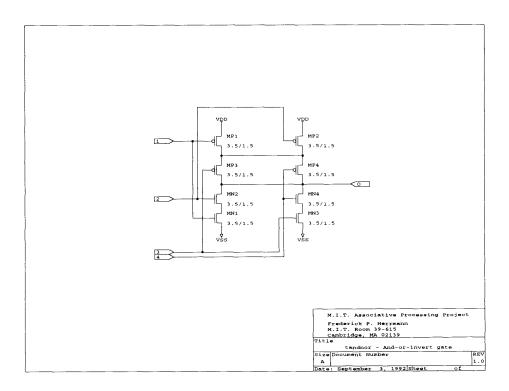

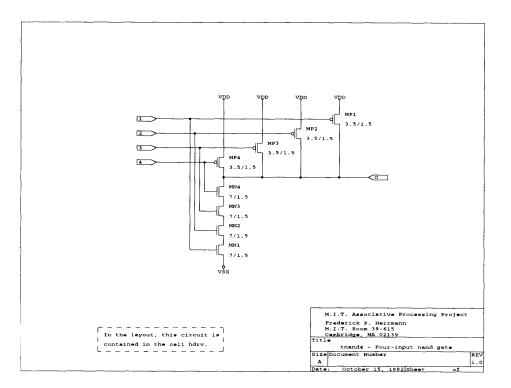

| 4.3        | Network cell circuits                                      |   |   |   |   |         |            |     |

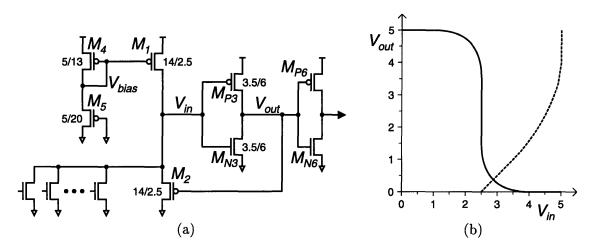

| 4.4        | Wired-OR circuit for some/none response resolution         |   |   |   |   |         |            |     |

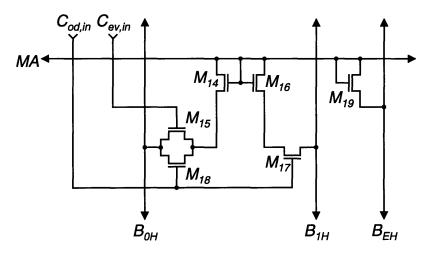

| 4.5        | Responder chain pass transistor circuits                   |   |   |   |   |         |            |     |

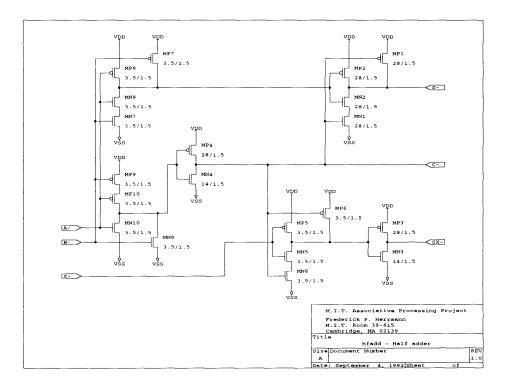

| 4.6        | Circuit diagram of responder cell HA                       |   |   |   |   |         |            |     |

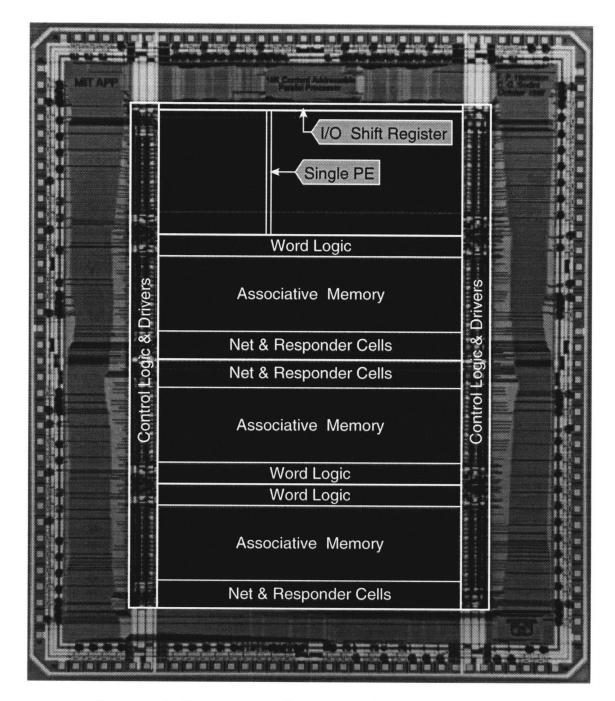

| 5.1        | Photomicrograph of integrated associative processor        |   |   |   |   | <br>    |            | 74  |

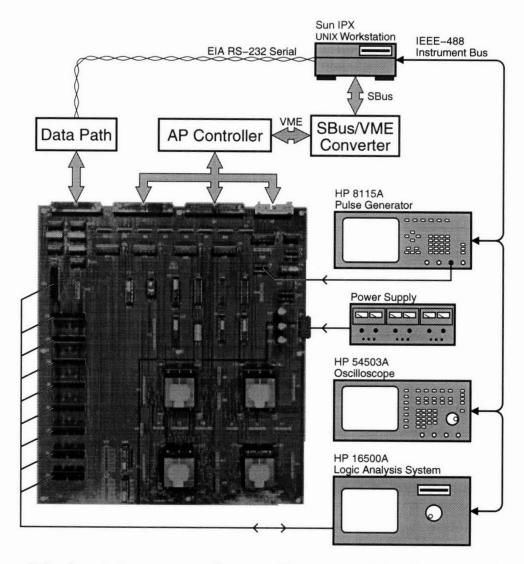

| 5.2        | Associative processor demonstration system                 |   |   |   |   |         |            |     |

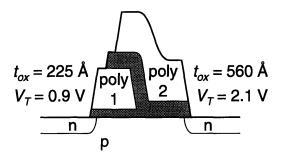

| 5.3        | Asymmetrical dual-gate device                              |   |   |   |   |         |            |     |

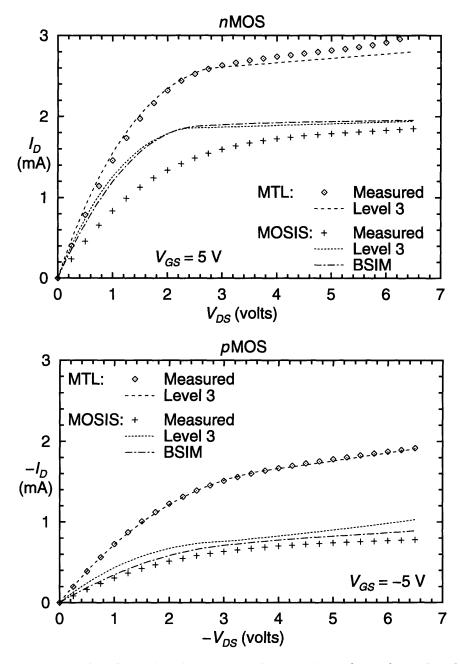

| 5.4        | Measured and simulated transistor characteristics          |   |   |   |   |         |            |     |

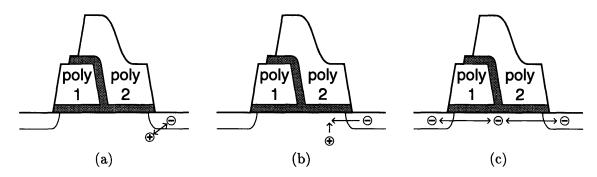

| 5.5        | Non-ideal charge transfer mechanisms                       |   |   |   |   |         |            |     |

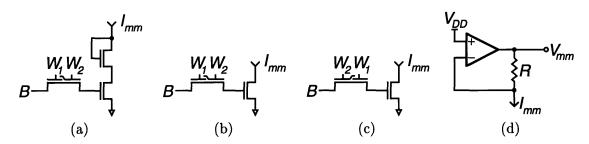

| 5.6        | Charge storage test circuits                               |   |   |   |   |         |            |     |

| 5.7        | Oscilloscope output of leakage test                        |   |   |   |   |         |            |     |

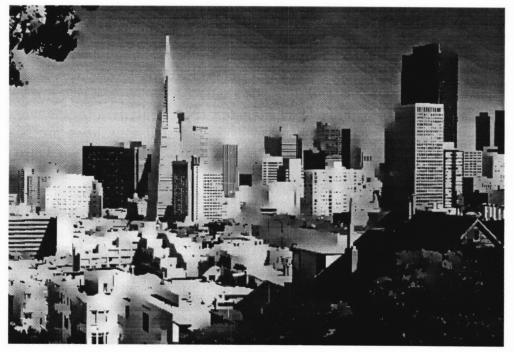

| 5.8        | Original and processed images of San Francisco skyline     |   |   |   |   |         |            |     |

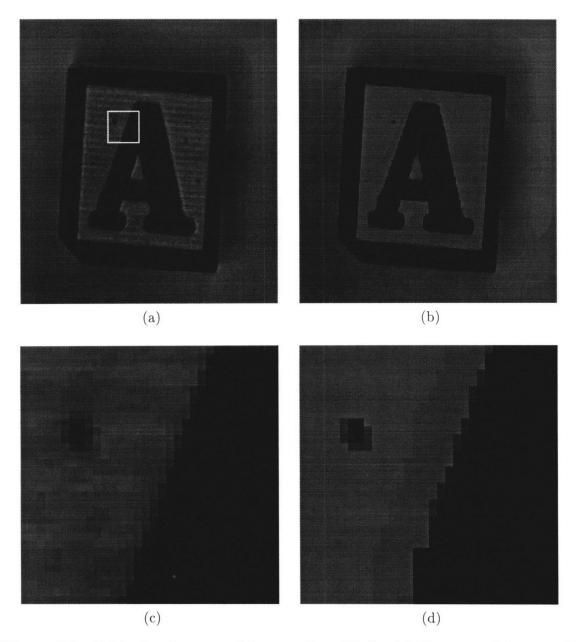

| 5.9        | Original and processed images of toy block                 |   |   |   |   |         |            |     |

| A.1        | Pin placement diagram                                      |   |   |   |   |         |            | 108 |

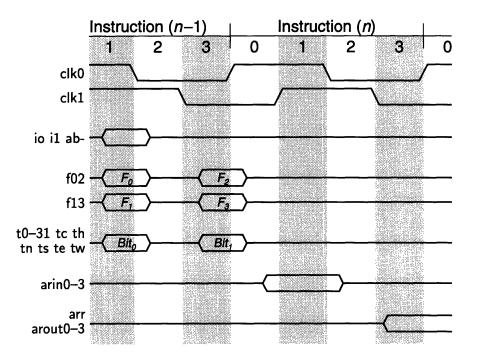

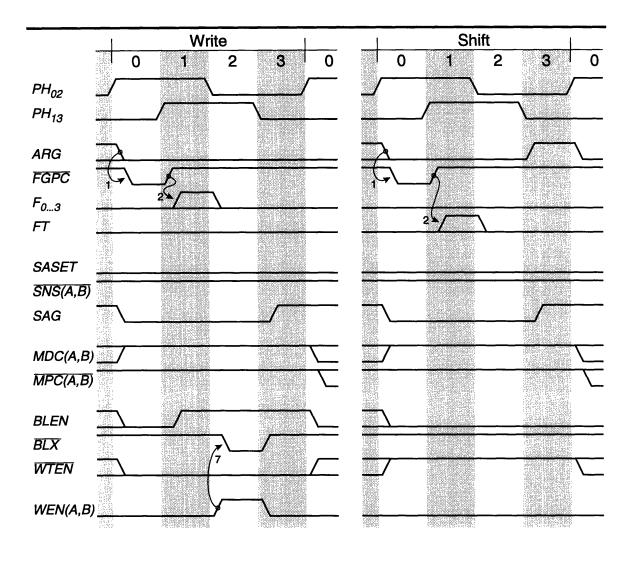

| A.2        | Instruction timing diagram                                 |   |   |   |   |         |            |     |

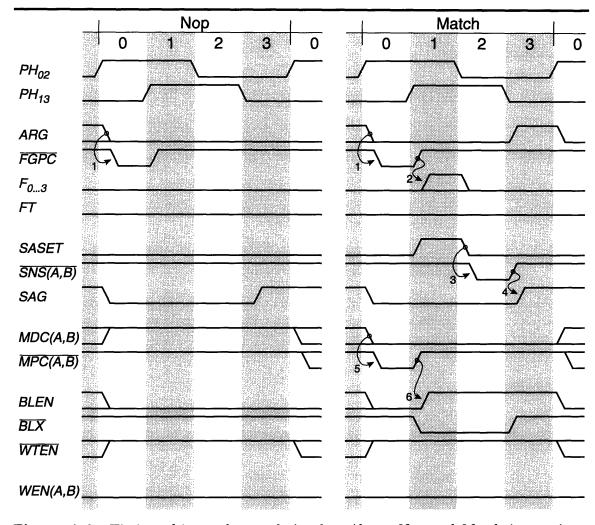

| A.2<br>A.3 | Timing of internal control signals                         |   |   |   |   |         |            |     |

| 11.0       |                                                            |   |   |   |   |         |            |     |

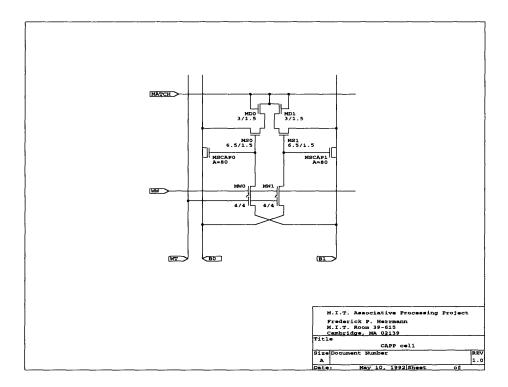

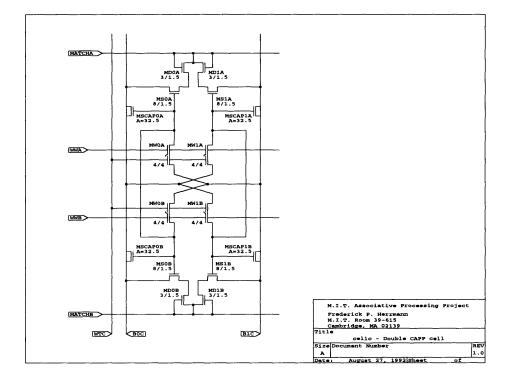

| D.1        | Dynamic associative processor cell schematic $\ldots$ .    |   |   |   |   |         |            |     |

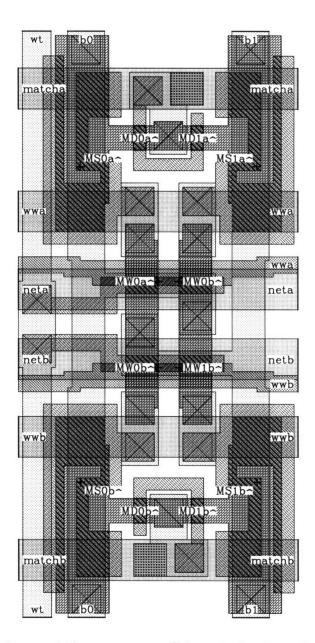

| D.2        | Dynamic associative processor cell layout                  | • | • | • | • | <br>•   | •          | 123 |

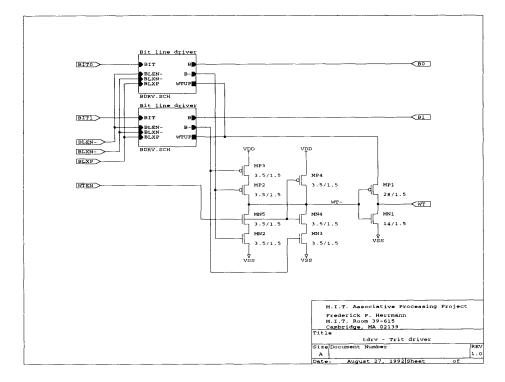

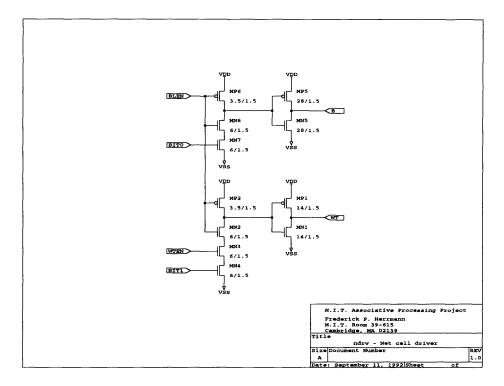

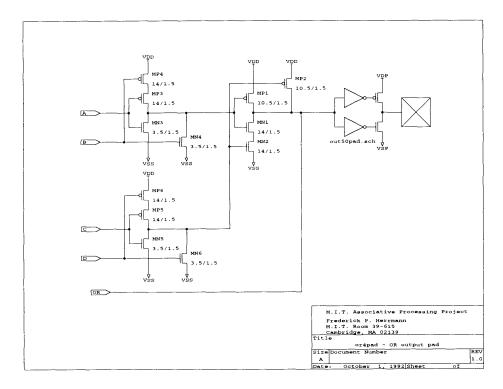

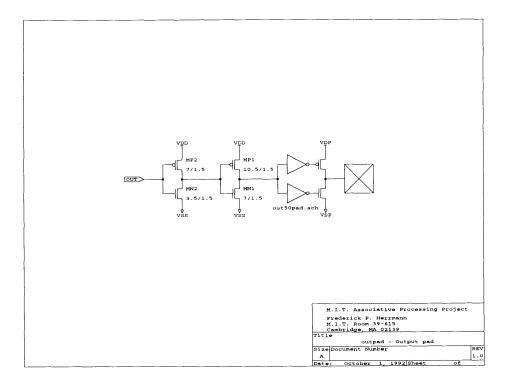

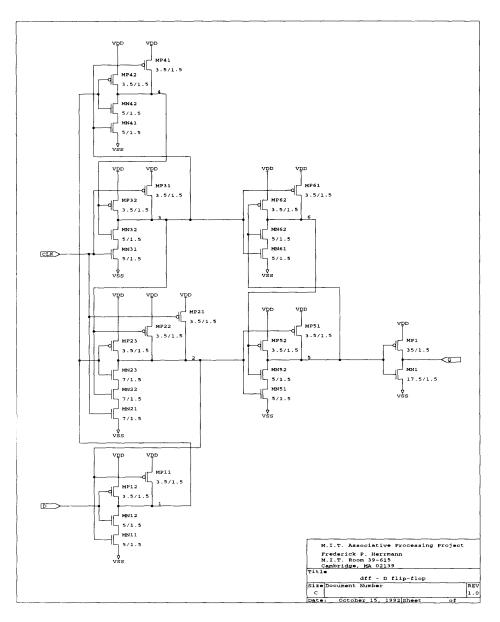

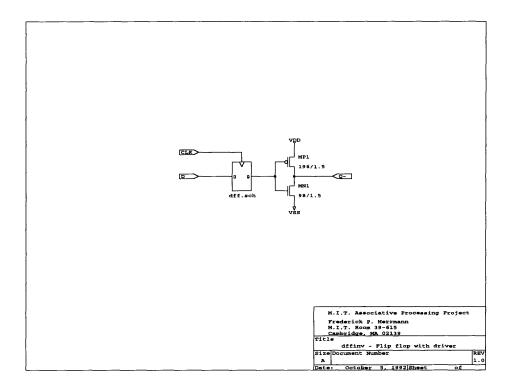

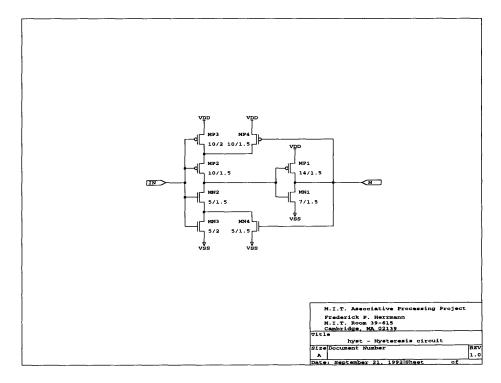

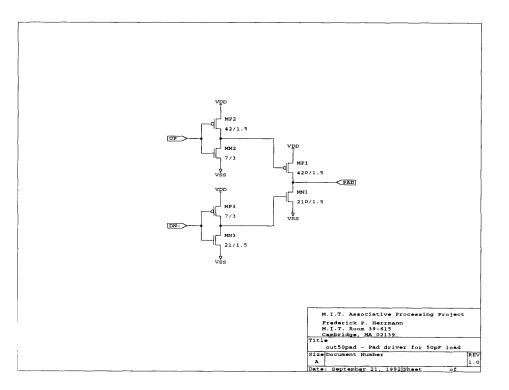

| E.1        | Trit column driver                                         | • |   | • | • | <br>•   | •          |     |

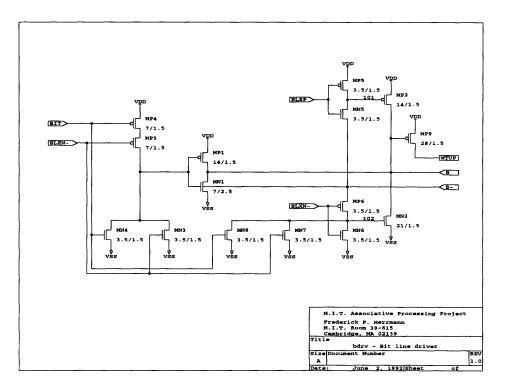

| E.2        | Bit line driver                                            | • |   | • |   | <br>•   | •          | 127 |

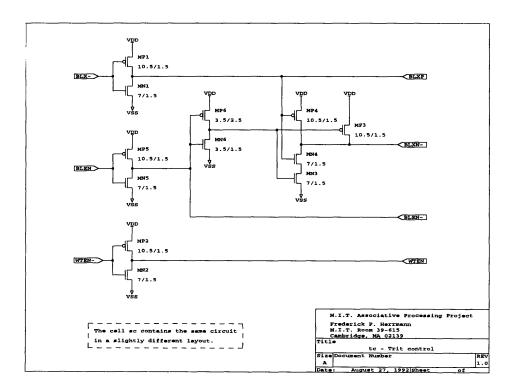

| E.3        | Trit control                                               |   |   |   |   |         |            | 127 |

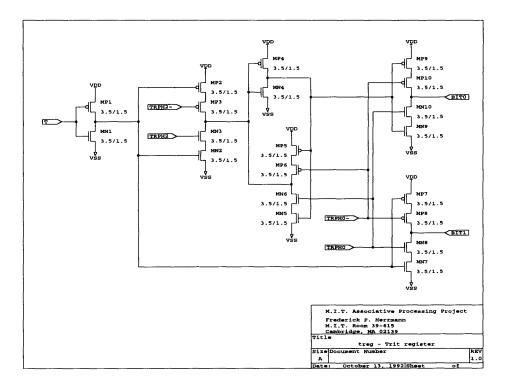

| E.4        | Trit register                                              |   | • | • | • | <br>•   | •          | 128 |

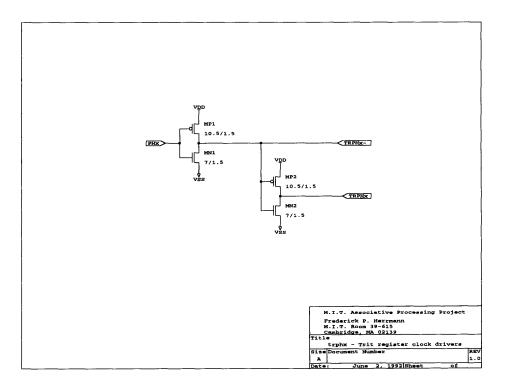

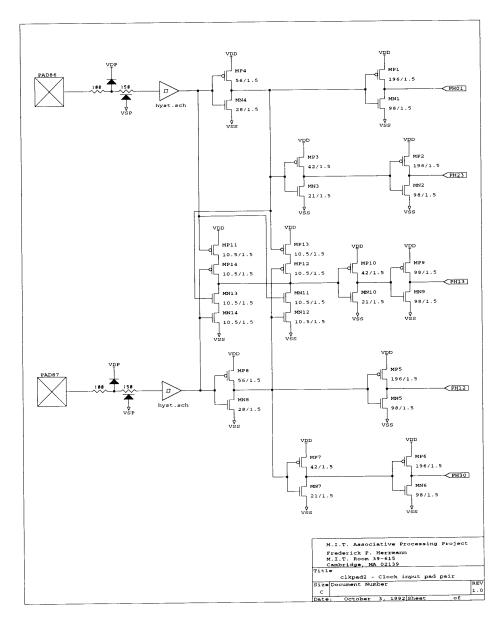

| E.5        | Trit register clock drivers                                | • | • | • |   | <br>•   | •          | 128 |

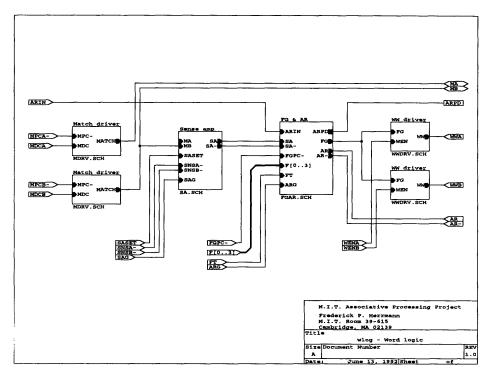

| E.6        | Word logic                                                 | • | • | • |   | <br>•   | •          | 129 |

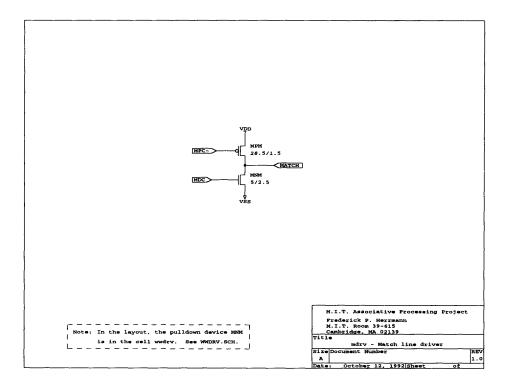

| E.7        | $Match line driver \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $ | • | • | • | • | <br>•   | •          | 130 |

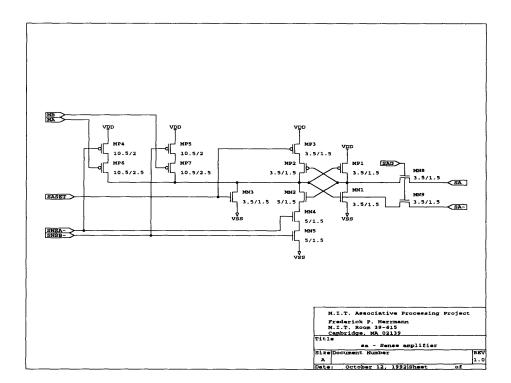

| E.8        | Sense amplifier                                            | • |   | • | • | <br>•   | •          | 130 |

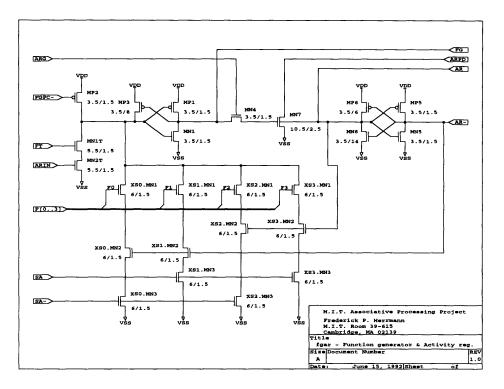

| E.9        | Function generator and activity register                   | • |   |   | • | <br>•   | •          | 131 |

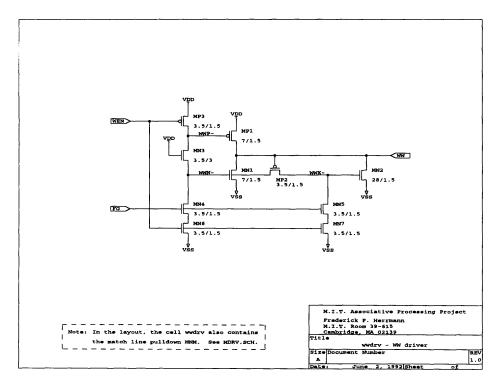

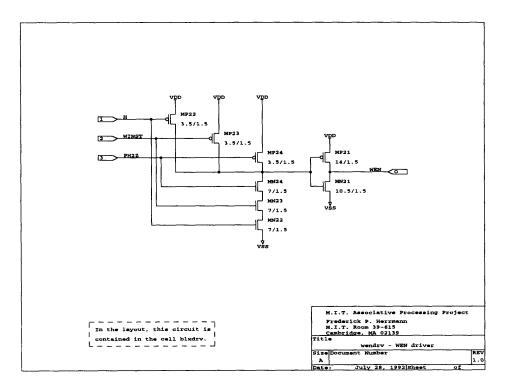

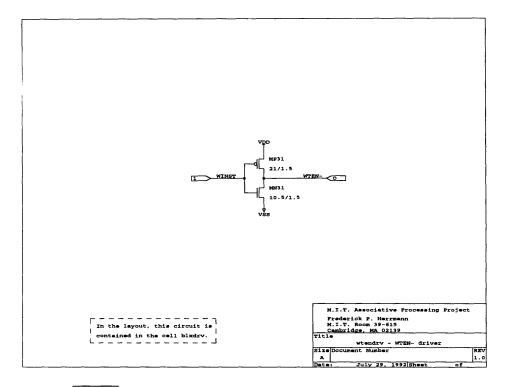

|            | Write-word driver                                          |   |   |   |   |         |            | 131 |

| E.11       | Carry cell                                                 | • | • | • | • | <br>•   |            | 132 |

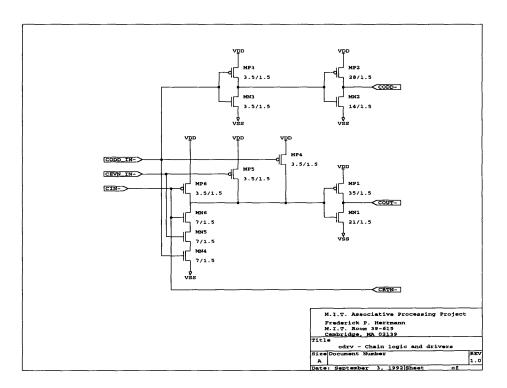

|            | Network direction cell pair                                |   |   |   |   |         |            | 133 |

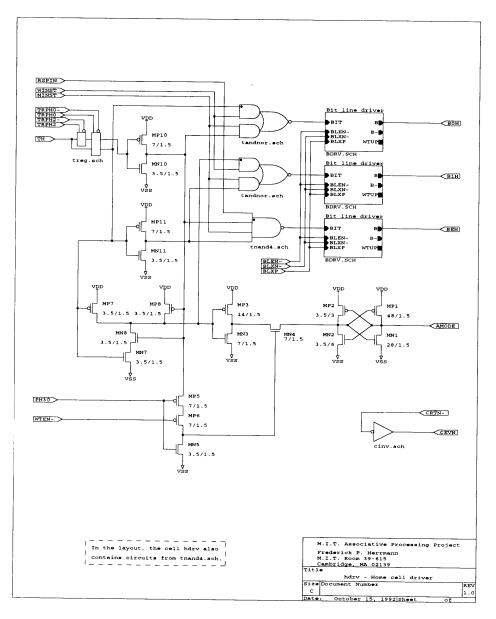

| E.13       | Home cell pair                                             | • | • |   | • | <br>•   | • •        | 133 |

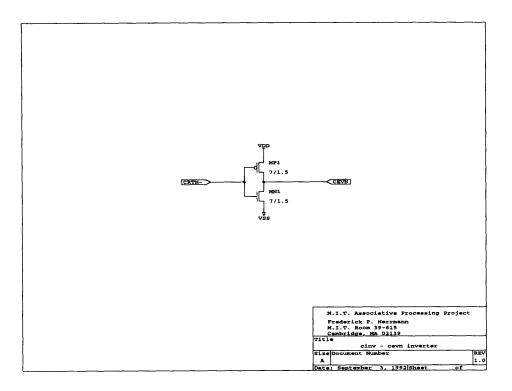

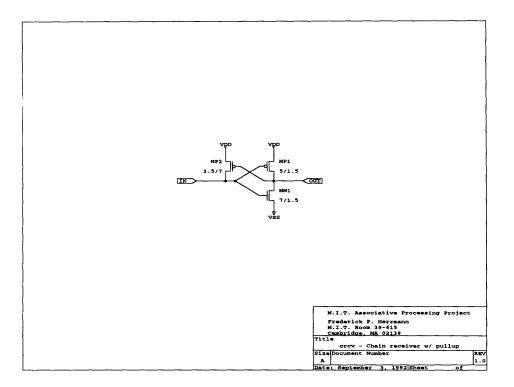

|            | Responder chain                                            |   |   |   |   |         |            | 134 |

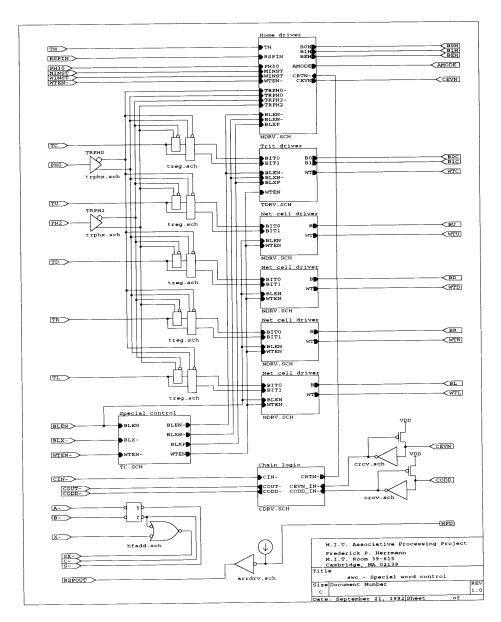

|            | Word logic control                                         |   |   |   |   |         |            | 135 |

| E.16       | Activity register enable driver                            | • | • | • | • | <br>· • | • •        | 136 |

| E.17 | $ARG$ enable driver $\ldots \ldots \ldots$ | 36 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| E.18 |                                                                                                                                                            | 37 |

| E.19 | AR return driver                                                                                                                                           | 37 |

| E.20 |                                                                                                                                                            | 38 |

| E.21 |                                                                                                                                                            | 38 |

| E.22 |                                                                                                                                                            | 39 |

| E.23 |                                                                                                                                                            | 39 |

|      |                                                                                                                                                            | 40 |

|      |                                                                                                                                                            | 40 |

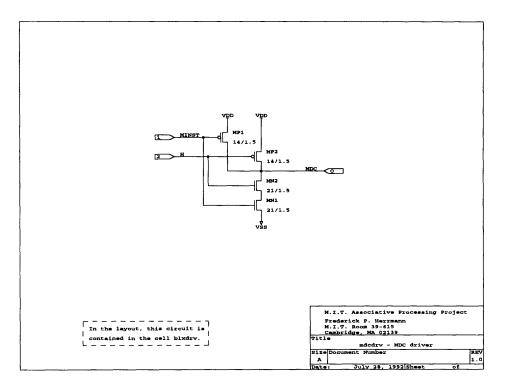

| E.26 | $MDC$ driver $\ldots \ldots \ldots$        | 41 |

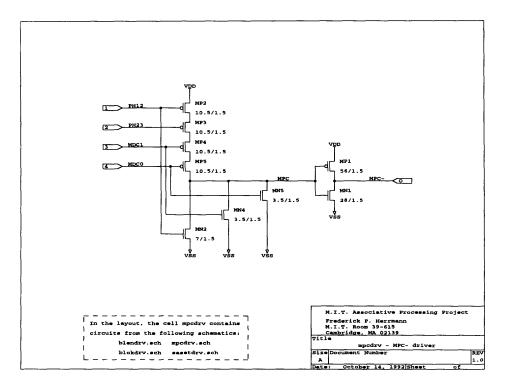

| E.27 |                                                                                                                                                            | 41 |

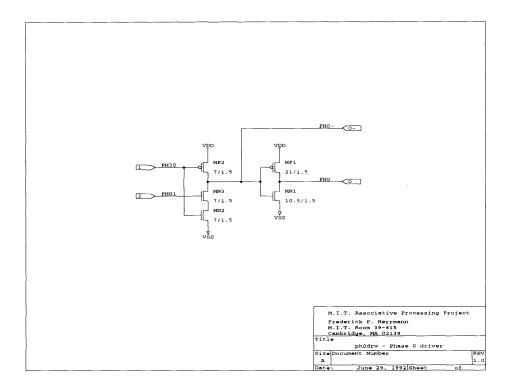

| E.28 |                                                                                                                                                            | 42 |

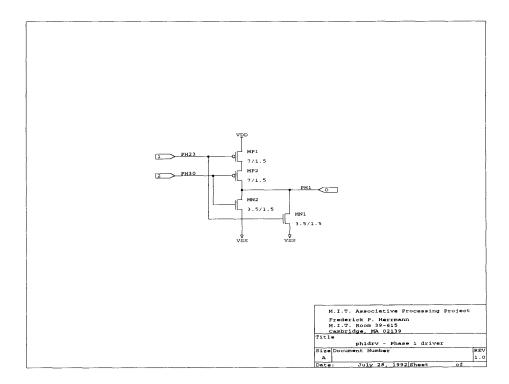

| E.29 | Phase 1 clock driver                                                                                                                                       | 42 |

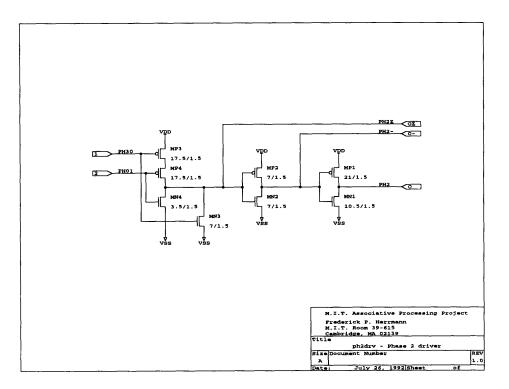

|      |                                                                                                                                                            | 43 |

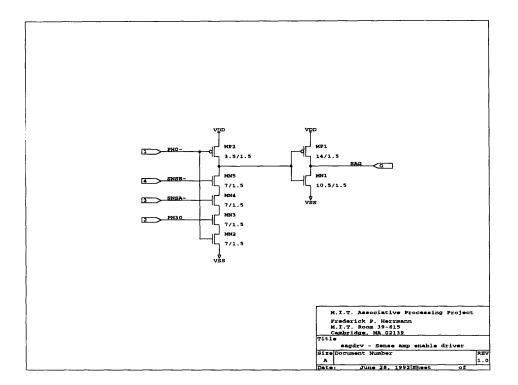

| E.31 | Sense amplifier enable driver                                                                                                                              | 43 |

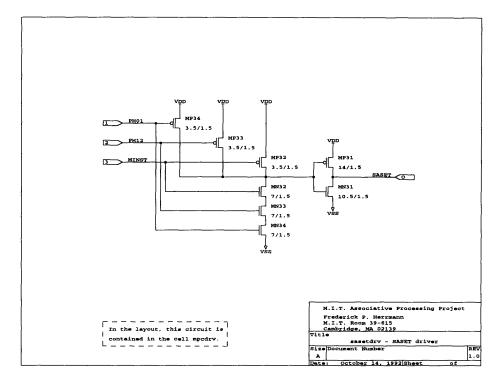

|      |                                                                                                                                                            | 44 |

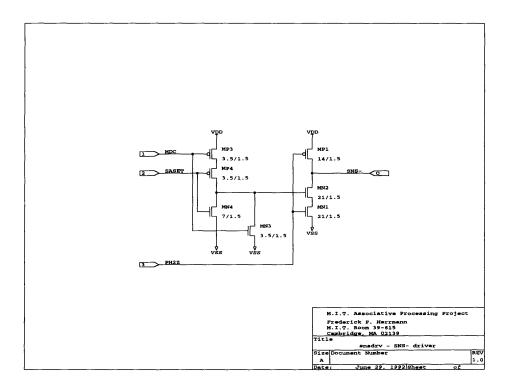

|      |                                                                                                                                                            | 44 |

|      |                                                                                                                                                            | 45 |

|      |                                                                                                                                                            | 45 |

|      |                                                                                                                                                            | 46 |

| E.37 |                                                                                                                                                            | 47 |

|      |                                                                                                                                                            | 48 |

|      |                                                                                                                                                            | 48 |

|      |                                                                                                                                                            | 49 |

|      |                                                                                                                                                            | 49 |

|      |                                                                                                                                                            | 50 |

| E.43 |                                                                                                                                                            | 50 |

|      |                                                                                                                                                            | 51 |

|      |                                                                                                                                                            | 52 |

|      |                                                                                                                                                            | 53 |

|      |                                                                                                                                                            | 53 |

| E.48 | · · · · · · · · · · · · · · · · · · ·                                                                                                                      | 54 |

|      |                                                                                                                                                            | 54 |

|      |                                                                                                                                                            | 55 |

|      | a se                                                                                                                    | 56 |

|      |                                                                                                                                                            | 57 |

|      |                                                                                                                                                            | 57 |

|      |                                                                                                                                                            | 58 |

|      |                                                                                                                                                            | 58 |

| E.56 |                                                                                                                                                            | 59 |

|      |                                                                                                                                                            | 60 |

| E.58 | The second se                                            | 60 |

| E.59 |                                                                                                                                                            | 61 |

| E.60 | Image I/O shift register  |   |  |   |   |  |  |  |  |  |  |  |  | • | 162 |

|------|---------------------------|---|--|---|---|--|--|--|--|--|--|--|--|---|-----|

| E.61 | Image I/O control logic . | • |  | • | • |  |  |  |  |  |  |  |  |   | 163 |

## List of Tables

| 1.1 | Comparison of image processing systems 21                    |

|-----|--------------------------------------------------------------|

| 2.1 | Full-add truth table and transformations                     |

| 2.2 | Full-add procedure                                           |

| 2.3 | The sixteen binary Boolean functions of two inputs           |

| 2.4 | Full-add procedure for improved word logic                   |

| 2.5 | Cycles required for arithmetic operations                    |

| 2.6 | Move-and-add procedure                                       |

| 2.7 | Responder chain behavior                                     |

| 3.1 | Summary of Mundy cell match operation                        |

| 3.2 | Charge at Mundy cell storage node                            |

| 3.3 | Summary of representative MOS CAM cells                      |

| 3.4 | Circuit and process data for cell test chip                  |

| 4.1 | HB cell write behavior                                       |

| 4.2 | HA cell match behavior                                       |

| 5.1 | Measured and simulated delays                                |

| 5.2 | Results of charge storage experiments on test circuits 83    |

| 5.3 | Results of charge storage experiments on the memory array 86 |

| 5.4 | Simulated execution times for smoothing and segmentation 90  |

| 5.5 | Associative processor chip specifications                    |

| A.1 | Operation codes                                              |

| A.2 | Trit encoding                                                |

|     |                                                              |

| B.1 | Device parameters                                            |

| B.2 | Junction capacitance                                         |

| B.3 | Interconnect resistance                                      |

| B.4 | Interconnect capacitance                                     |

| B.5 | Extensions for perimeter capacitance 116                     |

| F.1 | Ternary column refresh procedure                             |

| F.2 | Binary column refresh procedure                              |

| F.3 | Non-destructive addition procedure                           |

.

| F.4 | Scalar addition procedure  |  |  | • |  | • | • |  |  | • | • | • |   |   | • |  | 167 |

|-----|----------------------------|--|--|---|--|---|---|--|--|---|---|---|---|---|---|--|-----|

| F.5 | Absolute value procedure . |  |  | • |  |   |   |  |  |   | • | • | • | • |   |  | 167 |

## Chapter 1

### Introduction

Associative processors are parallel computing machines that perform both memory and processor functions in a single unit. They are therefore somewhat unconventional, since the two components are usually viewed as being completely separate. This perception affects the way computers are understood at every level, from design and manufacturing up through architecture and programming. In the field of circuit design, for example, memory and processor specialists have segregated themselves into distinct subdisciplines. Even in companies that make their primary business in processors, it is common practice to have one team of expert memory designers develop on-chip caches or control stores for several products. These memory subsystems are then "thrown over the wall" for other groups to incorporate into their own chip designs.

Given that memory subsystems can be integrated onto processor chips, it is natural to ask whether processing functions could be added to memory chips. This idea is especially attractive to memory designers, who look to the precedent established by video memories [1] and see that the addition of a few shift registers can turn a price-competitive commodity product into a highly profitable specialty part. Video memories represent an incremental approach to smart memory, but processor and memory can be combined more effectively when starting from scratch. Original designs afford greater flexibility to implement processor functions in the memory design style, which emphasizes large arrays of hand-crafted circuits. Because memory designers optimize each transistor of their key circuits, they must repeat these circuits many times over in order to justify their attention to detail. The design style is well matched to the fine-grained organization of an associative processor, in which every memory word acts as one processing element (PE) of a highly parallel system.

### 1.1 An Image Processing System

In the early years of associative processing, the pioneers of the field recognized picture processing as a promising source of applications for their new machines [2, 3]. Many image processing problems are rich in parallelism, with thousands of pixels receiving

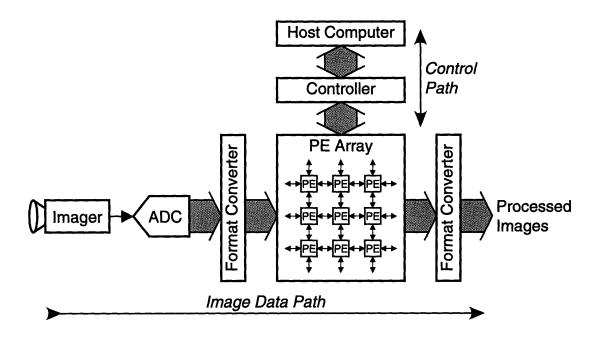

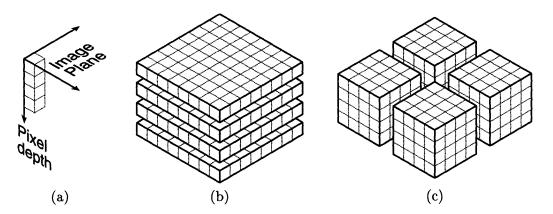

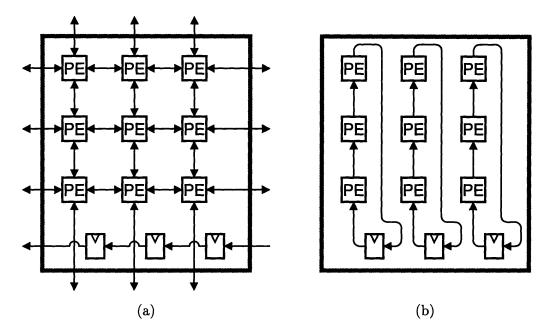

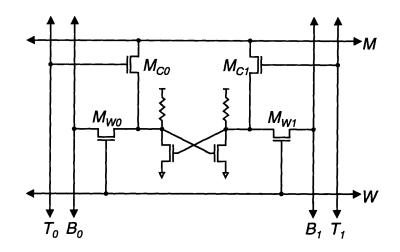

Figure 1.1: Image processing system using array of associative processing elements.

identical processing steps. The low precision of image data (typically 8-bit integers) and the often modest computational requirements at each pixel match the capabilities of very simple associative processing elements. Modern integrated circuit technology provides the density necessary to produce large arrays at low cost, with each PE assigned to a single pixel.

Similar arguments have been made in favor of analog circuits for early machine vision [4, 5]. Parallel arrays of relatively simple circuits can achieve adequate precision for many applications, and analog circuits have desirable speed, power, and density characteristics. The only drawback to these systems is their lack of generality; most are designed to solve only a single problem [6, 7, 8]. In contrast, massively parallel supercomputers provide all the flexibility of programmable digital systems, but these million-dollar machines are overkill for all but a few select applications. Associative processors occupy a middle ground, achieving massive parallelism and appropriately fine granularity while retaining the integration benefits of the device-intensive design style.

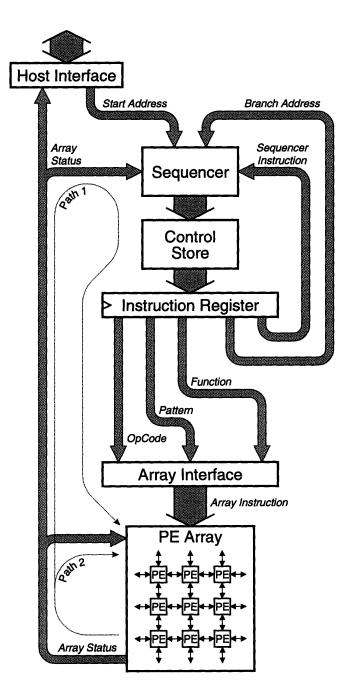

Figure 1.1 shows a block diagram of an image processing system based on an associative processor. A two-dimensional network connects the processing elements and also handles image input and output. Image data flow from left to right in the diagram, while the vertical control path carries instructions from the host computer to the array. Several conversion steps are necessary to prepare images for processing. An imager, such as a video camera, first converts from the (typically optical) acquisition domain to the analog electronic domain. The analog-to-digital converter then produces a digital signal representation, and a format converter reorders the image bits before loading them into the associative processor. A similar format converter may be necessary at the output, depending on the destination of the processed images.

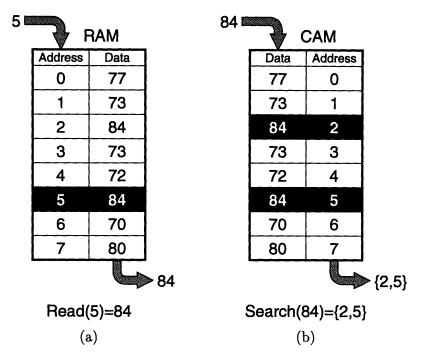

Figure 1.2: RAM read (a) and CAM search (b) operations.

Because the system of Fig. 1.1 requires very little interaction between the data and control paths, the design and construction tasks can be cleanly partitioned into manageably sized projects. This thesis concentrates on the design and integrated circuit implementation of the associative processor array. As of this writing, the control path is complete and the remainder of the data path is in the early planning stages. When the entire project is finished, the three components will constitute a coprocessor system for accelerating image processing tasks. It is believed that something very similar to this demonstration system may one day be standard equipment on workstations and personal computers, just as digital signal processing chips are now used for audio applications.

### **1.2** Associative Memories and Processors

If one wanted to define associative memory as broadly as possible, one could go so far as to claim that all memories are actually associative. The familiar random access memory (RAM), for example, is a special case in which each word is partitioned into separate address and data fields. As shown in Fig. 1.2(a), the read operation selects the word matching an input address (5), and reports the contents (84) of its associated data field. Each RAM address is hard-wired with a unique value corresponding to its physical location. It is therefore guaranteed that exactly one word will be selected for any valid input address. In contrast, a content addressable memory (CAM) can examine many words simultaneously. Figure 1.2(b) shows a CAM in which two words

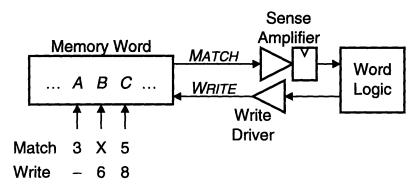

Figure 1.3: Associative processing element.

match the input value, and so two address are produced. Because the CAM's data contents are not hard-wired to predetermined values, it is not constrained to match only a single word.

There is an obvious symmetry between the RAM and CAM operations. Both compare an input value to a search field, and both produce output from a result field. Since all memories perform some restricted version of this associative match operation, all could reasonably be described as associative memories. Such a definition would be uselessly inclusive, however, and so the term *associative memory* is usually taken to exclude RAMs and other memories without modifiable search fields. Established usage accepts *content addressable* as a near synonym for *associative*, although the second adjective seems to be gaining favor.<sup>1</sup>

In systems with associative memory hardware, the central processor can use the search operation to find a few records of interest without needing to access many uninteresting records. Traffic from the memory to the processor is reduced, but the flow of data in the opposite direction is not much affected. Updates and modifications to the associative memory contents must still be performed sequentially, under control of the central processor. To take full advantage of the parallelism available in associative memories, the memory words must be endowed with some processing capabilities.

Figure 1.3 is a generalized diagram of a single associative processing element (PE), with its memory word divided into several fields  $(A, B, C, \ldots)$ . The match operation finds PEs that match a presented pattern, with unused fields marked with *don't cares* (Xs). For example, the operation Match(3, X, 5) would identify all PEs with A = 3 and C = 5, and would set their sense amplifier outputs to 1. (As indicated in the figure, it is assumed that the sense amplifier includes a register or some means to maintain its state until the next match operation.) Each PE's match result passes to its word logic, which in turn controls the write driver. In this way, match results can condition

<sup>&</sup>lt;sup>1</sup>Content addressable seems inappropriate in the absence of physically addressable words. Such is the case in certain neural and holographic systems [9, 10, 11]. However, these implementations will not be given further consideration in this work, and so the terms associative memory and content addressable memory will be used interchangeably.

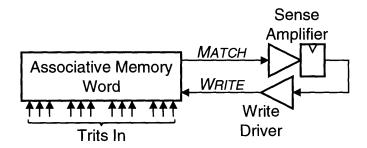

later write operations. If the write driver is not enabled, the PE is masked, and its memory remains unchanged. Fields within a word can also be masked, so that some fields are modified while others are preserved. The Write(-, 6, 8) operation sets B = 6 and C = 8 while leaving the contents of the A field unchanged. These match and conditional write operations turn out to be surprisingly powerful primitives, which can be combined to perform more complex tasks. Section 2.1 demonstrates bit-serial addition procedures on single-trit fields, where a *trit* is a ternary digit of value 0, 1, or X.

The example PE of Fig. 1.3 illustrates the two defining features that distinguish an associative processor or content addressable parallel processor from an associative memory [12]:<sup>2</sup>

- The feedback path allows match results to control later writes, and

- The masked write feature allows some parts of the word to be preserved while others are modified.

Computing systems incorporating associative processors as essential components are termed associative computers [14, 15].

The discussion so far has assumed *fully-parallel* operation, meaning that multiple bits of all PEs may be examined or modified simultaneously. Other organizations are also possible [16], such as bit-parallel/word-serial or bit-serial/word-parallel. The first approach allows several memory words to share the same word logic and sense amplifier [17]. The second and more common organization requires that match and write operations examine or modify only one bit of each memory word at a time [18, 19, 20]. Multibit operations take several cycles, and combining results of the singlebit matches requires relatively complex word logic. Both of these organizations give up some of the available parallelism, but they have the advantage of requiring only conventional RAM cells in their implementations. In contrast, fully-parallel systems must use more specialized associative memory cells, which historically have been relatively expensive compared to standard RAM. However, this work describes a dense new dynamic cell using only five *n*-channel transistors. This technology should make fully-parallel systems competitive, especially in applications requiring many relatively simple PEs.

### **1.3** Comparison to Other Image Processors

Pixel-parallel image processors can solve many problems in constant time, but their hardware requirements vary directly with image area. Although associative processing elements can be very compact when designed in the smart memory style, one might still wonder whether the pixel-parallel approach is too expensive. To answer the question, it is worth skipping ahead a bit to present some experimental results here in the introductory chapter.

<sup>&</sup>lt;sup>2</sup>Compare also the less precise definitions of [13, 14].

Table 1.1 compares the associative processor to several other systems. The entries are arranged in order of approximate flexibility, with an application-specific analog processor [8] on the top line and a general-purpose microprocessor [21] at the bottom. In between are two pipelined convolution chips from LSI Logic's family of image processing products [22, 23, 24], the four-PE Image Signal Multiprocessor (ISMP) from Matsushita [25], and the prototype associative processor of this work. Two image processing problems are used in the comparison: a  $3 \times 3$  Laplacian convolution and the nonlinear smooth and segment (S&S) operation described in Section 5.6. Per-image execution times are given for the pixel-parallel machines; per-pixel values for the others.

Two figures of merit are useful for comparative evaluations. The first of these can be understood as

$$\left(\frac{\text{Area}}{\text{Pixels per second}}\right),\tag{1.1}$$

the silicon area required to achieve a given rate of performance. Equivalently, as

$$\left(\frac{\text{Time} \times \text{Area}}{\text{pixel}}\right),\tag{1.2}$$

it reflects the resources utilized for each pixel processed. The rightmost column of the table presents the energy required for each pixel computation.

The analog focal plane processor is the clear winner by any numerical measure, but it achieves its efficiency at the expense of generality, as it performs only the smooth and segment operation. At the other end of the flexibility spectrum, the general-purpose Alpha microprocessor is by far the most resource-hungry of the systems. The remaining four systems obtain comparable scores on the time-area and energy metrics. For a given level of performance, the associative processor should not be substantially more expensive than the the other approaches, but it will be considerably more general. While the specialized pipelined parts might be preferred in certain embedded applications, the associative processor's flexibility makes it more attractive as a general-purpose image processing accelerator.

#### **1.4 Organization of Thesis**

This chapter introduced associative processing as a model of computation utilizing smart memories, and it described an image processing system based on the chips produced in this work. The remaining chapters discuss the primary contributions of this thesis, which include: 1) a new dynamic associative processor cell using dual-gate devices, 2) compact word logic for use with the cell, 3) an asynchronous reconfigurable mesh network for inter-processor communication, 4) a pass transistor network for responder prioritization and counting, and 5) the implementation and demonstration of a fully functional integrated associative processing system.

Chapter 2 describes the specific features of this associative processor design, at a level intended to familiarize potential users with the system's capabilities. Examples

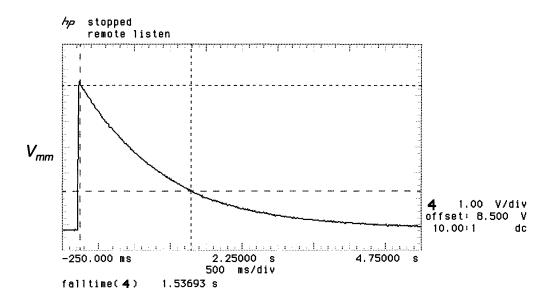

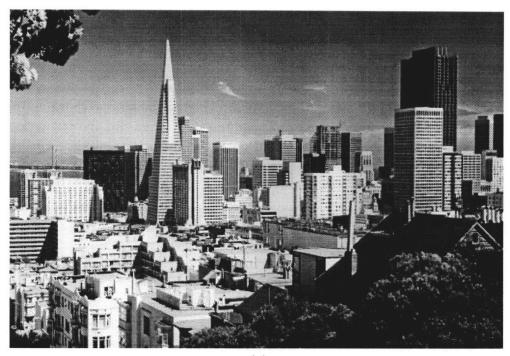

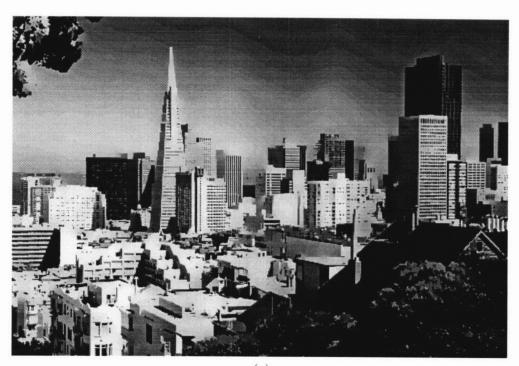

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Time per $\sqrt{N} \times \sqrt{N}$ image | $\operatorname{Time} 	imes \operatorname{Area}$ per pixel         | Energy<br>per pixel |