# A Miniature, Implantable Wireless Neural Stimulation System

by

Scott K. Arfin

Bachelor of Science in Electrical Engineering Columbia University, 2004

Submitted to the Department of Electrical Engineering and Computer Science

in partial fulfillment of the requirements for the degree of

Master of Science in Electrical Engineering

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

June 2006

© Massachusetts Institute of Technology 2006. All rights reserved.

| AuthorDepartment of                                           | of Electrical Engineering and Computer Science<br>May 12, 2006        |

|---------------------------------------------------------------|-----------------------------------------------------------------------|

| Certified by                                                  | Rahul Sarpeshkar  Associate Professor of Electrical Decreases ervisor |

| Accepted by  MASSACHUSETTS INSTITUTE OF TECHNOLOGY  Chairman, | Arthur C. Smith, Department Committee on Graduate Students            |

NOV 0 2 2006

**LIBRARIES**

BARKER

# A Miniature, Implantable Wireless Neural Stimulation System

by

Scott K. Arfin

Submitted to the Department of Electrical Engineering and Computer Science on May 12, 2006, in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering

#### **Abstract**

In this thesis, I present the design of a wireless neural stimulation system. The system consists of an external transmitter, controllable through a computer interface, and a miniature, implantable wireless receiver and stimulator. The implant is tailored for use in zebra finches – small birds weighing just 12-15g – as part of ongoing research into the neural mechanisms of sequence generation and learning. The implant, assembled on a miniature printed circuit board, contains a receiver coil, battery, electrodes, and a custom integrated circuit for data demodulation and neural stimulation. The chip, fabricated in a standard  $0.5\mu\text{m}$  CMOS process, is capable of delivering biphasic current pulses to 4 addressable electrode sites at 16 selectable current levels ranging from  $100\mu\text{A}$  to 1mA. Additionally, the biphasic pulses may be inverted. The entire implant weighs less than 1.5g and occupies a footprint smaller than  $1.5\text{cm}^2$ .

A miniaturized neural stimulator such as this one also has applications in neural prostheses for blindness, Parkinson's disease, and paralysis.

Thesis Supervisor: Rahul Sarpeshkar

Title: Associate Professor of Electrical Engineering

## Acknowledgments

There are many people whom I would like to thank for supporting me while I did the research for this thesis.

I would like to thank my adviser, Professor Rahul Sarpeshkar for his thoughtful advice and inspirational teaching. I have learned an enormous amount about circuit design and how to conduct research from him. Also, thanks to Professor Michale Fee in the Department of Brain and Cognitive Sciences for providing the vision for this project.

I would also like to thank my parents, Paula and Ronald, and my brother Daniel. My family has been there for me from the beginning. Their level of support is unsurpassed.

Next, I would like to thank the past and present members of the Analog VLSI & Biological Systems Group who helped and supported me with this research. They are Christopher Salthouse, Ji-Jon Sit, Keng-Hoong Wee, Lorenzo Turicchia, Woradorn Wattanapanitch, Micah O'Halloran, Michael Baker, Serhii Zhak, Soumyajit Mandal, Tim Lu, Heemin Yang, Maziar Tavakoli-Dastjerdi, and Andrew Selbst. I would also like to thank some past and present members of Professor John Wyatt's group who have aided me. They are Mariana Markova, Luke Theogarajan, and Dr. Shawn Kelly. I also owe thanks to Rose Englund and Gretchen Jones, administrative assistants for AVNSL, and my academic adviser, Professor Jae Lim.

On a lighter note, I would like to thank the Boston Red Sox for their once-ina-lifetime feat, which occurred during my first month as a student and Boston area resident here at MIT.

# Contents

| 1 | Inti | roduction                                             | 17 |

|---|------|-------------------------------------------------------|----|

|   | 1.1  | Neural Mechanisms of Sequence Generation and Learning | 17 |

|   | 1.2  | System Description                                    | 18 |

|   | 1.3  | Applications to Neural Prosthetics                    | 20 |

| 2 | Cou  | apled Coils                                           | 23 |

|   | 2.1  | Introduction                                          | 23 |

|   | 2.2  | Mutual Inductors                                      | 24 |

|   | 2.3  | Analysis of Mutual Inductors Using Feedback           | 26 |

|   | 2.4  | Coil Design and Measurements                          | 29 |

|   |      | 2.4.1 Secondary Coil                                  | 29 |

|   |      | 2.4.2 Primary Coil                                    | 31 |

|   |      | 2.4.3 Coupling Factor Measurements                    | 33 |

| 3 | Win  | reless Transmitter                                    | 39 |

|   | 3.1  | Class C Power Amplifier                               | 39 |

|   | 3.2  | Oscillator-Transmitter (Transmixer)                   | 43 |

|   | 3.3  | Modulation                                            | 45 |

| 4 | Elec | ctrode Modeling and Measurement                       | 49 |

|   | 4.1  | Introduction                                          | 49 |

|   | 4.2  | Electrode Modeling                                    | 50 |

|   |      | 4.2.1 The Randles Model                               | 50 |

|   |      | 4.2.2   | The Double-Layer Capacitance                  | 51  |

|---|------|---------|-----------------------------------------------|-----|

|   |      | 4.2.3   | The Solution Resistance                       | 52  |

|   |      | 4.2.4   | The Warburg Impedance                         | 53  |

|   |      | 4.2.5   | Low and High Frequency Limits                 | 53  |

|   | 4.3  | Measu   | rement Techniques for Electrochemical Systems | 54  |

|   |      | 4.3.1   | Controlled Potential                          | 55  |

|   |      | 4.3.2   | Electrode Impedance Spectroscopy              | 56  |

|   |      | 4.3.3   | Controlled Current                            | 57  |

|   | 4.4  | Exper   | imental Results                               | 58  |

| 5 | Elec | ctronic | : Integrated Circuits                         | 63  |

|   | 5.1  | Introd  | luction                                       | 63  |

|   | 5.2  | High S  | Speed Amplifier                               | 63  |

|   | 5.3  | Peak l  | Detector                                      | 67  |

|   | 5.4  | Pulse   | Width Demodulator                             | 72  |

|   | 5.5  | Outpu   | nt Driver Selection and Stimulation           | 76  |

|   |      | 5.5.1   | Output Driver Cell                            | 77  |

|   |      | 5.5.2   | Output Driver Timer                           | 80  |

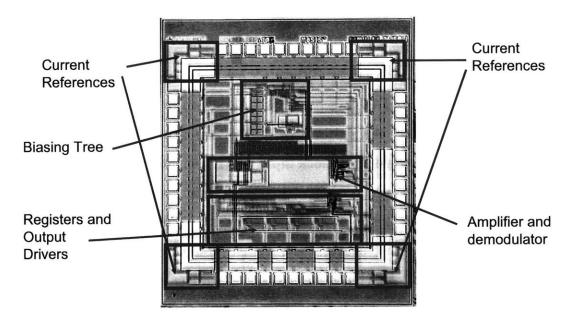

|   | 5.6  | Die M   | licrophotograph                               | 82  |

| 6 | On-  | Chip S  | Supply Independent Biasing                    | 83  |

|   | 6.1  | Introd  | luction                                       | 83  |

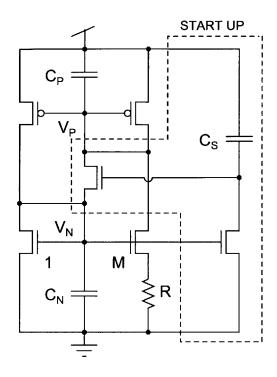

|   | 6.2  | Standa  | ard Current Reference                         | 84  |

|   | 6.3  | Capac   | citive Startup Circuit                        | 86  |

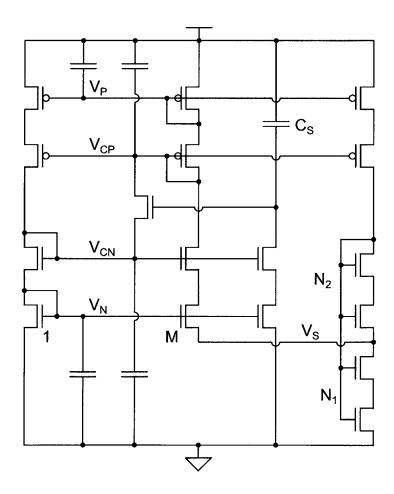

|   | 6.4  | Impro   | ved Current Reference                         | 87  |

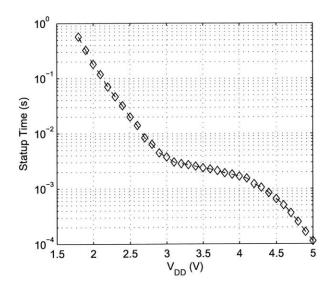

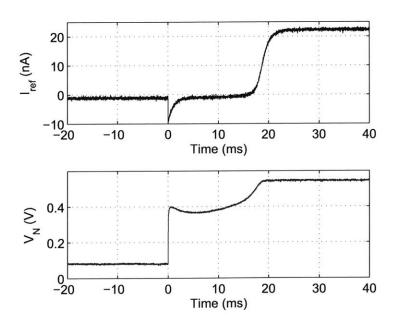

|   | 6.5  | Startu  | p Time and Temperature Dependence             | 89  |

| 7 | The  | Impla   | antable System                                | 93  |

|   | 7.1  | Printe  | ed Circuit Board Design                       | 93  |

|   | 7.2  | Weigh   | t Estimates                                   | 94  |

|   | 7.3  | Contro  | ol System                                     | Q.F |

| 8 | Fut | ure Work and Conclusions | 97  |

|---|-----|--------------------------|-----|

|   | 8.1 | Power Management System  | 97  |

|   | 8.2 | Conclusions              | 99  |

| A | Bat | tery Properties          | 101 |

# List of Figures

| 1-1  | Overview of entire wireless system                                                 | 19 |

|------|------------------------------------------------------------------------------------|----|

| 1-2  | Male Zebra Finch.                                                                  | 20 |

| 1-3  | Overview of a cortical visual prosthesis. The transcranial interconnect            |    |

|      | uses inductively coupled coils to wirelessly transmit data and power to            |    |

|      | the implanted system containing a VLSI chip and an array of electrodes.            | 21 |

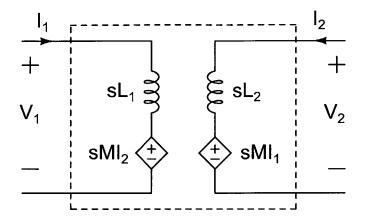

| 2-1  | Schematic representation of an ideal transformer                                   | 24 |

| 2-2  | Equivalent T-model of mutual inductors                                             | 25 |

| 2-3  | Two-port view of mutual inductors                                                  | 26 |

| 2-4  | Two-port view of mutual inductors with source and load                             | 27 |

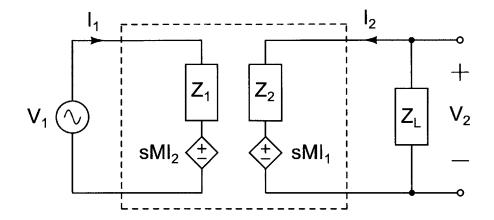

| 2-5  | Block diagram view of mutual inductors                                             | 27 |

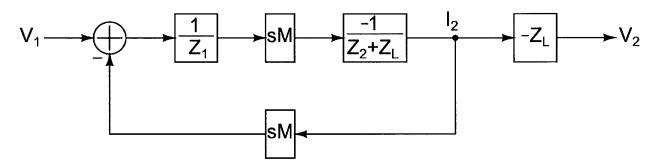

| 2-6  | Equivalent secondary coil circuit                                                  | 28 |

| 2-7  | Bode gain/phase plot for a high- $Q$ resonant low-pass filter                      | 29 |

| 2-8  | Overview of the primary and secondary coil functions                               | 30 |

| 2-9  | Two printed inductors                                                              | 31 |

| 2-10 | Measurements for small and large printed inductors                                 | 32 |

| 2-11 | Theoretical coil coupling curves for two on-axis loops of wire of radius           |    |

|      | $r_1$ and $r_2$ as a function of separation $x$ . The radius $r_2$ is fixed at 1cm |    |

|      | while $r_1$ is varied                                                              | 33 |

| 2-12 | Measured inductance and quality factor for the transmitter coil as a               |    |

|      | function of frequency                                                              | 34 |

| 2-13 | Testing arrangement for field measurements                                         | 36 |

|      |                                                                                    |    |

| 2-14 Magnetic coupling measurements as a function of radius for differen |                                                                           |    |  |

|--------------------------------------------------------------------------|---------------------------------------------------------------------------|----|--|

|                                                                          | heights and tilt angles                                                   | 37 |  |

| 3-1                                                                      | Class C power amplifier schematic                                         | 41 |  |

| 3-2                                                                      | Maximum Power Amplifier Efficiency versus Conduction Angle                | 42 |  |

| 3-3                                                                      | Colpitts Oscillator-Transmitter Schematic                                 | 46 |  |

| 3-4                                                                      | Photograph of the wireless transmitter. The transmitter coil is a single- |    |  |

|                                                                          | turn PCB trace                                                            | 47 |  |

| 3-5                                                                      | Transmitter power spectrum showing sidebands from data modulation.        |    |  |

|                                                                          | The first harmonic is about 23dB below the carrier                        | 48 |  |

| 4-1                                                                      | Randles electrode model                                                   | 50 |  |

| 4-2                                                                      | Randles high frequency electrode model                                    | 54 |  |

| 4-3                                                                      | Schematic of a potentiostat                                               | 55 |  |

| 4-4                                                                      | Example current and back voltage waveforms for electrodes under           |    |  |

|                                                                          | biphasic constant current drive                                           | 58 |  |

| 4-5                                                                      | An example electrochemical cell                                           | 59 |  |

| 4-6                                                                      | Pt-Ir and stainless steel electrode impedance spectra                     | 60 |  |

| 4-7                                                                      | Biphasic pulses of electrodes under constant current drive                | 61 |  |

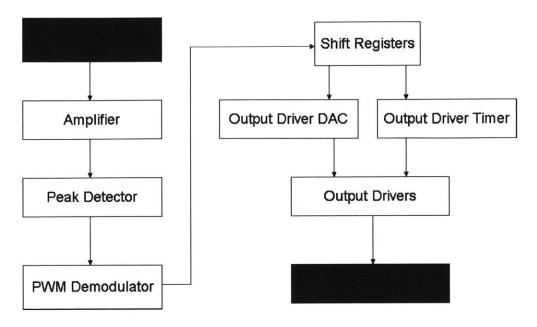

| 5-1                                                                      | Block diagram of the implant. The red blocks are off-chip while blue      |    |  |

|                                                                          | blocks are implemented on-chip                                            | 64 |  |

| 5-2                                                                      | Overview of the primary and secondary coil functions                      | 64 |  |

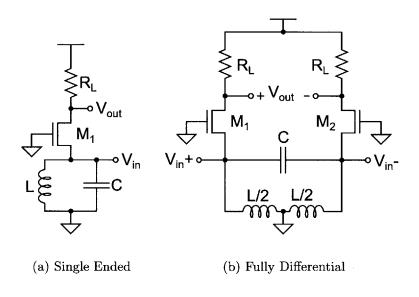

| 5-3                                                                      | Common-gate Amplifiers                                                    | 65 |  |

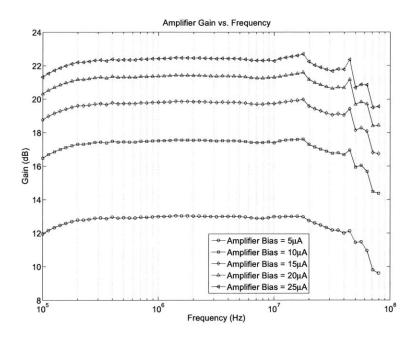

| 5-4                                                                      | Measured amplifier gain curves under different bias conditions            | 67 |  |

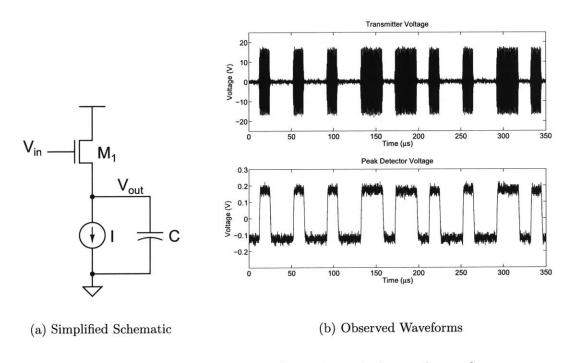

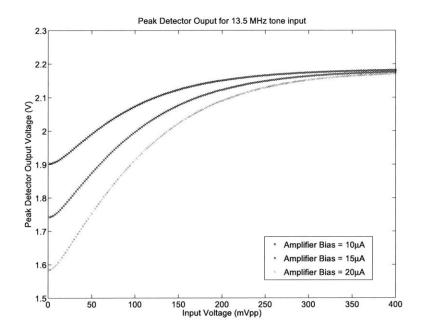

| 5-5                                                                      | Peak detector schematic and observed waveforms                            | 68 |  |

| 5-6                                                                      | Measured peak detector characteristics under different amplifier bias     |    |  |

|                                                                          | conditions                                                                | 69 |  |

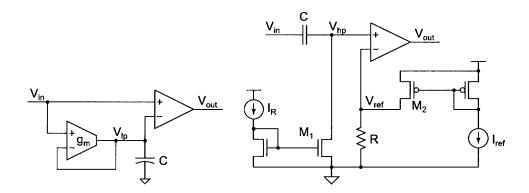

| 5-7                                                                      | Level Detectors                                                           | 71 |  |

| 5-8                                                                      | Simplified PWM Demodulator Schematic                                      | 74 |  |

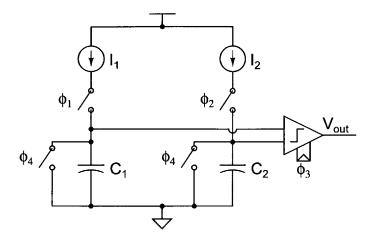

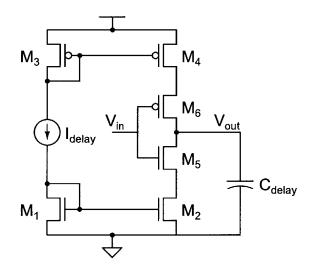

| 5-9                                                                      | Analog Delay Cell                                                         | 74 |  |

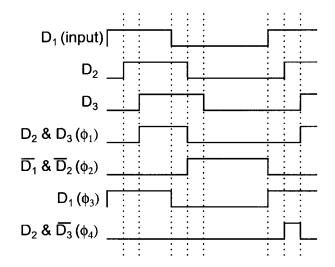

| 5-10 | PWM timing diagram                                                                     | 74  |

|------|----------------------------------------------------------------------------------------|-----|

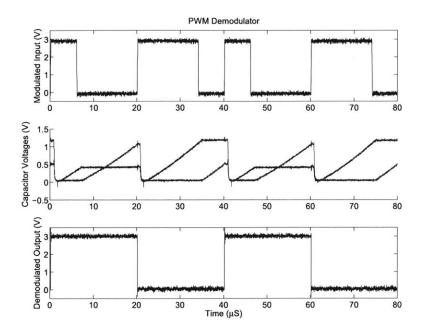

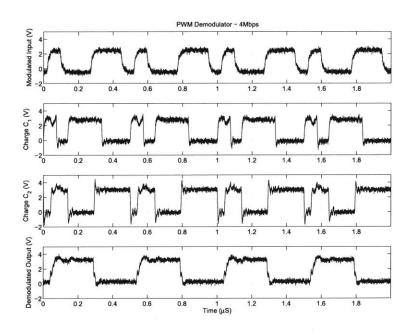

| 5-11 | PWM demodulator circuit operating at two different data rates                          | 75  |

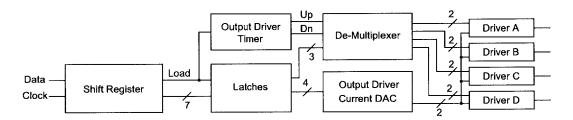

| 5-12 | Complete output driving timing and selection circuitry                                 | 76  |

| 5-13 | General data packet sequence showing recognition sequence, spacer                      |     |

|      | bits, and data bits.                                                                   | 77  |

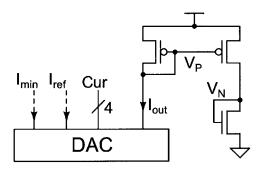

| 5-14 | Output driver current DAC                                                              | 78  |

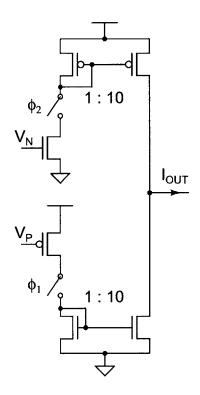

| 5-15 | Output driver cell                                                                     | 78  |

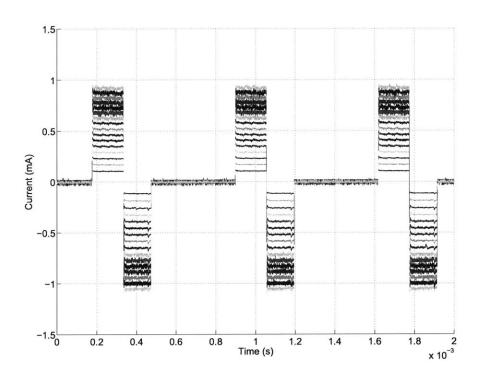

| 5-16 | Measured biphasic current pulses demonstrating all 16 levels from                      |     |

|      | $100\mu\mathrm{A}$ to 1mA                                                              | 79  |

| 5-17 | Output driver timer circuitry                                                          | 80  |

| 5-18 | Output driver control logic                                                            | 80  |

| 5-19 | Timing diagram for output driver                                                       | 81  |

| 5-20 | Die Microphotograph.                                                                   | 82  |

| 6-1  | CMOS current reference with capacitively-coupled startup circuit                       | 86  |

| 6-2  | CMOS current reference used in this thesis                                             | 88  |

| 6-3  | Experimentally observed $0.5\mu\mathrm{m}$ current reference startup time versus       |     |

|      | supply voltage                                                                         | 90  |

| 6-4  | Measured output current (top) and NMOS bias voltage (bottom) of                        |     |

|      | the 0.5 $\mu \rm m$ current reference. $V_{DD}$ was stepped from 0 to 2.5 V at time=0. | 90  |

| 6-5  | Current reference temperature data                                                     | 91  |

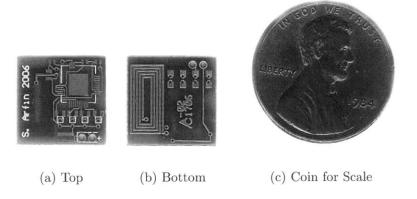

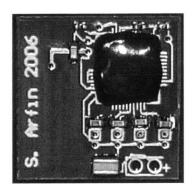

| 7-1  | Printed circuit board design, shown next to a coin for scale                           | 94  |

| 7-2  | Populated chip-on-board photograph                                                     | 94  |

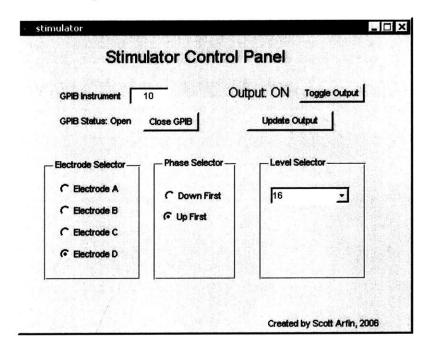

| 7-3  | Screenshot of the graphical user interface                                             | 95  |

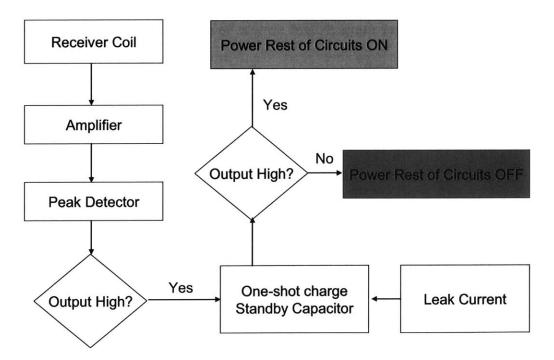

| 8-1  | Proposed standby circuit block diagram                                                 | 98  |

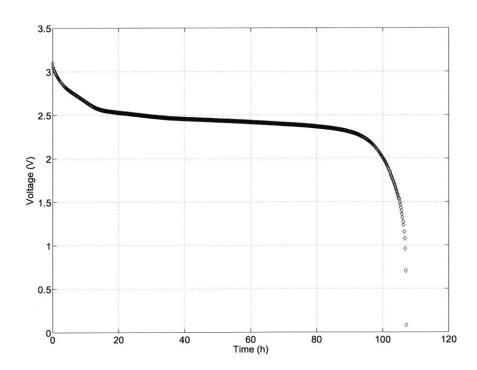

| A-1  | Discharge curve for battery with 50µA load current                                     | 102 |

# List of Tables

| 2.1 | Summary of primary and secondary coil parameters                                                     | 33  |

|-----|------------------------------------------------------------------------------------------------------|-----|

| 3.1 | Colpitts Oscillator Design Values                                                                    | 45  |

| 4.1 | $R_s$ and $C_{dl}$ measurements for $50\mu$ Stainless Steel Electrodes under constant current drive  | 59  |

| 4.2 | $R_s$ and $C_{dl}$ measurements for $50\mu$ Platinum-Iridium Electrodes under constant current drive | 60  |

| 5.1 | Summary of Common-Gate Amplifier Parameters                                                          | 67  |

| 5.2 | Summary of Peak Detector Parameters                                                                  | 69  |

| 5.3 | Summary of PWM Demodulator Parameters                                                                | 73  |

| A.1 | ML621S Battery Details                                                                               | 102 |

# Chapter 1

## Introduction

# 1.1 Neural Mechanisms of Sequence Generation and Learning

The focus of my thesis research is on the design and implementation of a miniature, implantable wireless neural stimulation system. The purpose of the device is to study the neural mechanisms of sequence generation in small songbirds. However, this work will also benefit research into the neurological behavior of larger animals such as rats, and even monkeys and humans, since the techniques explored here are also more generally applicable. In particular, hopes of curing serious neurological disorders in humans such as blindness, Parkinson's disease, and even paralysis, will be aided by wireless neural stimulation systems.

Adult male zebra finches (songbirds) are a popular subject for neurological study. Their song reproductions are an excellent example of the generation and learning of complex sequences in the brain. Further, avian brain areas involved in song learning are closely related to mammalian brain areas involved in motor learning [5]. Thus, the study of song generation in birds may teach us more general principles about sequence generation and learning in humans.

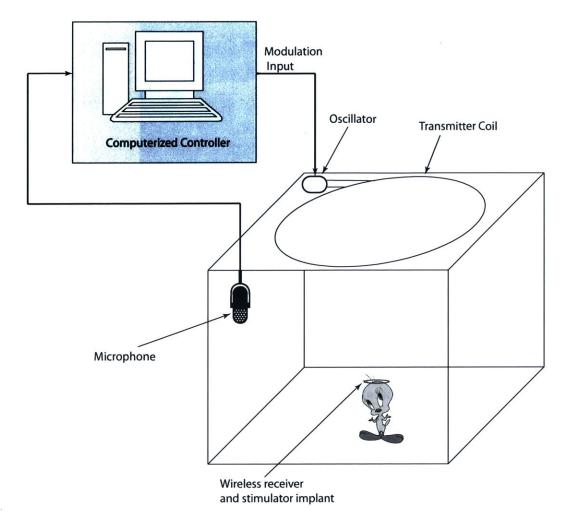

In previous experiments, researchers placed songbirds inside a cubic cage approximately 20cm on an edge inside an acoustically isolated chamber. Then, using several

carefully positioned electrodes implanted into the bird's brain and a microphone, the researchers simultaneously recorded sounds of the bird singing and the neural activity in its brain. However, they could not avoid wires coming out of the implant, impeding the bird's motion. To mitigate this difficulty, they used a bundle of fine wires connected to a motorized, commutating post. The motor ran automatically under a feedback control to reduce the torque experienced by the bird due to the bundle of wires [6]. However, an even better solution would be to replace the bundle of wires altogether with a wireless data link.

In this thesis, I implemented a wireless neural stimulation system rather than a recording system. Researchers plan to use wireless neural stimulation in the brain of the bird to attempt to influence and control the bird's song generation. For instance, a microphone and digital signal processor may be used to detect when the bird begins singing. When this happens, a computer program initiates wireless commands to stimulate neurons in the bird's brain.

## 1.2 System Description

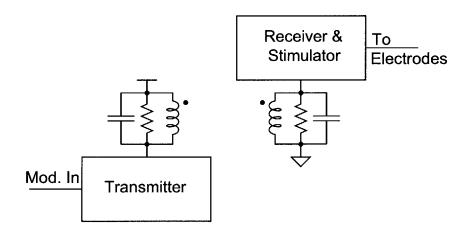

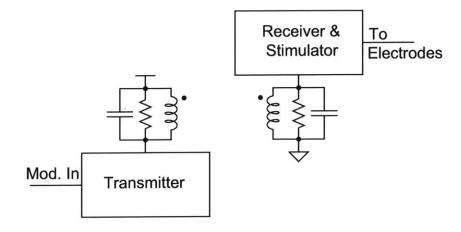

The wireless system, shown in Figure 1-1 consists of two parts: an external transmitter, controllable through a computer interface, and a miniature, implantable wireless receiver and stimulator. The implant is assembled on a miniature printed circuit board, and contains a receiver coil, battery, electrodes, and a custom integrated circuit for data demodulation and neural stimulation. The chip is fabricated in standard  $0.5\mu m$  CMOS process. It is capable of delivering biphasic current pulses to 4 addressable electrode sites at 16 selectable current levels ranging from  $100\mu A$  to 1mA. Additionally, the biphasic pulses may be inverted. The entire implant weighs less than 1.5g and occupies a footprint smaller than  $1.5cm^2$ . The system supports a data rate of 25kbps. Data rates of 1Mbps are also possible. Power is supplied from a 3.0V, 5mAh lithium-manganese rechargeable battery. The implant can run up to approximately 3 days on a single charge, depending on stimulation rate. Future improvements in static power dissipation will increase the operation time to approximately 20 days.

Figure 1-1: Overview of entire wireless system.

The overall size of the implant is restricted by the physical size of the zebra finch itself. Figure 1-2 shows a male zebra finch. Zebra finches generally weigh 12-15 grams. As a result, these small songbirds can only carry up to 2g on the cranium [6]. The implantable portion of the stimulation system must also fit within an area of 1.5cm<sup>2</sup> in order to fit adequately on the bird's head. A major challenge of this project was designing the implanted portion of the system to meet these size and weight specifications.

Figure 1-2: Male Zebra Finch.

## 1.3 Applications to Neural Prosthetics

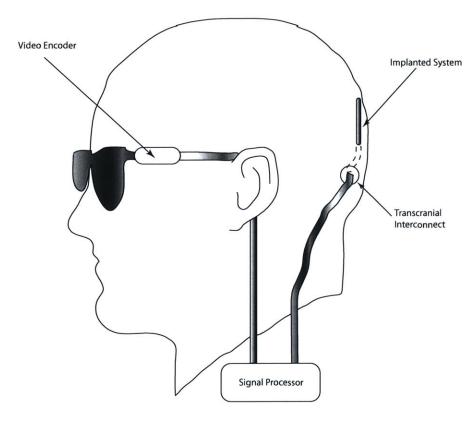

One application of wireless neural stimulation systems, apart from studying the neural mechanisms of sequence generation, is cortical visual prostheses for the blind. In 1929, Foerster successfully studied the effects of electrical stimulation of the occipital lobe of the human cortex. A patient who received this stimulation reported "seeing" a spot of light [8]. Since then, the idea of using neural stimulations at a single site to produce spots of light has evolved into using many sites simultaneously to produce entire images. A major breakthrough in cortical prostheses occurred in 1968 when Dr. Brindley and Dr. Lewin implanted a device with an array of 80 electrodes into a blind patient. They activated the sites using a wireless interface in which they placed the transmitting coil of an oscillator tuned to the appropriate frequency on the scalp directly over the electrode site. The patient reported seeing spots that corresponded approximately to the position of the electrode in the visual cortex [2].

Figure 1-3 shows an example of a practical, chronically implantable cortical visual prosthesis. An external light sensor captures and encodes video and passes this data to a digital signal processor, which maps the light information into neural stimulation data. The stimulation data is then transmitted across a transcranial wireless link, formed from a network of coupled coils placed on both sides of the skull, to a chip implanted inside the brain. The chip demodulates the wireless data and stimulates in the visual cortex. The wireless link in this thesis, designed at 13.5MHz, is also

compatible with human tissue. Loss due to attenuation from the skin becomes a significant problem at frequencies greater than 30MHz [15]. A practical visual prosthesis would also require many more stimulation sites than the 4 implemented in this thesis. However, due to the digital programmability of electrode selection, adding additional stimulation sites needed for vision would be easily accommodated.

Figure 1-3: Overview of a cortical visual prosthesis. The transcranial interconnect uses inductively coupled coils to wirelessly transmit data and power to the implanted system containing a VLSI chip and an array of electrodes.

# Chapter 2

# Coupled Coils

#### 2.1 Introduction

The wireless neural stimulation system presented in this thesis employs a pair of weakly coupled coils for sending data between the transmitter and the implant. The coils can be modeled as a transformer with a very small coupling coefficient, k. In this regard, the transmitter coil shall be referred to as the "primary" and the receiver coil as the "secondary."

A number of competing constraints resulted in coupled coils as the mechanism for data transmission. The factors considered were the size and weight of the implant, data rate, operating distance, and power consumption. If we are constrained to fit the implant into an area not exceeding 1.5cm<sup>2</sup> and with a mass not exceeding 1.5g, then it will not be possible to build an efficient antenna at any standard radio frequency that meets these considerations. An efficient antenna typically has some dimension equal to a certain fraction of the wavelength it is designed receive. For example, radio waves at 2.4GHz in free space have a wavelength of 12.5cm. An efficient antenna design at this frequency that also meets the area and weight specifications would be difficult to achieve. The problem only becomes more difficult at lower frequencies. Further, a wireless receiver at 2.4GHz would consume a significant amount of power—easily several milliwatts. The bandwidth afforded by such a high operating frequency well exceeds the 25kbps that is required. Shifting to a lower frequency to reduce

power consumption is desirable since the life of the implant depends on its power consumption. The entire implant needs to be powered by a miniature battery which should last the length of an experiment without having to be replaced. Fortunately, the distances over which we must transmit are quite small. The bird enclosure is a cube shaped box 20cm on each edge. Therefore, with the bird present in the cage and wearing the implant on its head, transmission distances may be approximately 5-15cm. At this range, selecting an operating frequency in which we are still in the magnetic near-field enables us to use a pair of coupled coils as the link between the transmitter and receiver [20].

For this application, we choose 13.56MHz. This unlicensed band is designated by the FCC for Industrial/Scientific/Medial (ISM) use. It also provides adequate bandwidth for our application. Even if demands on data rate increase, this band should still be sufficient. With a wavelength in air of approximately 22m, magnetic coupling is a viable option in the range of 5-15cm.

### 2.2 Mutual Inductors

When two inductors are placed near each other, or are coupled via a core with a high magnetic permeability, magnetic flux produced by either inductor is coupled to the other. The linked flux then induces a voltage in the opposite coil. We will exploit this property of coupled coils in our design.

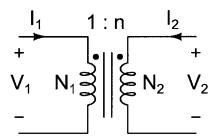

Figure 2-1: Schematic representation of an ideal transformer.

In an ideal transformer comprised of two windings on a common, infinitely permeable magnetic core, driving the primary side produces a time varying magnetic flux, of which all is coupled to the secondary side. Figure 2-1 is a schematic representation of an ideal transformer.  $N_1$  is the number of turns of the primary and  $N_2$  is the number of turns of the secondary. We can then define the turns ratio, n, to be  $N_2/N_1$ . It can be readily shown that the terminal voltages and currents are related by:

$$\frac{V_2}{V_1} = n \tag{2.1}$$

$$\frac{I_2}{I_1} = -\frac{1}{n} \tag{2.2}$$

To deal with the case where not all of the flux created by the primary is linked to the secondary, one must introduce the concept of mutual inductance. After some labor, one arrives at the terminal relations [4]:

$$V_1 = L_1 \frac{dI_1}{dt} + M \frac{dI_2}{dt} (2.3)$$

$$V_2 = L_2 \frac{dI_2}{dt} + M \frac{dI_1}{dt} (2.4)$$

where

$$M = k\sqrt{L_1 L_2} \tag{2.5}$$

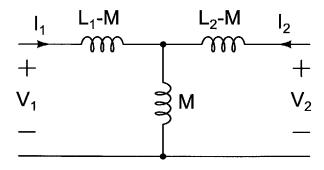

Figure 2-2: Equivalent T-model of mutual inductors.

Figure 2-3: Two-port view of mutual inductors.

The coupling coefficient, k, is a measure of the amount of coupling between the two coils. A coefficient of k=1 corresponds to the ideal case where all of the flux links both coils. For any physical system, 0 < k < 1. In our wireless data link, we expect the exact value of k to be difficult to calculate and likely to change during the course of an experiment as the bird moves inside the cage, or alters the angle of its head. However, we can be certain that  $k \ll 1$ , and will use this approximation to help simplify the design.

## 2.3 Analysis of Mutual Inductors Using Feedback

Equations 2.3 and 2.4 are not especially useful by themselves for understanding or analyzing circuits with mutual inductance. However, the two two-port models in Figures 2-2 and 2-3 are equivalent representations of these differential equations. The two-port model in Figure 2-3 arises directly from the differential equations. The T-model of mutual inductors in Figure 2-2, although it may contain negative inductances, is externally equivalent to the circuit in Figure 2-3. The T-model can also be verified by solving for the circuit's z-parameters. The equivalent two-port model in Figure 2-3 is then obtained.

To further aid in our understanding, we would like to construct a feedback model of the system of coupled inductors shown in Figure 2-4. We have taken the two-port model of Figure 2-3 and added a voltage source at port one. We have also replaced

Figure 2-4: Two-port view of mutual inductors with source and load.

the inductances with general impedances  $Z_1$  and  $Z_2$  and connected a load,  $Z_L$ , to port two. The resulting feedback model is shown in Figure 2-5.

Figure 2-5: Block diagram view of mutual inductors.

$$\frac{V_2}{V_1} = \frac{sMZ_L}{Z_1 \left(Z_2 + Z_L\right) - s^2 M^2} \tag{2.6}$$

$$\frac{V_2}{V_1} = \frac{MZ_L}{Z_L L_1 + sL_1 L_2 - sM^2} \tag{2.7}$$

Applying Black's Formula to the feedback block diagram, we obtain Equation 2.6. We also now assume that both inductors  $L_1$  and  $L_2$  are of high quality factor, and replace them with their respective impedances  $sL_1$  and  $sL_2$ , obtaining Equation 2.7. Next, we substitute in the denominator  $M^2 = k^2 L_1 L_2$ , and obtain Equation 2.8.

$$\frac{V_2}{V_1} = \frac{MZ_L}{Z_L L_1 + sL_1 L_2 (1 - k^2)}$$

(2.8)

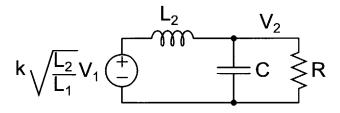

We now recognize that in the situation where the two coils are quite far apart and the received signals are small  $(k \ll 1)$ , the  $k^2$  term in the denominator of Equation 2.8 may be eliminated. The last step is to replace the load impedance,  $Z_L$ , with a parallel RC network. The C is chosen to resonate with  $L_2$  at the primary coil driving frequency. Upon making this final substitution, we obtain the familiar form of the resonant low-pass filter, multiplied by a scaling term,  $\beta$ . This result is shown in Equation 2.9.

$$\frac{V_2}{V_1} = \beta \cdot \frac{1}{s^2 L_2 C + \frac{sL_2}{R} + 1} \tag{2.9}$$

$$\beta = k\sqrt{\frac{L_2}{L_1}} \tag{2.10}$$

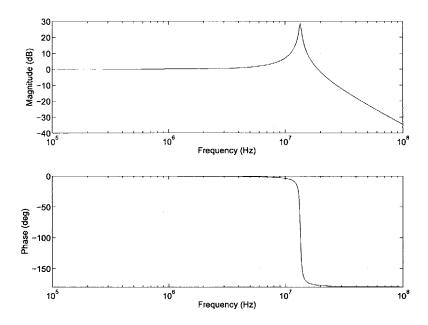

The results from this analysis can be explained intuitively. If k is small, then this is equivalent to opening the feedback loop, or eliminating the dependent source on the primary side of Figure 2-4. The dependent source on the secondary side, equal to  $sMI_1$ , is also equal to  $k\sqrt{\frac{L_2}{L_1}}$ . This arises from substituting  $k\sqrt{L_1L_2}$  for M and  $\frac{V_1}{sL_1}$  for  $I_1$ . The resulting equivalent secondary coil circuit is shown in Figure 2-6. Here we can clearly see how the resonant low-pass filter arises. The prefactor,  $\beta = k\sqrt{\frac{L_2}{L_1}}$ , results from the non-ideal transformer pair formed by the two coils. Figure 2-7 shows the Bode magnitude and phase plots for the transfer function  $\frac{V_2}{\beta V_1}$  of the resonant low-pass filter. In this example, the tank has a resonant frequency of 13.5MHz and a Q of 25.

Figure 2-6: Equivalent secondary coil circuit.

The ratio  $\sqrt{\frac{L_2}{L_1}}$  is sometimes written in the case of a transformer as the turns ratio,  $n = \frac{N_2}{N_1}$ . This is equivalent to  $\sqrt{\frac{L_2}{L_1}}$  because a coil of N turns nominally has an inductance  $L \propto N^2$ .

Figure 2-7: Bode gain/phase plot for a high-Q resonant low-pass filter.

## 2.4 Coil Design and Measurements

For this thesis project, both the primary and secondary coils need to be custom designed. The precise value of their inductance, size, and shape are important for the success of the wireless system. Figure 2-8 shows an overview of the functions of the primary and secondary coils in this system. As indicated, both coils will operate as part of tuned circuits. Use of resonance improves the spectral cleanliness of the output at the transmitter. At the receiver, resonance directly increases the voltage of the received signal by a factor of Q, the quality factor of the resonant tank.

### 2.4.1 Secondary Coil

First, let us examine the design of the secondary coil in this wireless system. Its design is more difficult than the primary coil because of the space constraint. The secondary coil must fit on the implant, which may not occupy more than 1.5cm<sup>2</sup> in area or weigh more than 1.5g. The implant must also fit the receiver chip, wirebonds, battery, and surface-mount components. Because the size of the secondary coil directly affects receiver performance, a significant portion of this area should be

allocated to the receiver coil. I chose to build the secondary coil as a spiral trace on the receiver printed circuit board. Printed circuit board traces are robust to handling and fabricate reliably. Alternative types of inductors include wound coils and commercially available surface-mount inductors. Commercial inductors, however, usually do not make good receiver coils because they are designed to control their flux inside a packaging so as not to disturb other circuits. They may also contain heavy ferrite cores which could exceed the implant's weight specification. A hand wound coil may achieve higher inductance than a printed spiral because it could be wound tighter than a printed spiral, but the printed spiral has the advantage of reliable inductance and ease of fabrication, since the receiver must already use a printed circuit board to mount all parts. Accurate, predictable inductance values are essential for tuned circuits.

Figure 2-8: Overview of the primary and secondary coil functions.

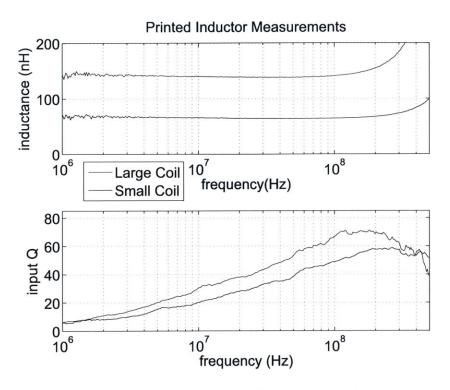

Figure 2-9 shows two printed spiral inductors. The approximate dimensions of the spirals are  $0.5 \times 0.5$ cm for the smaller spiral and  $0.5 \times 1.0$ cm for the larger spiral. Measurements of the inductance and quality factor of each spiral as a function of frequency is shown in Figure 2-10. As it turned out, there was sufficient space for the larger printed coil in the final implant design. From the measurements, we see that the larger coil has approximately 140nH of inductance and a quality of factor of about 30 at 13.5MHz. A discussion of how to approximate the inductance of planar spirals appears in [12].

Figure 2-9: Two printed inductors.

#### 2.4.2 Primary Coil

Given the restrictions on the design of the secondary coil, what is the optimal design of the primary coil? In many other types of neural recording and/or stimulation implants, such as cochlear implants and retinal implants, a transcutaneous inductive link is used to transmit both data and power to the implant. In this particular arrangement, the primary and secondary coils are placed as close together as possible<sup>2</sup>, typically achieving a coupling coefficient, k, between 0.08 and 0.24 [18]. Further, the primary and secondary coils always operate at a fixed, known distance apart. In this project, the primary and secondary coils operate at a varying distance apart.

Let us consider the case where the primary and secondary coils are on axis. Equation 2.11 gives an approximation for the k value for on-axis loops of wire of radii  $r_1$  and  $r_2$  separated by a distance x [7]. Such explicit calculation of k is only possible for very simple geometries.

$$k(x) \approx \frac{r_1^2 \cdot r_2^2}{\sqrt{r_1 \cdot r_2} \cdot \left(\sqrt{x^2 + \max(r_1, r_2)^2}\right)^3}$$

(2.11)

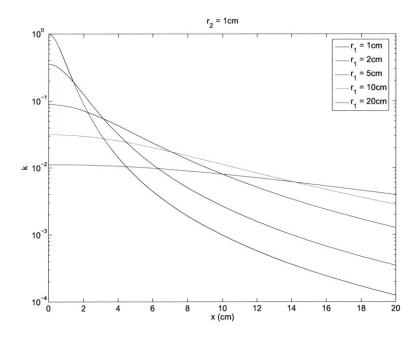

If we plot the k factor as a function of separation x for primary loops of various radii  $r_1$  while holding the secondary loop fixed with  $r_2 = 1$ cm, we obtain the plot in Figure 2-11. The results indicate that unity coupling is only possible for loops of wire

$<sup>^{2}</sup>$ In cochlear implants, the coils are separated by the thickness of the skin, typically about 7mm.

Figure 2-10: Measurements for small and large printed inductors.

of identical radius separated by 0 distance. This is intuitive because at 0 separation, the field generated by the primary is approximately uniform. Therefore, the coupling factor is just the ratio of the areas of the two coils. A more interesting effect occurs at larger separations, which is closer to where the transmitter-receiver pair in this thesis are likely to operate. At large separations, loops which are mismatched in geometry performed better than loops of similar size. This can be explained as a reduction in flux density, i.e. spreading of the magnetic flux to occupy a larger region. Smaller primary loops have their flux concentrated over a smaller region, and hence have a larger k factor at small separations. However, k falls rapidly as separation increases. In contrast, the flux density of large loops of wire decays gracefully. This property will be useful in this design where the coil separation can change by several centimeters.

One can observe empirically from Figure 2-11 that if one is constrained to a system with a fixed, small secondary size, then the radius of the primary loop that maximizes the coupling factor at a given distance is approximately equal to that operating distance. Assuming that this observation holds for other coil configurations besides single loops of wire, such as spiral inductors, we now have a simple criterion

Figure 2-11: Theoretical coil coupling curves for two on-axis loops of wire of radius  $r_1$  and  $r_2$  as a function of separation x. The radius  $r_2$  is fixed at 1cm while  $r_1$  is varied.

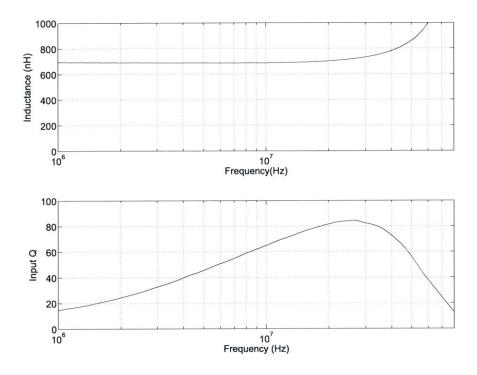

to design our primary coil. If we assume that the average operating distance between the primary and secondary coils is about 10cm, then we should choose a primary coil radius of 10cm. Due to practical constraints on the size of the primary coil, the actual primary coil radius used in this thesis is 8.6cm. Figure 2-12 shows the measured inductance and quality factor of the transmitter coil as a function of frequency.

Table 2.1 summarizes the important features and design parameters of the primary and secondary coils.

Table 2.1: Summary of primary and secondary coil parameters.

| Coil      | Radius             | Inductance | Q at                | Self-Resonance     |

|-----------|--------------------|------------|---------------------|--------------------|

|           |                    |            | $13.5 \mathrm{MHz}$ | Frequency          |

| Primary   | 8.6cm              | 700nH      | 65                  | 70MHz              |

| Secondary | 0.2cm (equivalent) | 140nH      | 30                  | $350 \mathrm{MHz}$ |

### 2.4.3 Coupling Factor Measurements

In order to validate the analysis in this chapter that k is very weak, we must substantiate that claim with some laboratory measurements. The following measurements

Figure 2-12: Measured inductance and quality factor for the transmitter coil as a function of frequency.

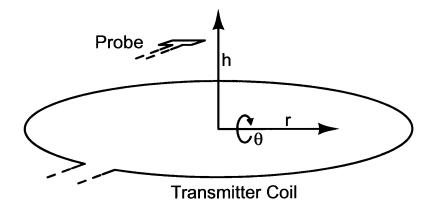

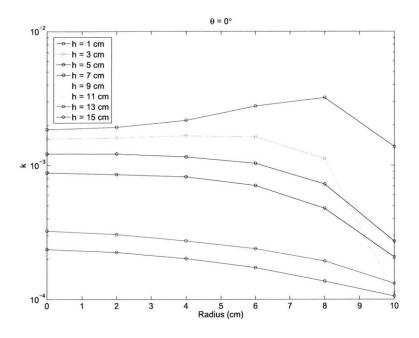

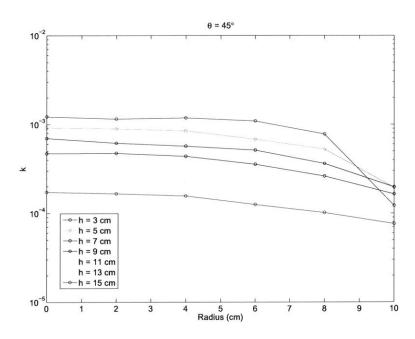

for k were taken at the operating frequency of 13.5MHz. Figure 2-13 shows the experimental setup for measuring the coupling coefficient. The small secondary coil, denoted as the probe in the figure, was positioned centrally over the transmitter coil. The amplitude of the transmitter output was measured independently to define  $V_1$ , the voltage level across the transmitter coil. The probe was then moved through the magnetic field generated by the transmitter. Its position is characterized by three parameters: r, the radial distance of the probe from the transmitter coil's geometric center, h, the height of the probe above the transmitter coil, and  $\theta$ , the angle the probe makes with transmitter coil. An angle of  $\theta = 0$  corresponds to both coils having identical, parallel orientation.

The amplitude of the signal received at the probe was measured with an Agilent 4395A spectrum analyzer. Although the transmitter was designed to be resonant to transmit at a single frequency, the probe in this experiment was designed not to be resonant. In theory, resonance contributes a certain amount of gain that can be

calibrated out. In practice, however, this calibration would be unreliable because in high Q systems, if the resonance of the probe is slightly off from the transmitter's resonance, this could result in a large error.

If we denote the voltage on the primary as  $V_1$  and the voltage on the secondary as  $V_2$ , then we can use Equation 2.9 with one modification to determine k. Since the resonance of the secondary coil has been removed, Equation 2.9 simplifies to:

$$\frac{V_2}{V_1} = k\sqrt{\frac{L_2}{L_1}} \tag{2.12}$$

which can be solved for k once the ration  $\frac{V_2}{V_1}$  has been measured.

The results of the field measurements, performed by sweeping r at several different heights for two different probe angles are shown in Figure 2-14. Immediately we see that the  $k \ll 1$  assumption is valid, since k ranges from about  $2 \times 10^{-4}$  to  $2 \times 10^{-3}$  depending on height, radius, and angle. We also see that this coil arrangement is actually relatively insensitive to all 3 parameters. This is because of the significant size mismatch between the transmitter and probe coils. The large transmitter coil generates a relatively uniform magnetic field. Because the probe is so small compared to the transmitter, any movements of the probe do not significantly alter the strength of the magnetic coupling. The received signal strength curve, as a function of radius, shifts towards smaller values of k as the probe height increases. This can be explained intuitively by a near-far argument. At greater heights, radial changes as a fraction of probe height decrease. The "view" of the transmitter coil as a function of r, as seen by the probe, does not change significantly at larger heights. The coupling factor's relative insensitivity to probe position and tilt is an important feature of our design because the bird is free to move about the cage.

One interesting observation is the peaking in the strength of the coupling in Figure 2-14(a) for h = 1cm. The peaking around r = 8cm occurs because the transmitter coil radius is 8.6cm. The magnetic probe is very close to the turn of wire on the transmitter coil. Once the probe is moved past the transmitter radius, the magnetic field strength falls off sharply. This peaking effect only occurs for small values of h. The

peaking is a purely local effect that can also be masked by tilting the probe. The peaking effect has also been noted in [15] and [19].

Figure 2-13: Testing arrangement for field measurements.

(a) Magnetic coupling measurements for  $\theta = 0^{\circ}$ .

(b) Magnetic coupling measurements for  $\theta=45^\circ$

Figure 2-14: Magnetic coupling measurements as a function of radius for different heights and tilt angles.

# Chapter 3

# Wireless Transmitter

As discussed earlier in the chapter on coupled coils, wireless communication occurs via a system of magnetically coupled coils. The transmitter coil is large and sits outside the bird cage. Its job is to produce a time varying magnetic flux which is gathered by the secondary coil on the receiver. We would like to transmit with a large voltage swing across the primary coil since the voltage swing on the secondary coil, and therefore the transmitter range, is directly proportional to the swing on the primary. The voltage received at the secondary will be directly amplified and demodulated.

From these design considerations, we realize that we need an amplification circuit capable of swinging large voltages across the transmitter coil. To this end, we will be interested in resonant amplifier circuits since transmission will take place at a single carrier frequency. Resonant circuits are capable of providing the voltage amplification that we need to make this wireless transmission work.

# 3.1 Class C Power Amplifier

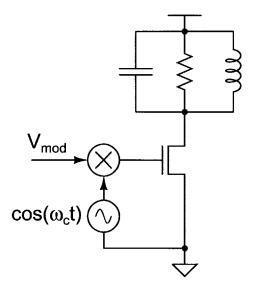

The Class C power amplifier shown in Figure 3-1 is a very simple, single device power amplifier designed for efficient operation. This circuit is the same as a Class A amplifier. The only difference is the conduction angle,  $\Phi$ , or the angular fraction of a period when the current through the power device is non-zero. In small signal amplifiers, the

device is biased at a particular DC operating point, and then driven with a gentle AC signal to avoid the nonlinearities in the device from causing distortion at the output. As long as the input drive is kept small, the voltage swing across the load remains proportional to the voltage swing at the input. In power amplifier applications, Class A does not refer to the linearity of the amplifier, but to the device conduction angle, – 360°. Since the load is tuned, it filters the drain current extensively. Even under large input voltage drives which would not normally be considered small signal, the output voltage of the tank may remain sinusoidal with an amplitude that is still reasonably proportional to the input drive amplitude. However, because there is a large DC current being burned in the amplifier which is not being delivered to the load, a large amount of the available power is wasted. The maximum Class A amplifier efficiency is 50%.

In this thesis, to call the transmitter a power amplifier is actually somewhat of a misnomer. In contrast to more conventional RF power amplifier applications, where the amplifier is designed to deliver a certain amount of power to a resistive load in the form of an antenna, this transmitter does not have an antenna. Rather, the coil stores energy in a magnetic field. Loading is caused by the inductor's finite Q, or loss due to resistance in the inductor. Also, a small amount of energy is captured by the secondary coil and used for data recovery. This is how data is transmitted through near-field magnetic coupling. Any far field radiation is negligible. Both of these losses are small which results in a high load impedance seen by the power device. Hence, the power amplifier is mainly a large signal voltage amplifier.

Our specifications require large voltage swings at the output. Rough estimations suggest that  $30\text{-}40\text{V}_{pp}$  is needed to obtain reliable transmission at 15cm separation. If we use the circuit in Figure 3-1, we expect that to get this level of output, we will need a very large input drive. Further, the device may be destroyed if it is biased with a large DC current. Since the amplifier will be operated in simple on/off fashion,

<sup>&</sup>lt;sup>1</sup>In some designs, the transmitter coil may be driven at the frequency where it radiates, and hence loads the resonant tank with some radiation impedance. The coil therefore acts as both an inductor and an antenna. Given the driving frequency of 13.5MHz, one would not ordinarily expect a coil 17.2cm in diameter to radiate at this frequency.

Figure 3-1: Class C power amplifier schematic.

linearity is not important. The solution is then to lower the DC operating point of the device so the zero input DC drain current is reduced to zero while keeping the input drive magnitude large enough to maintain the desired output swing. Lowering the DC operating point of the device such that it no longer conducts for 360° results in class AB operation for angles greater than 180° but less than 360°, class B operation for conduction angles exactly equal to 180°, and class C operation for conduction angles less than 180°.

In class C operation, the device is nominally off and only conducts for brief periods in each cycle when the input exceeds the transistor's threshold. When the transistor conducts, it acts as a current source, drawing spikes of current from the supply and passing it through the impedance of the LC tank. If the drive is periodic at the resonant frequency of the tank, the tank, which has maximum impedance at resonance, develops a large voltage across its terminals. At other frequencies away from resonance, the tank increasingly looks like a short circuit. The high frequency components of the drain current produce only small voltages at the output. The maximum possible efficiency of the class C power amplifier,  $\eta_{max}$ , as a function of conduction angle is calculated in [10] and shown in Equation 3.1. This equation is also valid for other classes of operation. It may be evaluated for any conduction

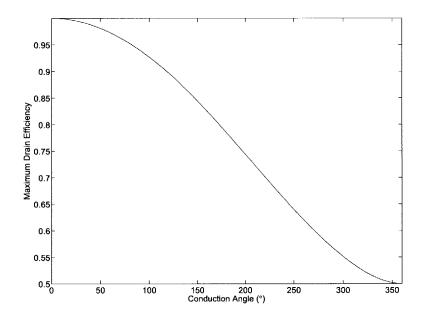

angle between 0 and 360°. Figure 3-2 shows a plot of the maximum power efficiency possible versus conduction angle.

$$\eta_{max} = \frac{\Phi + \sin\Phi}{4 \cdot \left(\sin\frac{\Phi}{2} - \frac{\Phi}{2}\cos\frac{\Phi}{2}\right)} \tag{3.1}$$

Figure 3-2: Maximum Power Amplifier Efficiency versus Conduction Angle.

This maximum efficiency curve makes several unrealistic assumptions. It assumes that the device behaves as a current source (remains saturated) even for  $v_{DS} = 0$ . It also assumes that the peak-to-peak output swings are a full  $2V_{DD}$ , and that there are no other losses in the circuit.

We have used this circuit successfully in lab to generate large peak-to-peak swings at the output, occasionally as large as  $60V_{pp}$ . Although the circuit lacks the ability to modulate the output voltage swing in a linear manner, such accurate control is not needed for on/off AM. Simply switching the amplifier drive from full power to off is effective for transmitting on/off amplitude modulated data. However, one important drawback of this circuit is that it is not capable of oscillating autonomously. The drive must be at the transmit frequency of 13.5MHz, mixed by the modulation input  $V_{mod}$ . In a laboratory setting, high frequency generators are expensive and not often

available to dedicate to one application. Since the overall data rate is comparatively low (in the tens of kbps), a low cost, low frequency, programmable signal generator can supply just the modulation input to the amplifier. The amplifier may be a combination oscillator-transmitter described in the next section.

## 3.2 Oscillator-Transmitter (Transmixer)

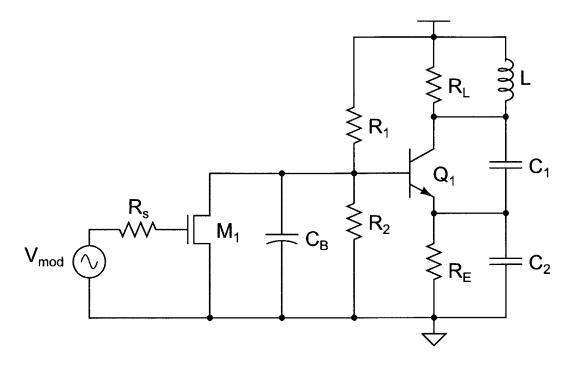

A Colpitts oscillator solves the problem of the oscillator-transmitter. The circuit can be tuned to oscillate at 13.5MHz. Next, a data input can be used to turn the oscillator on and off. Hence, the oscillator is simultaneously a transmitter and a mixer.

The schematic of the oscillator, with the modulation input, is shown in Figure 3-3. Operation of the oscillator can be explained as follows: For now, ignore the transistor  $M_1$  and the input  $V_{mod}$ . The remaining circuit is the Colpitts oscillator. Resistors  $R_1$  and  $R_2$  set a DC bias at the base of  $Q_1$ . Capacitor  $C_B$  is chosen large enough that the base of the transistor is at AC ground. The oscillator is essentially a common-base amplifier with positive feedback. Although drawn somewhat strangely, the combination of L,  $C_1$  and  $C_2$  is actually a resonant tank in the collector of  $Q_1$ . This configuration is an impedance transformer, sometimes referred to as a tapped-capacitor. Ignoring the "tap" connecting  $C_1$  and  $C_2$  to the emitter of  $Q_1$ , the configuration is more recognizable as a parallel tuned load with a resonance determined by L and the parallel combination of  $C_1$  and  $C_2$ . Thus, the frequency of oscillation is given by:

$$f_0 = \frac{1}{2\pi\sqrt{L\frac{C_1C_2}{C_1 + C_2}}} \tag{3.2}$$

In order to guarantee that oscillations will start up, we must determine an expression for the loop transmission, and choose component values such that the loop transmission is greater than one. If we view the circuit as a unidirectional common-base amplifier, we can see that any voltage that appears at the collector of  $Q_1$  is fed back to the emitter via the "tap" on the capacitive voltage divider due to  $C_1$  and  $C_2$ .

The tapped-capacitor structure also causes any impedance in the emitter to appear in parallel with the load, but transformed up by a factor of  $n^2$ , with:

$$n = \frac{C_1 + C_2}{C_1} \tag{3.3}$$

This impedance transformation only occurs near resonance. A more complete discussion of the tapped-capacitor is in [10].

The loop transmission at resonance is then given by:

$$(\omega_0) = g_m \cdot \left( R_L \parallel n^2 \cdot \left( R_E \parallel \frac{1}{g_m} \right) \right) \cdot \frac{1}{n}$$

(3.4)

where  $g_m$  is the small-signal transconductance of  $Q_1$ . It is acceptable in this case to use the small-signal  $g_m$  because we are simply testing for a loop transmission of greater than unity to ensure start-up. The signal amplitudes initially are small, which justifies this approach. The oscillation itself, of course, cannot be described using only small-signal analysis.

In this design, the impedance looking into the emitter of  $Q_1$  is  $\frac{1}{g_m}$ , except at low frequencies. This is because at 13.5MHz, the base biasing resistors have been adequately bypassed by  $C_B$ , and therefore do not contribute to the emitter input impedance. At a standard bias current of 1mA at room temperature, this impedance is about 25 $\Omega$ . Most practical values of  $R_E$  will be much larger than 25 $\Omega$ . The total impedance at the emitter node is  $\left(R_E \parallel \frac{1}{g_m}\right)$ , but under these conditions it is approximately  $\frac{1}{g_m}$ . Likewise, most practical values of  $R_L$  will be quite large, even in comparison to  $n^2 \cdot \frac{1}{g_m}$ . An explicit  $R_L$  need not be used. It can be due entirely to the equivalent parallel impedance of the LC tank at resonance. For example, a  $1\mu H$  inductor with a Q of 50 at 13.5MHz has a parallel equivalent impedance of  $5k\Omega$ . For values of n < 4, we can also ignore  $R_L$  in calculating the load impedance, since it is set by the lower impedance,  $n^2 \cdot \frac{1}{g_m}$ . In this situation, the loop transmission simplifies to:

$$L\left(\omega_{0}\right) \approx n\tag{3.5}$$

Table 3.1 shows a table of design values used in this Colpitts oscillator.

Table 3.1: Colpitts Oscillator Design Values.

| Parameter             | Value                               |

|-----------------------|-------------------------------------|

| Oscillation Frequency | 13.5MHz                             |

| $Q_1$                 | 2N2222                              |

| $M_1$                 | NDS351AN                            |

| $R_1$ and $R_2$       | $10 \mathrm{k}\Omega$ potentiometer |

| $C_b$                 | 1nF                                 |

| $R_L$                 | not used                            |

| $igl[ R_E igr]$       | $330\Omega$                         |

| L                     | 700nH                               |

| $C_1$                 | 220pF, tunable                      |

| $C_2$                 | 680pF                               |

| n                     | 4                                   |

#### 3.3 Modulation

Unlike the Class C power amplifier, which we had to drive at the carrier frequency, the oscillator-transmitter is capable of generating its own carrier frequency. With the Class C amplifier, we could amplitude modulate the carrier simply by alternately driving and grounding the gate of the MOS transistor in Figure 3-1. How does one modulate the amplitude of the output of the colpitts oscillator? The most reliable, linear way of changing the output amplitude is to modulate the supply voltage. However, this is impractical and unnecessary because we are only interested in on/off modulation. The solution we propose to this problem is the addition of  $M_1$  in Figure 3-3.

$M_1$  is operated as a switch. If its gate is grounded, then it behaves as an open circuit and is effectively removed from the circuit. If the gate is driven high, the switch turns on and creates a low impedance path to ground, discharging  $C_B$ . As the base of  $Q_1$  is brought to ground, the oscillation quickly dies. When  $M_1$  is opened,  $C_B$  begins to charge through  $R_1$  and  $R_2$ . As  $Q_1$ 's base returns to its normal operating point, the oscillation restarts.

This technique has been effective in laboratory tests at data rates exceeding

Figure 3-3: Colpitts Oscillator-Transmitter Schematic.

100kbps. However, pushing the data rate higher, which is not currently required by this application, would require some additional design modifications. The main limitation on the data rate is how quickly the oscillation can restart. The time-constant associated with  $C_B$  is  $\tau = (R_1 \parallel R_2) C_B$ . Reducing this time constant can increase the data rate. However, one must be careful not to raise the high-pass pole too high, since it is important to keep the base at AC ground. A similar modulation technique was reported in [21].

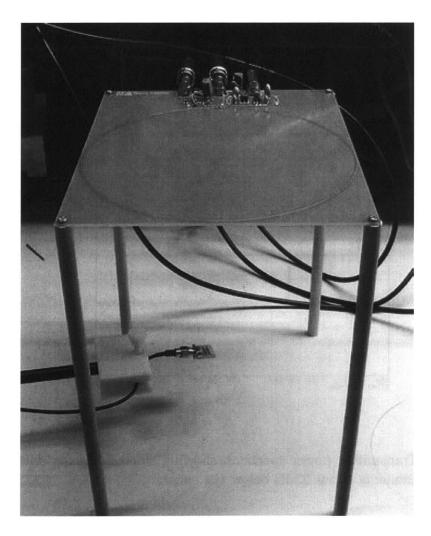

Figure 3-4: Photograph of the wireless transmitter. The transmitter coil is a single-turn PCB trace.

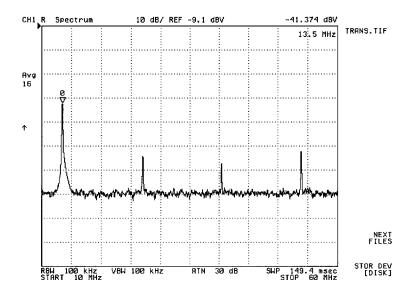

Figure 3-5: Transmitter power spectrum showing sidebands from data modulation. The first harmonic is about 23dB below the carrier.

# Chapter 4

# Electrode Modeling and

# Measurement

#### 4.1 Introduction

The purpose of this chapter is to review some basic principles of electrodes and electrochemistry that are needed for understanding neural stimulation. Electrodes provide the interface between the electrical and chemical domains. In neural stimulation, the purpose of the electrode is to interface the stimulator circuitry with the neural tissue. Neural stimulation uses charge balanced, biphasic pulses of current to artificially induce neurons near the electrode to fire. In particular, we would like to know what impedance the electrode will present to the current drivers.

Electrochemical cells always consist of at least two electrodes. In experiments, the electrode under observation is termed the working electrode, and the secondary electrode for carrying the return current is called the counter electrode. Sometimes a third reference electrode is used as well. Implanted neural stimulation electrodes may be modeled by an electrochemical cell consisting of the stimulating (working) and counter electrodes, and tissue, which may be modeled as a 0.9% NaCl electrolyte (physiological saline). In Section 4.2, we will look at electrode modeling, and in Section 4.3, we will look at some electrode measurements. A more detailed treatment of electrodes as they apply to neural stimulation may be found in [9,14], and a more

## 4.2 Electrode Modeling

#### 4.2.1 The Randles Model

The Randles model is a composition of electrical circuit elements that ideally behave identically to a real electrode in solution. However, this model is limited to small-signal excitations. Unfortunately, constant current drives for neural stimulation do not typically fall into the category of small-signal. Nevertheless, the Randles model is a good starting point for our investigation.

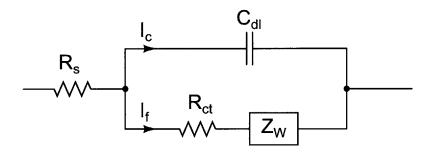

Figure 4-1 shows the general Randles model of the electrode. The model details two current paths,  $I_c$  and  $I_f$ .  $I_c$  is the current that charges the double-layer capacitance,  $C_{dl}$ . The other current path,  $I_f$ , represents the Faradaic current. Faradaic currents correspond to the oxidation or reduction of chemical species. The flow of Faradaic current is limited by the sum of two impedances,  $R_{ct}$  and  $Z_W$ . Physically,  $R_{ct}$  is the charge transfer resistance, or the impedance opposing an electron trying to transfer from the surface of the electrode into the electrolyte, and vice-versa. The Warburg impedance,  $Z_W$ , represents limitations on mass transport by diffusion inside the solution. The Warburg impedance is also frequency dependent.  $R_s$  is a general solution resistance, set by the conductivity of the electrolyte itself. Both the Faradaic and charging currents must pass through the solution resistance.

Figure 4-1: Randles electrode model.

#### 4.2.2 The Double-Layer Capacitance

One of the most significant features of electrode impedance is the double-layer capacitance. To get a general idea of how the Faradaic and charging currents interplay, first consider the Randles model of the electrode, shown in Figure 4-1. If a sufficiently large DC step in potential is applied to the working electrode in an electrochemical cell, initially a large current,  $I_c$ , flows to charge the double-layer capacitance. The charging time constant is set by the product of the double-layer capacitance,  $C_{dl}$ , and the series solution resistance,  $R_s$ . In fact, the charging of this capacitance is what actually causes polarization of the electrode. Once the capacitance charges appreciably, the Faradaic current due to redox processes,  $I_f$ , begins to take over and eventually dominates the total electrode current. After a few RC time constants, the double-layer charging current falls below detectable levels.

Physically, the double-layer capacitance arises due to a diffuse charge region in the electrolyte near the surface of the electrode. The geometry is similar to that of a parallel plate capacitor, where the top plate is the electrode itself, and the bottom plate is formed from charges in solution piling up near the electrode. The separation between the "plates" is on the order of molecular scales; hence the double-layer capacitance can be quite large. The parallel plate view of the double-layer capacitor is known as the Helmholtz model.

Unfortunately, the Helmholtz model is not accurate because it predicts  $C_{dl}$  is a constant. It also does not account for the fact that real charge distributions in solution do not take the shape of a parallel plate, but rather are most heavily concentrated near the electrode, and then taper off. One can define the thickness of the diffuse charge region as where the strength of the electrostatic forces fall below that of thermal processes. The Gouy-Chapman capacitance model takes into account the average distance of the separation between charges on the surface of the electrode and charges in solution. This improved model also takes into account the fact that as the electrode becomes more heavily polarized, the double-layer capacitance actually increases. The diffuse charge region shrinks under strong polarization, which results

in an increased capacitance. However, the double-layer capacitance does not increase without bound as the applied potential increases because the charge separation cannot become infinitely small. The Stern model improves the Gouy-Chapman model to account for this limit.

For the purposes of estimating the double-layer capacitance of an electrode, we can simply apply the Gouy-Chapman formula in Equation 4.1 with the applied potential,  $\phi_0$ , set to zero.  $C^*$  is the bulk concentration of the electrolyte in moles per liter. In this thesis, all experiments are performed in 0.9% NaCl solution, which has a molarity of 0.153. Therefore, we can calculate from Equation 4.1 the double-layer capacitance to be  $89\mu F/\text{cm}^2$ . For the  $50\mu$ m diameter electrodes used in this thesis, we can expect  $C_{dl} \approx 2\text{nF}$ .

$$C_{dl} = 228zC^{*1/2}\cosh(19.5z\phi_0)\,\mu F/\text{cm}^2$$

(4.1)

#### 4.2.3 The Solution Resistance

The solution resistance arises because all the electrode current, both Faradaic and charging, must pass through the solution to the cell's counter electrode. One model for the solution resistance, the hemispherical model, is derived in [14]. The result is presented here in Equation 4.2:

$$R_{hemi} = \frac{\rho}{2\pi a_0} \tag{4.2}$$

where  $\rho$  is the resistivity of the solution and  $a_0$  is the radius of the working electrode. It is assumed that the counter electrode has a significantly larger radius than the working electrode. A typical value for the resistivity of the physiological saline used in this thesis is  $85\Omega$ ·cm. For the  $50\mu$ m diameter electrodes, the hemispherical model predicts about  $5.5\mathrm{k}\Omega$  of solution resistance. From this equation, we see that the solution resistance scales directly with electrody and inversely with electrode radius.

An alternative model of the solution resistance is the disk model. Instead of the

electrode current spreading from a hemisphere, it spreads from a disk. The disk model, given in Equation 4.3 has the same dependencies as the hemispherical model, but is a factor of  $\pi/2$  greater. The disk model predicts a solution resistance of  $8.6k\Omega$ .

$$R_{disk} = \frac{\rho}{4a_0} \tag{4.3}$$

### 4.2.4 The Warburg Impedance

The Warburg impedance is one component of the impedance that sets the Faradaic current. Usually, it dominates the charge transfer resistance, i.e., most chemical reactions are mass transfer limited rather than charge transfer limited. Physically, the Warburg impedance arises from a diffusion current in the cell. As reactants in the cell are either oxidized or reduced, a concentration gradient arises in the cell due to a depletion of reactants near the electrode-electrolyte interface. This gradient is what allows for mass transport. More reactant will diffuse towards the interface to fuel the reaction. The Warburg impedance can be solved for by assuming a small, sinusoidally varying input to a semi-infinite RC transmission line. The Warburg impedance has a  $1/\sqrt{\omega}$  dependence on frequency.

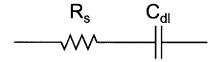

## 4.2.5 Low and High Frequency Limits

At low frequencies, the Warburg impedance and the double-layer capacitance compete to set the impedance of the cell. The impedance of  $C_{dl}$  rises linearly with decreasing frequency, but the Warburg impedance rises only with the square root of the decreasing frequency. Therefore, at extremely low frequencies,  $C_{dl}$  is effectively an open circuit, and  $Z_W$  in series with  $R_{ct}$  and  $R_s$  determine the total electrode impedance. Eventually,  $Z_W$  will also dominate  $R_{ct}$  and  $R_s$ . Strictly speaking, according to the Randles model, the Warburg impedance should have a constant phase angle of 45°. However, due to a number of simplifications in the Randles model, this is often not the case.

At high enough frequencies, the impedance of  $C_{dl}$  falls below the impedance of  $Z_W$

and effectively shorts out both components of the Faradaic impedance. The electrode impedance then appears as the solution resistance  $R_s$  in series with the double-layer capacitance  $C_{dl}$ . Figure 4-2 shows the Randles high frequency model. Electrode drive under constant current usually involves biphasic pulses which are quick enough to fall into the high frequency category.

Figure 4-2: Randles high frequency electrode model.

# 4.3 Measurement Techniques for Electrochemical Systems

Any electrochemical system may be characterized in a number of different ways. However, all techniques involve either controlling the voltage in the cell and measuring the current, or controlling the current and measuring the voltage. Within each technique, it is possible to measure the cell step response to changes in current or potential, or measure steady state response to low frequency or AC sweeps of current or potential, or any combination of the previous. However, in any electrochemical measurement, two electrodes are required. An incomplete cell with only a single electrode cannot be measured. This presents a problem because in an electrochemical system, the two electrodes are always in series. Without being able to "probe" the middle node between the two electrodes, any measurement of cell potential is just the difference of the two electrode potentials, and cannot be attributed in part to either electrode. The potentiostat, described in the next section, is an instrument which solves this problem. Fortunately, having the electrodes in series also means that measuring the current in either electrode is sufficient because both electrodes must carry the same current.

#### 4.3.1 Controlled Potential

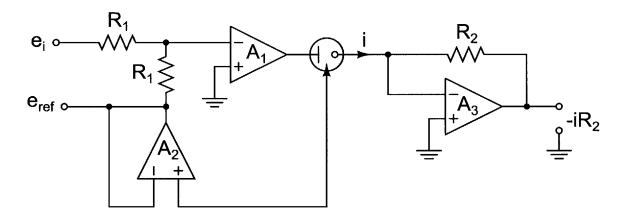

The potentiostat is a common instrument for controlling the potential of the working electrode in an electrochemical cell. Figure 4-3 is a schematic of a simple potentiostat. In the electrochemical cell in this figure, the working electrode is depicted as a circle and the counter electrode is shown as a flat plate. The counter electrode is present because without it, the cell would be incomplete and no current could flow. The third electrode in the cell, represented with an arrow, is the reference electrode. The reference electrode is what allows us to effectively "probe" inside the cell between the two electrodes.

Figure 4-3: Schematic of a potentiostat.

The potentiostat controls the potential of the working electrode with respect to the reference electrode. The reference electrode allows us to adjust the potential of the working electrode with respect to the reference without the need to control the potential of the counter electrode directly. By setting a desired potential between the working electrode and the reference, the potentiostat will drive the counter electrode to whatever potential is necessary to support the current flowing through the working electrode. The current flowing through the working and counter electrodes are necessarily the same because the reference electrode is designed such that it does not participate in any chemical reaction and therefore carries no current. Additionally, its reference potential is independent of composition of the cell.

To control the potential of the working electrode, we apply the desired potential,

$e_i$ , to the input. Since the inverting input to  $A_1$  is a virtual ground, the circuit automatically drives the counter electrode in such a way that the voltage sensed by the reference electrode becomes  $e_{ref} = -e_i$ . The reference electrode should not carry any current since any reaction taking place at the reference electrode would change its potential. The buffer  $A_2$  ensures that no current is drawn through the reference electrode. The op-amp  $A_3$  actively holds the working electrode at virtual ground. In this regard, the potential of the working electrode is equal to  $e_i$  with respect to the reference electrode. The amplifier  $A_3$  converts the cell current to a voltage so that it may be measured.

Controlled potential methods are especially useful for performing cyclic voltammetry. In cyclic voltammetry (CV), the potential of the working electrode is swept over some range while the cell current is monitored. Frequently, for low levels of polarization, negligible current is observed until a critical potential is reached, at which point an observable current corresponding to the oxidation or reduction of a chemical species begins to flow. Sweeping the potential through a complete cycle including the opposite direction can reveal information about the stability of products.

## 4.3.2 Electrode Impedance Spectroscopy

Unfortunately, CV is not directly applicable for characterizing the impedance of stimulation electrodes. Cyclic voltammetry is mainly useful in characterizing electrochemical systems that create products with DC currents, and where measurements of steady state currents versus potential are important. However, electrodes for neural stimulation are not used in this manner. In fact, a permanently polarized electrode can be extremely damaging to the electrode and the patient. In neural stimulation, electrodes are briefly charged by the stimulation current, then discharged in the opposite direction to remove all the transferred charge to ensure that there is no net DC current through the cell. A more effective technique than CV for determining cell impedance is with an AC technique called electrode impedance spectroscopy.

While the three electrode system is important for swept potential methods such as CV, where large voltages can appear even across the counter electrode, a two electrode system is sufficient for electrode impedance spectroscopy. Electrode impedance spectroscopy is a small signal measurement that applies small sinusoidal excitations swept over a range of frequencies to the cell. By measuring the current drawn, one can determine the electrode impedance as a function of frequency.

Under small signal drive, the polarization of the electrode is minimal. Therefore, we can dispense with the reference electrode and apply the potential difference to the cell directly if we are absolutely sure that the all the applied potential is dropped across the working electrode. To meet this condition, one can design the counter electrode to be much lower impedance than the working electrode. This is usually accomplished by building the working electrode out of a relatively inert material, such as platinum, and making its surface area much larger than the surface area of the working electrode. Since the current through the counter electrode and working electrodes is the same, the counter electrode will have a much lower current density and hence potential drop than the working electrode.

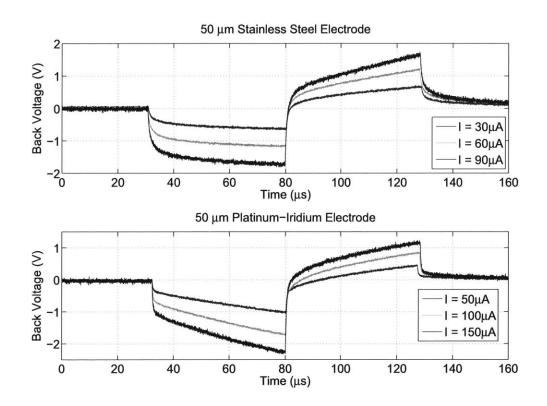

#### 4.3.3 Controlled Current

The final electrode measurement technique is controlled current. Since the implanted electrodes will be driven with biphasic pulses of current, the best way to characterize them in the laboratory is to drive them in the same manner that they will be used in the field. In constant current experiments, the working electrode is driven by a constant current, and the resulting back voltage that appears across the pair of electrodes is measured. Again, a large area counter electrode is needed to ensure that the measured potential difference is entirely attributable to the working electrode. The biphasic pulses of current are expected to last about  $100\mu$ s, which means that the Randles high frequency model should be in effect.

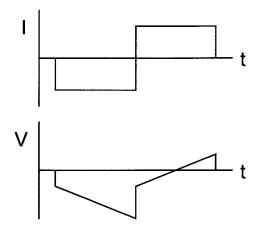

Figure 4-4 shows example current and back voltage waveforms for electrodes under biphasic constant current drive. When the pulse of current initially starts, a voltage change of  $-IR_s$  is observed, followed by a charging slope of  $\frac{-I}{C_{dl}} \text{V} \cdot \text{s}^-1$ . When the current switches direction, the back voltage moves by  $2IR_s$ , and the charges with a slope of  $\frac{I}{C_{dl}} \text{V} \cdot \text{s}^-1$ . When the current shuts off, if the pulse was precisely charge

balanced, the back voltage would return to 0.

Figure 4-4: Example current and back voltage waveforms for electrodes under biphasic constant current drive.

## 4.4 Experimental Results

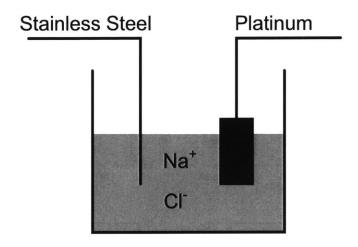

Next we took the experimental setup in Figure 4-5 into the laboratory and performed electrode impedance spectroscopy and biphasic amperometry. The working electrode is a piece of  $50\mu$ m diameter stainless steel or platinum-iridium wire clipped at the end. The counter electrode is a section of platinum with a large surface area. The impedance of the working and counter electrodes will appear in series; however, the impedance will be dominated by the working electrode because the counter electrode, with its very large relative area, is much lower impedance.

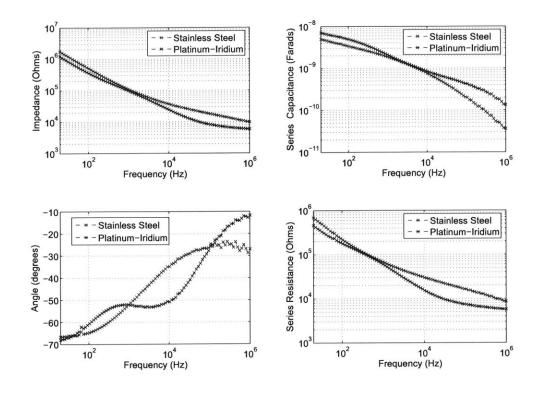

An Agilent LCR meter was used to make impedance measurements from 20Hz to 1MHz for the platinum-iridium and stainless steel electrodes in 0.9% NaCl. The 0.9% NaCl is sometimes referred to as physiological saline because it approximates the composition of living tissue. Since the driving signal is small, the electrodes are never appreciably polarized. Hence most of the measured current can be attributed to charging the double-layer capacitance. Figure 4-6 shows the measured electrode impedance spectra. The four panels show the electrode impedance magnitude and angle as a function of frequency, as well as the decomposition of the impedance into an equivalent series RC circuit in an attempt to fit the data to the high frequency

Figure 4-5: An example electrochemical cell.

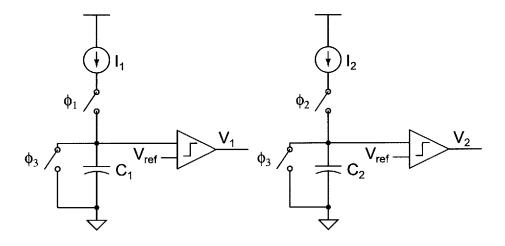

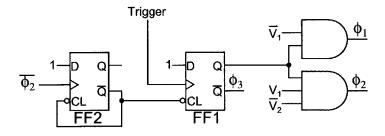

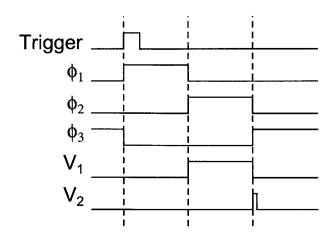

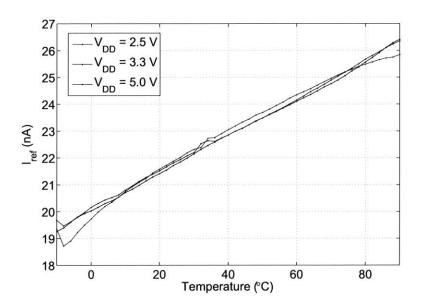

Randles model. At a frequency of 10kHz, both electrodes show close to 1nF of capacitance  $(C_{dl})$ . The resistance varies, with both being about 20k $\Omega$   $(R_s)$ .