## Run-Time Thread Management for Large-Scale Distributed-Memory Multiprocessors

by

### Daniel Nussbaum

B.S., Electrical Engineering and Computer Science Massachusetts Institute of Technology, 1985

S.M., Electrical Engineering and Computer Science Massachusetts Institute of Technology, 1988

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

at the

### MASSACHUSETTS INSTITUTE OF TECHNOLOGY MAS

MASSACHUSETTS INSTITUTE

September 1993

NOV 3 0. 1993

© Massachusetts Institute of Technology 1993

**ARCHIVES**

Certified by ..... Anant Agarwal

Associate Professor of Computer Science and Engineering Thesis Supervisor

Accepted by ...... Frederic R. Morgenthaler Chairman, EECS Committee on Graduate Students

## Run-Time Thread Management for Large-Scale Distributed-Memory Multiprocessors

by

#### Daniel Nussbaum

Submitted to the Department of Electrical Engineering and Computer Science on August 31, 1993, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

#### Abstract

Effective thread management is crucial to achieving good performance on large-scale distributed-memory multiprocessors that support dynamic threads. For a given parallel computation with some associated task graph, a thread-management algorithm produces a running schedule as output, subject to the precedence constraints imposed by the task graph and the constraints imposed by the interprocessor communications network. Optimal thread management is an NP-hard problem, even given full a priori knowledge of the entire task graph and assuming a highly simplified architecture abstraction. Thread management is even more difficult for dynamic data-dependent computations which must use online algorithms because their task graphs are not known a priori. This thesis investigates online thread-management algorithms and presents XTM, an online thread-management system for large-scale distributed-memory multiprocessors. XTM has been implemented for the MIT Alewife Multiprocessor. Simulation results indicate that XTM's behavior is robust, even when run on very large machines.

XTM makes the thread-management problem more tractable by splitting it into three sub-problems:

- 1. determining what information is needed for good thread management, and how to efficiently collect and disseminate that information in a distributed environment,

- 2. determining how to use that information to match runnable threads with idle processors, and

- 3. determining what interprocessor communication style XTM should use.

**XTM** solves these sub-problems as follows:

- 1. Global information is collected and disseminated using an X-Tree data structure embedded in the communications network. Each node in the X-Tree contains a "presence bit," the value of which indicates whether there are any runnable threads in the sub-tree headed by that node. On a machine with a sufficiently high, balanced workload, the expected cost of maintaining these presence bits is proved to be asymptotically constant, regardless of machine size.

- 2. The presence bit information, along with a combining process aided by the X-Tree, is used to match threads to processors. This matching process is shown to be eight-competitive with an idealized adversary, for a two-dimensional mesh network.

- 3. A message-passing communication style yields fundamental improvements in efficiency over a sharedmemory style. For the matching process, the advantage is shown to be a factor of  $\log l$ , where l is the distance between an idle processor and the nearest runnable thread.

Asymptotic analyses of XTM's information distribution and thread distribution algorithms are given, showing XTM to be competitive with idealized adversaries. While the solutions to the sub-problems given above have provably good characteristics, it is difficult to say anything concrete about their behavior when combined into one coherent system. Simulation results are therefore used to confirm the validity of the analyses, with the Alewife Multiprocessor as the target machine.

#### Thesis Supervisor: Anant Agarwal Title: Associate Professor of Computer Science and Engineering

## Acknowledgments<sup>1</sup>

I owe many people thanks and more for the assistance and support they lent during the time I was working on this thesis. I owe the most to Professor Anant Agarwal, my thesis advisor, for the guidance, encouragement and prodding he gave me throughout the course of the project. Many times I walked into his office convinced that this work was worthless and that the thesis would be a failure. Every time, I walked out armed with a new outlook and new and fresh ideas about how to proceed. In the time I have worked with Anant, not only have I learned about runtime systems, I have also developed ways of looking at large and complex computer systems that will be applicable throughout my career. Anant has been a pleasure to work with and to learn from.

I also want to thank Steve Ward, Bert Halstead and Baruch Awerbuch for the advice and insights I got from them. Steve and Bert not only acted as thesis readers, they also got involved early enough in the process that they could offer constructive suggestions and criticisms throughout the project. Baruch gave invaluable advice on theoretical matters. He first suggested modifying **XTM** into **XTM-C**, which seemed to be easier to write proofs for. We are currently working together on polylog-competitiveness proofs for **TTM**, **XTM** and **XTM-C**.

David Kranz, Beng-Hong Lim, David Chaiken, Kirk Johnson, Patrick Sobalvarro and Terri Iuzzolino took the time to read early, unreadable versions of this thesis. If the resulting work bears any resemblance to a coherent whole, it is through their efforts. Any remaining errors of omission, commission, awkwardness or inaccuracy are entirely my fault.

John Kubiatowicz, my office-mate, has probably borne the brunt of this thesis. He has had to put up with all kinds of annoyances, ranging from two-hour phone calls to the hurling of insults and stacks of paper. My only saving grace is that I expect no different from him when he writes his thesis.

Anne McCarthy was responsible for insulating me from most of the administrivia that can drive you crazy when other things have already pushed you over the edge. She handled all the planning for committee meetings, thesis talks and the like, and she constantly offered her assistance in any way that would save me from getting tangled up in red tape. If she had written this thesis, it would have been finished years ago.

Finally, I would like to thank my family and friends for bearing with me for all these years. There were times when I was convinced I would never finish, but my parents always kept the faith. They, more than anybody, convinced me that the long haul was worth it, and that I should see this through to the end. My brother Michael, my sister Beth and my sister-in-law Jill were also full of encouragement, willing to offer a sympathetic ear or a warm meal when the whole thing seemed overwhelming.

I can only hope that my gratitude can repay all these people for the help and support they have given me. Without them, this thesis would never have been written.

<sup>&</sup>lt;sup>1</sup>The research reported in this thesis was funded by ARPA grant # N00014-91-J-1698 and NSF grant # MIP-9012773.

## Contents

| 1 | Int | roduction                                                                         | 11 |

|---|-----|-----------------------------------------------------------------------------------|----|

|   | 1.1 | Principles for Algorithm Design in Distributed Environments                       | 12 |

|   | 1.2 | Contributions of This Thesis                                                      | 13 |

|   | 1.3 | Systems Framework and Assumptions                                                 | 16 |

|   | 1.4 | Terminology and Notation                                                          | 19 |

|   | 1.5 | Outline                                                                           | 19 |

| 2 | Bac | ckground                                                                          | 20 |

|   | 2.1 | Centralized Self-Scheduling                                                       | 21 |

|   | 2.2 | Fully Distributed On-Line Algorithms                                              | 22 |

|   |     | 2.2.1 Bidding Methods                                                             | 22 |

|   |     | 2.2.2 Drafting Methods                                                            | 24 |

|   |     | 2.2.3 Hybrid Methods                                                              | 24 |

| 3 | Hig | h-Level System Design                                                             | 27 |

|   | 3.1 | Global Information Management                                                     | 28 |

|   |     | 3.1.1 The Need for Global Information                                             | 29 |

|   |     | 3.1.2 Prospective Solutions                                                       | 30 |

|   | 3.2 | Matching Threads with Processors                                                  | 32 |

|   |     | 3.2.1 X-Tree-Based Design                                                         | 33 |

|   | 3.3 | Shared-Memory vs. Message-Passing                                                 | 34 |

| 4 | Х-Т | ree-Based Thread Management                                                       | 36 |

|   | 4.1 | X-Trees                                                                           | 39 |

|   |     | 4.1.1 Notation                                                                    | 39 |

|   |     | 4.1.2 Embedding a Tree in a $k$ -ary $n$ -Dimensional Mesh $\ldots \ldots \ldots$ | 42 |

|   | 4.2 | Updating Information in the X-Tree                                                | 47 |

|   | 4.3 | Thread Search                                                                     | 49 |

|   | 4.4 | An Example                                                                        | 50 |

| 5 | Ana | llysis                                                                            | 60 |

|   | 5.1 | One-Dimensional Case                                                              | 62 |

|   |     | 5.1.1 Search                                                                      | 62 |

|   |     | 5.1.2 Presence Bit Update                                                         | 67 |

|   | 5.2 | Two-Dimensional Case                                                              | 72 |

|   |      | 5.2.1 Search                                                       |

|---|------|--------------------------------------------------------------------|

|   |      | 5.2.2 Presence Bit Update                                          |

|   | 5.3  | <i>n</i> -Dimensional Case                                         |

|   |      | 5.3.1 Search                                                       |

|   |      | 5.3.2 Presence Bit Update                                          |

| 6 | Exj  | perimental Method 85                                               |

|   | 6.1  | NWO: The Alewife Simulator                                         |

|   | 6.2  | The PISCES Multiprocessor Simulator                                |

|   |      | 6.2.1 Timing Parameters                                            |

|   |      | 6.2.2 Inaccuracies                                                 |

|   |      | 6.2.3 Synchronization Datatypes 91                                 |

|   | 6.3  | Finding the Optimal Schedule                                       |

|   | 6.4  | Thread Management Algorithms 93                                    |

|   |      | 6.4.1 Unrealizable Algorithms                                      |

|   |      | 6.4.2 Realizable Algorithms                                        |

|   |      | 6.4.3 Queue Management                                             |

|   | 6.5  | Applications                                                       |

|   |      | 6.5.1 Application Parameters                                       |

| 7 | Res  | ults 102                                                           |

|   | 7.1  | Parameters                                                         |

|   |      | 7.1.1 Machine Parameters                                           |

|   |      | 7.1.2 Thread Management Parameters                                 |

|   |      | 7.1.3 Application Parameters                                       |

|   | 7.2  | Experiments                                                        |

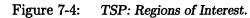

|   | 7.3  | Machine Size and Problem Size - "Regions of Interest"              |

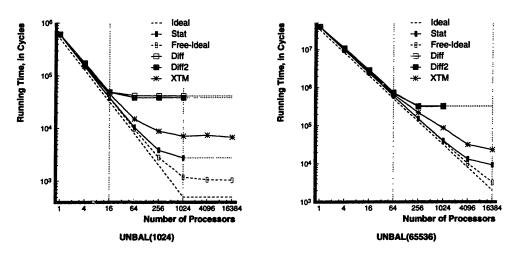

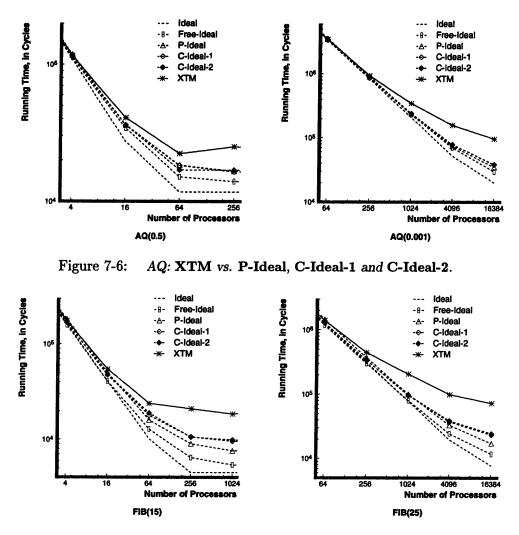

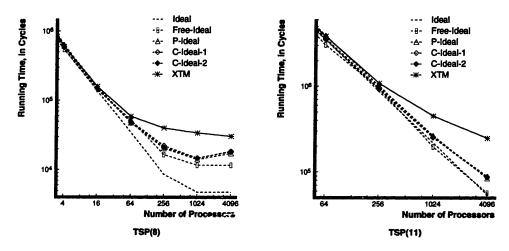

|   | 7.4  | Comparing Tree-Based Algorithms to Unrealizable Algorithms 115     |

|   | 7.5  | Comparing Tree-Based Algorithms to Other Realizable Algorithms 119 |

|   | 7.6  | Steal-One vs. Steal-Half                                           |

|   | 7.7  | Differences Between Tree-Based Algorithms                          |

|   | 7.8  | Faster Processors    128                                           |

|   | 7.9  | MATMUL: The Effects of Static Locality 132                         |

| 8 | Con  | clusions and Future Work 139                                       |

|   | 8.1  | Future Work                                                        |

| A | Pres | ence Bit Update Algorithm 143                                      |

| в | Ann  | lication Code 144                                                  |

| ~ |      | AQ144                                                              |

|   | B.2  | FIB                                                                |

|   |      | TSP                                                                |

|   |      | UNBAL                                                              |

|   | _·-  | B.4.1 Dynamic                                                      |

|   |      | B.4.2 Static                                                       |

|   | B.5        | MATMUL                           | 162        |

|---|------------|----------------------------------|------------|

|   |            | B.5.1 Common Code                | 162        |

|   |            | B.5.2 Cached Versions            | 168        |

|   |            | B.5.3 Uncached Versions          | 179        |

| С | Rav        | v Data                           | 184        |

| - |            | AQ                               | 184        |

|   |            | C.1.1 $t_n = 1$ Cycle / Flit-Hop | 184        |

|   |            | C.1.2 Variable $t_n$             | 187        |

|   | C.2        |                                  | 189        |

|   | 0.2        | C.2.1 $t_n = 1$ Cycle / Flit-Hop | 189        |

|   |            | C.2.2 Variable $t_n$             | 105        |

|   | C.3        |                                  | 191        |

|   | 0.0        | C.3.1 $t_n = 1$ Cycle / Flit-Hop | 193<br>193 |

|   |            | C.3.2 Variable $t_n$             | 195<br>195 |

|   | CA         | UNBAL $\dots$                    | 195<br>197 |

|   | 0.4        |                                  |            |

|   |            | C.4.1 $t_n = 1$ Cycle / Flit-Hop | 197        |

|   | 05         |                                  | 199        |

|   | C.5        | MATMUL: Coarse, Cached           | 201        |

|   |            |                                  | 201        |

|   | <b>a</b> a |                                  | 203        |

|   | C.6        | ,                                | 204        |

|   |            |                                  | 204        |

|   | -          |                                  | 206        |

|   | C.7        |                                  | 207        |

|   |            |                                  | 207        |

|   |            | C.7.2 Variable $t_n$             | 209        |

|   | C.8        | MATMUL: Fine, Uncached           | 211        |

|   |            | C.8.1 $t_n = 1$ Cycle / Flit-Hop | 211        |

|   |            | C.8.2 Variable $t_n$             | 213        |

## List of Tables

| 1.1        | Machine Parameter Notation 19                                   |

|------------|-----------------------------------------------------------------|

| 6.1<br>6.2 | Timing Parameters    90      Application Characteristics    101 |

| 7.1        | Experiments Performed $(t_n = 1)$ 109                           |

| 7.2        | Experiments Performed (variable $t_n$ )                         |

| 7.3        | Regions of Interest                                             |

| C.1        | AQ(0.5) – Running Times                                         |

| C.2        | AQ(0.1) – Running Times                                         |

| C.3        | AQ(0.05) – Running Times                                        |

| C.4        | AQ(0.01) – Running Times 185                                    |

| C.5        | AQ(0.005) – Running Times                                       |

| C.6        | AQ(0.001) – Running Times                                       |

| C.7        | $AQ(0.01) - t_n = 2$ Cycles / Flit-Hop – Running Times          |

| C.8        | $AQ(0.01) - t_n = 4$ Cycles / Flit-Hop – Running Times          |

| C.9        | $AQ(0.01) - t_n = 8$ Cycles / Flit-Hop – Running Times          |

| C.10       | $AQ(0.01) - t_n = 16$ Cycles / Flit-Hop – Running Times         |

|            | $AQ(0.01) - t_n = 64$ Cycles / Flit-Hop – Running Times         |

| C.12       | FIB(15) – Running Times                                         |

| C.13       | FIB(20) – Running Times                                         |

| C.14       | FIB(25) – Running Times                                         |

|            | $FIB(20) - t_n = 2$ Cycles / Flit-Hop – Running Times           |

| C.16       | $FIB(20) - t_n = 4$ Cycles / Flit-Hop – Running Times           |

|            | $FIB(20) - t_n = 8$ Cycles / Flit-Hop – Running Times           |

|            | $FIB(20) - t_n = 16$ Cycles / Flit-Hop – Running Times          |

| C.19       | $FIB(20) - t_n = 64$ Cycles / Flit-Hop – Running Times          |

|            | TSP(8) – Running Times                                          |

|            | TSP(9) – Running Times                                          |

|            | TSP(10) – Running Times                                         |

| C.23       | $TSP(11) - Running Times \dots 194$                             |

|            | $TSP(10) - t_n = 2$ Cycles / Flit-Hop – Running Times           |

|            | $TSP(10) - t_n = 4$ Cycles / Flit-Hop – Running Times           |

|            | $TSP(10) - t_n = 8$ Cycles / Flit-Hop – Running Times           |

|            | $TSP(10) - t_n = 16$ Cycles / Flit-Hop – Running Times          |

|            |                                                                 |

| C.28 TSP(10) – $t_n = 64$ Cycles / Flit-Hop – Running Times                                                                                                                             |   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| C.29 UNBAL(1024) – Running Times $\dots \dots \dots$                                    |   |

| $C.30 \text{ UNBAL}(4096) - \text{Running Times} \dots \dots$                     |   |

| C.31 UNBAL(16384) – Running Times $\dots \dots \dots$                                   |   |

| C.32 UNBAL(65536) – Running Times                                                                                                                                                       |   |

| C.33 UNBAL(16384) – $t_n = 2$ Cycles / Flit-Hop – Running Times                                                                                                                         |   |

| C.34 UNBAL(16384) – $t_n = 4$ Cycles / Flit-Hop – Running Times                                                                                                                         |   |

| C.35 UNBAL(16384) – $t_n = 8$ Cycles / Flit-Hop – Running Times 200                                                                                                                     | 1 |

| C.36 UNBAL(16384) – $t_n = 16$ Cycles / Flit-Hop – Running Times 200                                                                                                                    | ) |

| C.37 UNBAL(16384) – $t_n = 64$ Cycles / Flit-Hop – Running Times 200                                                                                                                    | ) |

| C.38 MATMUL(16) (coarse, cached) – Running Times                                                                                                                                        | , |

| C.39 MATMUL(32) (coarse, cached) – Running Times                                                                                                                                        |   |

| C.40 MATMUL(64) (coarse, cached) – Running Times                                                                                                                                        | } |

| C.41 MATMUL(64) (coarse, cached) $- t_n = 2$ Cycles / Flit-Hop – Running Times 203                                                                                                      | 5 |

| C.42 MATMUL(64) (coarse, cached) – $t_n = 4$ Cycles / Flit-Hop – Running Times 203                                                                                                      | į |

| C.43 MATMUL(64) (coarse, cached) – $t_n = 8$ Cycles / Flit-Hop – Running Times 203                                                                                                      | ; |

| C.44 MATMUL(16) (fine, cached) – Running Times                                                                                                                                          | : |

| C.45 MATMUL(32) (fine, cached) – Running Times                                                                                                                                          | : |

| C.46 MATMUL(64) (fine, cached) – Running Times                                                                                                                                          | , |

| C.47 MATMUL(64) (fine, cached) – $t_n = 2$ Cycles / Flit-Hop – Running Times . 206                                                                                                      | , |

| C.48 MATMUL(64) (fine, cached) – $t_n = 4$ Cycles / Flit-Hop – Running Times . 206                                                                                                      | , |

| C.49 MATMUL(64) (fine, cached) – $t_n = 8$ Cycles / Flit-Hop – Running Times . 206                                                                                                      | į |

| C.50 MATMUL(16) (coarse, uncached) – Running Times                                                                                                                                      | • |

| C.51 MATMUL(32) (coarse, uncached) – Running Times                                                                                                                                      | • |

| C.52 MATMUL(64) (coarse, uncached) – Running Times                                                                                                                                      |   |

| C.53 MATMUL(64) (coarse, uncached) – $t_n = 2$ Cycles / Flit-Hop – Running Times209                                                                                                     | 1 |

| C.54 MATMUL(64) (coarse, uncached) $-t_n = 4$ Cycles / Flit-Hop – Running Times209                                                                                                      |   |

| C.55 MATMUL(64) (coarse, uncached) $-t_n = 8$ Cycles / Flit-Hop – Running Times210                                                                                                      |   |

| C.56 MATMUL(16) (fine, uncached) – Running Times $\ldots \ldots \ldots$ |   |

| C.57 MATMUL(32) (fine, uncached) – Running Times                                                                                                                                        |   |

| C.58 MATMUL(64) (fine, uncached) – Running Times                                                                                                                                        |   |

| C.59 MATMUL(64) (fine, uncached) – $t_n = 2$ Cycles / Flit-Hop – Running Times 213                                                                                                      |   |

| C.60 MATMUL(64) (fine, uncached) $t_n = 2$ Cycles / Flit-Hop – Running Times 213<br>C.60 MATMUL(64) (fine, uncached) $-t_n = 4$ Cycles / Flit-Hop – Running Times 213                   |   |

| C.60 MATMUL(64) (fine, uncached) – $t_n = 4$ Cycles / Flit-Hop – Running Times 213<br>C.61 MATMUL(64) (fine, uncached) – $t_n = 8$ Cycles / Flit-Hop – Running Times 213                |   |

| 0.01 MATMOD(04) (fille, uncached) = $i_n = 0$ Oycles / Pitt-Hop = running Times 213                                                                                                     |   |

# List of Figures

| 1-1  | Self-Scheduled Model                                               | 17  |

|------|--------------------------------------------------------------------|-----|

| 1-2  | Self-Scheduled Implementation                                      | 18  |

| 2-1  | Taxonomy of Load Sharing Methods                                   | 21  |

| 3-1  | Combining Tree with Exact Queue Lengths                            | 31  |

| 3-2  | Combining Tree with Presence Bits                                  | 32  |

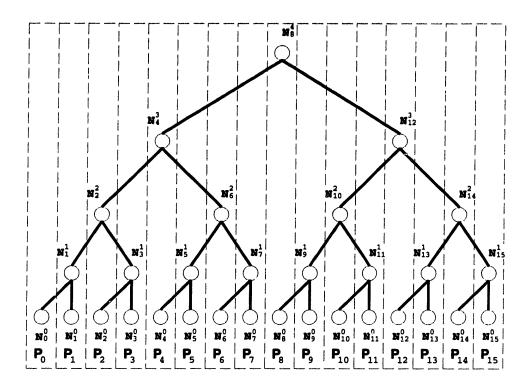

| 4-1  | Binary X-Tree on a One-Dimensional Mesh Network                    | 37  |

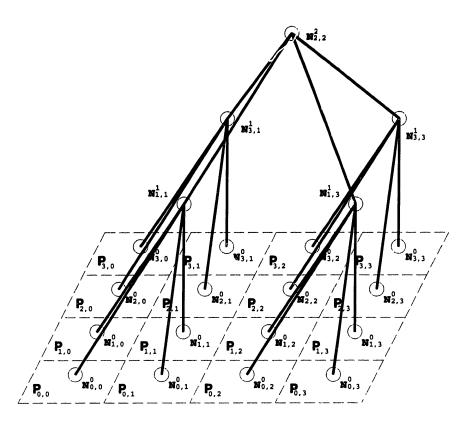

| 4-2  | Quad-X-Tree on a Two-Dimensional Mesh Network                      | 38  |

| 4-3  | Embedding a Binary Tree in a One-Dimensional Mesh: Naive Solution. | 42  |

| 4-4  | Embedding a Binary Tree in a One-Dimensional Mesh: Better Solution | 43  |

| 4-5  | Embedding a Quad-Tree in a Two-Dimensional Mesh.                   | 45  |

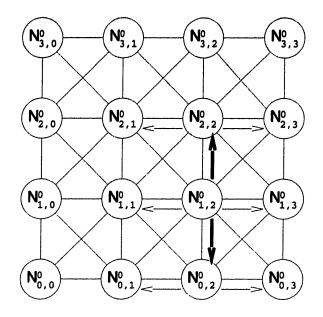

| 4-6  | Two-Dimensional Presence Bit Cache Update                          | 49  |

| 4-7  | Thread Search Example – I                                          | 51  |

| 4-8  | Thread Search Example – II                                         | 52  |

| 4-9  | Thread Search Example – III                                        | 53  |

| 4-10 | Thread Search Example – IV                                         | 54  |

| 4-11 | Thread Search Example – V                                          | 55  |

| 4-12 | Thread Search Example – VI                                         | 56  |

|      | Thread Search Example – VII                                        | 57  |

|      | Thread Search Example – VIII                                       | 58  |

|      | Thread Search Example – IX                                         | 59  |

|      |                                                                    | 00  |

| 5-1  | One-Dimensional Search – Worst Case                                | 64  |

| 5-2  | Two-Dimensional Search – Worst Case                                | 74  |

| 6-1  | The Alewife Machine                                                | 86  |

| 6-2  | NWO Simulator Organization                                         | 87  |

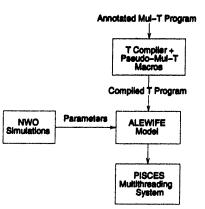

| 6-3  | PISCES Multithreader Organization                                  | 87  |

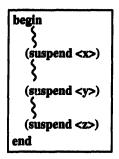

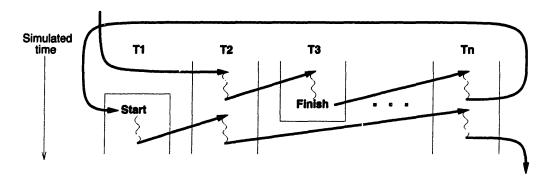

| 6-4  | A Typical PISCES Thread                                            | 88  |

| 6-5  | PISCES Thread Execution Order                                      | 88  |

| 6-6  | PISCES Alewife Simulation                                          | 89  |

| 6-7  | Thread Queue Management                                            | 97  |

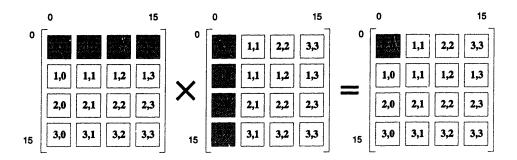

| 6-8  | Coarse-Grained MATMUL Partitioning                                 | 99  |

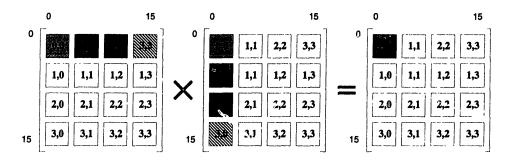

|      | Fine-Grained MATMUL Partitioning                                   | 100 |

|      |                                                                    |     |

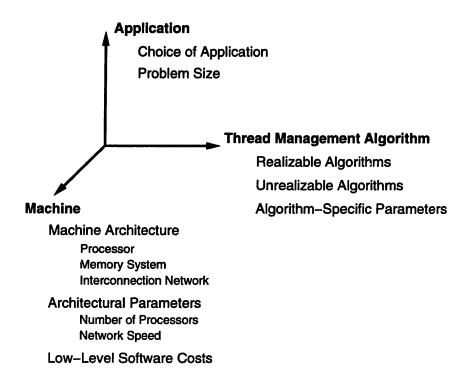

| 7-1  | Experimental Parameters                          | 105 |

|------|--------------------------------------------------|-----|

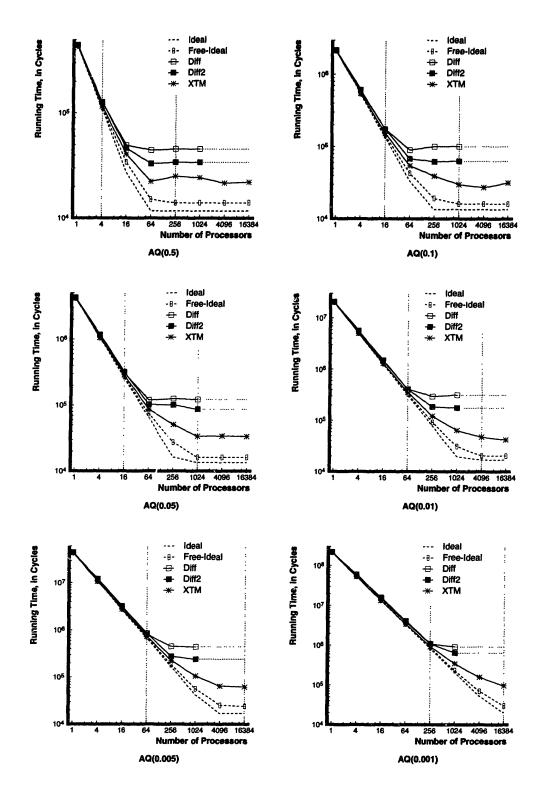

| 7-2  | AQ: Regions of Interest                          | 112 |

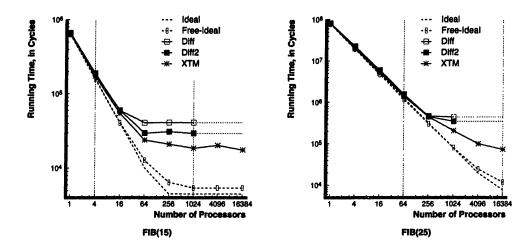

| 7-3  | FIB: Regions of Interest                         | 113 |

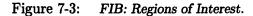

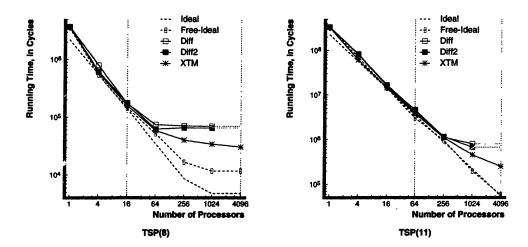

| 7-4  | TSP: Regions of Interest                         | 113 |

| 7-5  | UNBAL: Regions of Interest                       | 113 |

| 7-6  | AQ: XTM vs. P-Ideal, C-Ideal-1 and C-Ideal-2     | 115 |

| 7-7  | FIB: XTM vs. P-Ideal, C-Ideal-1 and C-Ideal-2    | 115 |

| 7-8  | TSP: XTM vs. P-Ideal, C-Ideal-1 and C-Ideal-2    | 116 |

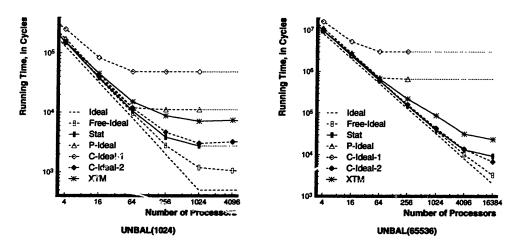

| 7-9  | UNBAL: XTM vs. P-Ideal, C-Ideal-1 and C-Ideal-2  | 116 |

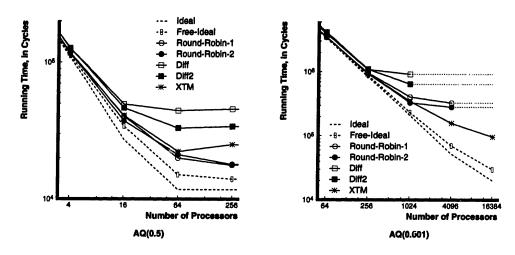

| 7-10 | AQ: XTM vs. Diff-1, Diff-2, RR-1 And RR-2        | 119 |

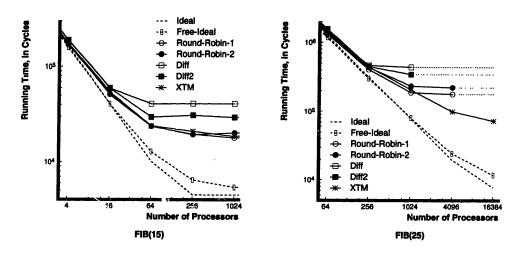

| 7-11 | FIB: XTM vs. Diff-1, Diff-2, RR-1 And RR-2       | 119 |

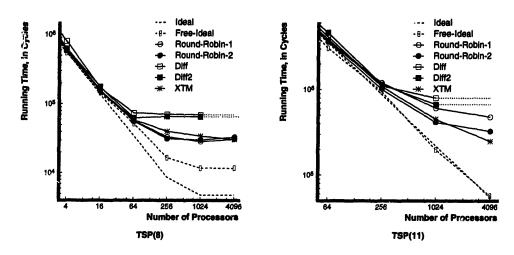

| 7-12 | TSP: XTM vs. Diff-1, Diff-2, RR-1 And RR-2       | 120 |

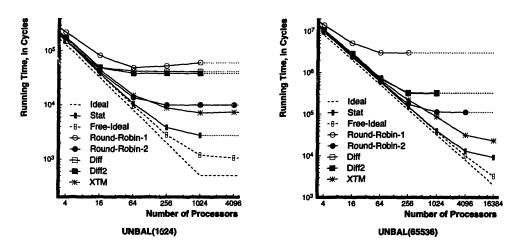

| 7-13 | UNBAL: XTM vs. Diff-1, Diff-2, RR-1 And RR-2     | 120 |

| 7-14 | Steal One vs. Steal Half                         | 123 |

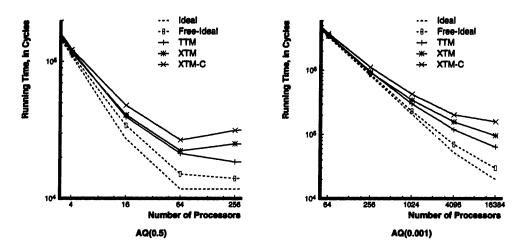

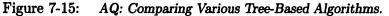

| 7-15 | AQ: Comparing Various Tree-Based Algorithms      | 125 |

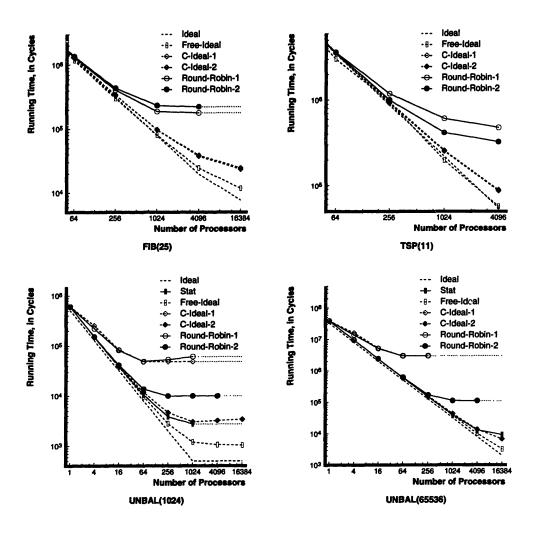

| 7-16 | FIB: Comparing Various Tree-Based Algorithms     | 125 |

| 7-17 | TSP: Comparing Various Tree-Based Algorithms     | 126 |

| 7-18 | UNBAL: – Comparing Various Tree-Based Algorithms | 126 |

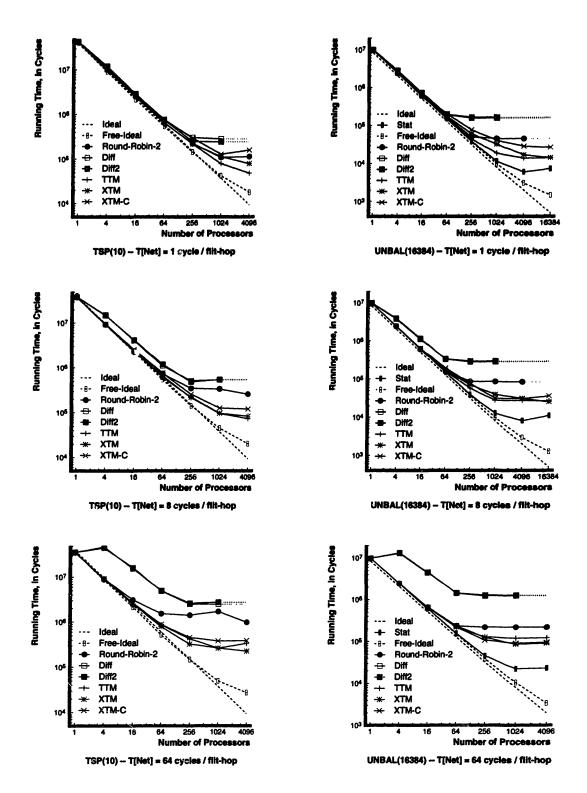

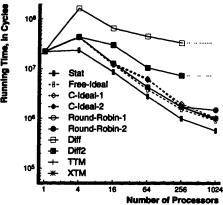

| 7-19 | AQ(0.01): Variable $t_n$                         | 130 |

| 7-20 | FIB(20): Variable $t_n$                          | 130 |

| 7-21 | TSP(10): Variable $t_n$                          | 131 |

| 7-22 | UNBAL(16384): Variable $t_n$                     | 131 |

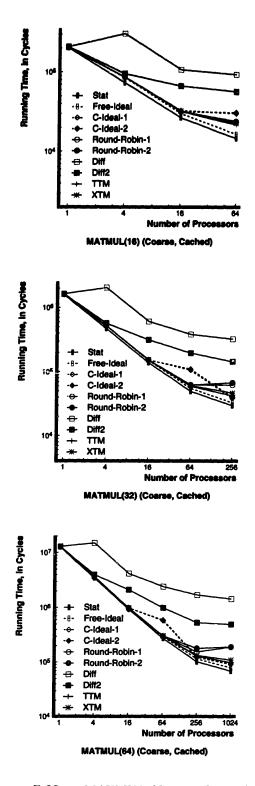

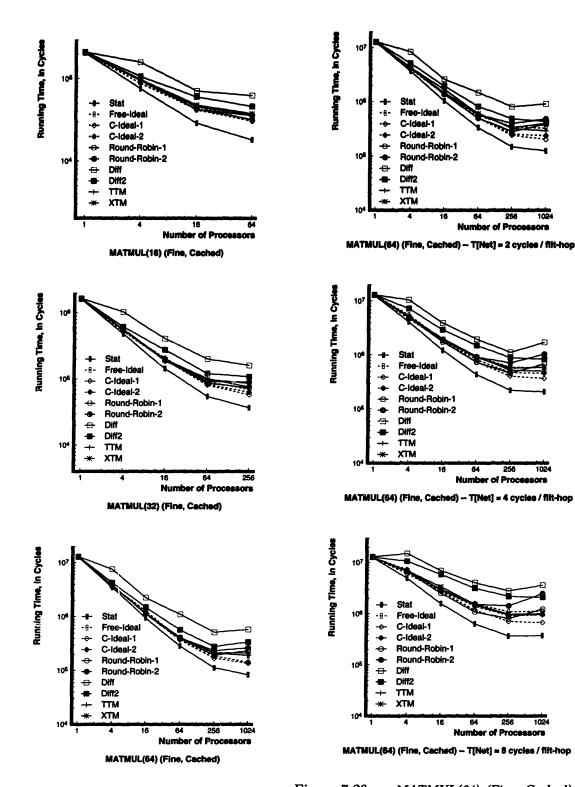

| 7-23 | MATMUL (Coarse, Cached)                          | 135 |

| 7-24 | MATMUL(64) (Coarse, Cached): Variable $t_n$      | 135 |

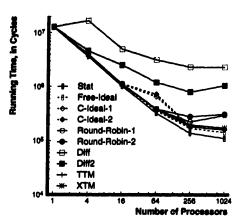

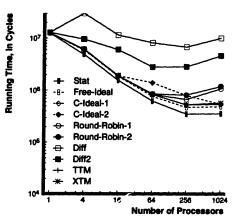

|      | MATMUL (Fine, Cached)                            | 136 |

| 7-26 | MATMUL(64) (Fine, Cached): Variable $t_n$        | 136 |

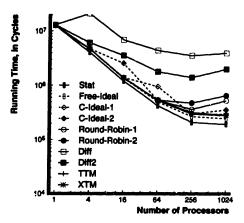

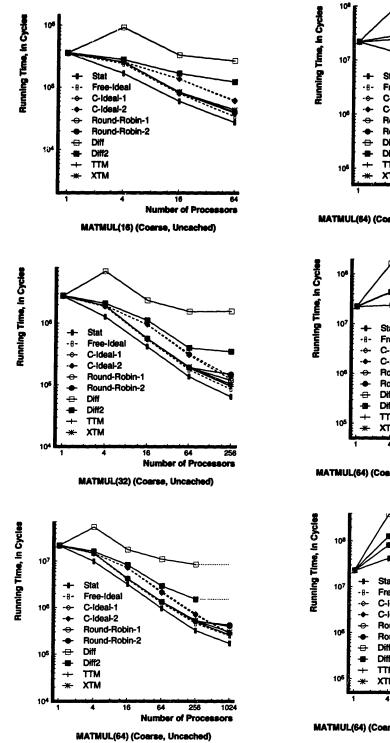

| 7-27 | MATMUL (Coarse, Uncached)                        | 137 |

| 7-28 | MATMUL(64) (Coarse, Uncached): Variable $t_n$    | 137 |

|      | MATMUL (Fine, Uncached)                          | 138 |

| 7-30 | MATMUL(64) (Fine, Uncached): Variable $t_n$      | 138 |

## Chapter 1

## Introduction

MIMD multiprocessors can attack a wide variety of difficult computational problems in an efficient and flexible manner. One programming model commonly supported by MIMD multiprocessors is the *dynamic threads* model. In this model, sequential *threads of execution* cooperate in solving the problem at hand. Thread models can be either *static* or *dynamic*. In the *static threads* model, the pattern of thread creation and termination is known before runtime. This makes it possible for decisions regarding placement and scheduling of the threads to be made in advance, either by the user or by a compiler. Unfortunately, many parallel applications do not have a structure that can be easily pre-analyzed. Some have running characteristics that are data-dependent; others are simply too complex to be amenable to compile-time analysis. This is where the dynamic aspect of the *dynamic threads* model enters the picture. If such programs are to be run in an efficient manner on large-scale multiprocessors, then efficient run-time thread placement and scheduling techniques are needed. This thesis examines the problems faced by an on-line thread-management system and presents **XTM**, an **X**-Tree-based [25, 6] **T**hread-Management system that attempts to overcome these problems.

The general thread-management problem is NP-hard [7]. The standard problem has the following characteristics: precedence relations are considered, the communications network is flat and infinitely fast, tasks take differing amounts of time to finish, preemptive scheduling is not allowed, and the thread-management algorithm can be sequential and off-line. Even if precedence relations are ignored, the problem is still NP-hard when tasks vary in

length and preemption is not allowed: it reduces to the bin-packing problem [7]. In the real world, such simplifications often do not apply: real programs contain precedence relations, communications networks are neither flat nor infinitely fast, and in order for thread management algorithms to be useful, they must be distributed and run in real time.

Since the overall problem is too difficult to tackle all at once, **XTM** breaks the threadmanagement problem down into three sub-problems, attacking each one separately. The sub-problems are identified as follows:

- 1. determining what global information is needed for good thread management and how to efficiently collect and disseminate that information in a distributed environment,

- 2. determining how to use that information to match runnable threads with idle processors, and

- 3. determining what interprocessor communication style to use.

For each of these sub-problems, we present a solution and show through formal analysis that the chosen solution has good behavior. Finally, we demonstrate, using high-level simulation results, that the mechanisms work well together.

## **1.1 Principles for Algorithm Design in Distributed Environments**

The optimal thread management problem is NP-hard, even when significantly simplified. The problem is further complicated by the requirement that it be solved in a distributed fashion. However, it is neither necessary nor practical to expect a multiprocessor thread manager to achieve an *optimal* schedule. The primary goal of such a system is to maximize processor utilization, thus minimizing overall running time. This task is especially challenging because information about the state of the machine is generated locally at the processors, but information about the state of the entire machine is needed in order to make good thread-management decisions. Collection and distribution of this type of global state information is difficult in a distributed environment. Therefore, we set forth several general principles to guide our design efforts: Eliminate ALL Hot-Spots: At any given time, the number of processors accessing a single data object and the number of messages being sent to a single processor should be limited. Otherwise serialization may result, with a corresponding loss in efficiency.

**Preserve Communication Locality:** Threads should be run physically near to the data they access, so as to minimize time spent waiting for transmissions across the communication network.

**Minimize System Overhead:** Overhead imposed by the thread manager should be kept to a minimum: time spent by a processor running system management code is time spent not running the application being managed.

Given a design choice, the path that follows these principles more closely will be more likely to attain good performance in a large-scale distributed system. Experience shows that overall system performance will suffer if any piece of the thread-management system should fail to follow any of these principles.

### **1.2** Contributions of This Thesis

This thesis examines and develops thread-management algorithms for large-scale distributed-memory multiprocessors. Guided by the design principles given above, we have developed **XTM**, a thread management system that is sound from both a theoretical and a practical perspective.

**XTM** solves the sub-problems identified above as follows:

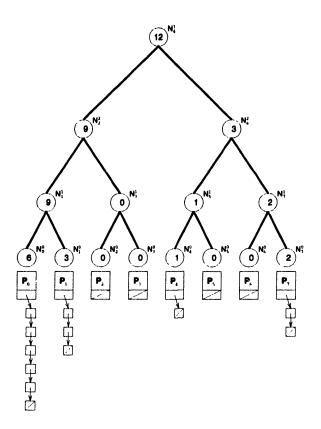

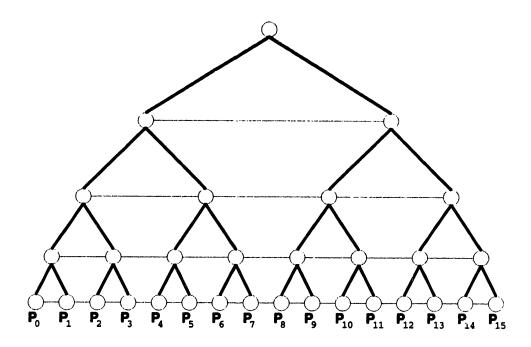

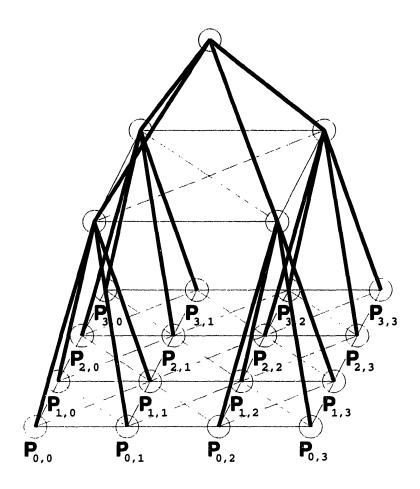

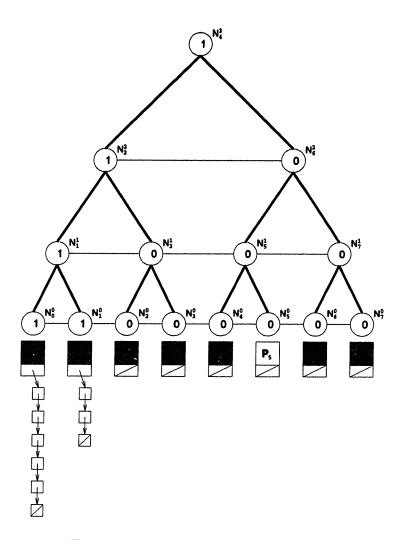

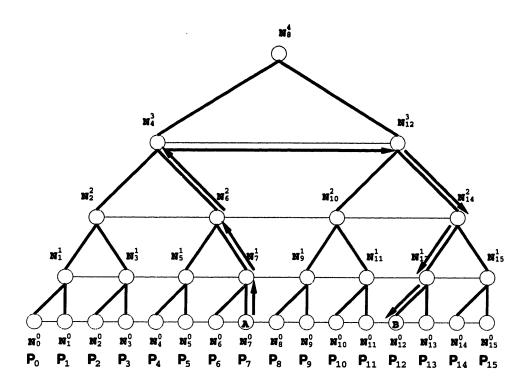

1. Global information is collected and disseminated using an X-Tree [25, 6] data structure embedded in the communications network (see Figures 4-1 and 4-2). Each node in the tree contains a "presence bit" whose value indicates whether there are any runnable threads in the sub-tree headed by that node. We show that on a machine with a sufficiently high, balanced workload, the expected cost of maintaining these presence bits is asymptotically constant, regardless of machine size. Presence-bit maintenance follows a simple or rule at the nodes of the tree. The state of a node's presence bit only changes when its *first* child's presence bit goes from zero to one, or when its *last* child's presence bit goes from one to zero. In this fashion, presence bit update messages are naturally combined at the nodes of the tree. This combining behavior has the effect of avoiding hot-spots that may otherwise appear at higher nodes in the tree and reduces **XTM**'s bandwidth requirements. Furthermore, the tree is embedded in the communications network in a locality-preserving fashion, thus preserving communication locality inherent to the application. Finally, the operations involved in maintaining global information are very simple, burdening the system with very little overhead.

2. The presence bit information, along with a combining process aided by the X-Tree, is used to match threads to processors. We show that this matching process can take no more than eight times as much time as a particular idealized (unimplementable) adversary, running on a two-dimensional mesh network.

Multiple requests for work from one area of the machine are combined at the X-Tree nodes, allowing single requests for work to serve many requesters. In this manner, large volumes of long-distance communication are avoided, and communication locality is enhanced. Furthermore, if a single area of the machine contains a disproportionately large amount of work, a few requests into that area are made to serve large numbers of requesters, therefore avoiding hot-spot behavior in that area of the machine.

3. A message-passing communication style yields fundamental improvements in efficiency over a shared-memory style. For the matching process, the advantage is a factor of  $\log l$ , where l is the distance between an idle processor and the nearest runnable thread.

The message-passing vs. shared-memory design choice boils down to an issue of locality. In a message-passing system, the locus of control follows the data; in a shared-memory system, the locus of control stays in one place. The locality gains inherent to the message-passing model yield significant performance gains that appear in both analytical and empirical results.

Chapter 5 gives asymptotic analyses of **XTM**'s information-distribution and thread-distribution algorithms that show **XTM** to be competitive with one idealized adversary.

In summary, **XTM** makes use of an X-Tree data structure to match idle processors with runnable threads. The X-Tree is used to guide efficient information distribution about where runnable threads can be found. The tree is also used to *combine* requests for work, so that a single work request can bring work to multiple idle processors. Finally, the mapping of the tree onto the physical processor array enhances communication locality of the application in a natural way, usually causing threads to run on processors near to where they were created.

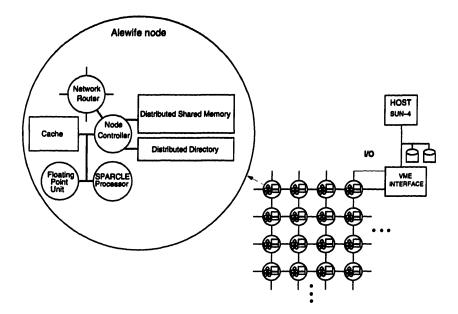

An implementation of **XTM** has been written for the MIT Alewife Multiprocessor [1, 2]. Alewife provides both an efficient implementation of the shared-memory abstraction and efficient interprocessor messages. **XTM** employs message-passing as its primary communication style. This message-passing implementation is made possible by the static mapping of the X-Tree data structure onto the physical processor array. Use of messages not only lowers the cost of primitive functions like thread creation, but it also improves communication locality over a shared-memory implementation. These locality-related gains are shown to become important as machine size increases. This thesis presents a detailed description of **XTM**. It presents asymptotic analyses of **XTM**'s information distribution and thread-distribution algorithms, showing **XTM** to be competitive with idealized algorithms. Simulation results bear out the theoretical analyses.

In the process of studying the behavior of **XTM** and other thread-management algorithms, we have come to the following conclusions, using both analytical and empirical arguments:

As machines become large (≥ 256 processors), communication locality attains a position of overriding importance. This has two consequences: First, a thread manager is itself an application. If the structure of the application is understood well enough, it can be implemented in a message-passing style, instead of using shared-memory. A message-passing implementation can achieve significant performance gains by lowering demands on the communication system. This is the case when the locus of computation follows the data being manipulated, drastically reducing the cost of ac-

cessing that data. Second, a good thread manager should attempt to keep threads that communicate with one another close together on the machine.

- Thread management is a global optimization problem. A good thread manager must therefore achieve efficient collection and distribution of relevant global information.

- Parallel algorithms for large machines must avoid hot-spot behavior, or else risk losing the benefits of large-scale parallelism. Therefore, the algorithms presented in this thesis are all fully distributed, employing *combining* techniques for the collection and distribution of the threads being managed and of the global information needed to achieve good thread management.

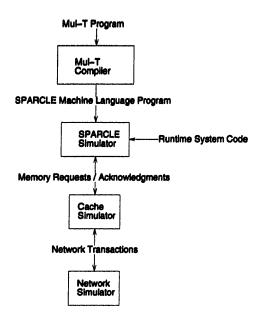

While the solutions to the sub-problems given above have provably good characteristics, it is difficult to say anything concrete about their behavior when combined into one coherent system. In order to study the behavior of different thread-management algorithms and to confirm the validity of the analyses, we developed a simulator for large-scale multiprocessors. This simulator, called PISCES, models the Alewife architecture and produced nearly all of the data comparing different thread managers on various-sized multiprocessors. These simulation results confirmed the theoretical results: for large machines, the techniques employed by **XTM** performed well. For example, a numerical integration application run on 16384 processors and managed by **XTM** ran ten times faster than the same application managed by a diffusion-based thread manager, and three times faster than the same application managed by a round-robin thread manager. In fact, the **XTM** run was within a factor of three of a tight lower bound on the fastest possible running time.

### **1.3** Systems Framework and Assumptions

The systems framework under which this research was performed has the following characteristics:

1. Thread creation is fully dynamic: a new thread may be created on any processor at any time.

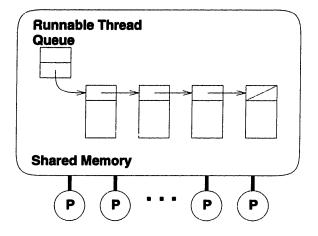

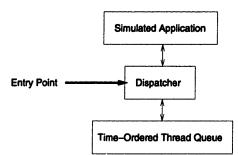

Figure 1-1: Self-Scheduled Model: Any thread can run on any processor. The processors themselves determine which thread runs on which processor.

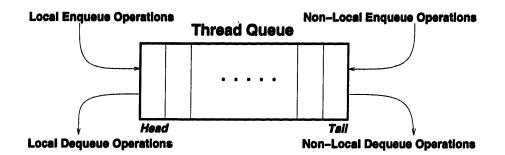

- 2. Threads follow the Self-Scheduled Model [14], as depicted in Figure 1-1. This means that the processors that execute application code also contend between themselves to decide on which processor the various threads that make up the application are run. There is no fundamental link between threads and processors: any thread can run on any processor. The actual thread queue is implemented in a distributed fashion. Every processor maintains its own local queue of threads (see Figure 1-2).

- 3. The scheduling policy is non-preemptive. A processor runs a thread until the thread either terminates or blocks on some synchronization construct. When the thread running on a processor blocks or terminates, the processor becomes *idle*: it needs to find another runnable thread to execute. The behavior of an idle processor varies significantly depending on the thread-management strategy. When a consumer-driven search is in place, idle processors search the machine for work; when a producer-driven search is being used, idle processors simply wait for more work to be delivered to them.

This non-preemptive policy places two requirements on applications being managed. First, fairness among threads that constitute an application must not be an issue. Second, deadlock issues are handled entirely by the application. We assume that applications that need a contended resource will block on a synchronization construct associated with the resource, thus taking themselves out of the runnable task pool.

Figure 1-2: Implementation of the Self-Scheduled Model: Every processor maintains a local queue of threads.

- 4. Differences between individual threads are ignored. Threads can differ with respect to such parameters as running time and communication behavior. For the purposes of this thesis, we assume that all threads run for the same amount of time.

- 5. For the purposes of formal analysis, we assume that there is no inter-thread communication. Furthermore, the shape of the application's task graph is assumed to be unknown. However, the actual implementation of **XTM** optimizes for the case where the task graph is a tree, with the likelihood of inter-thread communication between two threads diminishing with distance in the tree.

In order to analyze the performance of any algorithm on any multiprocessor, we need to know the communication structure provided by the machine. In this thesis, we examine that class of machines based on k-ary n-dimensional mesh communications networks connecting p processors, where  $p = k^n$ . Such an architecture is simple and can scale to arbitrarily large sizes without encountering wire-packing or wire-length problems for  $n \leq 3$  [5]. Similar analyses can be performed for networks with richer communication structures. In our analyses, we ignore the effects that network contention may have on performance.<sup>1</sup>

<sup>&</sup>lt;sup>1</sup>In [10], it is shown that for a large class of machines, the effect of network contention on performance is no worse than the effect of network latency, within a constant factor. This is true for all of the machines and applications simulated for this thesis.

| Parameter                                  | Description                                  |  |

|--------------------------------------------|----------------------------------------------|--|

| p                                          | Number of processors on a particular machine |  |

| $P_i$                                      | Labeling for processor number $i$            |  |

| Parameters for a k-ary n-cube Mesh Network |                                              |  |

| k                                          | Network Radix                                |  |

| n                                          | Network Dimensionality                       |  |

| $P_{i_0,i_1,,i_{n-1}}$                     | Labeling for processor with mesh coordinates |  |

|                                            | $i_0, i_1, i_{n-1}: \ 0 \le i_x \le k-1$     |  |

| $t_n$                                      | Network Speed: Cycles per Flit-Hop           |  |

Table 1.1: Machine Parameter Notation.

### **1.4 Terminology and Notation**

Table 1.1 lists notation used throughout this thesis. The parameters in Table 1.1 describe the particular machine under discussion, in terms of size, labeling, network parameters and the ratio between network speed and processor speed. A multiprocessor of a given size is referred to as a *p*-processor machine; the processors on that machine are labeled  $P_i$ , where *i* varies from 0 to p - 1. Mesh-based multiprocessors are defined in terms of *n*, their *dimensionality*, and *k*, their *radix*. On a *k*-ary *n*-cube mesh multiprocessor,  $p = k^n$ . Finally, the ratio between processor speed and network speed is given as  $t_n$ , the number of processor cycles it takes for one flit to travel one hop in the interconnection network.

### 1.5 Outline

The rest of this thesis is organized as follows. Chapter 2 presents other research in this area. Chapter 3 discusses high-level decisions that were made in the early stages of XTM's design. In Chapter 4, we give a more detailed presentation of the information-distribution and thread-distribution algorithms at the heart of XTM. These algorithms are subject to a formal analysis in Chapter 5, especially with respect to asymptotic behavior. An empirical approach is taken in Chapters 6 and 7. Chapter 6 describes the experimentation methodology used in examining the behavior of XTM's algorithms and other interesting thread-distribution algorithms; Chapter 7 compares XTM with the other thread-management algorithms, as run on several dynamic applications. Finally, Chapter 8 presents conclusions and suggestions for future research.

## Chapter 2

## Background

Although the practical aspects of thread management and load sharing have been discussed in the literature for the past decade, thread management for large-scale multiprocessors has only been seriously examined during the latter half of that period. Kremien and Kramer [13] state

...a flexible load sharing algorithm is required to be general, adaptable, stable, scalable, transparent to the application, fault tolerant and induce minimum overhead on the system...

This chapter explores the work of other investigators in this area and evaluates that work with respect to Kremien and Kramer's requirements.

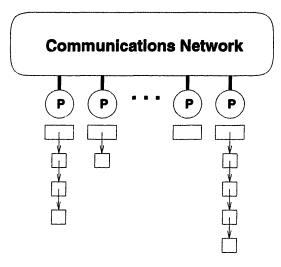

Znati, et. al. [31], give a taxonomy of load sharing algorithms, a modified version of which appears in Figure 2-1. Characteristics of generalized scheduling strategies are discussed in [16], in which the scalability of various candidate load-sharing schemes is examined, and [30], which looks at the effects of processor clustering.

In order to meet the criteria given in [13], a thread management system must be dynamic and fully distributed. In this thesis, we are especially interested in dynamic methods because we want to be able to solve problems whose structure is not known at compile time. The first widely-discussed dynamic Self-Scheduling schemes were not fully distributed; they employed a central queue, which posed no problem on small machines.

Figure 2-1: Taxonomy of Load Sharing Methods.

### 2.1 Centralized Self-Scheduling

One of the first references to the Self-Scheduling model in the literature appeared in 1985 in [14]. In this paper, the authors described Self-Scheduling, although they never explicitly named it such:

There are p processors, initially idle. At t = 0, they each take K subtasks from a job queue, each experiencing a delay h in that access. They then continue to run independently, taking batches of jobs and working them to completion, until all the jobs are done.

Assuming that the subtask running times are independent identically distributed random variables with mean  $\mu$  and variance  $\sigma^2$ , and given a requirement that K remain constant, the authors derive an optimal value for K, as a function of n (the total number of subtasks), h, p, and  $\sigma$ . They go on to show that when  $\frac{n}{p \log p} \geq 1$  and  $\frac{\sigma}{\mu} \leq 1$ , the system efficiency<sup>1</sup> is

<sup>&</sup>lt;sup>1</sup>System efficiency, for a given problem run on a given number of processors, is defined to be the total number of cycles of useful work performed divided by the total running time (in cycles) times the number

at least  $\frac{1}{1+\sqrt{2}}$ .

In 1987, Polychronopoulos and Kuck introduced Guided Self-Scheduling [21]. Their scheme, which is oriented towards the efficient scheduling of parallel FORTRAN loops, varies K with time. More specifically, whenever a processor becomes idle, it takes  $\lceil \frac{r}{p} \rceil$  jobs from the central queue, where r is the number of jobs in the queue at the time. Guided Self-Scheduling handles wide variations in thread run-times without introducing unacceptable levels of synchronization overhead. For certain types of loops, they show analytically that Guided Self-Scheduling uses minimal overhead and achieves optimal schedules.

All of the early Self-Scheduling work assumes that h is both independent of p and unaffected by contention for the central job queue. These assumptions limit this work to be only applicable to small machines.

### 2.2 Fully Distributed On-Line Algorithms

We define fully distributed algorithms to be algorithms that contain no single (or small number of) serialization points on an arbitrarily large multiprocessor. Znati, et. al. [31], divide such algorithms into three sub-categories: bidding methods, drafting methods and hybrid methods. In bidding or producer-oriented methods, the creators of new work push the work off onto processors with lighter loads. In drafting or consumer-oriented methods, processors with light workloads locate and then steal excess work from processors with heavier workloads. In hybrid methods, producers and consumers cooperate in the loadsharing process. In the rest of this section, we give examples that have appeared in the literature for each of these categories of load-sharing algorithms.

#### 2.2.1 Bidding Methods

Wu and Shu [28] present a Scatter Scheduling algorithm that is essentially the produceroriented dual of the round-robin drafting algorithm described in Chapter 6. When running

$$E = \frac{W}{pT}$$

Ì

of processors the problem was run on:

this algorithm, processor i sends the first thread it creates to processor i + 1, the second to processor i + 2, and so on. Assuming that the application is suitably partitioned, this algorithm should get a relatively even load balance on machines of small and moderate size. This expectation is borne out in the results presented in [28]. However, since producerprocessors send threads to essentially arbitrary destinations over time, any aspect of locality concerning data shared between related threads is lost. Furthermore the cost of thread creation goes up with the diameter of the machine, so on large machines, one would expect this algorithm to behave rather poorly.

Znati, et. al. [31], present a bidding scheme that takes distance between sender and receiver into account. When a new thread is created on a given processor, the processor recomputes and broadcasts its load to the rest of the system. Every processor then compares this new load with its own, taking the distance between itself and the source processor and itself into account. All processors that are eligible to receive the task based on the source processor's load, their own load and the distance between source and potential destination then contend for the job, the winner being the closest processor with the lightest load.

There are two problems with this scheme, both related to scalability. First, every time a new task is created, a global broadcast takes place. The bandwidth requirement for such a scheme is not satisfiable on an arbitrarily large machine. Second, every processor has to participate in every scheduling decision. As the multiprocessor gets large and the corresponding number of threads needed to keep it busy gets large, the thread scheduling overhead required of each processor will become unacceptably large. In fairness to the authors, one must realize that this work was done in the context of

...a loosely coupled large scale multiprocessing system with a number of processing elements interconnected through a broadcast based communication subnet...

This statement implies that the machines this algorithm is intended for are of limited size (despite the use of "large-scale"), and that the grain size of the tasks is also rather large, minimizing the effect of scheduling overhead on overall performance.

#### 2.2.2 Drafting Methods

Ni, Xu and Gendreau [20] present a drafting-style load-sharing algorithm that also seems to be oriented towards a relatively small number of independent computers connected to a single Local Area Network. In this scheme, each processor has an idea of the state of all other processors by maintaining a "load table," which has an entry for every other processor in the system. Processors can be in one of three states, light load, normal load or heavy load. As in [31], every processor in the system is informed of all changes in load on every other processor by means of broadcasts. When a processor  $P_i$  goes into the lightly loaded state, it sends a request for work to every processor in the system that it thinks is in the heavy load state. Each of those processors will respond with a "draft-age," which is a measure of how much the entire system would benefit from an exchange of work between that processor and  $P_i$ .  $P_i$  then determines which candidate will yield the highest benefit and gets work from that processor.

The same objections that applied to the scheme proposed in [31] apply here: such an algorithm isn't really scalable. Furthermore, the "draft-age" parameter used to compare drafting candidates does not take the distance between the two processors into account. This lack of attention to communication distances further limits this algorithms effectiveness on large multiprocessors.

#### 2.2.3 Hybrid Methods

#### Diffusion

Halstead and Ward proposed diffusion scheduling [9] as a means of propagating threads throughout the machine. Their description is a rather brief part of a larger picture and gives no specific details. However, the settling time for Jacobi Relaxation is proportional to the square of the diameter of the mesh upon which the relaxation takes place [3]. More sophisticated relaxation techniques, such as Multigrid methods [3], achieve much better convergence times at the expense of the locality achieved by simple diffusion methods. The XTM algorithm presented by this thesis can be thought of as the multigrid version of diffusion scheduling. We implemented both the simple diffusion scheduling algorithm described here and XTM. Results are given in Chapter 7.

#### **Gradient Model**

The Gradient Model proposed in [19] has a communication structure similar to that of diffusion scheduling. Processors are defined to be in one of three states: lightly loaded, moderately loaded or heavily loaded. Instead of moving threads based on the difference in the workload on neighboring processors, this scheme builds a gradient surface derived from estimates of the distance to the nearest lightly loaded processor. The gradient surface is defined to have a value of zero on lightly loaded processors; on every other processor, the value of the surface is defined to be one more than the minimum of its neighbors. The resulting surface gives an indication of the distance from and direction towards the nearest lightly loaded processor. The gradient surface is built by propagating information between nearest neighbors. A heavily loaded processor acts as a job source, sending jobs down the gradient in any "downhill" direction. A lightly loaded processor acts as a job sink, accepting jobs flowing towards it. A moderately loaded processor accepts jobs as if it were lightly loaded, but acts like a heavily loaded processor with respect to building the gradient. Finally, when there are no lightly loaded processors in the system, the gradient surface eventually flattens out at a maximum value equal to the machine diameter plus one. A machine in this state is said to be *saturated*.

The Gradient Model appears to scale well, independent of machine topology. However, there are some questions regarding its performance. The first question concerns the behavior of a saturated machine. In such a case, when a single processor becomes lightly loaded, a wave propagates out from that processor throughout the entire machine. In this manner, a number of tasks proportional to the square of the diameter of the machine will move between processors in response to a small local perturbation in the state of the machine. Second, gradient construction and job propagation takes place as a periodic process on every processor regardless of the state of the machine. This imposes a constant overhead on all processors independent of how well the processing load is spread about the machine: a price is paid for load-sharing whether needed or not. Finally, there is some question as to the stability of this scheme. It is easy to see that it tends to move jobs from heavily loaded processors towards lightly loaded processors; however, it seems possible to construct situations in which the time lag imposed by the propagation of gradient information could cause jobs to pile up at a single location, leading to a poor load balance at some time in the future.

#### **Random Scheduling**

Rudolph, et. al. [24], propose a load balancing scheme in which processors periodically balance their workloads with randomly selected partners. The frequency of such a load balancing operation is inversely proportional to the length of a processor's queue, so that heavily loaded machines (which have little need for load balancing) spend less time on load balancing leaving more time for useful computation. A probabilistic performance analysis of this scheme shows that it tends to yield a good balance: all task queues are highly likely to be within a small constant factor of the average task queue length.

Unfortunately, this work assumes that the time to perform a load balancing operation between two processors is independent of machine size. Clearly, in a large machine, it is more costly to balance between processors that are distant from each other than between processors that are close to each other. Since this scheme picks processors at random, the cost of a load balancing operation should rise for larger machines. Also, nothing is said in this paper about settling times or rates of convergence. The claim that a load-balancing scheme yields a balanced system is not worth much if the time it takes to achieve that balance is longer than the time a typical application is expected to run.

We have briefly surveyed a number of thread management algorithms given in the literature. For each algorithm, we have listed one or more potential problems that may be encountered when implementing the algorithm on a large-scale multiprocessor. In the rest of this thesis, we describe and evaluate a new thread management scheme that attempts to overcome all of these objections and tries to meet the requirements set forth by Kremien and Kramer [13].

## Chapter 3

## **High-Level System Design**

In this chapter, we present several high-level decisions that we made early on in the **XTM** design effort. These decisions were based mainly on the design principles given in Chapter 1: eliminate hot-spots, preserve communication locality and minimize system overhead. The details of the algorithms used by **XTM** will be given in Chapter 4. The goal of this chapter is to give the intuition behind the design of those algorithms.

As stated in Chapter 1, we break the thread management problem down into three sub-problems:

- 1. determining what global information is needed for good thread management and how to efficiently collect and disseminate that information in a distributed environment,

- 2. determining how to use that information to match runnable threads with idle processors, and

- 3. determining what interprocessor communication style to use.

Stated briefly, the high-level solutions to each of those sub-problems are:

1. Global information is collected and disseminated using an X-Tree [25, 6] data structure embedded in the communications network. Each node in the tree contains a "presence bit" whose value indicates whether there are any runnable threads in the sub-tree headed by that node.

- 2. The presence bit information, along with a combining process aided by the X-Tree, is used to match threads to processors.

- 3. A message-passing communication style yields fundamental improvements in efficiency over a shared-memory style.

In this chapter, we discuss each of these solutions in detail.

#### **3.1 Global Information Management**

In order to make good scheduling decisions, information about the state of the entire machine is needed, but this information is generated locally at the processors. A tree is a scalable data structure that can be used to efficiently collect and disseminate global information while avoiding hot-spots through combining techniques. Therefore, we use a tree-based data structure to aid in the efficient distribution of information about the state of the machine.

A tree, while good for efficiently collecting and distributing data, can create artificial boundaries where none actually exist. Processors that are physically near one another can be topologically distant from one another, depending on their relative positions in the tree, even when the tree is laid out so as to preserve as much of the locality afforded by the communications network as possible. This loss of locality can be alleviated by adding connections in the tree between nodes that are physically near each other. Such a tree, called an X-Tree, is the basic data structure upon which XTM's algorithms are based. Despain, *et. al.* [25, 6], first introduced the X-Tree data structure as a communications network topology. The particular variant of X-Tree we use is a *full-ring X-Tree without end-around connections*.

The rest of this section discusses the need for global information in solving the dynamic thread management problem. We then suggest combining trees as a mechanism for efficiently collecting and disseminating such global information.

#### **3.1.1** The Need for Global Information

As discussed in Chapter 1, thread management is essentially a global optimization problem. Even if we forego optimality, it is easy to see how global knowledge is necessary in order to make good local decisions. For example, in a system where the producers of threads are responsible for deciding where they should be run, the choice of where to send a new thread is strongly influenced by the overall state of the machine. If the machine is relatively "full," then we want to keep a newly created thread near its creator to enhance locality, but if the machine is relatively "empty," we may need to send the thread to some distant processor to improve load-sharing. Similarly, in a system where idle processors are responsible for "drafting" work, the overall state of the machine is just as important. If there is no work to be found on nearby processors, a searcher has to know what regions of the machine contain threads available to be run.

As shown in Chapter 7, diffusion methods and round-robin methods perform relatively poorly on large multiprocessors. Such thread-management algorithms share the attribute that they use no knowledge about the overall state of the machine. This seems to reduce the effectiveness of such methods, since some knowledge of overall machine state is necessary to achieve good load-sharing.

Management of global knowledge can be prohibitively expensive on large-scale machines. The minimum latency for a global broadcast is proportional to the machine diameter. Furthermore, such a broadcast places a load on the communications network at least proportional to the number of processors. If every processor continually produces information that changes the global state, it is clearly unacceptable for each processor to broadcast that information to the all other processors every time a local state change occurs. Similarly, if global information is concentrated on one node, prohibitive hot-spot problems can result. If every processor has to inform that node in the event of a change, and if every processor has to query that node to find out about changes, then the network traffic near that node and the load on the node itself becomes overwhelming, even for relatively small machines.

So the key question is the following: if global information is necessary in order to perform effective thread management, how can we manage that information in such a way as to not put an unacceptable load on any processor or any part of the communications network?

#### **3.1.2 Prospective Solutions**

As discussed in Section 1.3, we implement the global Self-Scheduled model [14, 21] by maintaining a queue of runnable threads on every processor. Therefore, the global information useful to a thread-management algorithm could potentially include the state of every one of these queues. However, the cost of keeping every processor informed of the state of every other processor's thread queue would quickly become unmanageable, even for relatively small machines, irrespective of communications architecture. Some way to distill this global information is needed, such that the cost of collecting and disseminating the distilled information is acceptable, while keeping around enough information to make good thread-management decisions.

Software combining [29] presents itself as the obvious way to keep information collection and dissemination costs manageable. When combining techniques are employed, the load on the communications network can be held to an acceptable level. Furthermore, if one is careful, certain combining strategies can guarantee an acceptably low load on all processors, even ones that contain nodes high up in the combining tree. Consequently, we require that the global information used by the thread manager must be organized in such a manner that combining techniques apply: any operation used to distill two separate pieces of global information into one piece must be associative.

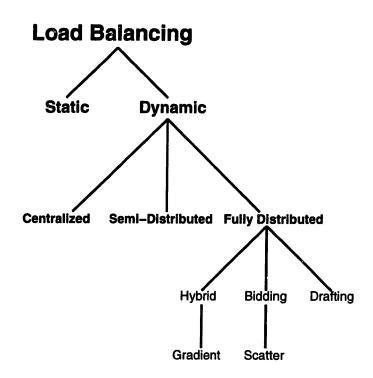

The most straightforward way to distill the state of an individual processor queue into one piece of information is to take the length of that queue. A simple sum can then be used to combine two such pieces of data (see Figure 3-1). Each node in such a combining tree keeps track of the sum of the queue lengths for the processors at the leaves of the subtree headed by that node. Unfortunately, it quickly becomes apparent that maintaining an exact sum is both expensive and impossible: impossible because of the communication delays along child-parent links in the tree, and expensive because in such a scheme, nodes near the root of the tree are constantly updating their own state, leaving no time for useful work (execution of threads).

Since maintenance of exact weights in the tree is impossible anyhow, perhaps approximate weights could keep costs acceptably low, while still providing sufficient information for the thread manager to function acceptably. In Chapters 5 and 7, we explore two such ap-

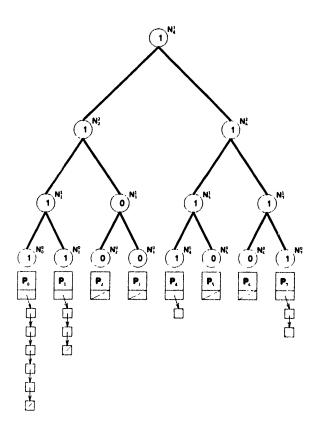

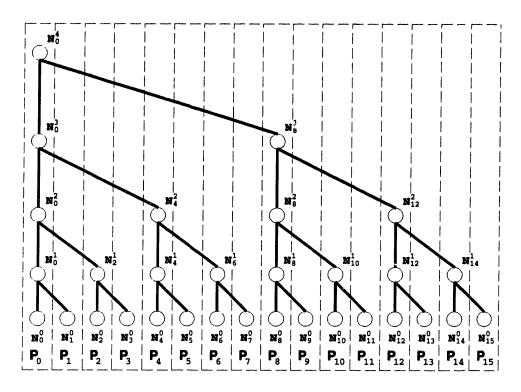

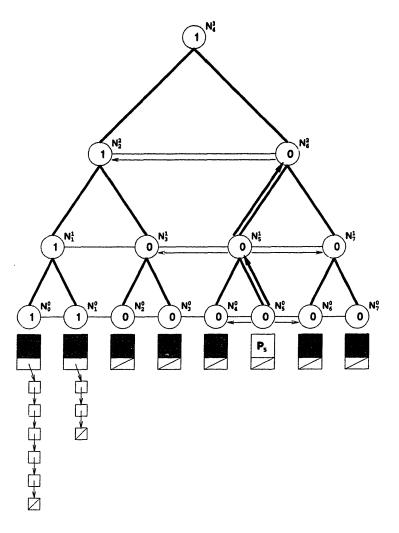

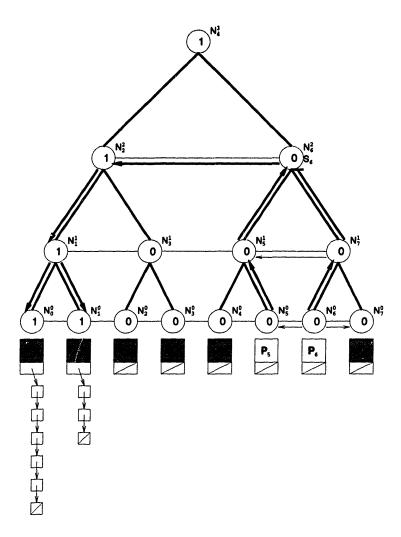

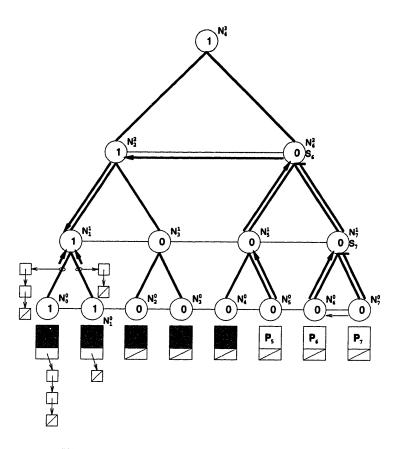

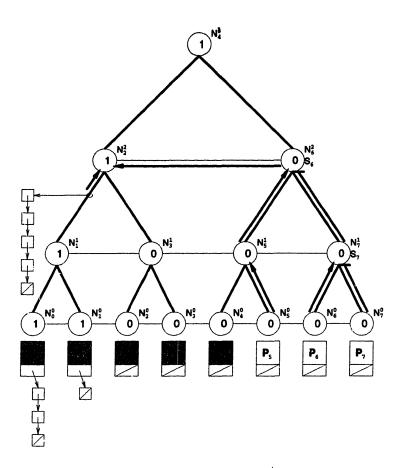

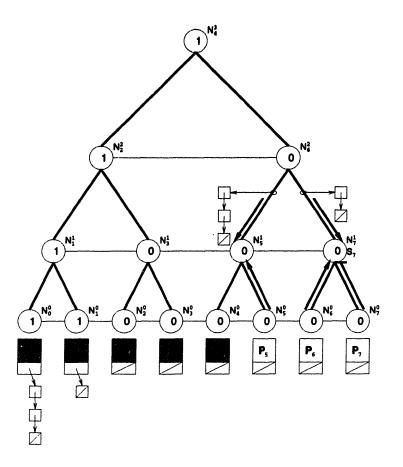

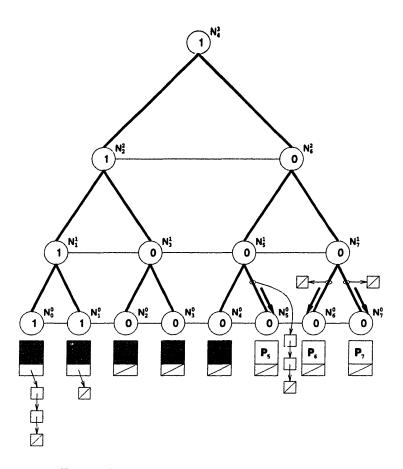

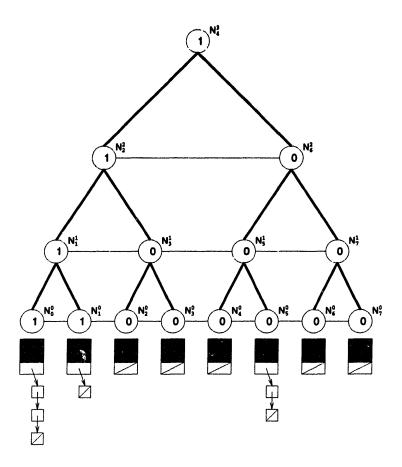

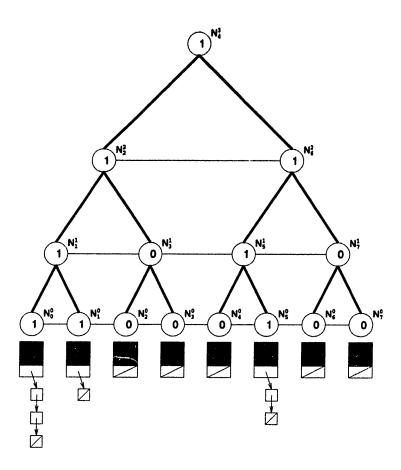

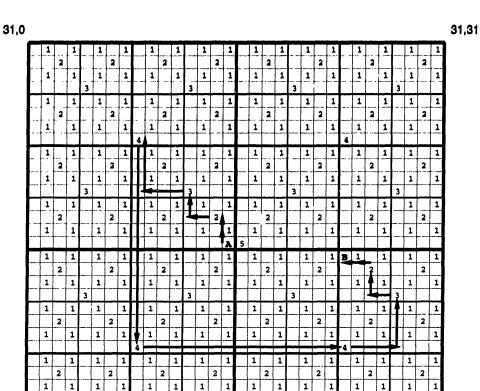

Figure 3-1: Combining Tree with Exact Queue Lengths: The tree is implemented as a data structure distributed among the various processors in the system. Each node in the tree keeps track of the total number of runnable threads on queues on the processors at the leaves of the subtree headed by that node. The rectangular boxes labeled  $P_i$  represent processors in a one-dimensional mesh. Each processor holds a queue of threads; in some cases, that queue is empty. The circles represent nodes in the combining tree. Node  $N_i^l$  represents a node at level l in the tree residing on processor  $P_i$ . Details of the mapping of tree nodes onto processors are given in Section 4.1.2.

proximation techniques. The first of these techniques maintains weights at each node of the combining tree as before, but instead of informing its parent whenever its weight changes, a node only informs its parent of a weight change that crosses one of a well-chosen set of boundaries. Details of this technique for disseminating global information are discussed more thoroughly in Section 6.4, under the heading **XTM-C**.

Results in Chapter 7 show that an even simpler approximation technique gives better practical results. Figure 3-2 illustrates this simpler approximation, which reduces the "weight" maintained at each node to a single "presence" bit. A node's presence bit is turned on when any of the processors at the leaves of the subtree headed by that node has at least one runnable thread on its queue.

Figure 3-2: Combining Tree with Presence Bits: The tree is distributed among the processors as described in Figure 3-1. Each node in the tree maintains a "presence bit," which is turned on whenever any queue on any processor at any leaf on the subtree headed by that node contains at least one runnable thread.

### **3.2** Matching Threads with Processors

In many dynamic computations, it is unavoidable that situations arise in which one area of the machine is rich with work, with most or all processors busy, while another area is starved for work, with most or all processors idle. In such situations, the communications network can easily be overloaded as work is transferred from the rich area to the sparse area. Furthermore, a tree-based algorithm is prone to hot-spot behavior at higher-level nodes. Both of these problems can be avoided if *combining* is employed: a single request can be made to serve multiple clients.

Combining techniques are not only useful for collecting and disseminating information, they can also be used to collect and disseminate the threads themselves. As an example of why combining is essential, consider the case where one section of a large machine is very busy, containing an excess of runnable threads. At the same time, some other section of the same machine is nearly idle, with very few runnable threads. If combining is not used, then drafting-style thread managers would have each processor in the idle section requesting work from the busy section, while producer-driven managers would have each processor in the busy section sending work over to the idle section. In either case, there would be many messages being sent over long distances.

We propose the use of combining to cut down on the number of long-distance messages. This combining should cause a single message to go from an idle section to a busy section, where all threads to be sent over are gathered, sent back in a single chunk, and then distributed among the idle processors.

#### 3.2.1 X-Tree-Based Design

The need for combining suggests the development of algorithms based on trees: a tree is an ideal structure around which to build algorithms that employ combining. Furthermore, trees are easy to embed in most known architectures in a natural, locality-preserving fashion. However, most communications architectures provided a richer communications structure than that of a tree. Therefore, if simple tree-based designs are used, there is a potential for a loss of locality: the tree can introduce topological boundaries where no physical boundaries exist. Locality lost in this manner can be regained by adding connections in the tree between nodes that are physically near each other. A tree enhanced with such links, introduced in [25] and [6] as a *full-ring X-Tree without end-around connections*, is the basic data structure upon which XTM's algorithms are based (see Figures 4-1 and 4-2).

In Chapter 5, we show that the nearest-neighbor links are needed to get good theoretical behavior. However, results in Chapter 7 demonstrate that for most applications, the simple tree-based design attains significantly higher performance than the X-Tree-based design. For systems in which the ratio of processor speed to network speed is higher, the X-Tree's performance surpasses the simple tree's performance.

### 3.3 Shared-Memory vs. Message-Passing

We use message-passing as the primary means of interprocessor communication. This reduces **XTM**'s communication requirements, thus increasing performance over a sharedmemory implementation. In Chapter 5 these performance gains are shown to become significant on large machines.

One of the earliest design decisions concerned programming style: should programs employ shared-memory or message-passing? This may seem odd, since any algorithm implemented in one of the two styles can be implemented in the other. However, there are compelling theoretical and practical arguments in favor of the message-passing style. This research was performed with the Alewife machine as the primary target machine. Since Alewife supports both efficient shared-memory and message-passing, we had the luxury of choosing between the two styles.

To start with, we give informal definitions of the terms "shared-memory" and "messagepassing." Briefly, the central difference between the two mechanisms is whether or not each communication transaction is acknowledged individually. In a message-passing environment, no acknowledgment is required for individual messages; in a sequentially consistent shared-memory environment, every communication transaction requires either a reply containing data or an acknowledgment that informs the requesting processor that the requested transaction is complete.

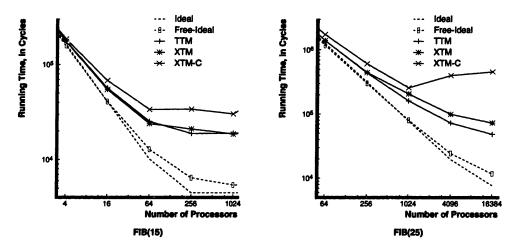

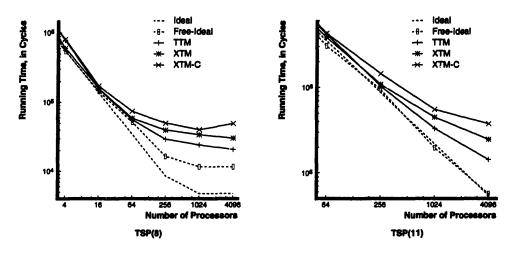

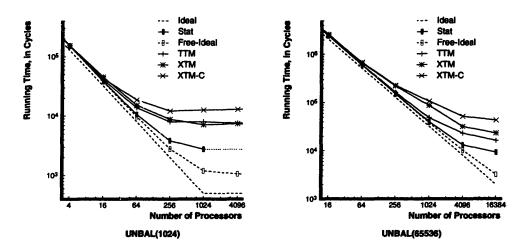

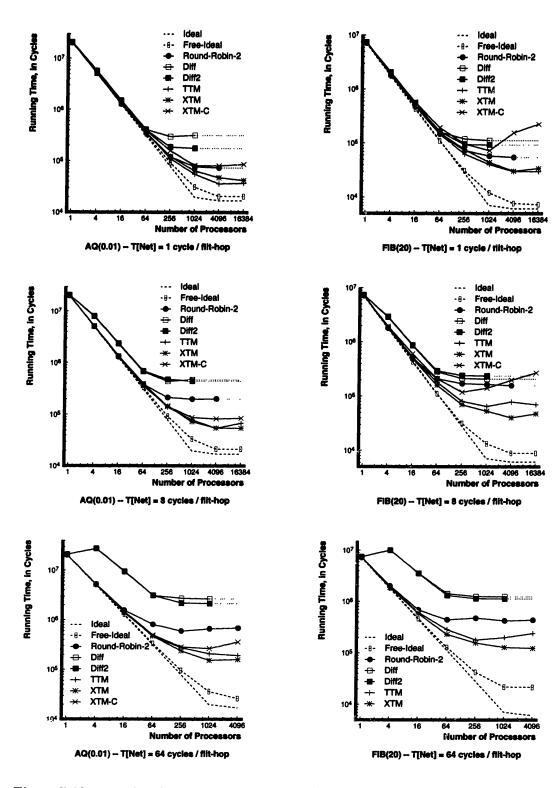

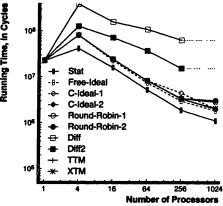

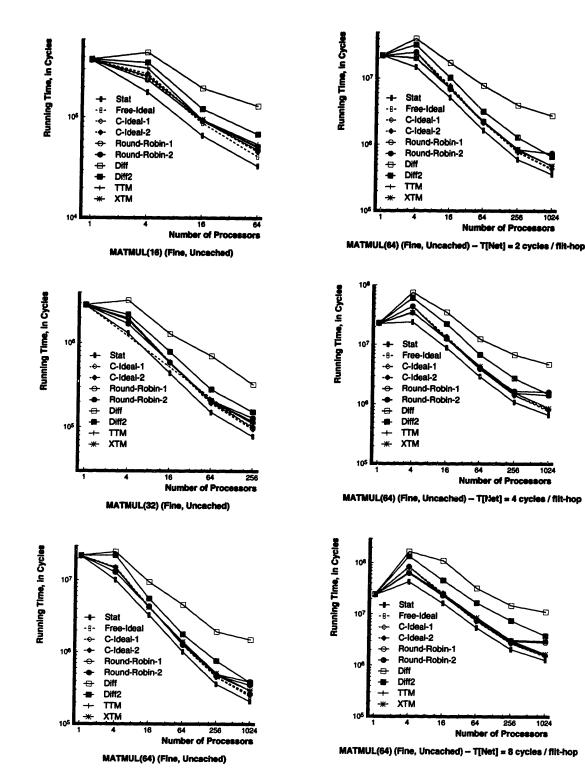

The two kinds of nodes in a shared-memory environment: processing nodes and memory nodes. Throughout this thesis, when we say shared-memory, we really mean the sequentially consistent shared-memory [17]. Communication takes place in the form of a request from a processor to a memory node, requiring an acknowledgment when the request has been satisfied. The actual low-level particulars of such a transaction depend on such machinespecific details as the existence of caches and the coherence model employed. Requests come in the form of *reads*, which require a reply containing the data being read; *writes*, which modify the data and require an acknowledgment, depending on the machine details, and *read-modify-writes*, which modify the data and require a reply containing the data.