### A MULTIPROCESSING PLATFORM FOR TRANSIENT EVENT DETECTION

by

#### UMAIR A. KHAN

### S.B. MATHEMATICS WITH COMPUTER SCIENCE MASSACHUSETTS INSTITUTE OF TECHNOLOGY (MAY 1992)

Submitted to the Department of Electrical Engineering and Computer Science in Partial Fulfillment of the Requirements for the Degree of

MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

at the

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

May 1995

© Umair A. Khan 1995 All rights reserved

The author hereby grants to MIT permission to reproduce and to distribute publicly paper and electronic copies of this thesis document in whole or in part.

· · · A I - ·

V1-16 Signature of Author\_ Department of Electrical Engineering and Computer Science May 26, 1995 Λ Certified by\_\_ Steven B. Leeb Carl Richard Soderberg Assistant Professor of Power Engineering Thesis Supervisor 11. Accepted by\_ F.R. Morgenthaler MASSACHUSERTS INSTITUTE Chairman, Department Committee on Graduate Theses OF TECHNOLOGY Barker Eng MAR 1 8 1996

LIBRARIES

#### A Multiprocessing Platform for Transient Event Detection

by

Umair A. Khan

Submitted to the Department of Electrical Engineering and Computer Science on May 26, 1995, in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering

#### Abstract

Conventional nonintrusive load monitoring relies on measurements of steady-state current and voltage for determining the operating schedule of loads of interest in a building. The Multiscale Transient Event Detector (TED) described in [1] advances the capabilities of conventional NILMs by using vector space methods to identify load transients or transient sections. The structure of the TED algorithm has significant parallelism inherent to it. This suggests the possibility of implementing the TED as a multiprocessing machine with several inexpensive processors performing the various tasks in parallel. The development of a parallel version of the sequential algorithm, the synthesis of a model for a multiprocessing platform for transient event detection based on the parallel algorithm, and the design and construction of a prototype Multiprocessing Load Monitor (MLM), were the major goals of this thesis. Data dependencies in the TED algorithm were identified and used to parallelize the TED algorithm. A model for the MLM was then developed keeping in mind complexity and reliability issues. Hardware design of the main subsystems was under taken. The MLM prototype consists of a data acquisition front-end and several computational units operating in parallel and communicating with one another. The acquisition front-end samples the analog input streams (envelopes of real and reactive power, etc.), stores and periodically transfers blocks of the digitized data to the computational modules. These 80C196-based modules may be configured to perform transient search on various time scales, time scaling of data using tree-structured decomposition [1], or result collation. They were designed to be scalable, and versatile enough to perform any of the TED operations. The MLM's user interface is implemented on a host PC, and allows, for instance, the downloading of code to the slave processors and the uploading of event detection results. The principal application of the prototype MLM was transient event detection on power load lines. The model, as well as the prototype, are general enough to allow transient detection in other environments.

Thesis Supervisor: Steven B. Leeb

Title: Carl Richard Soderberg Assistant Professor of Power Engineering

How could a blade of grass Repay the warmth from the Spring Sun.

— Meng Chio [751-814]

To my mother and my father

# Contents

| 1 | Intr | oducti  | ion and Background                               | 13         |

|---|------|---------|--------------------------------------------------|------------|

|   | 1.1  | Theore  | etical Background                                | 13         |

|   | 1.2  | Contri  | ibutions of This Work                            | 17         |

|   | 1.3  | Thesis  | Outline                                          | 19         |

| 2 | The  | Struc   | ture of the MLM                                  | <b>2</b> 1 |

|   | 2.1  | Paralle | elism in the TED Algorithm                       | 21         |

|   |      | 2.1.1   | Data Dependencies for TED Operations             | 22         |

|   |      | 2.1.2   | The Parallel Transient Event Detection Algorithm | 24         |

|   | 2.2  | Comp    | lexity/Reliability Tradeoffs                     | 25         |

|   | 2.3  | The S   | tructure of the MLM                              | 32         |

| 3 | The  | e Data  | Acquisition Front-End                            | 37         |

|   | 3.1  | The A   | nalog Preprocessor                               | 37         |

|   | 3.2  | Functi  | ional Overview of the Master Board               | 39         |

|   |      | 3.2.1   | Data Acquisition and Storage                     | 39         |

|   |      | 3.2.2   | Data Transfer to Slave Processors                | 40         |

|   |      | 3.2.3   | Host PC Communication                            | 41         |

|   |      | 3.2.4   | Control Logic                                    | 42         |

|   | 3.3  | Desigr  | n and Implementation                             | 42         |

|   |      | 3.3.1   | A/D Conversion                                   | 42         |

|   |      | 3.3.2   | Data Storage                                     | 43         |

|   |      | 3.3.3   | Slave Interface                                  | 46         |

|   |      | 3.3.4   | Control Logic                                    | 47         |

|   |      | 3.3.5   | Sampling Rate Generator                          | 50         |

|   |      | 3.3.6   | Reset Circuitry                           | 51 |

|---|------|---------|-------------------------------------------|----|

|   |      | 3.3.7   | PC Interface                              | 51 |

|   |      | 3.3.8   | Miscellaneous Hardware Components         | 53 |

|   | 3.4  | Hardw   | are Specifications                        | 54 |

| 4 | The  | MLM     | Computational Units                       | 56 |

|   | 4.1  | Design  | Overview of a Slave Module                | 56 |

|   |      | 4.1.1   | The Processing Engine                     | 57 |

|   |      | 4.1.2   | PC Interface                              | 57 |

|   |      | 4.1.3   | Master Board Interface                    | 60 |

|   |      | 4.1.4   | Inter-Slave Communication                 | 60 |

|   | 4.2  | Functi  | onal Overview of the Slave Module         | 61 |

|   |      | 4.2.1   | Event Detection                           | 62 |

|   |      | 4.2.2   | Tree-Structured Decomposition             | 66 |

|   |      | 4.2.3   | Result Collation                          | 66 |

|   | 4.3  | Slave I | Module Implementation Details             | 67 |

|   |      | 4.3.1   | Memory Section                            | 67 |

|   |      | 4.3.2   | Microprocessing Unit and Microcontrol PAL | 68 |

|   |      | 4.3.3   | PC Interface                              | 69 |

|   |      | 4.3.4   | Interconnection Details                   | 70 |

|   |      | 4.3.5   | Reset Circuitry                           | 72 |

|   | 4.4  | The M   | ILM Slave Board                           | 72 |

|   |      | 4.4.1   | PC Interface Glue Logic                   | 72 |

|   |      | 4.4.2   | Jumper Selections                         | 73 |

|   |      | 4.4.3   | Component Layout                          | 75 |

|   |      | 4.4.4   | Hardware Specifications                   | 76 |

| 5 | Soft | ware I  | mplementation of the MLM                  | 77 |

|   | 5.1  | Softwa  | re for Slave Processors                   | 77 |

|   |      | 5.1.1   | Acquisition of Input Data                 | 77 |

|   |      | 5.1.2   | Pattern Search                            | 78 |

|   |      | 5.1.3   | Software Implementation of Load Chains    | 81 |

|   |      | 5.1.4   | Template Management                       | 82 |

|    |       | 5.1.5   | Tree-structured Decomposition                 | 83  |

|----|-------|---------|-----------------------------------------------|-----|

|    |       | 5.1.6   | Result Collation                              | 85  |

|    |       | 5.1.7   | PC Communication                              | 87  |

|    | 5.2   | Softwa  | re Design of the PC interface                 | 88  |

|    |       | 5.2.1   | RISM Structure                                | 90  |

|    |       | 5.2.2   | ECM Program Structure                         | 92  |

|    |       | 5.2.3   | Communicating with the Master Board           | 93  |

|    |       | 5.2.4   | Master Board Mode Selection                   | 95  |

|    |       | 5.2.5   | Selecting a Slave Processor for Communication | 97  |

|    |       | 5.2.6   | Program Code Output Format                    | 97  |

|    |       | 5.2.7   | Template Collection                           | 98  |

|    |       | 5.2.8   | Communicating with the Slave Processors       | 103 |

|    |       | 5.2.9   | Collater Communication                        | 106 |

|    |       | 5.2.10  | Automatic Initialization of Slave Processors  | 109 |

| 6  | Pro   | totype  | Construction and Results                      | 112 |

|    | 6.1   | Develo  | opment Cycle for the MLM                      | 112 |

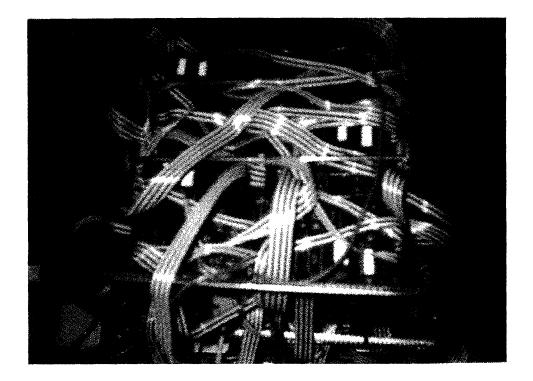

|    | 6.2   | Protot  | ype I : MLM-8S                                | 113 |

|    | 6.3   | Protot  | ype II:MLM-16S............................... | 115 |

|    | 6.4   | Result  | 8                                             | 118 |

|    | 6.5   | Summ    | ary                                           | 132 |

| 7  | Con   | clusio  | n                                             | 133 |

| Bi | bliog | graphy  |                                               | 138 |

| A  | Mas   | ster Bo | oard Schematics and Layouts                   | 140 |

| в  | Slav  | ve Boai | rd Schematics and Layouts                     | 148 |

| С  | PAI   | Code    | 3                                             | 156 |

|    | C.1   | Master  | r Board PALs                                  | 156 |

|    | C.2   | Slave I | Board PALs                                    | 177 |

| D  | Soft  | ware f  | for Slave Processors                          | 186 |

|              | D.1 Code for V-section Search              | . 187 |

|--------------|--------------------------------------------|-------|

|              | D.2 Code for Tree-structured Decomposition | . 209 |

|              | D.3 Code for Result Collation              | . 232 |

|              | D.4 Batch File for Code Compilation        | . 240 |

|              |                                            |       |

| $\mathbf{E}$ | Software for the Host PC Interface         | 241   |

|              | E.1 ECM Code                               | . 241 |

|              | E.2 Modifications Made to 80C196KC RISM    | . 280 |

| F            | PC I/O Card for MLM Control                | 283   |

| G            | The Analog Preprocessor                    | 286   |

| н            | Miscellaneous Details of Prototype Testing | 294   |

|              | H.1 V-section Sets                         | . 294 |

|              | H.2 Software for Multiple Load Activation  | . 295 |

| Ι            | The Genesis of the MLM                     | 297   |

# List of Figures

| 1.1         | Rapid Start Lamp Bank Transients in (a) Real Power (b) Reactive Power . | 15  |

|-------------|-------------------------------------------------------------------------|-----|

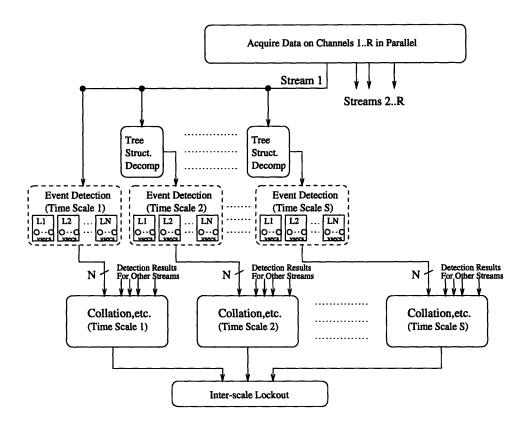

| 1. <b>2</b> | The Multiscale Transient Event Detection Algorithm                      | 16  |

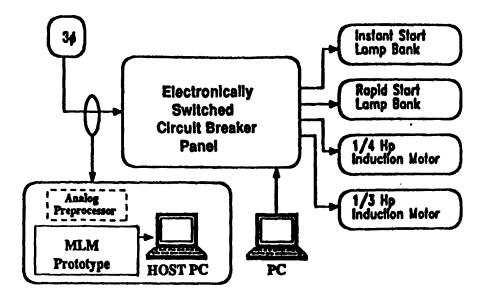

| 1.3         | The Multiprocessing Load Monitor (MLM)                                  | 18  |

| 2.1         | Data-Dependency Graph for TED Operations                                | 24  |

| 2.2         | The Parallel TED Algorithm                                              | 25  |

| 2.3         | Improving Reliability By V-section Search Over More Streams             | 30  |

| 2.4         | Identifying a Load on One Time Scale                                    | 32  |

| 2.5         | Identifying N Loads on One Time Scale                                   | 33  |

| 2.6         | A More Compact Load Assignment                                          | 34  |

| 2.7         | The MLM Model                                                           | 35  |

| 3.1         | The MLM Master Board                                                    | 40  |

| 4.1         | The MLM Slave Module                                                    | 58  |

| 4.2         | The Interconnection Circuitry for a Slave Module                        | 59  |

| 4.3         | The MLM Model                                                           | 62  |

| 4.4         | Load Chains in the MLM                                                  | 65  |

| 4.5         | Slave Board Connectors                                                  | 71  |

| 5.1         | ECM Main Menu                                                           | 93  |

| 5.2         | Displaying Channel Data                                                 | 95  |

| 5.3         | Master Acquisition Mode Submenu                                         | 96  |

| 5.4         | Slave Mode Selection Submenu                                            | 99  |

| 5.5         | Slave Communication Submenu                                             | 101 |

| 5.6         | Template Management Submenu                                             | 102 |

| 5.7  | Special Function Register Submenu                       | 105  |

|------|---------------------------------------------------------|------|

| 6.1  | Prototype Test Facility                                 | 118  |

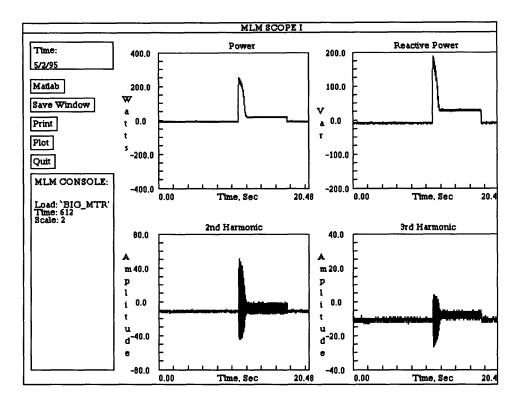

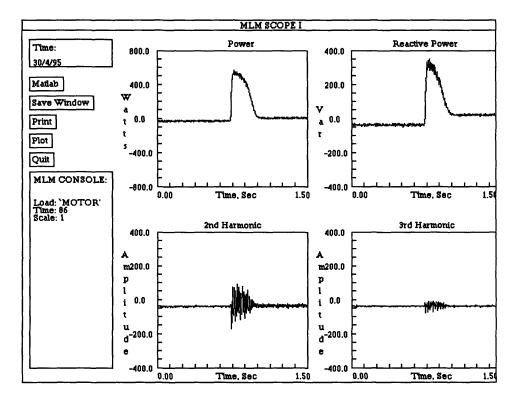

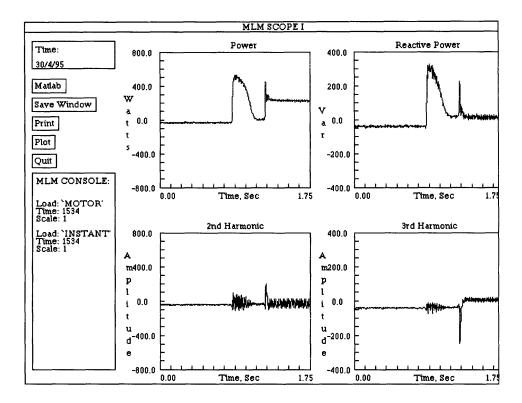

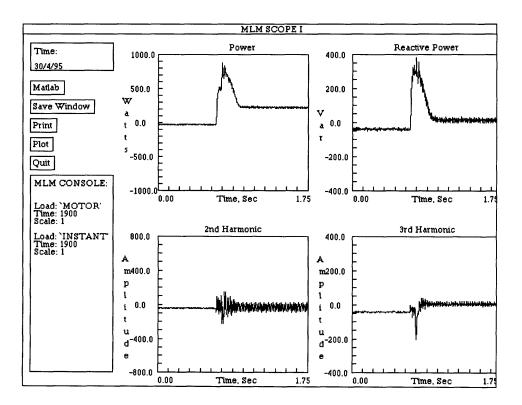

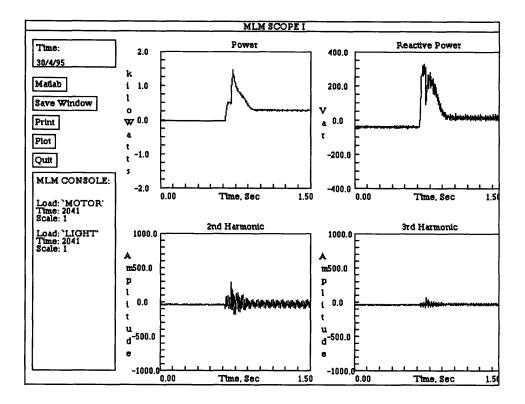

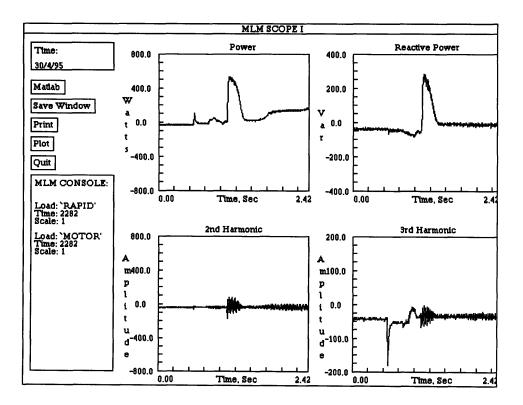

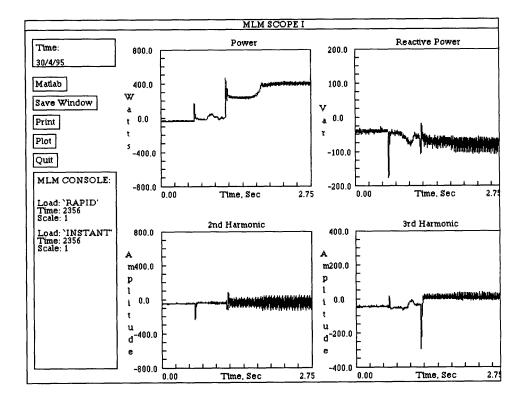

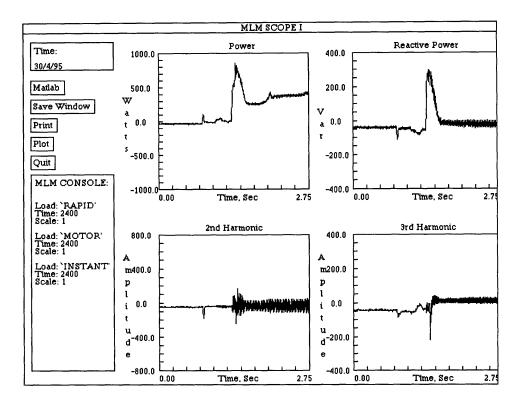

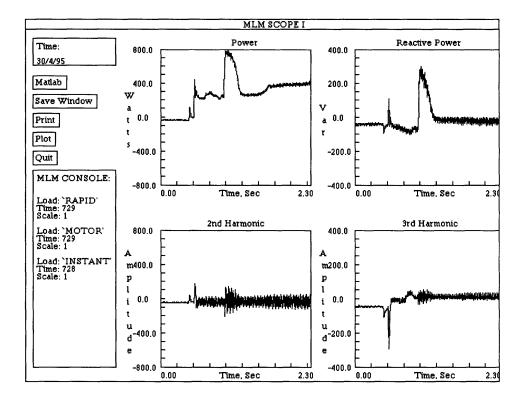

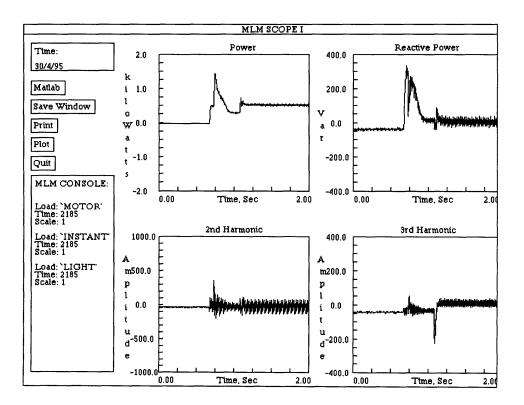

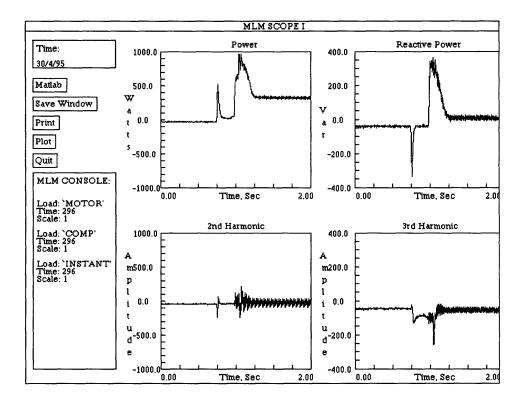

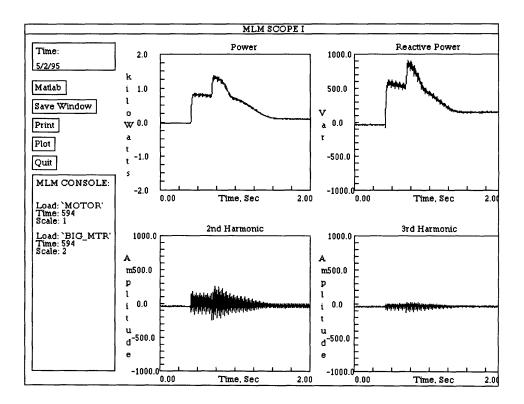

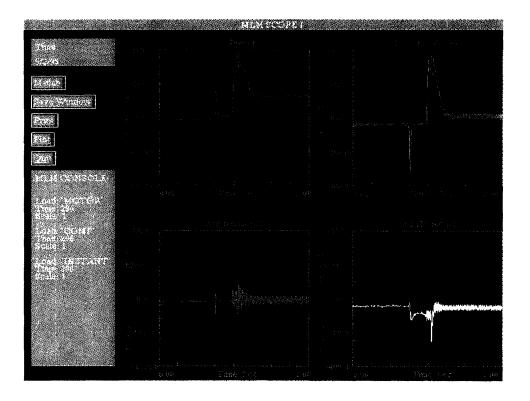

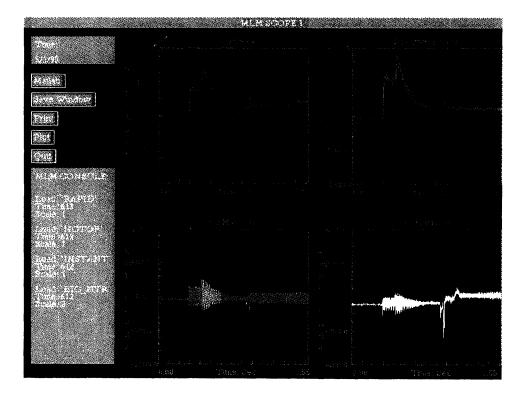

| 6.2  | MLMscope Report: Small Motor                            | 121  |

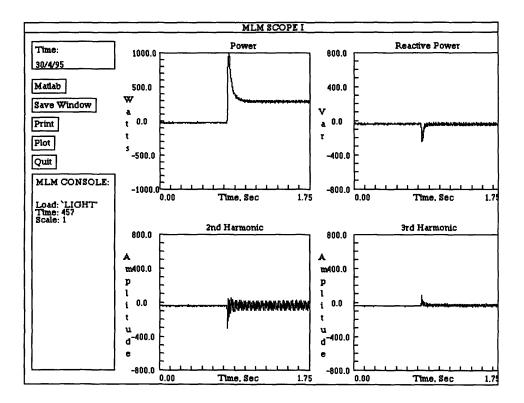

| 6.3  | MLMscope Report: Incandescent Light Bulbs               | 121  |

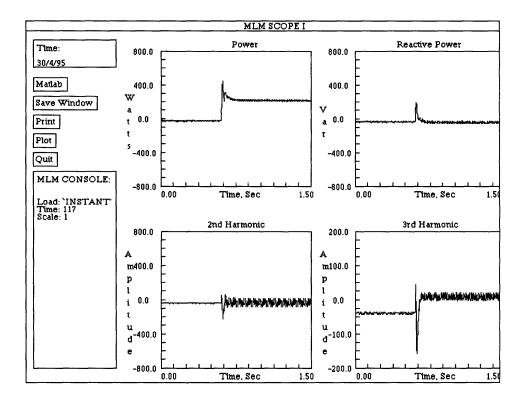

| 6.4  | MLMscope Report: Instant Start Lamps                    | 122  |

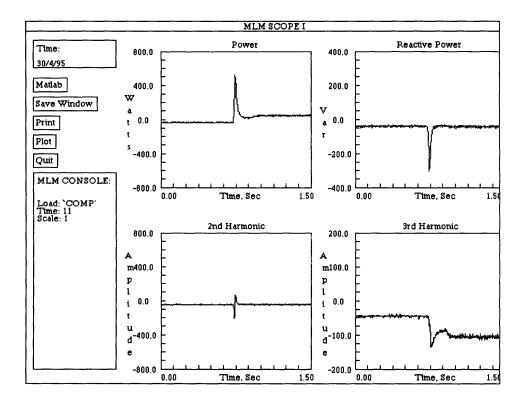

| 6.5  | MLMscope Report: Rapid Start Lamps                      | 122  |

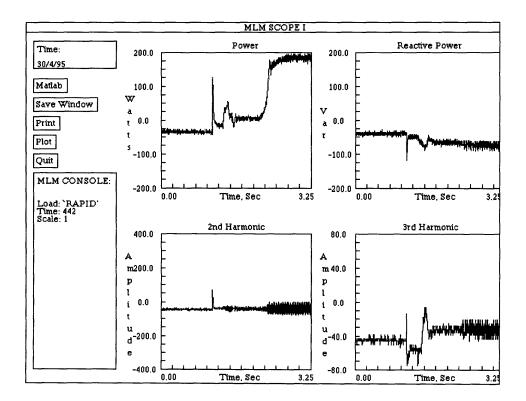

| 6.6  | MLMscope Report: Computer                               | 123  |

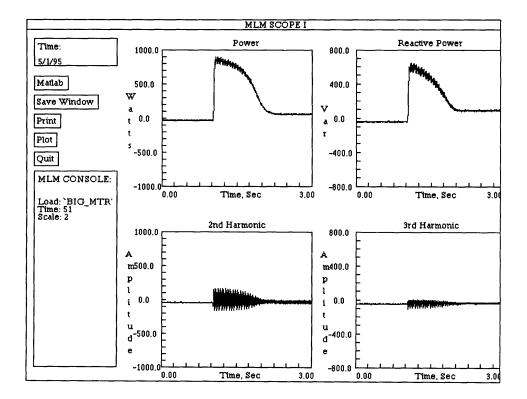

| 6.7  | MLMscope Report: Big Motor                              | 123  |

| 6.8  | MLMscope Report: Small Motor, Instant                   | 126  |

| 6.9  | MLMscope Report: Small Motor, Instant                   | 126  |

| 6.10 | MLMscope Report: Small Motor, Light                     | 127  |

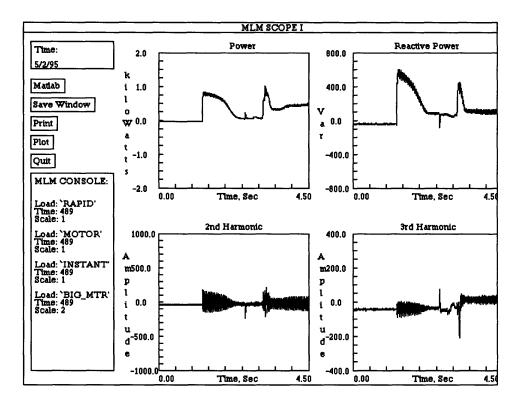

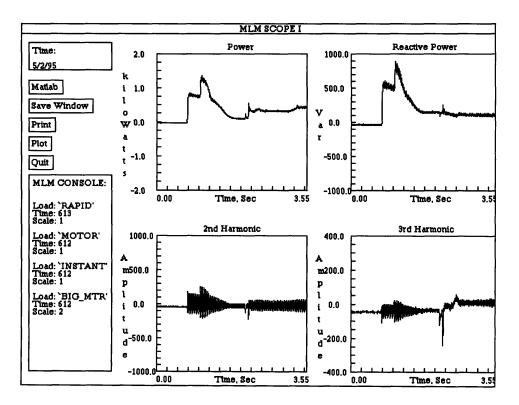

| 6.11 | MLMscope Report: Rapid, Small Motor                     | 127  |

| 6.12 | MLMscope Report: Rapid, Instant                         | 128  |

| 6.13 | MLMscope Report: Rapid, Small Motor, Instant            | 128  |

| 6.14 | MLMscope Report: Rapid, Instant, Small Motor            | 129  |

| 6.15 | MLMscope Report: Small Motor, Light, Instant            | 129  |

| 6.16 | MLMscope Report: Computer, Small Motor, Instant         | 130  |

| 6.17 | MLMscope Report: Big Motor, Small Motor                 | 130  |

| 6.18 | MLMscope Report: Big Motor, Rapid, Small Motor, Instant | 131  |

| 6.19 | MLMscope Report: Big Motor, Small Motor, Rapid, Instant | 131  |

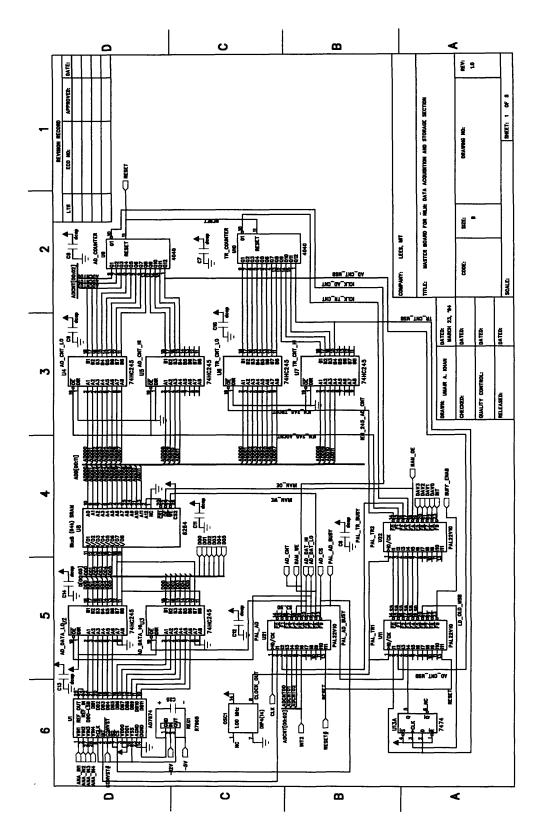

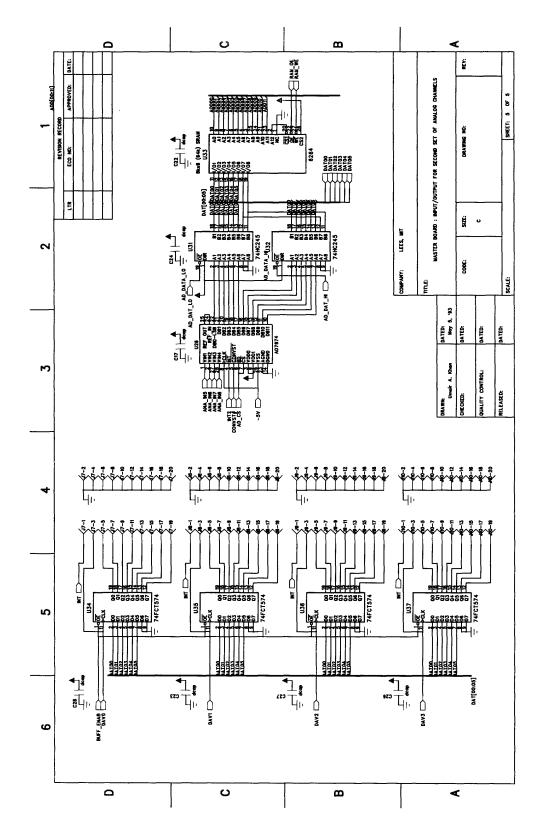

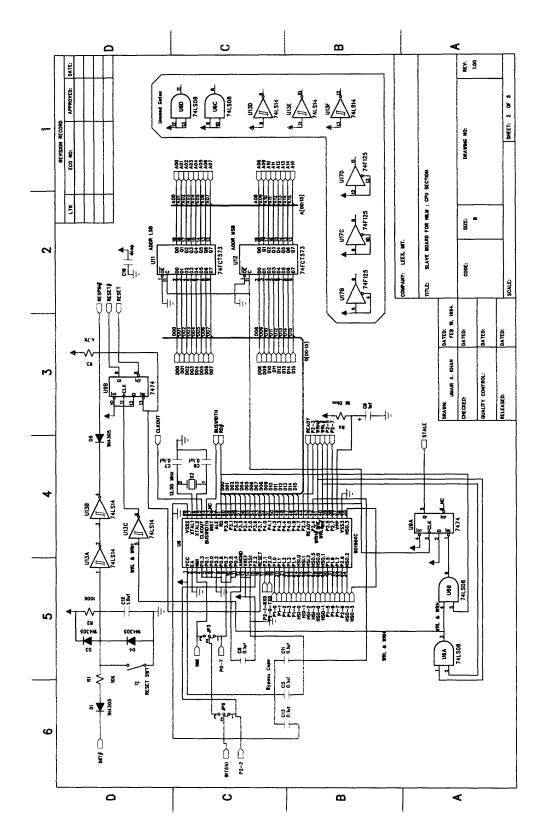

| A.1  | Master Board Schematic 1                                | 141  |

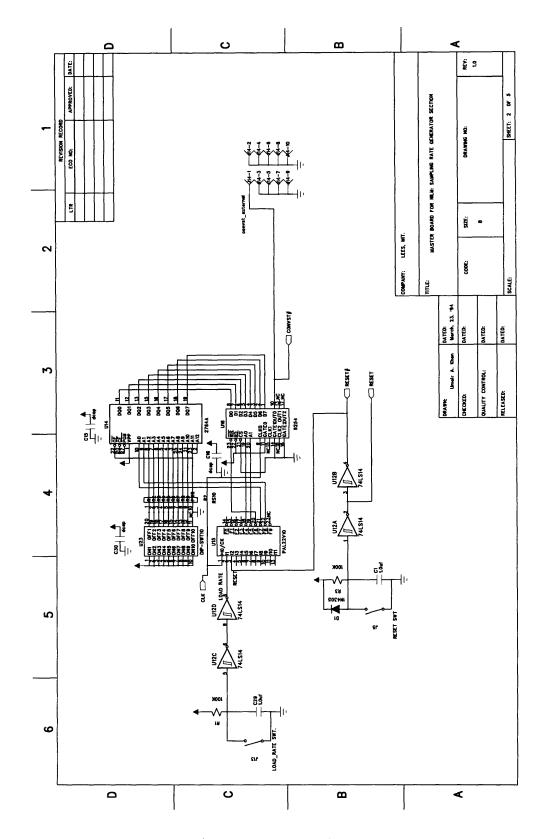

| A.2  | Master Board Schematic 2                                | 142  |

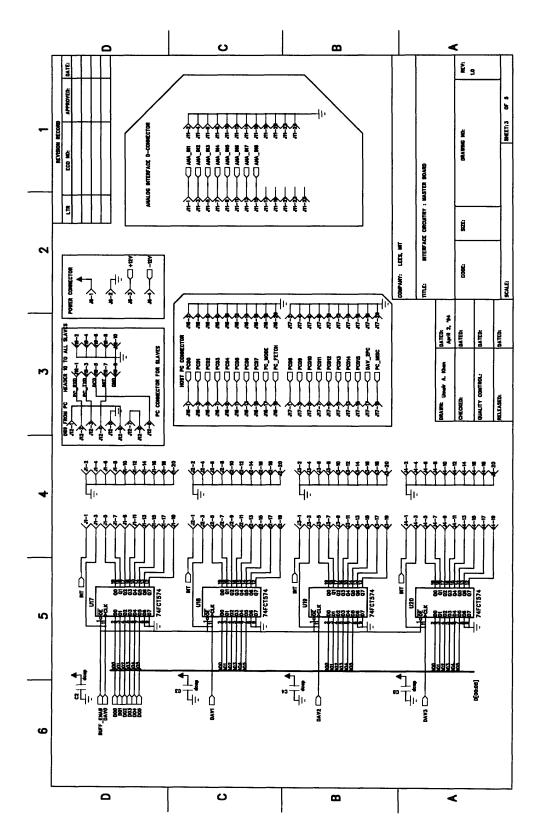

| A.3  | Master Board Schematic 3                                | 143  |

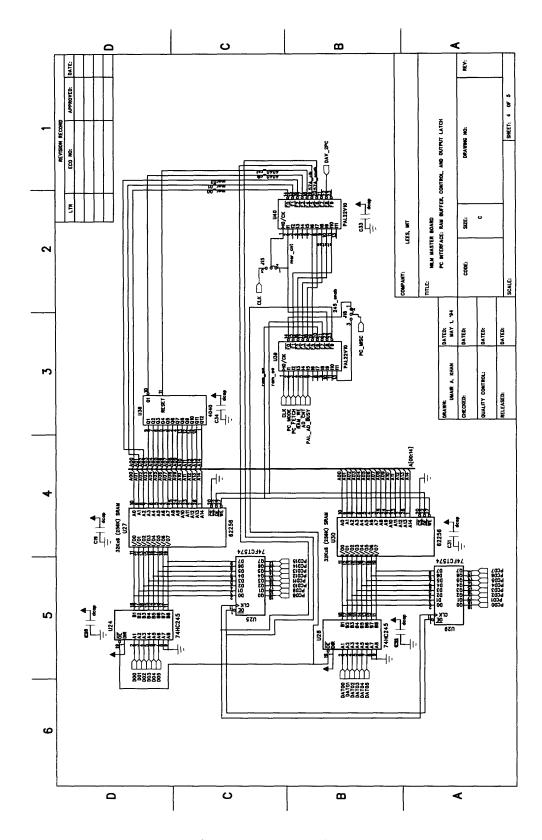

| A.4  | Master Board Schematic 4                                | 144  |

| A.5  | Master Board Schematic 5                                | 145  |

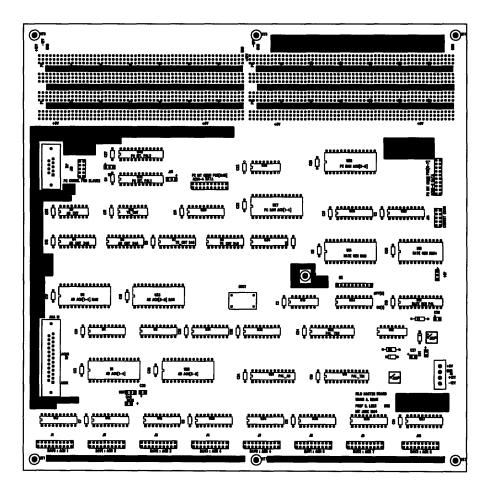

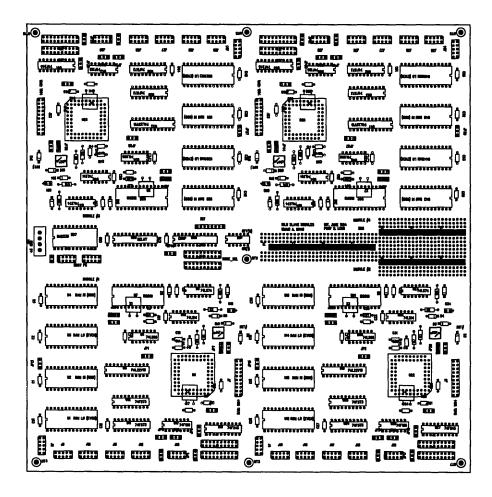

| A.6  | Master Board: PCB Component Layout                      | 146  |

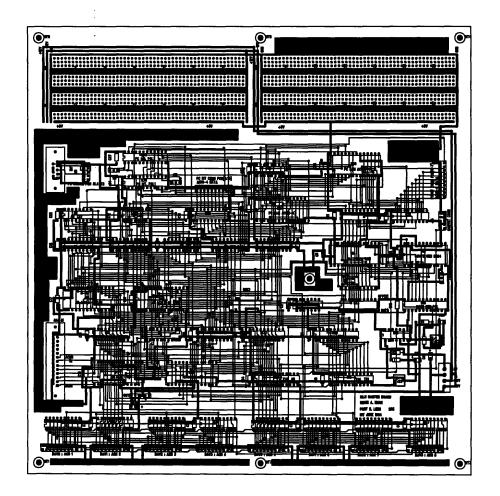

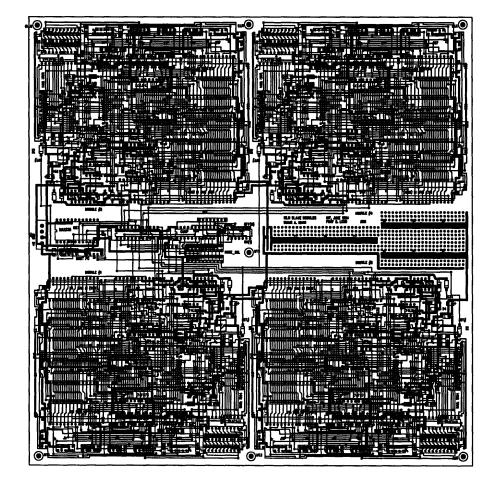

| A.7  | Master Board: PCB Component and Solder Sides            | 147  |

|      |                                                         | 7.11 |

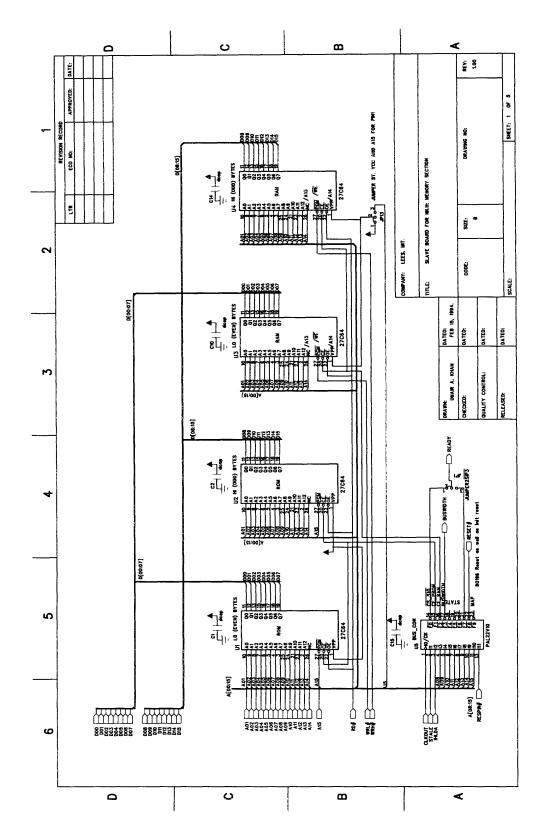

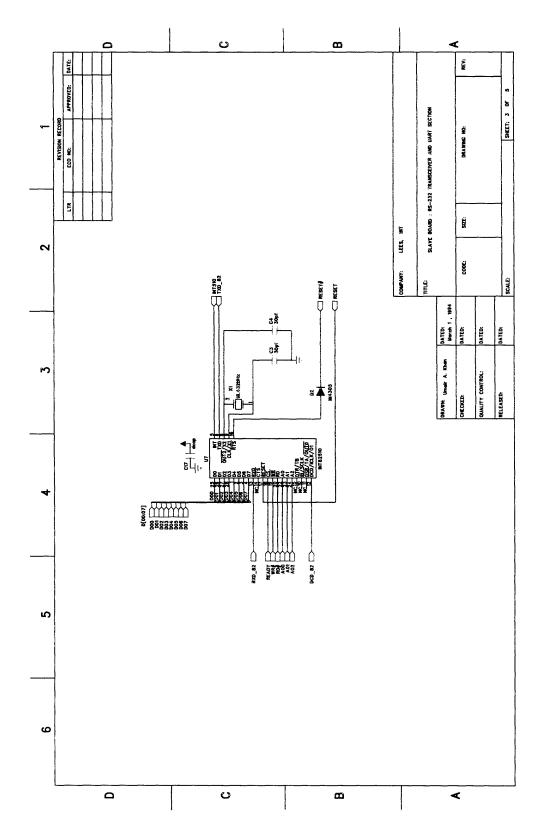

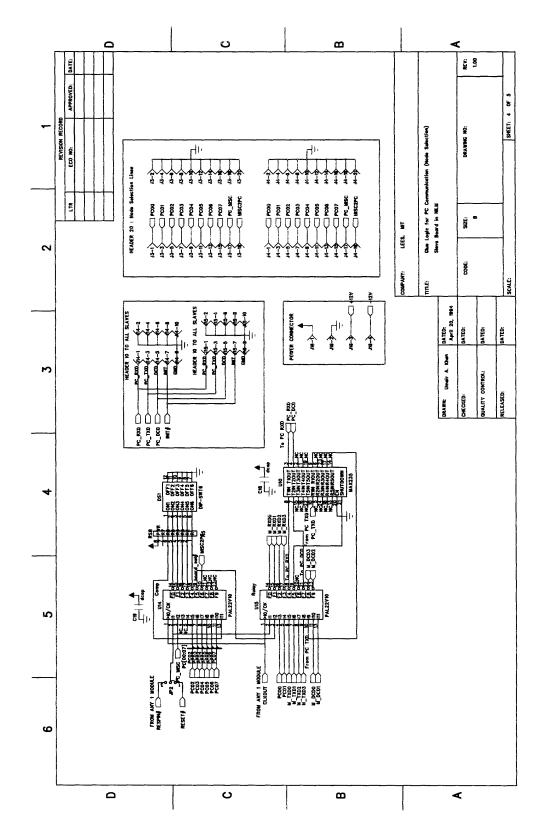

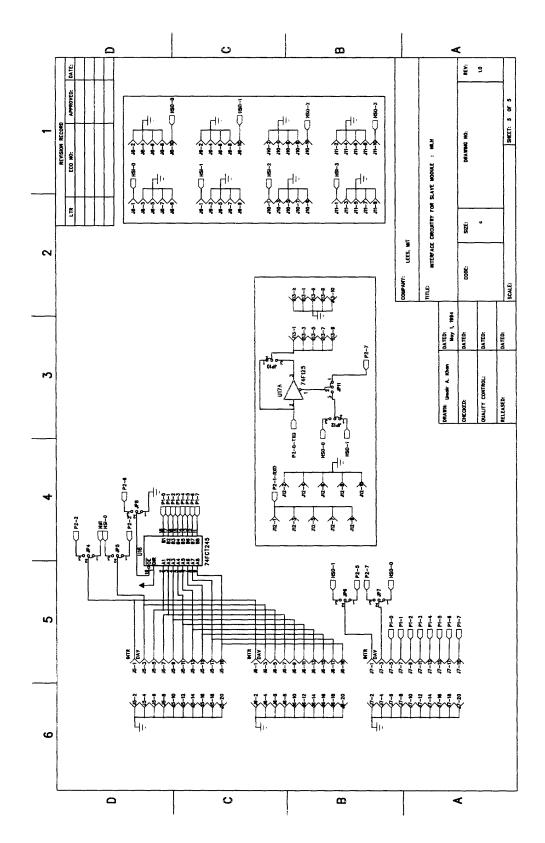

| B.1  | Slave Board Schematic 1                                 | 149  |

| B.2  | Slave Board Schematic 2                                 | 150  |

| B.3  | Slave Board Schematic 3                                 | 151  |

| B.4 | Slave Board Schematic 4                     | 152 |

|-----|---------------------------------------------|-----|

| B.5 | Slave Board Schematic 5                     | 153 |

| B.6 | Slave Board: PCB Component Layout           | 154 |

| B.7 | Slave Board: PCB Component and Solder Sides | 155 |

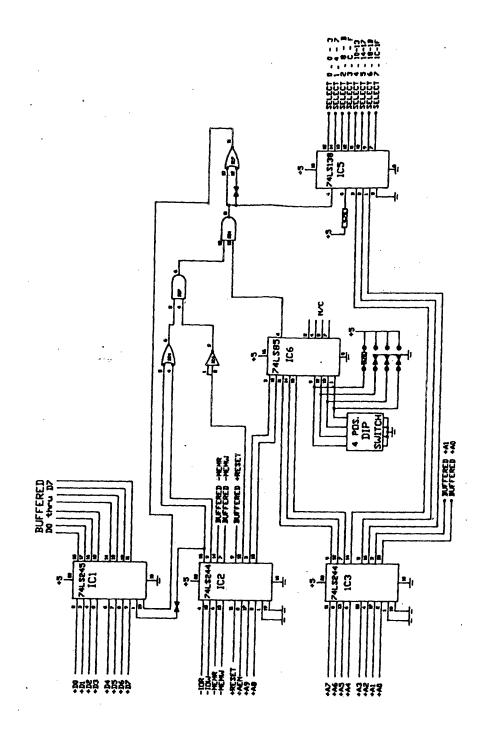

| F.1 | PC I/O Board Schematics                     | 285 |

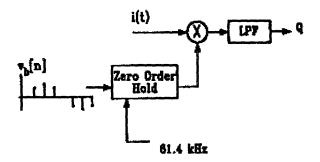

| G.1 | Signal Flow Graph                           | 290 |

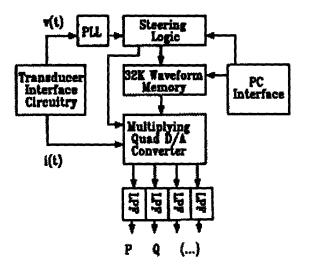

| G.2 | Envelope Preprocessor Block Diagram         | 291 |

| G.3 | Personal Computer Turn-On Transient         | 292 |

# List of Tables

| 3.1 | Master Board Component Listing                 | 54  |

|-----|------------------------------------------------|-----|

| 4.1 | Slave Board Component Listing                  | 76  |

| 5.1 | Memory Map of the Slave Module 80C196KC        | 91  |

| 5.2 | Naming Scheme for Raw V-section Template Files | 99  |

| 6.1 | Slave Module Configuration in the MLM-8S       | 113 |

| 6.2 | Slave-Slave Interconnections for MLM-8S        | 114 |

| 6.3 | Slave Module Configuration in the MLM-16S      | 115 |

| 6.4 | Slave-Slave Interconnections for MLM-16S       | 116 |

| 6.5 | Multiple Load Turn-on Delays                   | 125 |

#### Acknowledgements

I am grateful to ESEERCo and the Electric Power Research Institute for funding this project. Essential hardware for this project was made available through a generous grant from the Intel Corporation. Test equipment used in the course of this thesis was made available through a generous grant from Tektronix.

I am deeply grateful to Steven Leeb, my thesis advisor, on-the-spot trainer, motivater, trouble shooter, friend and mentor. Thank you for the opportunity, the experience and for making sure I finished by May 1995.

I must thank my friends and colleagues: Ahmed Mitwalli for being the funniest man on earth and the most helpful; Steve Shaw for all his help and advice, and for being Steve Shaw; Rob Lepard, Mark Lee and Krishna Pandey for their significant contributions in building the MLM; Aaron, Deron, Neils, Kamakshi, Jeff Chapman, Ganish, Khurram, and Dave Otten for their advice and support. A special thanks to Vivian for all her cooperation throughout my stay at LEES.

I am not sure how to thank someone for bearing the burden of the worst of times and for being responsible for all my happiest moments. But I thank my wife, Zareen, anyway. Thanks too, to our daughter Samar who ensured by her arrival that I would finish up at MIT this year.

I thank my sister, Shazaf, for all the cards, letters, impersonations and private jokes. I am grateful to my father for supporting me in every decision and standing by me in every effort. My love for mathematics and for education, I owe to him.

Finally, I thank my mother. She cannot read these words, but then, she does not need to, as every word I have ever written, she wrote for me.

# Chapter 1

# **Introduction and Background**

## **1.1 Theoretical Background**

The Nonintrusive Load Monitor (NILM) is a device that monitors the electric utility service entry of a building and, from measurements of voltage and aggregate current made solely at this point, is able to determine the operating schedule of every load of interest in the building. Nonintrusive load monitoring is a convenient and economical means of acquiring energy data for this purpose. Compared with conventional load monitoring, nonintrusive monitoring boasts easier installation, simplified data collection, and simplified data analysis because the NILM allows for all analysis to be done at a single central location [1]. Additionally, a NILM is a potentially powerful platform for power quality monitoring. "Power pollutants" are loads which do not draw sinusoidal input currents. Harmonic currents create harmonic voltages in the tranmission system and degrade the quality of the delivered voltage waveform [2]. In conjunction with determining the operating schedule of the loads, the NILM could check for power quality offenders by relating the introduction of undesirable harmonics with the simultaneous turning on of the offending loads.

While the NILM demonstrates much improvement over conventional metering procedures in both ease and scope of operation, more sophisticated techniques are needed to deal with loads in an industrial or commercial setting. State-of-the-art nonintrusive monitoring devices such as the residential NILM [3], depend upon changes in steady state real and reactive power for load identification. Such a NILM would not for instance, be able to distinguish loads that coincidentally draw nearly identical steady state power. This presents a potential limitation in the context of industrial settings which contain loads that may be modified to homogenize their steady state behavior [4].

The Multiscale Transient Event Detector (TED) described in [1] advances the capabilities of conventional NILMs by using vector space methods to identify load transients or transient sections. Instead of monitoring steady state conditions, it searches for transients and matches them to stored templates of the load whose activity caused them. Hence, it does not suffer from the limitations of a residential NILM in a commercial or industrial environment.

The basis for the TED is the observation that transient behavior of most important load classes is distinctive and repeatable. This allows reliable recognition of individual loads from the observed transients. Each transient in current, real or reactive power, and other quatities, may be subdivided into segments of *significant variation*, known as *v-sections*. A load may thus be modelled as a set of v-sections comprising its characteristic transient behavior. Detecting the turning on of a load would simply (and reliably) mean recognizing all the v-sections for the load in the input data stream. This pattern recognition may be done using any feasible pattern discrimination technique such as a euclidean filter or a transversal filter [5].

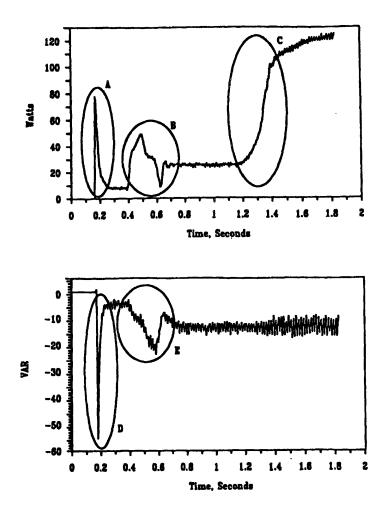

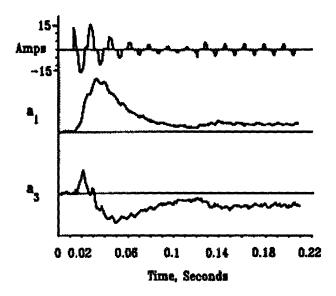

Figure 1.1, reproduced from [1], shows an example of a turn-on transient. Figure 1.1(a) shows the envelope of real power during the turn-on transient of a rapid start fluorescent lamp. The trace in Figure 1.1(b) shows the envelope of reactive power during the turn-on transient. The location of the v-sections in the two waveforms, computed by a change of mean detector implemented in MATLAB in [1], are schematically marked by ellipses A-E in the figures. The regions between the ellipses have very little variation in their level, i.e., are quasistatic. If two loads were to turn on simultaneously, the transients would overlap. This overlap, however, would *not* be intractable as long as the v-sections of one load transient occur during the quasistatic segments of the other load transient. As the widths of the v-sections are narrow, this may be quite probable, so that in most cases of overlap the TED would be able to resolve the loads correctly. By considering transients as sets of v-sections rather than as a single event to be detected, the TED allows for monitoring in a busy environment with a high rate of event generation.

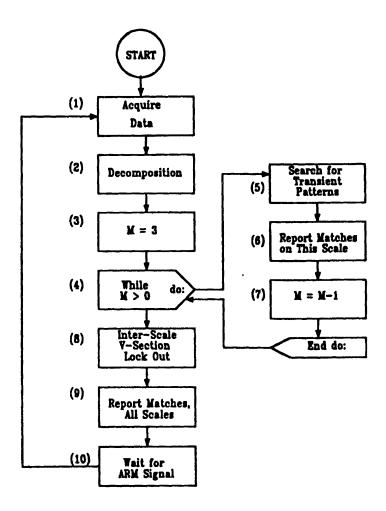

The algorithm for the prototype Transient Event Detector (TED) of [1] is flowcharted in Figure 1.2 (reproduced from [1]).

The first step is data acquisition. Once it is armed, the TED waits for a triggering event

Figure 1.1: Rapid Start Lamp Bank Transients in (a) Real Power (b) Reactive Power

(a change of mean in the input data stream), whereupon a block of samples is acquired. The v-sections of the load transients will have been previously collected and stored as templates. (The discriminating filter searches for these templates in the input data in step 5.)

Event detection may be carried out over several time scales. For instance, the input stream may be downsampled by factors of two and analyzed for v-sections on those time scales. The advantage of such an approach would be to allow templates of complex v-sections to be reduced to manageable sizes which would conserve both memory and processing time. Hence, for instance, data stream decomposition would allow us to identify a particular transient on a coarser time scale than the input stream. The procedure employed by the TED for downsampling data is known as tree-structured decomposition and is performed

Figure 1.2: The Multiscale Transient Event Detection Algorithm

at step 2. In the prototype, the input data block is downsampled twice to produce data on three time scales. Steps 3 and 4 then set up a loop to perform pattern search on each scale. Transversal filtering is used to detect v-sections in the input data stream.

A major concern in searching for v-sections to establish load activity is the possibility of superimposed transients due to simultaneous activity of multiple loads. As noted above, the v-sections are small enough to make complete superpositioning unlikely, thus allowing some degree of overlap in the transients. In the rare event of complete superpositioning, pattern recognition could fail. The danger still remains however, of a v-section being falsely detected due to the activity of another load with a more complicated set of v-sections. If all the v-sections in a complex v-section set of a certain load are found, it is very likely that the transient associated with the load is present in the input stream. If now a vsection belonging to a load with a simpler v-section set is also detected at about the same point in the input stream, it may be safely assumed that this v-section is not present and the identification is spurious. For instance, consider load X with a complicated transient consisting of four v-sections in an input stream, and load Y with only one v-section in the same input stream. If the v-section for Y resembles one of the v-sections for X, load Y may be falsely reported as activated each time load X turns on. To handle this case, an *intra-scale v-section lock out* is performed in step 5 on the result of the pattern search on each scale as follows: The pattern search on a scale is hierarchical, with v-sections belonging to the most complex transients being searched first. If a complex transient is detected, the locations of its v-sections are noted. A simpler transient will not be considered as identified if its v-sections are detected at the previously recorded, *locked out* locations.

Once all v-sections for a load on a time scale are found, the load transient is considered positively identified and a report is made of all events detected on that time scale (step 6). The TED then repeats event detection and lock out on the other time scales (step 7).

When all the patterns on all the scales have been searched, all events detected must be further conditioned by *inter-scale v-section lock out* (step 8). This follows the same principle as an intra-scale lockout. It guarantees that v-sections from a complex pattern on a coarse time scale were not used to match simpler v-sections on a finer time scale. Finally, a report of all loads identified is made in step 9, and the TED waits for the user to arm it again.

This multiscale transient event detection algorithm allows for several interesting routes for advancement. The event detection, tree-structured decomposition, and result collation procedures all have a high degree of parallelism inherent to them. This suggests the possibility of implementing the TED as a multiprocessing machine with several inexpensive processors performing the various tasks in parallel.

## 1.2 Contributions of This Work

The major contribution of this thesis was the development of a multiprocessing platform for multiscale transient event detection by extending the serial algorithm of [1]. The first step towards this goal was to analyze the TED algorithm in search for parallelism. The time/data dependencies of the major functional steps of this algorithm were brought out. Mapping these functions over a mesh of processors meant considering implementation issues early

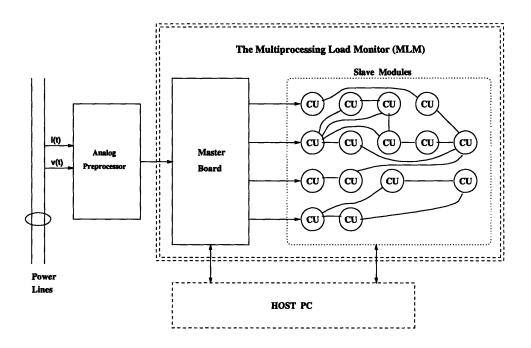

Figure 1.3: The Multiprocessing Load Monitor (MLM)

on. Thus, for instance, tradeoffs between computational complexity and reliability of event detection were considered. In the context of this study, an abstract model of a multiprocessing architecture for transient event detection was formulated. The Multiprocessing Load Monitor (MLM), as it is referred to throughout this work, was designed to fulfill the three objectives discussed below.

A primary purpose of the MLM developed as part of this thesis, was utilitarian: to develop an inexpensive and commercially viable implementation of the multiscale transient event detector presented in [1]. To achieve this goal, an effort was made to parallelize the event detection and tree-structured decomposition algorithms proposed in [1], as discussed earlier. This parallelism was then reflected in the machine model (see Figure 1.3) which consisted of **front-end preprocessing blocks** (the analog preprocessor and the master board — see Chapter 3) and a mesh of **computational units (CU)**, programmable and configurable to allow maximum flexibility of function. The event detection and tree-structured decomposition operations could be distributed over these units in a way that was deemed analytically and/or experimentally optimal. Cost-effectiveness in the physical implementation was achieved by using inexpensive microcontrollers and associated memory to form the computational units.

Transient event detection is implemented on the MLM by distributing the functions of event detection, tree-structured decomposition, and result collation over several computational units. In addition the v-sections associated with the loads must be assigned to the computational units, keeping in mind processing power and interconnection limitations. An important direction for future work would be to analytically determine the optimal distribution of these various functions and load transient assignments over the computational units. Hence, one aim of the MLM is to provide an experimental platform that may one day be used to test the theory of optimal implementation of the multiscale event detector algorithm in a parallel processing environment. This demanded that the architecture of the basic computational unit be flexible with regards to both intercommunication and individual functionality. A unit should, therefore, be configurable to allow communication with the master board, the host PC or another computational unit, as shown in Figure 1.3. It should also be able to function as a pattern recognizer, perform tree-structured decomposition, or gather and interpret results from the pattern recognizers.

Finally, the MLM was designed to form the basis for a platform for nonintrusive diagnostic evaluations of industrial loads. The MLM allows raw data to be shipped — in bulk — directly to the host PC, while reporting all events detected. Diagnostic routines on the PC could use this information to detect changes in the transient patterns (e.g. in the shapes and relative placements of v-sections) that may indicate potential problems with the loads being monitored. Problems could be detected and remedied before they lead to significant down-time.

#### **1.3 Thesis Outline**

In this chapter we introduced the concept of nonintrusive load monitoring and the versatility of the Transient Event Detector (TED) of [1]. A preliminary discussion of the rewards of taking a parallel approach to the sequential algorithm of the TED is made. This underscores the goal of the thesis: To design and implement a prototype of this parallellized TED algorithm in the form of the Multiprocessing Load Monitor (MLM).

Chapter 2 explores the parallelism in the TED algorithm. Tasks that may be subdivided, distributed over different processors, and performed in parallel are identified and a parallel version of the algorithm is constructed. A discussion on the tradeoff between the time/memory complexity and reliability of event detection is presented. In the context of the parallelized algorithm and complexity issues, an abstract model of the MLM is presented.

Chapter 3 describes one of the two main subsystems of the MLM, the Master Board, which is the data acquisition front-end. The data acquisition module's functionality and design methodology are explained, followed by a detailed report of the design and implementation of the module.

Chapter 4 rounds off our discussion of the hardware implementation of MLM by presenting the **Computational Units** of the MLM. Their function and top-level design are described, and supplemented with details of the actual implementation.

In Chapter 5, the software architecture of the MLM is elaborated. The code written for the computational units is described in the context of the parallel TED algorithm. The other major software effort was the design of the Host PC User Interface. Its functions and software implementation are also discussed in detail.

Chapter 6 presents the final configuration of the prototype MLM developed for this thesis. Results obtained during testing, and the performance achieved, are stated and evaluated with reference to the goals of this research.

Finally, Chapter 7 reiterates the aim of the thesis and gives a summary of the results achieved. It also indicates directions for future work based on the present research.

Several appendices are included at the end to support and enhance the body of this thesis. Appendices A and B consist of the schematics for the MLM and are important references for Chapters 3 and 4 respectively. Appendix C contains the PAL source code for both the data acquisition board and the computational modules. Appendix D lists the source code for the computational units. Appendix E gives details of the Host PC Interface software. Both ECM code and RISM code (resident in slave Read Only Memory) are included. Appendix F describes the design and construction of the PC I/O card used for MLM control. In Appendix G we give full details of the analog preprocessor by including [8] in its entirety. Appendix H supplements the discussion of prototype performance in Chapter 6. It gives details of the v-section sets for the monitored loads, as well as the software routines that activate the test loads in sequence. And finally, Appendix I is intended to be a pictorial guide to the construction of the prototype MLM.

# Chapter 2

# The Structure of the MLM

In this chapter we formulate the structure of a Multiprocessing System for transient event detection. We begin by analyzing the TED algorithm of [1] presented in Chapter 1, for data dependencies between its operations. Ensuring that these ordering constraints are met, a parallel version of the algorithm is developed. Before mapping this algorithm into a computation model, we discuss complexity and reliability tradeoffs. Finally, the structure of the Multiprocessing Load Monitor (MLM) designed and developed for this thesis is presented in Section 2.3.

## 2.1 Parallelism in the TED Algorithm

As discussed in Chapter 1, the TED algorithm of [1] monitors load activity by searching for transients in several data signals (e.g., real and reactive power) over several time scales. Consider the general case of searching for transients in data streams 1...R, over time scales 1...S. Transient event detection would consist of the following sequence of operations:

- 1. Sample data on each input stream [R operations].

- 2. Scale each stream in time, to get S-1 new streams for each original input stream [R(S-1) operations].

- 3. For each data stream (on each time scale), perform transient event detection [RS operations].

- Collate results and perform intra-scale v-section lockout on results for each time scale [S operations].

5. Perform inter-scale v-section lockout on results from all time scale [1 operation].

The total number of sequentially performed operations, O, is given by:

$$O = R + R(S - 1) + RS + S + 1$$

$$\Rightarrow O = 2RS + S + 1$$

Thus, for instance, if we were monitoring 5 input signals and searching over 3 time scales, a total of 34 operations would be sequentially performed. Most of these operations are not constrained to precede or follow one another. As a first step in bringing out the parallelism in the transient event detection algorithm, we must determine the *data dependencies* for the functions performed in the algorithm.

#### 2.1.1 Data Dependencies for TED Operations

We begin by explaining the terminology that will be used in the discussion to follow. Suppose an operation g cannot occur until another operation f has completed. We denote the start of g by  $g^s$  and the end of f by  $f^e$ . The *precedence relation* [6] between f and g can be expressed as:

$$f^e \preceq g^s$$

,

which is an inequality between the instants of the end of f and the start of g. This precedence constraint can be extended to cover entire operations by stating:

$$f \preceq g$$

,

which expresses the fact that f and g cannot proceed concurrently. The precedence constraint  $\leq$  is *transitive*, meaning that:

$$f \preceq g \& g \preceq h \Rightarrow f \preceq h$$

A precedence graph is a directed graph that represents the ordering on a set of events induced by precedence constraints. An arrow (directed edge) in the graph between vertices representing operations f and g specifies the constraint  $f \leq g$ .

One of the main sources of precedence constraints is *data dependency*. A data-dependency constraint between operations f and g occurs if some value produced by f is required as input to g. A *data-dependency graph* is a precedence graph depicting only constraints due to data dependencies. It is an important visual tool that we shall now use to impose an ordering on the TED algorithm.

Figure 2.1 shows the data-dependency graph for the TED operations, for a sample case examining two time scales. The following data dependencies are present in the TED algorithm:

- For each stream independently: Data Acq.  $\leq$  Event Detect. (original scale)

- For each stream independently: Data Acq.  $\leq$  TS Decomp.

- For each new scale independently: TS Decomp.  $\leq$  Event Detect.

- For each time scale independently: Event Detect.  $\leq$  Intra-scale lockout

- Over all time scales and all streams: Intra-scale lockouts  $\preceq$  Inter-scale lockout

Perhaps more importantly, the data-dependency graph states that the following operations are *independent*.

- The operations of data acquisition, tree-structured decomposition, and event detection can be performed on each data stream independently.

- For a given time scale:

- All result collation and intra-scale lockouts may be performed independently.

- For a given data stream:

- All tree-structured decomposition operations can be performed independently.

- All operations (event detection, collation and intra-scale lockout) on different time scales may be performed independently.

Figure 2.1: Data-Dependency Graph for TED Operations

#### 2.1.2 The Parallel Transient Event Detection Algorithm

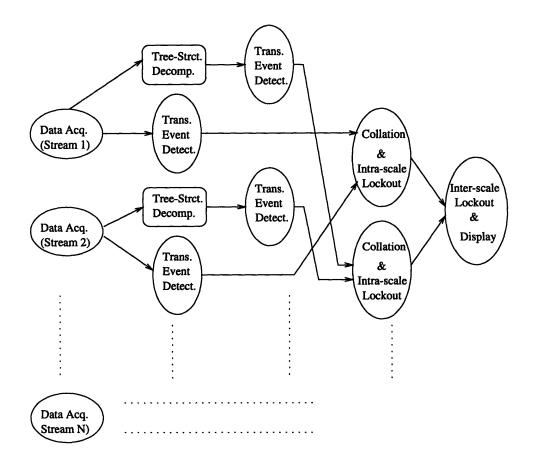

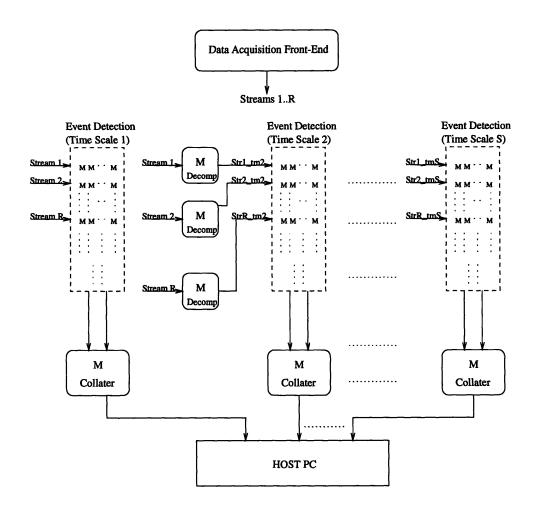

The data dependencies and "independencies" brought out in the previous section give us the guidelines by which to parallelize the transient event detection process. The Parallel Transient Event Detection Algorithm is given in Figure 2.2.

Here are the main steps in the algorithm:

- 1. Data acquisition is performed on all input streams in parallel.

- 2. The following operations are performed in parallel:

- Event detection on the original time scale is performed on all data streams in parallel. Each load's transients on every stream are searched for in parallel. In addition, the v-sections for a given load on a given stream may be searched for in parallel.

- Tree-structured decomposition is performed on all the streams in parallel.

Figure 2.2: The Parallel TED Algorithm

- 3. Event detection on all the time-scaled data streams is performed in parallel in the same manner as for the original data streams.

- 4. Result collation (including intra-scale lockout) is performed on each time scale in parallel.

- 5. Inter-scale lockout is performed on the results of the collaters.

## 2.2 Complexity/Reliability Tradeoffs

There is considerable freedom in mapping the parallel algorithm into an abstract model for a multiprocessing transient event detector. In producing a practical, reliable, and economically viable implementation, there are restrictions in addition to the precedence constraints of the algorithm. Thus, before we set up the MLM model of choice, we cover the issue of complexity and, in particular, the tradeoffs between complexity and reliability of operation.

As our discussion is geared towards designing an MLM model, let us begin by stating

the design features that arise naturally from the parallel TED algorithm. The task of digitizing data over several channels and storing and relaying data suggests the use of specialized hardware. Instead of using one or more processors for data acquisition, a seperate hardware module with specialized analog-to-digital converters, etc., should be designed to serve as the acquisition front-end. The sampling rate would be determined by the frequency characteristics of the inputs. The digitized data would be buffered and periodically shipped to the processors. The size of the transfer blocks and the sampling rate would determine the processing time available to the computational units between consecutive data arrivals. Thus, block size is related to the processing power of the units. The tasks of v-section search, tree-structured decomposition and result collation (with intra-scale lockout) would be distributed over a mesh of computational units, as stated earlier. Inter-scale lockout, the last step in the TED algorithm, may be performed by the host PC that would be needed to coordinate the MLM and provide a user interface. This last task assignment follows from the fact that inter-scale lockout requires significant memory (it requires access to information on all v-sections, their relative locations and their relative priority) and it need not be performed in real-time.

The mapping of loads and their v-sections over the processors and time scales available remains to be established. First we must decide on a processor that will give us adequate (yet inexpensive) computational power to perform the TED operations within the time frame established by the input sampling rate and the transfer block size. Another decision to be made is to determine the degree of parallelism to be incorporated in the final design: Just because two operations *can be done* in parallel does not mean they *have to be done* in parallel. This essentially means determining how many v-sections and how many loads should be sequentially processed by a single processor, as well as how many input streams a processor should search over. Finally, we must also decide which time scale a v-section should be identified on. A rigorous analytical solution to these questions is beyond the scope of our treatment of these issues. However, the factors that must be considered in determining the optimal MLM configuration are discussed here, and the architectural decisions made for the MLM (e.g., choice of processor and distribution of v-sections) are justified in the context of this discussion.

The most important factor governing the implementation of the parallel TED algorithm as a multiprocessing machine, is cost (remember that the goal of our work is to design an *economical* and commercially viable load monitor). An increase in complexity is most unattractive to the extent that it raises cost. Our discussion of complexity is made under this simplifying assumption.

System Complexity for the MLM may measured in terms of software complexity (or computational complexity) and hardware complexity (or *component count*). Software complexity itself represents the *computation latency* for a software operation as well as its memory requirements. Component count is an important factor as it directly affects cost. *Computation latency* of operations influences our design by helping us estimate the computation power needed of our processor. Moreover, the latencies of the various operations in the TED will determine how many tasks may be performed by a single processor within the established time frame. Higher latencies would mean adding more processors to perform all the operations, raising component count and hence, cost. Memory requirements are in a way the least important of the three factors: As long as the memory available in each processing module suffices, the memory requirements of an operation are irrelevant. The main influence on our MLM Model of the TED operations' memory utilization is in estimating the maximum memory that would ever be needed per computational unit. This would be used to define the memory range that must be provided by our processor. Once that is achieved, this part of system complexity may be ignored. Thus, as cost is our primary concern, for our purposes, system complexity is reflected and represented to a good approximation by component count alone.

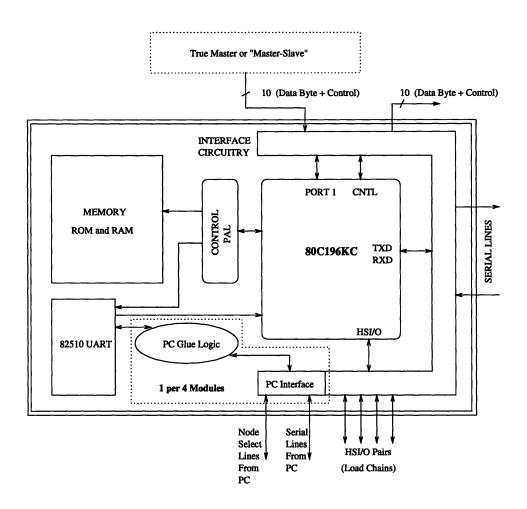

In selecting a processor for the MLM we used the software complexity of the TED operations as our guide. First of all, memory requirements were considered. A processor searching for several v-sections over an input data block requires, in general, far less than 10K of data memory and less than 10K of program memory. A 16-bit addressing architecture, giving access to 64K of memory was therefore decided upon. Since flexibility in inter-processor communication would be required, access to several I/O Ports and individual I/O pins, a serial port, versatile interrupt handling, and other features characteristic of an embedded controller were needed. The Intel 80C196KC appeared to fit the bill.

Computation latencies of the various TED operations, e.g., pattern search, were used to verify this choice. This required determining the block size of input data transfers. As a first step the range of possible sampling rates was fixed. For the types of inputs that the MLM would work on, the sampling rate would be between 100Hz and 250Hz. Given

the interrupt processing latencies of the 80C196KC, a block size of one (i.e., sending each sample as soon as it is acquired) would be unrealistic — too much time would be lost processing interrupts a few hundred times each second. If a very large transfer block size is chosen, say 5000 samples, new data would be shipped after 25 seconds (given a sampling rate of about 200Hz). This is impractical as it would make load identification lag the load activity by nearly a minute, if a v-section is split between two transfer blocks. Such a large block size would also be unsuitable because of the long transfer time. The correct size is somewhere between these extremes. The most important clue is the computation time of the TED operations on the 80C196. Experiments were conducted with various v-section sizes (varying from 10 to 200 points) on data blocks varying in length from 100 to 2000 sample points. Block sizes in the range 100-1000 points emerged as good choices. These gave the processors 0.5–5.0 seconds between consecutive data arrivals, and processor interrupt frequency was not unreasonable. We chose a block size of 500 points. The time needed to carry out pattern search using Euclidean filtering (see Chapter 4) on this block size for various template sizes was measured. The results showed that a 100 point template could be searched in about 0.75 seconds. Hence, the biggest template that could be searched would be about 325 points long. It was also seen that the total points searched determined the computation time, regardless of the fact that the points comprised a single v-section template or spanned several templates. Thus, five 30 point templates took about the same time (slightly more due to initialization overheads, etc.) as a single 150 point v-section. As it was estimated that actual v-section templates would vary in size from about 10 points to 35 points on average, this meant that about 10-25 v-sections could be identified on a single 80C196 in the alloted 2.5 seconds. Tree-structured decomposition required on the order of 0.3–0.4 seconds, which meant that a processor performing decomposition could double as an event detector. This timing data guaranteed us the flexibility in load and v-section assignment that we needed. The 80C196 was therefore judged a feasible choice for the given sampling rate and transfer block size.

Having established the time frame for processor computation, we now comment on the degree of parallelism needed in our model. Since we transfer data every 2.5 seconds, the worst-case lag between the *end* of a load transient and load identification being reported<sup>1</sup> is

<sup>&</sup>lt;sup>1</sup>Since the durations of transients vary from load to load, we measure identification lag from the end of the transient to the load being identified by the MLM.

just under 5 seconds. It therefore makes little sense to distribute one v-section per processor i.e., *completely* parallelize pattern search for load v-sections. Not only does this waste each processor's computation power, it makes no difference to the worst case delay in reporting load activity, while tremendously increasing component count. A much better scheme would be to allow some sequential processing per processor e.g., by alloting 5 to 10 v-sections to each event detector processor.

Component count could reasonably be increased if it leads to increased reliability in the functioning of the  $MLM^2$ . The MLM would be deemed *perfectly reliable* if a load turnon was reported **if and only if** the load turned on. That is, the MLM must never miss a load turning on and it must not be deceived into falsely reporting load activity when none occured. The problem with transient event detection (and with pattern recognition in general) is that the events — i.e., the v-sections — are not perfectly repeatable, are accompanied by background noise, and may occasionally be partially distorted due to high load activity in the monitored environment. The error threshold set must therefore be large enough to accomodate all possible v-section manifestations. This means transients due to other loads turning on or off may be seen by the discriminating filter to lie within the error bounds, so that a false identification may occur. We consider below some techniques for overcoming these problems and note how they inevitably require a complexity tradeoff.

One way to increase reliability would be to use a more sophisticated discriminating filter, or filters, to perform the pattern search. The hope would be that by the maximal use of the information available, these techniques may be able to define the tightest error threshold for positive recognition. The problem with this scenario is the necessary increase in software complexity (and, in particular, computation latency). This in turn would mean an increase in component count. In our case, the Euclidean Filter (see Section 4.2.1) was chosen for pattern discrimination largely because it was compatible with the processing power of the 80C196 - a more sophisticated filter might severely reduce the number of v-sections that may be processed per computational unit, leading to an unaffordable increase in complexity. However, more research is needed to determine the ideal filter in terms of resolution per computational complexity, for a given set of resources (such as processing power, allowed

<sup>&</sup>lt;sup>2</sup>The term reliability is used here to mean correctness of operation — i.e., how reliable is the MLM as a load monitor. It must not be confused with system reliability (in the context of robustness and fault tolerance) which is defined in terms of the mean time to failure of the system as a whole [7].

Figure 2.3: Improving Reliability By V-section Search Over More Streams

time, etc.).

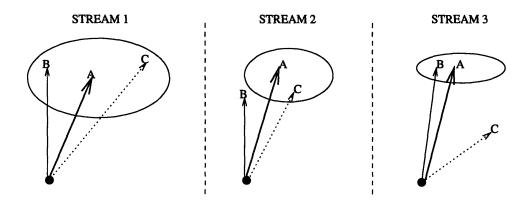

We could also improve MLM reliability by searching for more v-sections over more streams, in the identification of a load. Figure 2.3 shows the case of identifying load A, with the challenge of loads B and C giving turn-on transients that resemble the transient for A in certain input streams. The ovals represent "identification spaces" set up by the error thresholds for the transient sections of load A on each stream. The dark arrow represents a transient in the input stream due to the turning on of load A, the dotted arrow represents transients in the input due to load B, and the light arrow denotes transients due to load C. Note that the error threshold for load A in stream 1 is large enough to allow transients due to load B or load C to be occasionally interpreted as load A transients. Thus, if pattern search for load A is conducted only on stream 1, false identifications of A will occur. Load A has a transient v-section in stream 2 and if this is used in conjunction with stream 1's transient, we see that transients in stream 2 due to load B never make it to A's "identification space". In this way, false identification of load A due to B's activity is eliminated. Similarly, v-section search in stream 3, eliminates spurious reporting of load A turning on, due to load C's activity. Clearly, reliability is improved and, equally clearly, unfortunately, so is component count. Nevertheless the MLM model should allow the use of this technique to improve reliability.

An important issue in the context of reliability and complexity trade-offs is determining the best time scale on which to search for a v-section. If a v-section search is conducted on the finest scale possible (i.e., the highest sampling rate), we have more frequency contents of the input signal available (higher resolution) than at any other scale: To go to a coarser scale requires downsampling (including pre-filtering), in which the higher frequencies of the input stream would be lost [19]. Hence, reliability is maximized at the finest scale. However, this also means more points per v-section, which increases memory requirements and computation time, and consequently component count. Downsampling the input data and searching for a proportionally smaller v-section would save on processing complexity but may reduce the resolution of transient recognition. To strike the perfect balance would require studying the frequency characteristics of the v-section, the possibilities of a false hit, and the computation power available. In general, if the variations in the transient are slow, or scaled out in time — i.e., the input is predominantly a low frequency signal — so that no useful information is lost in the process of low-pass filtering and decimation, this procedure should be undertaken, and the v-section identified on the coarser scale. If the v-section varies quickly in time (high frequencies present), downsampling could affect identification reliability. Thus, tree-structured decomposition and identification on a coarser scale is a particularly good idea for v-sections that exhibit slow variation over an extended period of time.

It is possible to improve reliability without particularly increasing complexity. An example is the idea of having individual error thresholds for each v-section searched. Certain loads exhibit remarkably consistent transient behaviour on certain input streams. Other loads may not be as cooperative. If there was one global error threshold, reliability of load identification would be severly decreased. Hence, we should customize the error threshold for each pattern to be searched according to the degree of its repeatability. The increase in software complexity is minor as far as computation time goes, and not too costly in the extra memory needed.

The discussion in this section focussed on issues governing the optimal configuration of a multiprocessing machine for load monitoring via transient event detection. It was also intended to ground our choice of implementation of the parallel TED algorithm in reality. As stated earlier, much theoretical work needs to be done in this direction. The good news is that the MLM's design allows easy reconfiguration. This would therefore provide the ideal platform to test the optimal distribution of these various functions and load transient assignment over the MLM processors.

Figure 2.4: Identifying a Load on One Time Scale

## 2.3 The Structure of the MLM

The MLM model is now presented in the context of the TED dependency graph and the complexity issues raised in Section 2.2.

Consider once again the parallel TED algorithm in Figure 2.2. A natural way to structure the MLM would be to have a seperate subsystem for data acquisition, feeding a network of processing modules performing the rest of the operations. The data acquisition frontend would sample all input channels simultaneously. It would buffer the digitized data and periodically ship data blocks to the processing modules. This way the sampling and transference of input data are performed in parallel over all input channels.

The allocation of tasks over the processing modules follows naturally from the algorithm and the complexity constraints:

- Each processing module works on only one input stream.

- Each processing module is assigned exactly one of three functions:

- 1. Tree-structured decomposition.

Figure 2.5: Identifying N Loads on One Time Scale

- 2. Searching the input stream for v-sections belonging to one or more loads.

- 3. Collation of event detection results on a given time scale.

- Inter-scale lockout is performed by a host PC.

In keeping with our goal of a practical and economical implementation, we do not choose the "finest grain" distribution of tasks over the modules. Hence, while v-sections of a load on a stream may be distributed over different processors and identified in parallel, we choose to search for all v-sections on one data stream sequentially on one processor. Moreover, multiple loads may be assigned to a single processor. These decisions are not dictated by precedence constraints. Rather they reduce component count (fewer processors) and communication complexity, while not significantly affecting computation time.

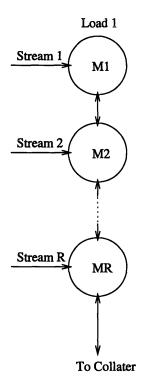

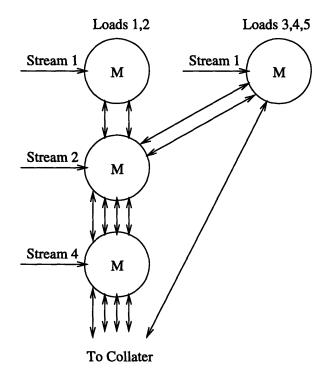

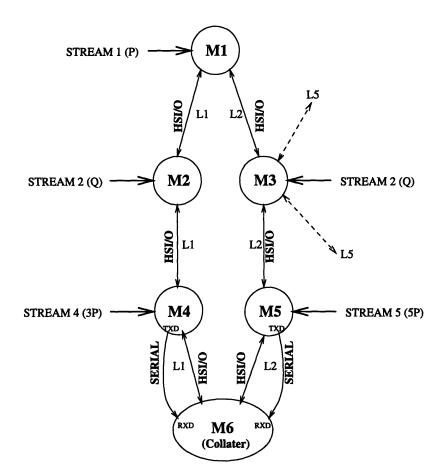

Consider the task of identifying one load on one time scale. Suppose the load has transient v-sections on streams 1 through R. Figure 2.4 shows the configuration of modules needed. Module M1 searches stream 1 for the v-sections present in that stream. Upon detecting all v-sections, it signals M2, which has been searching for v-sections in its own input stream. The detection results are thus passed down this linear chain. When all modules

Figure 2.6: A More Compact Load Assignment

including the final processor MR, have identified their v-sections, the load is considered identified on the given time scale and a message to that effect is passed on to the collater for that time scale.

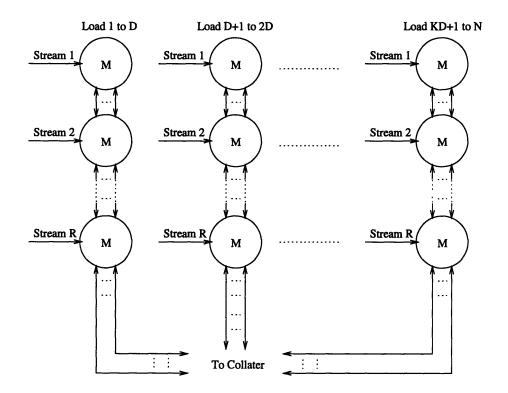

We now expand our example to cover the identification of N loads on a particular time scale, with v-section search being conducted on all R streams. Figure 2.5 shows the general processing module configuration. Each processor searches for v-sections of D loads on their respective input streams. Whenever a processor identifies all the v-sections for one of its loads, it relays a message to the next processor in the column. As multiple loads are being tracked, it is important for processors to communicate which load's v-sections have been identified. Note that the column-like placement or linear linking of modules, with communication possible only with neighbors, is an economical configuration which easily serves our purpose. Details of how the communication along these chains of processors is implemented are given in Chapter 4.

The symmetrical distribution of loads and their v-sections is somewhat misleading. In reality most loads will *not* have v-sections on all streams. They will also not have the same number of v-sections or similarly sized v-sections on different streams. The distribution and

Figure 2.7: The MLM Model

nature of v-sections will also differ from load to load. Thus while the columnar structure of 2.5 is a good visualization, a more compact configuration will be possible in most practical instances. Figure 2.6 shows the "custom" distribution of loads and v-sections across processing modules. Loads 1 and 2 have a large number of v-sections in stream 1 compared to loads 3,4, and 5. Hence, one processor is dedicated to v-sections of Loads 1 and 2 in stream 1. Another looks for stream 1 v-sections of Loads 3, 4, and 5. Loads 1 through 4 have fewer/smaller v-sections in streams 2 and 4. Load 5 has no v-sections in any stream other than stream 1. These facts are used to completely identify all five loads over four processors, as shown in Figure 2.6.

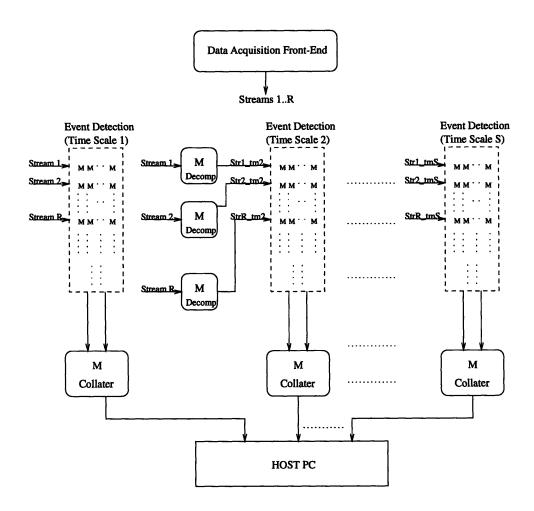

Figure 2.7 gives the model of the Multiprocessing Transient Event Detector that will be implemented in this thesis and utilized for load monitoring. A data acquisition front-end samples all input streams and relays the data blocks to the processing modules. Treestructured decomposition is performed on each stream independently. Event detection on the original time scale begins as soon as the front-end sends new data. Event detection on other scales is performed following the completion of tree-structured decomposition of the input data to that scale. Collation and intra-scale lockout are performed independently on each time scale. The task of inter-scale lockout is relegated to a host PC which also controls the entire MLM by downloading code to the processors and uploading results from them. The configuration of modules for event detection on each time scales is load-dependent. Details of this configuration are irrelevant in the abstract model.

Chapter 3 describes the hardware design and implementation of the data acquisition front end. Chapter 4 follows up with the design of the slave modules and details of how inter-slave communication takes place. Chapter 5 concludes the implementation details of the MLM by discussing the software design for the entire system including the software development of the host PC interface.

# Chapter 3

# The Data Acquisition Front-End

A major contribution of this thesis is the development of a multiprocessor-based nonintrusive load monitor. The **Multiprocessing Load Monitor (MLM)** consists of two distinct subsystems: the data acquisition front-end, or the **Master Board**, and the main computational unit, the **Slave Module**. In addition, an **Analog Preprocessor**<sup>1</sup> interfaces the MLM with the power load lines by providing conditioned analog inputs to the master board.

In this chapter we focus on the function and design of the data acquisition front-end. We begin with a brief discussion of the analog preprocessor and the inputs to the master board.

### 3.1 The Analog Preprocessor

The analog preprocessor is the primary interface between the digital world of the MLM and the *utility service entry*, i.e., the power lines driving the loads being monitored. Its principal outputs are estimates of the envelopes of real and reactive power, as well as inphase and quadrature third harmonic contents of current. It also gives the higher harmonic contents of the current, providing 16 analog channels per phase, to be analyzed by the MLM computational units. Full details of the analog preprocessor are given in [8]. This paper is included in its entirety in Appendix G.

Given below is a listing of the outputs of the analog preprocessor. Note that in-phase and quadrature harmonics are referred to with the same P and Q notation as "real power"

<sup>&</sup>lt;sup>1</sup>The Analog Preprocessor was designed and developed by S.B. Leeb and S.R. Shaw. See Appendix G for details of its functionality.

and "reactive power", even though there is generally no higher harmonic of voltage and so, strictly speaking, no high harmonics of power. The nomenclature used here is adopted from [8], and is simply a "short-hand" notation for describing the in-phase and quadrature higher current harmonics.

- 1. Envelope of real power, P.

- 2. Envelope of reactive power, Q.

- 3. Envelope of second harmonic of real power, 2P.

- 4. Envelope of second harmonic of reactive power, 2Q.

- 5. Envelope of third harmonic of real power, 3P.

- 6. Envelope of third harmonic of reactive power, 3Q.

- 7. Envelope of fourth harmonic of real power, 4P.

- 8. Envelope of fourth harmonic of reactive power, 4Q.

- 9. Envelope of fifth harmonic of real power, 5P.

- 10. Envelope of fifth harmonic of reactive power, 5Q.

- 11. Envelope of sixth harmonic of real power, 6P.

- 12. Envelope of sixth harmonic of reactive power, 6Q.

- 13. Envelope of seventh harmonic of real power, 7P.

- 14. Envelope of seventh harmonic of reactive power, 7Q.

- 15. Envelope of eighth harmonic of real power, 8P.

- 16. Envelope of eighth harmonic of reactive power, 8Q.

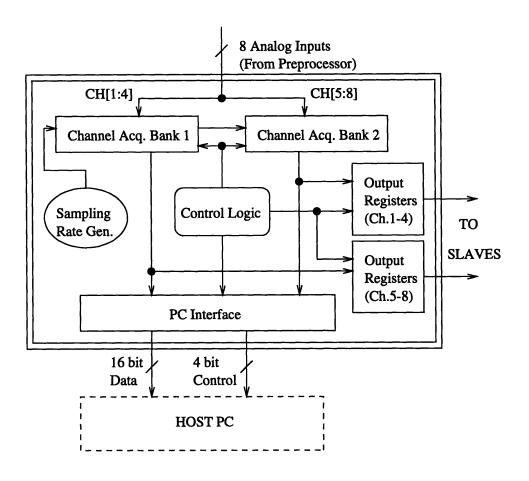

The master board accepts 8 analog inputs from the 16 choices. In a typical case, the master board would look at P, Q, 3P, 3Q, 5P, 6P, 7P, 8P. These inputs would be sampled and the data passed to the slave modules, which would search this data for transient events.

# **3.2 Functional Overview of the Master Board**

The Master Board acts as a digitizer, a buffer and a relay between the analog preprocessor and the computational units, as well as between the preprocessor and the host PC. It is proclaimed *master* because it has the highest priority in the eyes of the computational units (its *slaves*) when it informs these units that new data is ready to be transferred to them. Moreover, because of the single-sided handshaking between the master board and the slave modules, the master does not wait for the slaves to announce their availability, imperiously beginning the data transfer after a fixed time period.

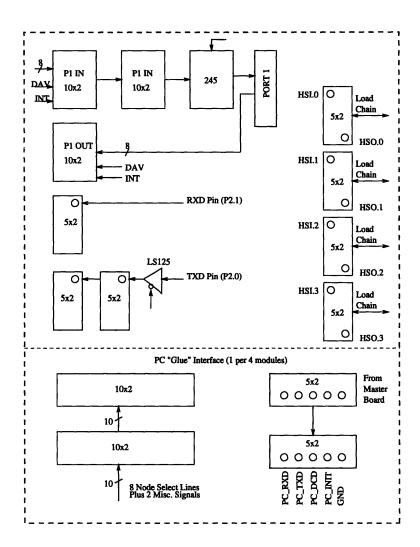

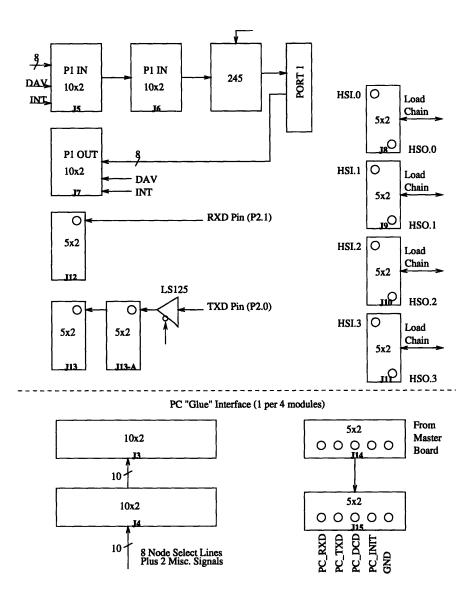

The master board is therefore, the data acquisition front-end of the MLM. It interfaces with the analog preprocessing module by accepting 8 analog channels from it, digitizing the signals, storing them in RAM, and periodically transferring the data blocks to the slave modules. It also interfaces with the host PC via a PC I/O card, and provides the PC with an expansive window of acquired data upon request. Its primary functions are:

- Digitize the analog data coming from the preprocessor.

- Collect and store the digital data.

- Periodically transfer suitable size blocks to the slave modules.

- Ensure data integrity by not allowing any loss of incoming data during transfer of sampled data to slave modules.

- Store, and upon request, transfer, large windows of data to the PC.

### **3.2.1** Data Acquisition and Storage

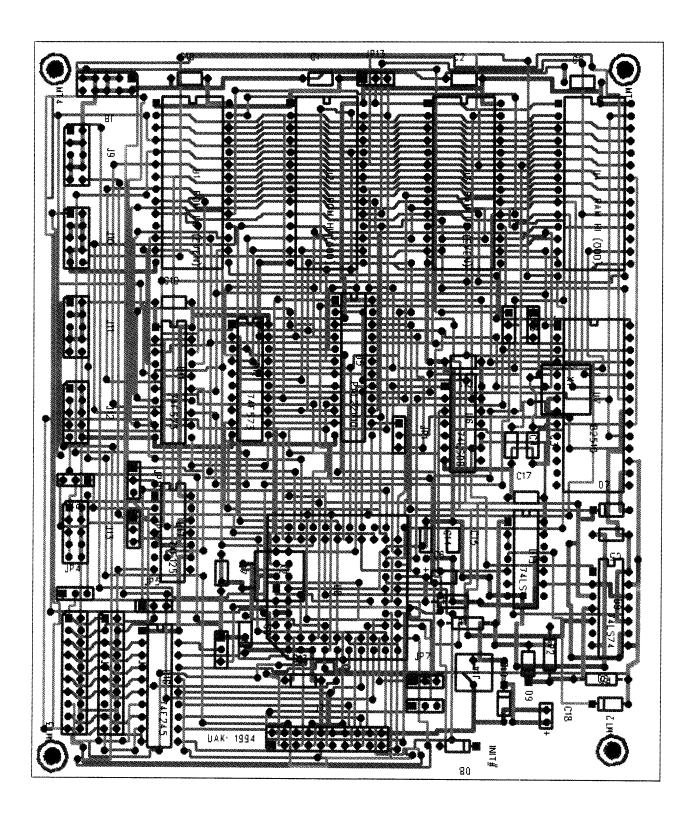

Figure 3.1 shows the basic blocks of the master board. The eight analog input channels get serviced by two 4-channel Analog-to-Digital Converters (ADCs). Each A-to-D converter relays its conversion results to dedicated memory in the form of 8Kx8 SRAMs. Each ADC, the associated memory ICs, and its memory address counters form an Acquisition Bank. Within each bank, the acquisition of data and its storage into memory is governed by the Sampling Rate Generator Module and the Control Logic. The basic data path of the master board consists of an 8-bit data bus, a 12-bit address bus, and various control and status signals. An important control signal, the Sampling Rate Signal is generated by the sample

Figure 3.1: The MLM Master Board

rate generator. This is a square wave which goes to both ADCs and triggers them to sample the input channels. Its frequency, which may be selected via dip-switch settings, determines the sampling rate. After each analog-to-digital conversion, a signal is sent to the control logic informing it that new sampled data is ready. The control logic then reads the data from the ADCs and writes it into memory.

### **3.2.2 Data Transfer to Slave Processors**

The acquired data must be periodically transferred to the slave processors. Transfer begins when the memory ICs are filled up. The master board issues an interrupt signal to all the slave processors. It allows the slaves to leave their computation activity and enter into a listening mode. Data is read sequentially from both acquisition banks simultaneously, and transmitted to the slaves. An "output" register is dedicated to the communication of data for each input channel. The output lines of the registers are connected to the input ports of the slaves for that input channel. During data transfer, each of these eight output registers is loaded with a data sample from their channel. The control logic then generates Data Available (DAV) signals to tell the slaves that data may be read. This cycle is repeated until the entire data block is transferred.

In the present implementation, the block size is 512 samples (1024 bytes). The transfer of this large set of data cannot usually happen neatly between two sampling events in the ADC. If an ADC conversion is not read, new conversions will overwrite it, compromising the integrity of the sampled data. To avoid this, the Programmable Array Logic (PAL) ICs controlling the transfer of data and the PAL controlling the its acquisition, communicate with one another: If the ADCs signal the arrival of new data during a block transfer, the acquisition PAL "interrupts" the transfer PALs, gains control of the address and data buses, reads the new data into the right memory location, and returns the control of the address and data buses to the transfer PALs.

### 3.2.3 Host PC Communication

The main function of the master board is to transfer data to the slave modules. In addition, the data is shipped to the host PC to allow, among other things, comparison with the results of transient event detection produced by the slaves and to carry out high-level diagnostic checks on the operating loads. For this purpose, the master board incorporates a PC interface section with its own memory, output registers, connectors, and control PALs. The schematics for this section are given in Figure A.4, in Appendix A.

The memory in the PC interface is larger than in the acquisition banks — eight times larger, allowing a total of eight data blocks to be stored and upon request, transferred to the PC. A transceiver IC, the LS245, in the interface section acts as the gateway to the PC interface memory: If the transceiver is enabled, the data bus of the acquisition bank is connected to the interface section data bus. In this case, all writes to the acquisition bank memory also go through to the PC interface memory. This is the storage mode. During the PC transfer mode, the PC interface module is disconnected from the rest of the board and writes in the acquisition bank are not seen by the interface memory. Instead, the data collected in the interface memory is read out and transmitted to the PC. Once the transfer is complete, the interface module returns to the storage mode.

### **3.2.4** Control Logic

There is no on-board processor for the master board. Instead, the microcontrol of the various functional blocks in the master board is implemented by Finite State Machines (see [6]) programmed into six Programmable Array Logic (PALs) ICs. Details of these FSMs are given in Section 3.3. The PAL Code is listed in Appendix C. A summary of the master board PALs, and their functions, follows:

- PAL\_AD: Controls the data acquisition process, including reading data from the ADCs into memory. Communicates with the *transfer PALs* (see below) to ensure no conversions in the ADCs are overwritten while a transfer is in progress.

- PAL\_TR1 and PAL\_TR2: Control the transfer of data to the slave modules, providing the necessary handshaking signals. Communicate with PAL\_AD to ensure integrity of acquired data.

- CLK\_GEN: Manages the operations of the sampling rate generator unit.

- PAL\_PC1 and PAL\_PC2: Govern the storage of data and its transfer (including performing the handshaking protocol) to the host PC.

# 3.3 Design and Implementation

Several functional subsections comprise the master board. Their data paths and logic-level details are given below.

### 3.3.1 A/D Conversion

The master board uses two AD7874s [9] for A-to-D conversion (see Figures A.1 and A.5). These Analog Devices IC's are complete 12-bit, 4-channel data acquisition systems with four track/hold amplifiers allowing simultaneous sampling of all channels. The ADC expects a negatively-asserted pulse on its  $\overline{CONVST}$  line. On the rising edge of  $\overline{CONVST}$ , all four input track/holds go from track to hold. Conversion is then performed sequentially on channels 1 through 4, and the results are stored in on-chip registers. Upon completion of all four conversions, the  $\overline{INT}$  signal goes low indicating data availability. Data is presented on the output lines DB[0-11], when  $\overline{CS}$  and  $\overline{RD}$  are asserted. To read the conversion results

of all four channels, the  $\overline{CS}$  and  $\overline{RD}$  lines must be asserted four times and each time the data must be read from the port. Thus, reading data from the AD7874 consists of four read operations. The first read after a conversion always accesses channel 1's conversion result, the second read always accesses the second channel's data register, and so on. Note that  $\overline{INT}$  is deasserted (goes high) after the first read operation.

In the master board, two AD7874's are used to sample eight analog inputs. In order to sample all eight channels simultaneously across both ADCs, the  $\overline{CONVST}$  inputs of both ADCs are tied together and driven externally from the same source. Also, in order to ensure good full-scale tracking across the ADCs, the *REF OUT* signal of the first ADC is fed to the *REF IN* input of the second ADC. The  $\overline{CS}$  and  $\overline{RD}$  inputs are also tied together. The voltage  $V_{ss}$  (-5v), is provided by a common voltage regulator (79L05), and AGND and DGND signals are tied together at a single point close to each AD7874 to reduce noise. Both ADCs have CLK tied to  $V_{ss}$  so that the internal laser-trimmed clock oscillator is used for all on-chip operations. With this internal clock source, the maximum conversion time, from the rising edge of  $\overline{CONVST}$  to the final conversion (channel 4's result registered), is 35us.

The data outputs of each ADC go to two buffers (74LS245s), the six LSBs to one and the six MSBs to the other. These buffers have their outputs tied together and connected to the 8-bit data bus (the 2 most significant bits of which are not used). The data bus goes to the I/O lines of an 8Kx8 SRAM. During a read operation, when the AD7874 outputs data, each latch is enabled in turn (the Low Data "Byte" first) and written into the SRAM. Note that each AD7874 has its own pair of buffers and its own storage RAM. The conversion results of both ADCs are transferred to memory in parallel.

In order to control the data acquisition process, a 22v10 PAL is used. This control PAL, labelled PAL\_AD in the schematics (see Figure A.1), and its operation are described in detail in Section 3.3.4. PAL listings are given in Appendix C.

### 3.3.2 Data Storage

The master board samples all channels, stores the data in RAM, and then transfers a block of data to the slave modules. For our purposes, a block size of 512 points was deemed optimal, each point occupying two bytes (12-bit A/D conversions). A total storage of 4K is needed per AD7874, as there are four channels per ADC. Hence, we used 8Kx8 RAMs [10]. These are addressed by HC4040's which are 12-bit synchoronous counters with positivelyasserted *RESET* inputs (see Figures A.1 and A.5). Both RAMs share the same counters. Two counters are used to address a RAM, one is labelled the "AD\_COUNTER", the other is called the "TR\_COUNTER". Each counter outputs its count to a pair of 8-bit buffers, the LS245's. The eight LSB's of the count go to one buffer, and the four MSB's of the count go to the other. The buffers drive the address lines of both RAMs. At a time, only one pair of buffers is enabled. Hence, only one counter addresses the two RAMs at any given time.

During the *acquisition* phase, the AD\_COUNTER addresses the RAMs, i.e., its buffers are enabled and the buffers in front of TR\_COUNTER are disabled. Each time a conversion is completed, eight bytes are written into each RAM (four sample points), and the AD\_COUNTER is properly incremented by the control logic to provide correct memory addressing. When 512 conversions have been completed and 4K of RAM has been filled, the AD\_COUNTER increments from 0x1111 to 0x0000. This signals the control logic that a window of data is ready for dispatch to the slaves. As a result, the *transfer* phase is entered. The AD\_COUNTER buffers are now disabled and the TR\_COUNTER buffers are enabled, so that memory is now addressed by TR\_COUNTER. The sample points are read out of memory and sent to the slave modules via the Slave Interface Circuitry, detailed in the next section. If during the transfer phase, the ADCs assert  $\overline{INT}$  to signal a conversion, the control logic disables the TR\_COUNTER buffers, re-enables the AD\_COUNTER buffers and stores the samples at the addresses dictated by AD\_COUNTER. It then passes addressing control back to TR\_COUNTER. At the end of the block transfer, the AD\_COUNTER buffers are enabled in place of the TR\_COUNTER. At buffers, and the board re-enters the *acquisition* mode.

One important aspect of addressing the RAM must be noted. The RAM is read sequentially during the transfer phase but it is *not written sequentially* during the acquisition phase. The order in which the samples are read from the ADC is as follows:

- 1. LSB of Channel 1 Data.

- 2. MSB of Channel 1 Data.