# Dynamic Computation Migration in Distributed Shared Memory Systems

by

# Wilson Cheng-Yi Hsieh

S.B., Massachusetts Institute of Technology (1988) S.M., Massachusetts Institute of Technology (1988)

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Computer Science

at the

## MASSACHUSETTS INSTITUTE OF TECHNOLOGY

September 1995

| r                                                                                            |

|----------------------------------------------------------------------------------------------|

| © Massachusetts Institute of Technology 1995. All rights reserved.                           |

| $\bigcap I A \bigcap \bigcap I A$                                                            |

| Department of Electrical Engineering and Computer Science September 5, 1995  Certified by    |

| Assistant Professor of Computer Science and Engineering Thesis Supervisor                    |

| William E. Weihl  Associate Professor of Computer Science and Engineering  Thesis Supervisor |

| Accepted by                                                                                  |

NOV 0 2 1995 Barker Eng

## Dynamic Computation Migration in Distributed Shared Memory Systems

by Wilson Cheng-Yi Hsieh

Submitted to the Department of Electrical Engineering and Computer Science on September 5, 1995, in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science

## **Abstract**

Computation migration is a new mechanism for accessing remote data in a parallel system. It is the partial migration of an active thread to data that it accesses, in contrast to data migration, which moves data to the computation that accesses it (often by making a copy). Computation migration improves performance relative to data migration, because data is not moved; as a result, it avoids sending protocol messages to keep replicated data consistent.

Performance measurements of two distributed shared memory systems demonstrate that computation migration is a useful mechanism that complements data migration. Computation migration performs well when data migration does not perform well; in particular, computation migration should be used instead of data migration when writes either are expensive or dominate reads.

The initial implementation of computation migration in the Prelude distributed shared memory system demonstrated that computation migration is useful for write-shared data, and that combining data migration and computation migration is useful for improving performance. The implementation of dynamic computation migration was done in the MCRL system. The decision to use data migration or computation migration in MCRL is deferred until runtime, when better knowledge of read/write ratios is available.

Experiments demonstrate that computation migration should be used for writes in two application kernels. For a concurrent distributed B-tree on Alewife, using computation migration for writes improves performance by 44%, relative to pure data migration, when the operation mix consists only of inserts. In addition, experiments demonstrate that dynamically choosing between data and computation migration for reads can improve performance. For a B-tree on Alewife with 80% lookups and 20% reads, using a dynamic choice for reads improves performance 23% relative to pure data migration; always using data migration for reads only improves performance by 5%.

Keywords: computation migration, data migration, distributed shared memory, parallel programming

Thesis Supervisor: M. Frans Kaashoek

Title: Assistant Professor of Computer Science and Engineering

Thesis Supervisor: William E. Weihl

Title: Associate Professor of Computer Science and Engineering

# Acknowledgments

My advisors, Professors Frans Kaashoek and Bill Weihl, have been wonderful to work with, both professionally and personally. I certainly would not have finished if it were not for their guidance and knowledge, and I've learned a lot about doing research from them. They let me explore many different research areas, which made graduate school a great learning experience.

The rest of my committee has also been wonderful: John Guttag has always given me sound advice, and David Kranz has always been available to answer my questions. My committee provided incredibly useful feedback on my dissertation, which as a result is orders of magnitude better. Any mistakes, misstatements, or other problems with this dissertation remain mine, of course.

I thank everyone who acted as a reference for me during my job search: Bill Weihl, Frans Kaashoek, Fran Allen, Ron Cytron, and John Guttag. In particular, I'd like to thank them for writing me reference letters even after I had virtually decided to go to UW.

Ken Mackenzie, Don Yeung, and especially John Kubiatowicz (without whom there would be no Alewife machine) were extremely helpful in answering my numerous questions about the Alewife system. David Chaiken and Beng-Hong Lim, were willing to answer Alewife questions even after they graduated, and Kirk Johnson answered all of my questions about CRL. I also borrowed (with permission) some of Kirk's text and numbers about CRL. Finally, Scott Blomquist was great in keeping the CM-5 up and running.

Everyone in the PDOS research group made the 5th floor a fun place to work. My officemates Kevin Lew and Max Poletto put up with me this past year; I forgive Max for eating my plant, and for not listening to my advice to leave MIT. Debby Wallach answered all of my questions about using the CM-5, and was generous with her time in helping me on the CM-5; she was particularly good at shredding bad drafts of these acknowledgments. Anthony Joseph has always been more than helpful with questions of any sort, especially when they were not thesis-related. I wish Anthony and Debby the best of luck in getting out of here quickly. Dawson Engler got me interested in dynamic code generation: 'C would not have been designed were it not for his interest in the topic. Ed Kohler was a great source of typesetting and design knowledge, and he improved the look of my dissertation immensely.

Quinton Zondervan played chess with me when I needed breaks, and Parry Husbands answered all of my random theory questions. Bob Gruber, Carl Waldspurger, and Sanjay Ghemawat were all here with me at the beginning of this millennium; I wish them the best of luck in their respective careers, and I hope to see them often! Paul Wang had the common sense to know what he really wanted, and I hope he becomes a rich and famous doctor (medical, that is).

The Apple Hill Chamber Music Players have given me a wonderful atmosphere in which to play music during the last few summers. It was a refreshing change of pace to be there, and they helped to keep me sane. The music section at MIT is also very special, and I'll miss it deeply; it was a wonderful part of both my undergraduate and graduate careers. I thank everyone in the section for providing many great opportunities for making music.

I will miss my friends and fellow chamber musicians of the last few years: Eran Egozy, Don Yeung, Elaine Chew, Ronni Schwartz, and Julia Ogrydziak. When we play together again I'll try to be less insistent on playing things my way. Not. I have a great admiration for Jamie McLaren and Marc Ryser, who had the guts to leave MIT and become musicians.

Marcus Thompson, now Robert R. Taylor Professor of Music, has a great teacher and friend for eleven years; I wish I could study viola with him for another eleven years. Being able to learn from him (about life as well as the viola) was a constant source of inspiration, and helped keep me sane through graduate school.

David Krakauer put up with me as a roommate for six years, even after I turned him down as a roommate in college. I owe him a great debt for letting me use his computer — especially when it was in his room and he was sleeping! Of course, Krak did his best to help me avoid my thesis: he always found computer games for me to play when I had work to do.

I give my deepest love to Helen Hsu, who has made my last year of graduate school far happier than it otherwise would have been. She has been my best friend as well as my biggest cheerleader, and I don't know if I would have finished this dissertation without her to cheer me up.

Last, but of course most importantly, I owe everything to my parents. They have my love and my gratitude for providing me with a wonderful upbringing and education, as well as their unfailing love and support.

Chapter 5 is a revision of text originally published in "Computation Migration: Enhancing Locality in Distributed-Memory Parallel Systems," by Wilson C. Hsieh, Paul Wang, and William E. Weihl, which appears in the Proceedings of the Fourth ACM SIGPLAN Symposium on Principles and Practice of Parallel Programming.

I was generously supported by an National Science Foundation Graduate Fellowship for the first three years of my graduate career. This research was also supported in part by many other sources: ARPA under Grants N00014-94-1-0985 and N00014-89-J-1988, an NSF National Young Investigator Award, Project Scout under ARPA contract MDA972-92-J-1032, NSF under Grant CCR-8716884, an equipment grant from DEC, and grants from AT&T and IBM.

The views and conclusions contained in this document are those of the author. They should not be interpreted as representing the official policies, either expressed or implied, of any of the organizations mentioned in the previous paragraph, or of the United States Government.

# **Contents**

| 1 | Intro                    | oduction | on .               | 15 |  |  |  |  |

|---|--------------------------|----------|--------------------|----|--|--|--|--|

|   | 1.1                      | Contex   | xt                 | 16 |  |  |  |  |

|   | 1.2                      | Overvi   | riew               | 17 |  |  |  |  |

|   | 1.3                      |          | ibutions           |    |  |  |  |  |

|   | 1.4                      |          | nization           |    |  |  |  |  |

| 2 | Rem                      | note Acc | ccess Mechanisms   | 21 |  |  |  |  |

|   | 2.1                      | Remot    | te Procedure Call  | 21 |  |  |  |  |

|   | 2.2                      | Data M   | Migration          | 22 |  |  |  |  |

|   | 2.3                      |          | d Migration        |    |  |  |  |  |

|   | 2.4                      |          | outation Migration |    |  |  |  |  |

|   | 2.5                      | _        | parison            |    |  |  |  |  |

| 3 | Computation migration 27 |          |                    |    |  |  |  |  |

|   | 3.1                      | Mecha    | anics              | 27 |  |  |  |  |

|   |                          | 3.1.1    | Runtime System     | 29 |  |  |  |  |

|   |                          | 3.1.2    | Compiler           |    |  |  |  |  |

|   | 3.2                      | Progra   | am Annotation      |    |  |  |  |  |

|   | 3.3                      | _        | tion Criteria      |    |  |  |  |  |

|   |                          | 3.3.1    | Static             |    |  |  |  |  |

|   |                          | 3.3.2    | Dynamic            |    |  |  |  |  |

|   |                          | 3.3.3    | Dynamic Protocol   |    |  |  |  |  |

| 4 | Ехр                      | eriment  | tal Environment    | 37 |  |  |  |  |

|   | 4.1                      | Alewife  | fe                 | 37 |  |  |  |  |

|   |                          | 4.1.1    | Hardware Overview  | 38 |  |  |  |  |

|   |                          | 4.1.2    | Software Overview  | 39 |  |  |  |  |

|   |                          | 4.1.3    | Ideal Alewife      |    |  |  |  |  |

|   | 4.2                      | CM-5     |                    |    |  |  |  |  |

|   |                          | 4.2.1    | Hardware Overview  |    |  |  |  |  |

|   |                          | 4.2.2    | Software Overview  |    |  |  |  |  |

|   | 4.3   | Discussion                                  | 3 |

|---|-------|---------------------------------------------|---|

|   | 4.4   | Proteus and Simulated Alewife               | 4 |

| 5 | Stati | c Computation Migration in Prelude 4        | 7 |

|   | 5.1   | Implementation                              | 8 |

|   | 5.2   | Prelude Results                             | 8 |

|   | 5.3   | Discussion                                  | 1 |

| 6 | Dyn   | amic Computation Migration in MCRL 5        | 3 |

|   | 6.1   | CRL Overview                                | 4 |

|   | 6.2   | Implementation Issues                       | 7 |

|   |       | 6.2.1 Language Issues                       | 7 |

|   |       | 6.2.2 Compiler Issues                       | 8 |

|   |       | 6.2.3 Optimistic Active Messages            | 8 |

|   | 6.3   | MCRL Implementation                         | 9 |

|   |       | 6.3.1 Multithreading Support                | 9 |

|   |       | 6.3.2 Dynamic Computation Migration Support | 0 |

|   | 6.4   | Implementation Details                      | 5 |

|   |       | 6.4.1 Alewife                               | 5 |

|   |       | 6.4.2 CM-5                                  | 7 |

|   | 6.5   | Limitations                                 | 8 |

| 7 | Perfe | ormance 6                                   | 9 |

|   | 7.1   | Measurement Techniques                      | 9 |

|   | 7.2   | •                                           | 0 |

|   |       | 7.2.1 Operation Latencies                   | 1 |

|   |       | 7.2.2 Migration Latency                     | 3 |

|   |       | ·                                           | 0 |

|   | 7.3   | Application Kernels                         | 7 |

|   |       | 7.3.1 Counting Network                      | 7 |

|   |       | 8                                           | 2 |

|   | 7.4   | Summary                                     | 8 |

| 8 | Rela  | ted Work                                    | 1 |

|   | 8.1   | Software Distributed Shared Memory          | 1 |

|   |       | 8.1.1 Language-level DSM                    |   |

|   |       | 8.1.2 OS-level DSM                          |   |

|   | 8.2   | Computation Migration                       |   |

|   | 8.3   | Distributed Systems                         |   |

| 9 | Con  | 14010110                 | 07  |

|---|------|--------------------------|-----|

|   | 9.1  | Summary                  |     |

|   |      | Future Trends            |     |

|   | 9.3  | Extensions               | 09  |

|   |      | Future Work              |     |

|   | 9.5  | Observations             | .10 |

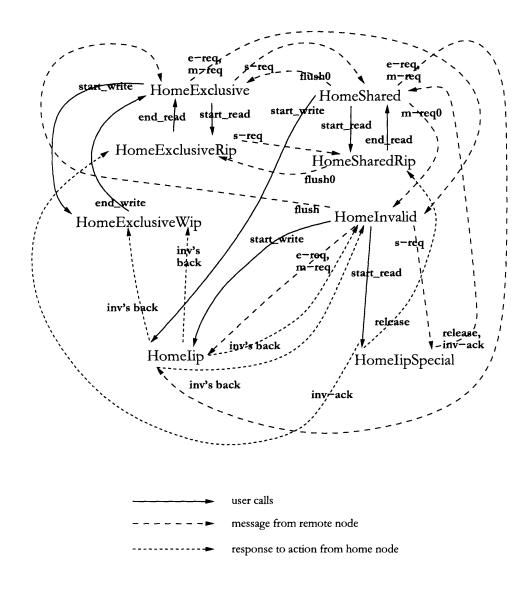

| A | CRI  | and MCRL Internals       | 13  |

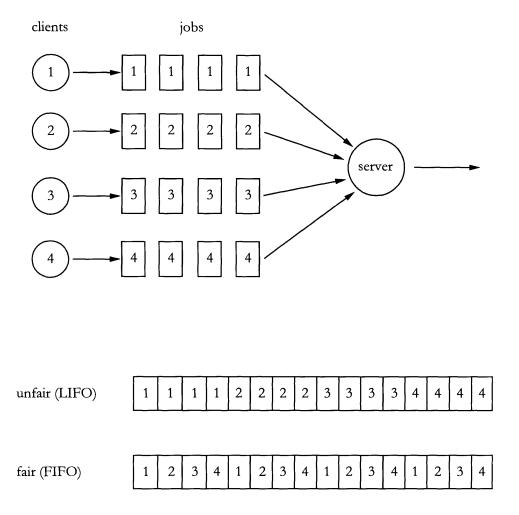

| В | LIF  | Versus FIFO Scheduling 1 | 19  |

| С | Regi | ession Formulas 1        | 21  |

# List of Tables

| 5.1 | B-tree throughput in Prelude: 0 cycle think time                              | 19 |

|-----|-------------------------------------------------------------------------------|----|

| 5.2 | B-tree bandwidth demands in Prelude: 0 cycle think time                       | 50 |

| 5.3 | B-tree throughput in Prelude: 10000 cycle think time                          | 51 |

| 5.4 | B-tree bandwidth demands in Prelude: 10000 cycle think time                   | 51 |

| 6.1 | Summary of the CRL shared memory interface                                    | 55 |

| 6.2 | Measured CRL latencies, 16-byte regions (in both cycles and microseconds) 5   | 56 |

| 6.3 | Measured CRL latencies, 256-byte regions (in both cycles and microseconds) 5  | 56 |

| 6.4 | MCRL non-blocking operations                                                  | 50 |

| 6.5 | MCRL operations for dynamic computation migration                             | 51 |

| 7.1 | Measured MCRL latencies, 16-byte regions (in both cycles and microseconds) 7  | 71 |

| 7.2 | Measured MCRL latencies, 256-byte regions (in both cycles and microseconds) 7 | 71 |

| 8.1 | Characterization of DSM systems                                               | )2 |

| A.1 | Calls and message types in CRL and MCRL state diagrams                        | 14 |

# List of Figures

| 2-1  | Message pattern under remote procedure call                                            | 22 |

|------|----------------------------------------------------------------------------------------|----|

| 2-2  | Message pattern under data migration.                                                  | 23 |

| 2-3  | Message pattern under computation migration                                            | 24 |

| 3-1  | Stack patterns under different access mechanisms                                       | 28 |

| 3-2  | Sample annotation for computation migration                                            | 31 |

| 3-3  | Sample annotation for computation migration of a partial frame                         | 32 |

| 3-4  | Message patterns under a dynamic protocol                                              | 35 |

| 4-1  | Software atomicity with half-threads on Alewife                                        | 40 |

| 6-1  | Hand optimization of code in MCRL                                                      | 57 |

| 6-2  | Client code for dynamic computation migration                                          | 63 |

| 6-3  | Server code for dynamic computation migration                                          | 64 |

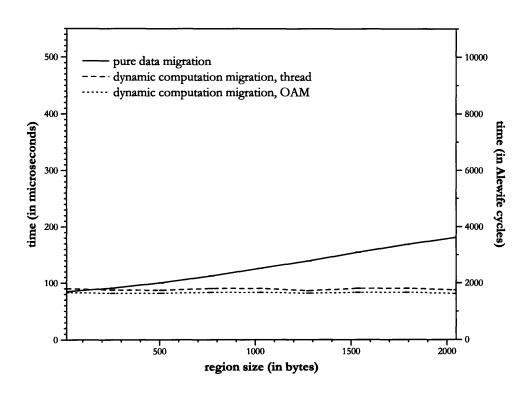

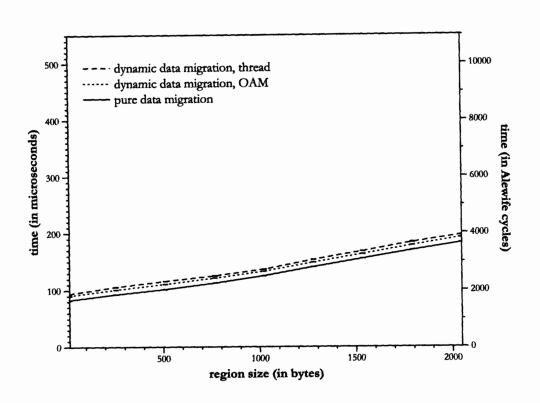

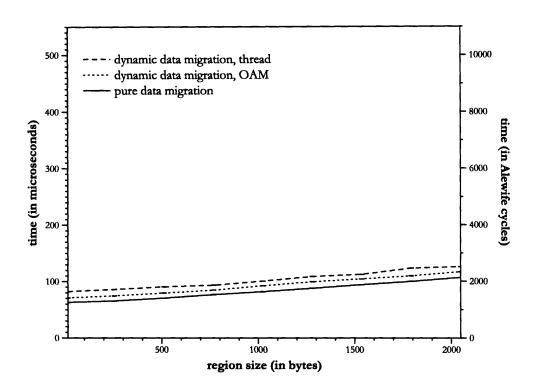

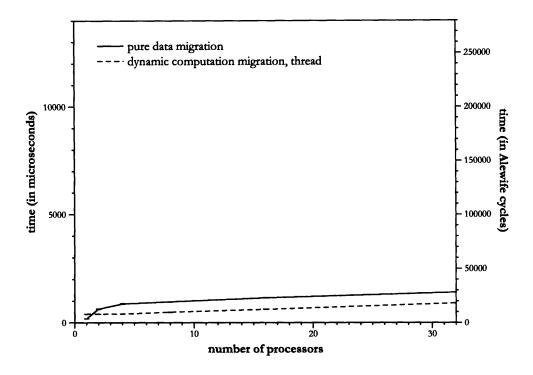

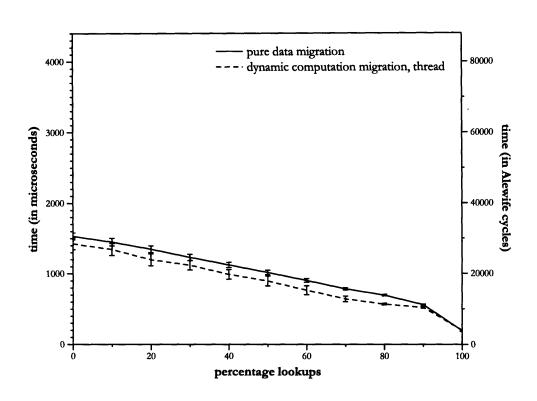

| 7-1  | Comparison of data migration costs and computation migration costs for MCRL on Alewife | 74 |

| 7-2  | Comparison of data migration costs for MCRL on Alewife                                 | 75 |

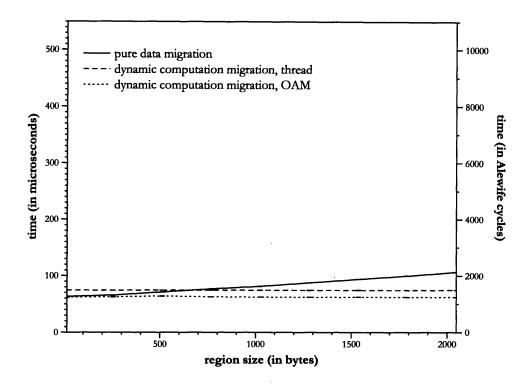

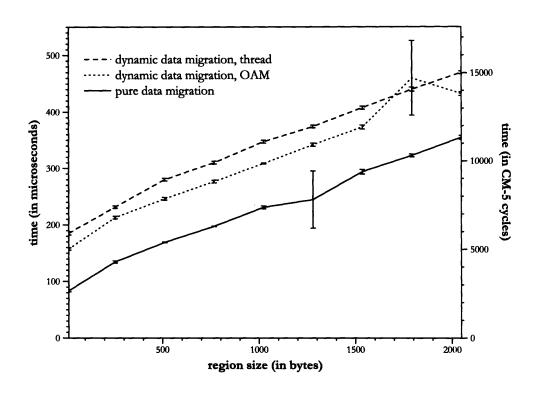

| 7-3  | Comparison of data migration and computation migration costs for MCRL on an            |    |

|      | ideal Alewife machine                                                                  | 76 |

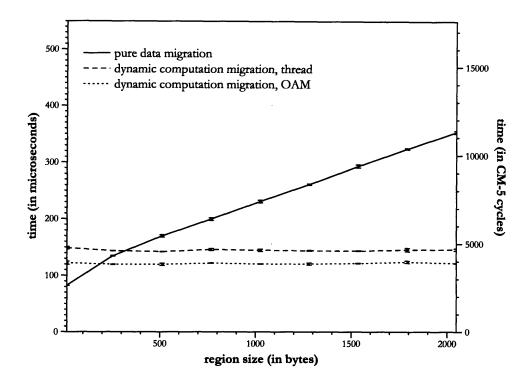

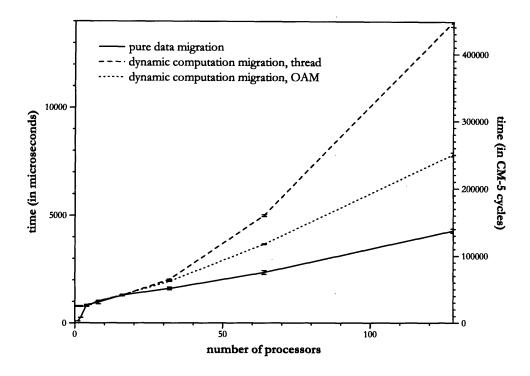

| 7-4  | Comparison of data migration costs for MCRL on an ideal Alewife machine                | 77 |

| 7-5  | Comparison of data migration and computation migration costs for MCRL on the           |    |

|      | CM-5                                                                                   | 78 |

| 7-6  | Comparison of data migration costs for MCRL on the CM-5                                | 79 |

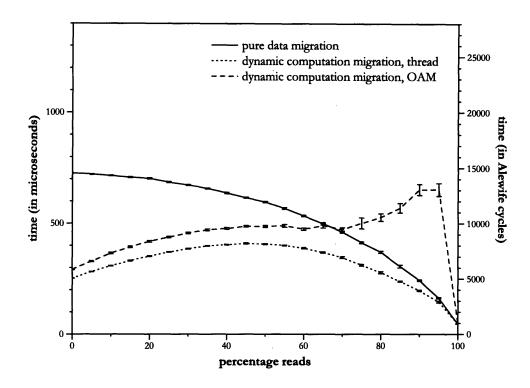

| 7-7  | Cost per microbenchmark iteration under the STATIC heuristic on Alewife                | 82 |

| 7-8  | Cost per microbenchmark iteration under the REPEAT heuristic on Alewife                | 83 |

| 7-9  | Cost per microbenchmark iteration under the STATIC heuristic on the CM-5               | 84 |

| 7-10 | Cost per microbenchmark iteration under the REPEAT heuristic on the CM-5               | 86 |

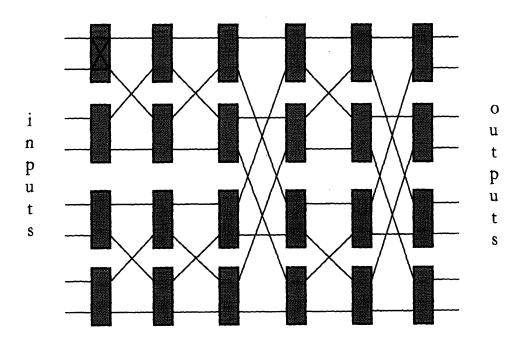

| 7-11 | An eight-input, eight-output bitonic counting network                                  | 88 |

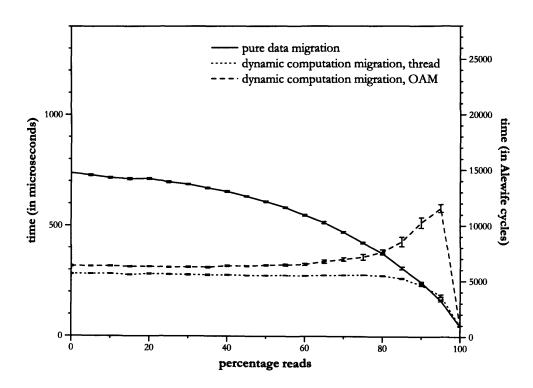

| 7-12 | Cost per iteration of accessing a counting network on Alewife                          | 89 |

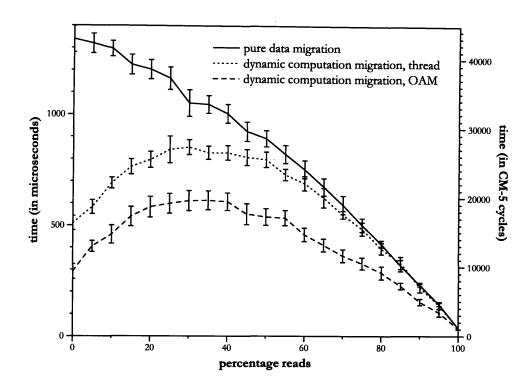

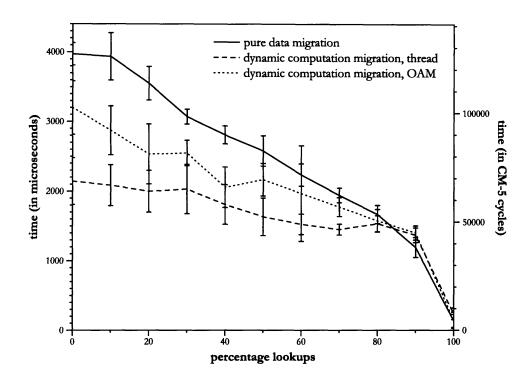

| 7-13 | Cost per iteration of accessing a counting network on the CM-5                         | 90 |

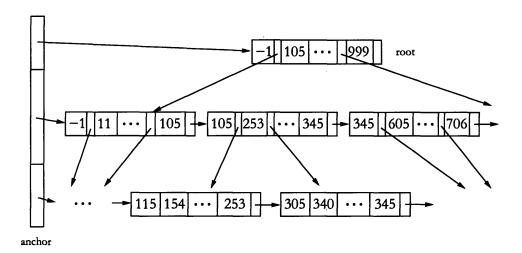

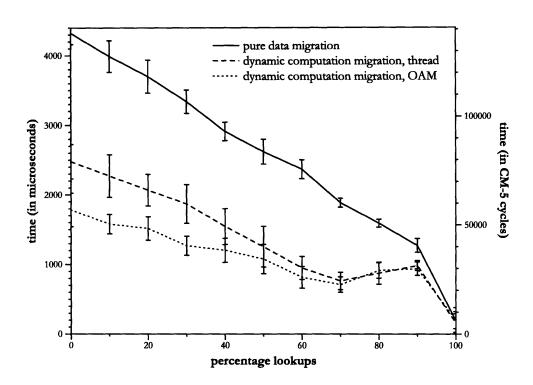

|      | A vertical cross-section of a B-tree                                                   | 92 |

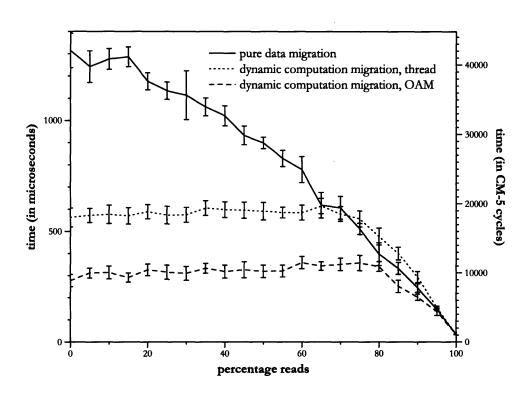

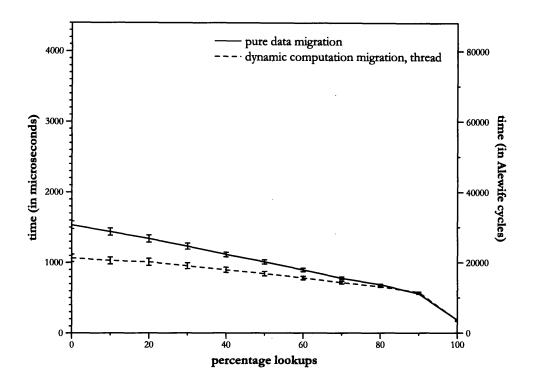

|      | Cost per iteration of accessing a B-tree on Alewife using the STATIC heuristic         | 94 |

| 7-16 | Cost per iteration of accessing a B-tree on Alewife using the REPEAT heuristic  | . 9   |

|------|---------------------------------------------------------------------------------|-------|

| 7-17 | Cost per iteration of accessing a B-tree on the CM-5 using the STATIC heuristic | . 9   |

| 7-18 | Cost per iteration of accessing a B-tree on the CM-5 using the REPEAT heuristic | . 9'  |

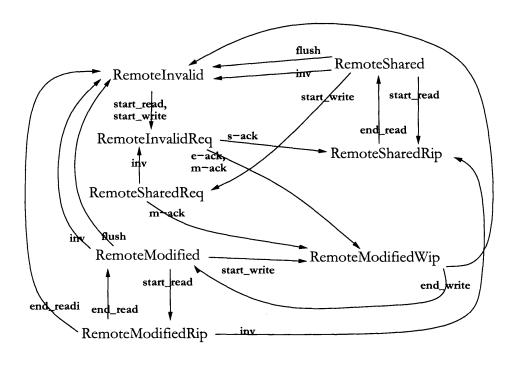

| A-1  | Home state diagram for CRL and MCRL                                             | . 11  |

| A-2  | Remote state diagram for CRL                                                    | . 11  |

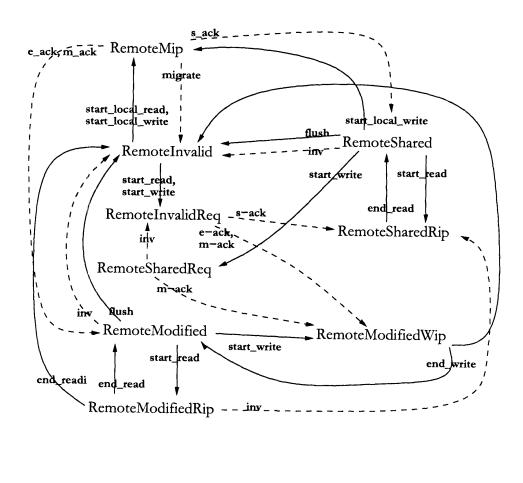

| A-3  | Remote state diagram for MCRL                                                   | . 11  |

| B-1  | LIFO versus FIFO scheduling                                                     | . 120 |

# Chapter 1

# Introduction

This dissertation investigates computation migration, a new mechanism for accessing remote data in a parallel system. Computation migration moves computation to data that it accesses, in contrast to data migration, which moves data to computation (often by making a copy of the data). This dissertation investigates the design issues involved in using computation migration, and describes two implementations of computation migration in distributed shared memory systems. Performance measurements of these systems demonstrate that computation migration is a useful mechanism that complements data migration. In particular, computation migration is particularly appropriate for write operations in applications that use graph traversal.

Computation migration is the partial migration of active threads. Thread state is moved, but not code; the assumption is that the same program is loaded on every processor. Under computation migration, a currently executing thread has some of its state migrated to remote data that it accesses. Others have explored the migration of entire threads for load balancing, but it is not effective for accessing remote data because the granularity of migration is fixed (and typically too large). Computation migration generalizes thread migration by moving only *part* of a thread. In particular, computation migration moves the part of a thread that corresponds to one or more activation frames at the top of the stack. Reducing the amount of state that must be moved for a remote access makes computation migration a cheap mechanism for accessing remote data.

Computation migration performs well when data migration with replication does not. Conversely, computation migration performs poorly when data migration with replication performs well. Data migration with replication improves the performance of read operations (operations that do not modify data), because it allows them to execute in parallel. However, data migration with replication hurts the performance of write operations (operations that modify data), because data must be kept coherent. Computation migration outperforms data migration when there are many writes, because it sends fewer messages: when data is not moved, coherence traffic is eliminated.

Reducing the number of messages sent improves performance for two reasons. First, it reduces the demand for network bandwidth, which reduces the occurrence of network hot spots. More importantly, it removes the various costs of message handling, on both the sending and receiving sides. These costs include marshaling and unmarshaling values, allocating buffers, and dispatching to message handlers.

As part of the coherence traffic that it eliminates, computation migration also avoids moving data. Data migration must move data from processor to processor; in the case of large data (where "large" is relative to the bandwidth of the communication network), simply moving the data from one processor to another can be a major cost.

The remainder of this chapter overviews the research described in this dissertation. Section 1.1 explains the context of this work, distributed shared memory systems. Section 1.2 overviews the systems that I have built to evaluate computation migration. Section 1.3 summarizes my contributions and conclusions. Finally, Section 1.4 outlines the structure of this dissertation.

## 1.1 Context

This dissertation evaluates computation migration in the context of distributed shared memory (DSM) systems. A DSM system is a parallel system with two defining characteristics: memory is physically distributed along with the processors, but the system provides a global shared name space that can be used on any processor. Distributed shared memory systems are important for three reasons. First, they provide for the exploitation of locality; the distribution of memory allows for the distinction between local and remote data. Second, they provide a convenient programming model; the presence of a shared name space simplifies programming. Finally, many of them provide a portable interface for parallel programming.

In order to support local caching of data, most distributed shared memory systems typically use data migration with replication when non-local data is accessed. Data migration means that non-local data is brought to the thread that references it (whether through a pointer indirection or a procedure call); replication means that a copy of the data is brought. Not all systems that provide data migration use replication, but most do in order to improve performance.

Replication leads to the problem of coherence: multiple copies of data must be kept "in sync" so that the address space behaves like a single memory. Although distributed shared memory systems provide a simple (and possibly portable) model of programming, they often cannot achieve the performance of hand-coded message-passing programs. DSM systems typically use only one protocol for maintaining the coherence of data, whereas the access patterns for data vary widely. The Munin project [9] is unique in that it provides various different coherence protocols that can be used for different types of data. However, as in other DSM systems, Munin restricts its attention to the migration of data, and does not allow for the migration of computation.

This dissertation introduces a new mechanism that should be provided in distributed shared memory systems, computation migration, which complements data migration with replication. The choice of mechanism for any particular remote access depends on an application's characteristics and on the architecture on which the application is being executed. Programmers (or preferably compilers) should be able to choose the option that is best for a specific application on a specific architecture.

## 1.2 Overview

In initial work we designed and implemented a prototype of static computation migration. "Static computation migration" means that the programmer statically indicates in the program where computation migration occurs. This prototype was implemented in the Prelude distributed shared memory system [100]. In Prelude we used compiler transformations to implement computation migration based on simple annotations.

This dissertation overviews our Prelude implementation and some of our performance results on a concurrent, distributed B-tree, which lead to two conclusions. First, a software implementation of static computation migration can performs nearly as well on a B-tree as a hardware implementation of data migration with replication. Second, a combination of computation migration and data migration could potentially outperform data migration.

In more recent work, I have designed and implemented a protocol for making a dynamic choice between computation migration and data migration. "Dynamic computation migration" means that the programmer indicates where computation migration may occur; the decision to use data migration or computation migration is deferred until runtime. This dissertation discusses the issues involved in designing such a protocol, as well two heuristics that make good choices between computation and data migration.

The protocol for dynamic computation migration is implemented in the MCRL distributed shared memory system. MCRL is a multithreaded object-based DSM library that provides support for variable-sized, programmer-defined regions of memory. Using a system that supports variable-sized regions avoids the false sharing of data, which can occur in systems that maintain coherence in fixed-sized units. Several DSM systems have gone to great lengths to avoid false sharing in their page-based coherence schemes [19, 60], so it is important to avoid letting false sharing obscure other performance effects.

This dissertation describes the implementation of MCRL, and the results of measuring its performance.

### 1.3 Contributions

This section summarizes my contributions and conclusions:

- I present computation migration, a new mechanism for accessing remote data in parallel systems. Computation migration complements data migration, in that it performs well when data migration does not.

- I describe how a simple annotation can be provided to express computation migration of single activation records. Such an annotation can be used to indicate a static decision to use computation migration, or can be used as a hint to indicate that a dynamic decision between data migration and computation migration should be made.

- I have built a multithreaded distributed shared memory system called MCRL that incorporates

dynamic computation migration. MCRL is a multithreaded extension of the CRL system [52];

it also supports a dynamic choice between computation migration and data migration. MCRL is an all-software distributed shared memory system: it does not depend on any special hardware support to provide shared memory. MCRL runs on the MIT Alewife machine and Thinking Machines' CM-5.

- I describe and evaluate two simple heuristics for choosing between computation migration and data migration, STATIC and REPEAT. My experiments with a microbenchmark demonstrate that simple heuristics can make good choices between data migration and computation migration for reads.

- My experiments demonstrate that computation migration should be used for write operations in the two application kernels measured. For a concurrent distributed B-tree on Alewife, using computation migration for writes improves performance by 44%, relative to pure data migration, when the operation mix consists only of inserts. In addition, my experiments demonstrate that dynamically choosing between data and computation migration for reads can improve performance. For a B-tree on Alewife with 80% lookups and 20% reads, using a dynamic choice for reads improves performance 23% relative to pure data migration; always using data migration for reads only improves performance by 5%.

- A comparison of MCRL on Alewife and the CM-5 provides some insight into architectural issues that impact data migration and computation migration. First, DMA is an important mechanism for data migration. Second, restrictions on message length need to be chosen with care, as they can severely limit performance.

- Finally, this dissertation provides some additional insight into the benefits and restrictions of using optimistic active messages. Optimistic active messages are a communication mechanism that generalizes active messages [95]; we have demonstrated its usefulness in other work [50, 97].

# 1.4 Organization

Chapter 2 overviews several remote access mechanisms: remote procedure call, data migration, and thread migration. It then briefly describes computation migration, and how it compares to the other mechanisms.

Chapter 3 discusses computation migration in more detail. It analyzes the design issues regarding computation migration, discusses why a dynamic choice between computation migration and data migration is useful, and describes two heuristics for making such a choice.

Chapter 4 describes the experimental environment for this dissertation. It overviews the platforms on which I evaluated computation migration: the MIT Alewife machine, Thinking Machines' CM-5, and a simulated version of Alewife on the Proteus simulator.

Chapter 5 describes our initial work on static computation migration. It describes the implementation of static computation migration in the Prelude system, summarizes some of the performance results, and explains why dynamic computation migration can be useful.

Chapter 6 describes the implementation of MCRL and the interface for dynamic computation migration that MCRL provides. It describes the differences between CRL and MCRL, as well as various implementation issues. It concludes by describing some of the implementation details on Alewife and the CM-5.

Chapter 7 describes and analyzes the performance results of using dynamic computation migration in MCRL. It measures the raw performance of MCRL, as well as the behavior of the two heuristics on a microbenchmark and two application kernels.

Chapter 8 discusses related work. Chapter 9 summarizes the results and conclusions of this dissertation and suggests directions for future work.

The appendices provide supplementary information. Appendix A gives some technical details on the internals of the CRL and MCRL systems. Appendix B explains the effect that LIFO scheduling of threads can have on measurement. Appendix C contains the linear regression formulas used to calculate my performance results.

# Chapter 2

# Remote Access Mechanisms

This chapter describes various forms of remote access: remote procedure call, data migration, thread migration, and computation migration. It then briefly compares computation migration to data migration and remote procedure call.

### 2.1 Remote Procedure Call

The most common mechanism for implementing remote access in a message-passing system is remote procedure call (RPC for short), which has been used in both distributed and parallel systems [12]. RPC, which is also referred to as "function shipping," is typically the choice of interface for client-server systems. Part of the reason is that an RPC interface provides protection through encapsulation (analogous to the protection that object-oriented languages provide).

RPC's resemble local procedure calls; the underlying message-passing is hidden by compiler-generated stubs. When an RPC occurs, a local call is made to a client stub, which marshals the arguments and sends a message to the processor where the data resides. At the remote processor, a server stub unmarshals the arguments and calls the procedure. When the remote procedure returns to the server stub, the server stub marshals any result values into a message and returns the message to the client stub; the client stub returns the results to the RPC caller.

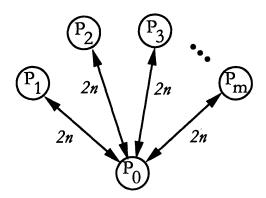

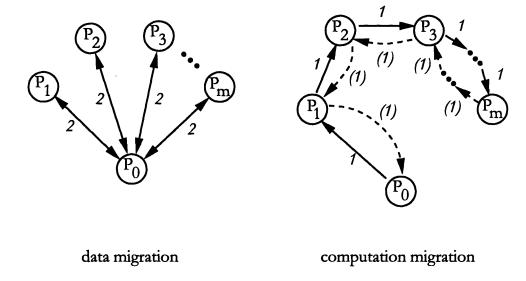

Remote procedure calls require two messages, one for the call and one for the reply. Using RPC for a series of accesses to remote data can result in no locality of access; each successive access is remote. Figure 2-1 illustrates the message-passing patterns of RPC, where one thread on processor  $P_0$  makes n consecutive accesses to each of m data items on processors 1 through m, respectively. A total of 2nm messages are required, ignoring coherence traffic.

One advantage of RPC is that it does not add excessive load on a server. That is, when a remote call finishes and returns, the thread that initiated the call does not consume any more resources on the server. Another advantage of RPC is that it performs well in the case of write-shared data (shared data that is frequently written). Since the semantics of writes requires that they be serialized, there is no parallelism to be gained by replicating data. As a result, when the pattern of writes is unpredictable, it is faster for writers to use RPC instead of moving data from writer to writer.

Figure 2-1. Message pattern under remote procedure call. A thread on processor  $P_0$  makes n consecutive accesses to each of m data items on processors 1 through m, respectively. Coherence traffic is not shown.

## 2.2 Data Migration

Data migration, also known as "data shipping," means that remote data is moved to the processor where a request is made. Data migration can be combined with replication, where a copy of the data is sent to the requesting processor; this introduces the problem of coherence. In the remainder of this dissertation I use "data migration" to include the use of replication, and explicitly state when replication is not involved. Data migration can take the form of hardware caching in shared-memory multiprocessors such as Alewife [1] and DASH [67].

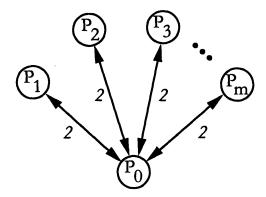

Data migration can also be implemented in software. For example, the Munin system [9] allows the programmer to choose among several different coherence protocols for shared data; some of the protocols use replication, and some do not. The Emerald system [56] is one of the few systems that uses data migration without replication. The use of replication is important for performance, however, particularly for read-shared objects, as it allows locally cached copies to be accessed without network overhead. Figure 2-2 illustrates the message-passing patterns of data migration, where one thread on processor  $P_0$  makes n consecutive accesses to each of m data items on processors 1 through m, respectively. A total of 2m messages are required, ignoring other coherence traffic.

Data migration can perform poorly under several circumstances. First, large data is expensive to migrate. Second, data that is written with any frequency is expensive to keep coherent. Writeshared data appears to occur moderately frequently, and can result in data that migrates from one cache to another with relatively few copies existing at any one time [40]. Some researchers have tried to optimize their cache-coherence algorithms for so-called "migratory data" [30, 89] to reduce the communication required to maintain consistency. Even so, RPC and computation migration require fewer messages than data migration for write-shared data, and can result in better overall performance.

Figure 2-2. Message pattern under data migration. A thread on processor  $P_0$  makes n consecutive accesses to each of m data items on processors 1 through m, respectively. Coherence traffic is not shown.

One important advantage of data migration combined with replication is that it can improve the locality of repeated accesses. After the first access by a thread to some data, successive accesses will be local, assuming that a thread on another processor does not invalidate the first thread's cached copy. In addition, data migration and replication increase the possible concurrency for accessing read-shared data (shared data that is rarely written); multiple copies of data can be read in parallel.

## 2.3 Thread Migration

Thread migration is a mechanism that has primarily been examined as a load balancing technique [24]. "Thread" is used in the sense of lightweight processes [28, 76], which contrasts with "run-to-completion" threads in systems such as TAM [85], Cilk [13], Filaments [34, 36], or Multipol [22]. Run-to-completion threads are even more lightweight than lightweight processes; however, they either cannot block or may only block in a limited set of circumstances.

Thread migration is analogous to process migration [56, 80, 87], but is more lightweight, because processes have much more state than threads. Thread and process migration can occur in two forms: active migration, where currently executing threads or processes are migrated, and inactive migration, where non-executing threads or processes are migrated.

Eager et al. [32] used analysis and simulation to investigate the performance benefits of migrating active processes to improve load balance. They found that active process migration has limited performance benefits over inactive process migration. Their results apply to thread migration as well, since they show that ignoring the cost of migration does not change the qualitative nature of their results.

Although active thread migration is of limited use in balancing load, and not widely used, many systems use inactive thread migration to balance load. To name just a few, the Topaz operating

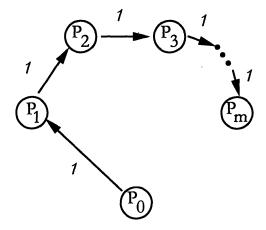

Figure 2-3. Message pattern under computation migration. A thread on processor  $P_0$  makes n consecutive accesses to each of m data items on processors 1 through m, respectively. Coherence traffic is not shown.

system [73] for the Firefly multiprocessor workstation [92] migrates inactive threads. Markatos [71] explored a scheduling policy that favors locality over load balance: threads are initially scheduled based on expected accesses, and idle threads are migrated to balance load. Anderson et al. [3] studied, among other things, the performance implications of using local queues for waiting threads; threads in these queues could be migrated to balance load.

None of these systems explored the possibility of using active thread migration to improve the locality of a remote access. The major problem with such an approach is that the grain of migration is too coarse: migrating an entire thread can be expensive. As a result, migrating an entire thread for a remote access may be overkill for two reasons. First, much of a thread's state may be unrelated to the access. Second, migrating an entire thread could cause load imbalance.

# 2.4 Computation Migration

Computation migration is a generalization of active thread migration, in which a portion of a thread migrates upon a remote access. Migrating only part of a thread reduces the granularity of migration, which alleviates the two problems of thread migration. First, we can migrate only the state relevant to a remote access. Second, we can avoid load imbalance by moving only small pieces of computation.

Figure 2-3 illustrates the message-passing patterns of computation migration, where one thread on processor  $P_0$  makes n consecutive accesses to each of m data items on processors 1 through m, respectively. A total of m-1 messages is required (plus one additional message if the call must return to  $P_0$ ), ignoring coherence traffic. Computation migration requires only "one-way"

messages, because unnecessary return messages are not sent. This optimization is a form of tail forwarding [48], which is a generalization of tail recursion to parallel systems.

Computation migration also gives some of the benefits of thread migration and RPC. If we move part of a thread's stack to the remote data, we can receive the benefit of increased locality of accesses; for example, if the executing thread makes a series of accesses to the same data, there is a great deal to be gained by moving those accesses to the data. At the same time, we gain the benefit of RPC; we can vary the granularity of the computation to be performed at the data. Keeping the computation small allows us to avoid the problem of overloading the resources at a single processor, since we move only the amount of state necessary to improve locality.

The cost of computation migration depends on the amount of computation state that must be moved. If the amount of state is large (such as a substantial portion of a thread) computation migration will be fairly expensive. In addition, when the amount of data that is accessed is small or rarely written, data migration with replication (especially when done in hardware) should outperform computation migration.

Computation migration is the dual of data migration. Instead of moving data to computation that accesses the data, the system moves the computation to the data. If a computation accesses different data, not all of which are on the same processor, some data migration may need to occur. In some cases it may be better to migrate the computation as well as some of the data; the pure data migration solution of always migrating all of the data to the computation may not always be the best.

# 2.5 Comparison

When comparing computation migration and data migration, the most obvious performance benefit is that computation migration does not move data. Although the resulting increase in performance can be great for very large data, it is not the primary reason that computation migration can outperform data migration. Figures 2-1 through 2-3 illustrate how computation migration can save messages when traversing a data structure, but that savings is also not the major benefit of computation migration. The major benefit of computation migration is that coherence traffic is eliminated.

The reason that computation migration reduces coherence traffic is because a migrated computation leaves the data in place for the next migrated computation. That is, the performance gain results from keeping the data at one processor. As a result, successive migrated computations need not perform any coherence activity. Although specialized coherence protocols can sometimes be used to reduce the cost of coherence (as in Munin [9]), they do not help when data is accessed unpredictably.

Although computation migration does not incur the cost of maintaining coherence, it has the disadvantage that it does not allow for replication. Replication allows reads from multiple processors to occur locally and in parallel, which dramatically improves their throughput. As a result, computation migration is more effective for write-shared data, whereas data migration with replication is more effective for read-shared data.

Finally, remote procedure call can be viewed as a special case of computation migration in which no thread state is migrated. As a result, using RPC can save coherence messages, just as computation migration does. The use of computation migration, however, can make successive accesses by a thread local; the use of remote procedure call means that successive remote procedure calls are non-local. (Section 8.3 describes research that investigates the batching of RPC's so as to reduce communication costs.) Similarly, computation migration saves messages by "short-circuiting" return messages; when a computation migrates and then executes a procedure, the procedure can return locally to its caller.

# Chapter 3

# Computation migration

The use of data migration treats a parallel machine as a two-level memory hierarchy: from the point of view of any processor, there is local memory and remote memory. However, a distributed-memory parallel machine is not just a memory hierarchy: computation can move from one memory's processor to another memory's processor. Remote procedure call allows computation to be initiated at a remote processor, but does not allow an existing computation to migrate. This chapter discusses high-level issues regarding computation migration: how much computation should be migrated, when computation should be migrated, how computation migration can be expressed, and how it can be implemented.

Section 3.1 discusses how computation can be migrated. Section 3.2 discusses how simple program annotations can be used to indicate the use computation migration. Finally, section 3.3 discusses how the decision to use computation migration can be made.

#### 3.1 Mechanics

Computation migration is partial thread migration. The first issue that must be resolved is the granularity at which computation is migrated. The simplest solution is to migrate a single activation record. Not only is it the unit in which a stack is usually allocated, but it is also easy to express the migration of an activation record, as described in Section 3.2.

It would be possible to migrate either multiple activation records, or just a portion of an activation record. The activation record/procedure unit is a unit of measure determined by the abstractions in a program, and may not always be the correct unit of migration. For example, it may be useful to migrate just the execution of a single loop in a procedure, instead of migrating the entire procedure.

Issues relating to the migration of partial or multiple records are discussed as they arise. The implementations of computation migration described in this dissertation only migrate single activation records. However, there is no fundamental reason why this research could not be generalized to migrate partial or multiple records.

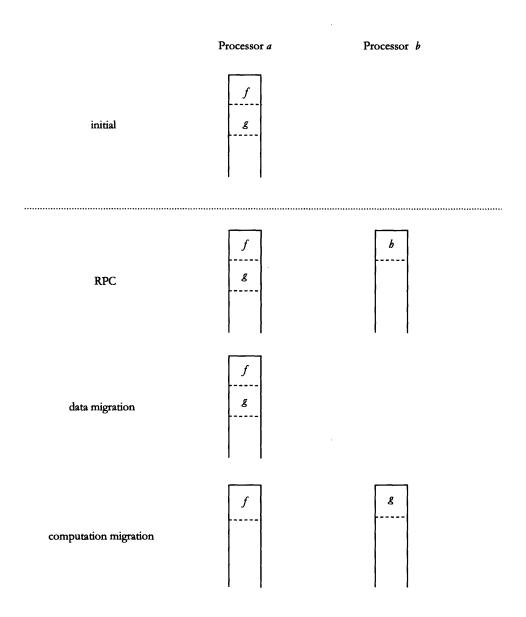

Figure 3-1. Stack patterns under different access mechanisms. Processor a is executing a thread, where f has called g. g is about to access remote data on processor b. Stacks grow downward in this figure.

Figure 3-1 illustrates the movement of activation records under RPC, data migration, and computation migration. In the figure, "initial" is the starting state. Processor a is currently executing a thread. In this thread, the procedure f has called the procedure g. g is about to access remote data on processor b. Under RPC, g calls a remote procedure h that runs in a new thread on processor b; this procedure returns its value to g. Under data migration, the data is moved or copied to processor a, and execution continues on processor a. Under computation migration, the activation record for g is moved to processor b, where the access to the data occurs.

In RPC implementations, compiler-generated "stubs" marshal arguments and return results. The stubs hide the details of communication from the actual code for g and h, so that the compiler can generate code for them normally. In data migration implementations, either the compiler, library, operating system, or hardware is responsible for moving data.

In computation migration implementations, some mechanism must be provided to move activation records. To move activation records safely, we must restrict the use of computation migration so that a processor does not export non-global memory addresses. This restriction only exists for implementations of computation migration that are not run on shared-memory systems.

The remainder of this section describes two implementations of computation migration. These two implementations have complementary strengths and weaknesses, and could be used together in one implementation. The first implementation described relies on the runtime system to implement migration, and has been implemented in the Olden system [42]. The second relies on the compiler to generate code to handle migration, and was implemented in Prelude [51]. MCRL provides an interface for a compiler-based implementation, but does not provide compiler support for using it.

#### 3.1.1 Runtime System

The most direct implementation of computation migration is to have the runtime system move an activation record. In other words, the runtime system must contain enough functionality to marshal an activation record, send it over the network, and unmarshal the activation record onto a stack. After setting a return stub, the runtime system can then return control directly to the migrated code. When the migrated code returns, the stub is responsible for returning control back to the original processor. The Olden project [17] takes this approach in implementing computation migration.

This implementation is flexible, in that multiple activation records can be migrated in a straightforward manner. However, it suffers from several complications. First, a simple implementation will move some unnecessary data; not all of the data in an activation record will be live at the time of migration. In order to avoid moving dead data, the interface for migrating an activation record must be fairly complex. The compiler must generate a template for each migration point that indicates which entries in an activation record are live. Second, even if moving dead data is not an issue, a similar issue arises if a partial frame needs to be moved. In order to move a partial activation record, the compiler would again need to tell the runtime system what slots in a record to move.

#### 3.1.2 Compiler

Another approach to implementing computation migration is to have the compiler (or user) explicitly generate migration procedures. Such an approach can be viewed as having the compiler

generate specialized migration code for each procedure. The compiler must generate a new procedure for each migration point. This procedure represents a "continuation" of the original procedure, in that it contains the code to be executed from the migration point to the end of the procedure. This continuation procedure is the code that is executed after a migration occurs. The data that needs to be moved to execute the continuation procedure is the set of live variables at the migration point.

This approach can produce better migration code, in that only the portion of the stack frame that needs to be migrated is actually transmitted. In addition, this approach is easily generalized to move a partial activation record. However, it suffers from two drawbacks. First, it leads to code expansion. By producing specialized code for each migration point, the compiler winds up duplicating a large amount of code. Second, generalizing this approach to migrate multiple frames requires some extra mechanism. For example, one way to extend this approach to the migration of multiple frames would be to pass the proper continuation procedure at every procedure call. Such a solution would risk making the common case (any procedure call) more expensive to support computation migration.

## 3.2 Program Annotation

There are several important reasons to use annotations for computation migration. First, it is simple to experiment with computation migration. Changing where migration occurs simply involves moving the annotation, and the programmer can easily switch between using computation migration, RPC, and data migration. Second, the annotation affects only the performance of a program, not its semantics. In other words, the annotation only affects where computation executes.

Some languages permit a programmer to code a structure explicitly that mimics the effect of computation migration. For example, Actor-based languages [70] encourage a "continuation-passing" style for programs, in which each actor does a small amount of computation and then calls another actor to perform the rest of the computation. In effect, the computation migrates from actor to actor. By carefully designing the message-passing structure of the program, a programmer can optimize the communication cost.

For several reasons, computation migration should not be coded explicitly into the structure of a program. The most important reason is that such programs are difficult to tune and port. Performance decisions in such a program are closely intertwined with the description of the algorithm; changing the communication pattern may require substantial changes to the program, and may result in inadvertent errors being introduced into the computation. It is better to separate the description of the computation from the decisions of how it is to be mapped onto a particular machine, and to let the compiler handle the details of the message-passing for computation migration.

Finally, experience with both parallel and distributed systems indicates that programming in terms of explicit message-passing can lead to programs that are much more complex than ones written in terms of shared memory. An explicit message-passing style is also undesirable from

```

void traverse(node *n)

{

read_lock(n);

while (! is_leaf(n)) {

next = next_node(n, k);

read_unlock(n);

n = next;

read_lock(n); move /* annotation */

}

read_unlock(n);

}

```

Figure 3-2. Sample annotation for computation migration. The annotation indicates that the procedure traverse should use computation migration to access n if it is remote.

a software engineering perspective, because it requires the modification of the interfaces of data objects to include additional procedures that represent the migrated computations.

Figure 3-2 illustrates how a simple annotation can be used to indicate computation migration in a C-like pseudocode. The annotation indicates that at the bottom of each iteration of the while loop, the computation should migrate to the next node if the node referenced by n is not local. The entire activation record moves; that is, the computation from the move annotation to an exit from traverse executes on the remote processor, unless it migrates again to yet another processor.

A simple annotation for migrating a partial frame is illustrated in Figure 3-3. Two annotations are used; one to indicate where a migration should begin, and one to indicate where a migration should return. In the figure, the annotations indicate that the code between read\_lock and write\_lock, inclusive, is the code to be migrated. If n is non-local when read\_lock is called, that block of code should execute on the processor where n is located. When the read\_unlock operation completes, control should return back to where traverse2 was executing.

A simple annotation for migrating multiple activation records is difficult to design, and is left for future work. Moving a single or partial record is easier to specify, since the textual representation of an activation record is captured by a single procedure. In addition, the migration of multiple records should be flow-sensitive; that is, multiple records should be migrated for certain call chains, but not for others.

## 3.3 Migration Criteria

This section describes how the decision to use computation migration could be made. First, it could be made statically, based on programmer knowledge about object sizes and reference patterns. If such knowledge is insufficient, a dynamic choice is necessary.

```

void traverse2(node *n)

{

read_lock(n); begin move /* annotation */

/*

some operations on n

*/

read_unlock(n); end move /* annotation */

}

```

Figure 3-3. Sample annotation for computation migration of a partial frame. The annotation indicates that the procedure traverse2 should use computation migration to access n if it is remote when read\_lock is called. The code should migrate back after read\_unlock.

#### 3.3.1 Static

The simplest strategy for providing computation migration is for the programmer to decide statically where computation migration should occur in a program. The decision can be indicated with a simple annotation, such as the one described in Section 3.2. The decision to use computation migration is based on the knowledge that computation migration outperforms data migration with replication under either of the following conditions:

- The object being accessed is large, so moving it rather than the computation is expensive.

- The object being accessed is written often, so maintaining coherence is expensive.

Although the first condition is easy to detect, the second may not be. More importantly, most objects are likely to be small, so the more important factor in determining whether to use computation migration is likely to be the second. As a result, except in the case of write-only or write-mostly data structures, it may be difficult for a programmer to know at compile-time that a remote access should always be performed using computation migration.

Another difficulty with statically determining when to use computation migration is that the same code may be used to access either a read-shared or a write-shared object. For example, in Figure 3-2, it is not possible to know whether the variable n will refer to a read-shared or a write-shared object. It would only be possible to know if the objects on which traverse is called are either all read-shared or all write-shared. This condition may hold for certain applications. For example, the counting network, which I describe in Section 7.3.1, is a completely write-shared data structure. However, for general data structures it is unlikely that the condition is true.

## 3.3.2 Dynamic

If the programmer cannot statically determine when computation migration should occur, then the logical choice is to choose dynamically when to use computation migration. Since the runtime system can monitor the reads and writes of an object, it can determine when computation migration would be beneficial. The programmer still uses an annotation, but the annotation becomes a hint. The runtime system is responsible for deciding whether the hint should be followed.

Unfortunately, past performance is not a guarantee of future performance. In other words, it is not in general possible to predict the future frequency of writes based on the past frequency of writes. However, in order to make a dynamic decision tractable, we must assume that the relative frequencies of reads and writes stay relatively constant for over short periods of time. Compile-time information can sometimes be used to predict future access patterns [5], but the information that can be gained using current techniques is limited.

We could use many metrics to determine the frequency of reads and writes. For example, any of the following might be useful:

- The average number of reads between writes. This measure would require some bookkeeping on every operation.

- The relative frequency of reads and writes. This measure requires a mechanism for counting time, which is difficult. It also requires some bookkeeping on every operation.

- The average number of read copies when a write begins. This measure is equivalent to the average number of invalidations that a write must perform.

- The average cache hit rate. Computing the hit rate requires bookkeeping on local operations, which is undesirable.

- The number of threads on each processor. Keeping count of the number of threads gives an indication of the load balance.

All of these metrics are fairly complex. They also require a mechanism for weighting more recent measurements more heavily than older measurements. Although the above metrics may lead to good decisions, the cost of computing them is relatively high. The following section describes two simple heuristics that make relatively good choices.

#### 3.3.3 Dynamic Protocol

The first question that arises when designing a protocol for dynamically choosing between data and computation migration is which processor makes the choice. When a client accesses non-local data of which it has a cached copy, it need not perform any protocol processing. However, when it does not have a cached copy, it must contact the server. When the client contacts the server, either processor could decide between data or computation migration:

- The client can decide whether to use data or computation migration. There is no overhead to using either mechanism beyond the decision itself.

- The client can request that the server decide to use data or computation migration. There is some overhead involved for either mechanism, since the client must pass enough information to allow the server to make the decision.

My protocol uses a server-based choice because the server has the most information about the pattern of global accesses to data. Although a client can keep track of its own access patterns, it does not have any information about other clients' access patterns. Even if the server regularly broadcasts global information to clients (which could potentially be expensive), a client never has information that is as up-to-date as the server. In addition, since the client must contact the server anyway, it seems advantageous to make use of the server's extra knowledge of global access patterns.

The protocol does not add any extra messages for using data migration, but does add an extra message for computation migration. It may be possible to design a dynamic migration protocol that does not require this extra acknowledgment, but this design point was chosen for the sake of simplicity.

A client and server interact in the protocol in the following manner. When a client accesses a local object (either its home is local or it is cached), the local copy can simply be used without any communication. When a client accesses a remote object, it sends a *migration request* message to the server. (It must also send such a message if it tries to acquire a read-only copy of a region in write mode.) This message must contain enough information for either data migration or computation migration to occur. That is, the processor must be in a state such that it can receive either a copy of the data or a migration acknowledgment, which I describe below.

When the server receives a migration request message, it must first decide whether to send the data back or to execute some computation. If the server decides to use data migration, it sends the data back to the client. If the server decides to use computation migration, it must send back a "migration acknowledgment" to the client; it can then either create a thread to defer the computation, or execute it directly.

Figure 3-4 illustrates some possible message patterns using my dynamic protocol. When a processor receives a migration request message, it decides whether to send back data or notify its client that it has decided to execute computation. The dynamic computation migration protocol requires more bandwidth than static computation migration, since the migration acknowledgment must be sent. However, the cost of sending and receiving this extra message does not have to be on the critical path of the migration, as this acknowledgment can be sent in the background. In Figure 3-4 the same decision (to migrate data or computation) is made at every processor; it is also possible for different decisions to be made at each processor.

#### STATIC Heuristic

The STATIC heuristic always migrates computation for non-local writes and data for non-local reads. Ignoring considerations of load balance, it is intuitively a clear benefit to always migrate writes to data (assuming that the computation is not much larger than the data). Given the semantics of writes, they must always be serialized anyway. As a result, it makes sense to execute them all at one processor, which avoids the cost of moving data from one writer to another. The only case where this heuristic fails to perform well is when exactly one remote processor accesses the region (and

Figure 3-4. Message patterns under a dynamic protocol. Messages labeled in parentheses can be sent in the background. Coherence traffic is not shown.

the processor occasionally writes the region). Note that the STATIC heuristic is not truly a dynamic scheme; in most programs any use of a CRL function can statically be determined to be either a read or a write.

The decision to migrate computation or data in the case of reads is less clear. There is an inherent tension between computation migration and data migration combined with replication. If reads are computation-migrated to the home, performance is reduced when there are many more reads than writes: future reads do not hit in the cache. On the other hand, if reads migrate data back to themselves, performance is reduced when there is a substantial number of writes: future writes must invalidate more cached copies of data.

#### REPEAT Heuristic

The REPEAT heuristic always migrates computation for non-local writes, for the same reason that the STATIC heuristic does. It dynamically chooses data migration or computation migration for non-local reads, depending on the relative frequency of reads and writes. The heuristic uses computation migration for reads that follow writes, until any processor performs a second read before another write occurs. That is, if a processor manages to execute two reads before any writes occur, data migration should be used.

The logic underlying this heuristic is that data migration will be useful when replication will help, which is exactly when multiple reads occur at one processor. Given the assumption that the relative frequency of reads and writes remains relatively constant over several operations, we interpret the

fact that two repeated reads occurred to mean that repeated reads are likely to occur in the near future.

Intuitively, this heuristic will perform better than the STATIC heuristic when there is a large proportion of writes. The STATIC heuristic migrates reads even when there are many writes. As a result, it forces writes to invalidate replicated copies unnecessarily. However, the REPEAT heuristic should do worse when the operation mix consists predominantly of reads, since it migrates some read operations following a write. As a result, the percentage of cache hits will decrease.

# Chapter 4

# **Experimental Environment**

This chapter describes the experimental environment for this dissertation. The evaluation of dynamic computation migration was done on two machines: the MIT Alewife machine and Thinking Machines' CM-5. The comparison of the two implementations demonstrates how communication performance and multithreading support affects DSM systems in general, and data migration and computation migration in particular.

- Although the CM-5's network has a greater total aggregate bandwidth into each processor, Alewife is able to use achieve a higher data transfer rate.

- The restriction on message length on the CM-5 dramatically reduces its communication performance.

- The high cost of context switching on the CM-5 dramatically reduces the advantage of multithreading.

In addition, various other architectural features have an effect on system performance. First, the expense of active message support on Alewife makes our optimistic active messages mechanism (which is described in Section 6.2.3) perform poorly. Second, the register windows on the CM-5 reduce the performance of active messages, and are the primary reason that context switches are so expensive.

Section 4.1 and 4.2 describe the important characteristics of Alewife and the CM-5. The implementation of dynamic computation migration in MCRL on these two machines is described in Chapter 6. Section 4.3 summarizes the main differences between Alewife and the CM-5. Section 4.4 describes the Proteus simulator and the simulation of Alewife that we used in our work on static computation migration, which is described in Chapter 5.

#### 4.1 Alewife

Alewife [1] is an experimental shared-memory multiprocessor. The Alewife architecture consists of processor/memory nodes connected by a packet-switched interconnection network. The network

is organized as a low-dimensional mesh; on the current machine it has two dimensions. The raw bandwidth of an interconnection link is approximately 45–50 Mbytes/second in each direction.

Each processor/memory node consists of a Sparcle processor [2], an off-the-shelf floating-point unit, a direct-mapped, 64K unified cache with 16-byte lines, eight megabytes of DRAM, the local portion of the interconnection network, and a Communications and Memory Management Unit (CMMU). The 8M of DRAM is divided into three portions, the first two of which can be used by the programmer: 4M of shared memory, 2M of local memory, and 2M of shared-memory directory. The Sparcle processor is derived from a SPARC v7 processor, and as a result is similar to a CM-5 processor.

Alewife provides efficient support for both coherent shared-memory and message-passing communication styles. Shared memory support is provided through an implementation of the LimitLESS cache coherence scheme [21]. In LimitLESS, limited sharing of memory blocks (up to five remote readers) is supported in hardware; higher-degree sharing is handled in software by trapping the home processor.

In addition to providing support for coherent shared memory, Alewife provides the processor with direct access to the interconnection network [62]. Efficient mechanisms are provided for sending and receiving both short (register-to-register) and long (memory-to-memory) messages. Using these message-passing mechanisms, a processor can send a message in a few user-level instructions. A processor that receives such a message traps; user-level software can respond either by executing a message handler or by queuing the message for later consideration.

#### 4.1.1 Hardware Overview

Alewife uses the SPARC register windows [86] as four hardware contexts for fast multithreading. As an example use for these contexts, the Alewife runtime system can be configured to automatically context switch to another hardware context upon a remote memory reference. The hardware contexts are also used for handling active messages; a hardware context is always left free for active messages to execute in. My experiments only use one hardware context for computation, and leave the remaining ones for active message handling.

Two bugs in the CMMU chip are worth mentioning. First, because of a timing conflict between the CMMU and the floating-point unit, codes that make significant use of floating-point computation must run at 20 MHz instead of the target clock rate of 33 MHz. Because of this, all Alewife experiments are run at 20 MHz. Second, in order to ensure data integrity when using the block transfer mechanism, it is necessary to flush message buffers from the memory system before using DMA. This overhead cuts the peak bandwidth of the block transfer mechanism from approximately 2.2 bytes/cycle (44 Mbytes/second at a 20 MHz clock rate) to roughly 0.9 bytes/cycle (18 Mbytes/second). Both of these bugs will be fixed in a planned respin of the CMMU.

Alewife uses a heuristic deadlock avoidance mechanism for the network. Whenever a processor detects that its send queue is full for "too long," it assumes that the network is clogged. The processor begins taking packets out of the network until it determines that the network is unclogged; when the network is unclogged, it then relaunches these packets. This mechanism definitely affects performance (and there appear to be bugs when network traffic is high), but turning it off risks deadlock. In my experiments the timeout is set to 65535 cycles (approximately 3.3 milliseconds).

#### 4.1.2 Software Overview

The Alewife C compiler is a research compiler that achieves approximately 90% of the performance of gcc with an optimization level of 02. It compiles a superset of C that includes a set of message-passing mechanisms. The compiler and runtime system provide support for creating computation in the form of two calls: thread\_on and user\_do\_on. The former call is used to create a thread (on any processor) to initiate computation; the latter is used to start an active message.

Threads on Alewife are non-preemptive. In other words, threads must explicitly yield the processor. However, threads can be interrupted by active messages, which execute in a separate hardware context. It takes approximately 175 cycles for a thread to be created and then start running after the thread creation message interrupts the processor. This assumes that no other thread is running, and that a context switch to the newly created thread happens immediately.

Active messages in Alewife are more general than those originally described by von Eicken et al. [95]. Active messages run atomically; that is, other active messages cannot interrupt the processor while an active message is running. It costs approximately 60 cycles for an active message to start executing after it has interrupted a processor.

The Alewife runtime system allows active messages to become "half-threads." A half-thread can be interrupted by another active message, but cannot block. The transition to a half-thread is accomplished by the user\_active\_global call, which takes about 100 cycles in the fast case (when the instruction path is warm and a free thread exists). However, if the total number of active threads and half-threads overflows the number of free hardware contexts, a half-thread can be descheduled. In the respin of the CMMU, the fast-case transition should only take a few cycles.

The support for the transition to a half-thread allows an active message to use software atomicity mechanisms. Before the transition to a half-thread, an active message is guaranteed to run atomically. During this time, it can setup software mechanisms for atomicity. Following the transition, it can then assume that it is still running atomically. Figure 4-1 illustrates this use of user\_active\_global; it contains an abstracted version of some message handling code from within the CRL distributed shared memory system.

The message handler illustrated in Figure 4-1 runs as an active message. It is not interruptible until it executes user\_active\_global. If the global variable atomicity\_bit is set, it means that a previous handler is executing; a continuation for the current call must be created. Otherwise, atomicity\_bit is set, and the call is executed.

The half-thread transition can be viewed as a variant of optimistic active messages [50, 97], which is describes in Section 6.2.3. Active messages on Alewife have hardware support in the form of the hardware contexts that Sparcle provides. However, the transition does not the same functionality as optimistic active messages. Several important restrictions of the current implementation of the runtime system limit its usefulness. These problems are not inherent in the system, but are merely artifacts of the current runtime system.

First, active messages can only transition to half-threads, not full-fledged threads that can block. Allowing optimistic active messages to block is one of the important features of the optimistic active message model. Future versions of the Alewife kernel should allow active messages to transition to full threads.

```

void message_handler(void)

/* active message handler */

if (atomicity_bit) {

/* create a continuation

and discard the message

*/

return;

}

/* extract the function and its arguments

from the message,

and discard the message

/* set the software atomicity bit */

atomicity_bit = 1;

/* transition to a half-thread */

user_active_global();

/* execute the function */

atomicity_bit = 0;

```

Figure 4-1. Software atomicity with half-threads on Alewife. This code is abstracted from the internals of the CRL distributed shared memory system.

Second, active messages and their associated half-threads are not guaranteed to execute in LIFO order. When an active message transitions to a half-thread, it may be descheduled to allow the last active message to run. Allowing a half-thread to be descheduled breaks the intended model of execution, where the transition allows further active messages to interrupt the processor. As a result, guaranteeing atomicity during the execution of nested active messages is expensive. This effect is discussed in more detail in Section 6.4.1.