# Memory System Architecture for Real-Time **Multitasking Systems**

by

Scott Rixner

Submitted to the Department of Electrical Engineering and Computer Science in Partial Fulfillment of the Requirements for the Degrees of

Bachelor of Science in Computer Science and Engineering and Master of Engineering in Electrical Engineering and Computer Science

at the

Massachusetts Institute of Technology

May 1995

© Scott Rixner, 1995. All rights reserved.

The author hereby grants to MIT permission to reproduce and to distribute publicly paper and electronic copies of this thesis document in whole or in part, and to grant others the right to do so.

Author .....

..... Department of Electrical Engineering and Computer Science May 26, 1995

Certified by ..... .....

> Jonathan Allen Professor of Electrical Engineering and Computer Science Director, Research Laboratory of Electronics Thesis Supervisor

10

Certified by ..... ...... C. Ross Ogilvie Advisory Engineer, International Business Machines Corporation

Thesis Supervisor (Cooperating Company)

Accepted by ..... Frederic R. Morgenthaler Chairman, Department Committee on Graduate Theses MASSACHUSETTS INSTITUTE OF TECHNOLOGY

AUG 1 0 1995

LIBRARIES Barker Eng

## Memory System Architecture for Real-Time Multitasking Systems

by

### Scott Rixner

Submitted to the Department of Electrical Engineering and Computer Science on May 26, 1995, in partial fulfillment of the requirements for the Degrees of Bachelor of Science in Computer Science and Engineering and Master of Engineering in Electrical Engineering and Computer Science

# ABSTRACT

Traditionally, caches have been used to reduce the average case memory latency in computer systems. However, real-time systems using preemptive scheduling algorithms cannot make use of this reduced latency, as it is not deterministic. A real-time system only benefits from an improvement of the worst case performance. Caches do little to improve worst case performance because preemptions allow cached data to be overwritten at unpredictable times, leading to nondeterministic behavior. Real-time systems using execution quantization can deterministically make use of a significant portion of the processor's resources despite the use of slow memory. Execution quantization allows deterministic caching by guaranteeing that tasks can execute for fixed length blocks of time once they start running, thereby controlling preemptions, and allowing cache restoration to occur predictably and efficiently.

Thesis Supervisor: Jonathan Allen Title: Professor of Electrical Engineering and Computer Science

# **Table of Contents**

| 1 | Intro      | Introduction                            |     |  |

|---|------------|-----------------------------------------|-----|--|

|   | 1.1        | Real-Time Computer Systems              | .11 |  |

|   | 1.2        | Research Goals                          | .12 |  |

|   | 1.3        | Organization                            | .13 |  |

| 2 | Real-      | Time Systems                            | .17 |  |

|   | 2.1        | Designing for Determinism               | .17 |  |

|   | 2.2        | The Frame Manager                       | .22 |  |

|   | 2.3        | Caching                                 | .27 |  |

| 3 | Desig      | gning a Real-Time Cache                 | .33 |  |

|   | 3.1        | Characteristics of the Target System    |     |  |

|   | 3.2        | Design Parameters                       | .35 |  |

| 4 | Mem        | ory Bandwidth                           | .41 |  |

|   | 4.1        | Cache Performance                       | .41 |  |

|   | 4.2        | Decreasing Memory Latency               | .42 |  |

|   | 4.3        | Reducing the Miss Rate                  | .44 |  |

| 5 | A Sir      | ngle Frame Manager System               | .47 |  |

|   | 5.1        | The Single Frame Manager                | .47 |  |

|   | 5.2        | The Loader and Unloader                 | .49 |  |

|   | 5.3        | Using DRAM in Page Mode                 | .50 |  |

|   | 5.4        | Task Timing                             | .51 |  |

| 6 | Exec       | ution Quantization                      |     |  |

|   | 6.1        | Preemptions                             | .53 |  |

|   | 6.2        | Quantization                            | .54 |  |

|   | 6.3        | Loading and Unloading the Cache         | .60 |  |

|   | 6.4        | The Operating System                    |     |  |

|   | 6.5        | Hardware Implementation of Quantization |     |  |

|   | 6.6        | DRAM Refresh                            | .69 |  |

|   | 6.7        | Memory Bandwidth                        | .70 |  |

|   | 6.8        | Shared Memory                           |     |  |

| 7 | Expa       | nding Execution Quantization            | .83 |  |

|   | 7.1        | Task Timing                             |     |  |

|   | 7.2        | On Chip DRAM Example                    | .90 |  |

|   | 7.3        | Real-Time Cache Performance             |     |  |

| 8 | Conc       | lusions                                 |     |  |

|   | 8.1        | Results                                 | 115 |  |

|   | 8.2        | Future Work                             | 116 |  |

| R | References |                                         |     |  |

# **List of Figures**

| Figure 2.1: A Periodic Execution Frame                                      | 18  |

|-----------------------------------------------------------------------------|-----|

| Figure 2.2: A Preemption by a Task with a Faster Frame Rate                 | 24  |

| Figure 2.3: Preemptions in Dynamic Deadline Scheduling                      | 25  |

| Figure 2.4: Conceptual LIFO Stack for the Schedule in Figure 2.3            | 26  |

| Figure 3.1: A Code Fragment and its Associated Graph Representation         | 39  |

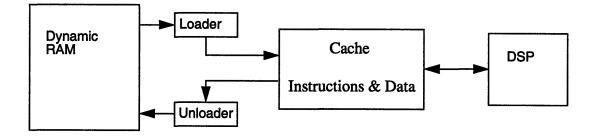

| Figure 5.1: Overview of a Real-Time Caching System                          | 49  |

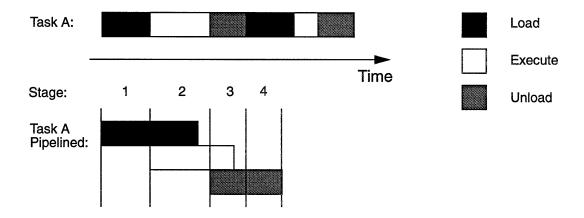

| Figure 5.2: Task Execution with One Frame Manager                           | 50  |

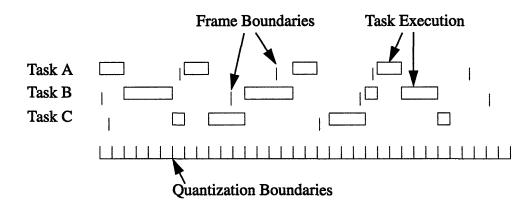

| Figure 6.1: Quantized Execution Using Dynamic Deadline Scheduling           | 55  |

| Figure 6.2: An Arbitrary Frame in the Schedule                              | 58  |

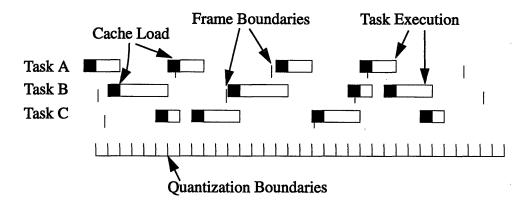

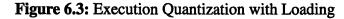

| Figure 6.3: Execution Quantization with Loading                             | 62  |

| Figure 6.4: Execution Quantization with Speculative Loading                 | 62  |

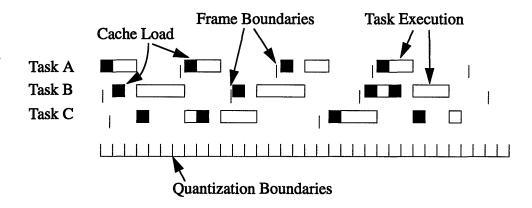

| Figure 6.5: Quantization Hardware                                           | 67  |

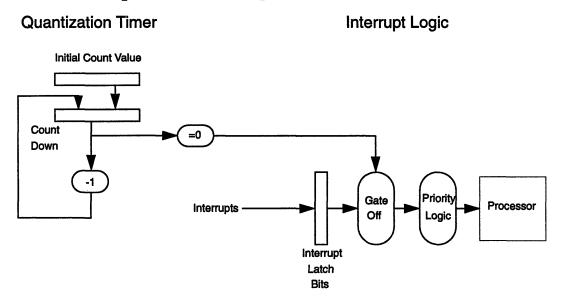

| Figure 6.6: A Real-Time Caching System                                      | 68  |

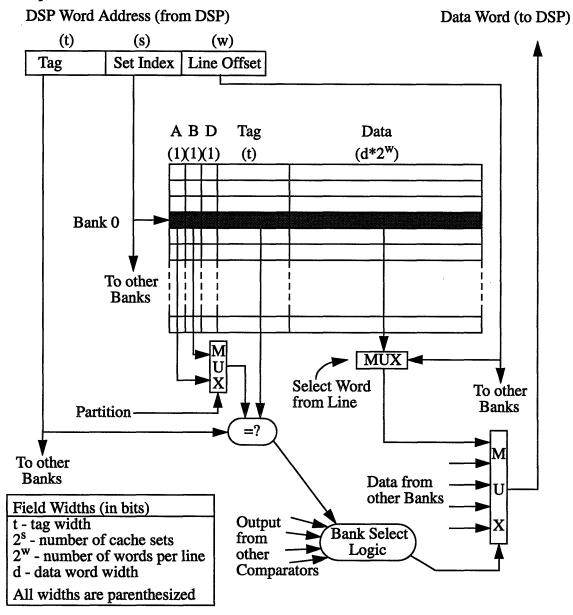

| Figure 6.7: A Data Read in a Cache with Virtual Partitions                  | 78  |

| Figure 7.1: Distribution of Cache Unload/Load Time in a Quantization Block. | 86  |

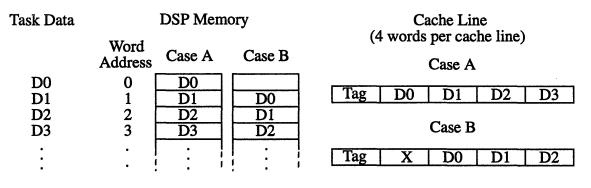

| Figure 7.2: The Affect of Load Placement on Cache Line Contents             | 87  |

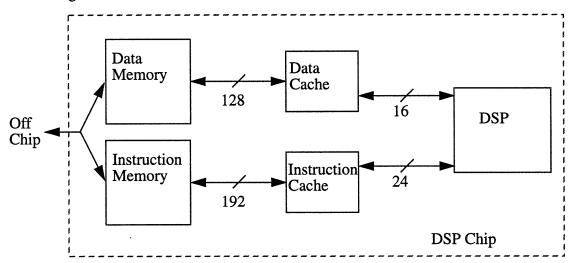

| Figure 7.3: On Chip DRAM System Configuration                               | 91  |

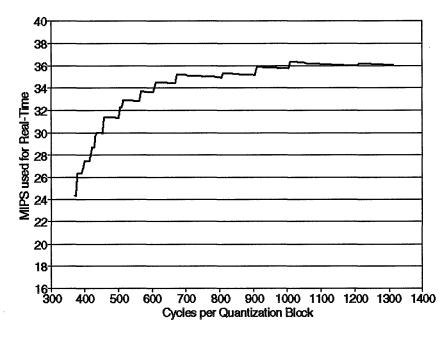

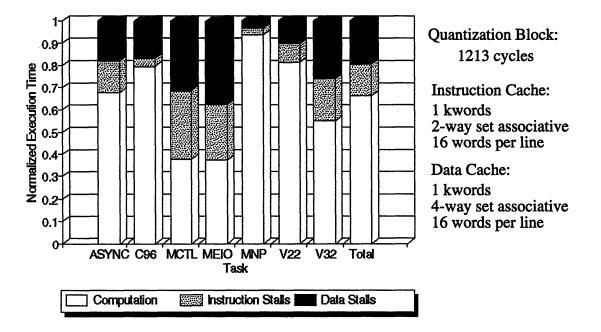

| Figure 7.4: Utilized MIPS in Simulation of MIDI Tasks on a 50 MIPS DSP      | 108 |

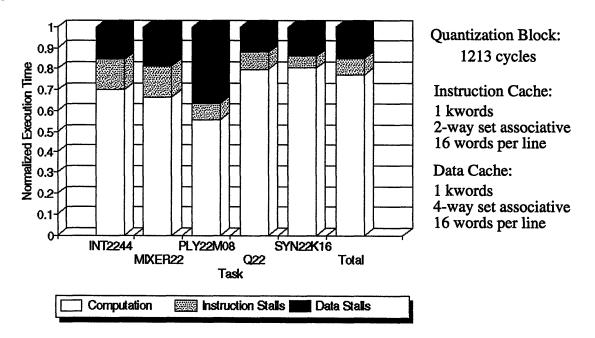

| Figure 7.5: Normalized Results of MIDI Synthesizer Simulation               | 109 |

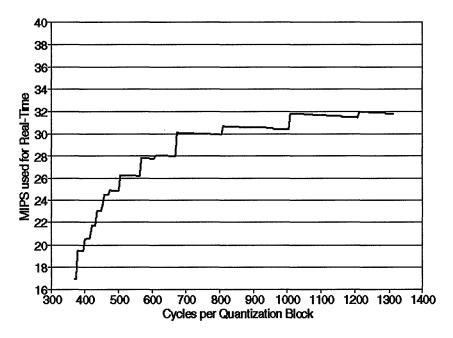

| Figure 7.6: Utilized MIPS in Simulation of Modem Tasks on a 50 MIPS DSP     | 110 |

| Figure 7.7: Normalized Results of 14,400 Baud Modem Simulation              | 111 |

|                                                                             |     |

# **List of Tables**

| Table 6.1: Quantization Block Size for Various Cache Configurations        | 72  |

|----------------------------------------------------------------------------|-----|

| Table 6.2: Cache Actions For DSP Half Cycles                               | 81  |

| Table 7.1: Transfer Time for a 1 kword Cache                               | 93  |

| Table 7.2: Quantization Block Size for Caches with 32 Words per Cache Line | 94  |

| Table 7.3: Partial Output from Instruction Cache Simulation of a MIDI Task | 100 |

| Table 7.4: Comparison of Several 1 kword 4-Way Set Associative Data Caches | 102 |

| Table 7.5: MIDI Synthesizer Tasks                                          | 106 |

| Table 7.6: 14,400 Baud Modem Tasks                                         | 107 |

|                                                                            |     |

# **Chapter 1**

# Introduction

## **1.1 Real-Time Computer Systems**

Traditionally, most real-time computer systems have been used for process control. In order for a process control system to function correctly, it must be able to react to external events before a given deadline, as well as perform other specific tasks periodically. These control systems must be predictable, in order to guarantee that all of the necessary functions will be performed. In many process control systems, a system failure can be disastrous, causing the loss of equipment, or maybe even lives. As safety is a major concern, the cost of a process control system is typically less important than guaranteeing that the system will function properly and tasks will be performed predictably. If the control system does not deliver enough performance, then the expense of obtaining a bigger and faster system can easily be tolerated.

The emergence of multimedia computer systems has led to the design of real-time digital signal processor (DSP) systems that are much more versatile than real-time process control systems. These systems are used to perform a wide variety of functions, which will change as the user requires different multimedia functionality. Also, the cost of a multimedia computer system is important, as competitive fixed function solutions exist that do not use real-time DSPs. There is also certainly no expensive equipment or lives in jeopardy if a multimedia system fails, so much more importance is placed on performance than fault tolerance.

Process control systems generally run a fixed set of tasks, as the entire system is designed specifically to perform one function, whereas in a multimedia system, it is not always clear exactly what tasks will be run. The DSP may be used to perform many different functions, and perhaps even some that were not anticipated when the system was originally designed. This difference further separates process control systems from multimedia DSP systems:

> In a typical real-time system, you have awareness of the tasks the system must perform, how often the tasks must run, and the required completion times of the tasks. When designing the system, you use a method that meets the needs of the system. In many cases, a simple round-robin scheduler is enough. At other times, you select multiple priority levels and use a preemptive scheduler.

> In the Windows/DSP [multimedia] case, on the other hand, you don't have this awareness. You can't predict which tasks the DSP will run and what the required priorities will be. For example, the DSP may be providing just a single function, such as a modem, or several simultaneous functions, such as a modem, compression, fax, and text to speech. You cannot predetermine the mix. [19]

A multimedia real-time system is much more versatile and cost constrained than a process control system. Users demand high performance, and are not willing to pay a premium for safety and customized software and hardware development as system requirements change.

### **1.2 Research Goals**

Most real-time system memory architectures do not include caching. Either memory that is as fast as the processor is used, or the cost of using slower memory to the system is determined and accounted for, so as not to sacrifice the system's predictability. However, there are some exceptions, but no caching system exists that allows for general purpose real-time computing without using software control, and placing extreme restrictions on the system. The introduction of a cache into a real-time system goes against the requirement that real-time systems must be predictable, as a cache, by its very nature, is unpredictable. Since cost is not an issue, process control systems do not need to make use of a cache to increase system performance while keeping costs low, but the advantages to a multimedia system in terms of cost and performance are enormous.

This is not to say that a process control system would not benefit from cheaper, slower memory in terms of cost, and a cache in terms of performance. Rather, the domain of multimedia computing is the driving force for this research, as cost and performance are much more important in that realm. Consumers are not as willing to pay large premiums for better multimedia performance as industry is for the required process control performance.

The primary goal of this research was to design a memory system, using memory that is slower than the processor's cycle time, for use in real-time systems that use priority driven preemptive scheduling. In order to be useful, the memory system must perform better than the trivial solution of just accounting for the slow memory's overhead in real-time resource allocation. Obviously, using slower memory will incur some sort of penalty, and this research is directed at minimizing that penalty. Furthermore, the details of the memory system should not alter the way software is run. The same software should be able to run on a system that uses fast memory that never stalls the processor, as well as on a system with slower memory and a cache. Automated tools may analyze the software to determine its behavior on either system, however, in order to ensure that the software will always be predictable.

### **1.3 Organization**

Chapter 2 is an overview of real-time systems. The primary constraints of real-time systems are discussed, as well as some of the different methods that can be used to schedule

real-time programs in order to guarantee predictability. In addition, the difficulties of realtime caching are presented, along with a brief description of one existing real-time caching system design. This chapter presents the background that is needed to understand the requirements of a real-time caching system, and why it is difficult to make such a system effective.

Chapter 3 is a description of real-time systems as they affect the memory system. The characteristics of the particular system that was used as a model for the research is described. The major parameters that are allowed in the design of a real-time memory system are then explained, and their impact on the memory system is given. These parameters were used throughout the research to guide the design of a useful memory system.

Chapter 4 explains the importance of high memory bandwidth, and presents several methods of increasing memory bandwidth. The available bandwidth between the memory and the cache significantly affects the overall system performance, and sets a bound on the available real-time resources. In all caching systems, data must be transferred between the main memory and the cache, and the faster this can be done, the better the system's performance will be.

Chapter 5 presents a memory system design for a system in which there are no preemptions. This is quite similar to another existing real-time caching method, and is mainly used here as a precursor to execution quantization, which is presented in the succeeding chapter. Even though this kind of a system is of limited use, it is important to understand how it works, as some of the ideas used in the design are quite useful if they are expanded properly.

Chapter 6 presents execution quantization. Execution quantization is an extension to existing scheduling algorithms and a cache design that allows priority driven preemptive scheduling in a real-time caching environment. The fundamental idea of execution quanti-

zation is that cache restoration can successfully negate the adverse effects that context switches have on cache contents, if it can be done in a controlled manner. By allocating execution time to tasks in fixed sized blocks, preemptions can be controlled, and cache restoration can be done efficiently.

Chapter 7 extends the idea of execution quantization to ensure predictability in almost all real-time systems. By not only allowing cache restoration to occur predictably and efficiently, but also allowing cache contents to be dynamic, with a predictable method of calculating the worst case execution times of tasks, execution quantization becomes a predictable and versatile method of real-time cache management. Several examples are given to show the usefulness of execution quantization, and how it can be applied to a real system.

Chapter 8 presents the conclusions of the research and its applicability to a wide range of real-time systems. Several directions for future research are also suggested to explore real-time caching further.

# **Chapter 2**

# **Real-Time Systems**

## 2.1 Designing for Determinism

Real-time systems are unique in that they require deterministic execution. This precludes most real-time system architectures from taking advantage of nondeterministic components such as a cache. Without a cache, the use of slow memory, like dynamic random access memory (DRAM), significantly decreases the amount of processing power that can be devoted to real-time tasks. The use of static random access memory (SRAM) in the memory system allows increased processor utilization, but is clearly undesirable for cost reasons. Despite this, the IBM Mwave<sup>†</sup> DSPs do in fact use SRAM.

Halang and Stoyenko point out that,

The thinking in probabilistic or statistical terms, which is common in computer science with respect to questions of performance evaluation, is as inappropriate in the real time domain as is the notion of fairness for the handling of competing requests or the minimisation of average reaction times as an optimality criterion of system design. Instead, worst cases, deadlines, maximum run-times, and maximum delays need to be considered. For the realisation of predictable and dependable real time systems, reasoning in static terms and the acceptance of physical constraints is a must all dynamic and "virtual" features are *considered harmful*. [7]

They further advocate that features such as "... caching, paging and swapping must either be disallowed or restricted." [7] These arguments do not necessarily rule out the use of DRAM and other high latency memories entirely. However, in their view, attempts at reducing the memory latency, for the purposes of determining worst case execution times,

<sup>†</sup> Mwave is a trademark of International Business Machines Corporation.

are potentially harmful, and do not allow a systematic improvement in performance. This leads to decreased processor utilization for real-time tasks that is unacceptable in the Mwave system, which employs a pipelined RISC architecture that suffers heavily from slow memory access times. However, it is important to remember that in real-time systems, achieving deterministic behavior is far more important than the speed of execution. [6]

**2.1.1 Execution Frames**

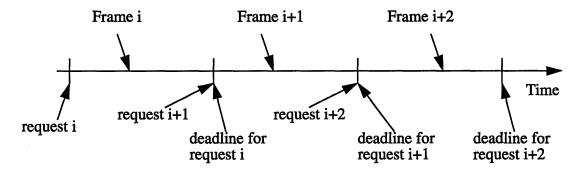

Figure 2.1: A Periodic Execution Frame

In a real-time system, each real-time task executes in an execution frame, which is a fixed length period of time. A frame starts when there is a request for service by a task and ends at the deadline by which execution must be completed. In general, there can be both periodic and aperiodic execution frames in a real-time system. A periodic execution frame is one which has a periodic request time, and typically the deadline for each request is the time at which the next request occurs, as shown in Figure 2.1. An aperiodic execution frame is one in which the requests for service come from an external aperiodic source and the deadline is defined to be a set amount of time after the request, regardless of when the request is made. The IBM Mwave system only allows tasks that run in periodic execution frames, and those frames are defined as a multiple of some periodic interrupt source. For instance, if a frame is given as 4 interrupts from an 8 kHz interrupt source, then there are 2000 frames per second, each lasting half a millisecond. A task must execute once in each

frame. This means that a task running in this particular frame has a hard deadline (one that cannot be missed) every half a millisecond. The frame rate is defined as the frequency of the execution frame, which in the above example is 2 kHz.

Each task must further provide its worst case instruction count. This is the maximum possible number of instructions that the task could ever execute in any one frame. Since the Mwave DSP has a pipeline that results in a throughput of one instruction per cycle, the worst case instruction count uniquely determines the worst case execution time of a task. A metric that is used to gauge how much of the processor's computation time must be devoted to a task is the number of millions of instructions per second (MIPS) needed for the task. Using the execution frame's frequency and the worst case execution time, the necessary MIPS for a task can easily be computed. [17]

#### **2.1.2 Scheduling Real-Time Tasks**

Scheduling real-time tasks is an extremely important part of any real-time system. If tasks are scheduled improperly, then tasks will miss deadlines, which can be catastrophic. If any task exceeds its worst case instruction count in the Mwave system, which could cause tasks to miss deadlines, then the whole system stops and signals an error. This prevents transient overloads and allows detection of the offending task, thereby discouraging programmers from falsely declaring worst case execution times. The two predominant scheduling algorithms for real-time systems that guarantee that all tasks will meet their deadlines are dynamic deadline scheduling (DDS) and rate monotonic scheduling (RMS). Both scheduling algorithms require that the worst case execution time of all tasks are known before they are scheduled. Otherwise, deterministic scheduling cannot be achieved.

As suggested by the name, DDS is a dynamic scheduling algorithm, meaning that task priorities are assigned dynamically. It can be shown that if any given task set can be suc-

cessfully scheduled on a processor, then DDS can also schedule that task set successfully. In this context, success denotes that all tasks will always meet their deadlines. DDS uses the proximity of a task's deadline as that task's priority, with higher priority given to tasks with closer deadlines. At any of the periodic interrupts, the scheduler schedules the task with the highest priority. It can be shown that theoretically DDS allows one hundred percent of the processor to be utilized. In practice, the actual processor utilization must be less than one hundred percent, because the scheduler uses some of the processor's time, and task switching takes some time as well. [10] [16] [20]

RMS is a static scheduling algorithm. RMS is an optimal scheduling algorithm in the sense that it can be shown that if any given task set can be successfully scheduled with a static algorithm, then that task set can also be successfully scheduled by RMS. RMS uses the frequency of execution of a task as that task's priority, with higher priority given to tasks with higher frequency frame rates. To construct the schedule, the highest priority task is scheduled first, and then the next highest priority task and so on until all tasks have been scheduled. Theoretically, the maximum possible utilization for a task set can be as low as sixty nine percent using RMS. In practice, however, usually much more than sixty nine percent of the processor can be utilized, and it is shown, using stochastic analysis, in [15] that the average scheduling bound for RMS is around eighty eight percent. As in DDS, however, the overhead of the scheduler and task switching must be taken into account. [16]

Task preemption is a significant event in a real-time system. When a task is preempted it is not allowed to complete its execution in the current frame. A preemption occurs when a task with a higher priority than the currently running task requests service. At that point there is a context switch and the higher priority task begins execution. When using DDS, preemptions are unpredictable and can occur at any time. In RMS, all preemptions are known ahead of time, since task priorities are fixed. The IBM Mwave system currently uses DDS to schedule real-time tasks because it allows higher processor utilization.

#### 2.1.3 Memory Systems

Real-time memory systems must also be deterministic. Memory latency must be predictable and repeatable. It is not beneficial to a real-time system for the memory system to have variable latencies depending on uncontrollable factors, which means that nondeterministic methods of decreasing memory latency are not useful. Caching serves to decrease the total time waiting for memory, but it does not ease the burden of the real-time environment, as the system must be prepared for everything to miss in the cache, as it well might for isolated sections of code. A cache monopolizes on significantly improving average case performance, whereas in a real-time system the only metric is worst case performance.

Currently, the IBM Mwave DSP uses SRAM in its memory system. The memory can be accessed in a single cycle so that the pipeline never stalls due to memory latency. This makes all execution times easily predictable from the worst case instruction count. The introduction of DRAM into the system causes problems. DRAM takes multiple cycles to access, so that the pipeline will stall on every memory access. Since the DSP must fetch the next instruction every cycle, this means that the pipeline will be stalled for every instruction. If there is a data memory access, it can go on concurrently with the instruction access because the Mwave system uses a Harvard architecture. This means that the worst case execution time of a task is still deterministically based on the worst case instruction count. However, if the DRAM takes four cycles to access, for example, then seventy five percent of the time, the processor will be stalled waiting for the memory system to return the data. The addition of a conventional cache would only lead to nondeterministic behavior, and is therefore not useful for decreasing worst case execution times.

Another minor issue is DRAM refresh. In a real-time system, the system cannot afford to have to wait while refresh occurs at unpredictable times. Therefore, the simplest and most effective solution is to have the operating system schedule a real-time task that refreshes the DRAM. That way, the refreshes will take place periodically, as they need to be, and they will only occur during the refresh task's execution so as not to interfere with other tasks.

### **2.2 The Frame Manager**

Each real-time task must specify an execution frame in which it is going to run. In the Mwave system, a corresponding frame manager exists for each such execution frame that is being used in the system. There is only one frame manager for each execution frame being used in the system, so all tasks that use the same execution frame are assigned to the same frame manager.

#### 2.2.1 Scheduling Tasks

The Mwave system makes use of these frame managers to schedule the real-time tasks using DDS. Each frame manager is responsible for scheduling the tasks in its frame. Since all of the tasks in any given frame manager have the same deadline, and therefore the same priority, they cannot preempt each other. Effectively, this means that once a frame manager is allowed to run on the DSP, it just runs through the list of tasks it is responsible for, and schedules the next one in the list until there are no tasks left. The frame manager then becomes idle until its next frame begins.

However, frame managers can preempt other frame managers, as each frame manager has a different priority based on its current deadline. A frame manager becomes active when its corresponding frame begins. At that point, if there is a lower priority frame manager, one with a later deadline, executing tasks on the machine then the newly activated frame manager will preempt the processor and begin executing its tasks. If the newly activated frame manager does not preempt another frame manager at the start of its frame, it must wait until all active frame managers with closer deadlines have run to completion before it will be allowed to run. Since the newly activated frame manager is now waiting to be run, a frame manager with a later deadline will not be allowed to run on the machine before the newly activated frame manager completes its execution. Since a lower priority frame manager will not be able to run, there is no chance for the newly activated frame manger to preempt the processor after the start of its corresponding frame. Therefore, the start of a frame is the only time at which a frame manager can preempt another frame manager.

#### **2.2.2 Interaction Among Frame Managers**

There are two important theorems that can be shown about the scheduling of frame managers using DDS. Both theorems deal with the order in which frame managers can run on the machine.

**Theorem 2.1:** In order for a frame manager to preempt another frame manager, the preempting frame manger must have a higher frequency frame rate than the preempted frame manager.

**Proof:** The nature of DDS is such that the highest priority task is always the task that is currently running. Priority is determined by the proximity of deadlines, so therefore the currently running task must have the closest deadline in the system. This means that all tasks with closer deadlines have already completed in their current frame. This is true in a theoretical DDS algorithm, but it is also true in the Mwave system. In the Mwave system, scheduling decisions are made at every interrupt and whenever a task completes execution. As previously stated, a preemption can only occur at the start of a frame. Also, frame boundaries always correspond to one of the periodic interrupts, as they are defined in relation to one of those interrupt sources. Since the only way that a task switch can occur is by

preemption or when a task completes, the Mwave DDS algorithm always schedules the same tasks that would be scheduled in the theoretical algorithm, as the scheduler is active in both of those situations.

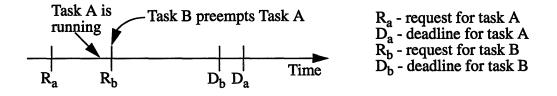

Figure 2.2: A Preemption by a Task with a Faster Frame Rate

Given that the currently running task must have the closest deadline in the system, it must belong to the frame manager that controls the frame with the closest deadline in the system. The only way that the currently running frame manager can be preempted is if another frame begins, since preemption only occurs on frame boundaries. It is also necessary that the preempting frame manager has a closer deadline than the current frame manager. Since the preempting frame manager controls a frame that begins after the current frame manager's frame and ends before it, this frame has a shorter period, and therefore must have a higher frequency. This can be seen in Figure 2.2. Task A is running prior to  $R_b$ , because it is the task that has the closest deadline on the machine that has not completed its execution in its current frame. At time  $R_b$ , task B becomes the highest priority task as  $D_b$  is sooner than  $D_a$ , and task B preempts task A. If  $D_b$  were after  $D_a$ , then task B would have lower priority, and no preemption would occur, which shows that the deadline of the preempting task must be sooner than the deadline of the task that is being preempted.

Some important consequences of Theorem 2.1 include the fact that the frame manager with the highest frequency can never be preempted, and the frame manager with the lowest frequency can never preempt another frame manager. This can be helpful in understanding certain aspects of real-time scheduling.

**Theorem 2.2:** Preempted frame managers resume execution on the processor in a last-in first-out order.

**Proof:** If a frame manager is preempted, it must be because another frame manager has a closer deadline. Therefore, the preempted frame manager cannot run on the DSP until the preempting frame manager completes its execution because the preempting frame manager has a higher priority. Also, any frame managers that are allowed to run between the time that a frame manager is preempted and resumed, must have a closer deadline than the preempted frame manager. Therefore, all of those frame managers must also complete execution, whether they are preempted themselves or not, before the preempted frame manager can be allowed to resume execution.

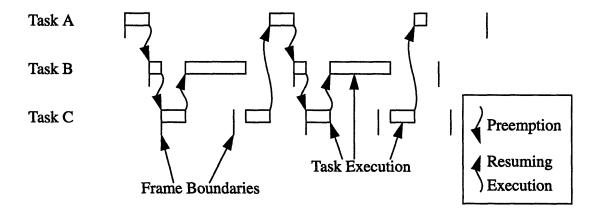

Figure 2.3: Preemptions in Dynamic Deadline Scheduling

Figure 2.3 illustrates how tasks are preempted and resumed. In the figure, downward crooked arrows represent preemptions and upward crooked arrows represent a preempted task resuming execution. Context switches that result from a task completing execution and a new task starting execution are not marked. From the figure, it can easily be seen that once a task is preempted, it does not resume execution until the preempting task completes execution. Furthermore, if other tasks commence execution before the preempted

task resumes, then those tasks will also complete their execution before the preempted task is resumed.

Thus, any preempted frame manager is effectively put on a LIFO stack and cannot resume execution until such time as it is on the top of the stack. This is true because all frame managers below a given frame manager on the conceptual LIFO stack must have later deadlines than the given frame manager, as it was allowed to run on the machine more recently than they were.

| Time |  |  |

|------|--|--|

|------|--|--|

| Preempted Tasks: A B A A A B A A Stac<br>A A A | $ \begin{array}{ccccc} A & B & C & B & C & A \\ & A & B & A & A \\ & & A \end{array} \right] $ Stack |

|------------------------------------------------|------------------------------------------------------------------------------------------------------|

|------------------------------------------------|------------------------------------------------------------------------------------------------------|

#### Figure 2.4: Conceptual LIFO Stack for the Schedule in Figure 2.3

Figure 2.4 shows the contents of the conceptual LIFO stack for the schedule in Figure 2.3. The stack is shown each time it changes, so the first entry just has task A running on the machine. Then, when task B preempts task A, task B is at the top of the stack, which corresponds to running on the machine, and task A is pushed down on the stack. This continues for the rest of the schedule that is shown in the figure. From Figure 2.4, it is very easy to see that tasks never reorder themselves on the stack. Once a task takes a position on the stack, it can only be pushed further down on the stack as new tasks with higher priorities execute on the machine, or be raised on the stack as tasks complete execution. Either way, the task always maintains its relative position on the stack.

The most important consequence of Theorem 2.2 is that there is a predefined order in which preempted frame managers resume execution. There may be other frame managers that run in between them, and frame managers could be preempted and resumed multiple times, but preempted frame managers will always leave the stack to resume execution in a last-in first-out order.

## 2.3 Caching

Conventional caches are driven by program memory accesses. This means that the data in the cache at any given time is completely dependant on the history of the current execution of a given process. This is assuming a non-multitasking system, so that processes do not interfere with each other in the cache. Once multitasking is allowed, however, it is impossible to predict what is contained in the cache.

The problem with multitasking is that preemptions are allowed, so different processes can overwrite each other's cache lines, thereby making the contents of the cache dependant on the history of the execution of all the processes on the system, as well as the order in which they were scheduled. Essentially this means that it cannot be predicted whether any given memory access will hit or miss in the cache. This is an unacceptable situation in real-time systems. A conventional caching scheme would only be useful if it were possible to predict exactly which memory accesses would hit in the cache and which ones would miss. Then the execution time of a task could accurately be predicted.

#### 2.3.1 Real-Time Caching

Either protection or restoration can be used to prevent interference amongst tasks in the cache. This would allow each task to behave as if it exclusively owned the entire cache. To protect data, each task's data must be preserved across preemptions. This can be done by allowing cache lines to be locked in place so that they cannot be evicted. A unique cache management scheme would have to be developed in order to handle locked cache lines properly. Also, provisions would have to be made for the possibility that the entire cache could be locked, rendering the cache essentially useless if there is data that needs to be accessed which is not already in the cache.

In a restoration scheme, each task would be allowed to use the entire cache, and then when a context switch occurs, the cache would be copied to memory and the cache image of the new task would be copied back into the cache. Restoration must occur before a task is allowed to execute on the machine. To restore data before execution without stalling the processor, the next task to run must be predicted. Using DDS, this can be quite difficult, if not impossible. If RMS were used, the next task to run could be easily determined by checking the schedule, which is completely predictable, as all frame managers have static priority. Another option is to delay a task's execution until the task's data can be completely loaded. This involves tampering with the real-time scheduling algorithm which could cause tasks to miss their deadlines unless extreme care is taken.

One of the best solutions to the real-time caching problem so far is the Strategic Memory Allocation for Real-Time (SMART) Cache. The SMART cache was developed for use in real-time systems that use RMS, however the SMART cache should work in systems using any preemptive scheduling algorithm. A system using the SMART cache can achieve processor utilization within ten percent of a system using a normal cache, and the SMART cache is deterministic. The SMART caching scheme uses protection to prevent task interference by dividing the cache into partitions. These partitions are then allocated among the tasks that are to be run on the processor. One larger partition is reserved as the shared pool, and acts as a normal cache. The shared pool allows shared memory to be cached without complicated cache coherence schemes. The shared pool can also be used to cache tasks when there are no available private partitions left. [12]

The allocation of partitions is static, since if it were dynamic some tasks could miss their deadlines while the cache was being reallocated. This means that the task mix to be run on the processor must be known ahead of time, so that a static analysis can be made to determine which tasks can use which partitions. Partitions can be reallocated dynamically, but it is time consuming. In his thesis, Kirk estimates the time to reallocate the partitions for a sample task mix running on a 25 MHz RISC processor to be around 0.15 seconds. [13] In that amount of time, almost every task will miss at least one deadline. However, the allocation scheme is quite clever in that it allocates partitions in such a manner that the utility of each cache partition is maximized. Unfortunately, to accomplish this it is necessary to have detailed information about each task's hit and miss rates given an arbitrary sized private cache. Once the partitions are allocated, the tasks own their partitions. Essentially, this means that only the task to which a partition is allocated can use that partition, so that data is preserved across preemptions. [14]

As well as the fact that a static task mix is preferable, another major drawback to the SMART cache is that it requires additional instructions in the instruction set to control which partitions are being accessed, either the private ones or the shared pool. This requires that the programmer or the compiler know too much about the actual hardware implementation, which may change. This is not desirable in the Mwave system, as software must be able to run on all Mwave systems, not just those that have DRAM in the memory system.

Using either a protection or a restoration scheme eliminates the problem of conflict between tasks, but does not eliminate the difficulty in timing individual tasks.

#### 2.3.2 Task Timing

The process of determining the worst case execution time of a task is called timing. In the current Mwave system, which uses SRAM so that there are no pipeline stalls due to memory accesses, all instructions take one cycle to complete because of the pipeline. In this system, timing tasks is reduced to finding the longest possible execution path through the code. With the introduction of DRAM and caching, timing becomes much more complicated. Now the longest execution path through the code might take less time than a shorter path that has significantly more cache misses.

Timing in this new situation requires keeping track of the state of the cache at all times, so that it is possible to determine if a given memory access will hit or miss in the cache. If the state of the cache is always known, then any execution path can be timed by simply adding the miss penalty for each cache miss to the time that it would have taken to execute the given execution path if there were no cache misses. This is in agreement with the assumption made by Halang and Stoyenko:

> The fundamental assumption we make is that only software and hardware that can be checked (i.e. analysed for schedulability) for adherence to the constraints *before the application is run* fit the requirements of predictable real time applications. [7]

Since it is not always possible to determine the address of a given memory access before run time, it becomes a very difficult problem to incorporate a cache into a real-time system and still be able to time all of the tasks. However, in order to adhere to the above assumption, a method must be devised to allow task timing prior to run time, or the use of a cache in a real time system may be impossible. A likely solution is to use a pessimistic algorithm in which unpredictable memory accesses are assumed to miss in the cache. That will provide an upper bound on execution time, but the pessimistic bound may not be tight enough to allow sufficient processor utilization.

#### 2.3.3 Task Size

One way to eliminate the timing problem is to make the cache large enough so that an entire task can fit into the cache, or a partition of the cache if partitioning is being used. Similarly, a restriction could be placed on task size to limit the tasks so that they fit in the cache. This is undesirable because cache sizes may be different on different processor implementations. However, if this is done, and a cache replacement scheme is used that does not allow data to be displaced from the cache, or optimally, the entire task is preloaded, then the task can simply be timed by noting that in the worst case, the task will miss in the cache exactly once for each memory location.

# **Chapter 3**

# **Designing a Real-Time Cache**

### **3.1 Characteristics of the Target System**

The specific system at which this research is targeted is the IBM Mwave digital signal processor for multimedia use. However, the results can be applied to other DSP systems and largely to real-time systems in general. Some of the important characteristics of the target system include having a flexible task set that can be changed dynamically by the user as the system is running, allowing the introduction of newly written software without redesigning the system, not requiring software to be aware of the hardware in the system, and allowing the system to use dynamic deadline scheduling.

The most important characteristic of the target system is that it is able to run arbitrary task sets. The user should be able to run whatever task set he wants, which may even include tasks he wrote himself. This is an important distinction, as many real-time systems only run fixed task sets, or dynamic subsets of a larger fixed set. By allowing arbitrary task sets, the memory system can be used in *all* real-time systems, specifically including DSPs for use in multimedia computer systems. Adding a cache, or other enhancement to allow the use of slow memory, should not prohibit the use of arbitrary task sets, if the system can otherwise do so.

Furthermore, users should be able to add and remove tasks from the task set while the system is running without disrupting *any* of the active tasks. This is important in a multimedia DSP system, as users do not want the music they are playing to be disrupted when they start up their fax or modem application, for example. Once again, adding a cache cannot enable the system to change the task set dynamically, but if the system can otherwise handle this, then the addition of a cache should not inhibit this ability. Another important restriction is that modifying the memory system should not prevent existing software from being used on the system. The introduction of a cache should not force all existing real-time tasks to be rewritten, but knowledge of how the caching system works may make it desirable to rewrite existing software for performance gains.

Using a cache should not preclude the use of dynamic deadline scheduling. Using DDS is desirable for the increased real-time utilization that it allows, as well as the simplicity of the scheduling feasibility checks. Also, if possible, it is desirable to allow as many tasks to run on the system as computation and memory resources allow using the given scheduling algorithm. Adding a cache should keep further restrictions placed on the task set to a minimum.

Most importantly, the addition of a cache should not lead to nondeterministic behavior, as discussed in Section 2.3 on page 27. If the addition of a cache makes the system nondeterministic, then the system may not function properly. Typically, in order to achieve deterministic behavior, real-time caching systems ignore the nondeterministic behavior associated with caches and assume that in the worst case all memory accesses will miss in the cache. By introducing a deterministic cache, this worst case performance can be significantly improved.

The target system described here is a little more flexible than many real-time systems. The fact that the DSP can be used by a wide variety of users to perform various multimedia functions makes the problem of adding a cache more difficult than in a controlled realtime system where the software and hardware are developed together, usually for one specific purpose. Therefore, a solution that works on this general target system should be easily adaptable to many real-time systems, including those with more specific purposes.

## **3.2 Design Parameters**

There are many factors that influence the design of a real-time caching system. However, five of these factors are more significant than the rest:

- the bandwidth between the memory and the cache,

- the number of frame managers allowed on the system,

- the use of shared memory,

- the size of typical tasks in relation to the size of the cache, and

- the method used to determine the time each task requires to run.

The bandwidth between the memory and the cache is the most significant factor in determining how fast cache pages can be swapped in and out. The number of frame managers running on the system can also have a significant impact on determining how to contain preemptions. The final three design parameters are dependent on the choice of the allowable number of frame managers, so they will be explored as they affect the design once that decision has been made. Whether or not shared memory is allowed can have an influence on the cache design if it is possible for the same address to be cached in more than one cache partition. Finally, the overall size of each task, and how each task will be timed are important in determining the usefulness of any real-time caching system.

#### **3.2.1 Memory to Cache Bandwidth**

Obviously, the higher the bandwidth, the less penalty there will be for using DRAM. A system that uses large cache blocks that are swapped in and out infrequently, rather than smaller cache blocks that are swapped quite frequently, is desirable, as sequential access offers the possibility for higher bandwidth.

If the bandwidth is sufficiently high, it may be possible to use a cache restoration scheme in which the cache is restored at context switch time by the operating system without much additional overhead. If the bandwidth is too low for this to occur, then the operating system will probably have to take more of the processor's resources to manage the cache in some less transparent manner. The bandwidth also affects the way that individual tasks and frame managers will manage their cache space. Higher available bandwidth gives more flexibility in cache management, and allows frequent changes in the data in the cache. Memory that has lower available bandwidth requires that more attention be paid to carefully organizing data changes in the cache, and opens the opportunity for pipelining the stages of moving data into the cache, executing the task, and writing data back out to memory.

#### **3.2.2 Number of Frame Managers**

The number of frame managers that are allowed on the system has a significant affect on the system design. There are essentially two cases. The first case is that only one frame manager can be running on the system. The second case is that an arbitrary number of frame managers can be running on the system simultaneously.

Handling the single frame manager case is obviously much easier than handling an unknown number of frame managers. If there is only one frame manager, then that frame manager completely owns the entire cache. Since only frame managers can preempt each other, there will be no preemptions. The problem is reduced to the problem of scheduling the cache for the tasks contained within the single frame manager. Since the tasks within any frame manager are always executed in a predetermined, sequential order, the problem is relatively straightforward, as much of the work can be done prior to run time. An extension of the single frame manager case is the case in which there are only a small bounded number of frame managers allowed to run concurrently. In that case, there can be an independent cache, or more likely an independent cache partition, dedicated to each frame manager, so that all of the frame managers on the machine act as if they were operating in the single frame manager case. In this way, preemptions simply reduce to changing which cache, or cache partition, is connected to the processor.

The case in which the number of active frame managers is unpredictable is much more difficult. In this case, frame managers can preempt each other, and it is not guaranteed that there will be enough cache space to support all of the running frame managers. This leads to contention for cache space among the frame managers. The key to this situation is to make each frame manager think that it is running in the single frame manager case. This is likely to require cache partitioning and a nontrivial cache management scheme.

### **3.2.3 Shared Memory**

If shared memory is allowed, cache coherence can become an issue. In any real-time caching system, each task will have its own cache image. If these images are separate caches or partitions, rather than sharing a single cache amongst all the tasks, then cache coherency must be maintained. Without shared memory, each frame manager can schedule its tasks and associated cache space without regard for other frame managers. However, once shared memory is allowed, there must be some method to prevent tasks from accessing stale data or updating data out of order. This is similar to the situation in multiprocessing systems where methods such as snoopy caching are used. [9]

There are many options to maintain cache coherence. One method is to require all shared data to be cached in a special shared partition which can be accessed by all tasks. This, however, brings about new problems of its own, as all shared data on the machine must be able to fit into this shared partition, and if it is not large enough, then cache scheduling problems will arise. Another option is to restrict shared data to reside in the cache in only one place at a time. That way, only the task that is currently using the data can have it in its cache space. Then when another task accesses that shared data, it will invalidate the existing copy and bring in its own copy. Once again, this will create timing problems, as it will almost never be possible to determine if shared data is resident in a particular frame manager's cache space in the face of preemptions.

### **3.2.4 Size of Tasks**

The maximum size of tasks is an important factor to consider in the design. Each frame manager must be able to function correctly given a finite sized cache or cache partition. If all the tasks can fit entirely into this cache space, then there is no problem as long as a task's data is loaded before it is needed and written back to memory once the task has completed execution. However, once the task becomes too large to fit into the available cache space, the problem becomes significantly more difficult.

When a task is too large to fit entirely in the cache, it becomes important to decide what data should be in the cache at what time. This is quite a significant problem when it is coupled with the fact that the task's execution must be deterministic. There must be a method of determining the maximum number of cache lines that will be swapped in and out by the task before the task is run. That would allow the cache overhead to be included in the determination of the task's worst case execution time.

### **3.2.5 Task Timing**

Task timing becomes necessary whenever there is a situation in which it is unclear whether or not a task's data will be resident in the cache. This encompasses just about all situations when DRAM and caching are components of the memory system. However, this is not a problem, as timing tasks is quite possible. Halang and Stoyenko present one such method, which they call a "schedulability analyser," in [7]. This method is part of the compiler, so it is completely automated, and is easily generalizable to any high level language that meets certain constraints, which they enumerate, that are necessary for use in a real-time system. The following is a brief description of such a method.

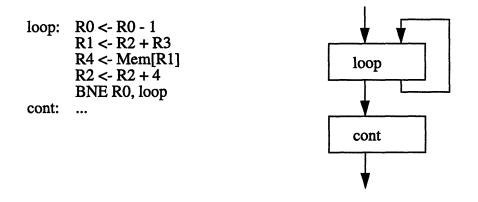

The heart of any task timing tool will involve constructing a weighted directed graph from the task's code. In the graph, the nodes represent straight line sections of code such that if the first instruction in the section is executed, then all of the instructions in the section will be executed sequentially. The edges represent possible control flow paths. In other words, each node will have edges leaving it to all of the possible other nodes to which the program could branch. An example is given in Figure 3.1, which shows how a simple program fragment can be turned into a program graph.

Sample Code Fragment

Associated Program Graph

Figure 3.1: A Code Fragment and its Associated Graph Representation.

Once this graph is constructed, the backward edges must be removed. In order for a task to be bounded in time, which is a necessary condition for any real-time task which must have an inviolable worst case execution time, all backward branches must have an upper bound on the number of times they can be taken. If a backward branch can be taken n times, then the graph can be unrolled to produce n copies of the loop. The last thing to do is to assign the edge weights. The weight of any given edge is the time it will take to execute the code represented by the node to which the edge points. This must take into account cache contents and reload times. Once this is completed, it is a simple matter to find the longest path through the graph, and there are many algorithms in existence that do exactly that. A few algorithms that find the shortest path in a weighted directed graph are given in [2]. They can easily be modified to find the longest path of the graph instead by changing the inequalities and making other minor modifications.

Timing tasks, therefore, while not a simple proposition, is entirely possible. The fact that all code used in the Mwave system is written in assembly language makes it a little more difficult to time. The branch targets and loop bounds are not always clearly defined in such a way that they could automatically be extracted from the code. This would require an interactive timing tool that requests input from the programmers, which, while not as elegant as the automatic tool of Halang and Stoyenko, is still possible.

# **Chapter 4**

# **Memory Bandwidth**

## **4.1 Cache Performance**

In any system that makes use of a cache, the memory latency of the slower memory limits the achievable processor utilization. If there is a cache miss, then the processor *must* wait until the slower memory returns the required data. Obviously, the faster the data can be transferred, the less time will be spent waiting on a cache miss. In a real-time caching system, as in other systems, it is important for cache misses not to degrade the system performance severely. The best way to decrease the penalty of a slow memory access is to group large blocks of sequential accesses together, as the additional overhead is significantly less than that for isolated accesses. This serves to reduce the average access times for all of the data within the block.

However, reducing the average memory access time by transferring large blocks of data does not necessarily decrease the cache miss penalty. In fact, it probably increases the cache miss penalty, as the processor may have to wait for the entire transfer to complete, depending on where the required data is located in the block and the cache miss protocol. Although, if the rest of the data in the block is accessed by the processor later, then the overall system performance will improve. There is a trade-off between the average access time and the largest useful data block. The optimal block size must be determined by the locality of reference in the system. If the block size is too large, then too much time will be spent transferring unneeded data. If the block size is too small, then the miss rate will be too high. This problem is not unique to real-time systems, rather it is fundamental to good cache design.

The following is an overview of many techniques that can be used to increase memory bandwidth, which can directly increase processor utilization, as time spent waiting for data is minimized.

## **4.2 Decreasing Memory Latency**

There are many ways to decrease the memory latency of DRAM. The problem is that none of the methods are deterministic. Almost all of the current research in the area of reducing memory latency is targeted at reducing the average case memory latency. Unfortunately, this is not effective for real-time systems, as the worst case memory latency must be reduced. However, by controlling the way the cache accesses the memory system, it may be possible to use some of these methods deterministically.

The use of static-column, or page mode, DRAM can help improve system performance. When data is accessed from static-column DRAM, the entire column that is being accessed is buffered. This allows subsequent accesses to the same column to be much quicker. If each task's data can be stored in one column of the DRAM, then worst case execution times are dependent on the column access time, rather than the DRAM's normal access time. This could easily increase processor utilization. If the data takes up multiple columns, even a small number of them, then a problem arises, as the task could access the columns alternately, and thus render the column buffer useless. However, for sequential block accesses within a column, the average memory access time is much lower when static-column DRAM is used instead of normal memory. [5]

Interleaved memory is a set of memory banks in which sequential addresses are spread across memory banks. The use of interleaved memory banks would allow multiple concurrent memory accesses. However, this is too easily defeated by simply using the data immediately after it is loaded. Interleaving can also be defeated by having consecutive

42

memory accesses to the same bank. This problem can be avoided to some extent by making use of several techniques designed to decrease the likelihood that consecutive memory accesses will be to the same memory bank. Interleaved memory works best for sequential accesses, as it is guaranteed that consecutive accesses will be to different banks. As long as consecutive accesses are to different banks, multiple memory accesses can occur concurrently, which dramatically increases the bandwidth of the DRAM. [8]

The use of video random access memory (VRAM) would allow quick instruction access for straight line sections of code. VRAM is dual ported DRAM in which one port is for random access, and the other is for sequential access. The sequential access port has very high throughput, so that the VRAM would be beneficial for sequential blocks of code, but whenever there is a branch that is taken, the full latency of the DRAM is incurred. [5]

Similarly, the use of a stream buffer would also help for straight line sections of code. A stream buffer is essentially a FIFO queue, in which instructions are prefetched sequentially after the current address and placed into the queue. If the DRAM has enough bandwidth to keep the stream buffer full, and there is a straight line section of code, the processor would be able to fetch instructions from the fast queue, instead of the DRAM. As with the use of VRAM, though, whenever there is a branch, the full memory latency of the DRAM will be incurred. [11]

Another possible option is to try to prefetch data and instructions. The stream buffer is really a method of prefetching instructions. Prefetching data requires looking ahead in the instruction stream to anticipate load instructions. Anticipating load instructions can be difficult due to branching, but when it is possible, a prefetch can be initiated. However, it may not be possible to determine the correct memory address if there is a register offset, which may change between the time of the prefetch and the time that the load is executed. A better method of prefetching would be to add instructions to the instruction set to allow code driven preloading. [1]

When used to access sequential blocks of data, many of these methods deterministically decrease the memory access time. The use of static-column DRAM, interleaved memory, and VRAM can easily be used to access sequential blocks of data quicker than if each data word were accessed individually.

## 4.3 Reducing the Miss Rate

The most useful approaches to reducing memory latency are those that combine caching and some other methods for reducing memory latency. Some of the methods with the most potential are backing up a cache with static-column DRAM so that miss penalties would be decreased, or using intelligent prefetching into the cache to increase the hit rate.

Since digital signal processing code typically has access patterns similar to vector code, data prefetching can be driven by anticipating vector accesses. If the vector access stride can be determined, then prefetching can occur without looking for load instructions in the instruction stream. [3] One possible method to determine the vector access stride as a task is running is to use a stride prediction table, as described in [4]. This would allow speculative prefetching to be done, with the prefetched data stored in the cache, hopefully increasing the hit rate. This is not likely to lead to deterministic behavior. However, if the stride is specified in the code, then prefetching can deterministically decrease execution times.

For instruction memory, a cache could be combined with stream buffers or VRAM. This would allow straight line sections of code to benefit from the sequential access capabilities of the stream buffer or VRAM, and branches to be handled by the cache.

44

Interleaved memory could also be used in conjunction with a cache. If the cache is used to hold large blocks of data instead of small lines, then memory interleaving can dramatically increase the memory bandwidth from the DRAM to the cache. In loading a large block of data, all memory accesses are sequential, which would allow the interleaved memory to make full use of all of the memory banks in the system simultaneously.

The methods mentioned here work best with a cache that holds large blocks of data rather than small lines. The larger the data block, the more the memory latency can be amortized across a long sequential access. Of course, there are limits, and the block size can be made too large to take advantage of the memory configuration successfully. Also, there is a point at which increasing the block size will also increase the miss rate, and therefore be detrimental to the system, as explained in Section 4.1 on page 41.

# **Chapter 5**

# A Single Frame Manager System

## 5.1 The Single Frame Manager

As mentioned in Section 3.2.2 on page 36, handling a single frame manager is much simpler than handling an unknown number of frame managers. There can be no preemptions with a single frame manager, as all tasks have the same priority, and tasks are always executed in a predetermined, sequential order. Therefore, the problem of dealing with the cache reduces to the problem of scheduling the cache for a predictable execution order of tasks.

A system in which there is only a single frame manager can be a useful system. That is effectively what is done in a system that uses the timeline scheduling algorithm, such as AT&T's VCOS<sup>†</sup> real-time operating system. [19] [20] [21] VCOS, which stands for Visible Caching Operating System, is intended for use in a real-time system with a visible cache. A visible cache is simply a cache that is visible to the users of the system, unlike conventional hidden caches, which are usually only visible to the operating system. In VCOS, there is only one execution frame, and in that frame, tasks are executed sequentially.

Functioning systems that use VCOS typically have small caches that contain about 1 or 2 kwords and store program code and data in the host system's memory, as the system does not have its own memory beyond the cache. The caches are small so that data can easily be transferred from the host memory to the cache without significantly degrading the system's real-time performance. All tasks must fit within the cache, as the miss penalty would be unbearable if data had to be fetched from the host memory. The cache load and

<sup>†</sup> VCOS is a trademark of AT&T.

unload takes place sequentially before and after a task's execution. This is moderated by the fact that the frame size is rather large (usually 10 ms) so the tasks are correspondingly longer, as they must operate on a larger number of samples. The load and unload time is therefore not as large a percentage of the execution time as it otherwise would be.

The tasks that can execute on this type of system are limited by both the cache size and the frame size. Tasks must be able to function in the given execution frame. If they need a shorter frame, they must do multiple frames' worth of work in the one larger frame, and if they need a larger frame, they must either split up the work among multiple frames, or do nothing in some frames. Having tasks that are idle in some frames is clearly a waste of real-time resources. Also, unless a task is executing in its desired frame, or possibly a multiple thereof, it will be inherently inefficient. However, this solution leads to a functioning caching system, which is not trivial. Tasks are limited to the cache size, because the DSP executes out of host memory space, so there is no way to effectively service a cache miss without forfeiting nearly all of the system's real-time capabilities.

In this framework, task writers do not have the flexibility to choose a frame rate that coincides with a useful number of samples for an efficient signal processing algorithm. Instead sample rate conversion must be done to simulate a particular sampling rate that is more efficient for the purpose of coding an algorithm. There are also other limitations to this type of system. If there can be only one frame rate in the system, it probably will be a slow one, so that all tasks can have useful work to do in each frame. This brings about issues of response time, as each task has to wait an entire frame before it can respond to an external event, which could be a severe constraint. Despite these problems, and possibly others that are related to digital signal processing issues, a usable system can be constructed that hides most of the memory latency with a single frame manager.

Ideally, a real-time system will be able to handle whatever frames the programmer desires. Obviously, full generality cannot be obtained, but hopefully more than one frame will be supported, as a system that only supports a single frame places a large burden on the programmer. However, a system that uses only a single frame manager can be used as a basis for constructing a more general system.

## **5.2 The Loader and Unloader**

In order to schedule the cache effectively, there needs to be a notion of a loader and an unloader for the cache. The loader is something that loads a task's data from memory into the cache, and likewise the unloader copies modified data in the cache back into memory upon completion of execution. The loader and unloader may be conceptual constructs or actual hardware. Figure 5.1 shows a simplistic design of how the loader and unloader would fit into a caching system.

## Figure 5.1: Overview of a Real-Time Caching System

The stages of a task's execution must be broken up into blocks of loading, execution, and unloading. Each task can specify multiple load and execution blocks, and unloads would occur automatically after each execution block on all modified data. If the loader and unloader cannot be active simultaneously with the DSP, then task execution would occur sequentially, in the following order: load, execute, and unload. However, if all three systems can be active simultaneously, then the next task in the schedule can be loaded and the previous task unloaded at the same time that the current task is executing. In this case, the length of each pipeline stage is the longest of loading, executing, or unloading.

Figure 5.2: Task Execution with One Frame Manager

Figure 5.2 shows an example of sequential and pipelined execution. If loading, execution, and unloading occur simultaneously, then there can be three tasks' data in the cache simultaneously. This means that either the size of the cache will seem one third as big to each task, or the cache size must be tripled in order to maintain the same effective cache size as in the sequential case. Also, cache coherency issues must be addressed if three tasks are allowed to reside in the cache simultaneously. A method of handling cache coherency in a partitioned cache will be presented in Chapter 6.

Using the pipelined system, tasks can be pipelined amongst themselves, and similarly, all of the tasks in the frame manager can be put into the pipeline one after another, with no pipeline stalls. Since everything is known in advance, the length of each stage can be predetermined, and the entire time of execution from the first load to the last unload can be calculated ahead of time for the frame. This allows deterministic execution, so the system can effectively operate in real-time without missing deadlines.

### **5.3 Using DRAM in Page Mode**

The above model also applies to DRAM that can be used in page mode without a cache.

Page mode DRAM, as described in Section 4.2 on page 42, is memory that allows a page to be accessed in the normal DRAM access time, but once that page has been accessed, subsequent accesses to the same page can be serviced quickly. When another page is accessed, the old page is lost. So effectively in this arrangement the active page can be considered the cache. The load time then becomes the time to bring up a page, and there is no unload time, as writes update the DRAM directly.

However, loading and execution cannot occur simultaneously, so paging DRAM can only be used in the sequential model. This is not too much of a problem, as the time to bring up a page is typically quite short, perhaps on the order of four or five machine cycles. The use of page mode does require timing on a finer granularity than using a cache, as a page in a DRAM is typically quite small, as it is really just the column that is selected in the DRAM which is stored in a fast buffer.

## 5.4 Task Timing

As discussed in Section 3.2.5 on page 38, task timing will be necessary if the cache is not large enough for the entire task to fit into the cache. However, in this system, timing can be simplified by separating a task into sections. If each section only accesses a block of data that is smaller than the cache size, then these sections can be pipelined in the loader, DSP, and unloader. Furthermore, if the execution time of each section is about the same or greater than the load time for the next section, and the unload time for the previous section, then there will be almost no overhead for loading and unloading the cache, except the initial priming of the pipe and the final flushing of the pipe in each frame.

If tasks cannot be broken down into small enough sections, then timing becomes much more difficult. In that case, the methods described in Section 3.2.5 on page 38 can be used to time the tasks. However, the sequential model must be used, as a cache miss cannot be serviced if the loader is busy loading up another cache partition.

,

# **Chapter 6**

# **Execution Quantization**

### 6.1 Preemptions

Preemptions occur when more than one frame manager are running on the system. It is impossible to predict when these preemptions will take place. As a result, it is necessary to manage the data that is stored in the cache carefully. When a task resumes execution after being preempted, the cache must contain the same data that it did when the task was preempted. The time taken to ensure that the cache contents are correct in spite of preemptions must be deterministic, and it must be guaranteed that there are sufficient resources available to manage the cache. These restrictions are important, because if they are not met, then it is conceivable that many tasks will not complete before their deadlines because the cache was not ready for them to use.

One way to manage the cache is to make each frame manager save the cache before it executes and restore the cache when it completes. This would guarantee that the cache contents are always correct, because after a preemption they will always be returned to the state they were in before the preempting frame manager started to execute. To guarantee that there are enough resources to make this possible, each frame manager must increase its worst case execution time to include the time needed to save and restore the cache. Since frame managers can only be preempted by other frame managers with a faster frame rate, as shown in Theorem 2.1, the slowest frame manager does not have to increase its worst case execution time, as it will never preempt another frame manager. This is a very simplistic method of cache management, and it is not very efficient. Clearly frame managers do not preempt each other at the start of every frame, but this method requires that they be prepared to do so anyway. This may be necessary because of the unpredictable nature of preemptions, but it is very costly. A significant amount of time is being reserved in case it is needed to save and restore the cache, and if it is not used, then it cannot be reclaimed for real-time use.

## **6.2 Quantization**

A better way to overcome the problem of preemptions is to guarantee that each task can execute for a certain length of time once it starts running. By providing a guarantee, the possibility of loading the cache only to execute a few instructions is eliminated. This is the basis for execution quantization (EQ). In EQ, time is broken up into equal sized quantization blocks. Each quantization block is a period of time in which only one task can execute, so once a task begins execution it is guaranteed that it can execute for the entire quantization block. These quantization blocks are separated by quantization boundaries. During the quantization boundaries, the scheduler can become active and decide which task will execute in the next quantization block. Effectively, the scheduler sees time discretely, as it only makes decisions on the equally spaced quantization boundaries.