### DESIGN OF A PHASE-LOCKED LOOP CIRCUIT IN GALLIUM ARSENIDE FOR USE IN A HIGH FREQUENCY CLOCK DISTRIBUTION CHIP

by

James H. Bandy

Submitted to the

### DEPARTMENT OF ELECTRICAL ENGINEERING AND COMPUTER SCIENCE

in partial fulfillment of the requirements

for the degrees of

### **BACHELOR OF SCIENCE**

and

### MASTER OF ENGINEERING

at the

### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

March, 1995

© James H. Bandy, 1995. All Rights Reserved.

The author hereby grants to MIT permission to reproduce and to distribute publicly

paper and electronic copies of this thesis document in whole or in part.

| Signature of Author |                                                                           |

|---------------------|---------------------------------------------------------------------------|

|                     | Department of Electrical Engineering and Computer Science, March 15, 1995 |

| Certified by        | ······································                                    |

|                     | C. G. Fonstad, Prof. of Elec. Eng.                                        |

| Certified by        |                                                                           |

|                     | P. J. Zdeber Company Supervisor                                           |

| Accepted by         |                                                                           |

|                     | F.R. Morgenthaler, Chair, Department Committee on Graduate Students       |

|                     | MASSACHUSETTS INSTITUTE                                                   |

|                     | JUL 1 7 1995                                                              |

## Design of a Phase-Locked Loop Circuit in Gallium Arsenide For Use in a High Frequency Clock Distribution Chip

by

James H. Bandy

Submitted to the Department of Electrical Engineering and Computer Science on March 15, 1995, in partial fulfillment of the requirements for the degrees of Bachelor of Science and Master of Engineering

### Abstract

This thesis discusses the design of a phase-locked loop (PLL) in GaAs for clock distribution applications. To reduce the skew between input and output clock signals from a clock distribution chip, a PLL may be used. By designing the PLL for this application in GaAs, higher frequency performance is possible than with a CMOS design. Basic PLL behavior is described, along with a detailed explanation of the motivations for designing with Source-Coupled FET Logic (SCFL) for an E/D MESFET process in GaAs. The work completed included the design of the major blocks for a PLL: a phase detector, a loop filter, and a voltage-controlled oscillator (VCO). The design considerations taken into account for each of these blocks are described in detail. The phase detector design was based on a novel implementation of a three-state phase detector. The VCO design was a ring oscillator with a frequency range of 200-500MHz. An active filter was used for the loop filter. Finally, a behavioral model was constructed to simulate the performance of the simulations, are described.

Thesis Supervisor: Clifton G. Fonstad Title: Prof. of Electrical Engineering

Company Supervisor: Peter J. Zdebel Company: Motorola, Semiconductor Products Sector

# **Table of Contents**

| 1.                 | Introduction                      |                                       |    |

|--------------------|-----------------------------------|---------------------------------------|----|

|                    | 1.1                               | Project Motivation 7                  |    |

|                    | 1.2                               | 5                                     |    |

|                    | 1.3                               | -                                     |    |

| 2.                 | MESFE                             | Is and Source-Coupled FET Logic       | 13 |

|                    | 2.1                               | Introduction 13                       |    |

|                    | 2.2                               | Fundamentals of MESFETs 13            |    |

|                    | 2.3                               | Source-Coupled FET Logic 19           |    |

| 3.                 | The Theory of Phase-Locked Loops  |                                       | 23 |

|                    | 3.1                               | Introduction 23                       |    |

|                    | 3.2                               | The Phase Detector 24                 |    |

|                    | 3.3                               | The Voltage Controlled Oscillator 26  |    |

|                    | 3.4                               | Linear Performance Characteristics 27 |    |

|                    | 3.5                               | Limits on Linear Behavior 37          |    |

|                    | 3.6                               | Frequency Acquisition 40              |    |

|                    | 3.7                               | Final PLL Architecture 47             |    |

| 4.                 | The Pha                           | se Detector                           | 49 |

|                    | 4.1                               | Introduction 49                       |    |

|                    | 4.2                               | Design Alternatives 49                |    |

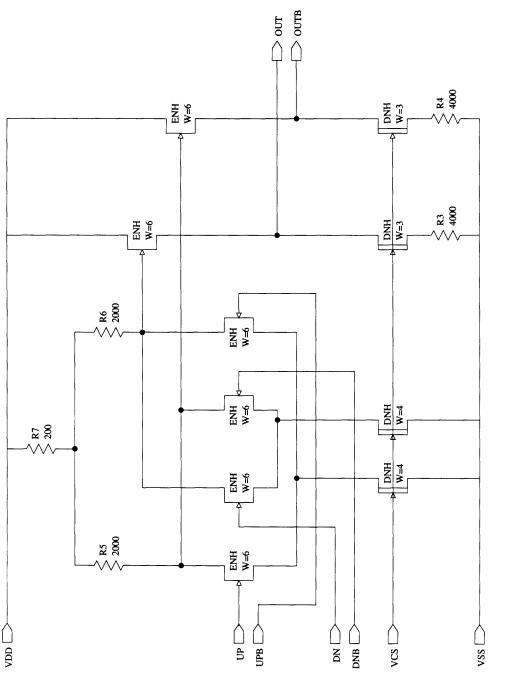

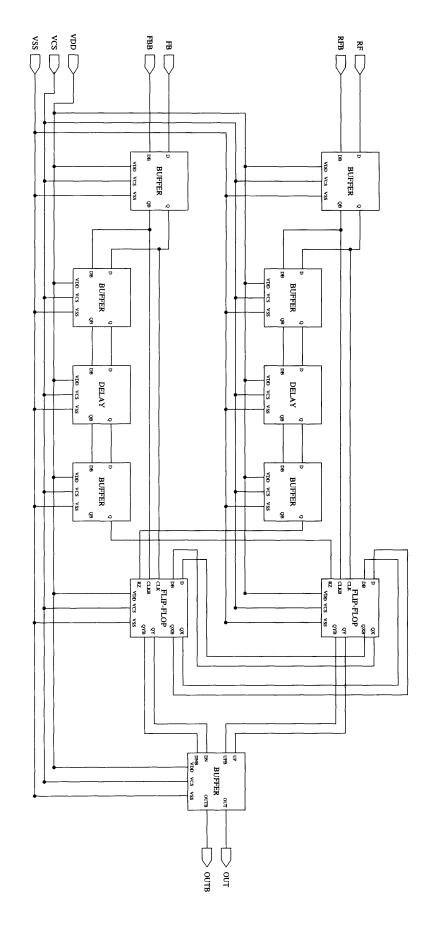

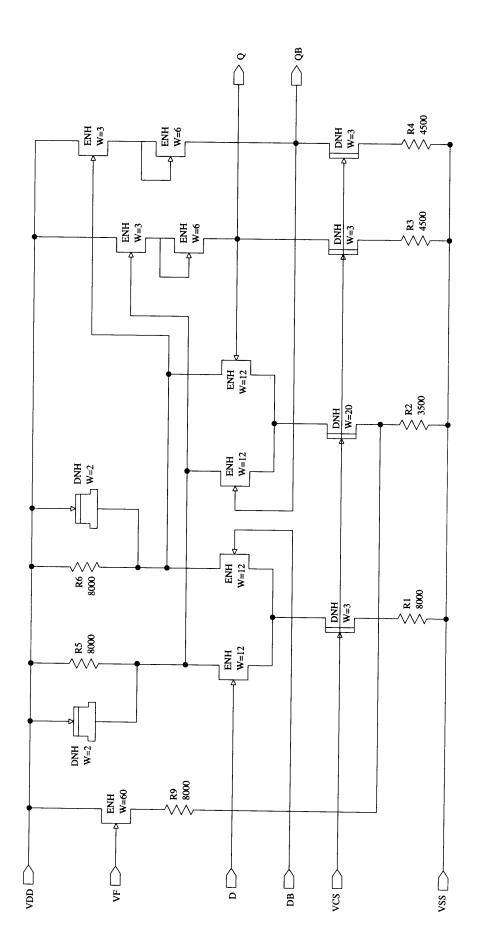

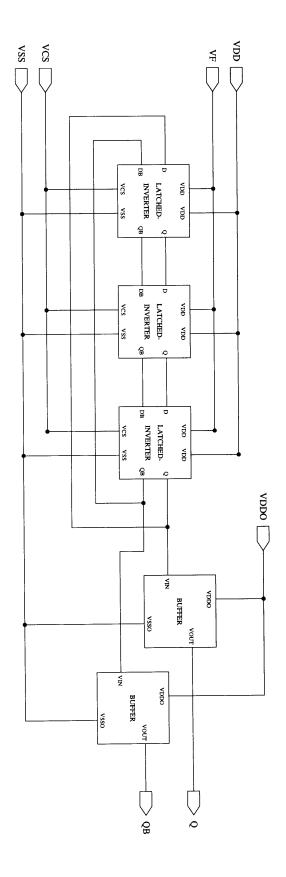

|                    | 4.3                               | Phase Detector Circuits 58            |    |

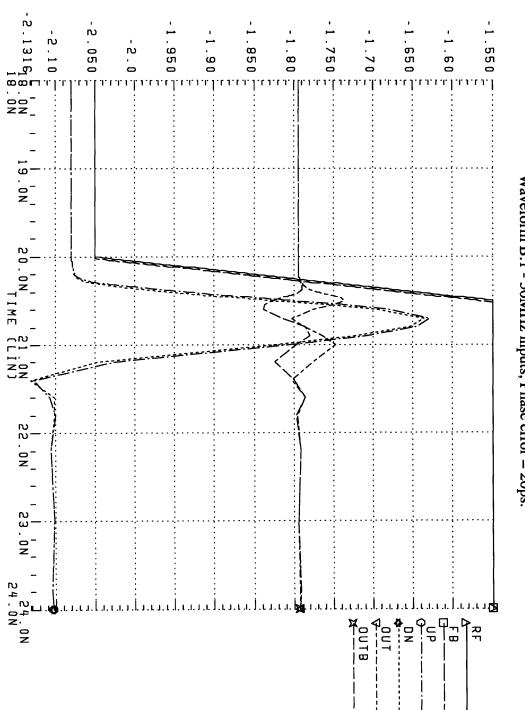

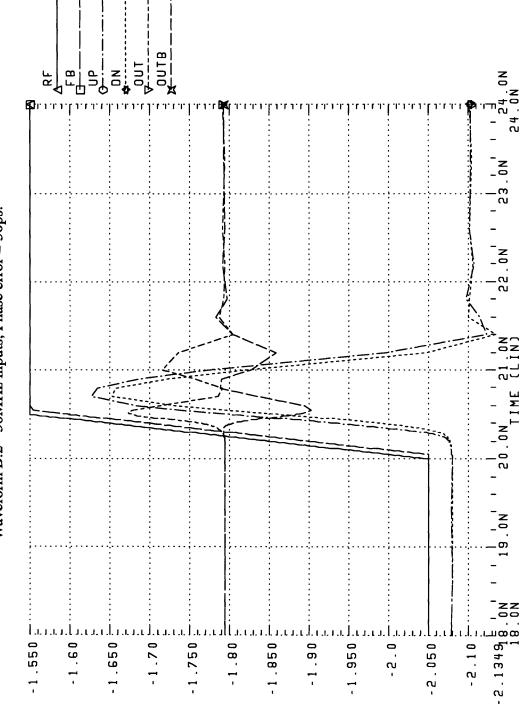

|                    | 4.4                               | Simulated Performance 64              |    |

| 5.                 | The Voltage-Controlled Oscillator |                                       | 69 |

|                    | 5.1                               | Introduction 69                       |    |

|                    | 5.2                               | VCO Performance Criteria 69           |    |

|                    | 5.3                               | Design Alternatives 71                |    |

|                    | 5.4                               | Effects of Using Divider Circuits 72  |    |

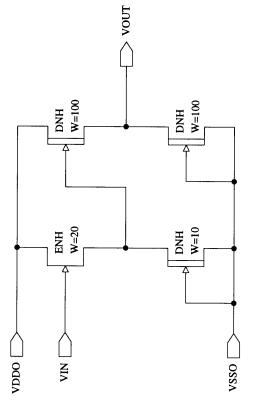

|                    | 5.5                               | Ring Oscillator Circuits 75           |    |

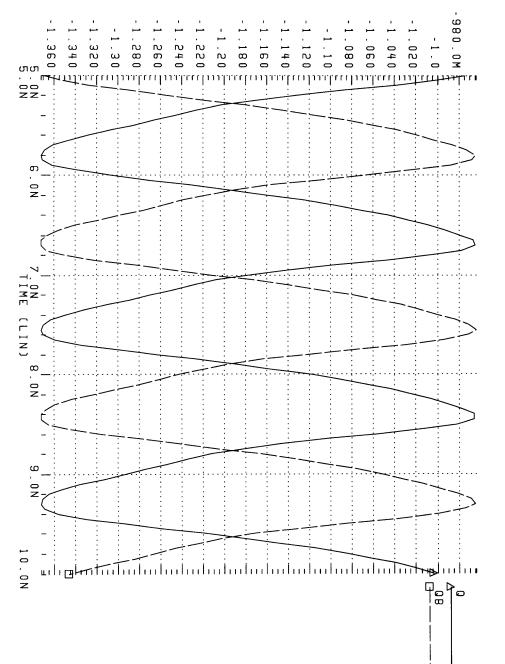

|                    | 5.6                               | Simulated VCO Performance 79          |    |

|                    | 5.7                               | Noise Considerations 81               |    |

| 6. The Loop Filter |                                   | p Filter                              | 83 |

|                    | 6.1                               | Introduction 83                       |    |

|                    | 6.2                               | Charge Pumps 83                       |    |

|                    | 6.3                               | Loop Filter Design Trade-offs 86      |    |

|                    | 6.4                               | Active Loop Filter Architecture 87    |    |

|                                                           | 6.5       | Op Amp Design 91                                     |     |

|-----------------------------------------------------------|-----------|------------------------------------------------------|-----|

|                                                           | 6.6       | Op Amp Performance and Effects on PLL Performance 93 |     |

| 7.                                                        | Behavior  | al Modeling                                          | 95  |

|                                                           | 7.1       | Introduction 95                                      |     |

|                                                           | 7.2       | Motivations for Behavioral Model 95                  |     |

|                                                           | 7.3       | Construction of Behavioral Models 95                 |     |

|                                                           | 7.4       | PLL Performance in the Behavioral Model 100          |     |

| 8.                                                        | Conclusi  | ons                                                  | 103 |

|                                                           | 8.1       | Summary of Work 103                                  |     |

|                                                           | 8.2       | Suggestions for Continuing Work 103                  |     |

| Bibliography                                              |           | 105                                                  |     |

| Acknowledgements                                          |           |                                                      | 107 |

| Appendices                                                |           |                                                      | 109 |

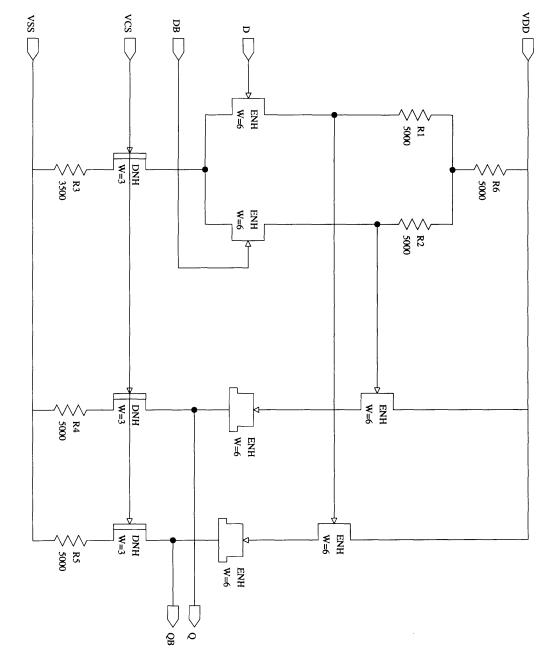

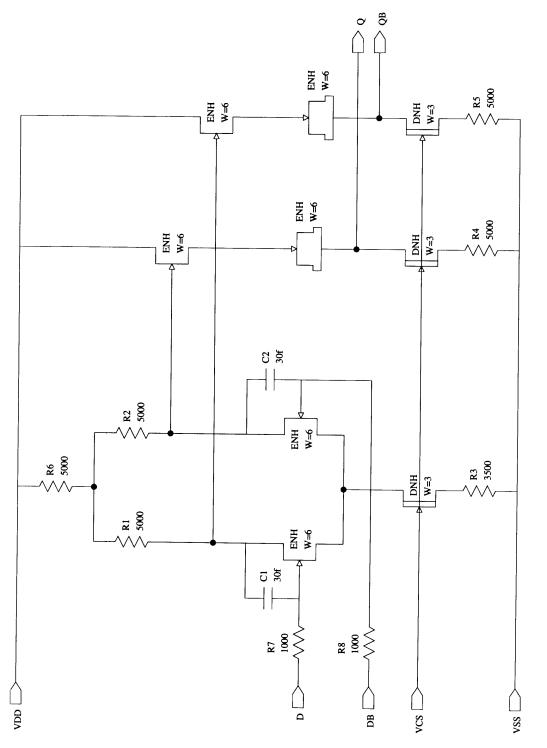

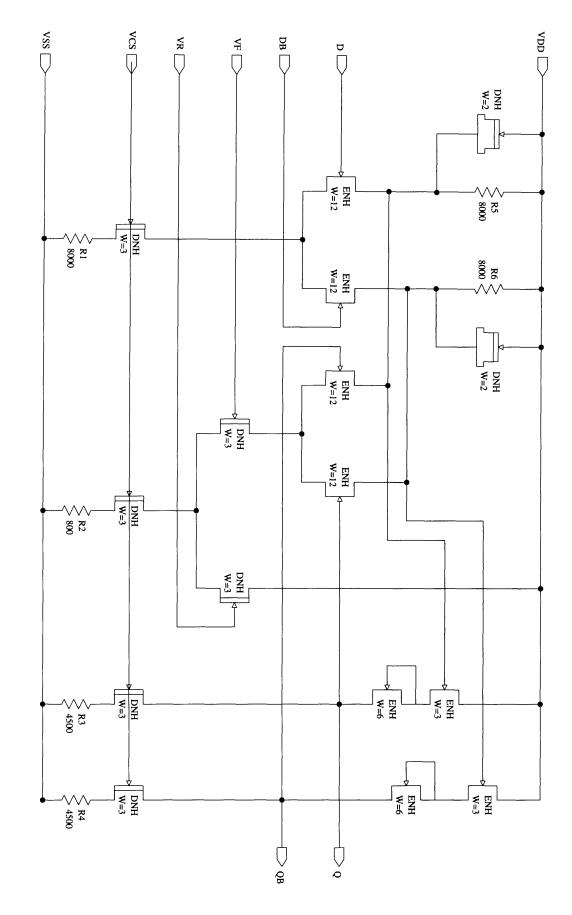

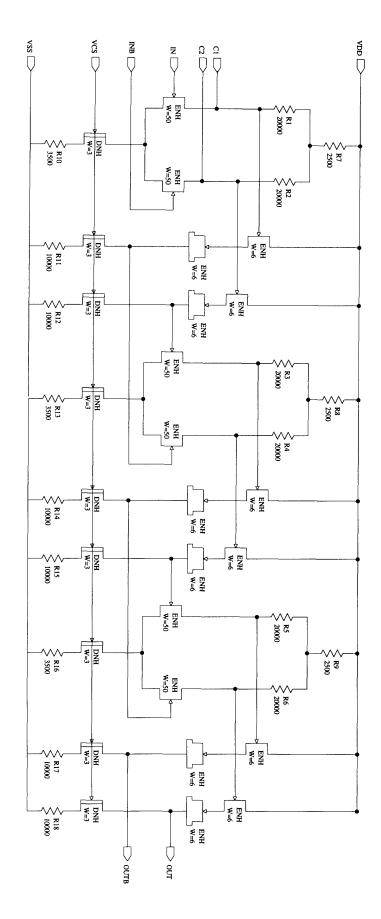

| Appendix A: Schematics for phase detector circuits        |           | 111                                                  |     |

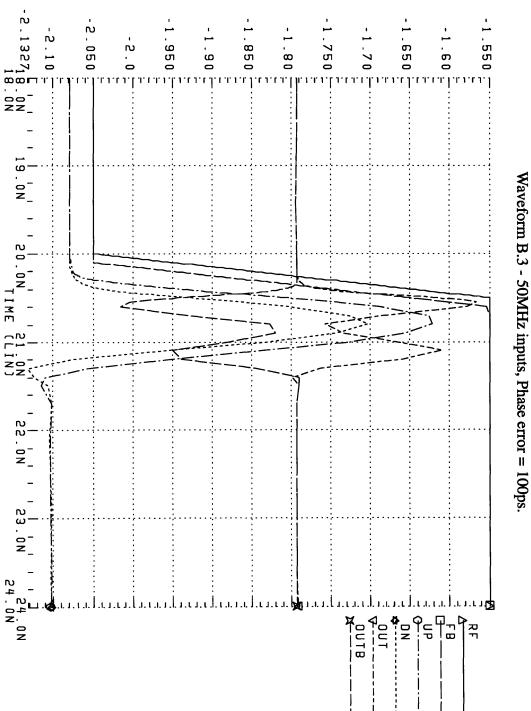

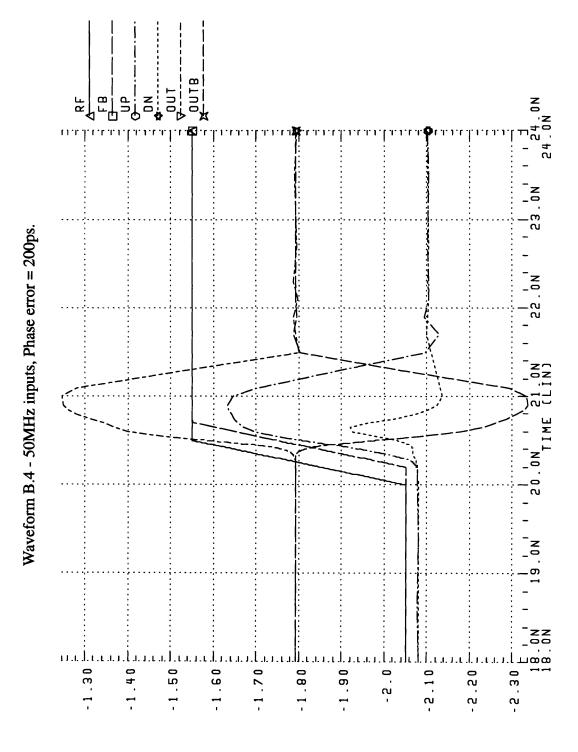

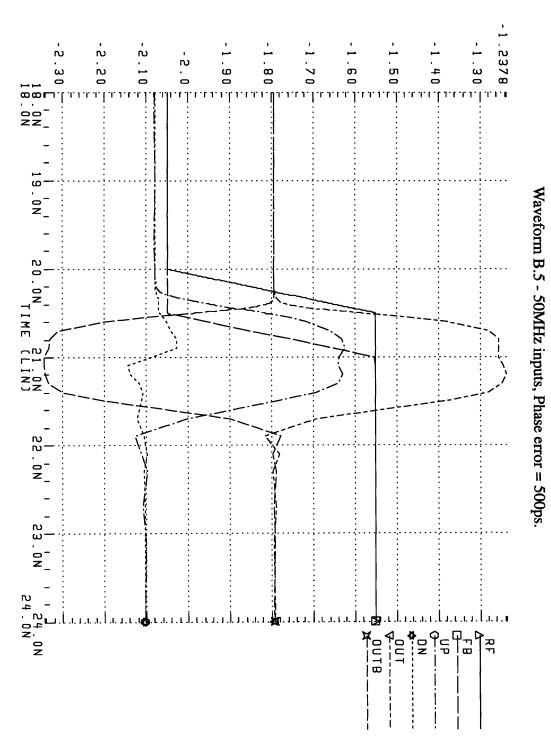

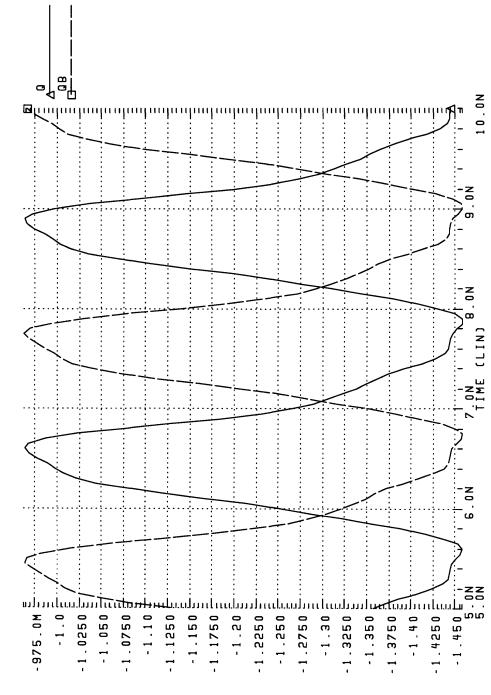

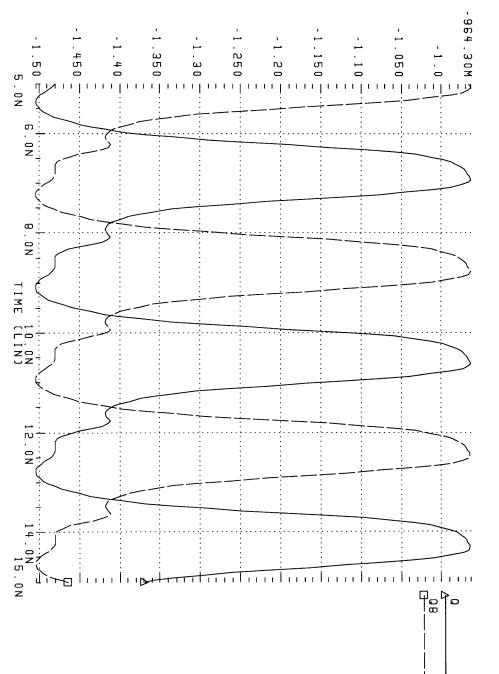

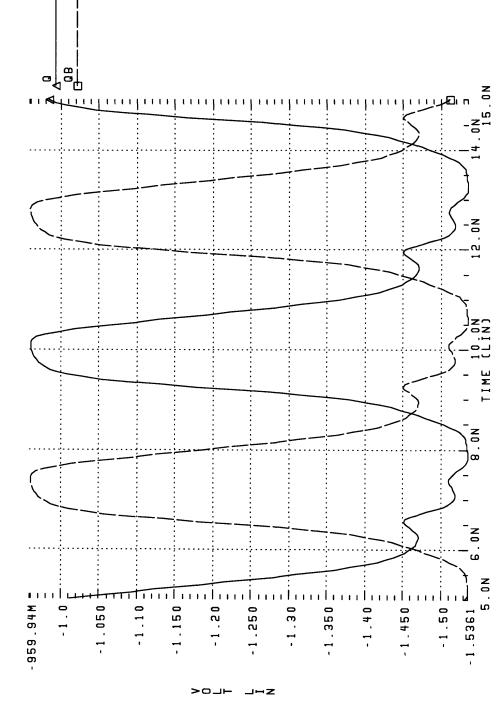

| Appendix B: Simulated output waveforms for phase detector |           | Simulated output waveforms for phase detector        | 117 |

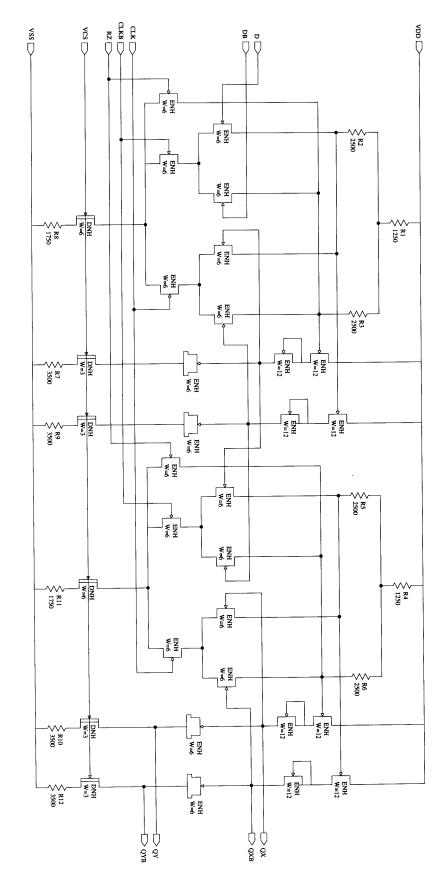

| Ap                                                        | pendix C: | Schematics for VCOs                                  | 123 |

| Ap                                                        | pendix D: | Simulated output waveforms for VCO                   | 129 |

| Ap                                                        | pendix E: | Schematics for loop filter                           | 135 |

| Ap                                                        | pendix F: | Behavioral model code for mixer                      | 139 |

## **Chapter 1 - Introduction**

### **1.1 Project Motivation**

As the speed of integrated circuits has increased due to advances in process and device technologies, it has been desirable to increase the rate of communication between chips by operating at higher clock rates. In order to communicate properly, however, the clock must arrive near synchronously at all chips. This requirement has led to demands for smaller and smaller clock signal skews between when the clock signal reaches each chip on a board. In order to address this problem in workstations and personal computers, manufacturers have resorted to using clock distribution chips to synchronize the clock pulse on each board. One main function of the clock distribution chip is to buffer the main clock signal which is normally heavily loaded, causing signal integrity problems. A second function is to redistribute the clock signal through each of its outputs with minimal skew between the outputs.

Initially clock distribution chips performed these functions through sophisticated use of normal buffer circuits with careful matching of the delay paths through the circuit to minimize the output skew. Recently, however, in order to improve the precision of these chips, internal phase-locked loop (PLL) circuits have been used to further reduce the output skew. These PLL circuits provide a negative feedback loop which minimizes the phase error between the edges of the input and output clock signals. Thus, this architecture can more accurately match the phase of the input clock signal than a scheme using normal input buffers. The use of a PLL can be used for frequency synthesis, it is possible to generate output clock signals from the clock distribution chip at multiples of the input clock frequency. This means the master clock signal distributed throughout the system can be at a lower frequency. Lowering the frequency of this signal permits a lower-cost crystal to be used, reduces the RF interference produced, and simplifies board design. [1]

Currently, clock distribution chips for the workstation and PC market are produced almost exclusively using silicon CMOS processing technologies. These chips operate at relatively low frequencies where CMOS circuitry performs well while consuming small

amounts of power. The introduction of new high speed microprocessors, such as Intel's Pentium (66MHz) and Motorola's Power PC (100MHz), stretch the maximum frequency range of CMOS circuits. Also, CMOS power consumption, which is a function of operating frequency, becomes less competitive. This has lead to the investigation of alternative process technologies. Two processing technologies which are being considered because of their inherent speed / power performance ratios are silicon BiCMOS and gallium arsenide E/D MESFET. The GaAs process is particularly attractive because it is a lower complexity process which would allow the chips to be produced at a lower cost.

The critical element in these new clock distribution chips will be the PLL circuitry. Optimization of the logic which surrounds the PLL in these circuits will only improve performance to a certain point. The performance of the PLL will be the predominant determinant of what output skew can be achieved. The motivation behind the work done for this thesis was to explore the alternatives for designing a high performance PLL suited to this application, and to develop a design for such a PLL in GaAs.

### **1.2 Scope of Thesis Work**

The primary focus of this thesis was the circuit design work required to build a phase-locked loop in gallium arsenide for use in a high frequency clock distribution chip. To form a basis for doing this work, solutions to this type of design in other semiconductor processing technologies were investigated and evaluated as to whether they could be realized in GaAs. This process involved both researching the relevant literature and speaking to other engineers within Motorola who were familiar with the design of PLLs. A number of the different design alternatives which were considered as part of this process, as well as the important design considerations that became apparent, are discussed within this thesis.

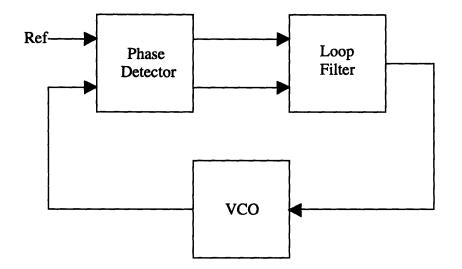

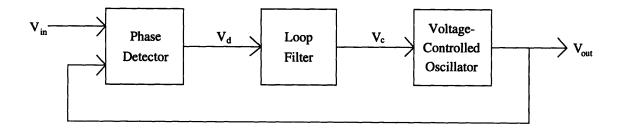

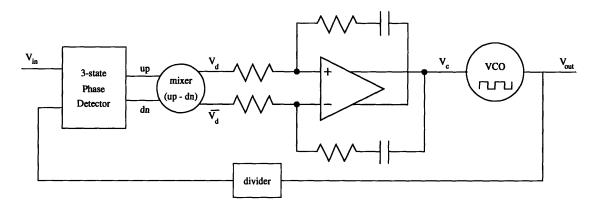

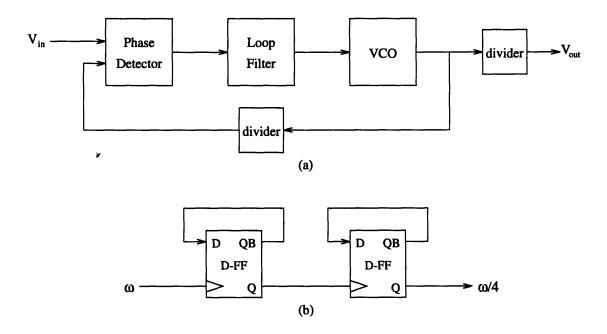

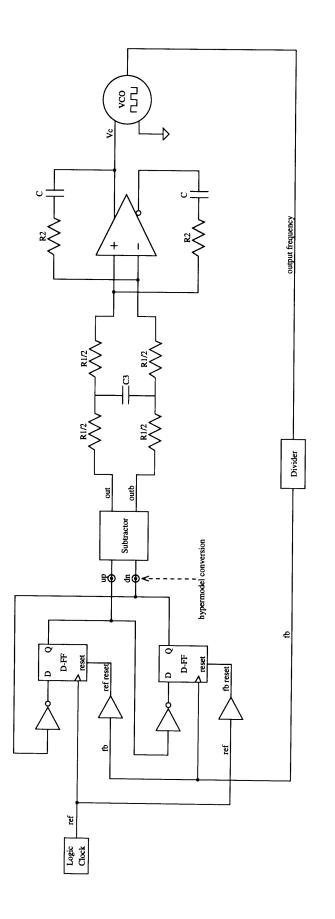

At the end of this research process, a set of designs were selected for the composition of a complete PLL circuit. In order to construct a PLL, three major circuits must be designed: a phase detector, a loop filter, and a voltage-controlled oscillator (VCO). Each of these circuits is described in detail later in this thesis. The arrangement of these circuits within the PLL is illustrated in Figure 1.1. The designs selected to

Figure 1.1 - Basic phase-locked loop design for clock synchronization

implement these circuits were then redesigned in Source-Coupled FET Logic (SCFL) in order to be implemented in an E/D MESFET GaAs process. The resulting circuits were simulated with HSPICE to verify their functionality and performance. The interactions between the phase detector circuit and the loop filter circuit and between the loop filter circuit and VCO circuit were also tested via simulations with HSPICE.

As a final step in the design process, the overall performance of the PLL was simulated through the construction of a behavioral model. The majority of the PLL circuits were modelled using standard elements available in the SABER behavioral modeling software package which was used. For the one circuit which could not be constructed out of standard elements, a new behavioral model was developed based on detailed HSPICE simulations of that circuit. The final behavioral model was used to perform extensive tests of the full PLL's performance.

While the phase detector and VCO circuits designed for this thesis were also laid out for fabrication, this work is not discussed here since it was done by other members of the design team. In addition, changes which were being made in the digital GaAs process flow used to fabricate these circuits delayed the return of fabricated circuits. This prevented the testing of fabricated circuits during the period when this thesis work was done. Some subsequent testing of the VCO circuits, however, has been done. These tests show the performance of the actually circuits to be close to the performance obtained in HSPICE simulations. [2]

It should be noted that this work was part of the first attempt within Motorola at designing a PLL in E/D MESFET GaAs technology. It was also part of the first attempt at designing a PLL-based, monolithic clock distribution integrated circuit with a frequency range of 100MHz to 200MHz in E/D MESFET GaAs technology.

### **1.3 Content and Organization of Thesis**

The content of this thesis has been written in the expectation of sufficiently instructing the reader such that they could continued the work begun here. Chapters 2 and 3 are intended to provide the reader with the necessary background for understanding the work discussed in the rest of the thesis. First, Chapter 2 examines the basic characteristics of MESFETs, as well as the basic elements of Source-Coupled FET Logic. This chapter also further explains the motivations behind using a GaAs E/D MESFET process and the reasons for designing in SCFL. Chapter 3 introduces the reader to the fundamentals of PLL design. It begins by describing the basic characteristics of both the PLL and its major blocks. This is followed by the derivation of the major equations for describing PLL performance.

Chapters 4, 5, and 6 are devoted to the details of the design of the phase detector, VCO, and loop filter, respectively. In each chapter, the design alternatives which were considered are presented first, along with the justification for the approach which was chosen. This comparison process also points out the important design parameters associated with each of the circuits. Next, the important details of the circuit architectures which were designed are examined. Finally, the simulated performance of each circuit, as well as any affects of this performance on the full PLL's behavior, are discussed.

Chapter 7 discusses the behavioral modelling work which was performed, and the results which were obtained. The final chapter, Chapter 8, summarizes the work which was done for this thesis, and makes suggestions for continuing the work.

## References

- [1] D. Chen, "Designing On-Chip Clock Generators," *IEEE Circuits and Devices*, vol. 8, pp 32-36, July 1992.

- [2] R. Sodhi, "Development of a DC Pulse Test Circuit for an Electromigration Study," Thesis for Bachelor of Science, MIT, Cambridge, MA, 1995.

## **Chapter 2 - MESFETs and Source-Coupled FET Logic**

### **2.1 Introduction**

This section essentially looks at the environment in which the circuits for this thesis were designed. Before any attempt was made to design the circuitry for the PLL, a number of decisions had already been made. The first of these was that the design was going to be attempted in Gallium Arsenide (GaAs). Since GaAs lacks a stable native oxide this meant that MOSFETs (metal-oxide-semiconductor field effect transistors) could not be used for the design, but instead MESFETs (metal-semiconductor field effect transistors) would be used. This section will present the basic structure and behavior of these devices and will point to some of the major differences between these devices and MOSFETs. The reasons for using only enhancement and depletion devices, rather than complementary devices, will also be mentioned.

Another decision that was made before beginning the circuit design process was to design in Source-Coupled FET Logic (SCFL). This section will discuss the basic characteristics of SCFL designs, which closely resemble those of ECL designs using bipolar devices. The reasons for choosing this family of logic over Direct-Coupled FET Logic (DCFL), the other major logic style in GaAs technology, will also be discussed.

### **2.2 Fundamentals of MESFETs**

As was mentioned above, a designer working in GaAs has no choice but to design with MESFETs instead of MOSFETs. To someone not familiar with circuit design in GaAs, the term MESFET may also be unfamiliar. In silicon, the majority of all digital circuit design is done with MOSFETs. Thus, in addition to explaining the basic behavior of MESFETs, this section will also point out the important differences between the two types of devices. This should help the make clear the trade-offs involved in choosing to design in GaAs rather than Si.

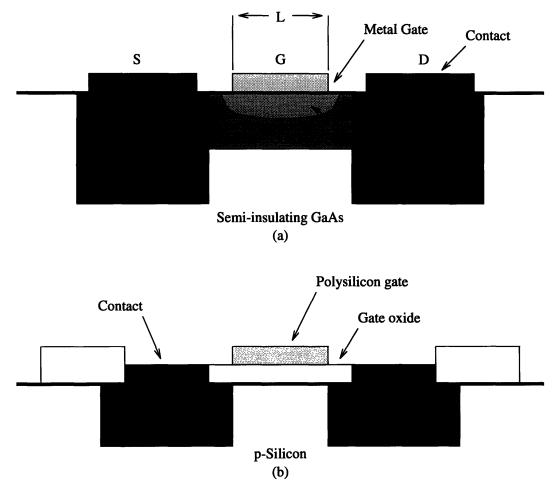

To begin, a cross-sectional view of a typical MESFET, as well as a MOSFET, are shown in Figure 2.1. Looking at this illustration, one sees that a MESFET is a three terminal device consisting of a gate contact, a source contact, and a drain contact. The source and the drain contacts are both ohmic contacts to n<sup>+</sup>-GaAs. The two contacts are

Figure 2.1 - Cross-sectional views (not to scale) of a MESFET (a) and a MOSFET (b)

physically identical because of the symmetry of the device, however, by convention they have different functions. A MESFET will always be placed in a design so that the current flows from the drain contact to the source contact. The names of the two contacts come from the electron flow within the device for this direction of current. Electrons will always be sourced at the source contact and drained away at the drain contact.

The gate contact is the control node for a MESFET. The biasing of this contact relative to the source contact will have the major effect on the magnitude of the device's drain-source current. This functionality of the three terminals is the same as that for the three terminals of a MOSFET. The critical difference between these two types of devices, however, is in how the gate contact to the channel region is formed. In a MOSFET, the gate is separated from the channel by a layer of oxide which insulates the two regions. In a MESFET, though, the gate makes direct contact with the channel region, forming a

metal-semiconductor or Schottky contact. This connection constrains the gate voltage of a MESFET because of the diode's forward conduction limit. As will be shown later, this property turns out to be an important factor in using this device in DCFL designs.

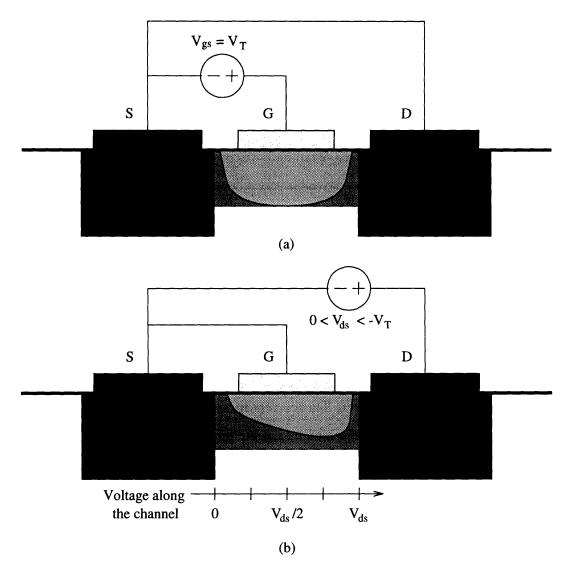

The connection of the gate to the channel also points to a second difference between the two devices. In the MESFET, the gate connects to a pre-existing channel formed by the n-GaAs region which extends between the source and drain contact regions. The width of this channel is modulated by varying the space-charge region of the Schottky diode formed by the gate contact. Decreasing the voltage of the gate will cause the spacecharge region of the Schottky diode, where majority carriers are depleted, to grow wider and pinch off more of the channel. The diagram of the MOSFET, which represents an enhancement type MOSFET, however, shows that there is no pre-existing channel for this device. Instead, the gate contact, which functions like a capacitor, must be used to invert the surface region under the gate. Positive charge placed on the gate will cause electrons to be pulled into the area under the gate, and when the number of electrons is sufficient to become the dominant carrier in this region, a conducting channel will be formed. The depletion MOSFET uses this same mechanism for modulating channel width, but does include a pre-existing, doped channel.

One last difference between the two devices in terms of construction is that a MESFET is built in a semi-insulating substrate while the n-type MOSFET is built in a p-type substrate. On the plus side for MESFETs, this leads to lower parasitic device capacitances, since MOSFETs must deal with the space charge region associated with a reverse biased pn junction. This pn junction, however, provides better isolation between devices. While the resistance of the semi-insulating substrate is quite high, typically on the order of  $10^6$  to  $10^8 \Omega$ cm, the possibility of charge flowing through the substrate and causing device interaction leads to less dense spacing rules than for Si MOSFETs.

Since choosing to work with MESFETs or MOSFETs is essentially a direct function of choosing whether to work in GaAs or Si, it is also worth noting the underlying differences in materials that one tries to take advantage of by designing in GaAs. The primary advantage of GaAs over Si is the dramatically higher mobility of electrons in GaAs for low electric fields. Translated, this means higher speeds at lower power levels. A disadvantage, however, is the slightly lower mobility of holes in GaAs. In Si, where

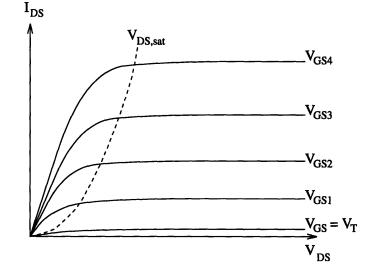

Figure 2.2 - Example  $I_{DS}$  -  $V_{DS}$  characteristic for a MESFET ( $V_{GS2} > V_{GS1}$ , etc)

these two mobilities are much closer together, the advantages of CMOS circuit design techniques can be utilized with a more acceptable penalty in speed. In GaAs, the complementary approach is avoided in order to preserve the speed advantage. For this reason, designs in GaAs generally use n-type enhancement and depletion devices and no p-type devices. This is similar to Si NMOS design. By avoiding using p-type devices, a second drawback of these devices is also avoided. The low barrier voltage of most metals on p-type GaAs makes fully depleting the channel difficult. This leads to higher leakage currents with p-type GaAs MESFETs.

Having outlined the motivations for designing with GaAs MESFETs, the behavior of these devices can now be looked at in more detail. A graph illustrating the  $I_{ds}$  vs.  $V_{ds}$ characteristic for a typical MESFET is shown in Figure 2.2.  $I_{ds}$  is the current from the drain contact to the source contact, while  $V_{ds}$  is the drain to source voltage. This graph includes a number of curves for different gate-source voltages,  $V_{gs}$ . The performance of a MESFET is broken into three regions: cut-off, linear, and saturation. In the cut-off region, the  $V_{gs}$  is such that the entire channel is pinched off by the depletion region of the Schottky diode without any  $V_{ds}$  being applied to the device. The  $V_{gs}$  for which this condition occurs is generally called the threshold voltage,  $V_T$ . While some current can flow through the device under this condition, called the subthreshold current, this current is very small compared to the magnitude of the currents in the other regions of operation.

Figure 2.3 - Illustration of MESFET channel in cut-off region (a) and in linear region (b).

A diagram illustrating this condition is shown in Figure 2.3 (a). The difference between a depletion device and an enhancement device when expressed in terms of  $V_T$  is that an enhancement device has a positive  $V_T$ , while a depletion device has a negative  $V_T$ .

The next region of performance is the linear region. Here  $V_{gs}$  is greater than  $V_{T}$ , meaning that the channel will not be pinched off when no  $V_{ds}$  is applied. If a finite  $V_{ds}$  is now applied, current will flow through the channel. This region is called linear because for small  $V_{ds}$ , the increase in current through the channel is directly proportional to the increase in  $V_{ds}$  divided by the resistance of the channel. The range of  $V_{ds}$  over which this increase in current is linear is fairly small, however, because of a second effect that starts to limit the increase in current. The  $V_{ds}$  applied to the device must be dropped along the channel between the drain and source. This results in a decrease in the gate to channel voltage near the drain contact which causes the channel to narrow at this end. Thus the increase in current through the channel for higher  $V_{ds}$  is being countered by the narrowing of the channel. This effect is illustrated in Figure 2.3 (b) for a depletion device. If  $V_{ds}$  continues to increase, the channel will eventually become completely pinched-off at the drain end of the device. This voltage, which varies depending on  $V_{gs}$ , is called the saturation voltage,  $V_{ds,sat}$ . The equation for  $V_{ds,sat}$  is

$$V_{ds,sat} = V_{gs} - V_{T}$$

(2.1)

For devices with short gate lengths (L <  $2\mu$ m), the current saturation point is moved even lower due to another effect that limits the current flow. In GaAs, the maximum electron velocity is reached for fairly low electric fields. For short gate length devices, this field strength will be reached at a rather low V<sub>ds</sub>. This V<sub>ds</sub> will be below the V<sub>ds</sub> required to pinch off the channel. This current limiting effect plays a significant role with the devices used in this thesis, which had a gate length of 0.7 µm.

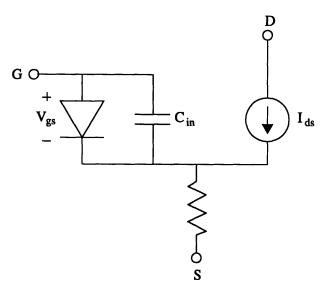

The final region of operation is the saturation region. In this region,  $V_{ds}$  is greater than  $V_{ds,dat}$ , so that  $V_{ds}$  no longer significantly affects the current through the device. There is some increase in current for higher  $V_{ds}$ , which translates into a finite output conductance. This is the desirable region to operate a MESFET in because its gain is highest here. As a side note, the gain of a short gate length MESFET is roughly 3-4 times higher in this region than that of a comparable Si MOSFET. Since this is the region where the circuits in this thesis were primarily operated, a simplified equivalent circuit model for a MESFET operating in this region is shown in Figure 2.4.

This model points out the major concerns a designer must keep in mind during the design process. The equation for  $I_{ds}$  in this model is

$$I_{ds,sat} = \beta \left( V_{gs} - V_T \right)^2$$

(2.2)

$$\beta = \frac{2\varepsilon_{s}\mu_{n}v_{sat}W}{b(\mu_{n}V_{po} + 3v_{sat}L)}$$

(2.3)

Figure 2.4 - Simplified equivalent circuit model for a MESFET operating in saturation region.

Rather than getting into the details of the equation for  $\beta$ , from the designers point of view, all the parameters for  $\beta$ , except for the devices width, W, are fixed for a process used. While gate length is sometimes deliberately increased in order to lower currents in non-speed critical proportions of a design, all high performance areas of a circuit will be designed using the minimum gate length possible with the process being used. Taking this simplified view, a few notes should be made about this current equation. First,  $V_{ds}$  is completely absent. Second, the devices current gain is a function of the square of  $V_{gs}$ . Finally, the gain of the device can be increased by increasing the width of the device. There is a trade-off here, however, in that the input node capacitance,  $C_{in}$ , increases proportionally with gate width. As a last note, the diode in this model points out the limit on the gate voltage of this device which is generally 0.6 to 0.7 V.

### 2.3 Source-Coupled FET Logic

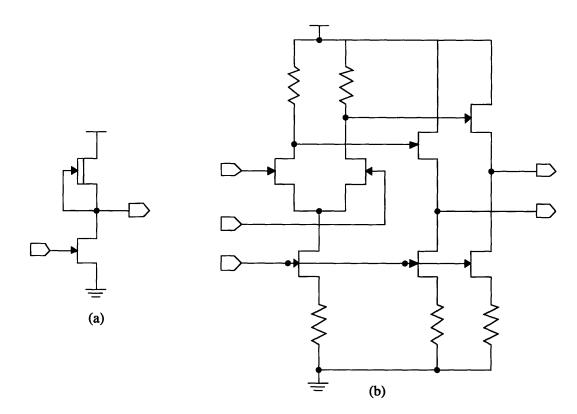

This section explains the reasons for designing the circuits for this thesis in Source-Coupled FET Logic (SCFL). The basic elements of SCFL design are presented. Throughout this section, a comparison is also made to Direct-Coupled FET Logic (DCFL) design, since this is the other major style of logic design which was considered. To begin, schematics for both a basic DCFL and SCFL gate are shown in Figure 2.5.

Figure 2.5 - Schematic of a DCFL gate (a) and a SCFL gate (b).

On a physical level, there are a number of differences between these two gates. Most obviously, the DCFL gate is quite significantly smaller. This is clearly good for VLSI, where one wants to pack the gates as close together as possible. It also means that yields for a particular circuit should be relatively better because of the smaller die area that will be required. On a more subtle level, the smaller number of devices required for the DCFL gate means that it can operate within narrower rail-to-rail voltages. This in turn can lead to designs that require less power than a comparable SCFL design.

Another physical difference is that a standard SCFL gate uses resistors, while DCFL gates do not. In terms of process complexity, not having resistors is an advantage for DCFL design. On the other hand, while it might be possible to remove the resistors from a SCFL design by using active loads and uncompensated current sources, there are advantages associated with including them. The first is that they allow a designer more precise control over the logic swing of the gate. In a DCFL gate, the output low voltage depends on the current within the gate and the drain-source resistance of the enhancement device, while the output high voltage is clamped by the Schottky diode behavior of the subsequent gates. In both cases, the swing is controlled by inherent parameters of the devices being used. Another important benefit of the resistors is that they provide compensation for both process and temperature variations. The output swing in an SCFL gate is controlled by a resistor ratio. Consider a case where resistor values in an SCFL design are lower than normal because of either temperature or process variation. The lower resistor values in the switching portion of the gate would mean a smaller output swing if the current through the gate remained fixed. The smaller resistor values in the current. Finally, the control a designer has over the output swing in this type of SCFL design has another advantage in that it allows a designer to design for smaller voltage swings. This in turn will allow for higher speeds.

On an architectural level, there are several more differences. First, the input and output for a SCFL gate is differential, while these are single-ended for a DCFL gate. This property minimizes the common-mode noise in a SCFL gate. This is a tremendous advantage since most noise that appears is common-mode. The architecture of a SCFL gate also makes it somewhat less sensitive to variations in device thresholds. Assuming that most variations in the threshold are seen across a wafer, but not locally, the switching portion of the SCFL gate should not be affected by the threshold voltage variation because it depends on a relative comparison of  $V_{gs}$  - $V_T$  in determining the current through the two sides of the current switch. The gate's overall current should not be affected since they are set primarily by the resistors. Another advantage of the SCFL gate is that the source followers give it superior fan out capability over that of a DCFL gate. Finally, one architectural similarity between SCFL and DCFL is that they are both constant current logic families, as opposed to CMOS design. This is an advantage over CMOS because it leads to reduced switching noise. At the same time, this means that when operating at the same voltage, neither SCFL or DCFL has a definite power advantage, but instead this depends on the details of the circuits. As mentioned above, though, an all DCFL circuit can be operated at lower voltages.

The eventual decision to design in SCFL reflected both circuit design considerations and concerns over the process which was going to be used. The better noise performance of SCFL circuits because of their differential inputs and outputs was

important because of the requirement for very low noise-induced jitter within the PLL. Power consumption was not as much an issue since whatever circuit was designed was still expected to be operated at 3V. Finally, the compensation properties of the SCFL gate were considered valuable since the process being worked with was still very new and was expected to have significant variations in device characteristics.

## **Chapter 3 - The Theory of Phase-Locked Loops**

### **3.1 Introduction**

This section looks at the basic theory surrounding the design and functioning of phase-locked loops. The object of this section is to provide the reader with a sufficient background to understand some of the higher level considerations that went into the design of the circuits for this thesis. For those readers who are interested in pursuing this topic further and designing their own PLLs, some suggestions for further reading can be made. Wolaver's book provides an excellent look at PLL design for a practicing engineer, focusing on the knowledge required to design a standard PLL. [1] Gardner's book is one of the classic texts on PLLs, providing more of the theory behind PLLs. [2]

The basic goal of a phase-locked loop is to produce an output signal whose frequency and phase are matched to the desired frequency component of its input signal. In its simplest form, the functionality of a PLL can be achieved by placing a phase detector together with a voltage controlled oscillator in a negative feedback loop. In all practical designs, however, a low-pass filter circuit is added into the forward path of the feedback loop because of the dramatic performance improvements it produces. This filter is called the loop filter because of its position within the feedback loop. Figure 3.1 shows this basic architecture.

Looking at this figure, one sees that a PLL is essentially a negative feedback system. The error signal which this system tries to minimize is the phase error between its input and output signals. Assume that the system starts with the phase and frequency of the two signals matched. Now suppose that the frequency of the input signal increases slightly. This will cause the phase of the PLL's output to start to fall behind that of the

Figure 3.1 - Basic phase-locked loop architecture

input signal. The increase in phase error, however, will cause the signal out of the phase detector to increase. Neglecting momentarily the effect of the loop filter, this higher phase detector output voltage will cause the VCO output frequency to increase. This will push the phase of the output back towards that of the input, so that the phase error is minimized again. At the same time, the frequency of the output signal will be tuned to the new frequency of the input signal. In general, one should be aware of the tight interconnection between phase and frequency, with frequency to be used to correct a phase error. Now consider the loop filters affect on this process. At low frequencies the loop filter might have a high gain which lowers the error signal the system will tolerate, while at high frequencies it may attenuate the system's response to changes in the input signal. This second effect may be desirable for eliminating the effect of higher frequency noise in the input signal. This example, however, only looks at a PLL's behavior for one region of operation.

The rest of this chapter is broken into a number of sections that address in a more detailed manner the behavior of a PLL within each of its regions of operation. One section will look at the in-lock behavior of a PLL. The term "in-lock" is used to indicate that the frequency of the PLL's oscillator has been tuned close enough to the frequency of the input that the PLL's behavior is linear. The performance of a PLL will be looked at under both steady-state and AC conditions in this section. The following section will look at the limits on the linear behavior of a PLL. This section describes the factors that determine a PLL's linear range of behavior and looks at what conditions might push a PLL out of its linear range. The next section of this chapter will deal with the frequency acquisition process, where the VCO's output frequency is tuned to within the PLL's linear range. A final section describes briefly the final architecture that was used for the PLL. First, however, the general output characteristics of the phase detector and the VCO are described and equations for their behavior are derived.

### **3.2 The Phase Detector**

A phase detector's basic function is to compare the phases of two input signals and to produce an output voltage that is proportional to the difference in phase between the

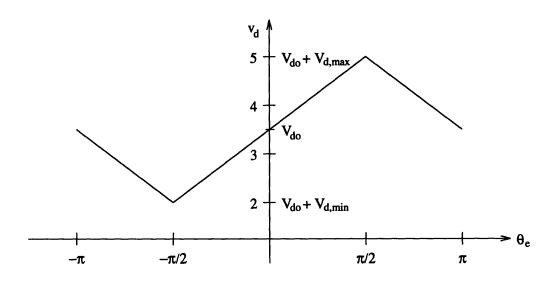

Figure 3.2 - Example phase detector output characteristic

two signals. Assuming from Figure 3.1 that  $\theta_i$  and  $\theta_o$  represent the phases of the phase detector's two input signals and that  $v_d$  is the phase detector output voltage, the equation for this behavior is

$$\mathbf{v}_{d} = \mathbf{K}_{d} \left( \boldsymbol{\theta}_{i} - \boldsymbol{\theta}_{o} \right) \tag{3.1}$$

In this equation,  $K_d$  is the phase detector gain and has units of V/rad. The difference in phase between the two inputs is referred to as the phase error,  $\theta_e$ .

$$\theta_{e} = \theta_{i} - \theta_{o} \tag{3.2}$$

This simplifies Equation (3.1) to

$$\mathbf{v}_{\mathbf{d}} = \mathbf{K}_{\mathbf{d}} \boldsymbol{\theta}_{\mathbf{e}} \tag{3.3}$$

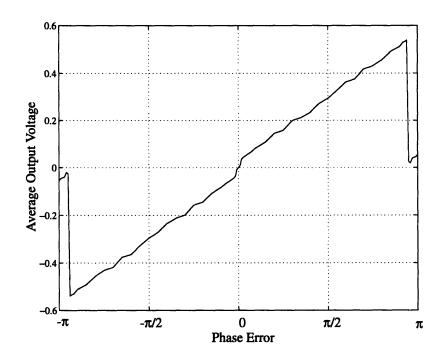

Figure 3.2 shows a potential output characteristic for a phase detector that illustrates this equation.

This particular output characteristic is called a triangular phase detector characteristic because of its triangle wave shape. The first thing to notice about this phase detector characteristic is that it is periodic. This characteristic repeats with a period of  $2\pi$ . While it is possible to extend a phase detector's period beyond  $2\pi$  by adding memory to the phase detector, all phase detectors do in fact have some period to their output characteristic because of the natural  $2\pi$  period of phase itself. Even more limiting in this case, however, is the fact that this phase detector has the same output voltage for multiple phase errors within this  $2\pi$  period. For example, the signal for a phase error of  $3\pi/4$  will look the same to the rest of the PLL as that for a phase error of  $\pi/4$ . While not all phase detectors exhibit this second property, when present this property together with the period of the phase detector determine the range of phase error for which the phase detector's behavior is linear. To address this limitation, a linear range is defined for each type of phase detector. In this range, the output of the phase detector would be  $-\pi/2 < \theta_e < \pi/2$ . When the phase error within the PLL exceeds this linear range, the PLL's behavior becomes non-linear, making it difficult to predict. These instances may cause a previously in-lock PLL to lose lock on the input signal.

A second interesting property of this output characteristic is that there is an output voltage from the phase detector when the phase error is zero. This voltage is called the phase detector offset voltage,  $V_{do}$ . This offset voltage has important consequences on both the steady-state and AC performance of the PLL. Finally, the phase detector gain,  $K_d$ , is illustrated graphically in this output characteristic. The phase detector gain is equivalent to the slope of the output voltage within the detector's linear range.

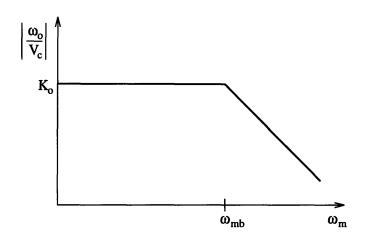

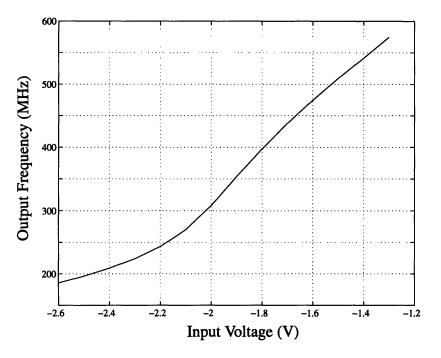

### 3.3 The Voltage Controlled Oscillator

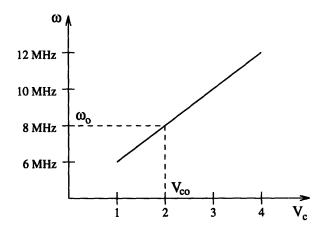

The basic behavior for a voltage-controlled oscillator is to output either a sinusoidal or square wave signal at a frequency which is proportional to the voltage at its input. Figure 3.3 illustrates a potential output characteristic for a VCO. Notice that, in order to produce the desired output frequency, the PLL must generate a non-zero voltage at the input of the VCO, and that this voltage varies depending on the frequency of the input to the PLL. This voltage is called the VCO offset voltage, V<sub>co</sub>. Using this offset voltage, it is possible to derive a linear equation for the deviation in VCO frequency,  $\Delta \omega$ , away from the input frequency.

$$\Delta \omega = K_o (V_c - V_{co})$$

(3.4)

$$\Delta \omega = \omega_{i} - \omega_{o} \tag{3.5}$$

Figure 3.3 - Example VCO output characteristic

Within this equation,  $K_0$  is a new variable called the VCO gain.  $K_0$  is measured in units of rad/s/V. Using this linear model for the VCO together with the linear model for the phase detector, it is now possible to proceed with the analysis of PLL performance.

### **3.4 Linear Performance Characteristics**

In this section, the key measures of a PLL's linear behavior will be defined and examined. A PLL's behavior is considered to be linear when all of its components are operating within their linear ranges. Since the loop filter's behavior is always linear, this means that the phase error in the system must be within the phase detector's linear range, and the frequency of the input signal must be within the VCO's frequency range. A more detailed look at the limits on linear behavior within a PLL will be taken in the next section. Within this section, two important parameters of PLL behavior are discussed, the static phase error and the frequency response. Also, the loop filter and its effect on loop performance will be discussed in more detail. In particular, it will be shown how the loop filter is used to resolve a compromise between the steady-state behavior and the frequency response of a PLL.

To begin, suppose that a PLL has been constructed like the one in Figure 3.1, where the phase detector and VCO have the output characteristics shown in Figures 3.2 and 3.3, respectively. For the time being, assume that the loop filter has a DC gain, F(0), of one. This PLL will be used to illustrate how a static phase error can appear within a PLL.

Suppose that the example PLL has locked to a steady-state input signal,  $\omega_i$ , at 10 MHz. Looking at the VCO characteristic, one sees that the voltage at its input, V<sub>c</sub>, must be 3 V. This voltage must be supplied to the VCO by the phase detector. Looking at the phase detector's output characteristic, however, it becomes apparent that there must be a phase error between its inputs in order to generate an output voltage of 3 V. This phase error is called the static phase error. Thus, within this PLL, some fixed phase error, which depends on the frequency of the input signal, must be present even when the PLL has fully locked to the input signal.

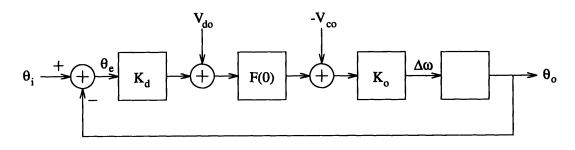

In order to develop a quantitative method for determining static phase error, a DC linear model for the loop is presented in Figure 3.4. This linear model was taken from Wolaver's book. [3] Within this model, the variable  $\Delta \omega$  represents the deviation of the output frequency from the input frequency. The equation for  $\Delta \omega$  in this system is

$$\Delta \omega = \theta_{e} K_{d} F(0) K_{o} + V_{do} F(0) K_{o} - V_{co} K_{o}$$

(3.6)

For the system to be in lock,  $\Delta \omega$  must equal zero. This, however, requires the presence of a static phase error of a sufficient magnitude to negate the voltages contributed by  $V_{do}$  and  $V_{co}$ . Equation 3.6 can be manipulated to produce an equation for this phase error.

$$\theta_{e} = \frac{-V_{do}}{K_{d}} + \frac{V_{co}}{F(0) K_{d}}$$

(3.7)

For the example PLL,  $V_{do} = 3.5 \text{ V}$ ,  $V_{co} = 3.0 \text{ V}$ , F(0) = 1, and  $K_d = 3/\pi \text{ rad/V}$  applies. Thus, there must be a static phase error of  $-\pi/6$  rads.

The static phase error found with a PLL is important because of its limiting effect on the linear range of the PLL. If F(0) were very small or  $V_{co}$  was very large, the static

Figure 3.4 - dc linear model of PLL

phase error required could be outside the linear range of the phase detector. In such cases, the PLL would not be able to lock to the input signal. The static phase error also has an important effect on the dynamic performance of the PLL. When the frequency of the input signal changes, a dynamic phase error will generally appear in the PLL which, depending on the direction of the frequency shift, may be additive to the static phase error. The combination of these phase errors may exceed the phase detector's linear range and thus possibly push the PLL out of lock. By eliminating any static phase error, a PLL has a better chance of staying in lock, where its performance is more predictable.

As Equation (3.7) suggests, one way to get rid of the VCO's contribution to the static phase error would be to make the DC loop filter gain very large. This is, in fact, what almost all PLLs do by including a loop filter that contains an integrator. The integrator gives the loop filter a DC gain of essentially infinity, and thus completely eliminates the effect of  $V_{co}$ . This makes sense physically since the integrator in the loop filter may be charged to whatever  $V_{co}$  is required. The contribution of  $V_{do}$  is handled by making changes in the details of the phase detector circuitry that either reduce  $V_{do}$  to zero or hide it from the rest of the PLL. Examples of how this can be done may be found in Wolaver's book. [4]

As was alluded to earlier, eliminating static phase error within the PLL is not the loop filter's only purpose. The loop filter is also the one element of a PLL a designer can modify in order to control the frequency response or, alternately, the bandwidth of a PLL. Before looking at how the loop filter is used in this regard, however, the frequency response of the example PLL, before the loop filter is added, should be examined.

The terms frequency response and bandwidth are used in regard to a PLL to reflect its ability to track changes in its input signal. A PLL with a low bandwidth will have problems tracking an input signal whose phase or frequency are changing rapidly. While this may be problematic in some situations, it may be desirable in others where the rapidly changing component of the PLL's input is due to noise. Another way of looking at the bandwidth of a PLL is in terms of how much of a reaction does an error in phase produce in the PLL. If a PLL has a phase detector with a very high gain, a small phase error will produce a large signal out of the phase detector. If the PLL also has a high VCO gain, the signal out of the phase detector will produce a large step in the output frequency of the

PLL. A PLL with these characteristics will be able to respond quickly to a change in the input signal. On the other hand, this PLL will also respond dramatically to any noise on the input signal. The bandwidth a designer aims for depends on what application the PLL is going to be used in.

In order to look at a PLL's frequency response quantitatively, the system function for the PLL must be derived. The first step in this process is to find the Laplace transforms of the equations for the phase detector and the VCO. For the phase detector, Equation (3.3) becomes

$$v_d = K_d \theta_e \implies V_d(s) = K_d \theta_e(s)$$

(3.8)

For the VCO, Equation (3.4) becomes

$$\Delta \omega = K_o (V_c - V_{co}) \quad \Rightarrow \quad \omega(s) = K_o V_c(s) \tag{3.9}$$

Within the feedback loop, however, the value of interest that is fed back from the VCO is its phase, not its frequency. Phase, however, is simply the integral of frequency.

$$\theta_{\rm o} = \int \omega_{\rm o} dt \tag{3.10}$$

In the frequency domain this is equivalent to a division by s, so that Equation (3.9) becomes

$$\theta_{o}(s) = \frac{\omega(s)}{s} = \frac{K_{o}V_{c}(s)}{s}$$

(3.11)

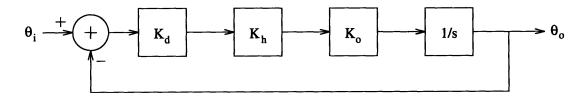

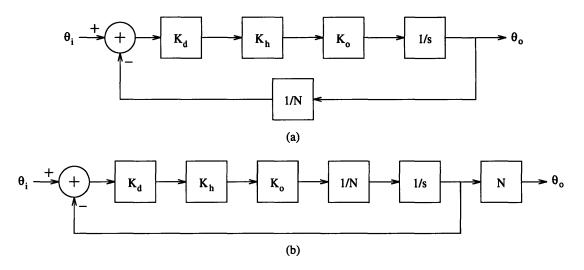

Using these new equations, an AC model of the PLL's behavior can be derived. This AC model is illustrated in Figure 3.5. Notice, that since this is an AC model, the DC offsets of both the phase detector and the VCO may be neglected. Also, while this model

Figure 3.5 - ac linear model for PLL

includes the loop filter gain,  $K_h$ , it is temporarily assumed that its gain is unity across all frequencies.

The system function for a PLL may now be derived from this AC model. Looking at the AC model, one sees that a PLL is essential a negative feedback system with unity feedback. The forward gain of this system is

$$G(s) = \frac{K_d K_o}{s}$$

(3.12)

Now, from feedback theory, the equation for the system function of a PLL is

$$H(s) = \frac{\theta_{o}(s)}{\theta_{i}(s)} = \frac{G(s)}{1 + G(s)}$$

(3.13)

Those familiar with feedback theory should be careful to note that H(s) is used to represent the whole system function here, rather than the feedback gain which, in this case, is always unity. Now, substituting G(s) in Equation (3.13) gives the full system function of the PLL without the loop filter.

$$H(s) = \frac{K_{d}K_{o}}{s + K_{d}K_{o}}$$

(3.14)

At this point, the exact way one defines the bandwidth of a PLL is somewhat arbitrary. One common measure of a system's bandwidth, however, is its -3db frequency. At low frequencies, the system function's gain is determined by the real components of the equation. For high frequencies, however, the imaginary components of the equation will dominate, and the system function's gain falls off rapidly with increasing frequency. The -3db frequency marks the transition between these two regions. The -3db frequency of this system is

$$\omega_{-3db} = K_d K_o \tag{3.15}$$

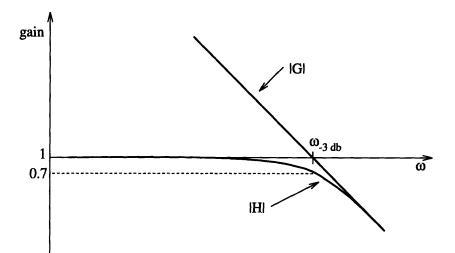

corresponding to the pole of the system function. The Bode plot of this PLL's system function is shown in Figure 3.6 to further illustrate the significance of the -3db frequency.

The problem with this PLL, where the loop filter has been left out, is that the designer has very little control over its bandwidth. The gain of the phase detector and the

Figure 3.6 - Bode plot for PLL without loop filter

VCO are largely fixed by the type of circuit chosen and the process technology used. By adding a loop filter to the PLL, the designer introduces an element into the system whose gain at high frequencies may be set arbitrarily, in order to control the PLL's bandwidth.

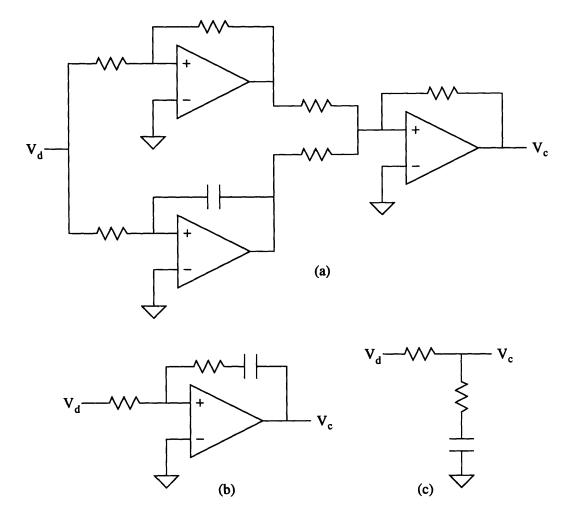

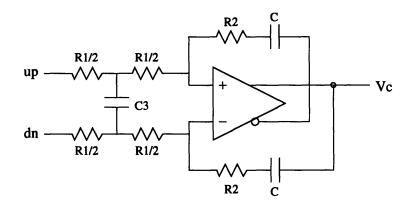

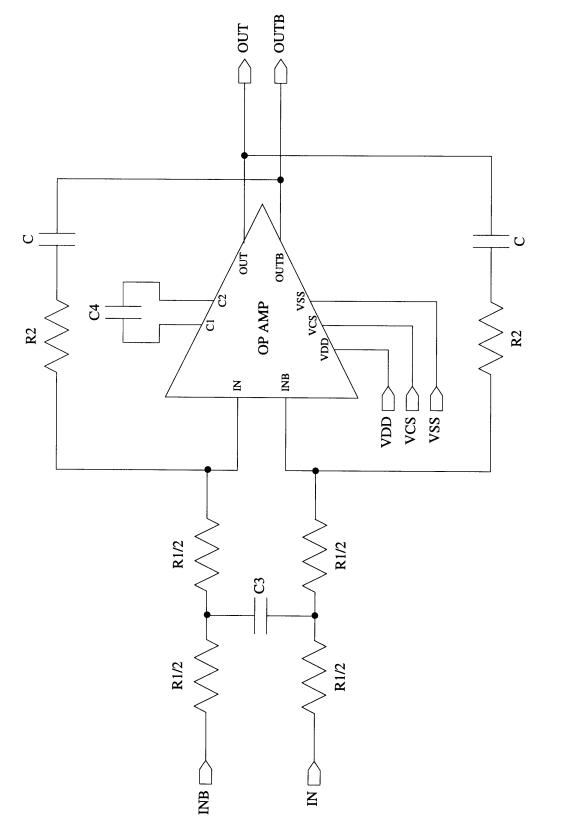

Assuming that an active loop filter design is used, the loop filter actually serves two purposes within the PLL. For the low frequency portion of the signal from the phase detector, the loop filter acts as an integrator so that there is no static phase error in the PLL. For the higher frequency portion of the signal, the loop filter functions as either an attenuator or an amplifier, depending on which is necessary to achieve the desired loop bandwidth. The behavior of the loop filter is therefore essentially the same as that of a integral plus proportional controller from feedback theory. An example of how the loop filter might be implemented is shown in Figure 3.7(a). The functionality of this loop filter can be implemented in a much more efficient architecture that requires only one op amp as shown in Figure 3.7(b). It is also possible to implement the loop filter using only passive components, as shown in Figure 3.7(c), however, this design is seldom used. The DC gain of a passive loop filter, F(0), can not exceed one. This means that, unlike the active filter designs which have high DC gains, this type of loop filter will not eliminate the static phase error caused by the VCO offset voltage. Also, a passive loop filter can only be used to attenuate at high frequencies. This is, however, the desired performance in most cases. On the other hand, in applications where a large static phase error can be tolerated, the advantage of a passive loop filter is that an op amp circuit does not have to be designed.

Figure 3.7 - Schematics for an integral plus proportional controller (a), an active loop filter (b), and a passive loop filter (c).

Supposing that the loop filter illustrated in Figure 3.7(b) is now included in the PLL, a new system function for the PLL needs to be found. The transfer function for the loop filter is

$$F(s) = K_{h} \frac{s + \omega_{z}}{s}$$

(3.16)

The loop filter alters the forward gain of the loop so that its new value is

$$G(s) = K_{d}K_{h}K_{o}\frac{s+\omega_{z}}{s^{2}}$$

(3.17)

To simplify this equation, a new variable called the loop gain is defined.

Figure 3.8 - Bode plots for PLL with loop filter

$$\mathbf{K} = \mathbf{K}_{\mathrm{d}} \mathbf{K}_{\mathrm{b}} \mathbf{K}_{\mathrm{o}} \tag{3.18}$$

This simplifies the forward gain transfer function to

$$G(s) = K \frac{s + \omega_z}{s^2}$$

(3.19)

Using this new forward gain, the system function for the PLL becomes

$$H(s) = \frac{G(s)}{1+G(s)} = \frac{Ks + K\omega_z}{s^2 + Ks + K\omega_z}$$

(3.20)

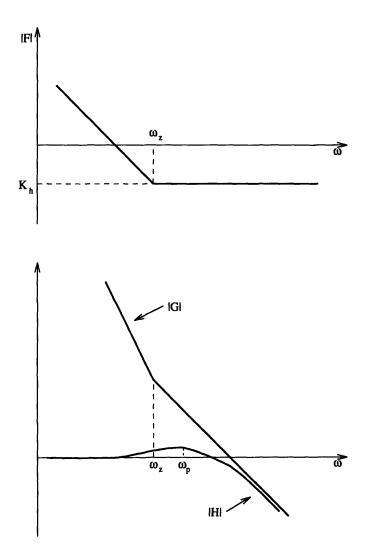

To illustrate the effect of the loop filter, the Bode plots for each of these equations are shown in Figure 3.8.

Looking at the new system function for the PLL and at its Bode plot, a new equation for the bandwidth of the loop can be derived. The new equation for the  $\omega_{-3db}$  frequency is

$$\omega_{-3db} = K_d K_h K_o = K$$

(3.21)

What is important to note here is that by adding a filter circuit into the PLL, rather than simply an attenuation stage with a gain equal to  $K_h$ , the DC performance of the loop does not have to be compromised in order to control the loop's bandwidth. Some consideration must be given, however, to where the loop filter's zero is placed. If the zero is placed too close to the -3db frequency of the system function, it will cause unacceptable peaking of the system response. In control theory terminology, this situation corresponds to the system being underdamped. As a general rule, choosing the frequency for the loop filter's zero,  $\omega_z$ , so that

$$\omega_{z} < \omega_{-3db}/4 \tag{3.22}$$

will produce acceptable performance. Choosing  $\omega_z$  such that  $\omega_z$  equals  $\omega_{-3db}/4$  results in a system that is critically damped.

The notation which has been used up to this point, looks at the frequency response of a PLL in terms of K and  $\omega_z$ . These parameters have the advantage of being easily associated with parameters of the components that make up the PLL. For those who are familiar with control theory, these parameters may be converted so that the behavior of the system may be expressed in terms of natural frequency,  $\omega_n$ , and damping ratio,  $\zeta$ . The equations for these conversions are

$$\zeta = \frac{1}{2} \sqrt{\frac{K}{\omega_z}}$$

(3.23)

$$\omega_{\rm n} = \sqrt{K\omega_{\rm z}} \tag{3.24}$$

As the previous references to the damping of the PLL imply, this conversion is sometimes useful to enable those familiar with control theory to draw on their background. In general, though, the notation used up to this point is considered clearer and more intuitive. Looking again at the Bode plot of the system function for the PLL which includes an active loop filter, one sees that the gain basically follows the lesser of unity and the forward loop gain, |G(s)|. There is, however, some peaking of the system response where the gain exceeds unity. As was mentioned earlier, the extent of this peaking varies with the position of the loop filter's zero. While acceptable performance is generally guaranteed by simply sticking to choosing  $\omega_z$  according to Equation (3.22), it is possible to calculate the peak value of the system response and the frequency at which it occurs. The equation for the peak value of the system response,  $H_p$ , is

$$H_{p} = [1 - 2\alpha - 2\alpha^{2} + 2\alpha (2\alpha + \alpha^{2})^{1/2}]^{-1/2}, \ \alpha = \omega_{z}/K$$

(3.25)

The equation for the frequency at which the peak occurs, called the peaking frequency,  $w_P$ , is

$$w_{p} = w_{z} \left[ \left( \frac{2K}{w_{z}} + 1 \right)^{1/2} - 1 \right]^{1/2}$$

(3.26)

These equations are taken from Wolaver's book, which also provides a chart of approximations to these equations which might be more useful to those trying to gain insight. [5] This chart is shown in Table 3.1.

| Damping  | ω <sub>z</sub> /K | ω <sub>p</sub>               | H <sub>p</sub>      |

|----------|-------------------|------------------------------|---------------------|

| Over     | <0.25             | $1.2\omega_{z}^{3/4}K^{1/4}$ | $1 + \omega_z/K$    |

| Critical | 0.25              | 1.4ω <sub>z</sub>            | 1.15                |

| Under    | >0.25             | $\sqrt{K\omega_z}$           | $\sqrt{\omega_z/K}$ |

Table 3.1 - Approximations for peaking parameters

A final note about the order of the PLL after the adding of the loop filter. Adding the loop filter to the PLL caused a  $s^2$  term to appear in the denominator of the system function. This makes the PLL a second order system. A PLL without a loop filter is a first order system because of the integration that takes place in the VCO. In some PLL's a loop filter with two integrators is added to the PLL, making the PLL a third order system. The advantage of such a loop filter is that the PLL is better able to track a ramp in frequency by its input signal. This type of loop filter is not used very often, however, because of the extra complexity involved, including that it is not inherently stable like a second order PLL. For these reasons, this type of PLL has not been discussed, but more information on it may be found in Gardner's book for those who are interested. [6]

### **3.5 Limits on Linear Behavior**

This section will discuss the limitations on a PLL's ability to remain in lock while tracking a changing input signal. This section will look at the response of a PLL to various changes in its input signal, including a phase-step, a frequency-step, and a frequency-ramp. A PLL's response to sinusoidal modulation of its input signal will also be discussed briefly. Before covering these areas, however, it is important to point out the absolute limits on steady-state tracking by a PLL.

The fundamental limitation on a PLL's ability to track an input signal is the frequency range of its VCO. Clearly, the VCO of a PLL must be designed so that all expected inputs fall well within its frequency range. This limitation aside, however, since all practical PLL's include at least one integrator in the loop filter, a PLL should be able to track any signal within its VCO's range. The output of the phase detector can be integrated to whatever control voltage is necessary at the input of the VCO. Without this integrator, the PLL's tracking range would be further limited by the range of output voltage possible from the phase detector, as well as any attenuation by the loop filter.

A number of assumptions are made for the remainder of this section. First, it is assumed that all inputs to the PLL remain within its steady-state tracking range. It is also assumed that the PLL starts out fully locked to the input signal. Finally, the analysis focuses on a PLL which includes an active filter of the type shown in Figure 3.7(b). To further simplify the presentation, it is assumed that the zero for this loop filter was chosen to be equal to a quarter of the PLL's bandwidth, making the system critically damped. The error responses that are looked at below would be different for different dampings, however this case should be sufficient to explain the basic behavior.

The key in determining whether a change in the input signal causes the loop to lose lock is to look at the phase error this signal generates within the loop. If the change causes

a phase error which is greater than the linear range of the phase detector, the loop's behavior is no longer linear, and it is considered to have lost lock. To determine if this happens, the transfer function for phase error in the system must first be found, beginning with

. . . . . . . . . . .

$$H_{e}(s) = \frac{\theta_{e}(s)}{\theta_{i}(s)}$$

(3.27)

Recalling Equations (3.2) and (3.13),

$$\theta_{e}(s) = \theta_{i}(s) - \theta_{o}(s) = \theta_{i}(s) - H(s)\theta_{i}(s)$$

(3.28)

$H_e(s)$  may be rewritten as

$$H_{e}(s) = 1 - H(s)$$

(3.29)

Using this equation, the transfer function for phase error may also be rewritten in terms of the forward gain of the PLL.

$$H_{e}(s) = \frac{1}{1+G(s)}$$

(3.30)

Using this equation, the phase error transfer function for the PLL under consideration may be determined as

$$H_{e}(s) = \frac{s^{2}}{s^{2} + Ks + Kw_{z}}$$

(3.31)

This transfer function may now be used to find the error signal for any input of interest. Multiplying the Laplace transform of the input signal by this transfer function and then finding the inverse Laplace transform will produce a time domain description of the error signal in the PLL. One may then look at this error signal to see if it exceeds the linear range of the PLL.

The three major changes in the input signal which are considered when looking at a PLL's error response are a step in phase, a step in frequency, and a ramp in frequency. The Laplace transforms for these three input conditions are  $\Delta\theta/s$ ,  $\Delta\omega/s^2$ , and  $\Delta\omega/s^3$ , respectively. The response of the example PLL, where  $\omega_z = K/4$ , has been calculated for

| Input               | Phase Step                                                                         | Frequency Step                              | Frequency Ramp                                                                             |

|---------------------|------------------------------------------------------------------------------------|---------------------------------------------|--------------------------------------------------------------------------------------------|

| $\theta_{i}(s)$     | Δθ/s                                                                               | $\Delta \omega / s^2$                       | Δώ/s <sup>3</sup>                                                                          |

| $\theta_{e}(s)$     | $\frac{\Delta\theta \text{ s}}{\text{s}^2 + \text{Ks} + \text{K}\omega_z}$         | $\frac{\Delta\omega}{s^2 + Ks + K\omega_z}$ | $\frac{1}{s} \frac{\Delta \dot{\omega}}{s^2 + Ks + K\omega_z}$                             |

| $\theta_{e}(t)$     | $\Delta \theta \left(1 - \frac{\mathrm{Kt}}{2}\right) \mathrm{e}^{-\mathrm{Kt}/2}$ | $\Delta \omega \cdot t e^{-Kt/2}$           | $\frac{\Delta\dot{\omega}}{K^2/4} \left(1 - \left(1 + \frac{Kt}{2}\right)e^{-Kt/2}\right)$ |

| θ <sub>e</sub> (∞)  | 0                                                                                  | 0                                           | $\frac{\Delta\dot{\omega}}{K^2/4}$                                                         |

| $\theta_{e,max}(t)$ | Δθ                                                                                 | $0.74 \frac{\Delta \omega}{K}$              | $\frac{\Delta\dot{\omega}}{K^2/4}$                                                         |

Table 3.2 - Error Response of a PLL

each of these input conditions, and the results are shown in Table 3.2. Along with the time domain equations which describe the error signal for each of these inputs, this chart also shows the maximum error seen for each of these inputs and the steady state error for each of these inputs. The steady state errors were calculated using the final value theorem.

$$\lim_{t \to \infty} y(t) = \lim_{s \to 0} s Y(s)$$

(3.32)

As was stated before, in order for the PLL to stay in lock, the maximum phase error seen for a change in the input must not exceed the linear range of the phase detector.

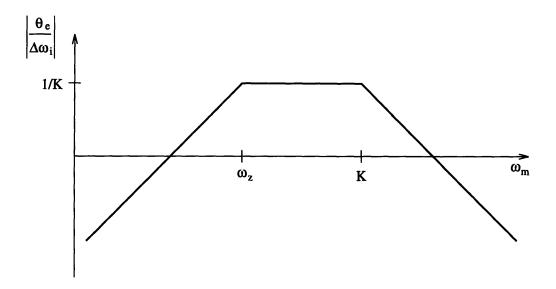

The other input signal which is generally of interest is an input with a sinusoidally modulated frequency.

$$\Delta \omega_{i} = \Delta \omega \sin \left( \omega_{m} t \right) \tag{3.33}$$

For this input signal, it is useful to find a transfer function relating phase error directly to the change in frequency of the input. This may be done easily by modifying the phase error transfer function.

$$\frac{\theta_{\rm e}}{\Delta\omega_{\rm i}} = \frac{\theta_{\rm i}}{\Delta\omega_{\rm i}}\frac{\theta_{\rm e}}{\theta_{\rm i}} = \frac{1}{\rm s}H_{\rm e}$$

(3.34)

Figure 3.9 - Transfer function for sinusoidal modulation of input frequency.

Thus, for the PLL being considered here, the new transfer function is

$$H_{we}(s) = \frac{\theta_e(s)}{\Delta \omega_i(s)} = \frac{s}{s^2 + Ks + K\omega_z}$$

(3.35)

Assuming that K is much larger than  $\omega_z$ , an approximation of this transfer function is shown in Figure 3.9. Looking at this Bode plot and remembering that the transform of the input will consist of an impulse at both  $\omega_m$  and  $-\omega_m$ , one can see that the error signal will simply be a sinusoid whose amplitude is modulated by the gain of this new transfer frequency at  $\omega_m$ .

$$\theta_{e}(t) = |H_{we}(\omega_{m})| \Delta \omega \sin(\omega_{m}t)$$

(3.36)

In this case, the loop should stay in lock as long as  $|H_{we}(\omega_m)| \Delta \omega$  is within the phase detector's linear range.

At this point, the behavior of the PLL within its linear range and the limits of this linear range should be fairly clear. The question now is how the PLL gets to this linear range, both initially and when it has been pushed out by some change in the input signal.

#### **3.6 Frequency Acquisition**

The process by which a PLL locks to an input signal occurs in two stages. First, the PLL matches the frequency of its output to the input, and then it matches its phase.

The first stage of this process is called frequency acquisition, and unlike the second stage, it is completely non-linear. While not going deep into the complexity of this topic, this section will describe the basic frequency acquisition process for a PLL which uses a 3-state phase detector and will point out the major design considerations regarding frequency acquisition for this kind of PLL.

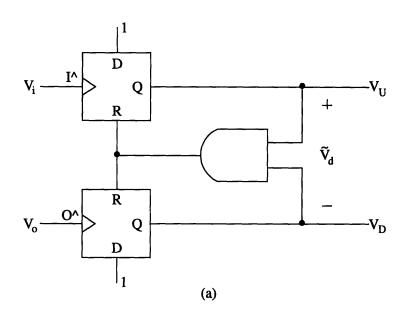

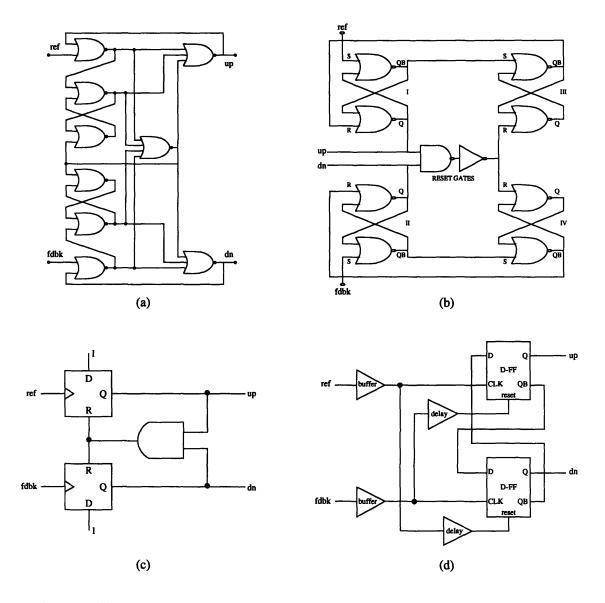

Frequency acquisition for a PLL with a 3-state phase detector is considered for two reasons. First, the PLL designed for this thesis uses this kind of phase detector. Second, this type of phase detector, unlike most other phase detectors, is sensitive to frequency as well as phase. For this reason, a 3-state phase detector is also often referred to as a phase frequency detector. PLL's which use other types of phase detectors generally require some additional frequency acquisition circuitry which is not necessary here.

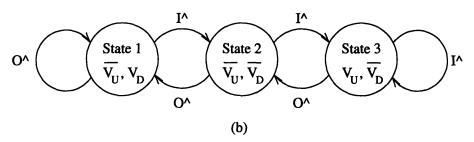

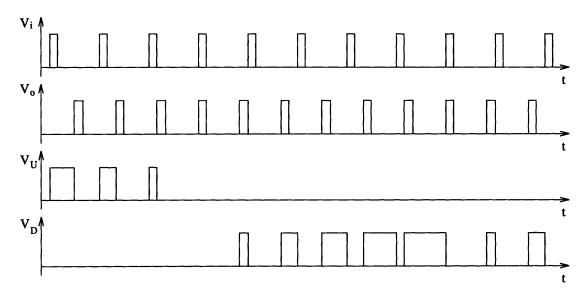

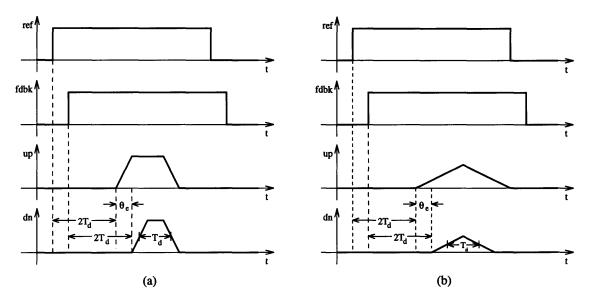

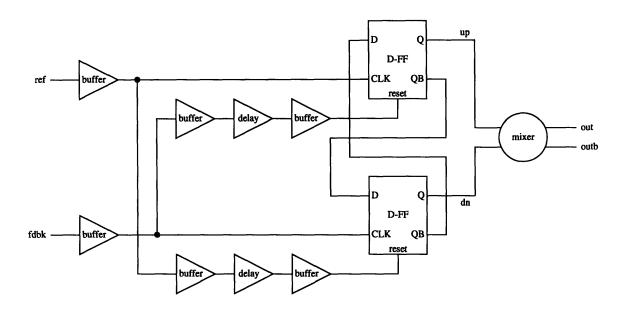

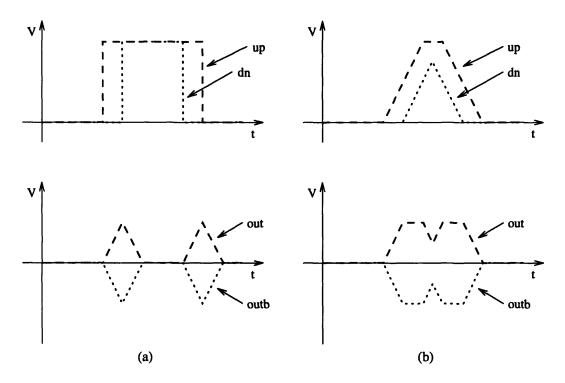

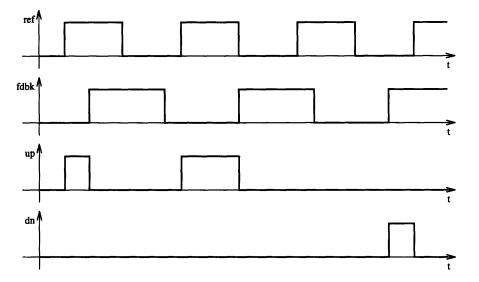

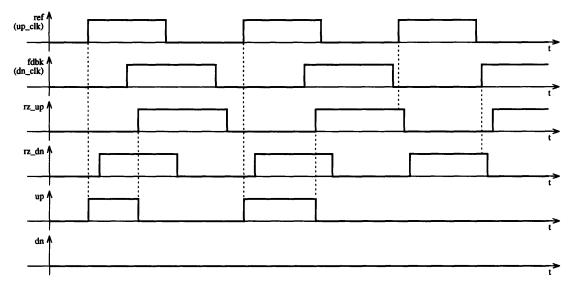

In order to look at the behavior of a 3-state phase detector, a sample architecture for this circuit and a state diagram illustrating its behavior are shown in Figure 3.10. The key feature of this phase detector, which differentiates it from other phase detectors, is that its output is edge-triggered. This feature causes its output to be discrete rather than continuous. Other phase detectors, such as a multiplier, produce a constant voltage that is proportional to the phase error. For the 3-state phase detector, the output for the signal which is being asserted will look like a square wave whose duty cycle is proportional to the phase error. This difference requires a rewriting of the linear equation for a phase detector. Now, it is the average voltage out of the phase detector,  $\tilde{v}_d$ , that is proportional to the phase error.

$$\tilde{\mathbf{v}}_{d} = \mathbf{K}_{d} \left( \boldsymbol{\theta}_{i} - \boldsymbol{\theta}_{o} \right) \tag{3.37}$$

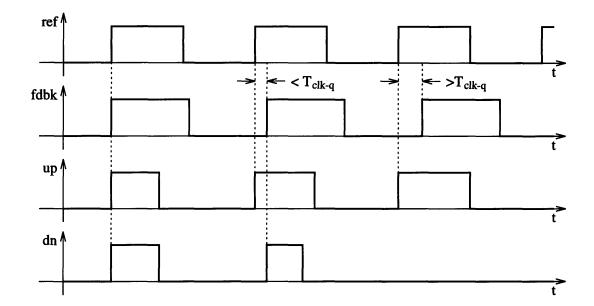

An example set of outputs for this phase detector are shown in Figure 3.11.

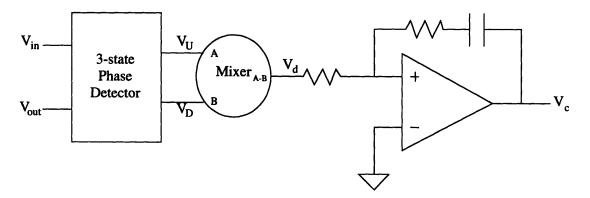

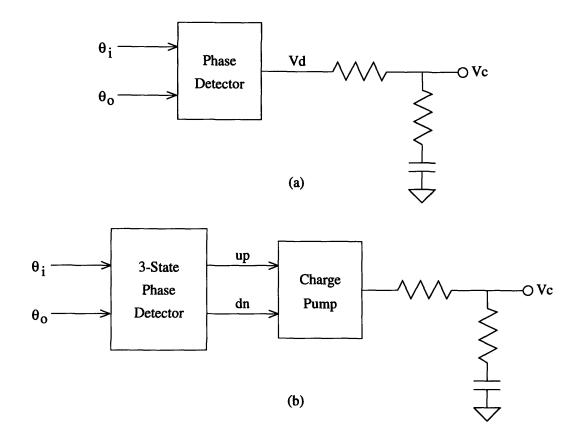

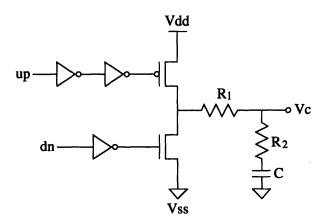

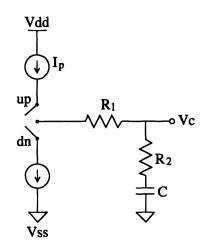

As shown in the sample architecture, another feature of this type of phase detector is that there are two outputs out of the phase detector, one for an up signal and one for a down signal. This design therefore requires a different type of the connection to the loop filter, which in most cases means including a charge pump circuit between the phase detector and the loop filter. The charge pump consists essentially of two switches, one connecting the loop filter node to ground, and the other connecting it to the power supply. Assuming that the VCO output frequency increases for increasing control voltages, when

Figure 3.10 - Sample architecture (a) and state diagram (b) for 3-state phase detector.

Figure 3.11 - Example set of outputs for 3-state phase detector

the up signal from the PLL turns on, the switch connected to the power supply is turned on. This causes charge to be pumped into the loop filter circuit, charging its capacitor. Conversely, charge is pulled off the loop filter capacitor when the down signal is asserted by turning on the switch connected to ground. As the state diagram shows, the phase detector is designed so that both signals are never asserted at the same time.

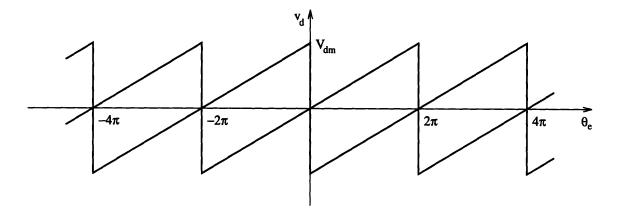

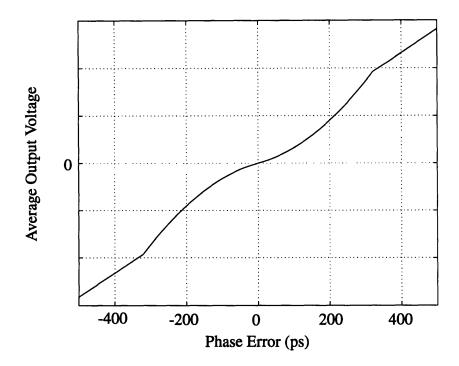

Another advantage of this phase detector is its wide linear range. As the output characteristic shown in Figure 3.12 illustrates, this detector has a range of  $\pm 2\pi$ . The overlapping nature of the output characteristic points out another feature of this phase detector. This phase detector has memory of what the previous inputs were that affects the next output. Also, note that this output characteristic represents a mixed signal of the two outputs,  $V_u - V_d$ .

This phase detector's sensitive to frequency can be understood by considering again the sample architecture and the state diagram which are shown in Figure 3.10. Assume that asserting  $V_u$  causes the output frequency of the VCO to increase, and that  $V_u$ will be asserted for cases where the phase of the input is ahead of the phase of the output. Next, consider the case where the frequency of the input signal is higher than the frequency of the PLL's output signal. In this case, the phase detector will see significantly more rising edges from the PLL's input, R^, than rising edges from the PLL's output, V^. This means that even if the phase detector starts out in State 1, it will quickly be pushed so that it oscillates back and forth being States 2 and 3. By keeping the phase detector in these two states, only the Vu signal will ever be asserted. This will cause the output

Figure 3.12 - Output characteristic of a 3-state phase detector

frequency of the VCO to increase, pushing the PLL towards frequency lock. Since this system is symmetric, the reverse behavior is true when the output frequency is higher than that of the input signal.

In designing a PLL, there is another critical design consideration that must be kept in mind in regard to frequency acquisition, and that is acquisition time. The amount of time a designer can allow a PLL for this process depends on the application. Looking at a standard active loop filter, such as the one shown in Figure 3.7(b), one sees that there are two components to the VCO control voltage, the voltage across the resistor,  $V_r$ , and the voltage across the capacitor,  $V_c$ . The voltage across the resistor can change very rapidly, however, it has a limited range. On the other hand, the voltage across the capacitor changes slowly, but is capable of spanning the whole input range of the VCO. From this viewpoint, frequency acquisition may be considered complete when the voltage across the capacitor has been moved close enough to the required control voltage that the resistor can provide the rest. Thus, to determine an equation for acquisition time, one must look at two things, the limit on resistor voltage and the rate at which charge can be moved to or from the loop filter capacitor.

The frequency tuning limit for the loop filter resistor is determined by the phase detector's linear range and the PLL's bandwidth. The equation for this may be derived by stepping through the conditions required to generate the maximum frequency deviation possible from the resistor voltage. The starting equation for this maximum frequency deviation is

$$\Delta \omega_{\rm rm} = K_0 V_{\rm m} \tag{3.38}$$

where  $V_{rm}$  is the maximum voltage that may be seen across the loop filter resistor. Remembering that this voltage is proportional to the maximum phase detector output voltage,  $V_{rm} = K_h V_{dm}$ , the equation becomes

$$\Delta \omega_{\rm rm} = K_{\rm h} K_{\rm o} V_{\rm dm} \tag{3.39}$$

where  $V_{dm} = K_d \theta_{em}$ , so that

$$\Delta \omega_{\rm rm} = K_{\rm d} K_{\rm h} K_{\rm o} \theta_{\rm em} = K \theta_{\rm em}$$

(3.40)

Thus for a PLL with a 3-state phase detector, the maximum frequency deviation possible from the resistor is

$$\Delta \omega_{\rm rm} = 2\pi K \tag{3.41}$$

When calculating the acquisition time, this value may be subtracted from the initial frequency error. The remaining frequency error must be compensated for by adjusting the capacitor's voltage.

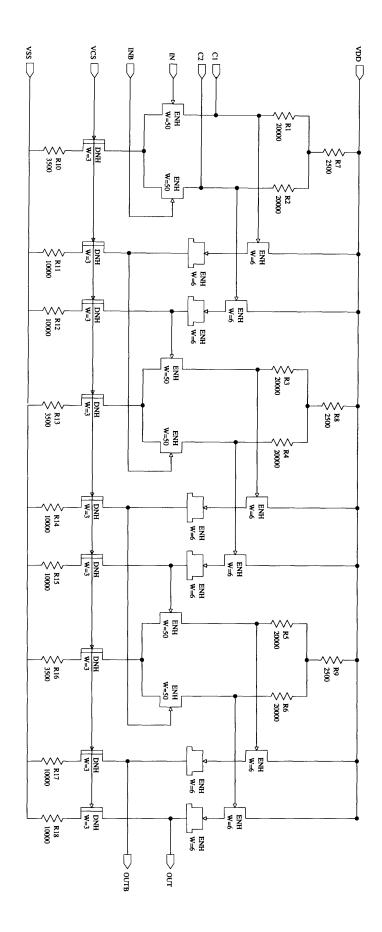

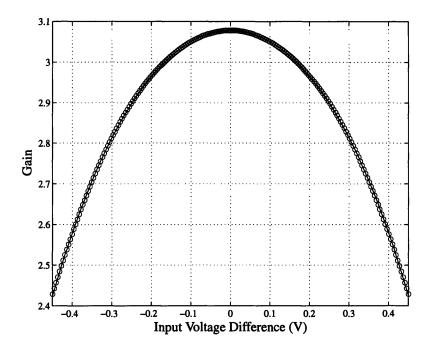

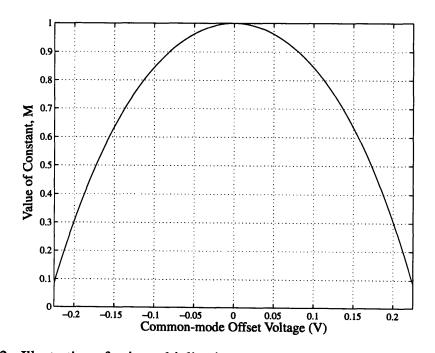

How fast the capacitor's voltage changes depends on the average current the capacitor sees during the tuning process. Within the PLL built for this thesis, the two output signals from the 3-state phase detector are mixed into a single signal, and this signal is connected directly to the input of the loop filter, rather than indirectly through a charge pump. This means that the current the loop filter capacitor sees is simply proportional to the voltage out of the phase detector divided by the input resistor of the loop filter. A simplified version of the architecture used is shown in Figure 3.13.

The question now becomes what voltages will be seen from the phase detector. For a 3-state phase detector, it is possible to place a conservative bound on what the average output voltage will be during this process. Consider a case where the frequency of the output is slightly higher than that of the input. If these two signals were to stay at the same frequency, the phase error between the input and output would slowly, but repeatedly grow from 0 to  $-2\pi$ . The average phase error would simply be  $-\pi$ . Thus, the average voltage out of the phase detector would be

Figure 3.13 - Simplified illustration of phase detector connection to loop filter.

$$\tilde{v}_{d} = -\pi K_{d} = \frac{-V_{dm}}{2}$$

(3.42)

It can be shown that as the frequency difference between the input and output grows, the average voltage out of the phase detector also grows. To get an idea of how this works, consider an output signal that is more than twice the frequency of the input signal. Since V<sup>^</sup> edges come at more than twice the rate of R<sup>^</sup> edges, the phase detector will have to spend at least half its time in State 3 of the state diagram shown in Figure 3.10. The average voltage out of the phase detector works out to be  $-3V_{dm}/4$ . On the other hand, whatever the frequency error is, the average voltage never goes below  $-V_{dm}/2$ . Thus, for the analysis here, this value serves as a conservative bound that is sufficient.

The equation for acquisition time may now be derived. First, frequency error within the system is defined via the equation

$$\omega_{\rm e} = \left| \omega_{\rm o} - \omega_{\rm i} \right| \tag{3.43}$$

with the initial frequency error in the system being labeled  $\omega_{eo}$ . The equation for the component of the output frequency due to the capacitor's voltage is

$$\omega_{\rm c} = K_{\rm o} V_{\rm c} \tag{3.44}$$

Assuming that the output frequency starts out above that of the input,  $\omega_c$  is initially equal to  $\omega_i + \omega_{eo}$ , while at the end of frequency acquisition it is equal to  $\omega_i + \omega_{rm}$ . Remembering that  $dV_c/dt = i/C$  and  $i = \tilde{v}_d/R_1$ ,

$$\frac{d\omega_{\rm c}}{dt} = K_{\rm o} \frac{dV_{\rm c}}{dt} = \frac{K_{\rm o} \tilde{v}_{\rm d}}{R_{\rm I} C}$$

(3.45)