## **A Lisp Oriented Architecture**

by

John W.F. McClain

Submitted to the Department of Electrical Engineering and Computer Science

in partial fulfillment of the requirements for the degrees of

Master of Science in Electrical Engineering and Computer Science

and

Bachelor of Science in Electrical Engineering

at the

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

September 1994

© John W.F. McClain, 1994

The author hereby grants to MIT permission to reproduce and to distribute copies of this thesis document in whole or in part.

Signature of Author ..... Department of Electrical Engineering and Computer Science August 5th, 1994

A. J. M.

## A Lisp Oriented Architecture by John W.F. McClain

Submitted to the Department of Electrical Engineering and Computer Science on August 5th, 1994, in partial fulfillment of the requirements for the degrees of Master of Science in Electrical Engineering and Computer Science and Bachelor of Science in Electrical Engineering

#### Abstract

In this thesis I describe LOOP, a new architecture for the efficient execution of programs written in Lisp like languages. LOOP allows Lisp programs to run at high speed without sacrificing safety or ease of programming. LOOP is a 64 bit, long instruction word architecture with support for generic arithmetic, 64 bit tagged IEEE floats, low cost fine grained read and write barriers, and fast traps. I make estimates for how much these Lisp specific features cost and how much they may speed up the execution of programs written in Lisp.

Keywords: Lisp, LIW, computer architecture.

Thesis Supervisor: Thomas F. Knight Jr. Title: Principal Research Scientist

## Acknowledgments

First, I would like to thank those who shaped me long before knew Lisp: my parents John and Kay, who supported and nurtured me all these years. More recently, my wife, Jennifer, and her parents Ed and Paulette Schwartz have also helped me through the difficult parts of being a graduate student.

In addition to my family, I also thank my good friends Matt Calef, Alex Dogon, Mark Donelan, Andrew Draper, and John Huebner, who helped me through high school and in the world beyond. Also, thanks to Mark's wife Anne, and Maxwell and Natasha.

More recently, many people have had a direct influence on the thesis itself. I had many hours of of interesting computer architecture, operating system, and compiler discussions with André DeHon who also kept me from making LOOP the CISCest architecture since the Intel 432 or Burroughs' B6500. I will miss these discussions and 7th AI lunches the most.

Thanks also to Olin Shivers who pointed me towards the IBM VLIW research and wrote one of the more enjoyable PhD. theses [43] I read in the course of my research.

Robert MacLachlan shared two unpublished manuscripts that described some of his ideas on computer architectures for Lisp.

Thanks to Robert Thau for being the local heretic<sup>1</sup> and introducing the AI Lab to the World Wide Web which is destined to become one of the greatest research tools of all time. He also helped me figure out why the user cache was really not needed.

John Mallery had a long talk with me one night and gave me the push I needed to get out of my first set of thesis doldrums.

Moon [36] and Hauck and Dent's [19] articles helped me realize that computer architectures don't all need 32 registers and a pair of memory instructions and got me thinking about how a modern Lisp Machine might look in the first place.

Finally thanks to Tom Knight, my thesis advisor, who suggested the idea of turning the answerer to that question into a project in the first place.

<sup>&</sup>lt;sup>1</sup>Which I mean in the best possible way.

## Contents

| 1 | Intr       | Introduction |                                   |      |  |  |

|---|------------|--------------|-----------------------------------|------|--|--|

|   | 1.1        | How I        | Disp is Different                 | . 9  |  |  |

|   |            | 1.1.1        | Dynamic Typing                    | . 9  |  |  |

|   |            | 1.1.2        | Memory Allocation                 | . 10 |  |  |

|   |            | 1.1.3        | Garbage Collection                |      |  |  |

|   |            | 1.1.4        | Pointer Intensive Data Structures |      |  |  |

|   |            | 1.1.5        | Higher Trap Frequency             | . 11 |  |  |

|   |            | 1.1.6        | More Function Calls               | . 11 |  |  |

|   |            | 1.1.7        | Unpredictable Control Flow        | . 11 |  |  |

|   | 1.2        | Past V       | Work                              | . 12 |  |  |

| 2 | Arc        | hitectı      | ıre                               | 15   |  |  |

|   | 2.1        | Archit       | ecture Data Types                 | . 15 |  |  |

|   |            | 2.1.1        | Tag Field                         | . 16 |  |  |

|   |            | 2.1.2        | Data Field                        | . 16 |  |  |

|   | <b>2.2</b> | Storag       | ge Model                          | . 18 |  |  |

|   |            | 2.2.1        | Register File                     | . 18 |  |  |

|   |            | 2.2.2        | Main Memory                       | . 18 |  |  |

|   |            | 2.2.3        | Special Purpose Registers         | . 19 |  |  |

|   | <b>2.3</b> | Instru       | ctions                            | . 20 |  |  |

|   |            | 2.3.1        | Operates                          | . 21 |  |  |

|   |            | 2.3.2        | Memory Operations                 | . 25 |  |  |

|   |            | 2.3.3        | Control Operation                 | . 28 |  |  |

|   |            | 2.3.4        | Wide Operations                   | . 30 |  |  |

|   |            | 2.3.5        | Instruction Format                | . 33 |  |  |

|   | 2.4        | Memo         | ry Management                     | . 35 |  |  |

|   | <b>2.5</b> | Traps        |                                   | . 35 |  |  |

| 3 | Not        | es on ]      | Implementation                    | 37   |  |  |

|   | 3.1        | Area I       | Estimates                         |      |  |  |

|   |            | 3.1.1        | LOOP Without Lisp Support         | . 38 |  |  |

|   |            | 3.1.2        | Cost of Lisp Support On Chip      |      |  |  |

|   | 3.2        | Pipe I       | jine                              | . 43 |  |  |

|   |            | 3.2.1        | Fetch Stage                       |      |  |  |

|   |            | 3.2.2        | Decode                            | . 44 |  |  |

|   |            | 3.2.3 Execute                              |  |  |  |  |

|---|------------|--------------------------------------------|--|--|--|--|

|   |            | 3.2.4 Write Back 45                        |  |  |  |  |

|   | <b>3.3</b> | Memory 45                                  |  |  |  |  |

|   |            | <b>3.3.1</b> Tags                          |  |  |  |  |

|   |            | 3.3.2 Knapsacks                            |  |  |  |  |

|   |            | 3.3.3 Wide Loads and Stores                |  |  |  |  |

| 4 | Evaluation |                                            |  |  |  |  |

|   | 4.1        | Tag Support         49                     |  |  |  |  |

|   |            | 4.1.1 Tag Checking and Generation          |  |  |  |  |

|   |            | 4.1.2 Extra Bits for Tag Field             |  |  |  |  |

|   | 4.2        | Fine Grained Memory Barrier Support        |  |  |  |  |

|   | 4.3        | Multiple Contexts to Support Fast Traps 54 |  |  |  |  |

|   | 4.4        | Allocating Stores with Subblock Valid Bits |  |  |  |  |

|   | 4.5        | What Else Can the Area be Used For?        |  |  |  |  |

|   |            | 4.5.1 More Cache                           |  |  |  |  |

|   |            | 4.5.2 Extra Functional Units               |  |  |  |  |

| 5 | Conclusion |                                            |  |  |  |  |

|   | 5.1        | Future Work                                |  |  |  |  |

# List of Figures

| 2-1 | Basic Machine Word             | 15 |

|-----|--------------------------------|----|

| 2-2 | Detailed View of Tag Field     | 16 |

| 2-3 | Format of A1 and A2 Operations | 34 |

| 2-4 | Format of M Operation          | 34 |

| 2-5 | Format of C Operation          | 34 |

|     |                                |    |

## Chapter 1

## Introduction

This thesis explores the possibilities for the design of a new Lisp oriented architecture. One can get good Lisp performance on stock hardware but you often have to twist your programming style and/or disable safety to get this performance, eliminating much of the reason for programming in Lisp in the first place. The architecture described in this thesis attempts to let programmers get good performance without a lot of declarations or turning safety off. Although I have not hesitated to add features that only help Lisp the architecture is not that different from those found in modern main line micro-processors.

The question of what makes a processor good for Lisp is interesting because Lisp like languages are becoming more important as programs get more complex and other languages begin to look more and more like Lisp. Also there has been little research in the past seven years into what makes a good Lisp processor, but in that time the fields of VLSI chips design and computer architecture have undergone tremendous changes.

The proposed architecture,  $LOOP^1$  is a four wide long instruction word (LIW) processor. It is not expected that implementations will do a lot of dynamic scheduling. Instead we rely on the compiler to find and exploit most of the instruction level parallelism. We also rely on the compiler for safety when its felt that this does not compromise speed.

## **1.1 How Lisp is Different**

Lisp differs from C and FORTRAN in several important ways. It is these differences which make current main line computer architectures a somewhat poor target for Lisp.

## 1.1.1 Dynamic Typing

Variables in most Lisps are not statically typed. Instead of associating the type with the variable it is associated with the data value. As a result Lisp programs have

<sup>&</sup>lt;sup>1</sup>Which stands for Lisp Oriented Processor.

to make many runtime type checks. This hits integers in Lisp systems particularly hard since in general a type check needs to be made before every integer operation, potentially doubling or tripling the time it takes to perform simple integer operations<sup>2</sup>. The type information also has to be stored somewhere. Floating point computations are hit very hard by this second problem, since the IEEE floating point format makes no allowance for type tags. Lisp implementations often have to resort to storing floats on the heap and referencing them by pointer instead. Both problems can be attenuated with declarations or by turning safety off, however, both options remove much of the benefit of for programing in Lisp in the first place. We address these problems in the traditional Lisp Machine [29, 36] way by adding hardware to make type checks in parallel with machine operations and by making the words wider than normal to accommodate type tags.

#### 1.1.2 Memory Allocation

Lisp programs are often written in a functional style which results in more memory allocation than most C and FORTRAN programs. C and FORTRAN programs tend to use the same memory over and over again under explicit programmer control. Diwan, Tarditi, and Moss [14] find that allocating stores with subblock valid bits can significantly increase the effectiveness of data caches in the face of allocation intensive programs. We adopt their findings by giving LOOP both allocating stores and subblock valid bits.

### **1.1.3 Garbage Collection**

Lisp programs can be written in a functional style because most Lisp systems have a garbage collector that periodically goes through memory and finds all data that can still be reached and separates it from the "dead" data. Basic garbage collectors have bad locality and/or fragment memory, cause frequent pauses in program execution which can be annoying to the user, and add significant runtime overhead. The runtime cost and locality concerns can be reduced by generational garbage collectors [35]. Unfortunately generational garbage collectors require associating a "barrier" with every non-allocating heap store. The pauses can be dealt with by making the collector "incremental" but this requires associating a barrier with every heap read and write, which adds substantial runtime overhead. LOOPs translation look aside buffer provides support for low cost, fine grained read and write barriers which can be used to implement generational and incremental garbage collectors at greatly reduced expense.

<sup>&</sup>lt;sup>2</sup>Actually its not uncommon in unoptimized Lisp systems/programs to find a simple integer add taking many 10s of instructions.

## **1.1.4 Pointer Intensive Data Structures**

Garbage collectors also make it easier for programers to use pointer intensive and dynamic data structures, resulting in an increased demand for memory bandwidth. LOOP provides wide loads and stores that can fetch or write 2 or 4 words at a time. Additionally I suggest a hardware feature that may interact with copying generational garbage collectors to increase the on chip hit rate and increase available memory bandwidth.

## 1.1.5 Higher Trap Frequency

Unlike many main line computer systems in which traps are only expected to handle infrequent and heavy weight events like page traps, or terminal events like overflows and memory access errors, many Lisp systems use traps to handle more frequent, light weight events. For example, in many Lisp systems when an integer overflows the capacity of the basic machine word the system replaces it with an arbitrary precision integer (aka "bignum"). The cost of creating such an integer is much less than taking a page trap. LOOP adopts many of the ideas from Johnson [24] to support fast trap handling and instruction emulation including shadow registers and user trap handlers. LOOP also provides multiple register contexts so registers don't have to be saved/restored on traps.

## 1.1.6 More Function Calls

Lisp programs generally have more function calls than C and FORTRAN programs. However, I have been reluctant to spend time trying to come up with hardware or architectural features to optimize procedures calls. Part of this reluctance come from the fact that Lisp procedure calling conventions and the algorithms that implement them can be very complex, and it is not at all clear which is the "best" one that deserves to be cast in silicon. Another problem is that different flavors of Lisp have very different features in there calling conventions. Common Lisp [46] is lexically scoped, has rest, optional, and keyword parameters. Scheme [8] is also lexically scoped but has only rest parameters. Yet Scheme also has call/cc which puts unique constraints on procedure calling convention. An architectural feature that supports one well is likely to be unhelpful for the other. And if we do find a feature that helps Common Lisp and Scheme it is unlikely to help GNU Emacs Lisp [31] which has rest and optional parameters but uses dynamic scoping.

## 1.1.7 Unpredictable Control Flow

Because most Lisps have first class procedures and/or generic function based object systems, control flow analysis is very difficult in Lisp programs. LOOP does very little to address this, in fact because its an LIW machine and statically scheduled the problem gets worse not better.

In addition to the features that help Lisp specifically LOOP has several features

that should make programs faster in general. I have not emphasized these in the text but I will mention them briefly here. LOOP gives the program a lot of control over the cache allowing the program to use the cache in a pro-active manner. LOOP supports speculative execution through a mechanism that allows most exceptions to be handled by producing a specialty tagged object instead of passing control to an exception handler. LOOP also has several performance counters to support profiling.

In the rest of this chapter we will talk about past Lisp oriented architectures. In chapter 2 we describe LOOP's instruction set architecture. In chapter 3 we talk about how LOOP might be implemented and make some estimates of how big it might be in terms of chip area and how much the individual Lisp features cost. In chapter 4 we evaluate how much performance improvement these various Lisp features might buy us. Finally in chapter 5 we make some concluding remarks and suggest some avenues for future research.

## **1.2 Past Work**

This first machines designed from the ground up to run Lisp were started in the early 1970s at MIT. The second of these machines, the CADR, inspired a number of commercial spin-offs by LISP Machines Inc., Texas Instruments, and Symbolics. All of these machines were stacked based, tagged architectures with support for generic operations. The implementations were heavily microcoded. Many of them used cdr coding, forwarding pointers, included hardware support for incremental garbage collection, and had built in array bounds checking [29, 36].

During the late 70s XEROX PARC developed the Dorado as a follow on to the their Alto computer [38]. It was heavily micro-pipelined, microcoded and had a 16 bit word size at the microcode level. It had a fixed number of microcode *tasks* each with a fixed priority. Each cycle the system would switch to the active microcode task with the highest priority. Most of the tasks were used to implement I/O device handlers with most devices having one task each. Most of the machine's registers were duplicated so each microcode task had its own copy, making it practical to switch tasks every cycle. The lowest priority microcode task implemented an emulator for language specific instruction sets. There were instruction sets for BCPL, Mesa, Interlisp, and Smalltalk. About halfway through the project a instruction fetch unit was added which significantly improved the speed of instruction set emulation.

Since these machines were developed very few projects have been started with the aim of developing a new Lisp oriented architecture. One of the most recent attempts was the SPUR [50] architecture developed at the University of California, Berkeley in the mid 80s. The SPUR is a typical early RISC architecture with some additional features to support Lisp. Like most RISC architectures the SPUR, is a load/store machine with a large register file and simple instructions that do not have to be microcoded, are easy to pipeline and mostly can complete in a single cycle. Unlike most RISCs it has tag bits with some support for generic operations; it also has register windows which are provided to make procedure calls faster. Notably the SPUR had a separate floating point unit with separate floating point registers making full generic arithmetic difficult.

I have also recently been informed of a Lisp computer architecture effort in the University of Indiana department of Computer Science, but no details are available at this time.

## Chapter 2

## Architecture

LOOP is a 64 bit, Long Instruction Word (LIW), load/store, tagged architecture. Each instruction can specify up to 4 operations to be executed in parallel. Each of these operations is similar in complexity to instructions found in current RISC microprocessors.

We use the word "trap" to mean traps, exceptions, or interrupts. We use the phrase an "exception is raised" to indicate an exceptional condition has been detected and one of two course of action will be taken, either control will pass to the handler for that exception or a specially tagged error object will be produced as the result of this operation. We use the phrase "an exception is taken" to indicate that an exceptional condition had been detected and control will pass to the handler for that exception.

An "instruction" in the LOOP architecture specifies several "operations" that will be executed in parallel and are all referred to by the same PC value. Because the different operations in an instruction are largely orthogonal with respect to each other we will often refer to them in the same way one might refer to instructions in a non-LIW architecture.

## 2.1 Architecture Data Types

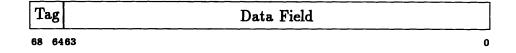

The basic LOOP data object is the machine word. Each word has two parts, a 64 bit data field and a 5 bit tag field. The tag field's size is nearly invisible at the architectural level because it is not directly addressable (see section 2.2.2 for details of the memory model.) Figure 2-1 shows the format of the basic machine word.

Figure 2-1: Basic Machine Word

| Ρ  | Т  | уре | Т  |

|----|----|-----|----|

| 68 | 67 | 65  | 64 |

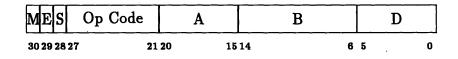

Figure 2-2: Detailed View of Tag Field

### 2.1.1 Tag Field

Four bits of the the tag field are used for the "type tag." They define how the data field is to be interpreted by the hardware. The hardware is responsible for checking if the types of an operation's operands are compatible with the operation and each other, raising an exception if they are not. The hardware is also responsible for generating the correct tag for the result.

The fifth bit is the "trap bit," most operations raise an exception when they operate on words which have their trap bit set. Only a WRTRAP operation will create a word with its trap bit set.

Figure 2-2 shows a detailed view of the tag field, P is the pointer bit, type is the remainder of the type field, and T is the trap bit.

#### 2.1.2 Data Field

The architectural interpretation of the data field depends on the value of the type tag. Currently there are twelve hardware types defined. The lead bit of the type tag indicates if the word is pointer or non-pointer data.

#### **Non-pointer Data**

If the lead bit of the type tag is 0 then the word is non-pointer data. There are five types of architecturally defined non-pointer data.

**Integer** A type tag of 0 indicates the data field is a 64 bit twos complement integer. Predicate operations use integer one and zero to represent true and false respectively. When extracted from their words tags are represented as integers. Some instructions treat integers as unsigned.

**IEEE Float** A type tag of 1 indicates the data field is a 64 bit IEEE double precision floating point number.

Instruction A type tag of 2 indicates the data field holds part of an instruction. Instructions take two words (see section Section 2.3 Instruction Format for details.)

Untyped A type tag of 3 indicates the data field holds 64 bits of data that as yet does not have a type associated with it. Most operations raise an exception if performed on untyped words.

**Error Object** A type tag of 4 indicates the data field holds an error object. Error objects are created by the hardware when an exception is raised but not taken. Most operations raise an exception if they are performed on error objects. The error object type tag is also used for uninitialized words.

**Extra Non-Pointer Type Tags** Type tags 5, 6, and 7 are reserved for future use. Hardware should treat words with these tags as error objects.

Most of the possible uses for these tags are for variants of instructions. LIW processors have a problem with code density when the code has low instruction level parallelism. One of these tags could be allocated to be an instruction type whose individual operations would be executed serially, not in parallel.

MacLachlan [34] suggests the idea of "millicode" routines. One of these tags could be allocated to be an instruction type that is treated as a macro. When fetched it would be expanded into a sequence of 2 - 4 instructions, possibly replacing some or all of the source fields of the first instruction and some or all of the destination fields of the last instruction with bit fields from the original macro instruction. Branches would be allowed out of the macro, but not into it since conceptually the expanded instruction would all be at the same PC. Whether millicode would be useful would depend highly on the low level details of the compiler and runtime system. At least the first pass of a compiler and runtime system for LOOP would have to be written before this idea is fully flushed out. Knowing that such a millicode feature could be useful it should be possible to leave hooks for a "millicode expander" at the beginning of a design.

#### **Pointer Types**

If the leading bit of the type tag is 1 then the word holds a pointer to a word or double word. All memory reference instructions except STAx and LDAx (section 2.3.2 Memory Operations) mask out the low 3 bits of word pointers (low 4 bits for double word pointers) before adding them to the offset, which has its low 3 bits masked out, to form the effective address that is presented to the memory system. Operate operations (described in section 2.3.1) interpret all pointers as 64 bit byte pointers.

**Basic Pointer** A type tag of 8 indicates the data field is a word pointer.

**Compound Number Pointer** A type tag of 9 indicates the data field is a word pointer. The only difference from a basic pointer is compound number pointers raise a different exception when used as an operand for an arithmetic operation.

**Pair Pointer** A type tag of 10 indicates the data field is a double word pointer to a Lisp cons cell. Dereferencing a pair pointer with an offset after scaling that is not 0 or 8 bytes will raise an exception.

Small Compound Number Pointer A type tag of 11 indicates the data field is a double word pointer to a pair. The only difference from a pair pointer is small compound number pointers raise a different exception when used as an operand for an arithmetic operation.

Instruction Pointer A type tag of 12 indicates the data field is a double word pointer to a LOOP instruction. Only words of this type can be the destination of a jump, any other type will causes an exception to be taken. Memory references through instruction pointers go through the instruction cache if one is present.

Future Pointer A type tag of 13 indicates the data field is a word pointer. Any operate operation (section 2.3.1) can be performed on futures but memory operations on futures will raise an exception.

**Physical Pointer** A type tag of 14 indicates the data field is a word pointer to a physical location in memory. A dereference of this pointer will not go through the page mapping hardware. An exception will be taken if a user program tries to create a new physical pointer.

**Extra Pointer Tags** Type tag 15 is reserved for future use. One possible use would be error objects that contained a pointer, either to the instruction that raised the exception or to some block that held information on the exception. Another option would be a basic pointer type that is goes through a cache with a different policy, probably a different line size.

## 2.2 Storage Model

LOOP has three programmer visible storage areas: the register file, the main memory, and the special purpose registers.

## 2.2.1 Register File

There are 63 general purpose registers, R0 through R62. A 64th register, R63, is hardwired to integer 0. Each general purpose register holds one machine word, including tag bits. Additionally each register has carry and overflow condition code bits associated with it [12]. These bits get set/reset when the register is used as a destination for an instruction. If a register is written out to memory with any of its condition code bits set a user exception is taken.

## 2.2.2 Main Memory

Main memory is a flat, 2 exaword virtual address space. Memory can only be accessed through load/store operations, (discussed in section 2.3.2.) All memory access is on aligned word boundaries, but all address arithmetic is done in bytes with the tag field being invisible. Most memory reference operations mask out the low 3 bit of word pointers (low 4 bits of double word pointers) and the low 3 bits of the scaled offset

before calculating the effective address. The combination of masking out the low bits and byte arithmetic leads to some interesting effects. For example: if R1 holds a word pointer to address A, LD(R1,1,R2) will load the word at A into R2. However, LD(R1,-1,R2) will load the the word before A. LD(R1,8,R2) will load the word after A, the tag is skipped.

Fine grained control of caches is provided to the programmer. Operations are provided to lock, unlock, flush, prefetch, and invalidate cache lines. The cache control instructions can be used with a write back cache to implement speculative stores. The lines you wish to do speculative stores to can be locked in, writes can then be done to these lines without destroying the copy in memory. The stores can be undone by invalidating the line and committed by unlocking the cache line.

Loads can be instructed to not cache the value being loaded. Variants of the basic store operation are provided that do not cache the store or do not load the rest of the line on a miss, instead just marking the other words in the line invalid. Non caching load and store operations provide a method of copying chunks of memory without polluting the cache. Not bringing the rest of the cache line in on stores has been shown by Diwan, Tarditi, and Moss [14] to significantly improve the performance of programs that are heap allocation intensive.

If an implementation uses an instruction cache, all references through instruction pointers must go through the instruction cache.

### 2.2.3 Special Purpose Registers

Values are moved between special purpose registers and the general purpose registers using special move operations. Because each operation field has one operand specifier that is 8 bits or larger accommodating 256 different special purpose register would not be difficult. Four different special purpose registers can be accessed each cycle. Access to some special purpose registers is privileged.

Writes to the special purpose registers are not visible until the instruction making the write has reached the commit stage of the pipe line.

Faculties accessed through the special purpose register are:

**Processor Status Word (PSW)** controls floating point rounding mode, which traps are enabled, which exception are taken, which produce error objects. The condition codes are *not* in the PSW.

#### Address of User Trap Vector

Address of System Trap Vector Writes of this register are privileged.

- User Cycle Counter A 64 bit counter that increment once every 1 to 16 (implementation dependent) cycles while the machine is in user mode.

- System Cycle Counter A 64 bit counter that increments once every 1 to 16 (implementation dependent) cycles.

- Cache Miss Counters Various counters to count the number of cache misses. The policy implemented by these counters and the cycles counters may be implemented with programmable logic [10].

- Page Table Root Register Points to root of virtual to physical page translation table. Writes of this register are privileged.

- Page Privilege Table Root Register Points to root of virtual page privilege table. Writes of this register are privileged.

- User Page Privilege Table Root Register Points to root of virtual user page privilege table.

- Network Interface Registers Henry and Joerg [21] find that a hardware register based network interface can reduce much of the overhead of network communications. The exact details of such an interface, including how many registers are needed, would depend on the details of the network. One possibility is to provide this interface through programmable logic [11].

- Jump Target Prediction Stack Writing pushes a new value on the stack. Reading pops the top of the stack into the specified register. Giving the user direct access to the jump prediction stack allow the user program to avoid the pipe line bubbles associated with calculated jumps if the target is known long enough before the jump is taken.

- **Trap Information Registers** A set of 4 registers. When a trap is taken the PC of the trapping instruction, a word describing the trap and destination of the trapping operation, and if appropriate the operands of the operation that caused the trap are placed in these registers. See section 2.5 for details.

- Overflow Bits Holds the overflow bits of all the general purpose registers, speeds up contexts switches. This register is only valid after a pipe drain instruction.

- Carry Bits Holds the carry bits of all the general purpose registers, speeds up contexts switches. This register is only valid after a pipe drain instruction.

## **2.3** Instructions

Conceptually LOOP has 4 functional units, A1, A2, M, and C. A1, A2, and C each have two read ports from and one write port into the register file. M has 2 read ports and 1 read/write port. All four have one read/write port into the special purpose register file. All four functional units can perform the operations listed below in the section 2.3.1 Operates. A1 and A2 can also do multiplication, shifts, rotates. They can also do arithmetic operations on floating point data. M is connected to the memory system and can perform the load, store, cache control and operations described in Section 2.3.2 Memory Operations. C can read and write the PC to perform branches, jumps and conditional traps as described in section 2.3.3 Control Operations.

In the operation descriptions the first operand is called A, and comes from the functional unit's first register file read port. The second operand is called B and comes from the second read port or a sign extended immediate field encoded in the operation. A1, A2, and M each have an 8 bit immediate field, C has a 15 bit immediate field. The register being written, through the functional unit's write port, is called D.

Results are unspecified if more than one operation in an instruction tries to write the same register, unless that register is R63, in which case none of the writes have any effect.

If a functional unit is programmed to perform a operation it can not do (i.e. M doing an add with a floating point word) a user exception is raised.

Each instruction can specify one operation for each functional unit. Each functional unit can be programmed on a per operation basis to return an error object instead of taking an exception if an exception is raised (this option is not available for operations that do write a value into the register file or control operations.) The A1, A2 and M functional units can be programmed on a per operation basis to squash their result if C performs a control operation that goes in the non-predicted direction.

Some operations require more that one functional unit, and are known as "wide operations." They are described in section 2.3.4.

In general passing operands of the wrong type to an operation will result in an illegal type exception being raised.

### 2.3.1 Operates

Operates include arithmetic, logical, predicate, and move operations. All four functional units can perform all of these operations. All operations unless otherwise mentioned clear the condition bits and trap bit of D. All operations unless otherwise mentioned will raise a trap bit exception if the trap bit of either operand is set.

- ADDx, SUBx Add or subtract B to/from A. A and B must be integers. If A or B are compound or small compound number pointers then a compound number exception will be raised instead of an illegal type exception. B will be scaled by x before the operation is performed. Valid values for x are 1,2,8 and 16 and is specified as part of the opcode. The result will be the same type as A. D's condition code bits will be set as appropriate. If an overflow occurs an overflow exception will be raised.

- UADD, USUB Unsigned add or subtract. Identical to ADDx and SUBx, except there is no scale factor and will not raise an exception on overflow.

- **MODPRIME** MODulo PRIME, D gets A mod  $2^{B}$ -1. A and B must be integers. The result will be an integer.

- CMPEQ, CMPLT, CMPLTE Compare A, equal, less than, and less than or equal to B. A and B must be integers. If A or B are compound or small compound

number pointers then a compound number exception will be raised instead of an illegal type exception. The result will be integer zero if the comparison is false and integer one otherwise.

- UCMPLT, UCMPLTE Compare A, unsigned less than, and unsigned less than or equal to B. A and B must be integers. The result will be integer zero if the comparison is false and integer one otherwise.

- **FEQ, DEQ** Compare A equal, including type tag, or data field only, to B. A and B can be any type except error object. The result will be integer zero if the comparison is false and integer one otherwise.

- AND, OR, NAND, XOR, XNOR Bitwise and, or, nand, xor, xnor the data field of A with the data field of B. A and B can be any type except error object. The result will have the same type as A.

- MOVEQ, MOVNEQ, MOVGT, MOVGTE, MOVLT, MOVLTE Conditionally copy B, into D, based on A being equal, not equal, greater than, greater than or equal, less than, less than or equal to zero. A must be an integer or a float. B can have any type.

- MOVS, MOVC Conditionally copy B, into D, based on the low bit of A being set, or clear. A must be an integer. B can have any type.

- **PADDx** Pointer add A to B. A must be a pointer and B must be an integer. B will be scaled by x before the operation is performed. Valid values for x are 1,2,8 and 16 and is specified as part of the opcode. The result will be the same type as A. D's condition code bits will be set as appropriate. If an overflow occurs an overflow exception will be raised.

- PSUBx Pointer subtract B from A. A must be a pointer and B must be an integer. B will be scaled by x before the operation is performed. Valid values for x are 1,2,8 and 16 and is specified as part of the opcode. The result will be the same type as A. D's condition code bits will be set as appropriate. If an overflow occurs an overflow exception will be raised.

- **PDIFF** Pointer difference. A and B must be a pointers. The result will be an integer that represents the number of bytes between A and B. The result will be positive if A is larger than B. D's condition code bits will be set as appropriate. If an overflow occurs an overflow exception will be raised.

- PCMPEQ, PCMPLT, PCMPLTE Pointer compare A, equal, less than, and less than or equal to B. A must be a pointer, B must be an integer or a pointer. The result will be integer zero if the comparison is false and integer one otherwise.

- BEXL, BEXB Little endian and big endian extract byte B from A. Only the low 3 bits of B are used as an index into A. A can be any type except error object, B must be a pointer or integer. The extracted byte will be zero extended to 64 bits, given the same type tag as A and placed in D.

- **CBIT, SBIT** Copy A into D replacing the Bth bit with 0 (CBIT) or 1 (SBIT.) Only the low 6 bits of B are used as the index. A can be any type except error object and B must be an integer.

- **RDBIT** Write integer zero into D if the Bth bit of A is 0, otherwise write integer one. Only the low 6 bits of B are used as the index. A can be any type except error object and B must be an integer.

- **CPYTAG** Copy A's data field into D's data field and B's type tag into D's type tag. A and B can be any type.

- WRTAG Copy A's data field into D's data field and the low 4 bits of B into D's type tag field. A can be any type, B must be an integer.

- **RDTAG** Zero extend the B's type tag to a 64 bit integer and place it in D. A is not used in this operation, B can have any type.

- **PTRP, NUMP** Write integer zero into D if A is not a pointer (PTRP) or A is not an integer, float, compound number pointer, or small compounded number pointer (NUMP), otherwise write integer one. B is not used in this operation, A can have any type.

- **TAGEQ** Write integer zero into D if the tag of A dose not equal the tag of B, otherwise write integer one. A and B can be any type.

- CHKTAG Write integer zero into D if the type tag of A does not equal the low 4 bits of B, otherwise write integer one. A can be any type, B must be an integer.

- WROV, WRCR Copy A into D, writing the low bit of B into D's overflow or carry flag. A can be any type except error object, B must be an integer.

- **RDOV, RDCR** Write integer zero into D if A's overflow (RDOV) or carry (RDCR) flag is cleared otherwise write integer one. B is not used in this operation, A can not be an error object.

- WRTRAP Copy A into D, writing the low bit of B into D's trap bit. A can be any type except error object, B must be an integer. This operation will not trap if A or D has its trap bit set.

- **RDTRAP** Write integer zero into D if A's trap bit is clear other wise write integer one. B is not used in this operation, A can have any type. This operation will not trap if A has its trap bit set.

- SPRWR Write A into the special purpose register specified by B. A can have any type, B must be an integer. D should be R63.

- SPRRD Write the continents of special purpose register specified by B into D. A is not used in this operation, B must be an integer.

Additionally A1 and A2 can perform the following operations:

- ADDx, SUBx, CMPEQ, CMPLT, CMPLTE Same as standard ADDx, SUBx, CMPEQ, CMPLT and CMPLTE except A and B can be floats as well as integers.

- **SMULT** The low 64 bits of the product of A and B is placed in D. A and B must be integer, or floats. If A or B are compound or small compound number pointers then a compound number exception will be raised instead of a illegal type error. The result will have the same type as A. D's condition code bits will be set as appropriate. If an overflow occurs an overflow exception will be raised.

- AS, LS, ROT Arithmetic shift, logical shift, or rotate, A B bits. A can be any type except error object, B must be an integer. If B is positive the shift/rotate will be left, otherwise to the right. The result will have the same type as A.

- **FF** Write the position of the first 1 bit in B. The result is tagged as an integer. A is not used in this operation, B can not be an error object.

- **BMXC** Select out the bits of A corresponding to the ones in B, then use them as the low order bits for the result, giving the same type tag as A. A and B can be any type except error object.

- M8ADD, M8SUB Multi-gauge add and subtract. A and B are treated as 8, 8 bit twos compliment integers. They are added pair wise. A and B must be integers, the result will be an integer. If any of the adds overflow an exception will be raised. The carry and overflow bits of D will be written with the logical or of the overflow and carry bits of the eight adds.

- M8UADD, M8USUB Multi-gauge unsigned add and subtract. Identical to M8ADD and M8SUB except will not raise an exception on overflow.

- M8SADD, M8SSUB Multi-gauge saturating add and subtract. A and B are treated as 8, 8 bit twos complement integers. They are added pair wise but saturate at +127 and -128. A and B must be integers, D will be an integer.

- M8CMPEQ, M8CMPLT, M8CMPLTE, M8UCMPLT, M8UCMPLTE Multi-gauge compare equal, less than, less than or equal, unsigned less than, unsigned less than or equal. If the i th byte of A and B have the appropriate relation then the i th byte of D is a one, otherwise its a zero. A and B must be integers, D will be an integer.

- M8AS, M8LS, M8ROT Multi-gauge arithmetic shift, logical shift, and rotate. If j is equal to the i th byte of B, then the i th byte of D is the i byte of A shifted or rotated j bits. The shift/rotation is to the left if j is positive and to the right otherwise. A and B must be integers, D will be an integer.

- Additionally A1 can perform the following operation:

IMASK Concatenate A and B and bitwise OR the result with the data fields of the next two instruction words as they enter the decode stage. Results are undefined if the instruction containing the IMASK operation or the instruction being masked takes an exception. Interrupts are disabled in such a way that if the instruction containing the IMASK operation completes then the next instruction will complete as well. The operation has no effect on the copy of the masked instruction in memory or in the caches. A and B can be any type. D should be R63.

## 2.3.2 Memory Operations

Memory operations include loading and storing words from memory, cache control and prefetching. These operations can only be used with the M functional unit. All memory operations use A as the base. For all memory operations except LDTAGx the base must a be pointer. With LDTAGx base can be any type of word. All memory operations use B as an offset which must be a signed integer representing a number of bytes. If the base and offset are not the correct type an illegal type exception is raised.

Effective virtual addresses are formed by adding the scaled offset and base. All memory operations except LDAx and STAx mask out the low 3 bits of the offset, and the low 3 bits (or 4 bits if it is a double word pointer) of the base before performing the add. All memory operations raise an exception if the low 3 bits of the virtual address are not zero.

If the base is an instruction pointer the operation goes through/affects the instruction cache if present.

#### Load Operations

All load operations have a scale factor, x, for the offset and a cache control flag, both are specified as part of the opcode. The scale factor can be 1,2,8 or 16 and is applied before the low bits of the offset are masked. The cache control flags determines if the reference should be cached. If the flag is set then the cache line of the word addressed will not be fetched into the cache.

Load operations with pair or small compound number bases will raise an exception if the scaled offset is not 8 or 0.

Load operations will raise a trap bit exception if the base or offset has its trap bit set.

All load operation which have a future as a base will raise a future exception. Loads clear the condition code bits of D.

LDx LDx forms the effective address, fetches the corresponding word from memory and places it in D. A trap bit exception will be raised if the word fetched from memory has its trap bit set. This exception is "imprecise," other instructions after the load that do not depended on it may have completed before this exception is raised.

- LDTAGx Identical to LDx unless base is a pair, small compound number, or not a pointer in which case base's type tag is padded with zeros to form a 64 bit integer and written to D.

- LDAx Identical to LDx except the low bits of the base and offset are not masked. As a result if the low 3 bits of the sum of the base and scaled offset are not zero an unaligned accesses exception will be raised. This, along with STAx bellow, allows byte pointers to be implemented in a manor similar to the DEC Alpha architecture [13].

- LDNTx Identical to LDx except it will not raise an exception if the word being fetched has its trap bit set.

- **CRx** Identical to LDx except it will raise an exception if base is not a pair or small compound number pointer.

- LDLx Identical to LDx except the address accessed is recorded in the locked-address register and the locked flag is set. The lock flag will be cleared if any stores are made to the location in the locked-address register. LDLx can be used with the BLL and store operations to implement atomic test and set operations. This facility is closely modeled on load locked/store conditional facility provided by the DEC Alpha architecture [13].

#### **Store Operations**

All store operations have a scale factor, x, for the offset and come in three versions that affect the cache in various ways, the scale factor and variants are all specified as part of the opcode. The scale factor can be 1,2,8 or 16 and is applied before the low bits of the offset are dropped.

The first variant is a standard store operation that will fetch the appropriate cache line into the cache as part of the store. The second variant will only write word into the cache if appropriate cache line is already there, it will not displace any line from the cache, this store is the counterpart to a load with the no-cache flag set. The final variant will allocate space in the cache for the word's cache line but will not fetch the rest of the line, instead the other words in the line will be marked invalid.

Store operations with pair or small compound number bases will take an exception if the scaled offset is not 8 or 0.

All Store operations will take a trap bit exception if the base or offset has its trap bit set.

All store operation which have a future as a base will take a future exception.

If the register being stored has any of its condition code bits set an exception will be taken.

STx STx forms the effective address and writes the continents of D to memory. A trap bit exception will be taken if the word being written has its trap bit set.

- STAx Identical to STx except the low bits of the base and offset are not masked. As a result if the low 3 bits of the sum of the base and scaled offset are not zero a unaligned accesses exception will be taken. This, along with LDAx above, allows byte pointers to be implemented in a manor similar to the DEC Alpha architecture [13]

- STNTx Identical to STx except it will not take an exception if the word being written has its trap bit set.

- **RPLAC**<sup>x</sup> Identical to ST<sub>x</sub> except it will take an exception if base is not a pair or small compound number.

#### **Cache Line Control**

LOOP provides a number of cache line control operations. In all cases the cache line affected is the line containing the effective address. These operation only use base and offset, D should be R63. These operations do not have a scale factor for the offset.

- FLUSH Will flush the appropriate cache line, writing it out to main memory if necessary. This operation has no effect if the line is not in cache.

- **INVAL** Will invalidate the appropriate cache line, clearing any dirty bits. The line will not be written out to memory. This operation has no effect if the line is not in the cache.

- **FETCH** Will move the cache line closer to the processor. This operation will never raise an exception.

- LOCK Will lock the cache line into the cache, fetching it if it not already there. The cache line will not be replaced until it is unlocked. Behavior is undefined if it is attempted to lock two lines into the cache that map to the same cache location.

- **UNLOCK** Will unlock a cache line that has been locked, allowing it to be bumped out of the cache.

### Memory Map Test

LOOP provides instructions to test the validity of a virtual address without actually performing a memory operation or raising any exceptions. These operations do not have a scale factor for the offset.

MMPLD Runs the effective address through the memory mapping hardware as if it was a load. Returns integer 0 if no exceptions would be raised if an actual load was performed of that effective address. If an exception would be raised an integer bit map is returned that indicates which exceptions would occur. Exceptions caused by the loading of words with their trap bit's set are not checked for. MMPST Runs the effective address through the memory mapping hardware as if it was a store. Returns integer 0 if no exceptions would be raised if an actual store was performed to that effective address. If an exception would be raised an integer bit map is returned that indicates which exceptions would occur. Exceptions caused by the writing of words with their trap bit's set are not checked for.

### 2.3.3 Control Operation

Control operations include branches, jumps, and conditional trap. They can only be executed by the C functional unit. All control operations write an instruction pointer to the instruction following the control operation to D, whether or not the branch, jump, or trap is taken.

#### Branches

All branches perform some test on A, if the test is true the branch is taken. B is used as branch offset and is interpreted as a signed number double words. Each branch has two flags specified in the opcode, I and P. If set the I flag will invert the sense of the test. If the P flag is set the branch will be predicted as taken, otherwise as not taken.

D's condition code bits are overwritten. Unless otherwise specified if A has its trap bit set an exception is taken.

- **BEQ** Branch if A is zero. A must be an integer or a float, if A is a compound or small compound number pointer a compound number trap will be taken instead of an illegal type exception.

- **BLT** Branch if A is less than 0. A must be an integer or a float, otherwise an incorrect type trap will be taken, if A is a compound or small compound number pointer a compound number trap will be taken instead of an illegal type exception.

- **BEQL** Branch if A is less than or equal to 0. A must be an integer or a float, otherwise an incorrect type trap will be taken, if A is a compound or small compound number pointer a compound number trap will be taken instead of an illegal type exception.

- **BLOW** Branch if the low bit of A's data field is one. A can be any type but error object.

- **BTRAP** Branch if A's trap bit is set. This instruction will not trap if it A's trap bit is set. A can be any type but error object.

- BNUM, BPTR, BPAIR Branch if A is a integer, float, compound, or small compound number (BNUM), or A is a pointer (BPTR), or A is a small compound or pair (BPAIR). A can have any type.

- **BOV, BCR** Branch if A's overflow (BOV) or carry (BCR) is set. A can be any type but error object.

- **BLL** Branch if the locked flag is not set and clear the lock flag. If in a multiprocessor system where more than one processor is executing a BLL operation with respect to the same value in their lock-address registers only one of the BLL operations can go in their predicted directions. BLL can be used with a store that has its squish bit set and a previous LDLx operations to implement atomic test and set operations. This facility is closely modeled on Load locked/store conditional facility provided by the DEC Alpha architecture [13].

- **BU** Branch unconditionally. This branch does not have the P and I flags of the other branches. Instead it has the same stack, pop, and push flags that are described for jumps. A is not used.

### Jumps

The destination of jumps are specified by B. If B is not an instruction pointer an incorrect type trap is taken. All jumps have three flags, stack, pop, and push, encoded in the opcode that determine how the jump's target should be predicted and the jump prediction stack should be modified. If stack is set the top of the jump prediction stack is used to predict the jump destination. If stack is not set the branch target cache<sup>1</sup> is used for prediction instead. If pop is set the top of the jump prediction stack is popped after it is used for any prediction. If push is set a pointer to the next instruction is pushed on the jump prediction stack after any reading or popping takes place. If B has it trap bit set a trap will be taken.

Conditional jumps have two more flags, I and P. I inverts the sense of the test. If P is set the jump is predicted taken. The test is performed on A. If A has its trap bit set a trap will be taken.

JUMP Unconditional jump.

JMPEQ Branch if A is zero. A must be an integer or a float, if A is a compound or small compound number pointer a compound number trap will be taken instead of an illegal type trap.

## **Conditional Traps**

Conditional traps perform a test on A and B. Conditional traps are alway predicted not taken. Each conditional trap operation has its own entry in the user trap vector. Each conditional trap has an I flag that inverts the test. If A or B have the trap bits set a trap bit exception will be taken.

**CTEQG** Conditional trap if A is greater than or equal to B. A and B must be integers.

<sup>&</sup>lt;sup>1</sup>Branch target caches are explained in section 3.1.1

- **CTTAGEQ** Conditional trap if A and B's type tags are equal. A and B can be any type.

- **CTFEQ, CTDEQ** Trap if A is equal, including type tag, or data field only to B. If A and B can be any type but error object.

- CTCHKTAG Trap if A's type tag is equal to the low 4 bits of B. A can be any type, B must be an integer.

- **CTPAIR** Trap if A is a pair or small compound number. A can have any type, B is not used.

- CTNUM Trap if A is a integer, float, compound, or small compound number pointer. A can have any type, B is not used.

- CTPTR Trap if A is a pointer. A can have any type, B is not used.

#### 2.3.4 Wide Operations

The functional units can also be used together in a wide operation. A wide operation is specified by a special opcode for A1 or A2. Wide operations use 2 or 4 of the functional units. Wide operations trap if any of their operands have there trap bit set unless otherwise specified.

In the description bellow A1.A is functional unit A1's A operand, A1.B is its B operand, etc.

- DMUL Double multiply. Uses A1 and A2, takes A1.A and A1.B and writes the low 64 bits of their product to A1.D and the high 64 bits to A2.D. A1.A and A1.B must be integers. The condition code bits of A1.D and A2.D are cleared.

- **UDMUL** Same as DMUL but the multiplication is performed unsigned.

- DMULAC Double multiply and accumulate. Uses A1 and A2. A1.A and A1.B are multiplied together to form a signed 128 bit product. The product is added to the number formed by concatenating A2.A and A2.B (with A2.B being the high order bits). If A2.A is a float then only it is used. The high order bits of the sum is written to A1.D, the low order bits to A2.D, unless A2.A was a float, then the sum is a float and only goes to A2.D. The condition code bits are set as appropriate. All the operands must be integers or floats, a compound number trap is taken if they are compound or small compound numbers instead of a illegal type trap.

- MS Multi-word shift. Uses A1 and A2. A1.A and A1.B can be any type but error object. A2.B must be an integer. A1.A is shifted A2.B bits and written to A1.D. Instead of shifting in zeros the high order A2.B bits of A1.B will be shifted in for left shifts and low order bits for right shifts. The bits that get push out the end will be zero extended to 64 bits, given the same tag as A1.A and written to A2.D. If A2.B is positive the shift will be to the left, otherwise to the right. Shifts of 64 or greater will copy A1.A into A2.D and A1.B into A1.D.

- **BINL, BINB** Little and big endian byte insert. Uses A1 and A2. The low order byte of A1.B is overwrites the A2.Bth byte of A1.A. The result is written to A1.D. A1.A and A1.B can be any type but error object. A2.B can be an integer or a pointer, only its low order 3 bits are used to form the index. A1.D will have the same type as A1.A.

- Double Loads Uses A2 and M. Same options and variants as single word loads. Base is M.A, offset is M.B. Word at effective address is loaded into M.D, word at effective address + 1 is loaded into A2.D. If base is a pair or small compound number offset must be 0 or an exception will be raised.

- Double Stores Uses A2 and M. Same options and variants as single word stores.

Base is M.A, offset is M.B. M.D is written into memory at the effective address.

A2.B is written into memory at effective address + 1. If base is a pair or small compound number offset must be 0 or an exception will be taken.

- Quad Loads Uses all four functional units. Same options and variants as single word loads. Base is M.A, offset is M.B. Word at effective address is loaded into M.D, word at effective address + 1 is loaded into A2.D, word at effective address + 2 is loaded into A1.D, and word at effective address + 3 is loaded into C.D. An exception will be raised if base is a pair or small compound number.

- Quad Stores Uses all four functional units. Same options and variants as single word stores. Base is M.A, offset is M.B. M.D is written into memory at the effective address. A2.B is written into memory at effective address + 1, A1.B at effective address + 2, and C.B as effective address + 3. An exception will be taken if base is a pair or small compound number.

- **DPIPE** Drain pipeline. Uses all four functional units. Lets all operation currently being executed complete before executing next instruction.

- Non-Instruction Tag If an instruction is fetch and ether word is not tagged as an instruction the word with the lower address gets written into R62, the other word gets written to R61. Alternatively the processor can be set to take a user exception if a non-instruction word is fetched.

#### Notes on the Instruction Set

Most of LOOP's operations would be at home in any modern RISC processor's instruction set. The uses of some the other operations may be non-obvious. Also the interactions between tags and some instructions may appear to be inconsistent with other aspects of the architecture.

**Pointer Integrity** The architecture does not make any serious attempt to enforce pointer integrity. This is really a job for the compiler. As a result the bitwise logic operations, shifts, and other bit twiddling operations all accept pointers as valid operands. This is done partly because systems will some times have to twiddle the bits of pointers. When a system does do this it will probably know what it is doing so putting type checking in its way seems counter productive.

The other problem with providing credible pointer integrity at the architectural level is that it is very expensive. In general it would require making each pointer a three word triplet of base, offset, and bound. The operations on these pointers would be long and complicated, probably requiring multiple cycles. Most pointers don't need this protection, especially in Lisp where the programer usually can't get his or her hands on a raw pointer the way they can in C. Software can provide this kind of protection if it is needed [3]. Implementing safe pointers in software has the added advantage that the compiler has more flexibility in scheduling the subparts of safe pointer operations.

LOOP does allow for single cycle loads and stores with bounds checking when it is needed. The CTEQG operation can be placed in the same instruction with a load or store to perform the bound check. This can be done safely by setting the memory operation's squish bit.

The one problem with this is that it requires the bound to be in a register. LOOP used to provide a variant of a vector length cache [30] in the form of a small user associative memory and a special conditional trap operation to get around this problem. The conditional trap would get a word out of the associative memory and compare it with an integer, trapping if the integer was larger than the value from the memory. By storing array bounds in the associative memory with the array's base as the key bounds checking could be implemented by issuing the conditional trap with the base and offset as the operands in the same cycle as the memory operation to be protected. This idea was dropped because its felt that most of time the compiler will have enough information to simply cache the array bound in a register. The only time a problem arises is in code like this<sup>2</sup>:

```

(define (get-element i)

(vector-ref some-vector i))

```

```

(map get-element some-list-of-numbers)

```

In this example it would be unreasonable to expect the compiler to be smart enough to cache the bound of some-vector in a register unless both vector-ref and get-element were inlined. However, if the calls are not inlined their cost is likely to dominate. The cost of an extra load is not significant.

The primary reason why some operations don't accept pointers is not pointer integrity but to make low cost generic arithmetic posable. We did not provide no pointer versions of the various bit twiddling operations because it is felt that Lisp programs don't do much bit twiddling. If a lot of bit twiddling is done it will probably be on fixed sized arrays of bits. In this case the compiler will probably be able to safely elide the type checks.

<sup>&</sup>lt;sup>2</sup>This example is in Scheme

**Byte Operations** The multi-gauge operations are provided so byte operations can be efficiently handled by our word addressed machine. Its often claimed that word addressed machines can't handle byte operations efficiently. If there are going to be a lot of byte operations the bytes are going to be in some sort of array, which can be packed efficiently in our 64 bit words and and quickly operated on in groups of eight bytes by the multi-gauge operations. It would not be surprising if LOOP is faster at many byte manipulation operations than a similar byte addressed machine without multi-gauge operations. The multi-gauge operations are not expected to be hard to implement. Most involve optionally blocking some of the carries in the adder. Another alternative would be just to add eight 8 bit ripple carry adders which may well be fast enough and would be very small. Eliminating byte addressability greatly simplifies the memory system and can allow the whole chip to be much faster.

Generic Function Calls The LDTAGx and MODPRIME operations were suggested by G.J. Rozas as a way to make generic function dispatch fast. With an appropriate software convention LDTAGx allows the type of an object to obtained with a single operation. MODPRIME can then be used as a hash function so the appropriate method can be looked up in a hash table.

#### **2.3.5** Instruction Format

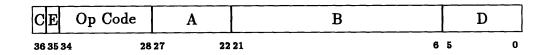

Each instruction fills the data field of two words, we will refer to the word with the higher address as the high word, and the one with the lower address as the low word.

There are four sections in each instruction, one for each functional unit. Each section has an opcode field, an A field, a B field, a D field and a no-exception flag. Additionally the sections for A1, A2, and M each have a squish flag. The sections for M and C each have an extra bit of opcode to differentiate between memory/control operations and operate operations.

The A field is 6 bits and specifies the register to get the A operand from.

The B field is 9 bits for A1, A2, and M, 16 bits for C. If the high bit of this field is 0 then the low 6 bits specify the register to get the B operand from, otherwise the low 8 (or 15) bits are sign extended, tagged as an integer and used as the B operand. Note branch operations always use the B field of C as an immediate and use the immediate/register select bit and no-exception flag to form a 17 bit immediate.

The D field is 6 bits and specifies what register the result will be written to. Store operation use this filed to specify what register should be written out to memory.

If the no-exceptions flag [10, 16] is set and the operation raises an exception it will be dealt with by writing an error object to D, not by passing control to an exception handler. This includes TLB misses on loads. Results are unpredictable if the bit is set on operations that do not return a value or on control operations. In the figures bellow the no-exception flag is indicated by an E.

If the squish flag is set and there is a control operation in the instruction the functional unit will squish it results (including writes to the memory system) if the control operation goes in the non-predicted direction. In the figures bellow the squish flag is indicated by an S.

| ES Op    | Code | Α     | В  |   | D |   |

|----------|------|-------|----|---|---|---|

| 29 28 27 | 21   | 20 15 | 14 | 6 | 5 | 0 |

Figure 2-3: Format of A1 and A2 Operations

Figure 2-4: Format of M Operation

#### Format for A1 and A2 operation

A1's section goes in the top 30 bits of the high word's data field, A2's section goes in the next 30 bits.

#### Format for M operations

M's section takes up the low 4 bits of the high word's data filed and the high 27 bits of the low word's data field. In figure 2-4 the M flag is set to one for memory operations and to zero otherwise.

#### Format for C operations

C's section uses the remaining 37 bits in the low word's data field. In the figure 2-5 the C flag is set to one for control operations and to zero otherwise.

Figure 2-5: Format of C Operation

## 2.4 Memory Management

LOOP supports the standard paged virtual memory abstraction with a few refinements. Protection information is handled independently from the address translation information, allowing multiple contexts to have one address space with different access privileges. Wulf's WM also has this feature [52], Chase, Levy, Backer-Harvey, and Lazowska [7] suggest that this would be useful in the type of single address space operating systems that may be practical with the very large address spaces 60+ address bits provide.

The LOOP memory management unit supports read and write barriers with a granularity of 8 to 256 words. This is done by making part of the TLB out of programmable logic and adding a few dozen extra bits to each TLB entry. The programmable logic in the TLB can be programmed to use the extra bits as dirty, write protect, or access protect bits for small sets of words.

## 2.5 Traps

LOOP supports fast trap handling by providing multiple contexts, user level traps, and direct support for instruction emulation.

LOOP has multiple "contexts" on chip. Each context consists of one complete register file and a set of pipe line registers. When a trap is taken the processor is switched to a clean context, as a result none of the state in the register file needs to be written out to memory, nor does the pipe line have to be drained.

We would expect to have at least two contexts, one for normal operations and one for the trap handler, although providing 1 or 2 others could be useful. A third context allows system traps to be active during user level trap handlers, freeing the user level trap handlers from knowing about details of operating system. A fourth context could allow the garbage collector traps to be active during other trap handler, though having the trap handlers make in-line GC checks would probably also be acceptable.

Many of LOOPs traps are "user traps," which don't perform a costly address context switch (they do perform the register/pipe line context switch described above.) Many traps, such as type, garbage collection, overflow, floating point, and unaligned address traps are easier to service in the addressing context of the task that trapped since that is where the necessary information usually is.

Johnson [24] suggests a nice mechanism for emulation that LOOP adopts in a slightly modified form. When an exception occurs in addition to the PC of the trapping operation being provided to the trap handler the operands and a word describing the exception and the destination of the operation are also provided in special purpose registers<sup>3</sup>. Operations are provided to read and write the registers of the task that trapped, and to restart the trapped task while squashing and optionally replacing the result of the operation that trapped, or restarting the instruction.

<sup>&</sup>lt;sup>3</sup>Johnson also suggest providing a copy of the trapping instruction as well since it may be difficult to get, primarily because it probably wont be in the data cache. This is not as much of a problem in LOOP because instruction pointer references are satisfied by the instruction cache.

# Chapter 3

# **Notes on Implementation**

By its traditional definition an "Instruction Set Architecture" gives no hint of how it might be implemented, however, only the foolish architect designs an architecture without considering how it may be implemented. Also RISC advocates have traditionally pushed for the barrier between "architecture" and "implementation" to be made porous. It can also be argued that VLIW machines make no distinction at all between the two. In this chapter we discuss the costs of some LOOP's lisp oriented features, how we think LOOP should be implemented, and some features which can not be properly termed "architectural" features.

# **3.1** Area Estimates

We base our area estimates on the DEC 21064 <sup>1</sup> [15], the first commercially available implementation of DEC's Alpha architecture [13]. The 21064 is a good chip to base our estimates on because it also implements a 64 bit architecture with a similar set of operations. It is also fast with a 5ns cycle time in a process with a  $0.5\mu$  effective minimum channel width.

Neither the Alpha architecture nor the 21064 directly support tags, fine grained memory barriers, or multiple on chip contexts. First we will present area estimates for a LOOP implementation without Lisp support based on data from the 21064. Then we will make estimates on how tags, memory barriers, and contexts impact the speed and size of a LOOP implementation. This will highlight the cost of Lisp support at the hardware level. In the next chapter we will look at what these features might buy us.

In the estimates, instead of using  $\mu$  or mills we will use,  $\lambda$  as our unit of measurement.  $\lambda$  is 1/2 the minimum feature size in a process and gives us a process independent way to measure areas. For reference the 21064 is 1.67 G $\lambda^2$ . Dally [9] suggests that by 1997 chip designers will have 10 G $\lambda^2$ to work with. The estimates for low level components such as memory cells also come from [9].

<sup>&</sup>lt;sup>1</sup>These estimates are from Prof. William Dally, he extracted this information the ISSCC 92 presentation on the 21064 and from talking to various people who worked on the chip.

## 3.1.1 LOOP Without Lisp Support

A LOOP implementation is likely to have 8 major components. The A1, A2, M and C function units, the register file, the instruction and data caches, and write buffer.

#### A1 and A2 functional Units

The A1 and A2 functional units are 64 bit integer/floating point units with barrel shifter and 64 bit multipliers. The 21064's integer unit is  $72M\lambda^2$ , this includes a non-pipelined 64 bit multiplier and barrel shifter.

A number for the 21064's floating point units is a little more difficult to get. The floating point unit is  $175M\lambda^2$ , but this includes a 5 port register file. Using the integer unit's 16.8  $M\lambda^2$  6 port register file as a model we estimate the floating point unit's register file is  $16.8M\lambda^2 \times 5^2/6^2 = 11.7M\lambda^2$ , suggesting that the floating point unit without register file is  $163M\lambda^2$ .

Taken together these estimates suggest the A1 and A2 functional units would be around  $235M\lambda^2$  each.

#### **Register File**

LOOP needs a register file with 8 read ports, 3 write ports, and 1 read/write port. One way to provide this is with two register files with 8 ports each. Since the size of a register file goes up with the square of the number of ports, the pair of smaller files is smaller than one big one. To get an estimate for an 8 port LOOP register file from the 21064's  $16.8M\lambda^2$  6 port register file we multiply its area by  $8^2/6^2$  to account for the extra ports, then by 2, because LOOP has 64 registers not 32. Using these number each 8 port file is  $60M\lambda^2$ .

#### **M** functional Unit

The M unit performs many of the same functions as the A units, but it does not do multiplies, shifts or floating point operations. It does need a TLB. The integer part of the A units is  $72M\lambda^2$ , but this includes a 64 bit multiplier and barrel shifter. Dally [9] estimates that a 64 bit multiplier would be  $15M\lambda^2$ , and a barrel shifter would be  $5M\lambda^2$ . Assuming a 512 KWord page size, TLB entries would need 52 bit keys, 61 bit physical addresses, 4 flag bits (valid, dirty, no-cache, and read-only). SRAM cells are around  $1K\lambda^2$ , content addressable memory cells are about  $1.5K\lambda^2$ , making each entry  $143K\lambda^2$ . A 32 entry TLB would be  $4.6M\lambda^2$ . This does not include the hardware for fine grain memory protection, we will add that later. Using these estimates the M unit should be about  $57M\lambda^2$ .

#### **C** functional Unit

The C unit is similar to the M unit but it does not have a TLB, suggesting the C unit is around  $52M\lambda^2$ .

#### Write Buffer

The 21064 has a 4 entry by 32 byte write buffer that is  $36M\lambda^2$ .

#### Caches

The 21064 data cache and instruction caches are  $1.3K\lambda^2$  and  $1.75K\lambda^2$  per bit respectively. These figures include the overhead for tags, valid bits etc. If we had 64 K byte (8 K words) data and instruction caches they would take up  $696M\lambda^2$  and  $928M\lambda^2$  respectively.

#### **Branch Address Table and Jump Prediction Stack**

To operate effectively pipelined processors need some way to predict changes in control flow. For conditional branches and jumps LOOP uses a taken/not taken bit in the instruction word, but it still needs a way to predict the address, preferably in the instruction fetch stage.

The address for jumps can be predicted using a jump prediction stack [13], subroutine calls push the return address on the stack and returns pop the top element and use it as a predicted address. Such a stack would be a 60 bit wide SRAM. A 32 entry stack, would be  $2M\lambda^2$ .