# **Reducing Variability in a Semiconductor Manufacturing Environment**

by

Minja Johanna Penttilä

M.S., Materials Science, Helsinki University of Technology (2000)

Submitted to the Sloan School of Management and the Department of Electrical Engineering and Computer Science in Partial Fulfillment of the Requirements for the Degrees of

> Master of Business Administration and Master of Science in Electrical Engineering and Computer Science

In conjunction with the Leaders for Manufacturing Program at the Massachusetts Institute of Technology June 2005

© 2005 Massachusetts Institute of Technology. All rights reserved.

| Signature of Author   | · · · · ·                                                   |

|-----------------------|-------------------------------------------------------------|

|                       | Sloan School of Management                                  |

|                       | Department of Electrical Engineering and Computer Science   |

|                       | - May 6, 2005                                               |

| Certified by          |                                                             |

|                       | Thomas Roemer                                               |

|                       | Assistant Professor of Operations Management                |

|                       | Thesis Advisor                                              |

| Certified by          |                                                             |

|                       | Roy E. Welsch                                               |

| Prof                  | essor of Statistics and Management Science, Director CCREMS |

|                       | Thesis Advisor                                              |

| Accepted by           |                                                             |

|                       | David Capodilupo                                            |

|                       | Executive Director, MBA Program                             |

|                       | Executive Director, MBA Program                             |

| Accepted by           |                                                             |

|                       | Arthur C. Smith                                             |

|                       | Chairman, Department Committee on Graduate Theses           |

| SSACHUSETTS INSTITUTE | Department of Electrical Engineering and Computer Science   |

|                       |                                                             |

| SEP 0 1 2005          | RKER                                                        |

|                       | BARKER                                                      |

| LIBRARIES             |                                                             |

1

·

. \*\*

1

2

## **Reducing Variability in a Semiconductor Manufacturing Environment**

by Minja Johanna Penttilä

Submitted to the Sloan School of Management and the Department of Electrical Engineering and Computer Science on May 6, 2005 in the Partial Fulfillment of the Requirements for the Degrees of Master of Business Administration and

# Master of Science in Electrical Engineering and Computer Science

#### ABSTRACT

The main drivers in today's flash memory business are low cost and flexibility. Low cost requires high tool utilizations, whereas flexibility and ability to respond quickly to changing customer demands require short throughput times. There is, however, an inherent operational conflict with achieving both high utilization and short cycle time simultaneously. Intel's flash memory factory is striving for shorter manufacturing throughput times without reducing tool utilizations. One of the major components in throughput time today is queuing time caused partly by variability in the manufacturing environment. Being able to reduce this variability component could result in improvements in throughput time.

In this work, Factory Physics methods are used to analyze variability in the manufacturing flow. First, potential high variability areas in the flow are identified. Second, manufacturing data is analyzed to find the main sources of variability. Third, ways to reduce variability are investigated. Finally, means to align manufacturing metrics with variability reduction efforts and the effect of metrics on organizational culture and change implementation are discussed.

During the study it was found out that the lithography area reduces the overall manufacturing flow variability. It was also found out, that the area is highly utilized and is thus introducing non-value adding queuing time for the product throughput time. Arriving material flow was identified to be the main source of variability. Recommendations for improving the area performance include optimizing tool dedications, standardizing operator decision making, and changing preventive maintenance operations.

The key takeaway from this study is the importance of metrics alignment. Metrics are the most powerful incentives for operator behavior. Unless the daily floor level performance measurements are aligned to support the organizational goals, implementing new operations management methods to reduce variability will be challenging.

Thesis Advisors:

Thomas Roemer Assistant Professor of Operations Management

Roy E. Welsch Professor of Statistics and Management Science, Director CCREMS

## **ACKNOWLEDGEMENTS**

I would like to thank the Leaders for Manufacturing program, Don Rosenfield and the program staff for this great two-year journey. I would also like to thank my thesis Advisors Thomas Roemer and Roy Welsch for their guidance during my internship project.

I would like to acknowledge Intel Corporation for providing me the opportunity to learn from one of the best semiconductor manufacturers in the world. I am especially grateful for Fab11 Plant Manager Dave Baglee for sponsoring my internship and for my company supervisor Jim Blumenschein for his time and guidance. In addition, I would like to thank Eric Stebbins, Zane Rakes, Randy Ortega, Tee Welton, Justin Sanchez, Kyle Lee, Tina Volzer, and George Castellano and the rest of the litho staff for their help and support.

These past two years would not have been the same without my awesome LFM and Sloan classmates; special thanks to my LFM summer team for countless laughs during those long summer evenings.

Most importantly, I would like to thank my family and loved ones for their infinite support.

# **TABLE OF CONTENTS**

| A | BSTRA            | ACT                                                                                                  | 3   |  |

|---|------------------|------------------------------------------------------------------------------------------------------|-----|--|

| A | ACKNOWLEDGEMENTS |                                                                                                      |     |  |

| L | ST OF            | FIGURES                                                                                              | 9   |  |

| L | ST OF            | TABLES                                                                                               | .11 |  |

| 1 | INT              | RODUCTION                                                                                            | 13  |  |

|   | 1.1              | Problem Statement                                                                                    | .13 |  |

|   | 1.2              | Motivation, Objectives and Methodology                                                               | .14 |  |

|   | 1.3              | Organization of Thesis                                                                               | .14 |  |

| 2 | ME               | MORY INDUSTRY ANALYSIS                                                                               | 15  |  |

|   | 2.1              | What Is a Flash Memory?                                                                              | 15  |  |

|   | 2.1.             |                                                                                                      |     |  |

|   | 2.2              | Five-Forces Analysis                                                                                 | .17 |  |

|   | 2.3              | Intel as an Industry Player                                                                          | .22 |  |

|   | 2.3.             |                                                                                                      |     |  |

| 3 |                  | CTORY PHYSICS CONCEPTS                                                                               |     |  |

|   | 3.1              | Key Terminology                                                                                      |     |  |

|   | 3.2              | Variability                                                                                          | 29  |  |

|   | 3.2.             |                                                                                                      |     |  |

|   | 3.2.2            |                                                                                                      |     |  |

|   | 3.2.3            |                                                                                                      |     |  |

|   | 3.3              | Challenges for Operations Management in a Semiconductor Environment                                  |     |  |

| 4 |                  | RIABILITY ANALYSIS                                                                                   |     |  |

|   | 4.1              | Step 1 – Selecting Focus Area                                                                        |     |  |

|   | 4.1.1            | 8 T J                                                                                                |     |  |

|   | 4.2              | Step 2 – Analyzing Variability Components                                                            | 39  |  |

|   | 4.2.             |                                                                                                      |     |  |

|   | 4.2.2            |                                                                                                      |     |  |

|   | 4.2.3            |                                                                                                      | 44  |  |

|   | 4.3              | Step 3 – Identifying Improvement Opportunities                                                       |     |  |

|   | 4.3.1            | 1 0                                                                                                  |     |  |

|   |                  | <ul><li>3.1.1 Feeder operations</li><li>3.1.2 Starts Policy and Tool-Operation Dedications</li></ul> |     |  |

|   | 4.3.2            | • -                                                                                                  |     |  |

|   |                  | 3.2.1 Operator Behavior                                                                              |     |  |

|   | 4.               | 3.2.2 Preventive Maintenance                                                                         | 53  |  |

|   | 4.4              | Analysis Results and Recommendations                                                                 | 55  |  |

| 5 |            | NUFACTURING METRICS<br>Metrics at Fab11                    |     |

|---|------------|------------------------------------------------------------|-----|

|   | 5.1.       | 1 Weaknesses in Current Metrics<br>Metrics Recommendations | .59 |

| 6 | OR0<br>6.1 | GANIZATIONAL CHALLENGES<br>Cultural Factors                |     |

|   | 6.2        | Strategic Design and Political Tensions                    | 71  |

| 7 |            | /MARY                                                      |     |

|   | 7.1        | Thesis Conclusions and Key Lessons Learned                 |     |

|   | 7.2        | Suggestions for Future Work                                |     |

| A | ppendix    | ς Ι                                                        | 76  |

# LIST OF FIGURES

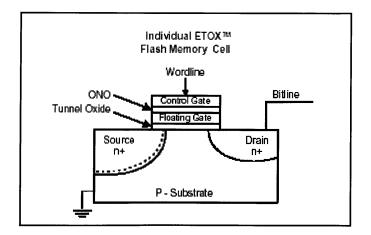

| Figure 1. Structure of a flash memory cell                                                     |

|------------------------------------------------------------------------------------------------|

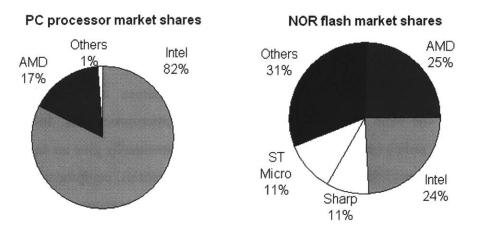

| Figure 2. Industry players and market shares in PC processors and NOR flash. <sup>,10</sup> 19 |

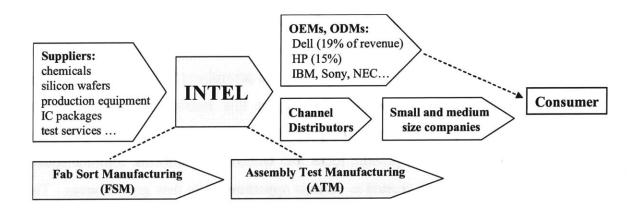

| Figure 3. Intel's operational value chain24                                                    |

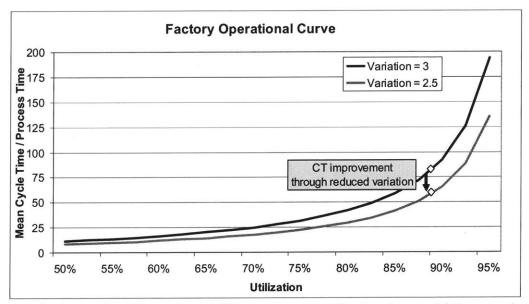

| Figure 4. The effect of variability on system cycle time (www.fabtime.com)29                   |

| Figure 5. Factory Physics VU analysis results for the main tool areas in the factory37         |

| Figure 6. A simplified lithography workstation layout                                          |

| Figure 7. Summary of lithography flow variability analysis for selected operations43           |

| Figure 8. Summary of lithography flow variability analysis for selected tools45                |

| Figure 9. Availability variation over time for selected lithography work stations              |

| Figure 10. Variability of arriving material flows into the lithography area classified by      |

| feeder tool type48                                                                             |

| Figure 11. An example illustrating the effect of tool-operation dedications on arrival         |

| variations50                                                                                   |

| Figure 12. Preventive maintenance durations by shift                                           |

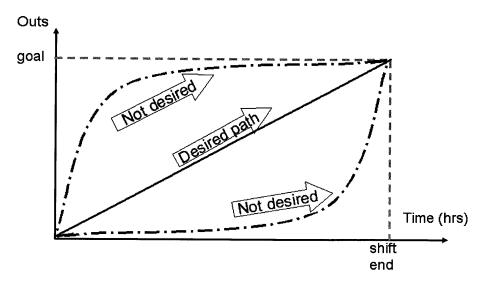

| Figure 13. An example of using an operational curve to track performance and goals62           |

| Figure 14. A method developed in-house to measure manufacturing flow variability63             |

| Figure 15. The preferred manufacturing flow at a work station                                  |

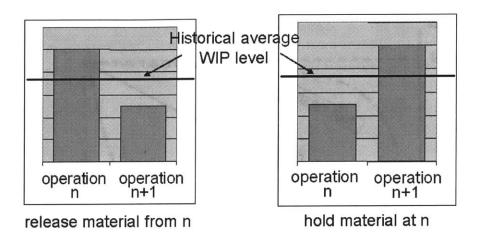

| Figure 16. Concept of "Minimum Inventory Variability" by Collins and Hoppensteadt              |

| (1997)                                                                                         |

# LIST OF TABLES

| Table 1. Historical and predicted future performance of Intel financial metrics    | 25        |

|------------------------------------------------------------------------------------|-----------|

| Table 2. Main topics contributing to variability in the lithography area according | g to area |

| supervisors                                                                        | 47        |

| Table 3. The main performance metrics used in Fab11                                | 58        |

| Table 4. Examples of improved manufacturing metrics.                               | 61        |

#### **1** INTRODUCTION

#### 1.1 PROBLEM STATEMENT

Intel Corporation is the world's largest semiconductor manufacturer. The company manufactures microprocessors (MPUs), flash memories, chipsets and related software for computers, servers, and consumer electronic products. This thesis work was conducted in Fab11 in Rio Rancho, New Mexico, where Intel manufactures mainly flash memory products. Flash is a non-volatile memory chip that holds its content even when the power in the mother device has been switched off. Flash memory is manufactured using standard semiconductor manufacturing technologies: implant and diffusion to introduce elements into silicon to form n- and p-type regions, photolithography to pattern various layer structures, and metallization to form conductive electrical circuitry.

The industry environment for flash products is very different than that for microprocessors. Intel has been the dominant player in the microprocessor industry since the company was founded. Conversely, in the highly segmented commodity-like flash business the company faces new challenges. Intense price competition and lower profit margins create strong pressures for manufacturers to manage their cost structures effectively. Since depreciation cost from capital equipment is one of the main components contributing to silicon wafer cost, tool utilization has become an important measure. In addition, timing of market entry and flexibility to respond to volatile customer demand create pressures for short manufacturing cycle times.

According to Factory Physics <sup>1</sup>, there is an inherent conflict with high tool utilization and low cycle time; cycle time approaches infinity when utilization approaches 100%. Cycle time is comprised of process time and queue time. From the customer's point of view only process time is value adding time. Queuing time on the other hand is non-value adding and can be introduced to the system due to a variety of reasons, such as waiting for an operator or a tool to become available. Queuing time is dependent among other things on variability in the manufacturing environment.

<sup>&</sup>lt;sup>1</sup> W.J. Hopp, M.L. Spearman: Factory Physics, 2<sup>nd</sup> Edition, McGraw-Hill 2001 New York

Fab11 needs to stay competitive in the intense flash industry environment. This can only be accomplished by achieving a low cost but highly flexible manufacturing environment. Currently, wafer cost is the dominating driver in the organization, which results in high forced tool utilizations. At the same time the factory suffers from high cycle times. In addition, current performance metrics in use in the facility might be promoting the wrong kind of behavior and hiding critical problems instead of supporting the factory mission.

#### 1.2 MOTIVATION, OBJECTIVES AND METHODOLOGY

The purpose of this thesis work was to help Fab11 to achieve operational excellence by reducing barriers to improved cycle time. The work focused on analyzing manufacturing variability and related performance metrics. The primary goals were to understand and reduce the sources of manufacturing variability, as well as to help Fab11 understand how to improve their manufacturing performance measurement systems.

The variability analysis work was done as part of an existing operations improvement task force team. The analysis used concepts both from Factory Physics as well as from lean manufacturing. Factory Physics methods were chosen since they supported on-going research activities in the organization. The metrics alignment work was conducted alongside with a company internal metrics team. Material was found from company internal documents and literature, as well as through interviews and direct observations on the floor level.

#### 1.3 ORGANIZATION OF THESIS

Chapter 1 presented the problem statement, objectives and methodologies. Chapter 2 will discuss flash memory technology and industry dynamics. Factory Physics concepts are introduced in more detail in Chapter 3. Chapter 4 focuses on variability analysis and presents the developed analysis method together with results and recommendations. Chapter 5 discusses the importance of metrics and presents weaknesses and improvement recommendations for the current metrics system. Organizational challenges for change implementation are covered in Chapter 6, and finally, thesis conclusions and key insights are given in Chapter 7.

#### 2 MEMORY INDUSTRY ANALYSIS

This chapter discusses flash memory structure, technologies as well as the dynamics in flash memory industry.

## 2.1 WHAT IS A FLASH MEMORY?

Flash is a non-volatile memory chip that holds its content even when the power in the mother device has been switched off. Flash is a form of EEPROM (electrically erasable programmable read-only-memory), which means that memory units, called blocks, can be electrically erased and reprogrammed. Unlike in EEPROM, flash allows multiple memory cells to be erased or reprogrammed in one operation which gives it higher speed. Other benefits include reliability, low-cost, high-density storage, operation at low voltages and retaining data when power is off. Typical applications of flash memory include memory sticks, digital cameras, cell phones, printers, and handheld computers.<sup>2,3</sup>

Flash memory is manufactured using standard semiconductor manufacturing processes: wafer fabrication, electrical die sort, die packaging and device testing. Flash memory cell structure is presented in the following figure:

Figure 1. Structure of a flash memory cell.<sup>4</sup>

<sup>&</sup>lt;sup>2</sup> http://en.wikipedia.org/wiki/Flash\_memory

<sup>&</sup>lt;sup>3</sup> "What is flash memory?" October 2002. http://www.intel.com/design/flash/articles/what.htm

<sup>&</sup>lt;sup>4</sup> www.intel.com

During the wafer fabrication phase memory cell structures are built on "empty" silicon wafers using standard semiconductor manufacturing technologies, such as implant and diffusion to introduce elements into silicon to form n- and p-type regions, photolithography to pattern various layer structures, and metallization to form conductive electrical circuitry. Through these processes each memory cell receives its physical transistor structure with source, drain and gate regions, as was shown in Figure 1. Hundreds of individual memory dies are formed on one silicon wafer. Wafer fabrication operations are comprised of hundreds of highly sensitive process steps. Though all dies on a wafer go through the same manufacturing flow, exposure on different areas on the silicon wafer surface might differ. Therefore, functional performance level of individual dies are classified into different product groups based on their performance. After sort dies are packaged to make them easier to test, to handle and to assemble by the end customer, for example a camera manufacturer.

#### 2.1.1 Flash Memory Technologies

Flash memory comes in two different types: NOR (Not Or) which is traditionally used for code storage (e.g. operating systems), and NAND (Not And) which is suitable for data storage (e.g. digital pictures). The names refer to the type of Bolean algebra logic operations used in storage cells.

NOR flash was invented by Intel in 1988. NOR is a high read speed type with full memory interface that allows random access to any cell location. This makes it suitable for storage of program code that needs to be infrequently updated. NAND flash was developed by Samsung and Toshiba in 1989. It is fast erase and write type which makes it more suitable for mass-storage devices that experience consistent need to update information, like memory cards in digital cameras. NAND has a significant cost-performance advantage over NOR, since NAND has lower cost per bit resulting from smaller physical size of memory cells. NAND can also achieve considerably higher memory densities: up to several Giga bytes vs. NOR Mega byte range. <sup>5</sup>

<sup>&</sup>lt;sup>5</sup> http://en.wikipedia.org/wiki/Flash\_memory

#### 2.2 FIVE-FORCES ANALYSIS

Semiconductor Industry Association (SIA) reported an 18% growth in semiconductor sales between 2002 and 2003. The estimate for 2004 showed a 28% growth from 2003, resulting in the overall semiconductor industry size of \$214 billion. Predictions for future vary, but the SIA anticipated the sales to be \$223 billion in 2005, \$221 billion in 2006 and around \$250 billion in 2007. Semiconductor industry is highly cyclical, and industry trends have been observed to follow closely the overall economic trends. This relationship is understandable, since the overall economic environment affects the demand of computers and consumer electronic products which are the main users of semiconductor products. While personal computers and large computer systems remain critical market segments, other segments like communications, handheld devices and automotive applications have experienced a rapid growth. <sup>6</sup>

#### Barriers To Entry

Intel's co-founder Gordon Moore forecasted in his famous law from 1965 that the number of transistors per chip will double every 2 years. Instead of a consumer pull, semiconductor industry has been driven by Moore's law resulting in technology push and continuous need to invest in manufacturing process technologies. For chip manufacturers Moore's law means exponentially growing transistor counts per chip, increased number of chips per wafer and thus increased revenue per wafer. However, shrinking chip feature sizes mean also increased investments and technical challenges. A good example is lithography, a key technology driver for the industry, which continuously needs to develop to enable the patterning of smaller and smaller device dimensions. Today top of the line lithography tools used in volume production cost around \$15 million a piece and use 193nm light sources to pattern average feature sizes of 90nm. Further investments in new photolithography technologies, such as EUV (extreme ultraviolet), are needed to reach average feature sizes of around 30nm.<sup>7</sup>

<sup>&</sup>lt;sup>6</sup> M. Singer: "Report Chills Chip Futures", http://www.internews.com/infra/article.php/3379791

<sup>&</sup>lt;sup>7</sup> www.news.com: "Intel sheds light on future chip technology", August 1, 2004.

In 2003, the industry leader Intel spent \$3.7 billion on capital investments and \$4.4 billion on R&D. The majority of the capital investments were spent on factories and equipment. Continuous investments in advanced manufacturing process technology enable Intel to increase uniqueness of its products: shrink transistor sizes and increase the number of transistors per chip, decrease the size of a chip or offer new features such as increased processing speed, lower power consumption or lower manufacturing cost. As an example, new 300mm wafer process yields twice the number of dies per wafer than older 200mm process, having thus a significant impact on manufacturing economies.<sup>8</sup> Older tool generations lack technical capability and manufacturing economies. The steep learning curve requiring high continuous investments in manufacturing process technology, high level of required technical knowledge as well as the dominant position of Intel in the market place can be seen as being the main barriers of entry for the microprocessor industry.

However, it is important to notice that the industry environment for flash products is very different from microprocessors. Microprocessors, such as Pentium chips, are high end and hard to manufacture, whereas flash is lower technology and can be seen as being more of a commodity. Due to these lower production technology requirements learning curve and capital requirements are lower making it easier for companies to enter the market. Some companies even function "fabless" meaning that they do not have any manufacturing facilities. Due to lower barriers to entry and positive future demand predictions, several players have entered the markets making the flash industry much more segmented than the microprocessor industry.

#### Competition

In the microprocessor industry barriers to entry have significantly limited competition. Intel, who invented the microprocessor, has been the dominant player in the industry since the company was founded. Today, Intel still continues to dominate with its leading edge chip generations resulting in 82% market share in PC processors (see Figure 2).

<sup>&</sup>lt;sup>8</sup> Intel Annual Report 2003

Intel's main direct competitor in the microprocessor segment is AMD (Advanced Micro Devices) with 17% market share.<sup>8</sup>

In flash rivalry is intense. The leading suppliers in non-volatile memory business today are Samsung, Intel, Spansion (AMD – Fujitsu joint venture), ST Microelectronics and Toshiba. Samsung and Toshiba-Sandisk dominate the NAND market, whereas the main NOR players are AMD, Intel, ST Microelectronics, and Sharp. The relative market shares of the players are shown in Figure 2.

Figure 2. Industry players and market shares in PC processors and NOR flash. 9,10

Intel supplies only NOR flash. In addition to the large semiconductor companies the industry has few fabless players in both memory categories. Due to intense price competition and economies of scale, value capturing is hard and profit margins in flash are much lower than in microprocessors. To distribute risk the main flash players excluding Sandisk do not focus solely on flash, but have also other semiconductor products in their portfolios. It has been estimated that AMD gets 41% of its total revenues from flash products, STMicroelectronics 10%, and Samsung and Intel only 6%. <sup>10, 11</sup>

Price competition in flash creates strong pressures for the manufacturers to manage their cost structures effectively. Depreciation costs from capital equipment are the main

<sup>&</sup>lt;sup>9</sup> http://news.com.com/AMD+gains+market+share,+but+so+does+Intel/2100-1006\_3-5557740.html

<sup>&</sup>lt;sup>10</sup> JPMorgan Asia Pacific Equity Research, Bhavin Shah, Hong Kong 12 Jul 2004. "Tech Hardware Supply Chain"

<sup>&</sup>lt;sup>11</sup> WRHambrecht + CO, Semiconductor Devices Research Report, June 17, 2004

component contributing to wafer cost. To lower depreciation costs semiconductor manufacturers use the so called waterfall approach for their fabrication facilities: New facilities are used to manufacture high end microprocessor products which give the highest profit margins. As facilities and equipment grow older and it becomes too expensive to update them to accommodate to the demands of latest microprocessor generations, facilities start producing lower technology flash products. This way equipment can be used in-house as long as possible. The down side is that companies to which flash is only a minor part of total revenues will not be able to enjoy the economic and technical advances brought by state-of-the-art flash fabrication facilities.

#### Suppliers and Buyers

Semiconductor equipment manufacturers, chemical companies and silicon wafer manufacturers are the main suppliers for both flash and microprocessors. In spite of Intel's copy exactly policy (see Chapter 6), which might momentarily give an equipment supplier a benefit by providing an entry point to all Intel's facilities, equipment suppliers face intense competition and continuous need for technical innovation. Chemical and silicon wafer suppliers on the other hand are selling commodity products. Thus, only cutting-edge equipment suppliers are seen as having power in the value chain. Demand for semiconductor products is highly cyclical, and since equipment manufacturers are furthest away from the end consumer, they suffer the highest demand volatilities due to the bullwhip effect.

Traditionally microprocessor buyers have not had power over chip makers. However, the strengthening of AMD as a competitor has offered buyers a choice. As a result large OEM customers have increased their power to bargain over prices and delivery schedules. In the flash industry, buyers on the other hand tend to extract considerable value. Due to the cost pressures for their own products buyers select their flash supplier mainly based on price. Depending on the application, memory density, speed and physical chip size can also be important factors. The situation is especially tough during times when flash supply equals or exceeds demand, because existing flash manufacturers

are not able to establish very long term sales contracts with their customers. Flash inventories are expensive and face the risk of obsolescence.

#### Substitutes and Emerging Technologies

NOR flash memory products, that Intel also manufactures, have started to face a threat from NAND flash. Traditionally NOR has been the higher revenue generating segment in the flash markets; NOR 2004 revenues were around \$10 billion versus NAND around \$6 billion. However, NAND is predicted to take over NOR in 2007 with revenues of around \$12 billion. The rise in NAND revenues and demand comes from the increased data storage requirements for consumer electronics and handset devices. To compete with NAND, NOR players like Intel and AMD have developed their own high density data storage NOR products (StrataFlash and Mirrorbit) that use so called Multi-level cell (MLC) technology. Typically NOR products can only store one bit of data in one memory cell. MLC technology allows memory cells to store 2 bits of data thus doubling memory density with the same price. <sup>11</sup>

Semiconductor flash memories do not currently have direct substitutes. However, research is being conducted for several alternative technologies that might pose a threat in the longer term, especially once flash CMOS based process technology starts to approach its size limitations: <sup>12</sup>

- Magnetoresistive Random Access Memory (MRAM) is a non-volatile memory technology with high enough speed to become a potential replacement for flash. MRAM uses magnetic charge instead of electrical charge to store information in a magnetically polarized thin film. Other advantages are reduced cost and smaller size. MRAM technology is backed up by for example IBM, Motorola and Infineon.

- Ovonyx Unified Memory (OUM) uses a phase-changing thin film alloy to store information. The manufacturing process follows the traditional CMOS logic flow used in flash but requires fewer process steps. The resulting advantages are

<sup>&</sup>lt;sup>12</sup> WRHambrecht + CO, Semiconductor Devices Research Report, June 17, 2004

shorter cycle times and smaller die sizes. Intel is one of the investors in this technology.

- FeRAM (Ferroelectric RAM) has a ferroelectric capacitor and a MOS transistor. The structure is faster and has lower power consumption than existing flash technologies. Companies interested in this technology include for example Infineon and Samsung.

- Bistable polymer chains can be used to store information by switching their molecular structure from one stage to the other with electric field. Polymers will maintain their structure even when the electrical field is turned off. Such "smart" structures can be built molecule by molecule enabling application customized designs. In addition the technology has the potential for greater storage capacity with lower price. For example Intel, Samsung and IBM are investing in this technology.

#### 2.3 INTEL AS AN INDUSTRY PLAYER

Intel is the world's largest semiconductor manufacturer with 2003 revenues of \$30.1 billion. The company manufacturers microprocessors, flash memories, chipsets and related software for computers, servers, cellular phones, digital cameras and various other consumer electronics products. Intel was established in 1968 and has currently 78,000 employees. Intel has a global presence with 27% of 2003 revenues coming from the Americas, 24% from Europe, 9% from Japan and the remaining 40% from the rest of Asia Pacific. In the past 5 years the main shift in revenue source has been from the Americas to Asia Pacific, when countries like China have started investing heavily in their IT infrastructure.<sup>13</sup>

More than 75% of Intel's manufacturing was conducted in the US: California, Arizona, New Mexico, Massachusetts, Oregon and Colorado. The remaining 25% of manufacturing was done in Ireland and Israel. The majority of Intel's fabrication facilities use 200mm (8-inch) wafers. By the end of 2004 the company had three fabs using the new 300mm (12-inch) wafer process. In addition to the established 130nm line-width

<sup>&</sup>lt;sup>13</sup> Intel Annual Report 2003

process technology some factories are capable of producing microprocessors with the more advanced 90nm process. Flash memory is manufactured using 130nm and 180nm process technologies. In addition of being high volume, some facilities produce also a high mix of products. Intel tends to manufacture products in more than one facility at a time to reduce the supply capability risk. <sup>13</sup>

At the end of 2004 Intel was divided into two main operational units: The Architecture Group and The Communications Group. The Architecture Group contributed 87% of company's 2003 net revenue. <sup>14</sup> Intel's mission in 2004 was to "do a great job for customers, employees and stockholders by being the preeminent building block supplier to the worldwide Internet economy". To support this mission and new customer requirements, the company announced a significant reorganization of its business units in January 2005, switching from product focus into technology platforms. Simultaneously two new organizations were created to address opportunities in new growth areas. The new business units are <sup>15</sup>:

- The Mobility Group developing platforms for notebook PCs and handheld computing and communications devices

- The Digital Enterprise Group developing computing and communications infrastructure platforms for business customers

- The Digital Home Group developing computing and communications platforms for the emerging digital home, with emphasis on living room entertainment applications and consumer electronics devices

- The Digital Health Group developing products for healthcare research, diagnostics and personal healthcare

- The Channel Products Group focused on developing and selling Intel products to meet the needs of local markets worldwide

Intel's suppliers include a large number of raw material, process equipment and service providers. Intel supplies its products both directly to large Original Equipment

<sup>&</sup>lt;sup>14</sup> Intel Annual Report 2003

<sup>&</sup>lt;sup>15</sup> www.intel.com

Manufacturers (OEMs), Original Design Manufacturers (ODMs) and resellers as well as to small and medium size businesses via distributor channels. The channel distributor segment is especially important for Intel in emerging markets. The two Intel internal units are Fab Sort Manufacturing (FSM) and Assembly Test Manufacturing (ATM). FSM includes wafer processing, testing and sort, whereas ATM includes die testing and packaging. The following figure gives a simplified illustration of Intel's value chain: <sup>16</sup>

Figure 3. Intel's operational value chain.

Historically Intel has captured a lion's share of the microprocessor market value due to continuous technical innovations, lack of competitors, and smart positioning in the microprocessor value chain through "Intel Inside" supply strategy. As a result of its dominant position Intel has been able to capture high margins and control the speed of development by correctly timing the introduction of new chip versions. After the emergence of AMD Intel started facing competition in value capturing for the first time. In addition to large OEMs creating pricing pressures, the switch to lower profit margin products, like flash memory, has influenced company revenues.

To respond to emerging competition in microprocessors and to accommodate to the new competitive environment in flash products Intel has been investing heavily on value adding services and features, such as product architectures and platforms. A platform is a collection of silicon and software components that together add more value to the end

<sup>&</sup>lt;sup>16</sup> Citigroup Smith Barney: The Global Supply Chain Handbook v3.1. July 16, 2004. pp. 92

user than they do individually. The recent reorganization of business units is a clear signal of a new strategic direction. Platform strategy in flash is intended to change a commodity product into something more valuable to ease the pressures for low cost manufacturing. Other complementary assets include strong brand, worldwide sales and marketing network, process technology know-how and Intel Capital securing future innovations. Despite the maturing industry and new competitive environments, Intel is strongly positioned with complementary assets that could become a critical advantage over competitors in the future. Accordingly, the long term financial metric forecasts are good, as shown in the following table:

| Financial metric  | Historical performance<br>(1992-2003) | Forecast performance<br>(2004-2013) |

|-------------------|---------------------------------------|-------------------------------------|

| Revenue growth    | 16.6%                                 | 7.0%                                |

| Gross margins     | 55.9%                                 | 58.8%                               |

| Operating margins | 27.7%                                 | 32.3%                               |

| Average EPS       | \$0.66                                | \$1.66                              |

| EPS growth        | 15.6%                                 | 11.3%                               |

Table 1. Historical and predicted future performance of Intel financial metrics.<sup>17</sup>

## 2.3.1 Intel Fab11<sup>18</sup>

Intel's New Mexico site has 465,000 square feet or 9.7 football fields of clean room area, the largest continuous clean room in the world. The site incorporates two fabrication facilities, Fab11 and Fab11X. Fab11X is a leading edge facility producing 90nm line width microprocessors with 300mm wafer technology.

Fab11 is a 200mm wafer facility producing flash memory products. The facility has been operational since 1995. It has 300,000 square feet or 6 football fields of class 1 (1 particle per cubic feet of air) clean room area. The facility produces thousands of wafers per week, and shipped its 1 billionth die in November 2002. In addition to high volume Fab11 has also high mix production of flash, integrated flash and chip set memory

<sup>&</sup>lt;sup>17</sup> Bernstein Research Call, US Semiconductors, August 9, 2004

<sup>&</sup>lt;sup>18</sup> www.intel.com and company internal material

products. Product lines include flash memories ranging from single chip capacities from 8Mbits up to 256Mbits. The main product line devices are used in cellular phones.

The Fab11 mission today is to "be Intel's most flexible, highest volume, and lowest cost manufacturer of leading edge products". This mission is well aligned with current market conditions but is very challenging. As was discussed earlier, the characteristics of the flash memory industry today are multiple players, intense price competition and low profit margins. Flexibility is important to be able to quickly respond to changing market demand and customer order requirements. High volumes are needed for dilution of capital costs. Low cost structure again is critical for successful price competition. Leading edge products require continuous technology development but act as a competitive advantage and barriers to entry against competitors. The mission is even more challenging considering the high volume / high product mix manufacturing environment in Fab11. Today Fab11 is striving to meet all three goals simultaneously. However, as will be seen in the following chapters there is an inherent conflict between flexibility, high volume and low cost.

#### **3 FACTORY PHYSICS CONCEPTS**

Factory Physics, as described by Hopp and Spearman, provides a set of fundamentals to explain the relationships and behaviors that exist in a manufacturing operation. Factory Physics methodologies give tools to analyze existing operations, design improvement efforts and analyze tradeoffs. The following chapters shortly introduce the basic terminology and key concepts.

## 3.1 KEY TERMINOLOGY<sup>19</sup>

Nominal process time  $t_0$  is the average time to complete one job without any distractions in the process (a.k.a. theoretical process time, raw process time).

*Availability* A is defined as the long term fraction of a time when a work station is not down for repair. In other words if tool availability is 80%, then for 80% of the time the tool is available for running production.

*Effective process time*  $t_e$  is the average time to complete one job including distractions such as setups, downtime, etc. Effective process time can be expressed using nominal process time and availability:

$$t_e = \frac{t_0}{A} \qquad \qquad \text{Eq. (1)}$$

If availability is 100%, in other words a work station has no unplanned failures and is constantly operational except for planned downtime, effective process time equals natural process time. In practice, however, most work stations experience some amount of random unplanned outages which reduces availability. Effective process time takes these events into account and is therefore longer than the theoretical process time.

*Utilization* u is defined as the probability a work station is busy. This includes the time when the work station is working on jobs or has parts waiting but is unable to process

<sup>&</sup>lt;sup>19</sup> W.J. Hopp, M.L. Spearman: Factory Physics, 2<sup>nd</sup> Edition, McGraw-Hill 2001 New York

them due to setup or machine failure. Utilization can be described using arrival rate  $r_a$  and effective tool process time  $t_e$ :

$$u = r_a t_e Eq. (2)$$

....

If utilization is more than one, a work station is always busy. Jobs arrive at the station faster than they can be processed,  $r_a > t_e$ . If utilization is << 1, jobs are processed faster than they arrive and work station experiences idle time due to lack of material.

Utilization term U is expressed as

$$U = \frac{1}{1-u}$$

Eq. (3)

*Cycle time* CT is the average time a job spends in the system, starting from the time it enters to when it exits. Cycle time is composed of mean effective process time and queuing time  $CT_q$ :

$$CT = t_e + CT_a$$

Eq. (4)

From a customer point of view only effective process time is value adding. Queuing time on the other hand is non-value adding and can be introduced to the system due to variety of reasons, for example waiting for an operator or a tool to become available. Queuing time depends on effective process time, variability V and utilization term, as shown in the following equation. Variability is discussed more in Chapter 3.2.

$$CT_q = VUt_e$$

Eq. (5)

Thus combining the previous two equations, cycle time can be expressed as:

$$CT = t_e + VUt_e = t_e(1 + VU)$$

Eq. (6)

*Little's law* is a fundamental relationship between cycle time, work in process WIP (inventory between start and end of the manufacturing line) and throughput TH (output of a production process):

$$WIP = CT * TH$$

Eq. (7)

This useful but some times counterintuitive relationship states that WIP levels depend on cycle time and throughput. Thus, if you want to keep throughput constant in your manufacturing system but reduce cycle time, you should reduce inventory levels.

#### 3.2 VARIABILITY <sup>20</sup>

From Equations 3 and 6 above it follows that

$$\frac{CT}{t_e} = V(\frac{1}{1-u}) + 1$$

Eq. (8)

The term  $CT/t_e$  is the so called cycle time X-factor, since it describes the relationship between the realized cycle time and the goal (effective process time). The higher the Xfactor, the more there is queuing time in the process. From the equation it can be seen that when utilization approaches 100%, cycle time factor approaches infinity. In other words high tool utilization is going to cost you in longer cycle times.

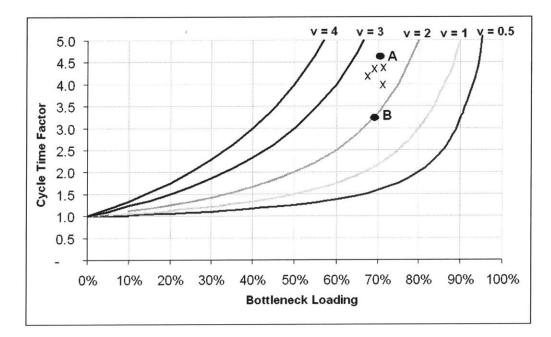

In addition to utilization, as was shown in Equation 6, cycle time depends also on variability V. In practice, process times are never quite steady but they vary around some average value due to for example unexpected equipment breakages, delays in operator availabilities or deviations in material quality. In other words, there is variability in the system which creates queuing time. The relationship between utilization, cycle time and variability can be illustrated with the following factory characteristic curves:

Figure 4. The effect of variability on system cycle time (www.fabtime.com).

<sup>&</sup>lt;sup>20</sup> W.J. Hopp, M.L. Spearman: Factory Physics, 2<sup>nd</sup> Edition, McGraw-Hill 2001 New York

Figure 4 illustrates two identical manufacturing environments that experience different degrees of variability. At a fixed utilization level the environment with more variability experiences higher cycle time than the factory environment with less variability. Thus reductions in cycle time while keeping utilization constant can be achieved by reducing variability.

Three elements can be used to buffer manufacturing system against variability: inventory, capacity and cycle time. Increasing variability always degrades the performance of a production system, but the three buffers make it possible to choose how variability will affect manufacturing. Choosing the right buffer strategy depends on the production environment and the overall business strategy of the company. In a manufacturing environment where timely customer delivery is crucial, variability should not be buffered with cycle time but either with increased capacity and/or increased inventory levels (increases in invested capital). Similarly, if additional capacity is extremely expensive, the system can accommodate to variability with increased cycle time and/or increased inventory levels. However, accommodating to variability is always a worse option than trying to reduce it, since buffering will cost in high inventory levels, access capacity, or prolonged cycle times.

Variability represents things that are not normal; deviations from the average. Variability is thus a description of a distribution and can be quantified using the term coefficient of variation, c, which is defined as sample standard deviation divided by sample mean:

$$c_e = \frac{s_e}{x_e} \qquad \qquad \text{Eq. (9)}$$

Factory Physics has defined three different variability classes: low variability (c < 0.75); moderate variability ( $0.75 \le c < 1.33$ ); and high variability ( $c \ge 1.33$ ).

#### 3.2.1 Variability in Manufacturing Flow

Variability of a work station depends on two factors: arriving material flow and actual processing time at the work station. Variations in the arriving material flow are described using a distribution of times-between-arrivals. Variations in the work station's effective

process time are described using a distribution of process times. Thus variation can be expressed as:

$$V = \frac{(c_a)^2}{2} + \frac{(c_e)^2}{2}$$

Eq. (10)

where  $c_a = \text{coefficient}$  of variation of time-between-arrivals; and  $c_e = \text{coefficient}$  of variation of effective process time.

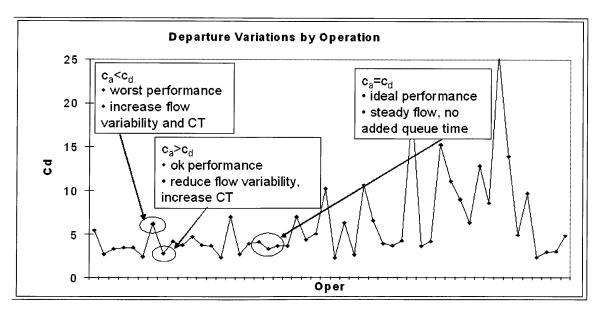

Variability tends to propagate through the manufacturing flow. Departures from a work station are arrivals to the next work station downstream; thus ignoring stockers and transportation, variations in departures at tool n become arrival variation for tool n+1. As a result, variability early in the process flow can be seen being worse than variability later in the process.

Variability of departures  $(c_d)$  depends on that of the arrival flow  $(c_a)$  and effective process time  $(c_e)$ . The relationship depends also on tool utilization and can be described with the following equation:

$$c_d^2 = u^2 c_e^2 + (1 - u^2) c_a^2$$

Eq. (11)

From this equation it can be seen that as utilization increases, effective process time variation becomes more significant for departure variation than variation in arrivals. Therefore, for a low utilization tool, regardless of the tool's own effective process time variability, departure variability from that tool tends to repeat the variability of the arrivals to that tool. In other words, low utilization tools do not change manufacturing flow variability, but simply just pass it on. On the other hand, high utilization tools with high effective process time variability have high departure variability regardless of the arrival variability. High utilization tools with low effective process time variability have low departure variability regardless of the arrival variability. In other words, flow variability through a high utilization tool reflects the tool's own effective process time variability.

It is important to notice that variability discussed in this study occurs in the manufacturing environment due to poor operations management. It increases non-value

adding queuing time and is therefore highly undesirable. This type of variability is different than variability that has been introduced into the system as part of a strategic choice by the company; for example to increase sales through more product variations or customization.

As was shown earlier, work station variability depends on variations in arrivals and process times. The following chapters discuss the main sources of variability in these two areas.

#### 3.2.2 Sources of Arrival Variability

Typical sources of arrival variability are

- upstream variability

- batching

- starts policy

Upstream variability is created for example during tool outages in upstream operations. This can be a significant source of arrival variability for a work station if the upstream station happens to have a poor reliability.

Batching is another source of arrival variability in situations where downstream operations use different batch sizes than upstream operations. This is very typical in a semiconductor facility, since manufacturing equipment comes from multiple different vendors and has not been designed to handle equal batch sizes (same number of lots or wafers per operation). In such cases, the coefficient of variation for arrivals is not zero even when batches are delivered in regular intervals. This is due to the different interarrival times that batch parts see: for the first part in a batch interarrival time is the time since the previous batch was delivered, whereas for all the remaining parts in the batch it is zero (since they all arrived at the same time with the first part).

Starts policy is a third potential source of arrival variability. It refers to the schedule how new material, in the case of semiconductor facility empty wafers, is released to the line. Often start schedules are controlled by demand forecasts. In volatile industries demand volumes can vary dramatically causing variations in material release schedules. From variability point of view, steady material release reflecting the capacity of the first work station would be the best policy.

### 3.2.3 Sources of Effective Process Time Variability

Typical sources of effective process time variability are

- variations in raw process time

- unscheduled outages, repair times

- operator availability and material handling

- scheduled set ups, preventive maintenance

- rework, priority lots

Variability in raw processing time, also called natural variation, is typical in manual operations. In highly automated environments raw process time variations tend to be low, but can be caused, for example, by differences in machine or material qualities.

Unscheduled outages can be caused for example by unexpected machine failures. The effect of unscheduled failures as well as scheduled maintenance work on variability is significant but often underestimated and poorly understood. According to Factory Physics long and infrequent repairs induce more variability on effective process time than short and frequent ones, since higher levels of work in process buffers are needed to prevent downstream operations from starving during long repairs. Higher WIP in line, as stated by Little's law, results in higher cycle times if throughput (bottle neck rate) remains constant.

Operator availability might be a problem in environments that have experienced head count cuts or do not have optimized labor resources. If operators need to run multiple tools simultaneously, they might not be able to program equipment or release finished material forward on time, thus increasing queuing time. Poorly managed break schedules might also cause unnecessary pauses in production.

In a high product mix environment setups could be frequently required due to product customization. Operator instructions or product-tool allocations might not be optimal resulting in too many setups and inefficient use of capacity. In addition, rework and priority lots which are typical in a semiconductor manufacturing environment tend to distract the manufacturing flow and cause variability.

# 3.3 CHALLENGES FOR OPERATIONS MANAGEMENT IN A SEMICONDUCTOR ENVIRONMENT

As became apparent from chapter 2, the main competitive drivers in the flash industry are flexibility and price. Flexibility and ability to respond rapidly to changing demand drives short cycle times, whereas low price drives high tool utilizations. As was seen from Figure 4, it is impossible to achieve 100% utilization while having low cycle times. Finding the right balance between these two drivers seems to be a major challenge in many semiconductor fabrication facilities.

Cost is often the main driver also for manufacturing operations. Extremely high capital investments and the way wafer costs are calculated leads to high tool utilizations. High utilization together with variability causes long cycle times with a high proportion of queuing time. Long cycle times can result in several problems. According to Little's law increased cycle times cause the WIP levels to increase, assuming that bottle neck rate (throughput) stays constant. This excess inventory ties up capital and causes losses due to decreased yield and increased risk of material becoming obsolete. If cycle times become longer than customer lead times, material has to be released into the factory based on demand forecast instead of secured orders. These forecasts could be very inaccurate in the rapidly changing environments resulting in poor order fulfillment or excess inventory.

Semiconductor manufacturing environments suffer also from other characters that make efficient operations management challenging. The manufacturing flow is very complicated due to the high number of re-entry and rework operations as well as priority lots. In this complex flow there is typically no one bottleneck tool or operation, but the bottleneck tends to shift depending on tool excursions. Over time Fab11 has gone through capacity changes, tool purchases and technology improvements which further complicate bottle neck identification. In addition, according to company terms, Fab11 has a high mix - high volume manufacturing environment. Volumes for different product series also vary

greatly. Due to the waterfall principle (see Chapter 2) the facility has a collection of aging machines that have different technical capabilities and that suffer from unscheduled outages. Data collection systems are also not as sophisticated as in newer facilities and fail to capture some useful operational details.

Fab11 staff hopes that Factory Physics principles will help them to get a better understanding of their manufacturing system and to identify improvement opportunities in order to survive in the increasingly competitive environment. However, the major challenge will not be to understand Factory Physics concepts, but to change current metrics and ways of thinking, and to overcome change resistance in the organization. The following chapters describe the methods and results from analyzing variability in the manufacturing flow with Factory Physics concepts, as well as the challenges of implementing change for the current performance metrics system and organization.

#### 4 VARIABILITY ANALYSIS

The concepts introduced in the previous chapter were used to develop a process for analyzing manufacturing flow variability in Fab11. The three main steps in the process were:

- 1. Find an area in the factory that is potentially suffering from high variability using Factory Physics analysis methods.

- 2. Analyze flow variability factors in the selected area (arrivals and process time) to find the major sources of variation.

- 3. Identify improvement opportunities.

The following chapters describe the detailed process steps, analysis methods, results and recommendations.

#### 4.1 STEP 1 – SELECTING FOCUS AREA

The overall factory analysis was done using a method developed by Factory Physics. From Equation 6 it follows that

$$VU = \frac{CT}{t_e} - 1$$

Eq. (12)

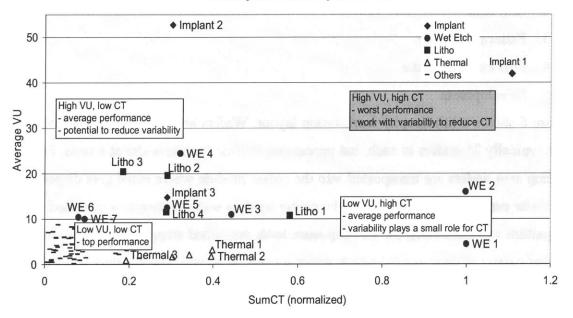

Since true cycle times and effective process times (goals) were recorded in the company data base, VU values could easily be calculated. In this case, effective process time was a fixed value, whereas cycle times were true average lot process durations varying from day-to-day. Using a data collection period of 13 weeks and grouping individual operations under tool areas, the graph shown in Figure 5 was produced.

Data points represent tool areas and each data point includes several tools. For example WE1 is comprised of type X tools in the wet etch area; WE2 represents type Y tools in the same area. VU value is plotted on the y-axis and normalized true cycle times are on the x-axis. Since  $VU \sim$  (true cycle time / goal cycle time), the term can be seen as a cycle time factor: the higher the value is, the worse the true cycle time performance is when compared to goal. In other words, the more queuing there is in total cycle time. Tool

areas located on the right hand side of the graph have the highest total cycle time. Thus in order to reduce the overall product cycle time, focus should be placed on fixing first the tool areas in the upper right hand corner of the graph, with high VU factor and high cycle times. Reducing variability in these tool areas would result in biggest time savings in the overall product cycle time.

#### VU Analysis Results by Tool Area

Figure 5. Factory Physics VU analysis results for the main tool areas in the factory.

Based on the analysis, the worst tool areas were found from implant and wet etch operations. However, since task forces to fix performance were already in place in these areas, the third worst area, lithography (litho), was chosen as the focus for this work. Lithography area was seen as an important target due to its importance for the overall manufacturing flow (high number of re-entry) and due to the upcoming capacity changes: changes occurring in the first half of 2005 will cause a 35% increase in the number of operations per tool, assuming current product mix. Litho area supervisors were familiar with lean manufacturing concepts and together with the operators were known to be supportive for the project. Additionally, the lithography area is often seen as the desired bottleneck for the factory due to most expensive equipment. To make the most of the investments tool utilizations are kept high which often creates queuing time for the process.

#### 4.1.1 Lithography Area Introduction

Silicon dies are comprised of several layers of different patterning. When layers are built on top of each other, the result is a three dimensional structure of connected wiring. Lithography is the transfer of a layer pattern from a reticle (mask) onto silicon wafer coated with photosensitive resist. The simplified process flow is:

- 1. Resist coat

- 2. Soft bake

- 3. Pattern exposure

- 4. Post exposure bake

- 5. Development

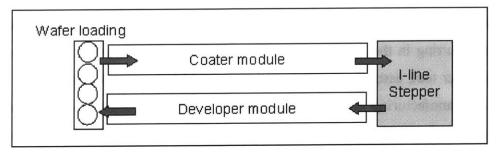

Figure 6 shows a lithography workstation layout. Wafers are loaded into the tool in lots with typically 25 wafers in each, but processing is done for one wafer at a time. From the loading area wafers are transported into the coater module where resist gets dispensed on the wafer surface (steps 1-2). From the coater module wafers move to a so called stepper for pattern exposure (step 3). The exposure tools are called steppers since they expose a smaller cluster of dies, not the whole wafer surface, at a time. The steppers studied in this work use the "I-line" ultra violet wavelength of 365nm. After exposure wafers are moved to the developer unit where the patterned resist is developed (steps 4-5).

In most cases the tool operator has to load and unload wafer lots manually but wafer transfer between the modules is done with automated serial arms. An operator controls the work station from a close by computer terminal.

Figure 6. A simplified lithography workstation layout.

# 4.2 STEP 2 – ANALYZING VARIABILITY COMPONENTS

As was discussed in chapter 3.2, manufacturing flow variability is comprised of three components: variation in the arriving material and variation in process times resulting in variation in departing material. In the litho area these components could be analyzed either by tool or by operation (wafer layer), since the area is running several re-entry operations. Both approaches were used to provide feedback on area performance, to find the major variability contributors, and to compare individual tools. Finally, tool availabilities over time were analyzed.

For both by tool and by operation approaches the analysis method was the same: first the time-between-arrivals, time-between-departures and process time data was collected. After that data points in each three areas were combined into distributions and coefficient-of-variations were calculated. Data was plotted on graphs to analyze the results. In the case of operations all needed data was readily available in the plant data bases, whereas in the case of tools parts of the data had to be statistically pooled.

### 4.2.1 Assumptions

# Data Collection Period

The data collection period should provide easy data handling but also serve the purpose of the analysis. Too short a time period, say few weeks, could give a false representation of the true situation due to a tool outage or a sick operator. On the other hand, the longer the time period the more the variations in the data get evened out and hidden in averages. Also, the amount of data increases rapidly with time. For this study a data collection period of thirteen weeks was chosen. For some variables this had to be reduced to ten weeks due to limitations in the data recording systems. All data was collected during August and October of 2004.

#### Product Mix

During the observed time period the factory was manufacturing several product types using four main process technologies. One technology was clearly dominating with 94% volume share. The next largest processes had 3% and 2% volume shares. Only these three technologies were included in variability calculations.

# Unit Quantity

Wafers move in lots of 25 through production. Data were collected on a per lot basis instead of a per wafer basis. Occasionally, a lot could have fewer than 25 wafers due to testing, failed products or engineering requests. A sample study revealed, however, that 97% of the lots moving through lithography area had 24 or more wafers. Thus the chosen per lot approach was believed to yield adequate accuracy.

#### Arrival Variation

The time-between-arrivals data was obtained using real time-between-departures data from the previous, i.e. feeding, operation. This assumption ignores lot transportation between work stations. Lots are moved with an automated material handling system that picks up finished lots from work stations and distributes them to central stockers. Operators then call lots from central stockers to their work stations. As a result timebetween-departures do not translate into time-between-arrivals with 100% accuracy. However, including the effects from transportation would have been very difficult. Lots are picked up and transported fairly rapidly, and thus believed not to cause too many inaccuracies for the lot interarrival times.

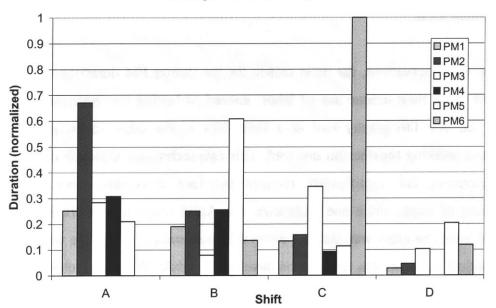

# **Tool Dedications**

Lithography tools are capable of running multiple different operations (layers), but setups might be required when switching between operations. Required setup times depend for example on what the operations in question are and how much time has passed since the tool ran the operation last time. Setup might be a simple and short mask change, or require a longer "send-ahead" lot to test process quality. Area supervisors are responsible for deciding what operations to run with which tools and in what order. To ease the operator decision making supervisors have created a tool-operation dedication matrix that tells which operations (layers) to run with which tools. Main considerations when creating these dedications are feeder operations' stocker locations, product volumes, technical tool capabilities and total available tool capacity.

The dedication matrix was used in the analysis to determine what operations the tools were running. It should be noticed that the reality might differ somewhat from the matrix depending on daily work in process levels and maintenance schedules. However, a sample test showed that tools obeyed their primary dedications whenever WIP was available. Also, the matrix changes over time to respond to changes in product mix and capacity, for example due to a long repair or new qualification requirements. Thus the dedications used in this analysis would not necessarily be valid for longer time periods.

### Pooling Arrival Distributions

The tool-operation dedication matrix (see above) was used to determine what operations were arriving to each tool. In most cases tools were dedicated to run more than one operation, in which case the following statistical pooling equations were used to combine several arrival distributions into one:

Stdev =

$$\sqrt{\frac{n_1 s_1^2 + n_2 s_2^2 + n_3 s_3^2 + \dots + n_k s_k^2}{n_1 + n_2 + n_3 + \dots + n_k}}$$

Eq. (13)

$$Average = \frac{n_1 \overline{x}_1 + n_2 \overline{x}_2 + n_3 \overline{x}_3 + ... + n_k \overline{x}_k}{n_1 + n_2 + n_3 + ... + n_k}$$

Eq. (14)

n = sample size (# of lots)

s = standard deviation

x = average

where

Interarrival times can be assumed to be exponential and thus memoryless, since it is hard to predict when the next arrival will occur. Thus these equations are a suitable method for pooling. However, the equation for pooled standard deviation assumes that arrival operations are independent. This is not the case in reality, since for example a power outage could influence arrivals from all operations. Yet finding out these correlations would be extremely difficult.

#### **Process Time Variation**

Factory Physics lists equations for calculating process time variations in cases where tools have random failures and require setups and rework. However, using these equations in practice turned out to be very complicated, mainly due to lack of data and slightly different definitions for availability and utilization between Intel and Factory Physics. Thus only raw process times ("move out – move in") were chosen to represent process time data. This data does not take into account variability caused by disturbances in availability (such as unscheduled outages). Therefore availability variability was studied separately.

#### **Departure Variation**

Time-between-departures data was obtained from real movements recorded in the company data base, just like time-between-arrivals. Equation 11 could have been used to calculate departure variations. However, the equation gave different departure variation values than real data. The inaccuracies were believed to be caused by utilization and process time variation terms: Intel's definition for tool utilization is slightly different from Factory Physics definition. Also, as explained above, process time variations in this work were estimated slightly differently from Factory Physics approach. Thus real data for departures was seen as the most reliable method.

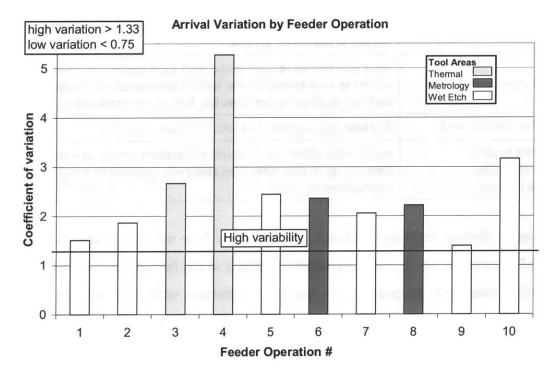

#### 4.2.2 Flow Variability Results by Operation

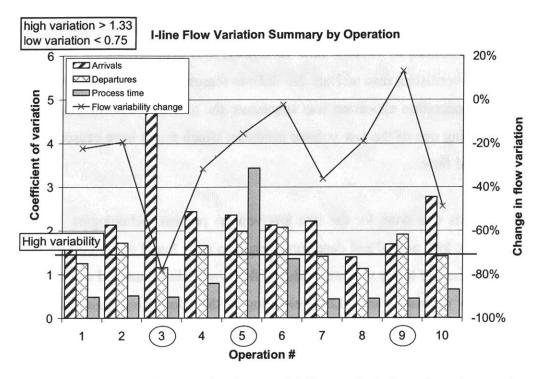

Figure 7 summarizes lithography flow variability results by operation for the main process technology. Only part of the operations was included for confidentiality. The figure lists ten litho operations (layers) on the x-axis. It should be noted that these are not consecutive wafer operations, but wafers visit other tool areas before returning into litho. The columns represent coefficient-of-variations for arriving material, departing material and process times. The solid line represents the change in flow variability, in other words the difference between arrival and departure variations. The straight horizontal line shows the limit for high variability; 1.33 as defined by Factory Physics.

Figure 7. Summary of lithography flow variability analysis for selected operations.

The first observation from the graph was that arrival variations were high for all operations. Departure variations were lower than arrival variations for all other operations except for operation number 9. Thus the lithography area in general seemed to be reducing the overall manufacturing flow variability. In most cases process time variations were low, which was the expected performance in a highly automated environment. According to chapter 3.2.1 the combination of flow variability reduction and low process time variations indicates high tool utilizations. Hence the lithography area could be a local bottleneck in the process. Being a bottleneck might be desirable due to the extremely high capital investments However, highly utilized tools are not always available when material arrives and thus tends to build queues. Thus the proportion of queuing time in the total cycle time is increased in this area.

Three operations were circled due to unique performances: operation number 3 had very high arrival variability. This indicated potential problems with the feeder operation or a poor match in batch sizes in the two adjacent operations. Operation number 5 had very high process time variability. The reason was likely a technical conversion work that was

interfering with production at the two tools running this operation. Finally, operation number 9 was noticed to increase flow variability, thus departures from the lithography area were less consistent than arrivals. No definite reason was identified for this behavior, but poor tool-operation allocation was suspected: the tool that was running operation 9 was also running one of the low volume products, which might have caused distractions for the material flow.

Similar analysis was done for the two low volume process technologies. Process time variations were low, arrival and departure variations were found out to be high but equal. Hence, in the case of lower volume products, flow variability remained constant and litho acted as a low utilization area. Lots belonging to the dominating high volume process technology had on average lower arrival variability than the lower volume products. This made sense since high volume lots were often prioritized over the other two technologies. Lower volume technologies tended to have higher standard deviations for time-between-arrivals due to more inconsistent material flow through the factory.

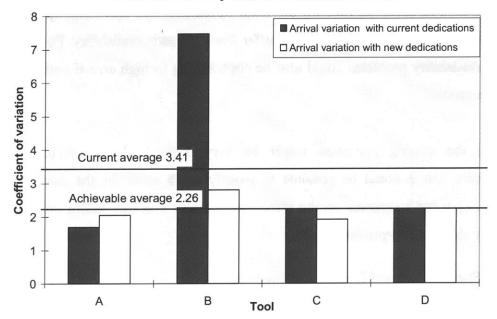

#### 4.2.3 Flow Variability Results by Tool

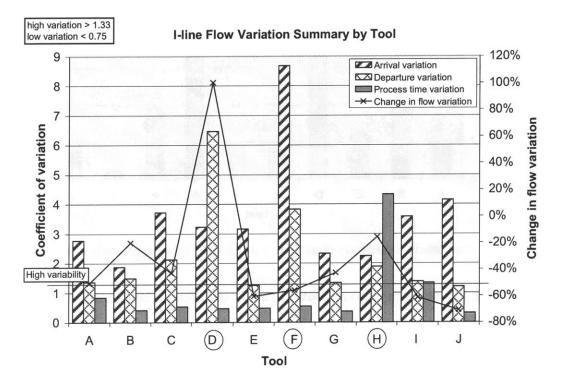

Figure 8 summarizes lithography flow variability results for individual tools including all the three process technologies. The graph is similar to the one shown in the previous chapter for operations.

Results were similar to the previous graph: overall the area seemed to be reducing manufacturing flow variability, and in general process time variations were small. Some problem tools could, however, be identified: Tool D was increasing overall flow variability since departing material flow had higher variations than arriving material flow. One of the reasons could have been operator behavior: the tool was running mainly one of the low volume products which tend to receive less attention from operators than the high volume main product. Tool F on the other hand was experiencing very high arrival variations. Though it might appear that this tool must have been running material from the worst feeder operation, surprisingly this was not the case. High arrival variability was caused by running a combination of high volume (low time-between-arrival average) and low volume (high standard deviation) products. Due to the way operations were pooled

into one distribution (Equations 13 and 14), the high standard deviations typical for the low volume arrivals caused the overall coefficient of variation to be very high. The three worst tools in terms of arrival variability were all running similar combinations. Tools running only low volume technology, even multiple layers, had lower arrival variations. This was an important finding and showed that high arrival variations could be avoided by better allocating operations from different product technologies to tools.

Figure 8. Summary of lithography flow variability analysis for selected tools.

Finally, tool H had very high process time variability. Average process times looked normal, so the variation was unlikely caused by continuous lack of operator resources. Standard deviation was very high, so there might have been few lots that experienced problematic qualifications or testing and were thus "trapped" at the tool for longer periods. Technical conversion at the tool might have caused the same issue, if lots were already logged in to the tool when conversion was started.

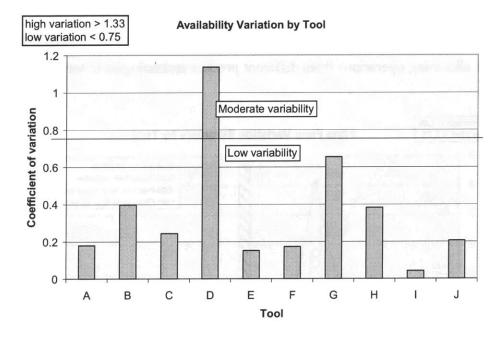

Due to company specific data recording systems a modified approach had to be used to analyze process time variations. The approach did not account for tool availabilities as the Factory Physics method would have done. Therefore tool availability variations over time were studied separately. Figure 9 summarizes availability variations for the selected tools.

Figure 9. Availability variation over time for selected lithography work stations.

As can be seen from the graph, tool availabilities do not seem to be a problem in this area since most tools experience low availability variations. Only tool D shows moderate variability. This tool was out of production 6 out of 13 weeks during the data collection period. This severe outage caused availability variability and weakened the tool performance. As was seen from Figure 8, tool D suffered from high departure variations which could be partly explained by this severe availability problem.

#### 4.3 STEP 3 – IDENTIFYING IMPROVEMENT OPPORTUNITIES