# Analyzing Sampling Methodologies in Semiconductor Manufacturing

by

**Richard M. Anthony**

Bachelor of Science in Mechanical Engineering Purdue University, 1994

Submitted to the Sloan School of Management and the Department of Mechanical Engineering in Partial Fulfillment of the Requirements for the Degrees of

> Master of Business Administration and Master of Science in Mechanical Engineering

In Conjunction with the Leaders for Manufacturing Program at the Massachusetts Institute of Technology June 2004 © 2004 Massachusetts Institute of Technology./All rights reserved.

Signature of Author Sloan School of Management Department of Mechanical Engineering May 7, 2004 Certified by\_ Sara L. Beckman, Thesis Advisor Senior Lecturer, Haas School of Business, University of California, Berkeley Certified by (Allayun David E. Hardt, Thesis Advisor Professor of Mechanical Engineering, Department of Mechanical Engineering And the second second Reviewed by Donald B. Rosenfield, Thesis Reader Director, Leaders for Manufacturing Program Senior Lecturer, Sloan School of Management Accepted by\_\_\_\_\_ Margaret C. Andrews, Executive Director of Masters Program Sloan School of Management Accepted by Ain Sonin, Charman, Graduating Committee Department of Mechanical Engineering MASSACHUSETTS INSTITUTE OF TECHNOLOGY JUL 0 1 2004

LIBRARIES

BARKER

- 2 -

# Analyzing Sampling Methodologies in Semiconductor Manufacturing

by

#### **Richard M. Anthony**

Submitted to the Sloan School of Management and the Department of Mechanical Engineering on May 7, 2004 in Partial Fulfillment of the Requirements for the Degrees of Master of Business Administration and Master of Science in Mechanical Engineering

#### ABSTRACT

This thesis describes work completed during an internship assignment at Intel Corporation's process development and wafer fabrication manufacturing facility in Santa Clara, California. At the highest level, this work relates to the importance of adequately creating and maintaining data within IT solutions in order to receive the full business benefit expected through the use of these systems.

More specifically, the project uses, as a case example, the sampling methodology used in the fab for metrology data collection to show that significant issues exist relating to the software application database and business processes concerning data accuracy and completeness. The organizational challenges contributing to this problem will also be discussed.

Various recommendations were undertaken to improve the application's effectiveness. As part of this effort, plans for an online reporting tool were developed allowing much greater visibility into the system's ongoing performance. Initial data updates and other improvements resulted in a reduction in both product cycle times and required labor hours for metrology operations.

Without a rigorous focus on the accuracy and completeness of data within manufacturing execution systems, the results of continuous improvement activities will be less than expected. Furthermore, sharing information relating to these projects across geographical boundaries and business units is vital to the success of manufacturing organizations.

Thesis Supervisors:

Sara L. Beckman Senior Lecturer, Haas School of Business, University of California, Berkeley

#### David E. Hardt

Professor of Mechanical Engineering, Department of Mechanical Engineering

Thesis Reader:

Donald B. Rosenfield

Director, Leaders for Manufacturing Program Senior Lecturer, Sloan School of Management

. - 4 -

#### ACKNOWLEDGEMENTS

I would like to thank the numerous co-workers, friends, and family members that have supported me during these last two years:

In particular, I would like to acknowledge the Leaders for Manufacturing program, a partnership between the Massachusetts Institute of Technology and major manufacturing partners, and the program's supporters for providing this opportunity for study at MIT. I would also like to thank my LFM classmates for helping to create a very unique learning environment.

I would like to give special recognition to my supporters and sponsors at Dell, especially Stephen Cook, John Egan, and Dick Hunter. I am very grateful for this wonderful opportunity and look forward to my continued career at Dell.

I would like to thank my thesis advisors, Sara Beckman and Dave Hardt, for their patience, guidance, and support during the internship and thesis writing experience.

I would like to extend my gratitude to Intel Corporation and employees at the D2 manufacturing facility for giving me the opportunity to carry out this work. Special thanks go to my sponsors, Chris Keith and Erik Stewart, and the entire Manufacturing Systems Engineering group (David Auchard, Hyung Kang, Joe McMorrow, and Chris Mullendore) for welcoming me into the group. I would also like to give my appreciation to John Powell for his advice and mentoring and Alan Wong for his active involvement during the project.

Most importantly, this work is dedicated to my wife, Michelle, and my daughter, Molly. Without their love, encouragement, and sacrifices this two-year adventure would not have been possible!

- 6 -

# TABLE OF CONTENTS

| Abstract                                                                     | 3   |

|------------------------------------------------------------------------------|-----|

| Acknowledgements                                                             | 5   |

| Table of Contents                                                            | 7   |

| Table of Figures                                                             | 9   |

| Table of Tables                                                              |     |

| Chapter 1 – Introduction & Overview                                          | .11 |

| 1.1 Project Overview                                                         |     |

| 1.2 Project Motivation                                                       |     |

| 1.3 Organization of the Thesis                                               |     |

| Chapter 2 – Project Background & Description                                 |     |

| 2.1 Intel Corporation Overview                                               |     |

| 2.1.1 Intel Operations                                                       |     |

| 2.1.2 Supply Chain Perspective for Semiconductor Manufacturing               |     |

| 2.2 Technology Development                                                   | .18 |

| 2.2.1 The Different Phases of Semiconductor Manufacturing                    |     |

| 2.2.2 California Technology Manufacturing                                    |     |

| 2.2.3 D2 Charter                                                             | 19  |

| 2.3 A Changing Market                                                        |     |

| 2.3.1 Intel Aggressively Enters the High Mix, Low Volume Market              |     |

| 2.3.2 Challenges of High Mix, Low Volume Manufacturing                       |     |

| 2.3.3 HMLV Summary                                                           | 22  |

| Chapter 3 – Semiconductor Manufacturing and Metrology                        | .23 |

| 3.1 Semiconductor Manufacturing                                              | .23 |

| 3.1.1 Manufacturing Overview                                                 | 23  |

| 3.1.2 Wafer Fabrication Processes and Equipment                              | 24  |

| 3.2 Semiconductor Metrology                                                  | .26 |

| 3.2.1 Photolithography (Litho) Metrology                                     | 27  |

| 3.2.2 Defect Metrology                                                       | 28  |

| Chapter 4 – Sampling Plans                                                   | .31 |

| 4.1 Acceptance Sampling                                                      |     |

| 4.2 Lot-by-lot Acceptance Sampling by Attributes                             |     |

| 4.2.1 Dodge-Romig Sampling Plans                                             |     |

| 4.2.2 Single Sampling Plan                                                   |     |

| 4.2.3 Double Sampling Plan                                                   | 33  |

| 4.2.4 Multiple Sampling Plan                                                 | 34  |

| 4.2.5 Switching Procedures between Normal, Tightened, and Reduced Inspection | 34  |

| 4.3 Acceptance Sampling by Variables                                         | .35 |

|                | inuous Sampling Plans                                           |    |

|----------------|-----------------------------------------------------------------|----|

|                | The First Continuous Sampling Plan, CSP-1                       |    |

|                | Continuous Sampling Plans, CSP-2 & CSP-3                        |    |

|                | Additional Continuous Sampling Plans                            |    |

| 1              | Lot Sampling Plans                                              |    |

|                | 's Sampling Process                                             |    |

|                | The SkipLot5 Application<br>The MOST Model                      |    |

|                |                                                                 |    |

| -              | Duality Audit                                                   |    |

|                | t is a Quality Audit?                                           |    |

|                | ysis of the SkipLot5 System                                     |    |

|                | Process for the D2 Measurement Rate Analysis                    |    |

|                | Measurement Rate Analysis Results Summary                       |    |

| -              | Lot5 System Quality Audit Overview                              |    |

| 5.3.1<br>5.3.2 | System Design<br>Business Processes                             |    |

|                | Ownership                                                       |    |

| 5.3.4          | Visibility into System's Performance                            |    |

|                | sient Data Study                                                |    |

| 5.4.1          | Current Practices                                               |    |

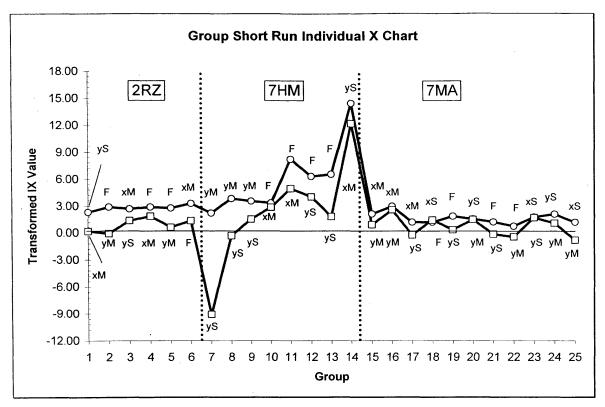

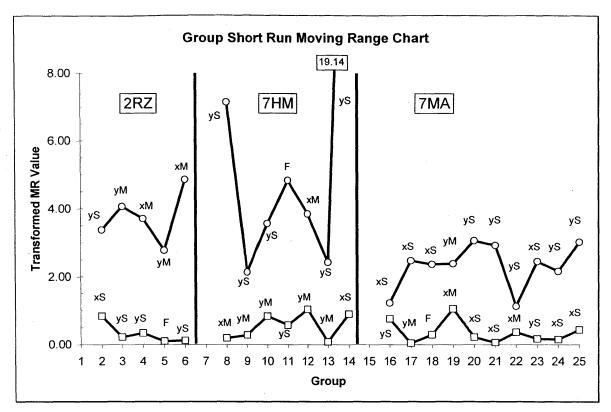

| 5.4.2          | The Group Short Run Individual X and Moving Range Control Chart |    |

| 5.4.3          | Interpretation of the Results                                   |    |

| Chapter 6 – C  | Organizational Change                                           | 65 |

| 6.1 Strat      | egic Design Lens                                                | 65 |

| 6.1.1          | Organizational Strategy                                         |    |

| 6.1.2          | Organizational Needs                                            |    |

| 6.1.3          | Organizational Structure                                        |    |

| 6.1.4          | Necessary Changes                                               |    |

|                | tical Lens                                                      |    |

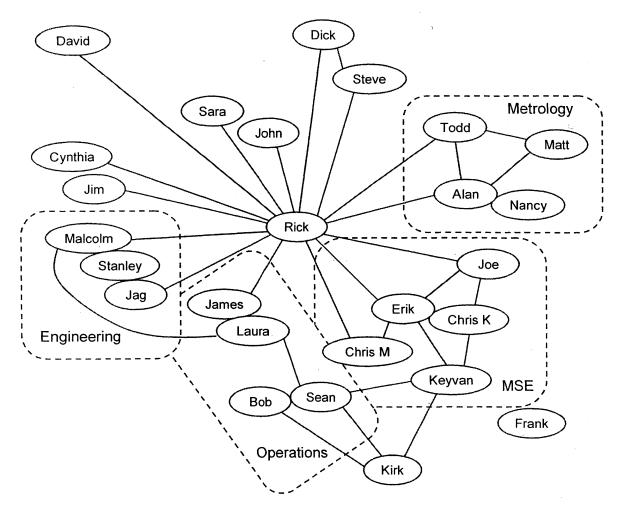

| 6.2.1          | Stakeholder Analysis                                            |    |

| 6.2.2          | Conflicts and Resolution                                        |    |

|                | ural Lens                                                       |    |

| 6.3.1          | Reinforcement of Norms, Values, and Basic Assumptions           |    |

| 6.3.2          | Information Sharing                                             |    |

|                | Recommendations and Concluding Remarks                          |    |

|                | ommendations                                                    |    |

| 7.1.1<br>7.1.2 | Short-Term Recommendations                                      |    |

|                | Long-Term Recommendations                                       |    |

|                | re Project Opportunity                                          |    |

|                | cluding Remarks                                                 | 41 |

|                | clusion                                                         |    |

| Bibliography   |                                                                 | 81 |

- 8 -

# TABLE OF FIGURES

| Figure 2.1: Semiconductor Manufacturing Supply Chain at Intel 1                        |     |

|----------------------------------------------------------------------------------------|-----|

| Figure 2.2: Different Phases of Semiconductor Manufacturing 1                          | . 8 |

| Figure 3.1: Representation of a Typical Semiconductor Fabrication Line                 |     |

| Figure 3.2: Re-entrant Nature of Semiconductor Processing                              | 24  |

| Figure 3.3: Examples of (a) Translation, (b) Rotation, and (c) Magnification Defects 2 | 28  |

| Figure 3.4: Examples of Particulate (a & b) and Missing Pattern (c & d) Defects        | 29  |

| Figure 4.1: Switching Rules for Normal, Tightened, and Reduced Inspection              | 35  |

| Figure 4.2: Alternating Periods of 100% Inspection and Sampling, CSP-1                 | 36  |

| Figure 4.3: CSP-2 Sampling Procedure.                                                  | 37  |

| Figure 4.4: The Basic Structure of a Skip Lot System                                   | 39  |

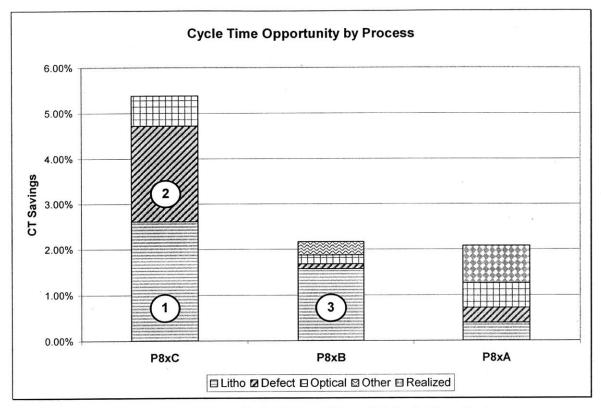

| Figure 5.1: Analysis Results in Terms of Potential Cycle Time Savings                  | 52  |

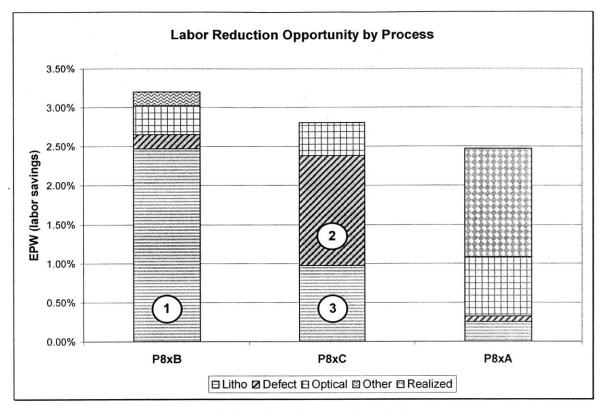

| Figure 5.2: Analysis Results in Terms of Potential Labor Savings.                      | 54  |

| Figure 5.3: The Control Chart Decision Tree.                                           | 59  |

| Figure 5.4: Group Short Run Individual X Chart.                                        | 51  |

| Figure 5.5: Group Short Run Moving Range Chart                                         | 52  |

| Figure 6.1: The Three Lenses.                                                          | 55  |

| Figure 6.2: Stakeholder Map                                                            |     |

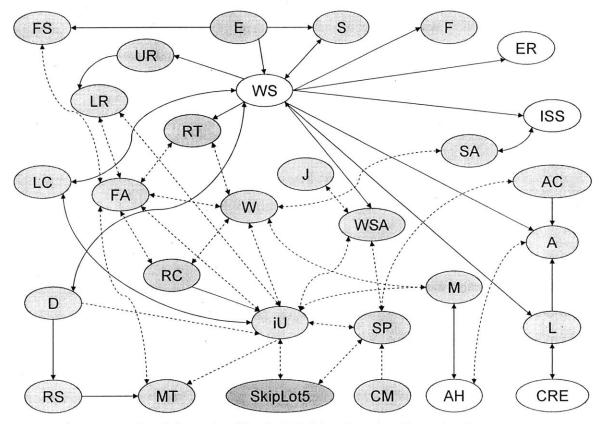

| Figure 7.1: Schematic of Intel's Fab Manufacturing Execution Systems                   |     |

# TABLE OF TABLES

| Table 3.1: Semiconductor Equipment Types and Applications. |    |

|------------------------------------------------------------|----|

| Table 4.1: Sample SkipLot5 Test Type Data Table.           |    |

| Table 4.2: Sample SkipLot5 Decision Point Data Table.      |    |

| Table 5.1: Simplified Measurement Rate Analysis.           | 50 |

•

# **CHAPTER 1 – INTRODUCTION & OVERVIEW**

#### 1.1 **Project Overview**

Many manufacturing companies are dealing with rapidly changing markets and industries. The most successful ones will be those that can deliver new and improved products to the customers at a faster pace than the competition – at a profit. Typically, manufacturing execution systems, necessary to keep pace with the industry's changing landscape, are weighted down by their own complexities causing great difficulties during their implementation or modification. This situation is especially true for those industries where product life cycles are getting shorter and the variety and complexity of the products are increasing.<sup>1</sup>

"While U.S. manufacturers recognize the importance of speed and flexibility, many are impeded by efforts to become more agile producers. Even highly automated plants and factories struggle to overcome difficulties in adapting or reconfiguring production operations to accommodate design changes and new product lines. Idiosyncrasies in manufacturing software and incompatibilities among software applications are a primary source of costly delays..."<sup>2</sup>

This thesis deals with these issues at a high level while using one particular example as a case study. The project undertaken at Intel's process development and semiconductor fabrication facility in Santa Clara, California involves the information technology application for their sampling methodology used for metrology data collection. Several issues exist with the accuracy and completeness of data due to the system design, organizational structure, and business processes. Each one of these will be discussed in later chapters.

<sup>1</sup> Christopher, Neil. National Institute of Standards and Technology. <u>Technologies for the Integration of Manufacturing Applications (TIMA)</u>. 22 May 2003. 17 Mar. 2004 <a href="http://www.atp.nist.gov/www/press/9705tima.htm">http://www.atp.nist.gov/www/press/9705tima.htm</a>.

<sup>2</sup> ibid

# **1.2 Project Motivation**

This project was motivated by the desire to improve one of the high mix, low volume challenges discussed in Chapter 2 – increased inspection requirements. Early in the internship assignment, it came to management's attention that the measurement rates for specific products at metrology operations were much higher than expected. Therefore, it was believed that by studying the data, systems, and business processes inherent to Intel's sampling methodology, improvements could be made to reduce the impact that the increased number of measurements caused by an increased product mix will have on D2's labor requirements and cycle time.

#### 1.3 Organization of the Thesis

This paper is divided into six subsequent chapters.

Chapter 2 discusses Intel Corporation, its products, and its latest strategy for entry into the demanding consumer electronics business. The technology development activities of semiconductor manufacturing at Intel are discussed with a review of the organization where the project work was completed.

Chapter 3 briefly reviews the complex semiconductor manufacturing processes in order to present these to a reader new to the topic. Metrology operations are then introduced providing special attention to those metrology areas studied during the project.

Chapter 4 reviews widely accepted sampling plans and, more importantly, Intel's current practices and application of their skip lot sampling methodology.

Chapter 5 begins with a discussion of a quality audit and includes a detailed system analysis of Intel's skip lot sampling plan. It presents the outcome of a quality review for this system, focusing on perceived versus actual measurement rates and includes a special study of transient data resulting from bringing equipment online after downtime events. This allows a comparison of the results of the analysis to actions taken in the fab. Finally, it reviews a reporting tool to improve the accessibility and availability of measurement rate data in the future.

Chapter 6 provides a cultural perspective on the above issues and the internship assignment, in particular.

Finally, Chapter 7 includes specific recommendations for improvement, the implementation status, a possible future project, and general observations regarding the flow of information within and across organizations.

- 14 -

# CHAPTER 2 – PROJECT BACKGROUND & DESCRIPTION

This chapter outlines details regarding Intel Corporation including its products, basic strategy for continued growth, and manufacturing operations as well as background materials specific to the project. This sets the stage for further chapters discussing quality assurance and sampling plans at the D2 research and development semiconductor wafer fabrication facility.

### 2.1 Intel Corporation Overview

Intel is the world's largest semiconductor chip manufacturer and holds a commanding lead over its nearest competitors with an estimated 80% share of the worldwide microprocessor market.<sup>3</sup> Fiscal year sales were just over \$30 Billion with net income exceeding \$5.6 Billion due to gross profit margins over 60%.<sup>4</sup>

The company's primary focus is to design, develop, manufacture, and market computing, networking, and communication products with the following corporate mission:

"Do a great job for our customers, employees and stockholders by being the preeminent building block supplier to the worldwide Internet economy."<sup>5</sup>

Intel's major product categories include microprocessors, chipsets, motherboards, wired and wireless connectivity products, flash memory, and both processors and chipsets for the cellular and handheld computing industries. At the end of 2003, the corporation was divided into three primary business units: Intel Architecture, Intel Communications Group (ICG), and the Wireless Communications and Computing Group (WCCG). Each segment works to develop improved integrated circuits and silicon solutions in support of the corporate goal.

<sup>&</sup>lt;sup>3</sup> Carbone, Jim. "Microprocessors Show Signs of Life as Demand Builds." <u>Purchasing</u>. 20 Nov. 2003: 17-18. Business Source Elite. EBSCOhost. 15 Mar. 2004. Keyword: Intel market share.

<sup>&</sup>lt;sup>4</sup> Edelstone, Mark L. (4 Mar. 2004). Intel Corp. Fine-Tuning EPS Estimate Lower. <u>Equity Research Note</u>. Morgan Stanley. Retrieved 15 Mar 2004 from InvestText Plus Database.

<sup>&</sup>lt;sup>5</sup> Intel Corporation. "From Silicon to Software." Intel's Quality System Handbook, 15 Mar. 2004 <a href="http://developer.intel.com/design/quality/quality.htm">http://developer.intel.com/design/quality/quality.htm</a>.

The Intel Architecture organization accounted for roughly 87% of the company's revenues in 2003 - 73% specifically from the microprocessor business. Within this group, technology solutions are developed using its microprocessor, motherboard, and chipset capabilities for the personal computing and server markets. The Intel Communications Group and Wireless Communications and Computing Group accounted for 7% and 6% of consolidated 2003 net revenues, respectively.<sup>6</sup>

#### 2.1.1 Intel Operations

The Technology and Manufacturing Group (TMG) is responsible for all of Intel's manufacturing operations and technology development activities worldwide. Manufacturing facilities are located in the United States, Israel, Ireland, Malaysia, the Philippines, China, and Costa Rica.

Fab Sort Manufacturing (FSM) and Assembly Test Manufacturing (ATM) report to TMG as well as several other organizations in charge of technology development, system manufacturing, and other support services. Fab Sort Manufacturing is responsible for Intel's wafer fabrication and sort facilities while Assembly Test Manufacturing controls the remaining activities of assembly and final test.

Each fab is assigned a set of products requiring various technologies and processes that it will manufacture based on the limitations and utilization of its existing equipment. For instance, Fab A may be dedicated to certain flash memory products while Fabs B and C utilize their resources to produce various microprocessor products. This would result in Fabs B and C being part of the logic "virtual factory" since they manufacture the same or similar (logic) products. The results of yield and output improvement projects are shared among all members of the "virtual factory" after being implemented at one facility. Within this "virtual factory" framework, changes to processes and equipment at all manufacturing sites are tightly controlled to ensure each

<sup>&</sup>lt;sup>6</sup> Intel Corporation. (27 Dec 2003). "Form 10-K." Annual Filing with the United States Securities and Exchange Commission, Retrieved 10 Mar 2004, from Thomson Research Database.

facility is as similar to the others for resource sharing, benchmarking, improved yield learning, increased speed to capacity ramp, and optimal manufacturing flexibility.<sup>7</sup>

#### 2.1.2 Supply Chain Perspective for Semiconductor Manufacturing

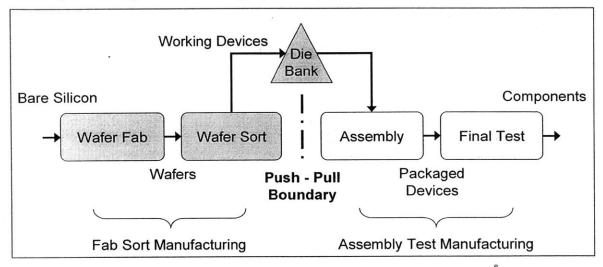

In order to convert silicon into packaged electronic components, four basic factory operations are necessary: wafer fabrication, wafer sort, packaged component assembly, and final test (reference Figure 2.1). Intel uses a die bank (an inventory of fabricated and cut wafers) as an interface between their push-based strategy (wafer fab and sort) and their pull-based strategy (assembly and final test).

Figure 2.1: Semiconductor Manufacturing Supply Chain at Intel.<sup>8</sup>

Within the wafer sort operation, each die (or microprocessor chip) on completed wafers is tested for functionality and performance. These wafers are then cut to separate the individual chips and sorted based on the test results. The good chips are sent to the die bank for future retrieval by assembly operations. Packaged devices are the result of the assembly process where individual die are mounted and prepared for use in customer applications. Prior to shipment, each one of these packaged microprocessors is tested again for functionality and performance in the final test operation.

<sup>&</sup>lt;sup>7</sup> Ponchner, Karen. "Implementing Advanced Process Control in a Copy EXACTLY! Environment." Thesis. Massachusetts Institute of Technology, 2002. 24-26.

<sup>&</sup>lt;sup>8</sup> Adapted from Atherton, Linda F., and Robert W. Atherton. <u>Wafer Fabrication: Factory Performance and Analysis</u>. Boston: Kluwer Academic, 1995. 6.

#### 2.2 Technology Development

This section discusses the different phases of semiconductor manufacturing including technology development. Specifically, the charter of Intel's California Technology Manufacturing D2 organization is explained to describe the context for this thesis project.

#### 2.2.1 The Different Phases of Semiconductor Manufacturing

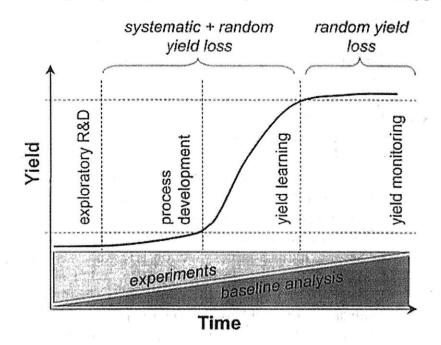

Yield management is critical to the success of a wafer fab. The yield learning cycle varies significantly between the different phases of semiconductor manufacturing. Figure 2.2 represents the expectations for yield improvements between these different phases: exploratory research and development, process development, yield learning during manufacturing ramp, and yield monitoring of a stable manufacturing process.

Figure 2.2: Different Phases of Semiconductor Manufacturing.<sup>9</sup>

During the first stage of research and development, relatively few measurements are taken for quality assurance since the primary purpose of this timeframe is to determine product feasibility through experiments. As the product progresses through the

<sup>&</sup>lt;sup>9</sup> Diebold, Alain C., ed. <u>Handbook of Silicon Semiconductor Metrology</u>. New York: Marcel Dekker, Inc., 2001. 679-681.

process development phase into manufacturing ramp, measurements and data collection processes are critical to maximize opportunities for yield learning. For this reason, data collection procedures are typically automated to gather the necessary information for improving yield. The number of measurements taken and time invested in metrology are at a maximum during this phase. The inspection process has a critical role in improving fab yield and cost effectiveness at this time by enabling both the early discovery of defects and the corrective action necessary to avoid similar mistakes. At this point in the manufacturing process maturity, additional inspections lead to fewer defects and higher yields. Finally, when the manufacturing processes mature and stabilize, the number of measurements needed to maintain optimized levels of yield is reduced for cost reasons.

#### 2.2.2 California Technology Manufacturing

During the process development phase, Intel uses technology development (TD) organizations to define the manufacturing processes prior to transferring the products and processes to high volume manufacturing fabs. One of these groups is California Technology Manufacturing (CTM) located in Santa Clara, California. CTM includes Intel's 200 mm process development wafer fab, known as D2, where this thesis work was performed. The following section describes D2's primary purpose and role within Intel and CTM.

#### 2.2.3 D2 Charter

The D2 wafer fab has a vision to deliver leading edge silicon processes to accelerate and broaden Intel's competitive leadership. In order to do this, their charter has three distinct goals:

- Develop process technologies

- Ensure successful transfers of new technologies to the virtual factory

- Maintain a stable manufacturing base for rapid deployment of the new products and process technologies to the virtual factory

D2 is one of the few Intel fabs focused on both high volume manufacturing and technology development for new processes. As a production facility, it joins the virtual

- 19 -

factory's attempts to improve yield learning while also helping to fulfill production volume requirements. Because of its dual purpose, there is an important need for resources to focus on the high mix, low volume challenges discussed in the next section.

#### 2.3 A Changing Market

Over the last several years a gradual shift has been realized for an ever-increasing demand of flash products and more variations to the memory product family.

#### 2.3.1 Intel Aggressively Enters the High Mix, Low Volume Market

Worldwide chip sales are projected to increase by 25% in 2004<sup>10</sup> due to the rising popularity of consumer electronic devices such as cellular phones, flat panel televisions, portable music and video players, and wireless home networking. With this surge of increased demand for digital content, the chip designers and manufacturers are placing a high priority on product development projects to enter this business. *Business Week* magazine reports that Walden Rhines, the CEO of chip design software maker Mentor Graphics, "expects chip companies to create 20% to 50% more new versions during the current upturn than in past recoveries."<sup>11</sup> Product development for these new markets is focused on the following four key areas:

- Finding ways to include more functionality onto smaller chips

- Capturing additional market opportunities with improved packaging

- Identifying new types of integrated circuitry

- Improving materials and manufacturing processes

Craig Barrett, Intel's CEO, has created a new plan to include Intel chips in every digital product available on the market. This corporate strategy has been tagged the "Intel Everywhere" plan by *Business Week* in contrast to the previous "Intel Inside"

<sup>&</sup>lt;sup>10</sup> Kharif, Olga. "A Whole New World of Chips." Business Week Online 21 Jan. 2004. 13 Mar. 2004 <a href="http://www.businessweek.com/technology/content/jan2004/tc20040121\_4923\_tc139.htm">http://www.businessweek.com/technology/content/jan2004/tc20040121\_4923\_tc139.htm</a>>.

<sup>&</sup>lt;sup>11</sup> ibid

marketing campaign.<sup>12</sup> "Barrett fully intends to upend the status quo in communications and consumer electronics markets. Think of Intel as the silicon arms dealer."<sup>13</sup>

To meet this challenge, new products for the communications markets are being developed by Intel's research and development fabs. There is "a lot more variety [in chips] than there has ever been," quotes *Business Week* of Brian Matas, an analyst for the semiconductor consulting firm IC Insights.<sup>14</sup> Due to the types and numerous markets ready for entry, each of these new product variations will ultimately be produced in lower volumes than the typical Intel Architecture microprocessor product family. This has and will continue to force Intel's manufacturing environments to deal with a higher mix of products at lower volumes.

#### 2.3.2 Challenges of High Mix, Low Volume Manufacturing

As suggested by the product-process matrix described by Hayes and Wheelwright<sup>15</sup> in 1979, it would be difficult to simply assign high mix, low volume products to Intel's existing high volume manufacturing facilities. This situation requires an analysis of the manufacturing characteristics required to efficiently run a high mix, low volume manufacturing environment. Some of the many problems an existing high volume semiconductor manufacturing facility would encounter when producing components of a high mix in lower volumes are listed below.<sup>16</sup>

Reduced yield – High volume fabs allow benefits to be gained and improvements to be made over time as learning occurs. When a facility is forced to run a lower volume of many more products, this learning effect cannot be realized (through repetition of running the exact same product over and over) in order to significantly improve the product yield.

<sup>13</sup> ibid

<sup>&</sup>lt;sup>12</sup> Edwards, Cliff, Moon Ihlwan, and Andy Reinhardt. "What is CEO Craig Barrett Up To? Hint: It's About Much More than Computers." Business Week Online 8 Mar. 2004. 10 Mar. 2004 <a href="http://www.businessweek.com/magazine/content/04">http://www.businessweek.com/magazine/content/04</a> 10/b3873001 mz001.htm>.

<sup>&</sup>lt;sup>14</sup> Kharif, Olga. "Memory: Beyond Flash and DRAM." Business Week Online 21 Jan. 2004. 14 Mar. 2004 <a href="http://www.businessweek.com/technology/content/jan2004/tc20040121">http://www.businessweek.com/technology/content/jan2004/tc20040121</a> 9640 tc139.htm>.

<sup>&</sup>lt;sup>15</sup> Hayes, Robert, and Steven Wheelwright. "Link Manufacturing Process and Product Life Cycles." <u>Harvard Business Review</u> 1979.

<sup>&</sup>lt;sup>16</sup> Scholtz III, Robert L. "Strategies for Manufacturing Low Volume Semiconductor Products in a High <sup>7</sup> Volume Manufacturing Environment." Thesis. Massachusetts Institute of Technology, 2002. 10-11.

- Increased inspection requirements These low volume products require an increased level of inspection to ensure a high quality product is delivered to the customer.

- Increased setup costs The higher mix of lower volume products requires extra setups to be performed taking away valuable equipment utilization time.

- Increased number of new product introductions The new product introduction (NPI) process is designed to optimize the manufacturing environment for a given product when it is first produced at a new facility. This NPI process is time-consuming and resource intensive. With the large amount of products beginning to enter Intel's manufacturing facilities, many more NPIs will result than in recent history, demanding additional time and resources.

#### 2.3.3 HMLV Summary

In summary, Intel has chosen a new strategy to aggressively enter the consumer electronic device and communications markets. Due to the nature of this new arena, several product variations, each of relatively low volume, will be required to meet customer demands. As a result, Intel is now faced with a high volume manufacturing organization that must learn to incorporate high mix, low volume products into its existing manufacturing infrastructure.

# **CHAPTER 3 – SEMICONDUCTOR MANUFACTURING AND METROLOGY**

This chapter introduces the manufacturing processes and complex nature of semiconductor wafer fabrication facilities followed by a review of semiconductor metrology operations.

# 3.1 Semiconductor Manufacturing

#### 3.1.1 Manufacturing Overview

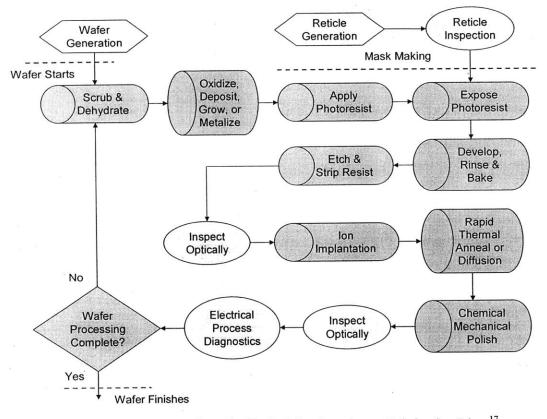

Semiconductor manufacturing consists of a complex sequence of processes that build three-dimensional structures onto the surface of single-crystal silicon wafers. This manufacturing process includes many processing steps where layers of various materials are deposited onto the wafer for specific reasons. Each layer is then patterned and connected to underlying layers. Figure 3.1 shows a schematic of the typical process flow.

Figure 3.1: Representation of a Typical Semiconductor Fabrication Line.<sup>17</sup>

<sup>&</sup>lt;sup>17</sup> Adapted from Doering, Robert, and Yoshio Nishi, eds. <u>Handbook of Semiconductor Manufacturing</u> Technology. New York: Marcel Dekker, Inc., 2000. 25.

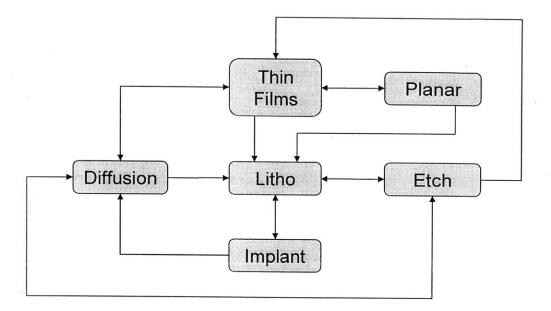

A sequence of several hundred steps is necessary to complete this highly reentrant manufacturing process. Figure 3.2 is a schematic of the re-entrant nature of a typical microprocessor product between the six major processing steps. These steps are discussed in more detail in the next section.

Figure 3.2: Re-entrant Nature of Semiconductor Processing.<sup>18</sup>

# 3.1.2 Wafer Fabrication Processes and Equipment

As indicated above, there are six primary processes involved with microprocessor production: diffusion, thin films, implant, photolithography (litho), etch, and planar. Each one of these is explained below.

- Diffusion In the diffusion area, wafers are heated in the presence of reactive gases to grow layers on the wafer surface or un-reactive gases to "drive" implanted materials to their desired depth.

- Thin films Thin films are deposited onto the wafer surface using chemical vapor deposition, sputtering, or an electroplating process.

<sup>&</sup>lt;sup>18</sup> Adapted from Quirk, Michael, and Julian Serda. <u>Semiconductor Manufacturing Technology</u>. Upper Saddle River, NJ: Prentice Hall, 2001, 201.

- Implant In order for silicon to conduct electricity, impurities are implanted into the surface of the wafer by way of the ion implantation process.

- Litho Patterns are printed onto masks (or reticles) which are then transferred to the wafer surface through the process of spinning resist onto the wafer, exposing the resist using the reticle, and developing the resist.

- Etch Etching takes place in an acid bath (wet etch) or in an oxygen plasma environment (dry etch). This etching process removes the resist pattern from the wafer.

- Planar During the planar or polishing steps, chemical and mechanical processing of the wafer removes surface topography ensuring a smooth and flat surface for further processing.

Semiconductor manufacturing is highly technical work accomplished by specialized equipment within a fabrication facility's clean room for minimum exposure to particulate contamination. In advanced fabs, as many as fifty different types of equipment may be necessary to complete this entire process. A brief summary of the major classifications of equipment types is shown in Table 3.1.

| Equipment Type                | Application                                              |

|-------------------------------|----------------------------------------------------------|

| Deposition                    | Deposit thin film layer on wafer surface                 |

| Etching                       | Remove thin film layer from wafer surface                |

| Photoresist                   | Apply photoresistive organic polymer film                |

| Photolithography              | Inscribe pattern on photosensitive layer                 |

| Resist Development            | Remove image from patterned coating                      |

| Wafer Clean                   | Remove unwanted layer or particles                       |

| Plasma Etching                | Etch underlying layer according to pattern resist        |

| Resist Stripping              | Remove photoresist layer of hardened organic film        |

| Ion Implantation              | Implant dopants into exposed layer                       |

| Oxidation                     | Grow silicon dioxide layer                               |

| Diffusion                     | Introduce dopants into exposed layer                     |

| Chemical Vapor Deposition     | Deposit layers of dielectrics, metals, or semiconductors |

| Sputtering                    | Deposit layers of dielectrics or metals                  |

| Chemical-Mechanical Polishing | Smooth or remove a patterned layer                       |

Table 3.1: Semiconductor Equipment Types and Applications.<sup>19</sup>

#### 3.2 Semiconductor Metrology

Variations during the integrated circuit manufacturing process can result in defects in the semiconductor device's performance. At times, these product variations can result in dramatic reductions to a fab's yield. Therefore, manufacturing of integrated circuits includes metrology operations after each major processing step to improve the yield learning cycle (and ultimately, the fab's yield). These metrology steps verify that particle contamination is within certain parameters and product design requirements are being met.

There are two main types of metrology operations studied during the course of this work at Intel's D2 process development wafer fab: photolithography (litho) metrology and defect metrology. Combined, these metrology operations account for roughly 30% of the total number of steps in the manufacturing sequence and

<sup>&</sup>lt;sup>19</sup> Atherton, Linda F., and Robert W. Atherton. <u>Wafer Fabrication: Factory Performance and Analysis</u>. Boston: Kluwer Academic, 1995. 7-9.

approximately 39% of the cycle time required to complete the semiconductor device.<sup>20</sup> The different types of metrology operations are briefly described in the next two sections.

#### 3.2.1 Photolithography (Litho) Metrology

After the value-add processing step is completed for each litho layer, various problems are identified through four types of metrology operations: macro inspect, develop check, critical dimension verification, and image placement. For most products and layers, all four of these metrology operations are completed resulting in numerous occasions where manufacturing technicians handle the wafers checking for different defect types.

- Macro inspect During this operation, a metrology technician uses special equipment to rotate the wafer under a monochromatic light to visually detect easily identifiable issues (at the macro level) resulting from the resist processing steps.

- Develop check An optical microscope is used for the develop check operation to inspect wafers for resist pattern defects or other anomalies only visible under magnification.

- Critical dimension verification A scanning electron microscope (SEM) is used to measure the critical dimensions of pre-defined features to verify they are within product parameters.

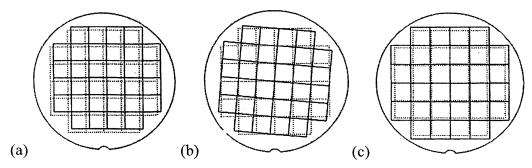

- Image placement This step (known as registration) determines the amount of overlay between the current layer and an alignment layer underneath. Three common errors are shown in Figure 3.3.

<sup>&</sup>lt;sup>20</sup> Data taken from a typical product (P8xB) manufactured at D2 in December 2003.

Figure 3.3: Examples of (a) Translation, (b) Rotation, and (c) Magnification Defects.<sup>21</sup>

#### 3.2.2 Defect Metrology

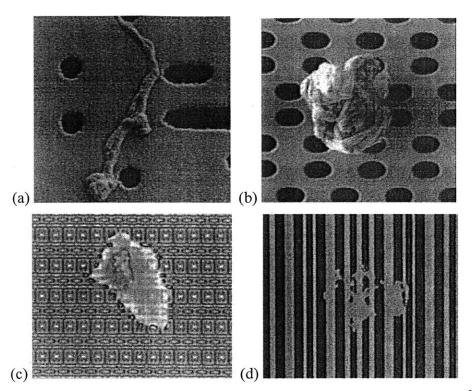

Litho metrology involves identification of errors specifically associated with the photolithography processes such as spinning resist onto the wafer, exposing the resist using the reticle, and developing the resist. This second major classification of metrology, defect metrology, deals with other types of defects that negatively impact product value or functionality leading to lost revenue. These defects can be particles or other imperfections on the wafer that are not intended to be there or any feature missing from the wafer. These defects need to be located as early as possible during the manufacturing process allowing for fewer wafers to be affected, a faster feedback loop for problem resolution, and a lower cost of production.

Typically, either an optical microscope or a SEM would be used to initially inspect wafers and locate the existence of defects such as those shown in Figure 3.4. Defect review tools are also used to further inspect and characterize the nature of unknown material enabling the root cause of the defect to be isolated and contained. The equipment used for defect review is similar to the optical microscopes and SEMs. However, the purpose of their use is to verify that a "detected" defect truly exists and to provide for element classification.

<sup>&</sup>lt;sup>21</sup> Doering, Robert, and Yoshio Nishi, eds. <u>Handbook of Semiconductor Manufacturing Technology</u>. New York: Marcel Dekker, Inc., 2000.

Figure 3.4: Examples of Particulate (a & b) and Missing Pattern (c & d) Defects.<sup>22</sup>

<sup>&</sup>lt;sup>22</sup> Diebold, Alain C., ed. <u>Handbook of Silicon Semiconductor Metrology</u>. New York: Marcel Dekker, Inc., 2001. 693.

- 30 -

# **CHAPTER 4 – SAMPLING PLANS**

The previous chapter presented an overview of semiconductor manufacturing, its complexities, and typical metrology operations necessary to improve yield learning. This chapter deals specifically with different methods to gather the inspection data while also reducing the impacts these activities have on manufacturing costs and productivity.

### 4.1 Acceptance Sampling

There are three approaches to the decision-making process regarding product lot quality:<sup>23</sup>

- Accept lots without any form of inspection

- Inspect all lots and remove, rework, or replace defective units

- Implement the use of acceptance sampling for lot quality review

Accepting lots without inspection would typically only be done for those processes that have been consistently proven to be in control over a long period of time. At the other end of the spectrum, all lots may be inspected in those cases where critical product features must be tightly controlled or when the process capability is inadequate to meet specifications. In between, acceptance sampling may be used for the following types of situations:<sup>24</sup>

- When the testing procedure is destructive making 100% inspection clearly impractical

- When the costs of 100% inspection are relatively high

- When the inspection and analysis process takes a relatively long period of time

- When a reduction from 100% inspection is desired, but the process capability does not warrant zero inspections.

- When product liability justifies continuous monitoring

<sup>&</sup>lt;sup>23</sup> Montgomery, Douglas C. Introduction to Statistical Quality Control. New York: John Wiley & Sons, 1985. 351-354.

<sup>&</sup>lt;sup>24</sup> ibid

Intel semiconductor metrology operations fall into the third and fourth categories above. A large amount of time is necessary for some test results to be returned to the technician who is making processing decisions (e.g. continue running the batch under current conditions or tweak the equipment settings to produce a better product). This can result in unwanted equipment idle time adversely affecting fab capacity, cycle time, and costs. Furthermore, due to the increasing shift towards high mix, low volume manufacturing, discussed in chapter 2, efforts have been initiated to reduce the quantity of measurements taken throughout the manufacturing process while still requiring some form of ongoing monitoring.

Many advantages to acceptance sampling plans exist when compared to 100% inspection plans. These include a decreased number of inspections resulting in lower production costs, less metrology labor involvement, and less product manipulation where unnecessary product damage could result. However, there is also an increased opportunity for accepting "bad" lots and rejecting "good" lots. Another disadvantage is that the learning cycle gained from the data collected during the inspection process is slowed due to the reduced number of measurements.

Therefore, the key to gathering data is to do so frequently enough that process changes are captured but not so often that the activity of data collection and analysis is too expensive to be useful. Many different types of inspection methodologies are used within manufacturing operations for the purpose of accepting or rejecting product based on adherence to a standard. Some of the more common acceptance sampling methods are described in the following sections for the purpose of providing context for Intel's acceptance sampling system.

#### 4.2 Lot-by-lot Acceptance Sampling by Attributes

This section explains various types of lot-by-lot acceptance sampling plans using attribute data to classify items as either defective or non-defective based on pass/fail conditions.

#### 4.2.1 Dodge-Romig Sampling Plans

Two types of sampling plans were developed by H. F. Dodge and H. G. Romig that use a set of sampling inspection tables specifically for lot-by-lot inspection: lot tolerance percent defective (LTPD) and average outgoing quality limit (AOQL). The LTPD sampling plan provides protection for the downstream customer in that it involves a risk no greater than the specified amount of accepting any given lot of unsatisfactory quality. AOQL sampling plans are designed for those situations where there is little interest in the quality level of individual lots. Here, protection is provided to the customer in terms of the average outgoing quality for the product over a series of lots.<sup>25</sup> Both of these systems can be developed with the single and double sampling procedures explained in the following sections.

#### 4.2.2 Single Sampling Plan

A single sampling plan is a decision-making process where one sample of n units is randomly chosen from a given lot. An acceptance number c is used to determine the disposition of the entire lot. If more than c defective items are found in the sample, the lot is rejected. Otherwise, the entire lot is accepted for further processing or delivery to a customer.

#### 4.2.3 Double Sampling Plan

A double sampling plan is similar with additional complications. After the initial sample is evaluated, the entire lot is accepted, rejected, or submitted for a second sample. In those cases where a second sample is necessary, the information from both samples is used to disposition the lot. The parameters that define this type of sampling plan are a sample size for the first and second samples  $(n_1 \text{ and } n_2)$ , an acceptance number for the first sample  $(c_1)$ , and an acceptance number for the combined samples  $(c_2)$ .

If the number of defects observed in the first sample  $(d_1)$  is less than  $c_1$ , then the lot is accepted. The lot is rejected if  $d_1$  exceeds  $c_2$ . In those situations where  $d_1$  is between  $c_1$  and  $c_2$ , a second random sample of size  $n_2$  is required. At this point, the lot is

<sup>&</sup>lt;sup>25</sup> Dodge, Harold F. "Notes on the Evolution of Acceptance Sampling." American Society for Quality Control (1973).

accepted if the combined number of defects observed in both samples  $(d_1 + d_2)$  is less than  $c_2$  and rejected if it is larger than  $c_2$ .

#### 4.2.4 Multiple Sampling Plan

A multiple sampling plan is similar to the double-sampling plan except in the case where more than two samples may be necessary to disposition a given lot. After any stage of the sampling process, if the number of total defects observed ( $\sum d_i$ ) is less than or equal to the acceptance number for that particular stage ( $c_j$ ), then the lot is accepted. The lot is rejected after any stage of sampling if the total number of defects observed is greater than the acceptance number for that stage. If neither situation occurs, then sampling continues until all stages of sampling are satisfied.

This sampling method is complex to implement but can result in cost savings associated with the sampling process since the sample sizes are typically smaller than single or double sampling plans.

#### 4.2.5 Switching Procedures between Normal, Tightened, and Reduced Inspection

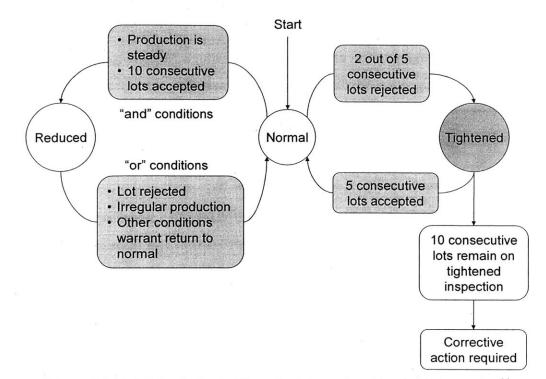

Military standard 105D (or the civilian equivalent ANSI/ASQC Z1.4) provides for different inspection levels based on the specified acceptable quality level (AQL). Normal inspection is used at the start of the measurement activity and under normal conditions where the manufacturing process is producing acceptable results. Tightened inspection levels are required when quality degrades. Reduced inspection can be implemented with exceptionally good product quality.

Figure 4.1: Switching Rules for Normal, Tightened, and Reduced Inspection.<sup>26</sup>

The criteria specified in Figure 4.1 are used to determine whether or not it is appropriate to switch from one state to another. For example, when the inspection process is operating under tightened conditions, the observation of five consecutive acceptable lots allows a switch to the normal operating conditions. The difference between normal, tightened, and reduced inspection conditions involves changes to the lot size (n) and acceptance number (c). Full tables specifying these various inspection systems are available in MIL-STD 105D and reprinted in Montgomery (1985).

### 4.3 Acceptance Sampling by Variables

Variables sampling plans specify the product to be sampled and the criteria for decision-making using measurements to identify the quality characteristics of certain product features. Typically, this is accomplished based on the sample average and sample standard deviation where lot acceptance depends on the sample average in relation to the upper or lower specification limit.

<sup>&</sup>lt;sup>26</sup> Adapted from Montgomery, Douglas C. <u>Introduction to Statistical Quality Control</u>. New York: John Wiley & Sons, 1985. 389-392.

#### 4.4 **Continuous Sampling Plans**

In some manufacturing environments, the natural formation of lots does not exist. Therefore, sampling plans involving continuous sampling versus lot sampling are used for processes consisting of a nearly continuous flow of products. Several different plans of this type are presented below.

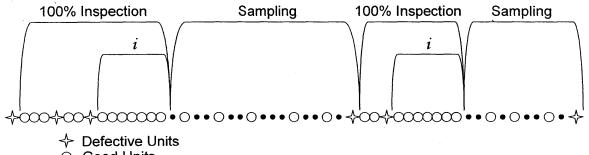

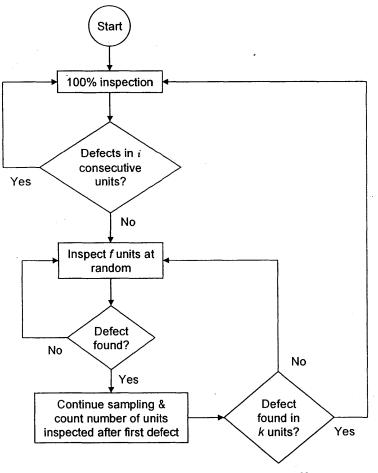

#### 4.4.1 The First Continuous Sampling Plan, CSP-1

The CSP-1 plan specifies a clearing interval (*i*) and a sampling frequency (*f*). The process includes intervals of 100% inspection alternating with periods of random sampling from the continuous flow of products. During the 100% inspection period, once *i* consecutive units are found to be free from defects, random sampling at the rate of frequency *f* begins. When a defect is identified at any point during the sampling stage, 100% inspection resumes. Figure 4.2 shows these alternating periods of 100% inspection and acceptance sampling.

O Good Units

Figure 4.2: Alternating Periods of 100% Inspection and Sampling, CSP-1.<sup>27</sup>

#### 4.4.2 Continuous Sampling Plans, CSP-2 & CSP-3

The CSP-1 acceptance sampling plan explained above requires the return to 100% inspection for any defect identified within the sample. This is equivalent to an acceptance number (c) equal to zero in a single sampling plan. However, it may not always be necessary to take action (such as returning to 100% inspection) when a defect is found. The CSP-2 and CSP-3 plans were developed for these situations.

<sup>&</sup>lt;sup>27</sup> Dodge, Harold F. "Notes on the Evolution of Acceptance Sampling." American Society for Quality Control (1973).

Another parameter called the clearing interval (k) is added which allows for sampling to continue as long as multiple defects are not found too close to each other. During sampling, no action is taken with the identification of the first defect. Only if multiple defects are found within k samples, does the process return to 100% inspection. A schematic of the CSP-2 procedure is shown in Figure 4.3.

Figure 4.3: CSP-2 Sampling Procedure.<sup>28</sup>

The CSP-3 sampling plan differs slightly from the CSP-2 plan in that it also includes the inspection of the next four units after the first defect is found. If a defect is found within this mini-clearing interval, the process returns to 100% inspection.

<sup>&</sup>lt;sup>28</sup> Adapted from Montgomery, Douglas C. <u>Introduction to Statistical Quality Control</u>. New York: John Wiley & Sons, 1985. 468-470. and Stephens, Kenneth S. "Volume 2: How to Perform Continuous Sampling (CSP)." <u>The ASQC Basic References in Quality Control: Statistical Techniques</u>. Milwaukee: American Society for Quality Control, 1986. 12.

# 4.4.3 Additional Continuous Sampling Plans

In addition to CSP-1, CSP-2, and CSP-3, several other continuous sampling plans have been developed and used over time. The more relevant ones are presented here.

- CSP-A plans are based on the CSP-1 concept but includes a stopping rule, identified by parameter *a*. This stopping rule limits the total number of defects that can be found within a production run. When more than *a* defects are found, production and inspection are suspended until the cause of the high rate of defective units is identified and corrected.

- CSP-M, or multi-level continuous sampling, is a continuation of CSP-3 type plans. Multiple levels of successive reductions to the sampling inspection rate (f) are allowed after zero defects are found on i consecutive units. Successive increases to the sampling rate are required when defects are found. This reduction and increase to the sampling frequency are done exponentially with integer powers of f.

- CSP-T, or tightened multi-level continuous sampling, is similar to CSP-M. However, the sampling rate *f* is reduced geometrically by one half when zero defects are found within *i* consecutive units.

# 4.5 Skip Lot Sampling Plans

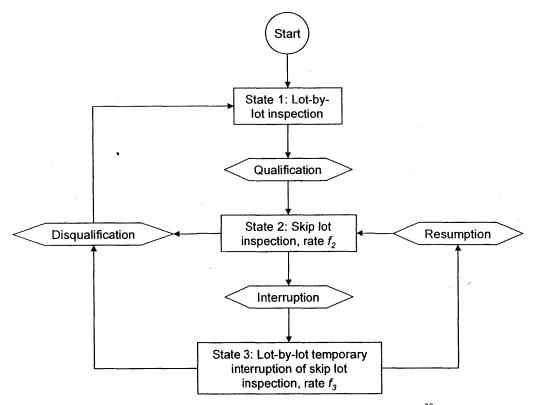

Skip lot sampling plans are an extension of the continuous sampling plans reviewed in earlier sections. Basically, these types of plans apply the same methodology described in the continuous sampling section to lots instead of to individual units. They have had extensive industrial application and are very useful in providing for reduced inspections.<sup>29</sup>

Skip lot sampling (SkSP-1) is similar to CSP-1 in its primary plan parameters: the number of lots required to qualify for skip lot inspection (*i*), the fraction of lots inspected during skip lot inspection ( $f_2$ ), and the fraction of lots inspected during the temporary

<sup>&</sup>lt;sup>29</sup> Montgomery, Douglas C. <u>Introduction to Statistical Quality Control</u>. New York: John Wiley & Sons, 1985. 476.

interruption of skip lot inspection ( $f_3$ ). This program consists of three different states shown in Figure 4.4.

- State 1 Not qualified for skipping, lot-by-lot inspection (100% inspection of lots)

- State 2 Qualified for skip lot inspection (when some lots pass by or skip inspection)

- State 3 Re-qualifying for skipping due to temporary interruption

Figure 4.4: The Basic Structure of a Skip Lot System.<sup>30</sup>

At any given time, one of these three states is active. Switching rules protect against accepting "bad" lots while also minimizing the frequency of switching between the states. Once a product has qualified for skip lot inspection by having had i consecutive lots accepted during lot-by-lot inspection, the process is qualified for

<sup>&</sup>lt;sup>30</sup> Liebesman, Burton S., and Bernard Saperstein. "A Proposed Attribute Skip-Lot Sampling Program." Journal of Quality Technology July 1983: 132.

skipping and enters state 2. While in state 2, the inspection frequency  $f_2$  determines how many lots are inspected. Any rejected lot forces the process to state 3 where the inspection frequency  $f_3$  is used. Regular skip lot inspection resumes with four consecutive accepted lots. Furthermore, when processing from state 2, skip lot inspection is disqualified if two lots are rejected within ten consecutive inspected lots, forcing a return to 100% inspection.<sup>31</sup>

# 4.6 Intel's Sampling Process

The acceptance sampling plan in place at Intel's wafer fabrication facilities is a combination of skip lot sampling and a variation of the tightened multi-level continuous sampling plan (CSP-T). This system basically works within the parameters of the skip lot program; however, there is a continual change to the fraction of lots inspected during skip lot inspection ( $f_2$ ).

Using Intel's system, s lots are skipped followed by a single lot that gets inspected. There are three differences between Intel's system and CSP-T. First, the fraction of lots inspected is not geometrically reduced by half for each successfully accepted sequence of i consecutive lots. Instead, the skip rate s is incremented upward by one or more units after every successfully accepted lot. Second, a rejected lot returns the skip rate s back to its minimum value instead of slowly incrementing toward  $f_2$  as defined by CSP-T. Third, random sampling is not performed. Intel uses a very organized approach of "skip s lots, and then measure one."

By increasing the skip rate upward by one or more units, Intel's sampling methodology is much more conservative than both the CSP-M and CSP-T plans. This implies more sampling and inspection will be performed with the Intel skip rate process. Furthermore, the non-random nature of Intel's system exposes the manufacturing process and quality system to errors or other defects that occur with regularity.

<sup>31</sup> ibid

# 4.6.1 The SkipLot5 Application<sup>32</sup>

SkipLot5 is the name of the IT application at Intel that gives users the ability to define when lots can skip various metrology operations in the manufacturing process flow. It functions in coordination with Intel's WorkStream system<sup>33</sup> enabling WorkStream users to easily recognize which lots require measurements and which lots may skip the metrology operations. The SkipLot5 application is intended to allow lots to be processed quickly while taking a limited and controlled amount of risk.

In order to use this application, process engineers define a specific amount of risk to be taken based on statistics for a given set of circumstances. Skip rates are assigned based on the process capability (Cpk value). For example, a skip rate of four (measure one, then skip four) would be typical for a product, route, and operation combination having a process capability value of 1.4. The statistics necessary to run the application are then entered into the SkipLot5 database via WorkStream (automatic updates for manufacturing data), the SPC++ system<sup>34</sup> (automatic updates for measurement results), and manual interfaces (data entry and skip algorithm definitions). Based on this data, the SkipLot5 application controls the movement of lots at metrology operations by forcing them to move through or allowing them to skip any given operation.

The SkipLot5 system is a state machine as described in Chapter 4.5. The algorithm starts in state 1 where it will remain until a predetermined number of lots  $(i_1)$  are tested and accepted. If any out of control instance is recorded during this period, the counters are reset until another consecutive set of  $i_1$  lots are accepted. At this point, the system switches to state 2. In state 2, skipping is allowed at the minimum skip rate  $(s_{min})$  specified in the database. Once a lot is measured and accepted, the skip rate s increments upward by the rate change unit (r) until the maximum skip rate  $(s_{max})$  is reached. If the result of a tested lot is found to be out of control, the algorithm automatically shifts to state 3. While in this re-qualification stage, if a predetermined number of lots  $(i_3)$  are

<sup>&</sup>lt;sup>32</sup> Intel Corporation. "SkipLot5." User's Guide, 1998.

<sup>&</sup>lt;sup>33</sup> WorkStream is the manufacturing shop floor application that technicians and engineers use to schedule and process lots within the fab manufacturing environment.

<sup>&</sup>lt;sup>34</sup> SPC++ is a system that monitors and controls processes in the manufacturing facility. It detects when equipment is operating outside of specified parameters enabling process engineers to be warned of the problem to take corrective action.

tested and accepted, the system returns to state 2 at  $s_{min}$ . Otherwise, any out of control lot returns the program back to state 1 where 100% inspection is required.

It should be noted that skip rates, defined by s, and measurement rates, indicated by m, are often interchangeable depending on the purpose of the discussion. It is beneficial to provide a conversion between the two:

$$m = \frac{1}{s_{Average} + 1}$$

Therefore, a measurement rate of 20% results from having an average skip rate of four – measure one, then skip four.

Data within the application is maintained through the use of tables and a user interface controlled by the Information Systems department. Those tables relevant to this document are explained here.

• Test Type table – Table 4.1 provides a sample SkipLot5 test type data table. This table contains the pieces of data necessary to define a given test type including: Qual – the number of lots that must be accepted for the system to qualify for skipping  $(i_1)$ , ReQual – the number of lots that must be accepted for the system to re-qualify for skipping  $(i_3)$ , Rate Chg – the rate change interval (r), and the maximum (Max Rate) and minimum (Min Rate) skip rates  $(s_{max} \text{ and } s_{min})$ . The Max Risk data field identifies the maximum number of lots that may be present ("at risk") between the value-add processing step and the metrology operation. The Max Interval column indicates the maximum number of hours that may pass between successive measurements for each given test type. A measurement is forced once either the Max Risk or Max Interval values are exceeded.

| Test Type<br>Name | Qual | Re-<br>Qual | Rate<br>Chg | Max<br>Rate | Min<br>Rate | Max<br>Risk | Max<br>Interval |

|-------------------|------|-------------|-------------|-------------|-------------|-------------|-----------------|

| TTN-01            | 1    | 1           | 1           | 4           | 1           | 12          | 168             |

| TTN-02            | 1    | 1           | 2           | 4           | 2           | 12          | 168             |

| TTN-03            | 5    | 3           | 1           | 10          | 6           | 25          | 168             |

| TTN-04            | 3    | 3           | 1           | 10          | 6           | 25          | 168             |

| TTN-05            | 2    | 3           | 1           | 10          | 6           | 25          | 168             |

| TTN-06            | 5    | 1           | 1           | 6           | 2           | 12          | 168             |

| TTN-07            | 1    | 1           | 1           | 4           | 1           | 50          | 168             |

| TTN-08            | 1    | 1           | 2           | 4           | 2           | 50          | 168             |

| TTN-09            | 1    | 3           | 2           | 4           | 1           | 50          | 168             |

| TTN-10            | 3    | 1           | 2           | 6           | 2           | 50          | 168             |

| TTN-11            | 1    | 1           | 2           | 4           | 1           | 50          | 168             |

| TTN-12            | 1 .  | 1           | 1           | 10          | 6           | 50          | 168             |

Table 4.1: Sample SkipLot5 Test Type Data Table.<sup>35</sup>

Decision Point table – A decision point is the reference to a combination of route and operation at which point the decision to skip a metrology operation will be made. These decision points link metrology operations to value-add processing points and are associated with a particular test type. Table 4.2 shows this association between test types (Test Type Name), value-add routes (VA Route), value-add operations (VA Oper), test routes, and metrology operations (Test Oper). Each one of these decision points can be activated or made inactive by way of the column on the far left hand side of the table (A). This active flag allows skipping to be manually interrupted in those cases where known excursions exist in the fab. In these situations, an engineer can deactivate the skipping algorithm for the appropriate decision. For instance, Table 4.2 shows the fifth entry for value-add route TTN-05 and value-add operation SR-B2 to be inactive since the A column contains an N for "not active."

<sup>&</sup>lt;sup>35</sup> The test type names and test type data have been changed for confidentiality purposes.

| A | Test Type<br>Name | VA Route | VA Oper  | Test Route | Test Oper |

|---|-------------------|----------|----------|------------|-----------|

| Y | TTN-01            | SR-A1    | Oper-110 | SR-A1      | Oper-115  |

| Y | TTN-02            | SR-A1    | Oper-220 | SR-A1      | Oper-225  |

| Y | TTN-03            | SR-A1    | Oper-420 | SR-A1      | Oper-425  |

| Y | TTN-01            | SR-B2    | Oper-110 | SR-B2      | Oper-115  |

| N | TTN-05            | SR-B2    | Oper-220 | SR-B2      | Oper-225  |

| Y | TTN-06            | SR-B2    | Oper 550 | SR-B2      | Oper-555  |

| Y | TTN-07            | SR-B2    | Oper-560 | SR-B2      | Oper-565  |

| Y | TTN-02            | SR-B5    | Oper-120 | SR-B5      | Oper-125  |

| Y | TTN-03            | SR-B5    | Oper-220 | SR-B5      | Oper-225  |

| Y | TTN-04            | SR-B5    | Oper-420 | SR-B5      | Oper-425  |

| Y | TTN-05            | SR-B5    | Oper-550 | SR-B5      | Oper-555  |

| Y | TTN-02            | SR-C4    | Oper-420 | SR-C4      | Oper-425  |

Table 4.2: Sample SkipLot5 Decision Point Data Table.<sup>36</sup>

The counters that control the actions of the SkipLot5 system are reset whenever a measurement is out of control, when inventory levels of lots waiting to be measured reach the maximum at risk value, and when the time since last inspection exceeds the maximum allowable time interval. Each one of these events forces the next lot entering the given operation to be measured. There is also the possibility that downtime events, such as preventative maintenance or reticle changes, could force the counters to reset. This changes the skip inspection sequence. This nuance of the system will be investigated in Chapter 5.

# 4.6.2 The MOST Model<sup>37</sup>

The Monitor Optimization and Sampling Tool (MOST) is an automated model used to optimize sampling frequency for measurements. Most of Intel's wafer fabs use a simple table from the "Monitor Reduction Worksheet"<sup>38</sup> to identify skip rates based solely on process capabilities.

However, a few locations have implemented the MOST model to minimize total sampling costs by balancing excursion costs and sampling costs. The cost of an excursion is calculated using the costs for finished wafers, labor, spare parts, and warranty contracts. The cost of a given sampling plan is a function of many factors

<sup>&</sup>lt;sup>36</sup> The test type names, value-add routes, value-add operation numbers, test routes, and test operation numbers have been changed for confidentiality purposes.

<sup>&</sup>lt;sup>37</sup> Intel Corporation. "MOST Concept Presentation." Corporate Presentation, 2003.

<sup>&</sup>lt;sup>38</sup> Intel Corporation. "Monitor Reduction Worksheet." Statistics Users Group Initial Assessment. 2001.

including the current skip rate, historical percentage of product out of control, and the probability of detecting an excursion. Using this type of data (and more), the model runs hundreds of times and selects the minimal total sampling cost for each simulation. As a result, the MOST model determines optimal skip rates that are then used as the parameters for the SkipLot5 application.

The key differentiator between fabs that use the MOST model and those that do not is that those using the model are optimizing their sampling rates for a minimum total sampling cost. The remaining facilities set their skip rate *s* based on historical statistical data of their process capabilities. In effect, these facilities are minimizing risk as opposed to minimizing total sampling costs. Both methodologies use the SkipLot5 application to control the implementation and execution of the acceptance sampling plans.

# CHAPTER 5 – QUALITY AUDIT

This chapter first introduces the concept of a quality audit. The results of an extensive audit on D2's data, systems, and business processes involved in Intel's acceptance sampling methodology are then discussed. This material serves as a case study for those instances where manufacturing execution systems fail to provide the expected results due to a breakdown in data management, system design, and/or business process execution.

## 5.1 What is a Quality Audit?

"Quality Audit – A systematic and independent examination to determine whether quality activities and related results comply with planned arrangements and whether these arrangements are implemented effectively and are suitable to achieve objectives."<sup>39</sup>

The quality audit is a tool that management teams can use to evaluate and analyze their quality systems to either verify their effectiveness or to identify gaps needing improvement. If conducted properly, the results of a quality audit can provide objective evidence about different aspects of a given quality system.

In general, three parties are involved in the audit: the client, the groups being audited, and the auditor. The client is the organization that recognizes the need for a system review and requests the auditor to perform his/her activities.

Two major types of quality audits exist. The suitability quality audit evaluates and compares a quality program against a standard used for reference. The conformity quality audit validates the implementation, execution, corrective action, and follow-up activities against the defined quality program's design.<sup>40</sup>

<sup>&</sup>lt;sup>39</sup> Mills, Charles A. <u>The Quality Audit: A Management Evaluation Tool</u>. New York: McGraw-Hill Company, 1989. 1-2.

<sup>40</sup> ibid

# 5.2 Analysis of the SkipLot5 System

For this particular project, D2's Manufacturing Systems Engineering group within the Operations organization sponsored the effort as the client. The activities performed at D2 were of the conformity quality audit type where repeated, periodic audits were completed to verify continuing compliance and to track improvement progress over time. Furthermore, only the D2 facility was reviewed making this a location-oriented quality audit. Due to the focused nature of the location-oriented quality audit, this technique is very beneficial to analyze the interactions of the various groups and processes involved.<sup>41</sup>

The basis of the project was to determine the causes of several problems identified during a quick analysis performed early in the internship assignment. At that time, the measurement rates experienced within the fab environment for a fairly stable and mature product were much higher than expected. Therefore, the project's goal was to provide a corrective action plan in order to improve labor requirements and cycle time for the metrology areas. This was accomplished by determining the baseline measurement rates, troubleshooting the results, and working with and communicating to the various engineering groups involved in the process. A means for reducing the amount of manual analysis over the long-term was also provided.

# 5.2.1 Process for the D2 Measurement Rate Analysis

The measurement rate analysis performed at D2 was accomplished by first developing an analysis tool that assisted in gathering the necessary data from several unlinked databases. As a starting point, it was necessary to determine how much D2 was actually measuring relative to the expected measurement rates entered into the SkipLot5 database.

The following is a step-by-step description of the process used to build this analysis tool.

• Select appropriate routes: Identify the routes that carry a majority of the inventory by using information from an inventory-based database. This step limits the analysis to these high volume routes while maximizing the impact of the results

<sup>&</sup>lt;sup>41</sup> ibid, 33-34.

by focusing only on the active product flows. In high volume manufacturing facilities, this step would probably not be necessary since all products would most likely be included in the analysis.

- Determine operation sequence: Download the sequence of operations for each of these routes. This data provides access to detailed information for the routes of interest. In particular, it is necessary to know the operation numbers, operation descriptions, and the functional areas and clusters assigned to these operations. This information is used in a spreadsheet as the foundation for the analysis.

- Locate the number of wafers processed through each operation: Determine how many wafers were processed by each operation for a given route over the time period of the study. The CTOP database<sup>42</sup> provides the necessary information. After copying only the relevant detail into the analysis spreadsheet, the next several steps can be performed.

- Calculate the measurement rates: Calculate the measure rate percentages for all non-value add metrology operations in the routes of interest.

- Identify all of the non-value add metrology operations: The route information is filtered using functional area and cluster data in order to isolate those operations assigned to the metrology categories.

- Identify associated value-add processing steps to determine those operations that trigger the decision points: The decision point tables from the SkipLot5 database are then used to identify most of the processing steps associated with each of the non-value add operations identified above. It is also necessary to rely on experiential knowledge to locate the remaining value-add processing steps and to associate these with the appropriate non-value add metrology operations due to incomplete data in the decision point tables. (This issue will be discussed in subsequent sections.) Finally, the measurement rates are calculated by dividing the number of wafers processed through each

<sup>&</sup>lt;sup>42</sup> CTOP tracks and records data for manufacturing including such information as the number of wafers processed or reworked and their processing times.

metrology operation by the number of wafers processed through its associated value-add processing operation.

Troubleshoot results

A simplified sample of the resulting analysis is shown in Table 5.1 for clarification purposes.

| Operation<br>Number | Operation<br>Description | Operation Category  | Wafers<br>Processed | Measure<br>Percentage | Value-Add<br>Operation |