#### **Redefining Manufacturing Quality Control in the Electronics Industry**

by

#### Maureen Fresquez Simington

B.S., Mechanical Engineering, New Mexico State University, 1992

Submitted to the Sloan School of Management and the Department of Materials Science & Engineering in Partial Fulfillment of the Requirements for the Degrees of

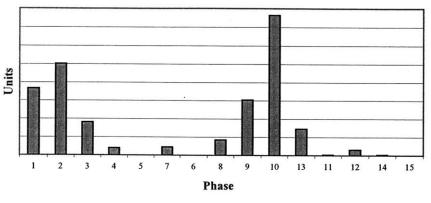

Master of Science in Management and Master of Science in Materials Science & Engineering

in Conjunction with the Leaders For Manufacturing Program

at the Massachusetts Institute of Technology June 2000

©2000 Massachusetts Institute of Technology All Rights Reserved

| Signature of Author | MIT Sloan School/of Management<br>Department of Materials Science & Engineering<br>May 5, 2000                                           |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Certified by        | Thomas W. EagarUProfessor of Materials Engineering<br>Thesis Supervisor                                                                  |

| Certified by        | C/ Roy E. Welsch<br>Professor of Statistics & Management Science<br>Thesis Supervisor                                                    |

| Accepted by         | Carl V. Thompson<br>Stavros Salapatas Professor of Materials Science & Engineering<br>Chair, Departmental Committee on Graduate Students |

| Accepted by         | Margaret Andrews<br>Executive Director of the MBA Program<br>MIT Sloan School of Management                                              |

|                     | JUN 1 3 2000<br>LIBRARIES                                                                                                                |

. . · ·

## Redefining Manufacturing Quality Control in the Electronics Industry

by

Maureen Fresquez Simington

#### Submitted to the Sloan School of Management and the Department of Materials Science & Engineering on May 5, 2000 in Partial Fulfillment of the Requirements for the Degrees of

Master of Science in Management and Master of Science in Materials Science & Engineering

#### Abstract

The most time consuming and capital intensive portion in the assembly of power electronic devices is the test system. A comprehensive test system including functional and stress screening technologies can significantly increase assembly times and more than double the capital investment required in a new assembly line. The primary purpose of the test system is to screen components for early life failures and to verify proper assembly. Determination of key performance characteristics and the resultant test system are developed during the product design phase and are seldom revised after the product has been released to manufacturing. This thesis explores best practices in testing methods and develops new methods to analyze test system performance. Both efforts were conducted in an effort to optimize existing test regimes.

Upon completion of the above analyses the existing test sequence was reduced by 50%. This was primarily due to a discovery in the Burn In test cycle which indicated that failures correlated strongly with the on/off cycles inherent in the test sequence. A new test cycle was proposed to accommodate this finding and test results verified the initial hypothesis. Additionally, the summary of best practices identified new forms of product testing including Highly Accelerated Stress Testing (HAST), moving additional product testing into the development phase consequently reducing testing requirements during assembly.

#### **Thesis Advisors:**

Thomas W. Eagar Professor of Materials Engineering

Roy E. Welsch Professor of Statistics & Management Science

4

.

**`**

## Table of Contents

| List of Figures                                       | 6    |

|-------------------------------------------------------|------|

| List of Tables                                        | 8    |

| List of Equations                                     | 8    |

| Acknowledgements                                      | 9.   |

| Chapter 1 Introduction                                | .1.1 |

| 1.1 Project Motivation                                | .11  |

| 1.2 Project Definition and Resulting Priorities       | .12  |

| 1.3 Approach & Methodology                            |      |

| 1.4 Project Goals, Measurements, and Deliverables     | .14  |

| Chapter 2 Competitive Benchmarking                    |      |

| 2.1 Industry Overview & Market Share                  | .15  |

| 2.2 Overview of Subject Companies                     | .1.6 |

| 2.3 Testing at Subject Companies                      | .1.7 |

| 2.4 Summary of Benchmarking Study                     |      |

| Chapter 3 Product Line                                |      |

| 3.1 Product Overview                                  |      |

| 3.2 Product Flow                                      |      |

| 3.3 On-line Production Test System and Database       | .29  |

| Chapter 4 Hi Pot Performance Analysis                 |      |

| 4.1. Failure Analysis                                 |      |

| 4.2. First Pass Yield Analysis                        |      |

| 4.3 Pareto Analysis                                   |      |

| 4.4 Summary of Results                                |      |

| Chapter 5. System Tests 1 and 2 Performance Analysis  |      |

| 5.1. First Pass Yield Analysis                        |      |

| 5.2. Pareto Analysis                                  |      |

| 5.3. Summary of Results                               |      |

| Chapter 6 Burn In Analysis                            |      |

| 6.1 Burn In Testing Yields                            |      |

| 6.2 Failures vs. Time Spent in Sauna                  |      |

| 6.3 Fault Type Characterization                       |      |

| 6.4 Test Reduction Hypothesis                         |      |

| Chapter 7 Product Performance Analysis                |      |

| 7.1. Initial Findings                                 |      |

| 7.2. Performance Analysis                             |      |

|                                                       | .7.6 |

| 7.4. Recommendations for Future Analysis              |      |

| Chapter 8: Solder Study                               |      |

| 8.1 Solder Quality                                    |      |

| 8.2 The Soldering System                              | .1.5 |

| 8.3 Soldering – The Existing System                   | 84   |

| 8.4 Solder Tip Preventative Maintenance               |      |

| 8.5 Summary                                           |      |

| Chapter 9 Results and Conclusions                     | 95   |

| 9.1 Benchmarking Study Conclusions and Summary        | 92   |

| 9.2 Burn In Testing Reduction Results and Conclusions | .55  |

| 9.3 Concluding Remarks                                |      |

| Bibliography                                          |      |

| End Notes                                             |      |

|                                                       |      |

# List of Figures

| Figure 1 - Market Share of Leading Micro Product Players              |     |

|-----------------------------------------------------------------------|-----|

| Figure 2 – Market Share of Leading Macro Segment Players              | 15  |

| Figure 3 - Manufacturing Product Flow                                 | 27  |

| Figure 4 – Burn In Test Cycle                                         |     |

| Figure 5 - Failure Analysis                                           |     |

| Figure 6 - Failure Rates vs. Units Produced                           |     |

| Figure 7 - Hi Pot FPY                                                 |     |

| Figure 8 - Hi Pot Failure Pareto                                      |     |

| Figure 9 - Hi Pot Failure Pareto by Test Phase                        | 40  |

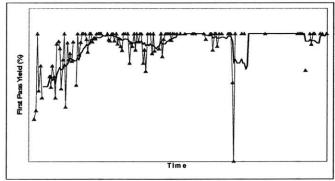

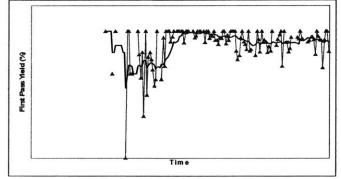

| Figure 10 - System Test 1 FPY                                         |     |

| Figure 11 - System Test 2 FPY                                         |     |

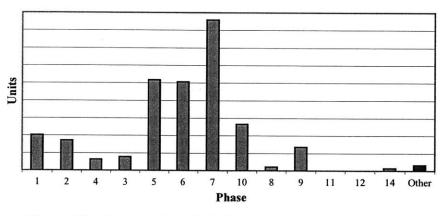

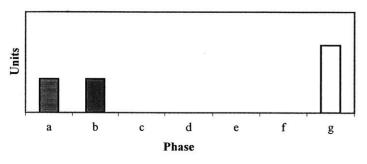

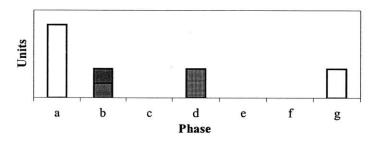

| Figure 12 - System Test 1 Failure Pareto by Test Phase                | 45  |

| Figure 13 - System Test 2 Failure Pareto by Test Phase                | 45  |

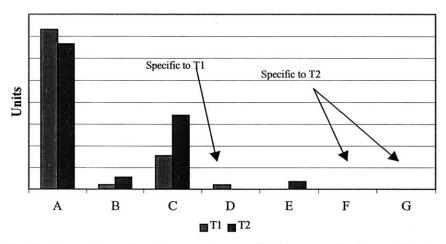

| Figure 14 - T1 vs. T2 by Test Phase                                   |     |

| Figure 15 - System Test 1 Phase B Failure Pareto                      | 47  |

| Figure 16 - System Test 2 Phase B Failure Pareto                      |     |

| Figure 17 – FPY Device Size 1                                         | 5.1 |

| Figure 18 – FPY Device Size 2                                         | 5.1 |

| Figure 19 – FPY Device Size 3                                         | 5.1 |

| Figure 20 – FPY Device Size 4                                         |     |

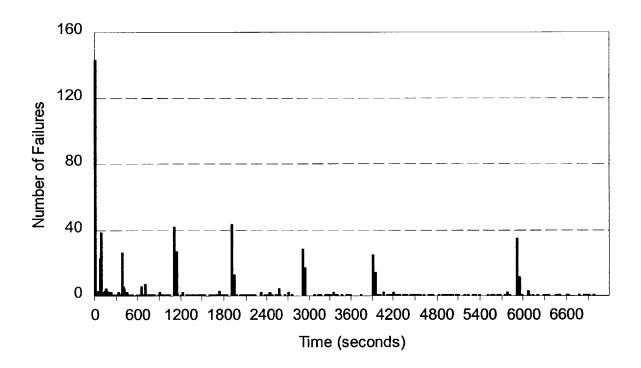

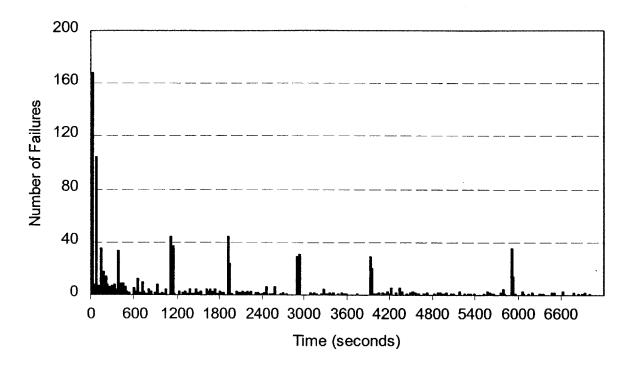

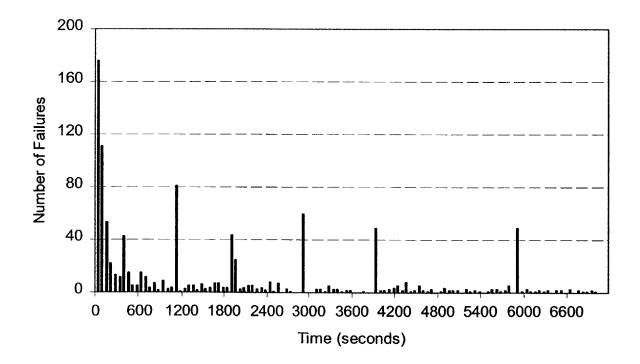

| Figure 21 – Device Burn In Failures (no bins)                         | 52  |

| Figure 22 – Device Burn In Failures (30 second bins)                  | 53  |

| Figure 23 – Device Burn In Failures (60 second bins)                  | 53  |

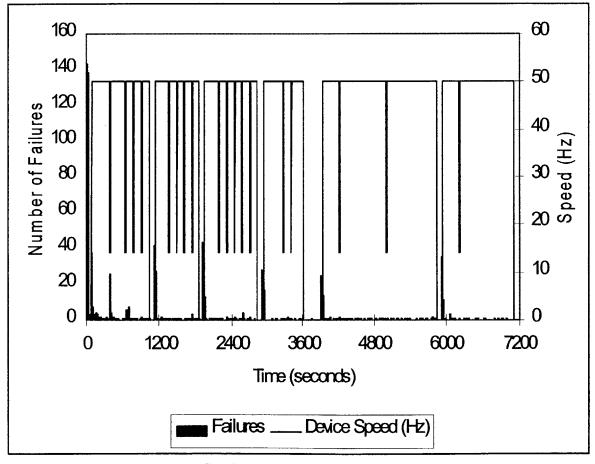

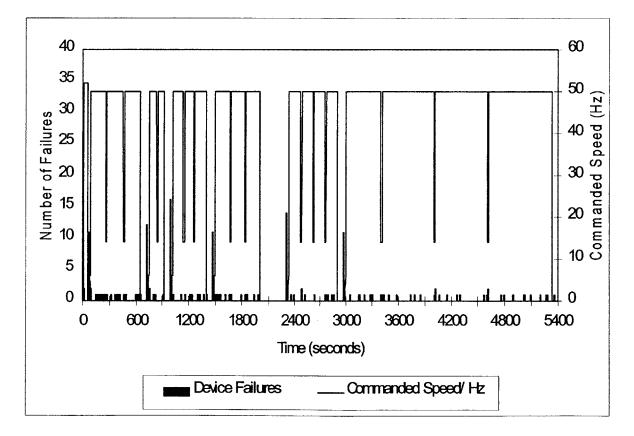

| Figure 24 – Device Failures vs. Commanded Speed                       |     |

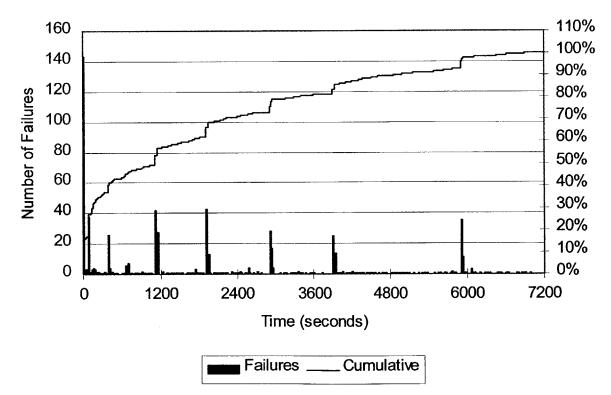

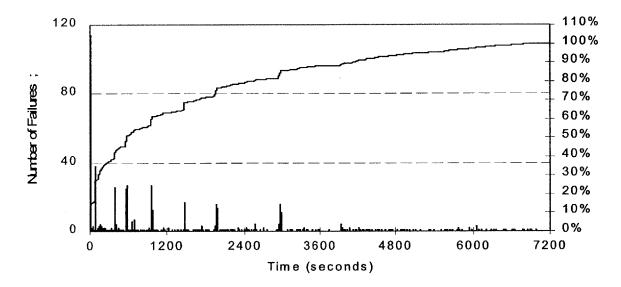

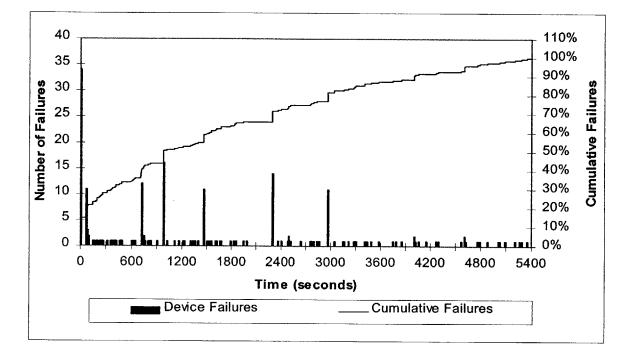

| Figure 25 – Cumulative Failure Rate                                   |     |

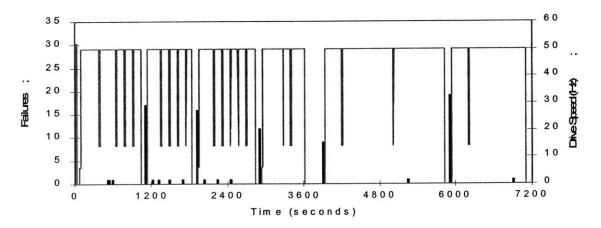

| Figure 26 - F24 Failures vs. Command Speed                            |     |

| Figure 27 – F24 as a Percentage of Overall Failures                   |     |

| Figure 28 – Failure Curve Without F24                                 |     |

| Figure 29 – Large Device Internal Temperature vs. Commanded Speed     | 61  |

| Figure 30 – Control Board Temperature vs. Test Time                   |     |

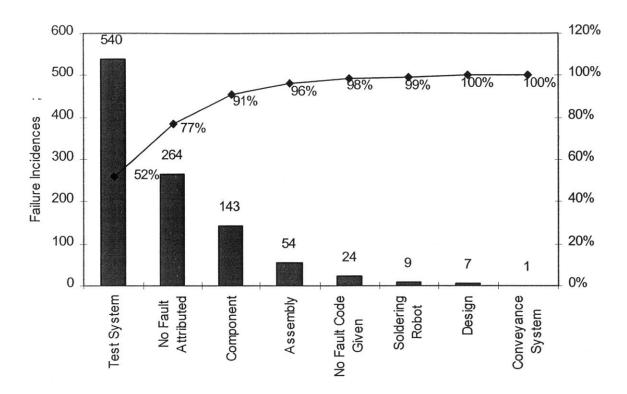

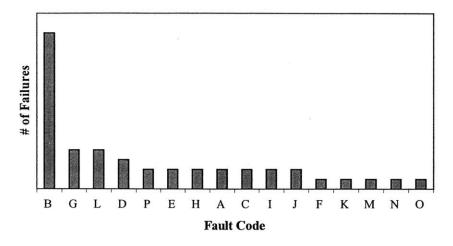

| Figure 31 – Fault Code Grouping Pareto                                | 64  |

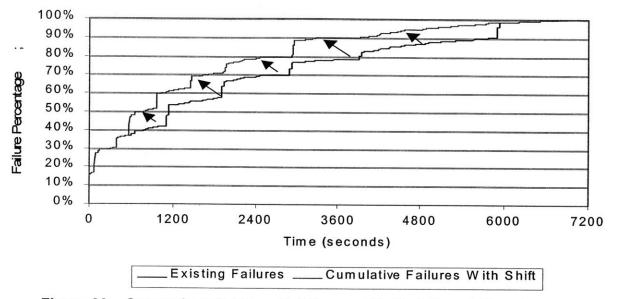

| Figure 32 – Projected Cumulative Failures with Spikes Shifted         |     |

| Figure 33 – Comparison Between Existing and Shifted Cumulative Curves |     |

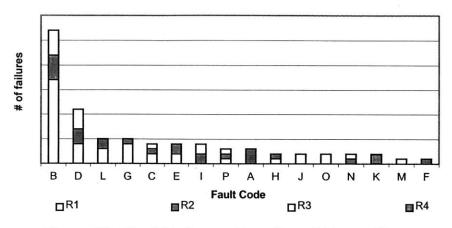

| Figure 34 - Fault Code as a Function of Frame Size                    | 69  |

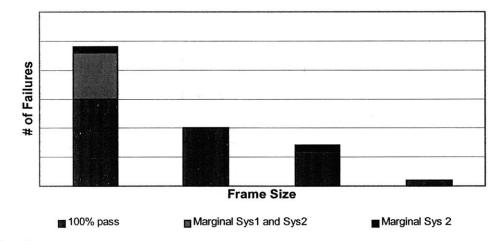

| Figure 35 - Test Results: Units that passed all quality tests         | 70  |

| Figure 36 - Units with 100% Cumulative FPY                            |     |

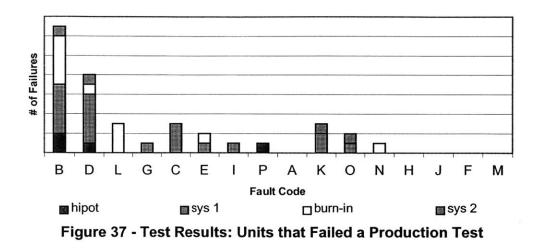

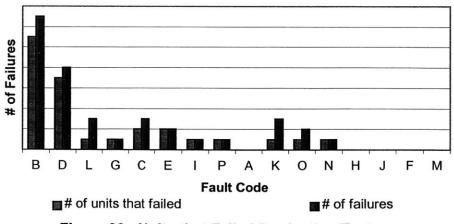

| Figure 37 - Test Results: Units that Failed a Production Test         | 72  |

| Figure 38 - Units that Failed Production Tests                        | 72  |

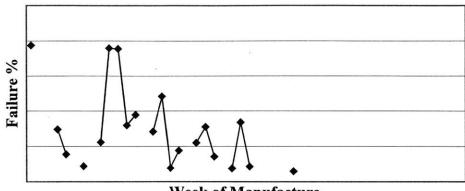

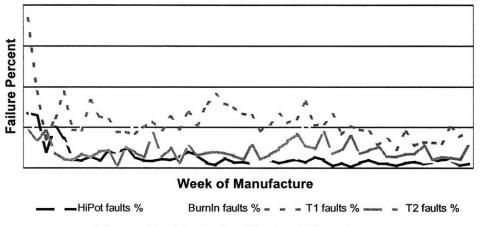

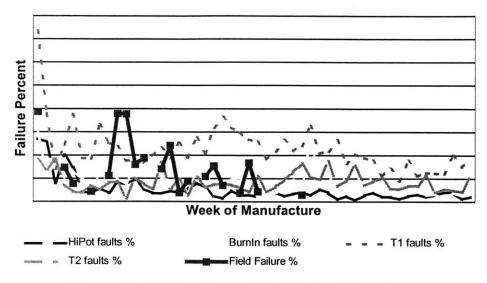

| Figure 39 - Failures by Week of Manufacture                           | 73  |

| Figure 40 - Field Failure Percent by Week of Manufacture              | 74  |

| Figure 41 - Faults by Week of Manufacture                             | 7.4 |

| Figure 42 - Failure Percent by Week of Manufacture                    |     |

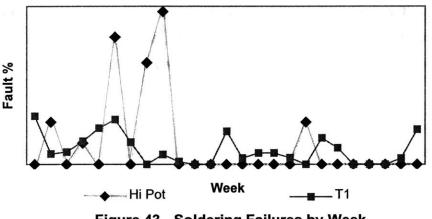

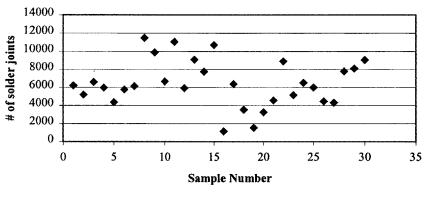

| Figure 43 - Soldering Failures by Week                                | 80  |

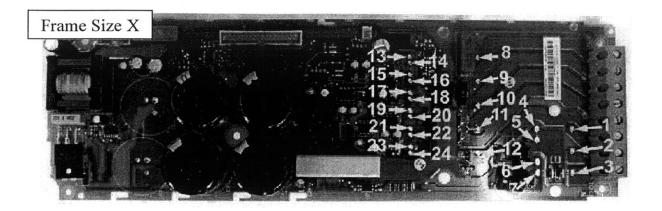

| Figure 44 - Photo Identifying Solder Joints                           | 81  |

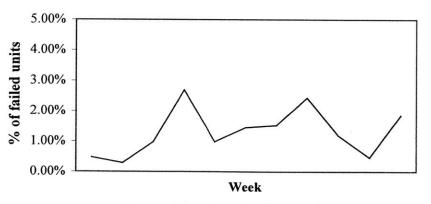

| Figure 45 - Operator Inspection Data                                  | 81  |

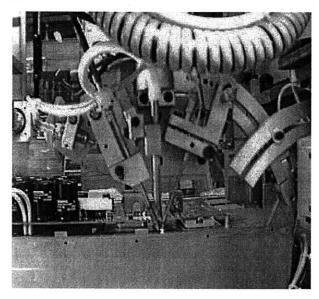

| Figure 46 - Solder Fixture                                            | 82  |

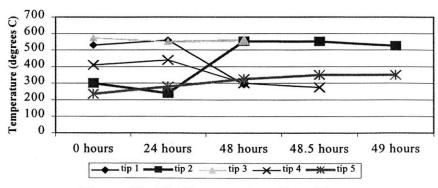

| Figure 47 - Solder Tip Data                                           | 86  |

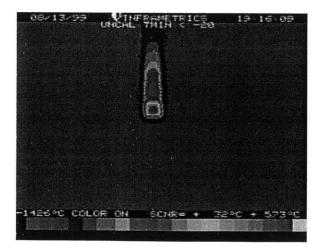

| Figure 48 - IR Camera Output                                          | 87  |

| Figure 49 - Tip Temperature Over Time                                 | 88  |

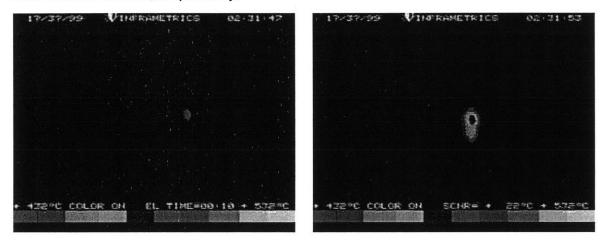

| Figure 50 - Initial Sign of Heat                     | 90   |

|------------------------------------------------------|------|

| Figure 51 - Thermal Signature of Tip at Steady State | 90   |

| Figure 52 - Initial Sign of Heat                     |      |

| Figure 53 - Stable Temperature                       |      |

| Figure 54 - Original 2 Hour Burn In Cycle            | 99   |

| Figure 55 - New 1.5 Hour Burn In Test Cycle          |      |

| Figure 56 - Failure Rate for New Burn In Sequence    |      |

| Figure 57 - New Burn In Test Cumulative Failures     | .101 |

## List of Tables

| Table 1 – Fault Codes             | 63 |

|-----------------------------------|----|

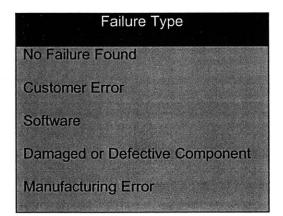

| Table 2 - Aggregate Failure Types |    |

| Table 3 - Benchmarking Results    |    |

# List of Equations

~

| Equation 1 – Statistical Capability Index |  |

|-------------------------------------------|--|

| Equation 2 - First Pass Yield             |  |

## Acknowledgements

First I would like to thank my husband Ken, for without him none of this would have been possible. His love and encouragement sustained me throughout the last two years. Ken has been a constant source of support for me. His patience with my busy schedule and my mood swings was angelic. Thank you so much Ken! I would also like to thank my family for their love and prayers.

Many thanks to my host company. I learned a great deal from the entire staff but especially from Mr. Harri Heimonen, my internship supervisor. I would also like to thank all the wonderful people who helped me survive the 6-month internship. Special thanks to my very good friends: Maria Lindroos, Meri Parm, Mika Winqvist, and Sami Wainio.

Next I would like to acknowledge Roger Maddocks and Charlie Brown from the Eastman Kodak Company for the corporate sponsorship I received during my time in the LFM program.

I would also like to acknowledge the overlap in thesis content between this thesis and that of my internship colleague, Erik Nelson. The collaborative effort throughout the course of the internship was a primary factor in the overall success of the project. Additionally, without the wisdom of Professor Thomas W. Eagar and Mr. Roy Welsch my academic advisors, this thesis would never have come together. Their guidance and advice throughout the internship and thesis authorship was priceless. Thank you.

Finally, much gratitude to Mr. Don Rosenfield and the entire LFM staff for their support over the last 2 years. LFM is an exceptional program and I feel honored to be an official alumnus of the program, MIT and Sloan.

| Kokoo kokoon koko kokko | Gather the bonfire together! |

|-------------------------|------------------------------|

| Koko kokkoko?           | You mean the whole bonfire?  |

| Koko kokko!             | Yes, the whole bonfire!      |

.

· .

`

## **Chapter 1 Introduction**

#### 1.1 Project Motivation

The motivation for this project came from a large industrial concern operating in the power electronics industry. This company manufactures many products both large and small and has a major presence in both the domestic and international markets for its diverse product portfolio. Although this company has many products, which it supplies to many industries, the company was primarily interested in optimizing the manufacturing of a specific product. This product is an electronics product within the larger power electronics product family and is utilized for a very wide array of uses. For confidentiality reasons the company which is the subject of this study will be forthwith referred to as "The Company". In addition, to mask the identity of The Company the products, which are the focus here, will be simply referred to as "The Product".

The space which The Product operates in is currently rather dynamic by the staid metrics of traditional industrial concerns. "The market for "The Product" experienced an annual growth rate of just over 7% between 1995 and the year 2000<sup>1</sup>". Dramatic economic growth in developing countries such as China, India, and Southeast Asia is providing enormous potential for the product in these regions. Furthermore industrialized nations such as North America and Japan continue to purchase this product, to improve manufacturing quality and increase productivity.

Fierce competition and declining prices of power electronics are driving the average selling prices of products such as these down. Additionally, technology is moving so fast today that product life cycle is rapidly declining. Once lasting 10 to 15 years, product life cycles have been driven down to 3 to 5 years for micro (0-4 kW) and small (5-40 kW) products. Accelerating competitive pressures are driving suppliers to find the most cost-effective production methods.

Recent advances in materials and electronic component technology accompanied by price pressure, has made it necessary for most suppliers to out-source the fabrication of virtually all product components. Specifically, components such as printed circuit boards and power semi-conductors have become commodity products and have been outsourced as a competitive advantage. Outsourcing has reduced internal overhead costs and provides direct access to the latest technological developments in these areas. Today the core competencies of product suppliers lie in the realm of product design & development and assembly.

Perhaps the most time consuming and capital intensive portion of assembly of this product is the test system. Although the level and thoroughness of these systems varies by manufacturer, a comprehensive test system including functional and stress screening technologies can increase assembly times by up to 400% and can more than double the capital investment required in a new assembly line. Comprehensive test systems not only increase capital investment and assembly costs, but in many cases add an additional level of complexity to the process, ultimately increasing ramp-up times and reducing flexibility as volumes fluctuate.

The primary purpose of the test system is to screen components for early life failures and to verify proper assembly, ultimately resulting in increased outgoing quality levels and reduced failures during customer operation. However determination of key performance characteristics and the resultant test system are typically developed during the design phase of the product and are seldom revised after the design has been released to manufacturing. The Company believes there is value in optimizing test methods, without negatively impacting quality. This is the impetus behind this project and thesis.

#### 1.2 Project Definition and Resulting Priorities

The original scope of the project was broadly defined as 'an effort to develop a new philosophy and new methods in production testing'. Early in the venture The Company's project definition was summarized into two concise statements:

**Priority 1**: Benchmark industry best practices amongst competition and equivalent companies to determine optimal quality control procedures with minimal cost impact

**Priority 2**: Determine optimal test methods to achieve desired quality goals and decrease overall test times by 50%

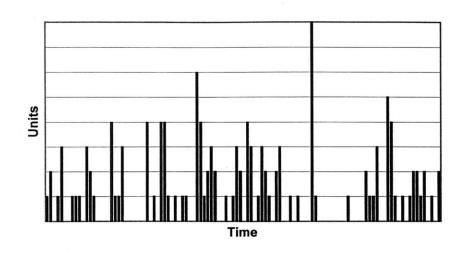

Four product lines were identified that accurately represented the manufacturer's business. This list of four was further focused down to one product line that had a significant amount of data available for analysis. This data was collected by an on-line production test system, stored in a database and was thought to be the most accurate data available. Additional information and description of the product line and test system will be provided in Chapter 3.

The development of two priorities and the identification of a key product line became the basis to approach development of new test philosophies and test methods over the course of the project.

### 1.3 Approach & Methodology

The two priorities, although based loosely on each other, were approached simultaneously. Each had an individual approach and required different resources, as outlined below.

#### 1.3.1 Priority 1

Eight companies were identified for the benchmarking study. The companies included some competing directly in this industry and others in the computer, printer and copier industry. Additional industries were chosen, as they were expected to share like electronics components and have similar assembly, quality and test system issues. The benchmarking study was also used as a vehicle to leverage Massachusetts Institute of Technology (MIT) Leaders For Manufacturing (LFM) program relationships in an effort to gain access to similar manufacturing processes and to promote knowledge transfer.

Each company included in the benchmarking study was interviewed and questioned from which a correlation matrix was developed. The matrix became the basis for developing new test system methodologies and for making recommendations to the product design and development process.

#### 1.3.2 Priority 2

An extensive analysis of data collected by The Company's on-line production test system was performed. The on-line test system records and stores test results from each of the four System Tests. The four System Tests consist of Hi Pot, System Test 1 (T1), Burn In and System Test 2 (T2). A complete description of each test can be found in Chapter 3. When possible the data was analyzed in product sub-groupings according to various product characteristics, including device size and voltage rating.

Using the production data, a failure analysis of the number of units that failed per units tested was completed. The Pareto analysis of test failures was then compiled and compared across products. Next, a first pass yield definition was agreed upon and

calculated for each System Test. Finally, field failure data was analyzed and compared with the findings from the on-line test system performance analysis.

The industry benchmarking findings and test system analysis results became the basis for recommendations to the product development process, redefining the production test methods, and the justification to reduce test times. This thesis explores the above analysis and findings in depth.

#### 1.4 Project Goals, Measurements, and Deliverables

The project goals were again based on priority. From the benchmarking study, priority 1, a summary of industry best practices in quality control and test procedures was compiled. The summary compared test methods on a product rating, hp or kW, basis. This analysis and summary can be found in Chapter 2.

By establishing new test methods (priority 2) test times were to be reduced by 50%, without compromising current field quality levels. The baseline used for test time reduction was established in the first week of the on-site investigation. Recommended changes to the current product development process and modifications to the current test methods were presented upon the completion of the on-site investigation. Recommendations to improve the current test methods are discussed in Chapters 4 through 6.

## **Chapter 2 Competitive Benchmarking**

#### 2.1 Industry Overview & Market Share

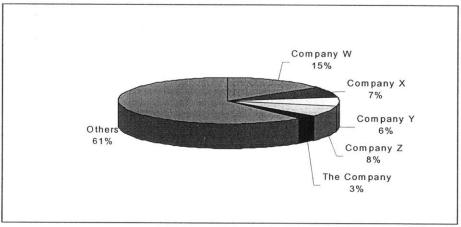

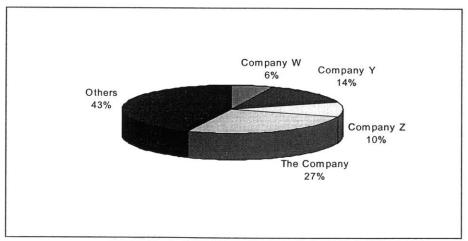

These devices are typically categorized into five output capacity (kW rating) segments: micro (1-4 kW), small (5-40 kW), midrange (41-200 kW), large (201-600 kW) and mega (>600 kW). Growth in the industry will primarily come from the micro and mega segments. Companies such as The Company and Its other large competitors are considered the leaders in The Product's industry, accounting for the majority of worldwide revenues. In 1995, industry shipments of the product and associated services totaled \$4.13B. Shown below are the respective market shares in the Micro (Figure 1) and Mega (Figure 2) segments:

Figure 1 - Market Share of Leading Micro Product Players

Figure 2 – Market Share of Leading Macro Segment Players

#### 2.2 Overview of Subject Companies

Ż

The subject companies for this benchmarking study come from a wide variety of industries. The purpose was to gain insight into the testing systems used in the greater electronics manufacturing industry. Although the environmental conditions under which The Products operate may present both thermal and particulate-born challenges (i.e. dirt, dust, chips, and other contaminants) to the product design and operation, the underlying electronics should require similar testing to ensure product quality and operational excellence. Therefore, the scope of companies and industries examined were not limited only to The Product's industry or even to the power electronics industry, although, both are present in the subject population. The following presents an overview of the companies, their products, and the environmental conditions under which they may operate. This is done so as to provide a framework from which to base comparisons of testing systems to those used at The Company.

Company A is a producer of high-speed digital imaging and printing systems. Their products consist of very large units capable of handling global network printing responsibilities. The copiers are highly customized and produced on a make-to-order basis. The majority of their products operate at 220 VAC with both 50 and 60 Hz options. Under these power ratings internal thermal conditions are high, especially on a component by component basis, however, generally the units are operated almost exclusively in environmentally controlled rooms. The conditions here are generally less than 80° Fahrenheit and humidity is controlled.

Company B is a global player in the personal computer and workstation industry. Company B produces a wide range of both laptops and desktop units covering entry level units up to networked workstations. The power ratings on their products range from 110 VAC on the smaller units up to 220 VAC on their larger workstations. The division that was studied are responsible for building desktop units only, both for the PC and workstation markets. This division builds both standardized and customized products supplying both make-to-stock and make-to-order demand scenarios. Internal thermal conditions in these products is rather benign when compared to the industrial environment, however, component specific heating is a problem.

Company C manufactures high-end electrical devices mainly for the North American market. The company supplies these devices in the 0.4 to 750 kW range with power ratings of 230, 460, and 575 VAC. The larger sizes are very customized and built-to-

order, whereas the smaller devices have little to moderate customization and are mostly built-to-stock. These devices are used almost entirely in industrial environments where conditions are not controlled. The thermal conditions can be challenging as high temperatures are generally present. Additionally, dirt, dust, and various other contaminants common to industrial settings are present and may work into the devices.

Company D is a global producer of large and small printers and test and measurement equipment. The products have voltage ratings of 110 VAC and more. These broad ranges of products operate in a wide variety of environments. The office products generally operate in temperature and humidity controlled environments whereas the test and measurement equipment may be exposed to more deleterious environments such as those generally found in the industrial setting.

#### 2.3 Testing at Subject Companies

#### 2.3.1 Company A

Manufacturing at the division of Company A (note: only one division was investigated) consists mostly of final assembly. It is here that components and sub-assemblies from suppliers are assembled and tested prior to delivery to the customer. The cycle time for the product is approximately 33 hours; approximately 11 hours of which is attributed to assembly and approximately 22 hours of which is attributed to testing.

The test sequence consists of four steps. The first step is the Hi Pot test. This test is a safety check of the unit's circuitry. Here, as is typical within the electronics industry, a large potential is applied to the products main circuitry to ensure load-carrying capability. Next, the unit is subjected to its first power up. Here, generally, is where the first failures are encountered.

The automation and conveyance system responsible for controlling the printer's 'paper path' are both delicate and significant to the printer's proper operation. In addition, each component's harmonious operation with its neighbors is crucial to the overall performance. The next step, therefore, is to test this system by performing a continuous 'paper run'. The length of this test is approximately 25 minutes and can best understood as a functional test of the entire paper path. It is, however, the printer's first

period of extended operation and, therefore, the first test of component performance and reliability.

After assembling the outer cabinet a final quality check is performed on the printer prior to shipment. Some units may be exposed to an additional quality test at this point. This test consists of an extended paper run test and is performed on a sampling basis, only. This test is a quality check of both the manufacturing and design systems. It is here that small defects may be exacerbated into larger problems resulting in product degradation and, quite possibly, unit failure.

Although the extended paper run test might be perceived as a test performed specifically to highlight and expose 'early life' failures it does not necessarily perform that function. Notably, in fact, company A does not perform any tests to identify early life failures. This is considered to be the domain and responsibility of the component and sub-assembly suppliers. The company's perception of itself is as an assembly operation only and the extended paper run test is performed to ensure systemic quality is maintained and product wide functionality optimized.

Due to the fact that the unit was recently sold, field quality data was unavailable. It is just beginning to become available internally. Therefore, the data currently is only beginning to be evaluated for product performance and is not a good measure of overall test system effectiveness.

In addition to the quality processes used in printer assembly, company A also focuses on the quality of incoming components. During the product design phase components critical to overall product quality are identified and quality level specifications are established. The desired level for the supplier's process capability is also established. This number is typically set at a Capability Index of  $C_{pk}$ =1.5. The Capability Index is a statistical representation for process control widely used in industry.  $C_{pk}$  is defined by the following equation:

$$C_{pk} = \min\left[\frac{USL - \overline{X}}{3\sigma}, \frac{\overline{X} - LSL}{3\sigma}\right]$$

Equation 1 – Statistical Capability Index<sup>2</sup>

where

USL = Upper Specification Limit LSL = Lower Specification Limit  $\sigma$  = Process Standard Deviation  $\overline{X}$  = Process Mean

Company A then meets with suppliers, prior to establishing contracts, to verify the suppliers' manufacturing process can meet the required specifications. The Supplier Quality Assurance Group is assigned this job. The Group is a team of technical professionals involved in the product design phase as well as the manufacturing process. In notable situations where the company is concerned, the team has even gone into the supplier's factory and worked with the supplier to reduce process variability and meet required quality levels. Hands-on grooming, such as this, can prove immensely rewarding in understanding the supplier's underlying process capabilities. The company is, subsequently at a distinct advantage, such that the impact of proposed future changes and suggestions on product functionality and quality are better understood.

#### 2.3.2 Company B

The testing at company B consists of three very different approaches which when combined is designed to minimize production testing. These three testing procedures are known as HAST, HASS, and run-in. HAST refers to Highly Accelerated Stress Testing. HASS refers to Highly Accelerated Stress Screening. Run-in simply refers to an extended period of operation.

HAST testing at company B is performed during the product design phase. In fact all HAST testing should be performed prior to product release to manufacturing. The idea is to test the 'goodness' of the design as one company representative noted. When the initial product design reaches a certain maturity in which component, sub-assembly, and/or full-assembly designs have been agreed upon the unit is tested to destruction under a wide array of environmental conditions. The designs are generally subjected to vibration and rapidly changing thermal environments to incur increasingly stressful conditions. When the unit fails under these conditions a quality examination loop is used to determine the failure mechanism. This information is then fed back into the design loop and the product is redesigned to correct the offending condition. After several

iterations the most likely failures are identified and corrected, thereby increasing the overall robustness of design and reducing the incidence of failure under normal or even extreme environments. Company B feels that they are testing not only component quality and design, but also assembly errors and manufacturing induced failures.

The next level of product testing performed at company B is HASS testing. HASS testing, due to the expense, is not performed on all products. Products, which receive HASS testing, are chosen based upon their cost and complexity. Only the more complex and/or costly products are chosen, as the cost for this level of testing may be high.

HASS testing backs off from the extremes of HAST testing. The objective of the one hour long test is not to take the product to destruction, but to test it to the outer operating design limits or specifications. The purpose is to highlight areas in the in-line production process and design which may be marginal and, therefore, not be able to stand up to the rigors of the outer operating regimes. As in HAST testing, the products are subjected to vibration and rapidly changing thermal environments to induce the greatest environmental stresses. Again, however, these stresses should only be at the design limits. As failures occur, a profile of failure mechanisms can be obtained. In addition, failure rates begin to be understood.

Unlike HAST testing, however, HASS testing is performed mostly during the manufacturing ramp up stages. At the beginning of product manufacture the sampling rate is 100%. Although timely, the low volumes allow for maximum testing. Quickly the sampling rate is dropped as failure profiles are developed and rates climb. Company B ultimately drops HASS testing as full volumes are generated and data acquisition is complete.

The final level of testing utilized by company B is the run-in test. This test verifies the entire manufacturing process is in control. The length of the run-in test is chosen at 96 hours. The units are allowed to operate in a normal environment and failures are monitored. The company uses the information from this test to develop a Mean Time To Failure (MTTF) profile. As the MTTF profile is better understood, the optimal point for run-in is identified and the test length can be modified to account for the changes. A sampling rate is used for the run-in test, however, this rate was not identified.

Company B has also established quality programs with their suppliers. Critical components, specifically PCB's, have additional testing requirements placed upon them. These tests are performed at the supplier. Specifically, boards are subjected to stress screening at elevated temperatures and with high and low voltages applied. The boards, along with other delicate components, are also exposed to a series of shipping tests, including drop tests to verify packaging requirements. Contracts with suppliers include specifications as to the type and degree of testing, as well as minimum acceptable quality levels. Company B also has a group of component quality engineers, who sample poor components and provide feedback to the supplier regarding quality levels. In some cases, they might also utilize their unique viewpoint as a customer to work with the supplier to recommend improvements to the manufacturing processes.

#### 2.3.3 Company C

To ensure testing success company C maintains a rigorous quality program. This program begins with an incoming inspection on new and poor quality level components. Such inspections are carried out to verify supplier compliance with existing design and quality goals. All components are subjected to inspection. In addition, the manufacturing process is audited to ensure that it is capable. A random sampling of the process steps is conducted to ensure adequate coverage and in-process quality.

Interestingly, to maintain quality of the most delicate components, company C actually builds and assembles the PCB's in-house. The company has both through-hole and surface mount technology manufacturing capability. Leveraging a company wide competency in the manufacture, assembly, and test of PCB's allows the company to ensure a steady flow of quality boards. The company maintains a 'Center of Excellence' approach in the design and build of its boards. After board design the company will maintain board production in house through prototype and pilot stages. Only after the process has been determined to be in control and capable is the board manufacturing subbed out. Ultimately, they sub-contract up to 50% of the long term production, but always keep the remainder in-house to ensure adequate part flow. An additional benefit of maintaining up to half of the board production is that it gives the company a sense of the sub-contractors capabilities. By doing this the company can always discern between true production problems at the sub-contractor from others. Company C, therefore, effectively has a tight leash on its most delicate component's supply base.

As the PCB's are seen to be the most delicate part in company C's product with respect to reliability and manufacturing process the control of this step is seen as crucial to their product's manufacturing success. Using several SPC techniques as outlined within ISO 9000 guidelines the PCB manufacturing process is controlled. All product and process discrepancies are documented. Each discrepancy is then corrected and the corrective action is traced back to its source to ensure no further occurrences. This final step in preventative process 'maintenance' is key to long term process maturity.

The company has several quality improvement programs that it institutes as its primary continuous improvement tool. Utilizing field and manufacturing quality data the company has developed a fact based prioritization program to focus on the most dominant issues affecting its customer base and its manufacturing community. Issues in the manufacturing phase can be anything affecting the design, component, or assembly of the product. Focusing only on major product lines, the failure mechanisms are ranked and the top five are identified for investigation and solution recommendations. The top five problems can be identified via feedback from the field and/or issues affecting plant yields.

Using product return information, manufacturing data, service call information, and repair center data, the process is to sort, categorize, and pareto the data. This will allow the identification of the top five product issues. Next, ownership is assigned. Ultimately, corrective action is determined and implemented. The process output can be changes to product design, manufacturing process, testing procedures, or simply documentation.

The company employs a team-based solution to this process. The team is led by a quality group, but is cross-functional in its nature. The rest of team is picked from engineering, engineering quality, component engineering, quality/test engineering, manufacturing engineering, repair and technical support, purchasing, customer quality support, and marketing. Such diverse team membership ensures a wide scope to the solution and to the corrective action.

Quality programs at company C do not stop at the time of product delivery. The company has set up a Technical Rapid Response Team. The purpose of the team is to provide 24-hour response for all direct out-of-the-box failures. In such an occurrence a new product is immediately routed to the customer. The failed unit is, meanwhile, direct shipped to the company's engineering department for failure analysis. This process not only provides immediate customer response and, hopefully, satisfaction in the face of a

22

ź

rather difficult scenario, but also provides the company with direct access to failure data. In light of the typical problems surrounding holes in field data this advantage can be notable.

Product testing at company C corresponds strongly with the life cycle requirements of the product. During the product design phase the company employs Highly Accelerated Life Testing (HALT) very similarly to the HAST testing employed by company B. During the pilot and ramp-up stages a typical Burn In testing process is used. When the product is at full manufacturing run, an audit Burn In testing strategy is used. Finally, to support the long term product life, reliability testing is conducted.

During the design phase HALT testing is used to validate and demonstrate the design limits and tolerances of the product. Here the upper and lower destructive limits of the product are explored and documented. Through a series of repetitive applications of thermal, electrical, and/or vibrational stresses the lowest common denominator of failure mechanisms can be quickly identified. Additionally, their solutions can be verified via the same tests ensuring a long-term fix. It is important here to note that the stresses that are applied need to be applied not only with a large enough magnitude to induce failure, but also at a high rate of change. For instance, a thermal stress may be applied, however, a constant thermal stress is of less value than a changing thermal gradient on the order of 10-20 °C per minute. The applied stresses in these cases are far more severe. Correctly applied, HALT testing during the design phase should capture design failures and component defects.

Burn in testing is used during the pilot stage of the product life cycle. Using the operational limits as boundaries for load application, the products are subjected to thermal loads and power cycles. This testing should discover process, supplier, and design defects. Additionally, the Burn In process should be a validation of the proper use of Design For Manufacturing techniques, the manufacturing process, and supplier quality. During the pilot stage a 100% Burn In testing rate is conducted on an identified pilot lot. The testing is conducted at a fixed elevated temperature. This temperature is chosen to be the product rating temperature.

The length of the Burn In time is quite long at the beginning of the pilot stage and is shortened throughout the stage. Initially, a Burn In time of 96 hours is chosen. The units, therefore, are run using inductive loading only (no complementary device loading) for a full 96 straight hours in a chamber with an ambient temperature equivalent to the

product's design operational limit. Eventually as product design and operational confidence is achieved the Burn In time is reduced... first to 48 hours, then 24, and finally 12 hours. Each pilot lot receives 100% Burn In coverage during these stages.

After the pilot and ramp up stages Company C employs an audit Burn In or final product Run In test. The purpose of this type of testing is to assure process control and supplier quality; effectively to maintain overall quality assurance while minimizing field quality problems. Run in testing differs from Burn In testing in the length of time tested and the applied ambient thermal loads. In the case of the Run In tests 100% of the units produced experience full load dynamic testing. Depending upon the product size test lengths vary from 12 minutes to two hours and are based upon ensuring that, at minimum, three product time constants are achieved. Additionally, the current load is cycled approximately every two minutes from 50% to 100% and then to 150% to induce the dynamic loads. The loads are simulated using matching motor dynamometers. Finally, in lieu of operating the Run In tests at an elevated ambient temperature the heat generated from the electrical loads is deemed to be sufficient to simulate thermal loading.

The long-term reliability of the product is also tested. Here units are randomly sampled from the line. Long-term operational tests are conducted at the rated temperatures, loads, and power cycles to help understand duration capabilities. Such testing tests the long-term reliability of the design, process, and components.

Lastly, Company C, in addition to its product life based testing, performs extensive PCB testing. In circuit testing and parametric functional testing are conducted in an attempt to achieve high rates of out-of-the-board shop quality levels. Again, PCB's are considered to be a company key technology, or core competence, and this testing attempts to maintain high levels of quality in what they consider to be the most delicate component. Additionally, the vendors that Company C ultimately chooses perform board level testing in the form of "bed of nails" conductance tests<sup>3</sup>. Coverage, however, was estimated to be only 70% at best. Interestingly, Company C used to perform Burn In testing on the PCB's but no longer does so. Unfortunately, the reason for the cessation of testing was not determined.

#### 2.3.4 Company D

Due to the diversity of its product testing at Company D is, by necessity, similarly quite diverse. Due to this diversity, specific testing procedures were not explored. Instead, investigation focused more on general testing trends at the company. Specifically, the use of HAST testing, in lieu of the traditional Burn In testing, was explored.

At Company D the use of Burn In testing was slowly phased out over many years in favor of HAST. Although the company had a long history of performing Burn In testing to identify infant mortality failures there is almost no Burn In conducted anymore. Company representatives did, however, note that pockets of resistance to new procedures did remain as members in these areas were not yet convinced of reported testing benefits provided by HAST.

To understand the benefits of Burn In Company D representatives required data. To convince themselves, tests were performed in which even serial numbers on a given product line were shipped without Burn In and odd serial numbers were shipped after the normal Burn In procedure. After waiting upwards of 1-2 years for the necessary field quality data to be given adequate time to be reported, the experimenters determined that there was no statistical evidence to buttress the additional testing. Specifically, they could not show with statistical clarity that field quality improved (i.e. the rate of early failures was reduced) by performing a traditional Burn In test. To ensure they had enough data to capture the necessary failure instances the even/odd experiment was performed for an entire year's production run.

The results from this study have apparently changed the way production testing is performed at the company. Incorporating HAST into the normal design phase is much more commonplace. To enhance these procedures the process includes the use of thermal stressing with a very high rate of thermal change ( $\Delta T > 10 \,^{\circ}C/minute$ ). In fact, the company believes subjecting the product to a constant temperature is a very poor application of stress and is not productive in ferreting out failures.

In addition, the company is exploring the use of vibrational stressing to investigate how applied vibration can affect the product life and failure rates. The company claims to have shown that subjecting a product to five minutes on a vibrating table induced the same failure rates as a week of stress testing. Unfortunately, these claims are unsubstantiated otherwise. In vibrational testing it was pointed out that pseudo random

vibrations should be applied to ensure no directional bias is applied. Such a bias might induce rapid failure rates in favored directions and ignore failure rates in non-favored directions. To support such pseudo random vibrational testing the company uses a 6-axis vibration table. Internally, the company refers to the application of thermal cycling and random vibrational testing as STRIFE testing (STress and LIFE testing).

To implement the HAST testing the company uses a sampling strategy to ensure consistent testing application during the production run. The reported sampling rate is approximately 1%. It was not discovered how this rate was determined. To ensure useful results from the HAST testing the company tracks down the failure's root causes and corrects them. This is the most important role of the testing procedure.

#### 2.4 Summary of Benchmarking Study

This benchmarking study provided insight into some of the testing procedures currently being employed within the electronics manufacturing industry. Apparently procedures such as HAST testing are being utilized in an effort to provide more robust designs to the manufacturing floor so that in-line testing such as traditional Burn In may be reduced. This philosophy, if employed correctly appears to provide a more robust product design greatly reducing cycle time and subsequently product cost.

Other results from the study showed that there is a wide tendency within the industry to work much closer with the supplier base. Several of the companies investigated were conducting extensive supplier relations. To the extent that the suppliers were comfortable allowing these companies onto their manufacturing lines and even their product design groups, these companies were quite successful in building mutually beneficial relationships. The relationships served both sides by improving incoming component quality to the company's manufacturing lines and ensuring future business for the suppliers who showed a willingness to grow and adapt to process improvements. Such improvements with component quality are sure to improve yields for in-line testing possibly allowing the companies to reduce their dependence upon such testing

Additionally, by evaluating the capabilities of their supplier's processes the companies were able to successfully manage future product and process changes. Specifically, they were able to reduce incoming product variability reducing the need for more extensive in-line testing. Effectively, such testing was successfully removed from the company's manufacturing and pushed upstream, where appropriate, to the supplier.

## **Chapter 3 Product Line**

#### 3.1 Product Overview

The product line consists of four frame sizes. The term frame size refers to the physical size or footprint of the unit. A further sub-set of product differentiation within each frame size is the type series. The rated output power (kVA), voltage rating (Vac) and enclosure class designate a type series. For the purpose of this study, only units manufactured at the internship site were analyzed, yielding a final number of type series of 10.

#### 3.2 Product Flow

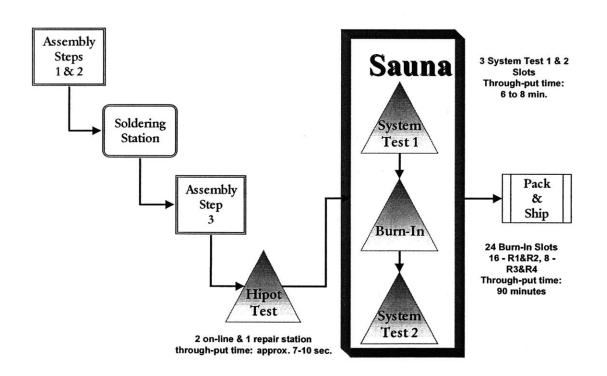

The product flow is shown in Figure 3 below:

#### Figure 3 - Manufacturing Product Flow

All products are assembled on this production line, in various sizes and voltage ranges. Batches can run from as little as 1 unit to as many as 15. Assembly step 1 is a basic assembly step where the heat sink and various components such as fans, etc. are attached to the frame or platen. The platen is the board that supports the unit

throughout the production process, allowing it to be transferred by powered roller conveyors. The platen has a bar code that contains all vital product information and is used in all product-tracking software throughout the assembly process. Assembly stage 1 feeds assembly stage 2 via powered conveyors.

Assembly stage 2 consists of two identical and parallel assembly cells, with one operator in each cell. As in all cell designs, each operator has all the tools and components in the cell necessary to perform the assembly process. The operator assembles additional components onto the unit, performs a visual quality check, and releases the unit to another powered conveyor. Immediately after assembly stage 2 the powered conveyors merge, feeding a single soldering robot.

As the unit enters the soldering station, the robot visually aligns itself to the size of the platen/unit, reads the bar code and proceeds with the soldering process. Upon completion of the soldering sequence, the unit is transferred to a power conveyor which, using a queuing algorithm built into the system software, transfers the unit to one of two assembly stage 3 cells.

At assembly stage 3, the operator performs a visual inspection of the solder quality, attaches additional components to the unit and releases the device to the first of four consecutive test stages. Each test stage is highlighted in the diagram above for clarity.

There is one Hi Pot test station on each line and also one at the repair station. Upon passing the Hi Pot test, the device enters the 'sauna' for the remainder of the test sequence. The sauna is a thermally controlled environment, operating at ~45° Celsius. While in the sauna, the device is subjected to three additional tests: System Test 1, Burn In, and System Test 2. The device navigates within various testing slots with the aid of a manipulator arm. The diagram above indicates the number of test slots designated for each test and frame size. If the device fails any of the four tests, it is immediately rejected and sent to the repair station (located outside the sauna). Additional explanation of each test sequence is found in section 3.3.

After completing the test regime successfully, the device is transferred from the sauna to the pack station. The device is removed from the platen, the cover is placed on the unit and it is boxed. Product manuals and information sheets are placed in the box prior to the taping operation. The boxes are then transferred to the palletizing line for

stretch wrapping and shipping. Platens are subsequently returned to assembly stage 1 via a high-tech, over-head powered conveyor.

#### 3.3 On-line Production Test System and Database

The product-line utilizes an advanced test system to ensure product quality. This test system was developed in partnership with a local software provider. Tests are performed after the final assembly stage of the unit to verify the unit is assembled and working correctly. The test system consists of four product tests: Hi Pot, System Tests 1 & 2 and Burn In. Each test has several potential outcomes. The two most common outcomes are pass and fail. If the device under test (DUT) receives a test outcome of 'pass' the unit proceeds to the next test or the final stage of production. If the DUT fails a System Test, the unit is automatically sent to the repair station where a trained operator inspects the unit. After the unit is repaired it returns to the production flow at the first System Test, Hi Pot. Each unit must receive 4 consecutive passes, one from each test, prior to shipping.

All test results are stored in an on-line production database in various data tables. A brief explanation of each System Test and potential outcomes is discussed below.

## 3.3.1 Hi Pot Test Description

The purpose of the Hi Pot or insulation test is to ensure that the construction of the converter has not been damaged in any way and that the device has the capability to withstand the demanded voltage. There are three Hi Pot test stations, one after each assembly stage 3 cell and one at the repair station. The duration of the Hi Pot test is 7 to 10 seconds, depending on the frame size being tested. The two possible results of the HIPOT test are pass and fail.

The test consists of 3 primary phases: insulation test 1, voltage withstand, and insulation test 2. A brief description of each phase follows:

**1. Insulation Test 1:** Measures the insulation resistance between the main circuit and the chassis. Measures insulation resistance. This test is considered a safety check

**2. Voltage Withstand:** Connects power between main circuit and chassis. Measures leakage current and verifies insulation is OK.

**3. Insulation Test 2:** Repeats insulation test 1. Verifies the voltage withstand test has not compromised the integrity of the unit.

If the unit passes the test, it is sent into the 'sauna' to continue the test sequence. If the device fails, the test system records the failed phase and the measured values of the test. The unit is subsequently released to the repair station. When the repairperson is confident the unit is operating correctly, she re-tests the unit at the Hi Pot station located at the repair station. If the unit passes, it is transferred to the sauna and proceeds to the next test stage. If the device fails, the repairperson continues to troubleshoot the problem until the device passes the Hi Pot test. Upon each trial, the repairperson records her efforts in the on-line database, including the action taken or component replaced.

#### 3.3.2 System Test 1 & 2 Test Description

The purpose of System Test 1 & 2 is to ensure the components of the converter are not damaged or defective and that the converter operates as designed. The two System Tests are virtually the same; however, in System Test 2 the device has been exposed to Burn In and is operating at an elevated temperature (see the next section for a detailed description of Burn In). Each of the System Tests has four possible outcomes: pass, fail, marginal, and abort. The pass and fail qualifiers were discussed in the previous section. A marginal outcome indicates the unit has passed the test but the measured values are within 10% of test limits. Upon receiving a marginal qualifier, the unit proceeds to the next step in the production process without delay. Operators are unaware of a marginal test outcome. The abort qualifier indicates an operator aborted the test due to operator error or test system error.

The System Tests are anywhere from 6 to 8 minutes in length. The test time varies based on System Test 1 vs. System Test 2 and the frame size. The tests consist of the following 15 phases. Each description is numbered first with the phase number corresponding to System Test 1, followed by the phase number of System Test 2. An X indicates phases absent from the test pattern and exceptions are noted in the test description:

**1,X. Verification test of the intermediate circuit:** Consists of a low voltage and high voltage level. Verifies there is no short circuit in the main circuit, DC capacitors are operating correctly, and that discharge resistors are good. This test is specific to System Test 1.

**2,1. Connection of Supply Voltage:** Exposes the unit to normal operating condition and voltage. Measures the supply voltage, verifies capacitors are balanced and that electronics have supply voltage.

**3,2. Voltage measurement and serial communication verification test:** Measures that the unit sees the same voltage as measured in the test above and that the software is running.

**4,X. Size Check Test:** Reads the unit specification from the palette and verifies the correct printed circuit board has been used in the assembly process. This test is specific to System Test 1.

**5,X. Software Version:** Verifies the correct software or chip has been loaded on the printed circuit board. This test is specific to System Test 1.

**7,4. Temperature Measurement Verification Test:** Makes a temperature measurement below the IGBT, compares this value to the high and low limit. Checks for overheating.

**6,3. Loading of Parameters:** In System Test 1, loads test parameters for remainder of System Test 1 and 2. In System Test 2, load type specific parameters and set fault memories to zero.

**8,5. Current Measurement Verification Test:** Verifies the current the unit is experiencing to the known current placed on the unit.

**9,6. Verification Test of the Ain1, Ain2, Digital Inputs, Aout, and Relay Outputs:** Tests the functionality of the control board; checks board inputs and outputs.

**10,7. Test of Basic Functions:** Tests the unit under light load and nominal load conditions. Verifies complementary device runs in the right direction, charge relay is energized, line currents are symmetric, and the fan is rotating.

**13,10. Earth Fault Trip Test:** Verifies the complementary device is running and the unit self-protection (earth fault trip) function works correctly. This test is specific to System Test 2.

**11,8. Overvoltage Trip:** Verifies the complementary device is running and the unit self-protection (overvoltage trip) function works correctly. This test is specific to System Test 2.

**12,9. Overcurrent Trip:** Verifies (overcurrent trip) the unit self-protection function works.

**14,X. Loading of Burn In parameters:** Sets test parameters for the next sequence, Burn In. This test is specific to System Test 1.

**X,11. Loading of factory default parameters:** Sets factory default parameters in preparation for use at the customer site. This test is specific to System Test 2.

**X,12. Set Other Parameters:** Sets test date, sets previous faults to zero, and checks the unit ID code. This test is specific to System Test 2.

**15,14. Discharge the intermediate circuit:** Disconnect mains, power supply shuts down.

Upon completing System Test 1 successfully, the device is transferred to a Burn In slot, if the device fails it is transferred to the repair station. The repairperson follows a similar trouble shooting process as outlined above but also checks the online database

to learn what phase of the test the device failed. This can often lead the repairperson to a specific root cause, such as a defective board or loose connection. When the repairperson determines that the problem is resolved, the unit is once again subjected to the Hi Pot test. If the unit passes, it returns to the 'sauna' to resume the test sequence.

The above process is also true for System Test 2, however, if the unit receives a pass after the test, the unit is transferred to the packing and shipping station. If the device fails, it is similarly inspected and re-tested. Each device must receive four consecutive passes before reaching the final production stage, packing and shipping.

Similar to the Hi Pot test, when a unit fails either System Test 1 or 2, the test system records the failure including which phase of the test failed and the measured values for the phase.

#### 3.3.3 Burn In Test Description

The purpose of the Burn In test, as described by The Company, is to identify those components that may fail during the early periods of unit life and thus induce so-called early-life failures. Specifically, this is attempted by running each unit at an elevated temperature so as to induce thermal degrading loads on the unit's circuitry and components. Since, the DUT remains in the sauna after System Test 1 this is relatively easy. Placed between the two System Tests, the Burn In test is conducted within the elevated temperature environment (~45°C) of the sauna.

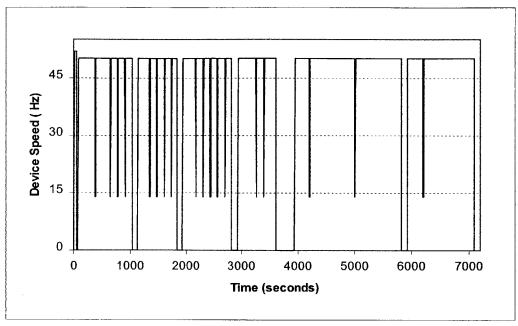

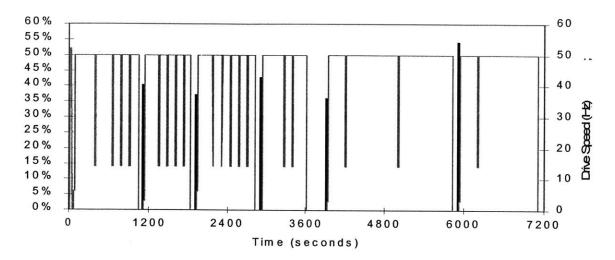

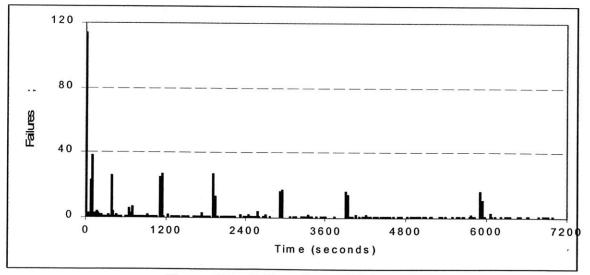

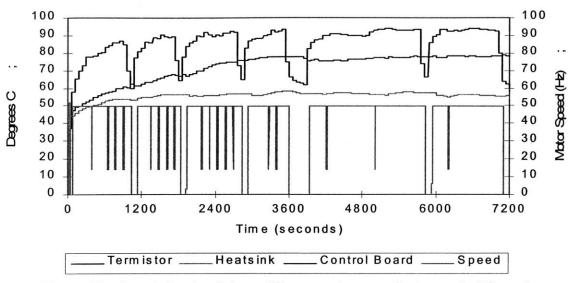

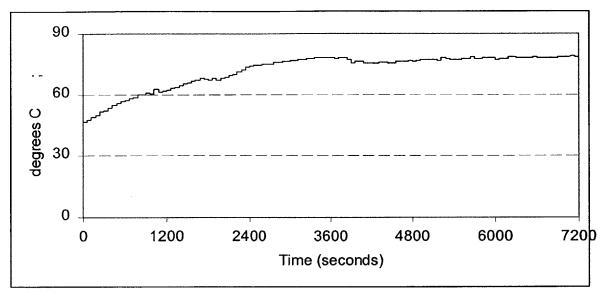

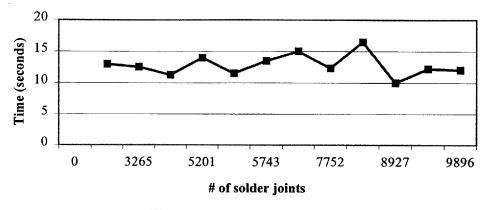

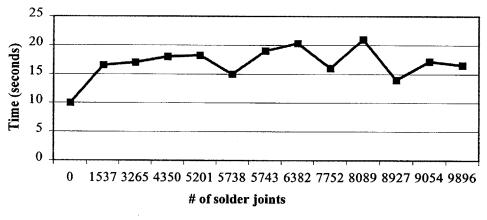

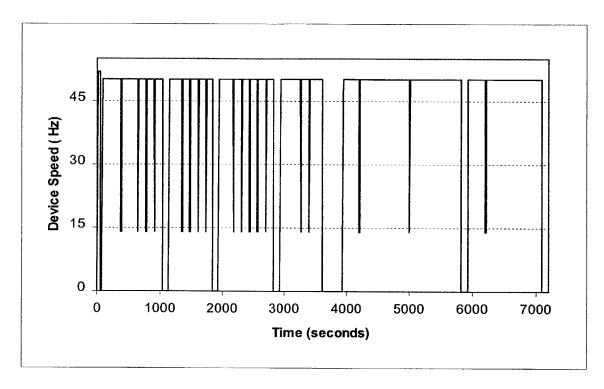

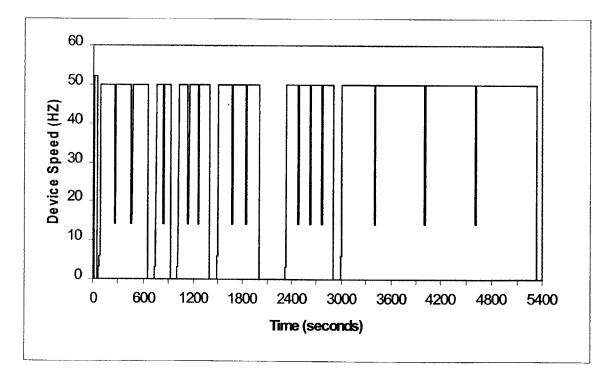

While the test steps performed during the two System Tests are aimed at verifying the unit's functionality and stressing individual components, the purpose of the Burn In test is to operate the device for a set period of time and verify system robustness. While in the sauna the unit will operate with nominal current and through a pre-ordained loading sequence to simulate an actual working environment (see Figure 4). As such, the Burn In test period is significantly different from the other three tests conducted. The Burn In test consists of an automated series of changing complementary device speeds that the unit must command.

Figure 4 – Burn In Test Cycle

If, as in the two System Tests, the unit should fail it will be automatically removed from the sauna and transferred to the repair area. The test database automatically records the time to failure in seconds beginning with zero at test inception. After arriving at the repair station the repairperson will analyze the unit and attempt to diagnose the problem. If the diagnosis is successful the repair will be implemented, a repair code will be assigned based upon the nature of the failure, and the unit will be returned to the product flow. At the same time, the repairperson will manually enter the repair instructions and any other pertinent data into the database. Whether the unit returns to the product flow upstream of Hi Pot or System Test 1 depends upon the nature of the repair and whether it is safe to do so.

In the case where the diagnosis is unsuccessful in identifying the failure mode an "unknown condition" type code will be assigned to the event and the unit will begin the Burn In test again. Ultimately, the unit will pass all tests and then it will be directed to System Test 2 that was described above. To do this, the DUT will be automatically removed from the Burn In slot that it occupied during the Burn In test and transferred to the System Test slot. As identified in Figure 3 there are three slots dedicated to performing the System Tests while there are 24 slots (16 slots for the smaller frame sizes and 8 slots for bigger frame sizes) dedicated for the Burn In operation. The large difference is due to the large disparity in time required for the System Tests versus that

dedicated to the Burn In operation. As the figure shows, each System Test requires approximately six to eight minutes to complete. Similarly, the Burn In operation lasted 120 minutes at project inception.

The pass criterion for the Burn In test is simple, either it fails to operate at the prescribed speeds or not. In the case of failure, "FAILED" is recorded in the database for that sequence and in the acceptable case "PASS" is recorded.

## **Chapter 4 Hi Pot Performance Analysis**

As indicated in previous chapters, each unit is subjected to the four-phase test regime prior to shipment. The 100% test philosophy has established world class levels of reliability and performance in customer applications.

The results from each test phase are stored real-time in the production database and organized in information tables. Using the data from multiple tables, a Microsoft Access query was developed to extract and organize the data in a user-friendly format. The resulting information was transferred to a Microsoft Excel spreadsheet for further manipulation.

As Hi Pot was the first test in the system that was analyzed, it served as the vehicle to become familiar with the databases and to understand what data was available and how it was organized. As the Hi Pot analysis progressed, the findings were used to establish the process with which to analyze the remaining test system. The discussion below describes the trial and error process that was used on the Hi Pot analysis, the identified test time reduction and the method that was established to analyze the remaining test system.

#### 4.1. Failure Analysis

The first study performed on the Hi Pot test was a failure analysis. A failure analysis was considered to be a good indicator of failure trends in the test system. From this data, it was assumed that a relationship would be identified between various levels of production and test performance. The analysis was performed at the daily production level, calculating the number of units that failed the test and the total number of individual units tested. As explained in previous sections, units that fail a test are diagnosed, repaired and returned to the production line. Any unit that fails a test phase must return to the beginning of the test system and be re-tested at each test station. The process repeats until that unit receives concurrent passes at each test phase. The test system tracks the performance of each unit by assigning a sequence number each time a unit is tested at a particular station. Therefore, units may be tested multiple times at each test station and thus the importance of measuring the number of individual units tested as opposed to the total number of tests per day. A query was designed to extract this data. A second query was used to establish the total number of failed tests per day.

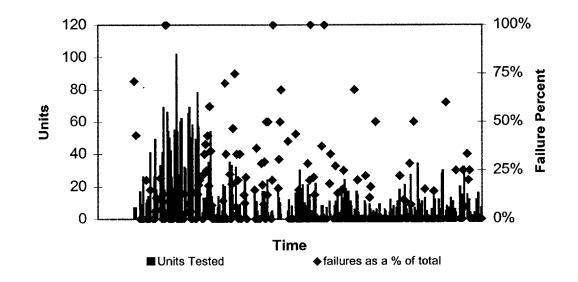

Utilizing the output from the two queries, the daily failure rate was calculated. The failure rate was defined as the number of failed units per number of units tested. The number of units tested and the failure rate were plotted versus day of production. The intent was to identify a trend between the total number of units manufactured and the number of failures. It was expected that a higher failure rate would be seen on days when production was low and lower failure rates seen on days when production was high. An example of this chart is shown in Figure 5 below:

No conclusive relationships were identified from the information. As the chart did not provide the insight intended, it was decided that a scatter plot might be a better format to investigate correlation between units produced and failure rate<sup>4</sup>.

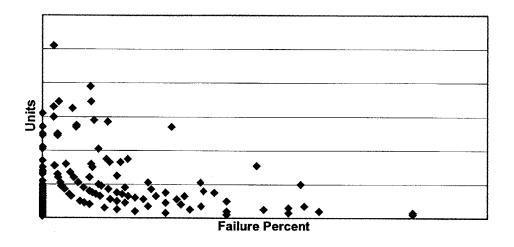

The scatter plot in Figure 6 was created using the same data as depicted in Figure 5. It is apparent that failure rates diminish as the number of units produced increases. However, the data populations also indicate an equal likelihood of low failure rates on high or low production days. After repeating this analysis on all available data at the type series and frame size level, no conclusive relationships were established. The original hypothesis to establish a correlation between production levels and test performance was questioned. In retrospect, the value derived in identifying a correlation would have been for the manufacturing planning process and not for improvements to

the test system. It was decided there was little value in pursuing this type of analysis for the remaining test system and the failure rate analysis was abandoned.

#### Figure 6 - Failure Rates vs. Units Produced

It was learned at this time that the production line under analysis was installed one year prior to this investigation, thus data in the earlier months of production could be skewed due to learning curve effects. After considering all product variations and corresponding time in production, it was determined that future analyses should include data from the present year only. The remaining discussion regarding data analysis will reflect this protocol.

# 4.2. First Pass Yield Analysis

Industry literature indicates when a manufacturing process achieves higher levels of process control and reliability, quality inspection can be reduced, resulting in significant cost savings to the company. First pass yield has been used as technique to justify reduced testing schemes in many industries. In this case, if first pass yield levels demonstrated consistent performance and approached six-sigma levels; perhaps the company could challenge the 100% test philosophy and justify a new methodology based on a significantly reduced sampling level. This redefinition would reduce the load on the existing testing station and simplify the test process. In the future, it would also reduce the level of capital expenditure required for installation of new production lines. It was agreed that this was a potentially beneficial analysis.

As mentioned in the previous section, the test system assigns a sequence number to a unit each time it is tested at a test station. Of specific interest in this case were test results with a sequence number '1' representing the first time each unit was tested at the Hi Pot test station. A query was designed to extract the total number of sequence number 1's per day and the outcome (pass or fail) of the test. A daily first pass yield was calculated and defined as the number of units that received a pass on sequence number 1 divided by the total number of sequence 1's. See Equation 2 below for the formula:

First Pass Yield (FPY) = <u># of Units with a pass on Sequence #1</u> Total number of Sequence #1's

**Equation 2 - First Pass Yield**

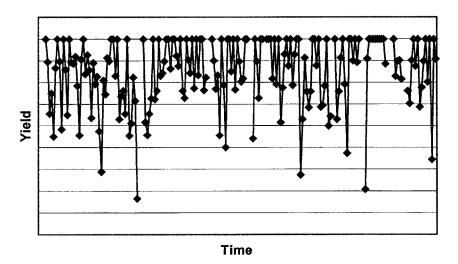

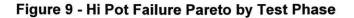

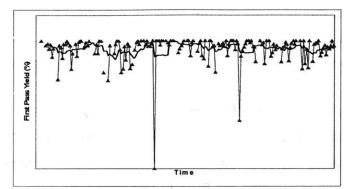

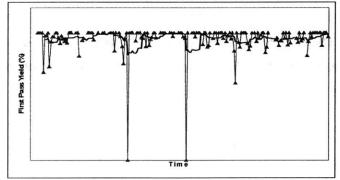

Figure 7 shows the FPY performance over time for all product variations:

This analysis was also conducted at the type series and frame series level. None of the product variations exhibited consistent first pass yield levels or approached sixsigma performance. Using these characteristics as the basis for test reduction, no recommendation could be made to modify the current 100% test philosophy.

Upon discussion of the results with the technical experts, it was discovered that there were two additional considerations that would prohibit future reductions in testing levels. The first consideration was that the Hi Pot test is a regulatory requirement for all products in this industry. Thus, any modifications to the Hi Pot test must continue to

meet the minimum requirements of the regulation. The second consideration was potential risk to downstream operations. It was widely believed that the risk of passing a defective unit to System Test 1, where a unit could potentially explode in the 'sauna', more than justified the test and resultant capital investment. Given these two issues, regulatory requirements and risk level, the technical team decided it was in the company's best interest to maintain the 100% test philosophy for the Hi Pot test, even as test performance consistently achieved six sigma levels of performance.

## 4.3 Pareto Analysis

The final analysis performed on the Hi Pot test was an analysis of failed units. There were two purposes to this analysis. The first was to characterize the modes of failure and correlate the data with field returns. If a relationship were identified between test system failures and field failures, it might be possible to use the on-line test system as a predictor of field performance. On the other hand, if there were no correlation, the test system may need to be re-designed to increase the 'robustness' of the test in an effort to reduce failures in the field. Chapter 7 has been devoted to this analysis.

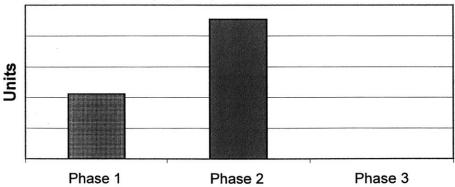

The second purpose of the analysis was to Pareto the failures by test phase. As mentioned in Chapter 3, there were 3 primary phases in the Hi Pot test pattern. When a unit failed the test sequence, the test system recorded the phase of the test pattern that the unit failed. The intent here was to Pareto the modes of failure by test phase. This might better identify the relationship between failure mode and the phase in which the failure occurred.

Figure 8 - Hi Pot Failure Pareto

A query was created to extract this data from the database. In this case all data was pertinent, including units that failed Hi Pot multiple times. Thus sequence number was ignored. Secondly, the query provided the 'test name' data, which made it possible to identify which phase the unit failed. Upon immediate inspection of the data, there were only two failures: A and B. The data was plotted and is shown in Figure 8. Here it is seen that for every "A" failure, there are two "B" failures.

Upon further exploration, the initial finding of the 2:1 relationship of failures between failure mode "A" and "B" was an outcome that was considered normal and not particularly insightful. The next step of the analysis was to sort failures by test phase.

Failure Mode: A(diamond) and B(diagonal)

In Figure 9 above, two pieces of information are revealed. First, it is apparent that the two failure modes correspond directly to a specific test phase, meaning that failure

mode A occurs only in phase 1 and failure mode B occurs only in phase 2. Secondly, failures occur in phases 1 and 2, but not phase 3. As previously described in Chapter 3, phase 3 verifies that phase 2 has not compromised the integrity of the unit and is identical test to phase 1. As there are no failures in phase 3, it is evident that phase 2 does not disturb the operation of the unit. A case could be made that phase 3 is redundant and can be removed from the test pattern. Removing the test phase reduces test time by 30% and simultaneously simplifies the test pattern, minimizes test complexity and ultimately reduces database storage requirements. This was thought to be a highly attractive justification for eliminating the test phase. However, this was ultimately rejected. The technical experts determined that reducing the Hi Pot test by a factor of seconds was not a value-added use of their software resources.

# 4.4 Summary of Results

Two data analysis techniques were identified in this analysis. The first pass yield technique was thought to be beneficial in challenging the 100% test philosophy. Although the Hi Pot test was not currently performing at six-sigma levels and other external factors prevented a reduction in testing levels, first pass yield was identified as a leading indicator for challenging the 100% test philosophy in the remaining test system. The second technique identified was the phase Pareto analysis. Utilizing this technique, the value of each test phase is evaluated. From this analysis, it is clear that this technique can aid in determining unnecessary or redundant test phases. Again, this technique can be applied throughout the test system and across product lines.

Although no significant benefits were achieved from the Hi Pot analysis, the technical team embraced the new data analysis techniques. More importantly, the analysis completed here served as the test subject for the project and the learning's were applied to the remaining test system analysis.

41

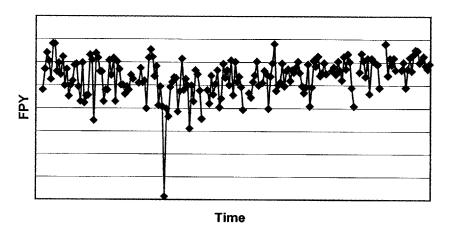

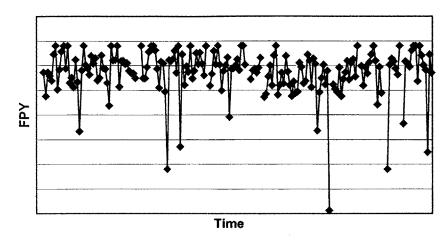

# Chapter 5. System Tests 1 and 2 Performance Analysis

As discussed in Chapter 3, the purpose of the System Test is to ensure the unit operates as designed. The actual test pattern differences between the System Test 1 (T1) and System Test 2 (T2) are minimal. The primary difference being that T2 operates the device immediately after the Burn In phase, while the device is warm, in an attempt to screen thermally induced failures. Consequently, as the T1 analysis progressed, the similarity of the System Tests became an increasingly valuable factor. So much so, that the analysis evolved into a simultaneous study of T1 and T2 performance. Acknowledging the interdependence of the analysis demands that the subsequent discussion be addressed concurrently, rather than addressing each test independently.