### Secure Application Partitioning for Intellectual Property Protection

by

Charles W. O'Donnell

B.S. in Computer Engineering, Columbia University in the City of New York, 2003

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Master of Science in Electrical Engineering and Computer Science

at the

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

© Massachusetts Institute of Technology 2005. All rights reserved.

Author ..... Department of Electrical Engineering and Computer Science August 26, 2005 1 Certified by..... Srinivas Devadas Professor of Electrical Engineering and Computer Science Thesis Supervisor Accepted by ..... 1 Arthur C. Smith Chairman, Department Committee on Graduate Students MASSACHUSETTS INSTITUTE OF TECHNOLOGY BARKER MAR 2 8 2006 LIBRARIES

.

#### Secure Application Partitioning for Intellectual Property Protection

bv

Charles W. O'Donnell

Submitted to the Department of Electrical Engineering and Computer Science on August 26, 2005, in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering and Computer Science

#### Abstract

Intellectual property protection is a major concern for both hardware and software architects today. Recently secure platforms have been proposed to protect the privacy of application code and enforce that an application can only be run or accessed by authorized hosts. Unfortunately, these capabilities incur a sizeable performance overhead. Partitioning an application into secure and insecure regions can help diminish overheads but invalidates guarantees of privacy and access control.

This work examines the problem of securely partitioning an application into public and private regions so that private code confidentiality is guaranteed and only authorized hosts can execute the application. This problem must be framed within the context of whole application execution for any solution to have meaning, which is a critical point when evaluating software security. The adversarial model presented balances practical generality with concrete security guarantees, and it is shown that under this model the best attack possible is a "Memoization Attack." A practical Memoization Attack is implemented, and experimentation reveals that naive partitioning strategies can expose the functionality of hidden code in real applications, allowing unauthorized execution. To protect against such an attack, a set of indicators are presented that enable an application designer to identify these insecure applications to partition an application in a manner that protects the privacy of intellectual property and prohibits unauthorized execution.

Thesis Supervisor: Srinivas Devadas

Title: Professor of Electrical Engineering and Computer Science

#### Acknowledgements

I would like to thank Srini for encouraging me to pursue whatever ideas I find interesting, for his inexhaustible energy, and for his suggestions which led to this thesis topic. I would like to thank Ed for being an outstanding mentor and for his considerable help in much of my work, including help in giving this thesis direction. I would like to thank Marten for suffering through many hours of theoretical musings concerning the nature of this unwieldy problem. I would also like to thank Dan and Blaise for their useful comments during the writing of this text. I would especially like to thank all of my labmates who consistently remind me that its my peers who teach me the most, including Ed, Daihyun, Prahbat, Ian, Nirav, Michael, Karen, Dan, Dave, Dwaine, Blaise, Jae, Albert, Bill, Chris, Mike, and Rob. I would love to thank Adrienne for her fine editorial skills, and for keeping me company at the beach and ever since. Finally, I would like to thank my parents and family, who played the greatest role in my accomplishments (and existence).

## Contents

| 1 | Intr       | ou dou ou o | <b>13</b> |

|---|------------|----------------------------------------------|-----------|

|   | 1.1        | Existing Solutions                           | 14        |

|   | 1.2        | T di titioning                               | 14        |

|   | 1.3        | Goals of Work                                | 15        |

|   | 1.4        | Organization                                 | 15        |

| 2 | Prie       | or Work                                      | 17        |

|   | 2.1        | Software Secrecy                             | 17        |

|   | <b>2.2</b> | boltmare r nacy                              | 18        |

|   | 2.3        | i logiani i al tritoling.                    | 19        |

|   | 2.4        | Application Complexity                       | 20        |

| 3 | Mo         | leling an Attack                             | <b>21</b> |

|   | 3.1        | Application Operation Equivalence            | 21        |

|   | 3.2        | System Model                                 | 23        |

|   |            | 3.2.1 Secure Coprocessors                    | 23        |

|   |            | 3.2.2 AEGIS                                  | 25        |

|   | <b>3.3</b> | Adversarial Knowledge                        | 27        |

|   |            | 3.3.1 Input/Output Relations                 | 27        |

|   |            | 3.3.2 Obtaining Input/Output Pairs           | 28        |

|   | 3.4        | Monitor & Swap Attack                        | 30        |

| 4 | Adv        | ersarial Capabilities                        | 33        |

|   | 4.1        | Definitions                                  | 33        |

|   | 4.2        | Success Probability                          | 35        |

|   |            | 4.2.1 Trial Success $P_{call}$               | 35        |

|   |            | 4.2.2 Memoization                            | 36        |

| 5 | Imp        | lementing a Memoization Attack               | 39        |

|   | 5.1        |                                              | 39        |

|   | 5.2        |                                              | 41        |

|   |            | 5.2.1 System Setup                           | 42        |

|   |            |                                              | 43        |

|   |            | 5.2.3 Partially Repeated Workloads           | 46        |

|   |            | 5.2.4 Composite Workloads                    | 48        |

|   | 5.3        |                                              | 49        |

|   |            | 5.3.1 Read Value Distance                    | 50        |

|   |            | 5.3.2 Address Path History                   | 50        |

| 6 | Ind | icators of Insecurity 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 6.1 | Empirical Correlations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | 6.2 | Input Saturation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   |     | 6.2.1 Individual Input Counting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |     | 6.2.2 Real-World Saturation Rates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   | 6.3 | Data Egress                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   |     | 6.3.1 Output Counting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   |     | 6.3.2 Real-World Output Egress Weights and Counts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   | 6.4 | Application Designer Use of Indicators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | -   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 7 |     | titioning Methodologies 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   | 7.1 | Essential Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   |     | 7.1.1 Call Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   |     | 7.1.2 Input Data Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   |     | 7.1.3 Call Tree Location                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   | 7.2 | Weighted DFG/CFG Bisection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   |     | 7.2.1 Graph Construction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   |     | 7.2.2 Bisection Metric                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 8 | Cor | clusions 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| U | 8.1 | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   | 8.2 | Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   | 0.2 | 8.2.1 Private Libraries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   |     | 8.2.2 Versioning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   |     | 8.2.3 Probabilistic Application Operation Equivalence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   |     | 8.2.4 Input Selection for Active Adversaries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   | 8.3 | terrent in the second sec |

|   | 0.0 | Final Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

# List of Figures

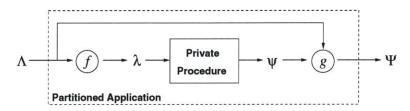

| 3 - 1 | Partitioned application inputs and outputs                                | 2 |

|-------|---------------------------------------------------------------------------|---|

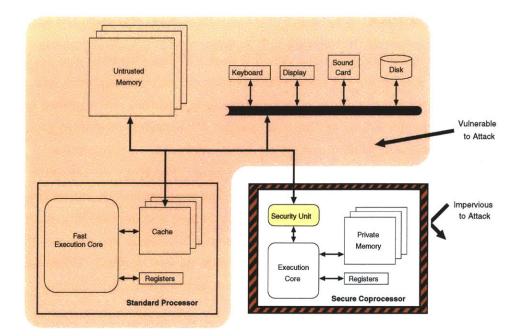

| 3-2   | Secure coprocessor model                                                  | 4 |

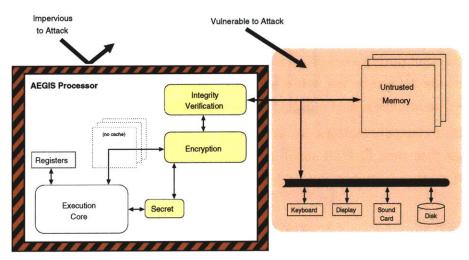

| 3-3   | AEGIS processor model                                                     | 5 |

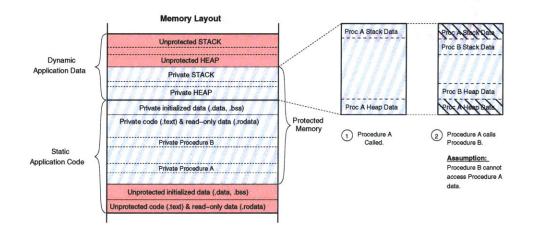

| 3-4   | AEGIS memory layout of application                                        | 6 |

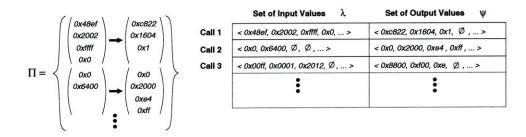

| 3-5   | Set of input/output relationship pairs $\Pi$                              | 7 |

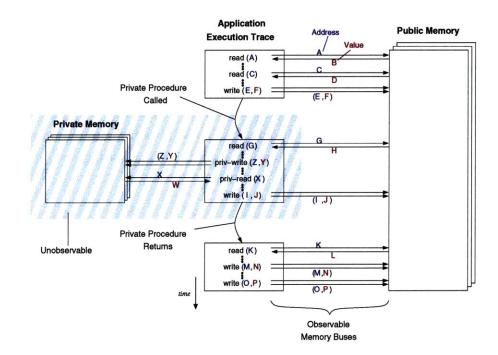

| 3-6   | Observing inputs & outputs with a secure coprocessor                      | 8 |

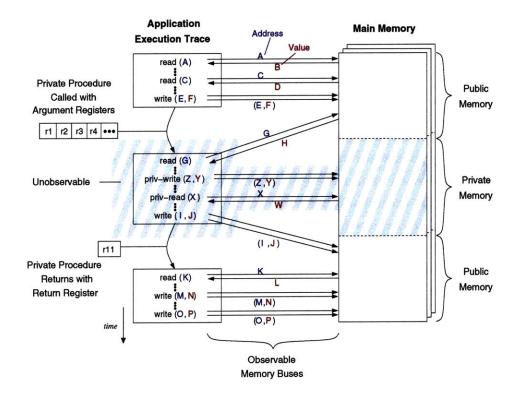

| 3-7   | Observing inputs & outputs with AEGIS                                     | 9 |

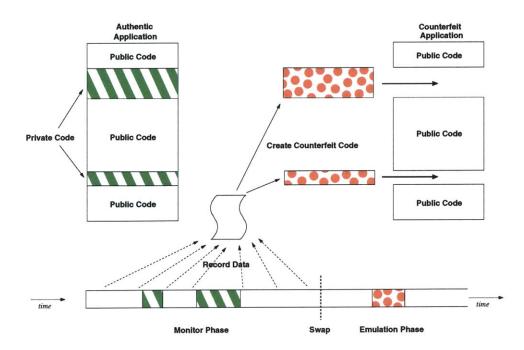

| 3-8   | Monitor & Swap Attack                                                     | 1 |

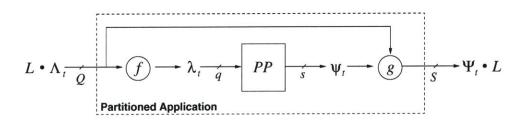

| 4-1   | Partitioned application attack model                                      | 3 |

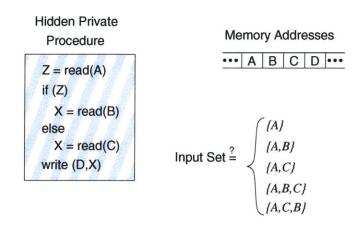

| 5-1   | Uncertainty of inputs on private procedure call                           |   |

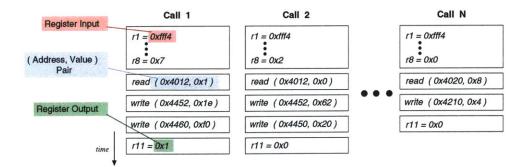

| 5-2   | Basic private procedure interaction table $\Xi$                           |   |

| 5-3   | General methodology for emulation using Temporal Memoization 4            |   |

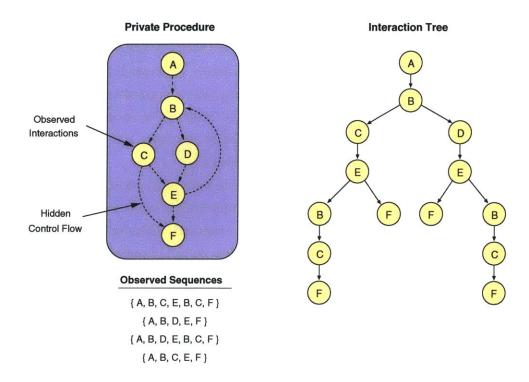

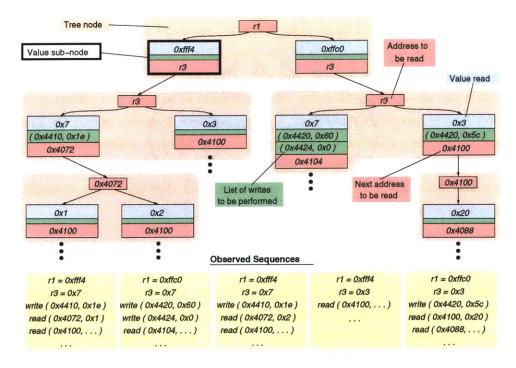

| 5-4   | Hidden control flow graph represented by a tree                           |   |

| 5 - 5 | Interaction tree for Temporal Memoization                                 |   |

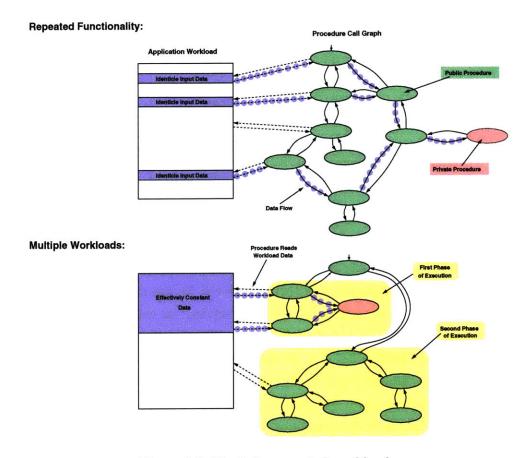

| 5-6   | Partially repeated workloads                                              |   |

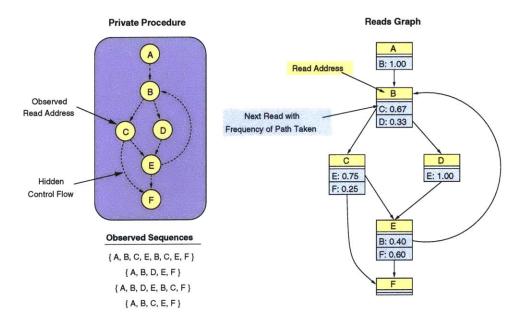

| 5-7   | Reads Graph attempting to match hidden control flow graph                 | 1 |

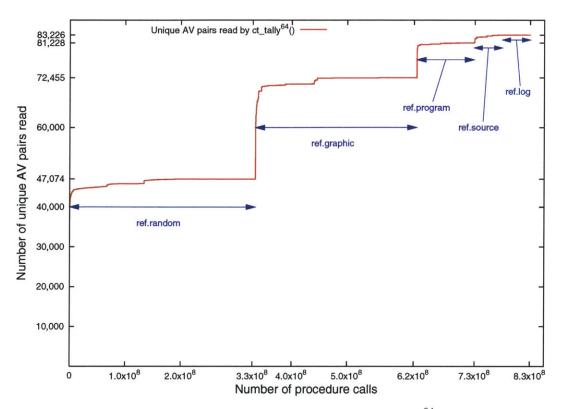

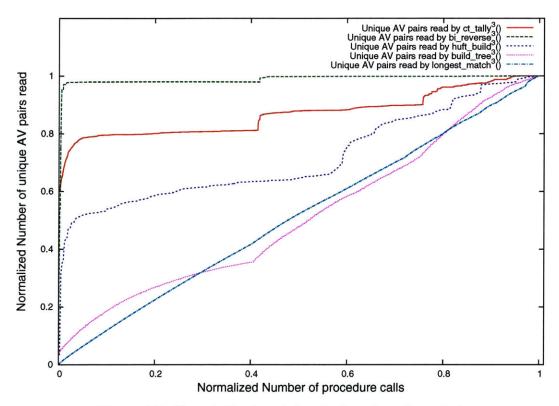

| 6-1   | Cumulative input density function of $ct_tally^{64}$ () from <i>Gzip.</i> |   |

| 6-2   | Cumulative input density functions from <i>Gzip.</i>                      |   |

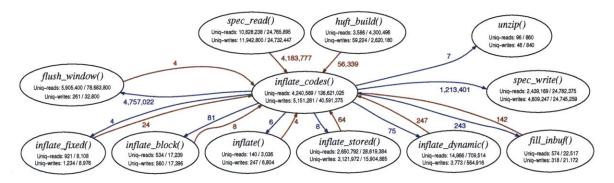

| 6-3   | Unique outputs of the inflate_codes() procedure in <i>Gzip</i> 6          | 1 |

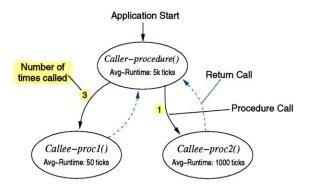

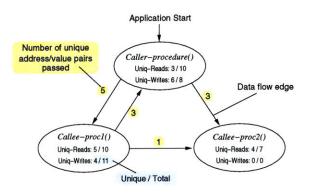

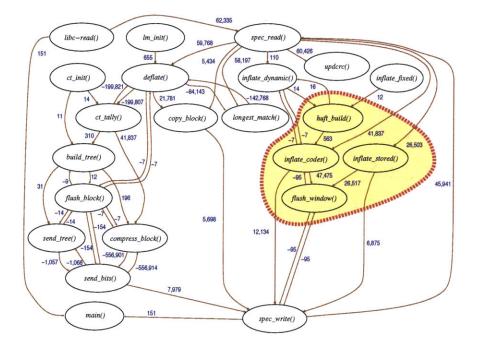

| 7-1   | Weighted Control Flow Graph (W-CFG)                                       |   |

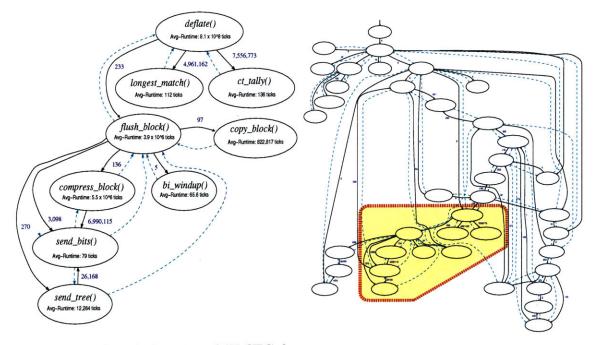

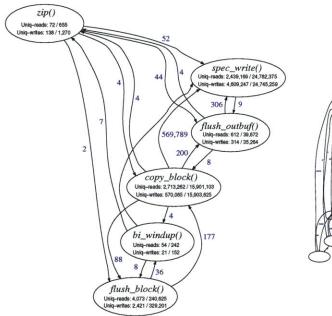

| 7 - 2 | Magnified region of W-CFG for <i>Gzip</i>                                 |   |

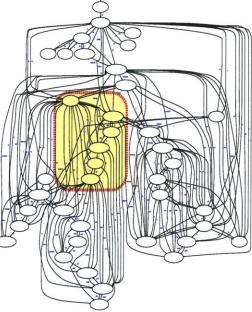

| 7-3   | Entire W-CFG for <i>Gzip</i>                                              |   |

| 7-4   | Weighted Data Flow Graph (W-DFG)                                          |   |

| 7-5   | Magnified region of W-DFG for <i>Gzip</i>                                 |   |

| 7-6   | Entire W-DFG for <i>Gzip</i>                                              |   |

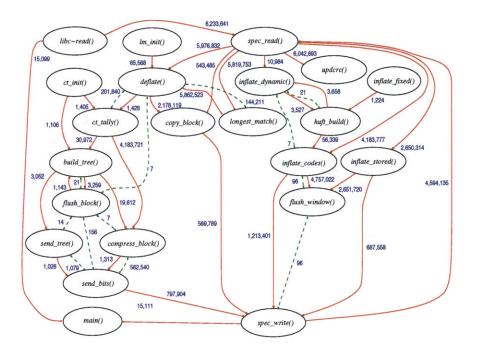

| 7-7   | Combination of W-DFG and W-CFG for 22 procedures in <i>Gzip.</i> 7        |   |

| 7-8   | Gzip combined graph $G$ with public/private bisection                     | 2 |

# List of Tables

| 5.1 | Interaction table used in this implementation of Temporal Memoization | 45 |

|-----|-----------------------------------------------------------------------|----|

| 5.2 | Size of memoized private procedures                                   | 48 |

| 5.3 | Success of Temporal Memoization Attack on real applications           | 49 |

| 6.1 | Rate of input saturation for five <i>Gzip</i> procedures              | 57 |

| 6.2 | Output egress weights and counts for six <i>Gzip</i> procedures       | 62 |

### Chapter 1

## Introduction

With the increasing interconnectivity of computing devices worldwide, system and application security has become a first order concern for both hardware and software architects. One chief worry for these designers is the guarantee that their product will be used in its original and intended fashion.

This concern can be broken into three major considerations. First, software inventors may want to protect the intellectual effort that went into the making of an application. That is, the secrecy of their Intellectual Property (IP) must be maintained even after an application has been distributed throughout the world. Second, designers commonly desire control over who can use their application and who cannot. This is broadly referred to as software piracy prevention or software licensing. Third, benevolent inventors do not want their application to be used maliciously, which may decrease the productivity of their application and others. The ability of an application to withstand malicious attacks which intend to modify the functionality of software is often referred to as application tamperresistance.

These desires stem from a number of motives, including a designer's altruistic intentions, as well as his capitalistic disposition and financial dependencies. Software businesses must adhere to economic models that allow developers to actually get paid for their work. More often than not, this requires individuals or organizations to purchase the rights to use an application. Without control over who can use an application and who cannot, there is no consumer incentive to purchase the rights to use an application. Similarly, without the protection of intellectual property, organizations can circumvent the required purchase by developing their own copy of an application based on IP found in the original application. Finally, preventing malicious attack is not only a generally agreed "good idea," but also saves businesses large amounts of money that can be lost through patch distribution and decline in consumer confidence.

#### 1.1 Existing Solutions

Although countless techniques and architectures have been proposed to tackle one or all of these points we find it prudent to only focus on physically secure solutions. These solutions make software protection guarantees against even the most motivated adversaries who can prod and poke the actual hardware components of a computing system [23, 31, 43]. Most commonly, software applications are executed on personally owned and operated computing systems. When it comes to issues of IP, licensing, and tamper-resistance, it would be naive for application designers to expect full cooperation from the owners of the systems that run the application. Since these owners have physical access to their system, an application inventor cannot expect any strong security assurances unless the system is based on a physically secure architecture. We chose the AEGIS physically secure architecture [50] as the focus of our work, however other architectures exist that offer similar physical security promises [35].

The AEGIS architecture protects intellectual property privacy and secures software licensing through application code encryption. Every AEGIS processor contains a unique secret which can be used to decrypt encrypted applications on the fly, without revealing the true application code to anyone. For example, each processor may contain a private symmetric encryption key which can be shared with a software designer. The designer can then encrypt his entire application with one processor's key, and make the encrypted application publicly available. The AEGIS architecture guarantees that only that single processor will be able to execute the encrypted application. The architecture also contains integrity verification techniques that provide application tamper-resistance. More details on how AEGIS processors work can be found in [67, 68].

If one is agreeable to a licensing scheme that ties an application to a physical processor, the AEGIS architecture appears to satisfy the three major concerns described. However, the architecture cannot offer these encryption and integrity verification mechanisms without a cost. There is a performance overhead for any application that uses these mechanisms (that is, an application operating in a secure mode). Further, requiring an application to be encrypted *as a whole* can be restrictive for designers, prohibiting the use of shared libraries, amongst other things.

#### 1.2 Partitioning

The AEGIS architecture remedies these failings by allowing small, disconnected portions of an application to execute in a secure mode, while the remaining regions execute in an unencrypted, insecure mode. Allowing an application to switch between these modes during operation leads to an interesting design problem. Tamper-resistance can only be assured for the secure regions of the application. Application code encryption exists for these same small regions, however it is unclear if the same IP privacy assumptions hold. Finally, the licensing scheme used by AEGIS is intended to bind an application to a processor, but a partitioned application really only binds secure regions of an application to a processor. Therefore, a designer's problem is how to partition an application into secure and insecure regions so as to maximize performance while still maintaining tamper-resistance, IP privacy, and license protection. Ultimately, the designer would like to ensure that no one can recreate his application through dissection of his code, that only authorized consumers can use his application, and that it is impossible to modify the way that his application runs for malicious purposes.

#### 1.3 Goals of Work

This work takes a look at what properties are required of a partitioned application to ensure the secrecy of small regions of application code, and to prevent application execution by unauthorized parties. Importantly, these properties focus on the relationship between the partitioned regions of code and the application as a whole, since this is what matters for an actual attack. The specific contents of a partitioned region is independently of little consequence.

Specifically, we analyze one type of attack, given a general but manageable adversarial model, and put forth one practical attack implementation. We then propose metrics that can be used to identify whether a partitioned region of application code can be considered private even in the face of attack. This is not at all clear since, as we show, it is possible to determine the functionality of application code within a small hidden region simply from its interaction with the rest of the application. We also discuss the issue of license protection for partitioned applications and propose a simple bisection rule which ensures that a partitioned application can still be bound to a single processor.

Tamper-resistance guarantees are outside the scope of this work. Most of the physically secure architectures mentioned already focus on this problem extensively. These architectures formulate quite strong security assurances that can be combined with other work related to information flow to ensure tamper-resistance of partitioned applications.

#### 1.4 Organization

This thesis is structured as follows. Chapter 2 begins with a review of previous techniques that were used to ensure application code privacy and to prevent unauthorized execution.

Chapter 3 introduces the adversarial model that is the basis for our investigation, identifying an adversary who is able to observe the input/output relationship of a hidden region of code. Chapter 4 formally discusses the limitations of any such adversary, and Chapter 5 describes the implementation of an attack that is able to create operation equivalent regions of hidden application code. This implementation requires a number of optimizations, but is able to successfully duplicate the functionality of real-world applications.

To defend against such an attack, Chapter 6 presents a number of tests which an application designer can use to identify vulnerabilities in his partitioned application. Further, Chapter 7 describes the important factors that must be taken into account when an application designer partitions his application, and suggests one simple partitioning scheme. We conclude in Chapter 8.

### Chapter 2

## **Prior Work**

Intellectual property protection and software licensing has persisted as an open problem in computer science for decades. Application designers have implemented countless mechanisms that attempt to hide the functionality of instruction code and ensure that only authorized users can execute the application in question.

#### 2.1 Software Secrecy

Gosler [9] was one of the first to examine the problem of software secrecy and the possibility of modifying application code to specifically prevent an adversary from determining its contents. In his work he discussed some of the capabilities of adversaries of his era and suggested a set of goals for software protection. Later studies [12, 13, 15, 41] found that simple techniques can be used by an adversary to decipher the contents of hidden applications. To offer such protection of intellectual property privacy, some have proposed methods of "obfuscating" an original application in ways to create an executable binary that is sufficiently incomprehensible, but still functionally equivalent to the original. Collberg et. al. [24, 39] present an in-depth discussion on obfuscation transforms which can be applied to any given block of application code. These transformations are implemented in their code obfuscating compiler, "Kava". Obfuscation can increase the difficulty of an adversary to discover the contents of obfuscation code, but also can increase the execute time required to run such regions of code.

Unfortunately, a theoretical treatment of the obfuscation problem by Barak et. al. [37] proved that cryptographically secure obfuscation is impossible for a large family of functions. Recently, Lynn et. al. [56] and Wee [69] have presented positive results which show that some functions can be obfuscated in a cryptographically sound manner. However, the family of functions discussed are too restrictive to be useful for general application protection. Along a similar vain, Sander and Tschudin [29, 28] suggested a protocol which uses homomorphic encryption schemes to allow an executing algorithm to conceal the values being computed while still performing its intended operation. Sadly, this work is again limited to only a small class of functions.

Alternatively, a cryptographically secure means of protecting the intellectual property privacy of a region of application code is to simply encrypt the application instructions themselves. The decryption and execution of the encrypted instructions is then left up to some trusted source. One of the first to suggest this idea was Kent [2] who identified a physically shielded processor as a trust base. Physical security is important since a motivated adversary could easily intercept decrypted machine instructions if a softwareonly encryption technique is used. Many others [6, 7, 21] have suggested similar solutions. Methods for secure software distribution has also been examined by Herzberg et. al. [11] and Wilhelm [26]. Although these techniques involve encrypted application code and a trusted computing system, they do not satisfactorily detail how to design a physically secure trust base.

More recent architectures, such as XOM [35, 48, 49] and AEGIS [50, 67, 68], remedy this by reducing the size of the trusted base to a single chip and introducing architectural mechanisms that protect the integrity and privacy of off-chip memory. With this, the XOM architecture and AEGIS processor allows applications to be encrypted and executed in a physically secure manner. These architectures follow a similar line of thinking as other recent works that propose specialized hardware modifications for security purposes [25, 30, 52, 70].

Even though these systems encrypt the contents of application code during execution, it is still possible for an adversary to discover the contents of the application code through its use of memory addresses. Address obfuscation [10, 22] is one method which defends against such a discovery. Address obfuscation applies a set of transformations to application code regions that hinder an adversary's abilities to reconstruct the contents of hidden code. An alternative approach is to simply design the application in a way so that no application information is leaked. Agat [33] has suggested a few methods which remove the specific problem of timing leaks. Zhuang et. al. have also suggested additional hardware mechanisms that help protect against leakage [58].

#### 2.2 Software Piracy

There have also been a large number of techniques proposed to handle software licensing. Watermarking, renewability, online-verification, encryption, and authentication have all been suggested to prevent application execution by unauthorized parties. In general, there are only two tactics employed to prevent software piracy, application alteration and execution protection.

Watermarking, renewability, and online-verification all fall under application alteration.

Watermarking [38, 39] is a technique that affixes an indelible signature to an application which uniquely identifies that application, even after an adversary attempts to mutate a duplicated version. This tactic then relies on legal action to thwart an adversary's attempts to use the application in an unauthorized manner. The concept of renewability [40] effectively creates an application expiration date and online-verification [60] requires an application to contact a remote server to run correctly. An idea similar to online-verification is that of a "dongle," [63] which is an individual hardware element that contains some secret and is externally attached to a computing system. During execution of a protected application, special calls are made which require that the dongle be attached to the system.

One of the fundamental problems with application alteration techniques is that they add extra, otherwise useless content to the application code. Consequently, although it may be extremely difficult, it is almost always possible for a motivated adversary to remove this extra code.

Execution protection looks to guarantee that a certain application can only *execute* on a particular computing system. This requires a specialized architecture which is able to execute an encrypted application, or authenticate the integrity of an application using some secret. The XOM architecture [35, 48], the AEGIS processor [68] are both examples of such specialized architectures. In most cases, execution protection is guaranteed by a check made to identify the contents of an application and determine if the application is authorized to run on that particular system and operating system. These architectures also allow application code to be encrypted such that only one particular system can use its secret to decrypt and run the application. TPM from TCG [55], SP-processors [61], and Next Generation Secure Computing Base (NGSCB) from Microsoft [46, 64] are other architectures that add specialized hardware to guarantee the authenticity of applications under execution, however they do not offer the same privacy guarantees as XOM or AEGIS.

#### 2.3 Program Partitioning

The act of partitioning an application for security reasons is not a new approach. Although, to our knowledge, there has not been any work that considered application operation as a whole when analyzing both intellectual property protection and software licensing. Yee [20] discussed the possibility of partitioning applications for copy protection, but did not analyze this problem in depth. White and Comerford [14] developed the ABYSS architecture which allows for secure software partitioning, but only offer a high-level discussion of possible characteristics that can impact the security of a partitioned application. Zhang et. al. [53] suggest program slicing as a means to prevent software piracy but mainly focus on compiler modifications to enable secure partitioning. Their work focuses on efficient transformations that determine how to partition an application which best prevents software piracy. To

do this they analyze the contents of candidate partitioned regions and do not consider the possibility that privacy may not be guaranteed. Our work investigates the problem of privacy protection in general, using a model that looks at application protection as whole and treats partitioned regions of code as "black-boxes." A couple sources indicate that the company "Netquartz" [65] also works on similar techniques, but it is difficult to obtain information explaining their exact technology. Most of the remaining work related to application partitioning examines the protection of program user data and the protection of information flow.

"Privtrans" is a tool created by Brumley and Song [54] that automatically separates program source code into two executables, a monitor and a slave. The monitoring code operates within a secure computing environment (a secure execution mode), while the bulk of the application is designated as slave code and is permitted to do whatever it desires. The monitoring code exists to periodically perform checks on the slave code to ensure that it is behaving honorably.

"Secure program partitioning" has been presented by Zdancewic et al. [45] as a languagelevel technique to protect data privacy. Their work focuses on compiling a single program to run in a distributed computational environment, while still enforcing confidentiality policies on information flow. To this extent, secure program partitioning focuses on guaranteeing end-to-end information flow security.

Finally, a number of architectures *allow* an application to be partitioned [14, 35, 68], but make no guarantees of protecting the privacy of data flowing between partitions. In this regard, information flow techniques offer a more comprehensive solution.

#### 2.4 Application Complexity