## Low Phase Noise, High Bandwidth Frequency Synthesis Techniques

by

Scott Edward Meninger

Bachelor of Science in Electrical Engineering and Computer Science Boston University, June 1996 Master of Science in Electrical Engineering and Computer Science Massachusetts Institute of Technology, June 1999

Submitted to the Department of Electrical Engineering and Computer Science

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

at the

### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

May 2005

© Massachusetts Institute of Technology 2005. All rights reserved.

Author ...... Department of Electrical Engineering and Computer Science May 12, 2005

Certified by...

Michael H. Perrott Assistant Professor Thesis Supervisor

Chairman, Department Committee on Graduate Students

BARKER

| M | ASSACHUSETTS INSTITUT<br>OF TECHNOLOGY | ΓE. |

|---|----------------------------------------|-----|

|   | OCT 2 1 2005                           |     |

|   | LIBRARIES                              |     |

## Low Phase Noise, High Bandwidth Frequency Synthesis

#### Techniques

by

### Scott Edward Meninger

Submitted to the Department of Electrical Engineering and Computer Science on May 12, 2005, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

#### Abstract

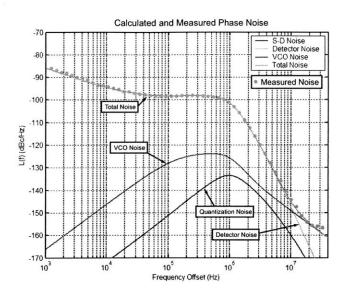

A quantization noise reduction technique is proposed that allows fractional-N frequency synthesizers to achieve high closed loop bandwidth and low output phase noise simultaneously. Quantization induced phase noise is the bottleneck in state-ofthe-art synthesizer design, and results in a noise-bandwidth tradeoff that typically limits closed loop synthesizer bandwidths to be <100kHz for adequate phase noise performance to be achieved. Using the proposed technique, quantization noise is reduced to the point where intrinsic noise sources (VCO, charge-pump, reference and PFD noise) ultimately limit noise performance.

An analytical model that draws an analogy between fractional-N frequency synthesizers and MASH  $\Sigma\Delta$  digital-to-analog converters is proposed. Calculated performance of a synthesizer implementing the proposed quantization noise reduction techniques shows excellent agreement with simulation results of a behavioral model. Behavioral modeling techniques that progressively incorporate non-ideal circuit behavior based on SPICE level simulations are proposed.

The critical circuits used to build the proposed synthesizer are presented. These include a divider retiming circuit that avoids meta-stability related to synchronizing an asynchronous signal, a timing mismatch compensation block used by a dual divider path PFD, and a unit element current source design for reduced output phase noise.

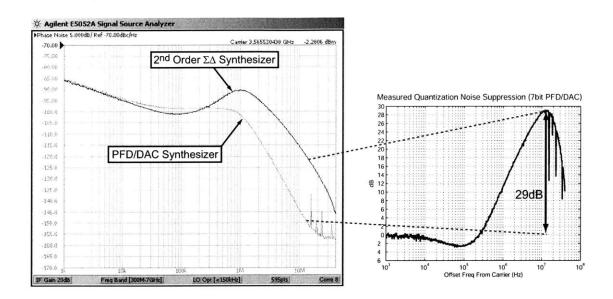

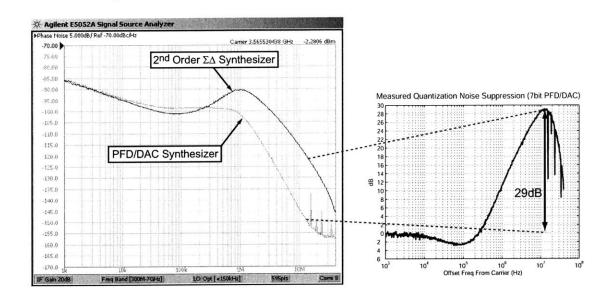

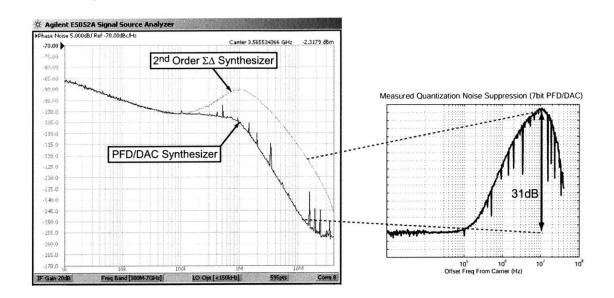

Measurement results of a prototype  $0.18\mu m$  CMOS synthesizer show that quantization noise is suppressed by 29dB when the proposed synthesizer architecture is compared to  $2^{nd}$  order  $\Sigma\Delta$  frequency synthesizer. The 1MHz closed loop bandwidth allows the synthesizer to be modulated by up to 1Mb/s GMSK data for use as a transmitter with 1.8GHz and 900MHz outputs. The analytical model is used to back extract on-chip mismatch parameters that are not directly measurable. This represents a new analysis technique that is useful in the characterization of fractional-N frequency synthesizers.

Thesis Supervisor: Michael H. Perrott Title: Assistant Professor This thesis is dedicated to the example and inspiration of my parents, Donald T. and Mary J. Meninger. Dad, I miss you every day. You will always be my best man.

"While I'm still confused and uncertain, it's on a much higher plane, d'you see, and at least I know I'm bewildered about the really fundamental and important facts of the universe." Treatle nodded. "I hadn't looked at it like that," he said, "But you're absolutely right. He's really pushed back the boundaries of ignorance".

They both savored the strange warm glow of being much more ignorant than ordinary people, who were only ignorant of ordinary things.

- Terry Pratchett, Equal Rites

### Acknowledgments

"Give a man a fire and he's warm for a day, but set fire to him and he's warm for the rest of his life."

#### - Terry Pratchett, Jingo

In many ways, the grad school experience is like being set on fire. There's an initial burst of enthusiasm after which you feel like you're running around desperately asking people to put you out. After various periods of flaming up, someone dumps a bucket of water on you, and you wind up feeling a bit burnt out, but happy that the pain has stopped. And along the way you've learned a few valuable lessons....

....Of course, another way of looking at it is that grad school is in no way like being lit on fire. In fact, one could argue that grad school is the exact opposite of being lit on fire. And one thing you definitely learn in grad school is to be very, very careful about general statements and assumptions, so I'll just say that grad school is very much like being lit on fire, while in no way like being lit on fire.

So, on to more important matters ...

There are countless numbers of people to thank for the help, influence, and inspiration they have given me over the course of my PhD experience. In advance, I apologize if anyone is not included in this acknowledgment section who should be.

I'd like to start by thanking my thesis advisor Professor Mike Perrott. Mike has been a constant motivating force and positive influence on the work that is presented in this thesis. I have learned a phenomenal amount over the last four years, and owe much of my education to Mike's personal tutelage.

I owe my committee, Professors Anantha Chandrakasan and Jacob White a debt of gratitude for taking the time to meet with me during the course of this work, and for reading this thesis. I would not have made it through the PhD experience without the help and support of numerous grad students working in MTL. They have aided me technically, as well as in the more important aspect of having some fun. Anh Pham, John Fiorenza, Nisha Checka, Albert Jerng, Andrew Chen, Mark Spaeth, and Tod Sepke all were sources of good technical discussions as well as good guys to grab a beer or go ski with. Tod also was very helpful (and patient) in helping me get a handle on noise processes and simulation.

The members of the High Speed Circuits and Systems Group have coped with my .... personality over the last four years, and so I owe them a huge debt of gratitude. Ethan Crain has been a great lab-mate to design with and work out with. Assuming I'm not trying to keep up with him running, that is. I'm not sure who owes who a beer at this point, but I look forward to being able to enjoy one with him in a more relaxed setting soon. Charlotte Lau has borne the brunt of what will be referred to as my "humor". Her patience and help (and lack of litigation to this point), are much appreciated. I'll miss our trips to ABP for lunch, and the recognition that comes with walking around with the queen of MIT. Belal Helal and I have had far too many late night discussions that have increased our graduation dates as well as our understanding. Belal's thoroughness has been an example. Matt Park is responsible for the excellent work on the data-weighted averager circuit used by my test chip. There are not many undergrads who I would trust with my something going into my thesis chip, but Matt was a clear exception. I'm looking forward to seeing the work he'll produce in the future. I also owe thanks to Min Park, Chun-Ming Hsu, Shawn Kuo, and Muyi Ogunnika, who have helped me out in numerous ways over the last four years.

Our group administrators, Rosa Fuentes and Valerie DiNardo, have been a great help getting the lab set up and putting through my very disorganized reimbursements.

The MTL staff has done a great job helping the students make our way through the grad school experience. Debb Hodges Pabon, in particular, has always made herself available to us and done a fantastic job coordinating the numerous MTL gatherings.

I'd like to thank Marilyn Pierce in the EECS grad office for her help, guidance, and patience over the years that have comprised my eclectic grad school schedule.

The folks at National Semiconductor helped make my tapeout process as easy as it could be. In particular, Sangamesh Buddhiraju's CAD help was critical in getting the National setup working at MIT, and his excellent front-end work saved us countless hours of frustration. The National-MIT program wouldn't even exist if it wasn't for the work of Peter Holloway, who I've been lucky enough to work for and with over the years. Pete is truly one of the great guys I've met in the course of my travels, and I look forward to our paths crossing again.

I'd like to thank MTL CICS and MARCO for funding my research. I'd also like to thank the folks at Teradyne, especially Kurt Ware and Ron Sartchev, for funding me as a Teradyne fellow for a year. It was encouraging along the way to see that my research was sparking real-world interest.

I'd also like to thank Duke Xanthopoulos for helping me out with the initial CAD setup, and setting up a great situation for me at Cavium. I'm really looking forward to getting started.

My friends have been very supportive, in what can only be called their unique and "special" way. The boys of DOAIHPS have helped me enjoy what little free time I've had over the last four years, and I'm looking forward to finally having some time to waste with them now. Ken, Chris, Rufus, and Rob, the first \$1.35 (or, \$1.85 now...) at York is on me. (Hopefully you won't read this until *after* York...)

My family has been a strong influence on my life. I'd like to thank Steven, Mark, Cheryl, Donna, D.A., Kathy, Laureen, Dorene, Ellen, and John for the impact they've had in my getting to this point. Another way to look at this, of course, is that they are at least partly to blame. This is the way the youngest of eleven learns to think. I'm sure the survival skills I learned growing up in such a large family have helped me out in un-accounted for ways over the years. Figuring out ways to reduce quantization noise by 29dB is nothing compared to trying to figure out, as an 8 year old, how to buy 21 Christmas presents with \$20. Now that is tough math.

I'd like to thank my extended family, the Rhoads and Garlands, for their support over the many years they've known me.

I thank my wife, Stacy Meninger, for helping shape me to be the man I am today.

Finally, as long as this thesis is, if I spent every page trying to thank my parents for what they've done for me over the years, I'd run out of space. The example they've set and the support they've shown me have been overwhelming. So thank you most of all, Mom and Dad.

# Contents

| 1        | Area               | a of Fo                                              | ocus: Fractional-N Synthesis                           | 29                               |

|----------|--------------------|------------------------------------------------------|--------------------------------------------------------|----------------------------------|

|          | 1.1                | The Is                                               | sue of Fractional-N Quantization Noise                 | 30                               |

|          | 1.2                | Prior V                                              | Work Aimed at Reducing Fractional-N Quantization Noise | 31                               |

|          | 1.3                | Propos                                               | sed Quantization Noise Reduction Technique             | 33                               |

|          | 1.4                | Thesis                                               | Scope and Contributions                                | 35                               |

|          |                    | 1.4.1                                                | System Analytical Noise Modeling                       | 36                               |

|          |                    | 1.4.2                                                | Behavioral Modeling and Simulation                     | 37                               |

|          |                    | 1.4.3                                                | Circuit Design                                         | 38                               |

|          |                    | 1.4.4                                                | Measured Results                                       | 42                               |

|          |                    | 1.4.5                                                | Thesis Outline                                         | 43                               |

|          |                    |                                                      |                                                        |                                  |

| <b>2</b> | Free               | quency                                               | Synthesis Background                                   | 45                               |

| 2        | <b>Free</b><br>2.1 |                                                      | Synthesis Background                                   | <b>45</b>                        |

| 2        |                    |                                                      |                                                        |                                  |

| 2        |                    | Motiva                                               | ation for Fractional-N Synthesis                       | 45                               |

| 2        |                    | Motiva<br>2.1.1<br>2.1.2                             | ation for Fractional-N Synthesis                       | 45<br>45                         |

| 2        | 2.1                | Motiva<br>2.1.1<br>2.1.2                             | ation for Fractional-N Synthesis                       | $45 \\ 45 \\ 47$                 |

| 2        | 2.1                | Motiva<br>2.1.1<br>2.1.2<br>Freque                   | ation for Fractional-N Synthesis                       | 45<br>45<br>47<br>48             |

| 2        | 2.1                | Motiva<br>2.1.1<br>2.1.2<br>Freque<br>2.2.1          | ation for Fractional-N Synthesis                       | 45<br>45<br>47<br>48<br>48       |

| 2        | 2.1                | Motiva<br>2.1.1<br>2.1.2<br>Freque<br>2.2.1<br>2.2.2 | ation for Fractional-N Synthesis                       | 45<br>45<br>47<br>48<br>48<br>49 |

| 3 | Fra | ctional | -N Synthesizer Noise Modeling                                         | 57  |

|---|-----|---------|-----------------------------------------------------------------------|-----|

|   | 3.1 | Basics  | s of Noise Modeling of Fractional-N Synthesizers                      | 57  |

|   | 3.2 | A Nev   | w Analytical Model View of Fractional-N Synthesizers                  | 60  |

|   |     | 3.2.1   | Phase Interpolation Fractional-N Synthesis                            | 61  |

|   |     | 3.2.2   | $\Sigma\Delta$ Fractional-N Synthesis                                 | 70  |

|   |     | 3.2.3   | Similarity Between a Fractional-N Synthesizer and $\Sigma\Delta$ MASH |     |

|   |     |         | DAC                                                                   | 71  |

|   | 3.3 | Summ    | nary                                                                  | 73  |

| 4 | Pro | posed   | Quantization Noise Reduction Technique                                | 75  |

|   | 4.1 | The P   | PFD/DAC Approach                                                      | 76  |

|   |     | 4.1.1   | The PFD/DAC Approach: Constant Charge Delivery                        | 78  |

|   |     | 4.1.2   | Comparison of Charge Balance in a Classical Fractional-N Syn-         |     |

|   |     |         | the<br>sizer with the PFD/DAC Synthesizer $\hdots$                    | 82  |

|   |     | 4.1.3   | An Alternative Explanation of the PFD/DAC Approach $\ . \ .$ .        | 84  |

|   |     | 4.1.4   | Model for the PFD/DAC Synthesizer                                     | 89  |

|   |     | 4.1.5   | The Issue of Mismatch                                                 | 90  |

|   | 4.2 | Propo   | sed Solution: A Mismatch Compensated PFD/DAC Synthesizer              |     |

|   |     | Archit  | tecture                                                               | 91  |

|   |     | 4.2.1   | Using a Noise Shaped Cancellation DAC for Improved In-band            |     |

|   |     |         | Noise                                                                 | 92  |

|   |     | 4.2.2   | Non-idealities Within the Charge-box                                  | 95  |

|   |     | 4.2.3   | $\rm PFD/DAC$ Unit Element Mismatch and Compensation                  | 96  |

|   |     | 4.2.4   | $\rm PFD/DAC$ Internal Timing Mismatch and Compensation               | 97  |

|   |     | 4.2.5   | Shape Mismatch Between the Error Signal and Cancellation              |     |

|   |     |         | Signal                                                                | 100 |

|   | 4.3 | Summ    | nary                                                                  | 103 |

| 5 | Beł | naviora | al Simulation of Fractional-N Synthesizers                            | 105 |

|   | 5.1 | Settin  | g the PLL Dynamics and Preliminary Noise Analysis Using the           |     |

|   |     | PLL I   | Design Assistant                                                      | 106 |

|   | 5.2  | PFD/   | DAC Synthesizer Base Behavioral Model                        | 109 |

|---|------|--------|--------------------------------------------------------------|-----|

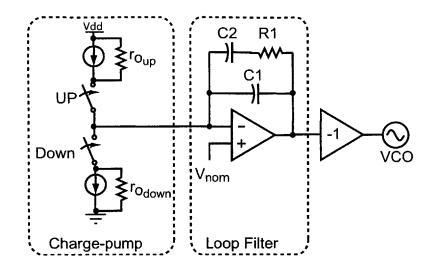

|   |      | 5.2.1  | Loop Filter and Loop Gain Calculation                        | 111 |

|   |      | 5.2.2  | Baseline Noise Calculations                                  | 112 |

|   |      | 5.2.3  | Detector Phase Noise Calculation                             | 113 |

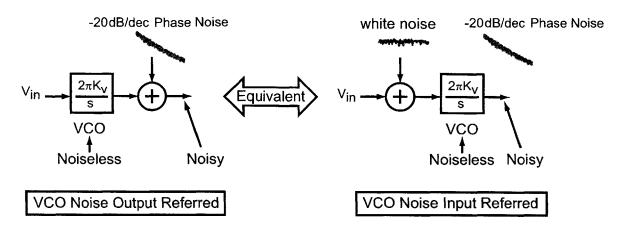

|   |      | 5.2.4  | VCO Phase Noise Calculation                                  | 115 |

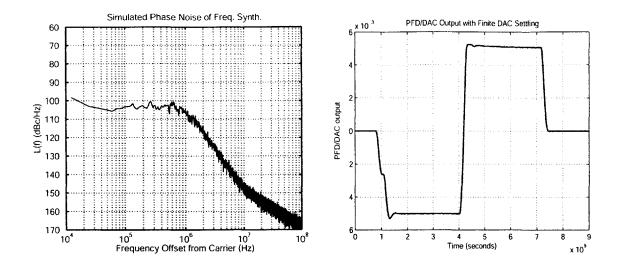

|   |      | 5.2.5  | Baseline Phase Noise Simulation                              | 118 |

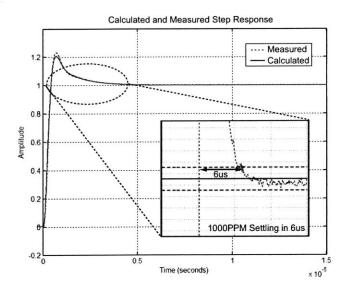

|   |      | 5.2.6  | Baseline Dynamic Performance                                 | 119 |

|   | 5.3  | Behav  | ioral Simulation of Non-Idealities and Proposed Compensation |     |

|   |      | Techn  | iques                                                        | 121 |

|   |      | 5.3.1  | Compensation of Magnitude Mismatch in the Charge-Box         | 121 |

|   |      | 5.3.2  | Source of Unit Element Mismatch                              | 124 |

|   |      | 5.3.3  | Compensation of Timing Mismatch in the Charge Box            | 125 |

|   |      | 5.3.4  | Eliminating Shape Mismatch With a Sample-and-Hold            | 127 |

|   |      | 5.3.5  | A Digital Compensation Scheme for Reducing Shape Mismatch    |     |

|   |      |        | Spurs                                                        | 128 |

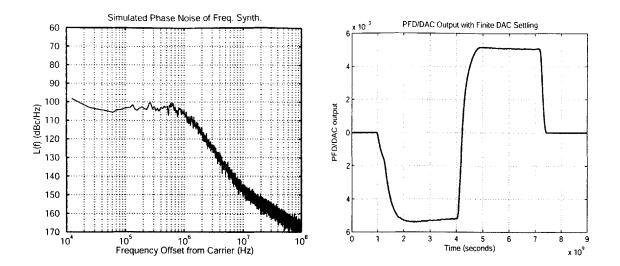

|   |      | 5.3.6  | Impact of Finite PFD/DAC Settling                            | 132 |

|   |      | 5.3.7  | Impact of Finite Charge-Pump Output Impedance                | 134 |

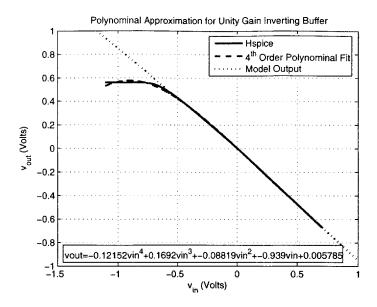

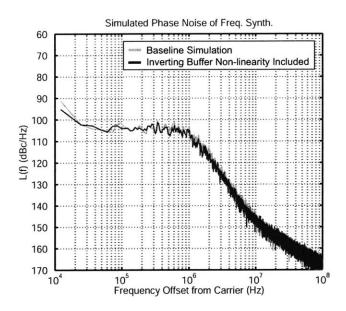

|   |      | 5.3.8  | Impact of Unity Gain Buffer Non-linearity                    | 137 |

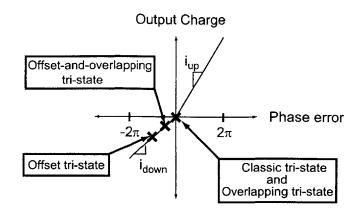

|   | 5.4  | Choos  | sing the PFD Architecture for Best Charge-Pump Linearity     | 141 |

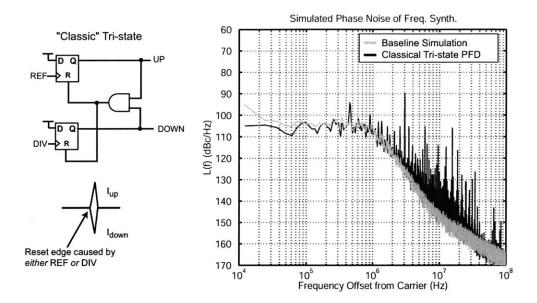

|   |      | 5.4.1  | Classic Tri-state PFD                                        | 141 |

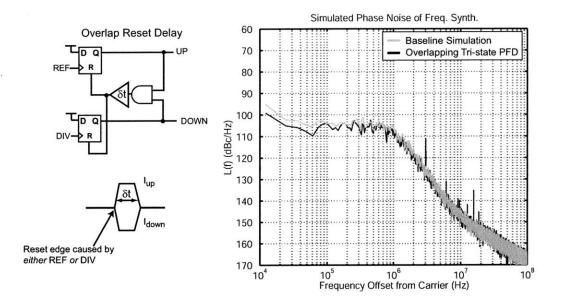

|   |      | 5.4.2  | Overlapping Tri-state PFD                                    | 144 |

|   |      | 5.4.3  | Offset Tri-state PFD                                         | 146 |

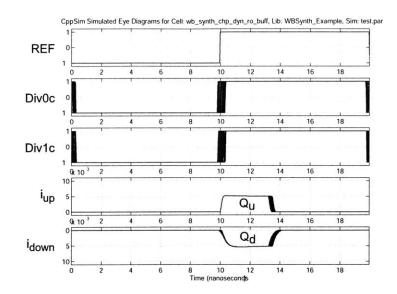

|   |      | 5.4.4  | Overlapping and Offset PFD                                   | 148 |

|   | 5.5  | GMSI   | K Modulated Synthesizer Model                                | 149 |

|   |      | 5.5.1  | Direct GMSK Modulation                                       | 149 |

|   | 5.6  | Summ   | nary                                                         | 151 |

| 6 | Cire | cuit D | esign                                                        | 155 |

|   | 6.1  | Divide | er and Divider Retimer                                       | 156 |

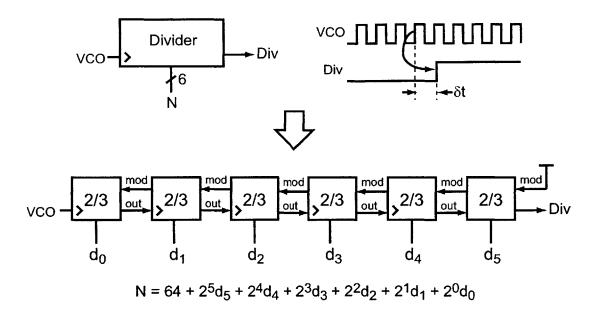

|   |      | 6.1.1  | High-speed, Multi-modulus Divider                            | 157 |

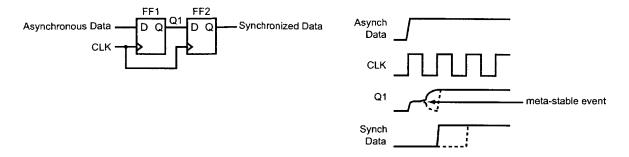

|   |      | 6.1.2  | Retiming and the Issue of Meta-stability                         | 157        |

|---|------|--------|------------------------------------------------------------------|------------|

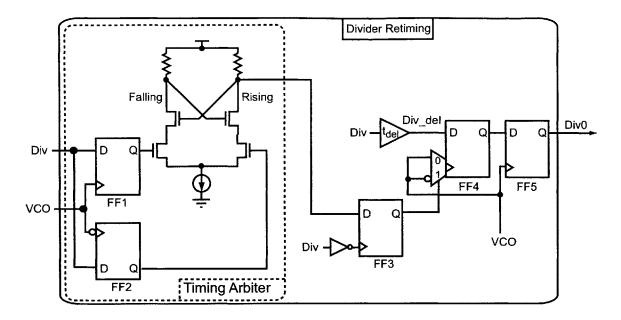

|   |      | 6.1.3  | Divider Retimer                                                  | 159        |

|   |      | 6.1.4  | A Phase-space Methodology for Understanding Divider Retimin      | g160       |

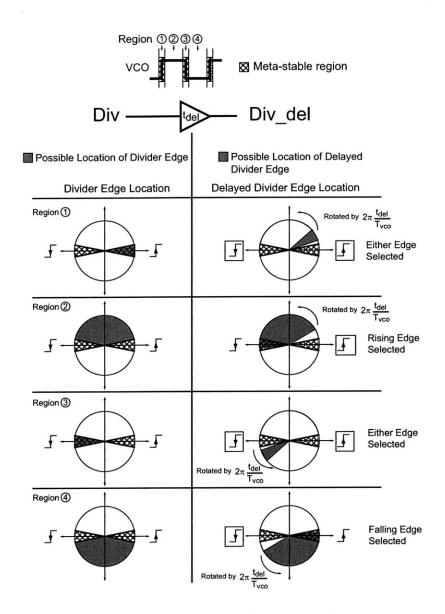

|   |      | 6.1.5  | Divider Retimer Operation In Phase-space                         | 162        |

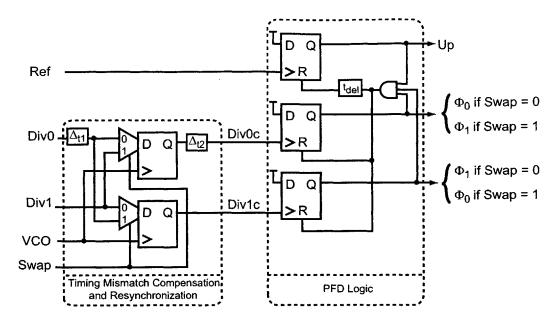

|   | 6.2  | PFD I  | logic and Timing Compensation                                    | 165        |

|   | 6.3  | PFD/I  | DAC Unit Element Current Source                                  | 167        |

|   | 6.4  | Loop I | Filter                                                           | 171        |

|   | 6.5  | Unity  | Gain Inverting Buffer                                            | 173        |

|   | 6.6  | Op-am  | ap and Buffer Noise Considerations                               | 175        |

|   | 6.7  | Sample | e and Hold Circuitry                                             | 176        |

|   |      | 6.7.1  | Charge Injection and Compensation                                | 178        |

|   |      | 6.7.2  | Differential-to-single-ended Converter                           | 181        |

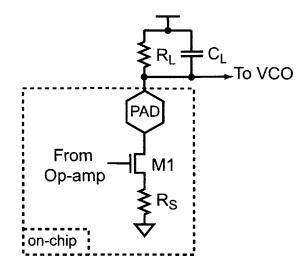

|   | 6.8  | High S | Speed I/O Design                                                 | 183        |

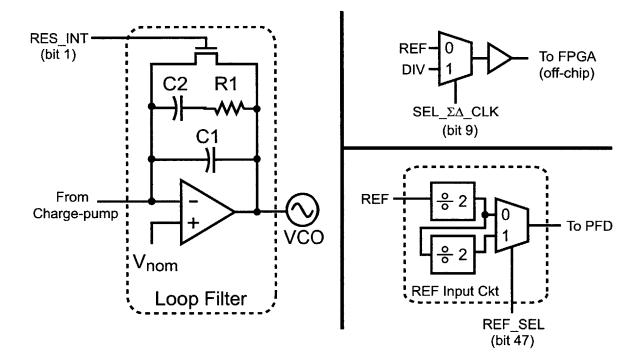

|   |      | 6.8.1  | VCO and Reference Input Buffer                                   | 183        |

|   |      | 6.8.2  | Output Band Select Divider                                       | 184        |

|   | 6.9  | Protot | ype PFD/DAC Synthesizer IC                                       | 186        |

|   | 6.10 | Summ   | ary                                                              | 186        |

| 7 | Mea  | sured  | Results                                                          | 187        |

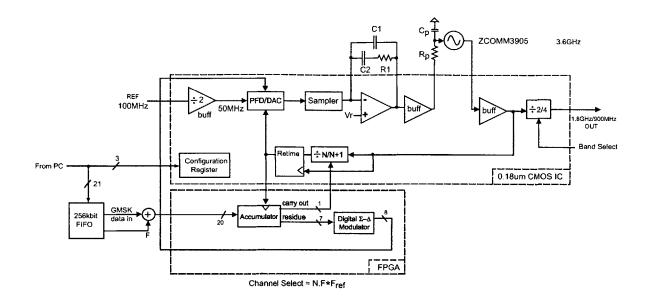

| • | 7.1  |        | ype Mismatch Compensated PFD/DAC Synthesizer System              | 188        |

|   | 1.1  | 7.1.1  | System Programmability                                           |            |

|   | 7.2  |        | ne Measured Performance: The Integer-N Synthesizer               | 190        |

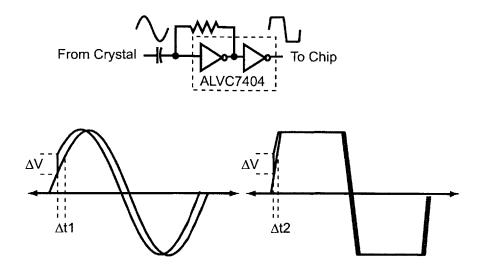

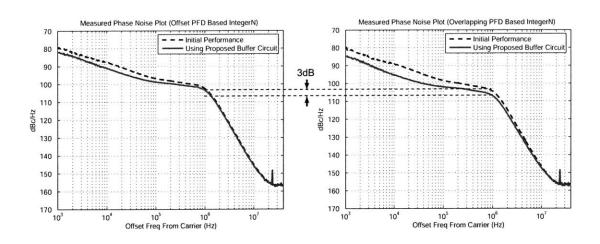

|   | 1.2  | 7.2.1  | Reference Buffer Jitter Induced Noise                            | 190        |

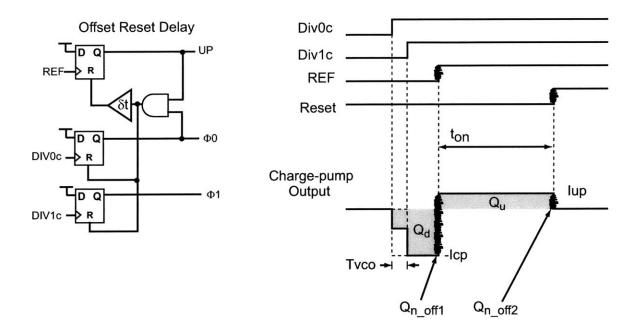

|   |      | 7.2.2  | PFD Reset Jitter Induced Noise                                   | 195        |

|   |      | 7.2.3  | Reference Jitter Extraction Using the Analytical Model           | 195        |

|   | 7.3  |        | Dedulated PFD/DAC Synthesizer Measured Performance               | 200        |

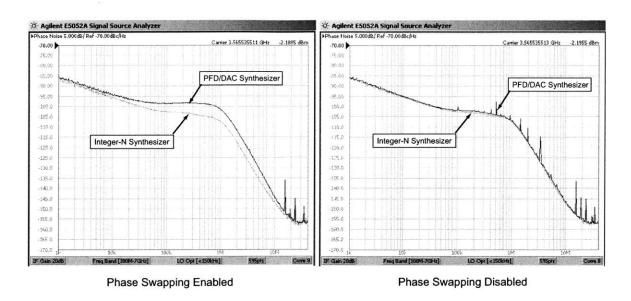

|   | (.)  | 7.3.1  | PFD/DAC Synthesizer Vs. Integer-N Synthesizer                    |            |

|   |      |        |                                                                  | 200        |

|   |      | 7.3.2  | PFD/DAC Timing Mismatch Extraction Using the Analytical<br>Model | <u>901</u> |

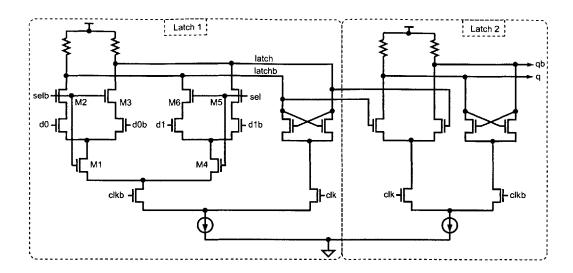

|   |      | 799    |                                                                  | 201        |

|   |      | 7.3.3  | Dynamic Response                                                 | 203        |

|   |                | 7.3.4 PFD/DAC Synthesizer Vs. $\Sigma\Delta$ Synthesizer $\ldots$ | 204 |

|---|----------------|-------------------------------------------------------------------|-----|

|   |                | 7.3.5 Impact of Sample-and-Hold Loop Filter and Spurious Perfor-  |     |

|   |                | mance                                                             | 205 |

|   |                | 7.3.6 Comparison to Prior Work                                    | 208 |

|   | 7.4            | Modulated Synthesizer Measured Performance                        | 213 |

|   | 7.5            | Summary                                                           | 217 |

| 8 | Con            | clusions and Future Work                                          | 219 |

|   | 8.1            | Mismatch Compensated PFD/DAC Synthesizer                          | 219 |

|   | 8.2            | Analytical Modeling Contributions                                 | 220 |

|   | 8.3            | Behavioral Modeling Contributions                                 | 220 |

|   | 8.4            | Circuit Contributions                                             | 221 |

|   | 8.5            | Future Work                                                       | 222 |

|   |                | 8.5.1 Quantization Noise                                          | 222 |

|   |                | 8.5.2 Intrinsic Noise                                             | 223 |

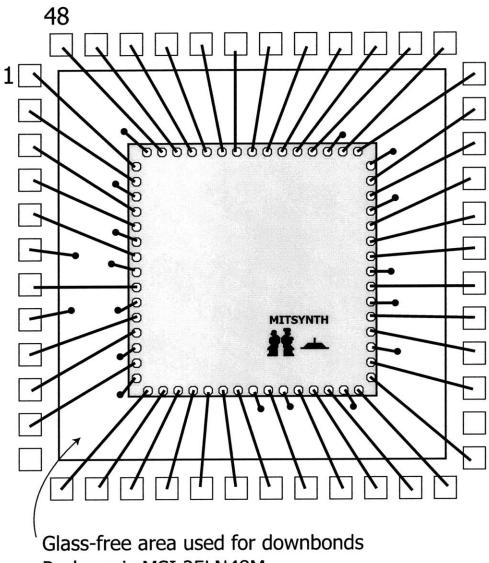

| A | Chi            | p Pinout and Bonding Diagram                                      | 225 |

| в | $\mathbf{Syn}$ | thesizer Configuration Register                                   | 229 |

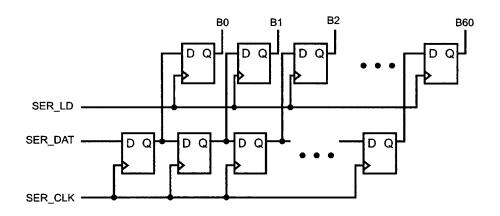

|   | B.1            | Register Organization                                             | 230 |

|   | B.2            | General Configuration                                             | 232 |

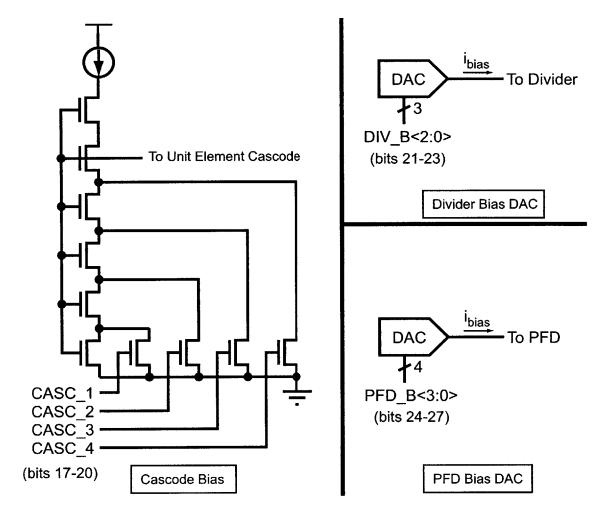

|   | B.3            | Bias Configuration                                                | 234 |

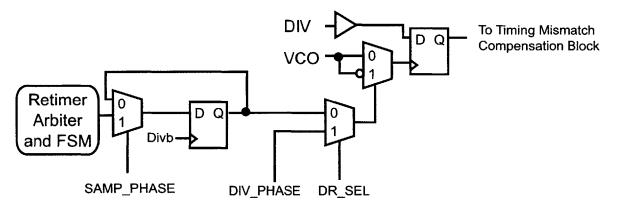

|   | B.4            | Divider Retimer Configuration                                     | 236 |

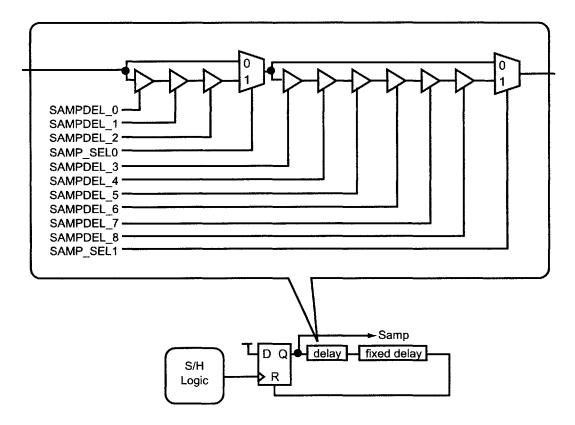

|   | B.5            | S/H Configuration                                                 | 238 |

|   | B.6            | PFD Configuration                                                 | 240 |

# List of Figures

| 1-1  | Classic Fractional-N Synthesis with Phase Interpolation                       | 30 |

|------|-------------------------------------------------------------------------------|----|

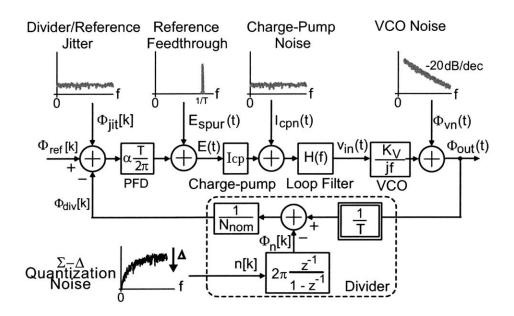

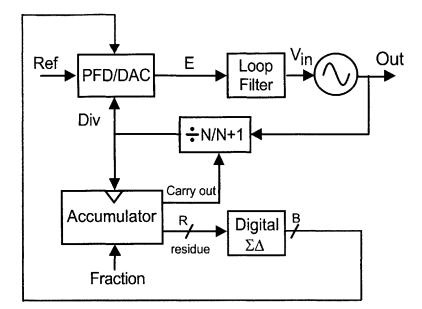

| 1-2  | $\Sigma\Delta$ Fractional-N Synthesizer and Noise-Bandwidth Tradeoff $\ .$    | 31 |

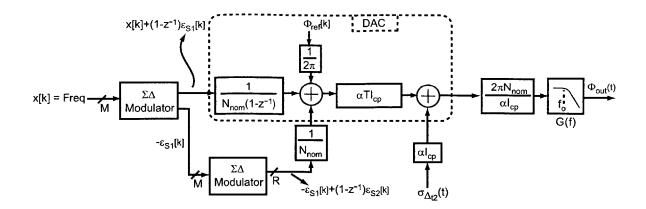

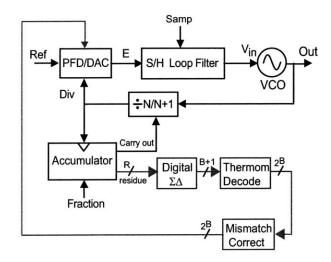

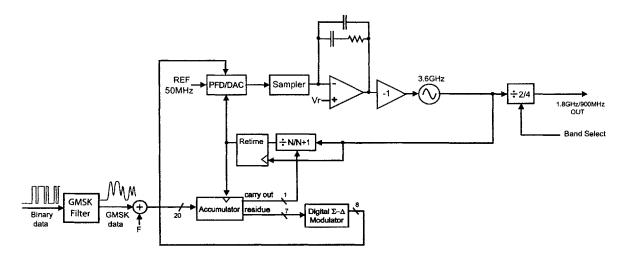

| 1-3  | Proposed Synthesizer Architecture                                             | 33 |

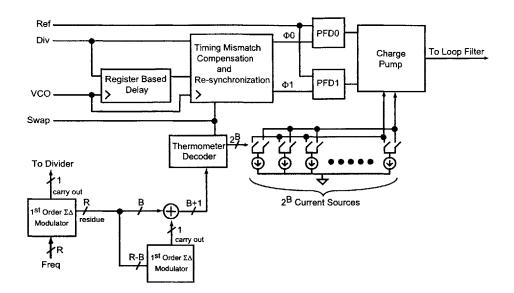

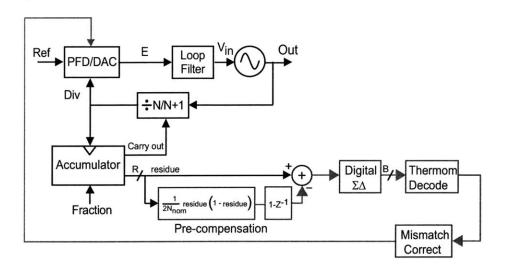

| 1-4  | Proposed Mismatch Compensated PFD/DAC                                         | 34 |

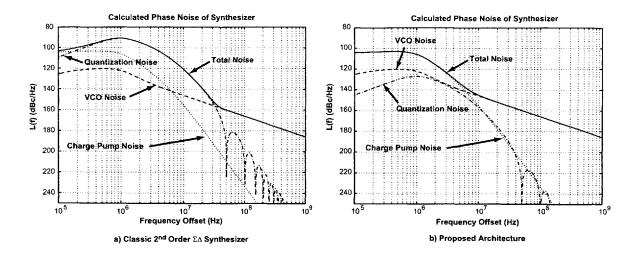

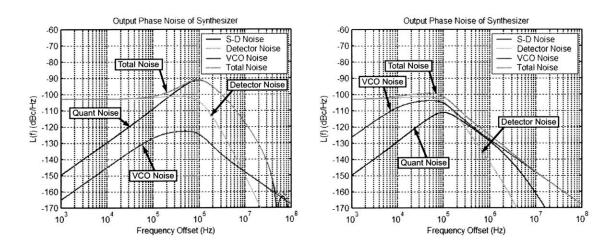

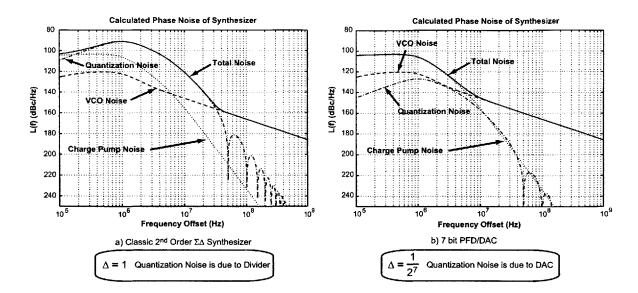

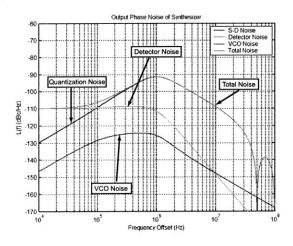

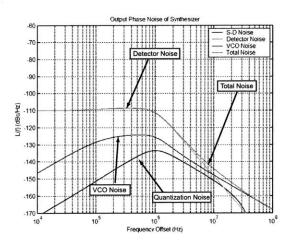

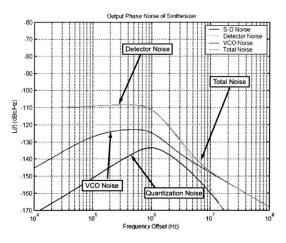

| 1-5  | Calculated Phase Noise                                                        | 35 |

| 1-6  | New Model View of Fractional-N Synthesizer as a MASH $\Sigma\Delta$ DAC $~$ . | 36 |

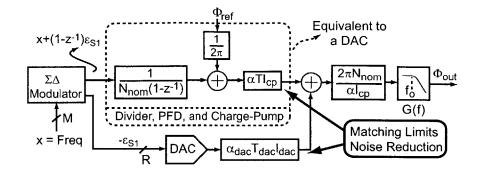

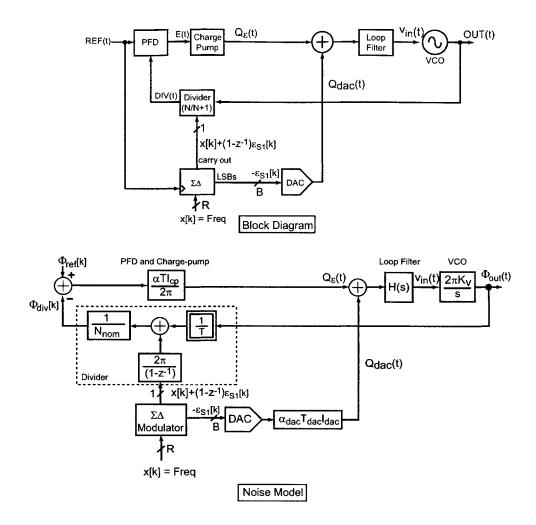

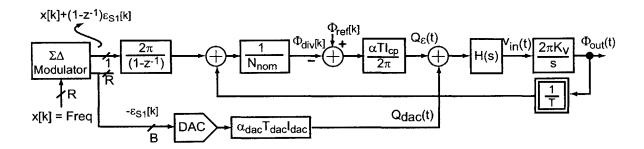

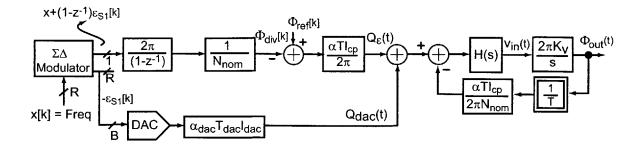

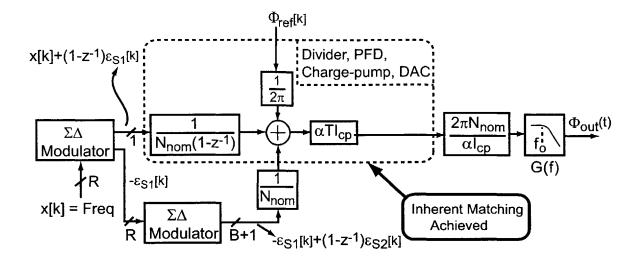

| 1-7  | PFD/DAC Synthesizer Model                                                     | 36 |

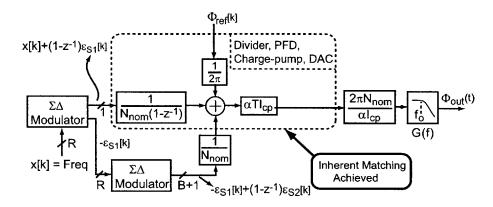

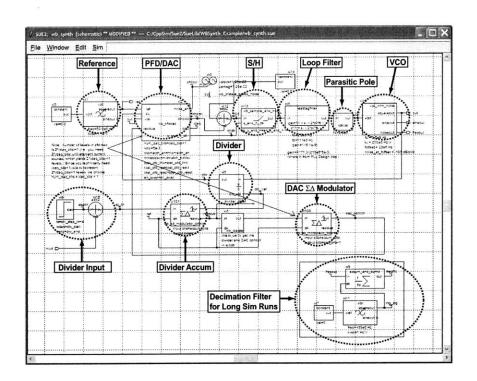

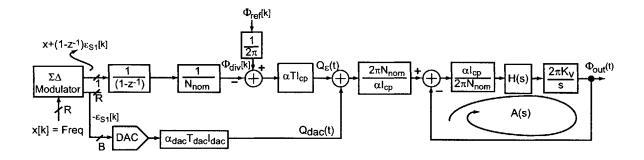

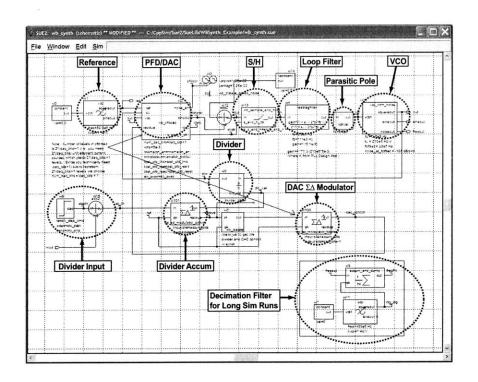

| 1-8  | Behavioral Model for PFD/DAC Synthesizer                                      | 37 |

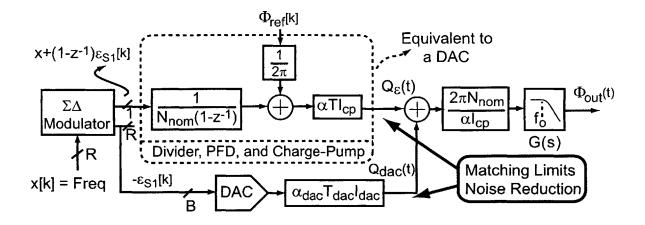

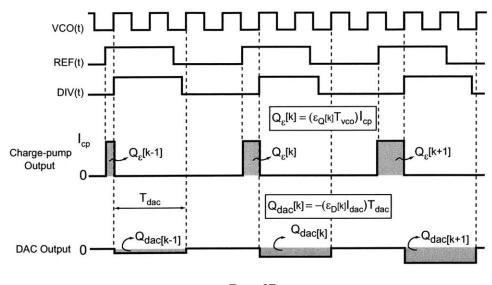

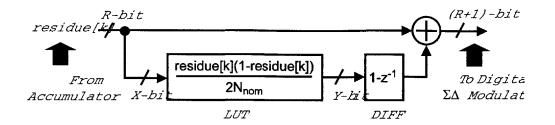

| 1-9  | PFD/DAC Technique Charge-box                                                  | 38 |

| 1-10 | Proposed Mismatch Compensated PFD/DAC                                         | 40 |

| 1-11 | Proposed Divider Retiming Circuit                                             | 41 |

| 1-12 | Measured Phase Noise Comparison of PFD/DAC Synthesizer Vs. $2^{nd}$           |    |

|      | Order $\Sigma\Delta$ Synthesizer                                              | 42 |

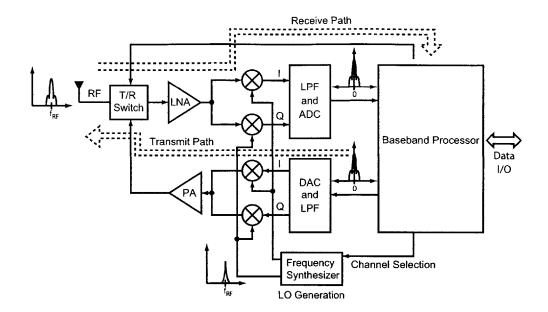

| 2-1  | Typical RF Transceiver                                                        | 46 |

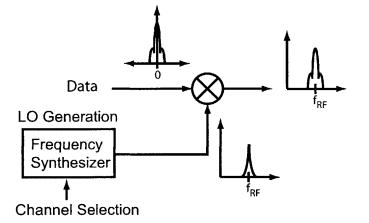

| 2-2  | Mixer Up-conversion Operation                                                 | 47 |

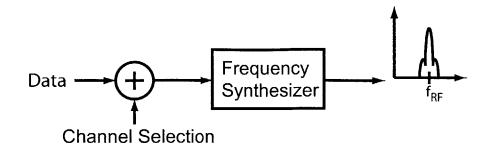

| 2-3  | Direct Modulation Transmitter                                                 | 48 |

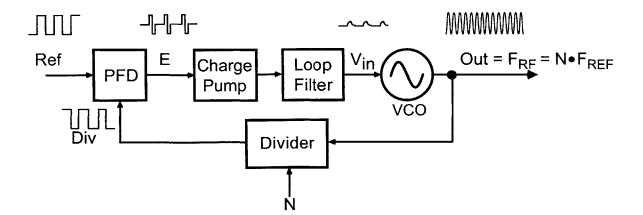

| 2-4  | Integer-N Synthesizer                                                         | 49 |

| 2-5  | Classical Fractional-N Synthesizer                                            | 50 |

| 2-6  | Quantization Noise in Fractional-N Synthesis for $N.F = 4.25$                 | 51 |

| 2-7  | Classical Fractional-N Synthesizer With Phase Interpolation                   | 52 |

| 2-8  | $\Sigma\Delta$ Fractional-N Synthesizer and Noise/Bandwidth Tradeoff          | 54 |

| 3-1  | Noise Model for a $\Sigma\Delta$ Synthesizer from [1]                         | 58 |

| 3-2  | PLL Filtering of System Noise Sources                                                        | 59 |

|------|----------------------------------------------------------------------------------------------|----|

| 3-3  | PI Synthesizer System Block Diagram and Noise Model                                          | 60 |

| 3-4  | Base PI Noise Model                                                                          | 61 |

| 3-5  | PI Noise Model: Step 1                                                                       | 62 |

| 3-6  | PI Noise Model: Step 2                                                                       | 62 |

| 3-7  | PI Noise Model: Step 3                                                                       | 63 |

| 3-8  | Charge Cancellation in PI Synthesis                                                          | 64 |

| 3-9  | PI Synthesizer Block Diagram Including DAC Quantization Noise                                | 66 |

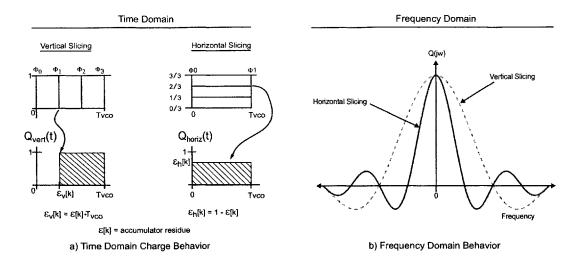

| 3-10 | Vertical Vs. Horizontal Resolution                                                           | 67 |

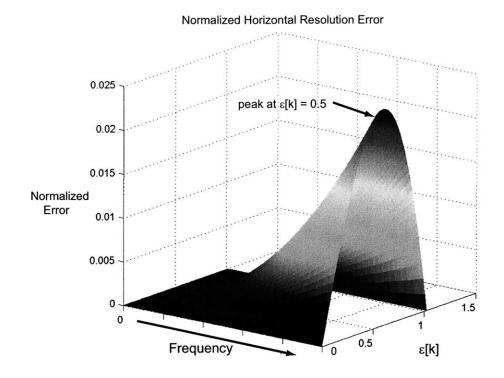

| 3-11 | Shape Mismatch Error as a Function of Frequency and Discrete Index ${\bf k}$                 | 69 |

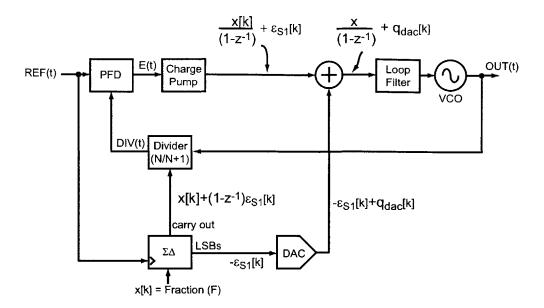

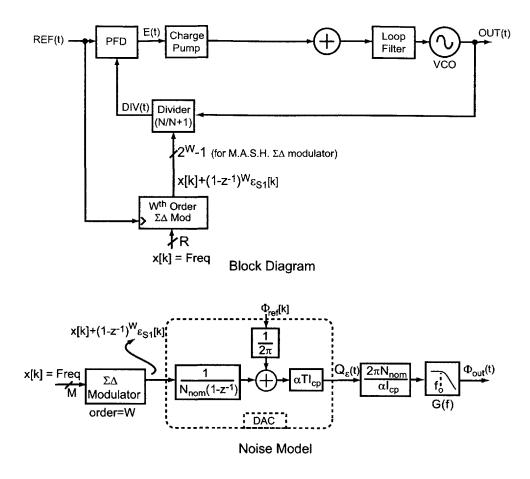

| 3-12 | $\Sigma\Delta$ Synthesizer Block Diagram and Noise Model                                     | 70 |

| 3-13 | Comparison of Fractional-N Synthesizer and MASH $\Sigma\Delta$ DAC $\ .$                     | 72 |

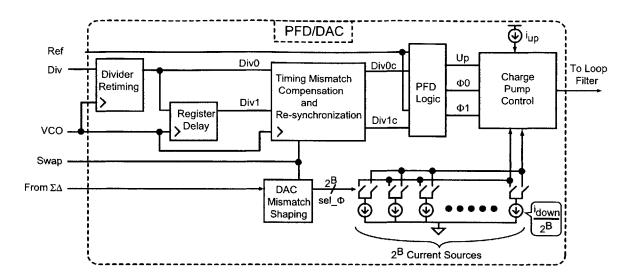

| 4-1  | PFD/DAC Synthesizer Architecture                                                             | 76 |

| 4-2  | PFD/DAC Architecture                                                                         | 77 |

| 4-3  | PFD/DAC Operation: The Charge Box                                                            | 77 |

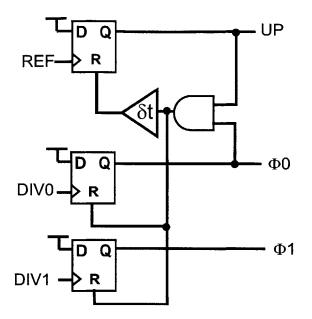

| 4-4  | $\rm PFD$ Logic Architecture for a Practical Implementation of the $\rm PFD/DAC$             | 78 |

| 4-5  | PFD/DAC Operation: A Practical Example                                                       | 79 |

| 4-6  | Charge Balance In the PFD/DAC Using the Two Right-most Charge-                               |    |

|      | packets in Figure 4-5                                                                        | 80 |

| 4-7  | Charge Balance in a Classical Fractional-N Synthesizer for $N{=}8.25$                        | 82 |

| 4-8  | Charge Balance in a PFD/DAC Fractional-N Synthesizer for N=8.25 $$                           | 83 |

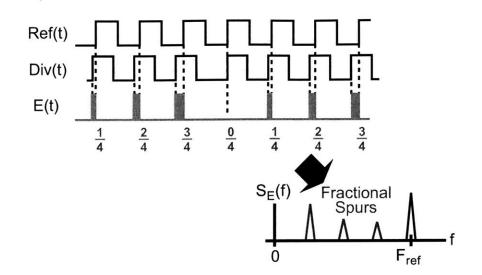

| 4-9  | Fractional-N Spurs in Classical Fractional-N Synthesis                                       | 85 |

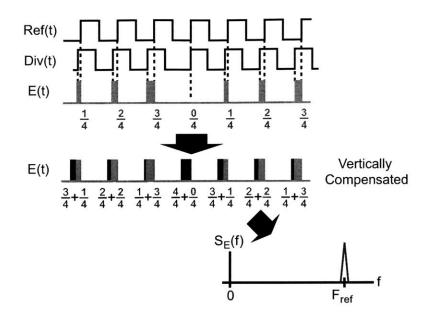

| 4-10 | Vertical Compensation of fractional spurs                                                    | 86 |

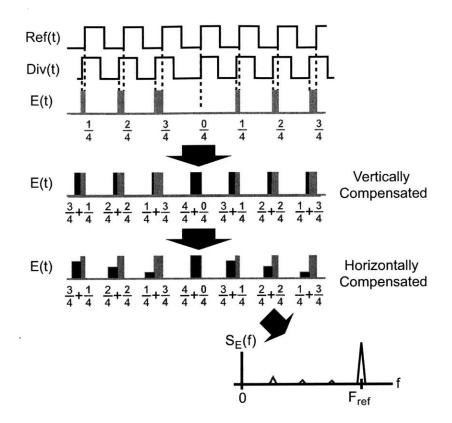

| 4-11 | Horizontal Compensation of fractional spurs                                                  | 87 |

| 4-12 | Implementation of the Horizontal Compensation Scheme                                         | 88 |

| 4-13 | Horizontal Compensation Error Signals                                                        | 89 |

| 4-14 | $\operatorname{PFD}/\operatorname{DAC}$ Implementation of the Horizontal Cancellation Scheme | 90 |

| 4-15 | Model for PFD/DAC Synthesizer                                                                | 91 |

| 4-16 | Using a Noise Shaped PFD/DAC                                                                 | 92 |

| 4-17 | Quantization Noise Suppression                                                     | 93  |

|------|------------------------------------------------------------------------------------|-----|

| 4-18 | Model for Noise Shaped PFD/DAC Synthesizer                                         | 94  |

| 4-19 | Noise Shaped PFD/DAC Architecture                                                  | 95  |

| 4-20 | Non-ideal Charge-box                                                               | 95  |

| 4-21 | Dynamic Element Matching to Reduce Unit Element Mismatch                           | 96  |

| 4-22 | Mismatch Compensated PFD/DAC                                                       | 98  |

| 4-23 | Dynamic Phase Matching Block                                                       | 99  |

| 4-24 | Model with Timing Mismatch                                                         | 100 |

| 4-25 | Digital Gain Compensation Block                                                    | 101 |

| 4-26 | Digitally Compensated PFD/DAC Synthesizer                                          | 102 |

| 4-27 | Using a Sample-and-Hold to Eliminate Shape Mismatch                                | 104 |

| 4-28 | $\rm PFD/DAC$ Synthesizer with Sample-and-Hold to Eliminate Shape Mis-             |     |

|      | match                                                                              | 104 |

| 5-1  | PLL Design Assistant (PDA) Design Parameters for $2^{nd}$ Order $\Sigma\Delta$     |     |

|      | Synthesizer                                                                        | 107 |

| 5-2  | PLL Design Assistant Calculated Phase Noise for $2^{nd}$ Order $\Sigma\Delta$ Syn- |     |

|      | thesizer                                                                           | 107 |

| 5-3  | PLL Design Assistant (PDA) Design Parameters for 7-bit PFD/DAC $$                  |     |

|      | Synthesizer                                                                        | 108 |

| 5-4  | PLL Design Assistant (PDA) Calculated Phase Noise for 7-bit PFD/DAC $$             |     |

|      | Synthesizer                                                                        | 108 |

| 5-5  | PLL Design Assistant (PDA) Design Parameters for 7-bit PFD/DAC $$                  |     |

|      | Synthesizer With Added Pole                                                        | 109 |

| 5-6  | PLL Design Assistant (PDA) Calculated Phase Noise for 7-bit PFD/DAC $$             |     |

|      | Synthesizer With Added Pole                                                        | 110 |

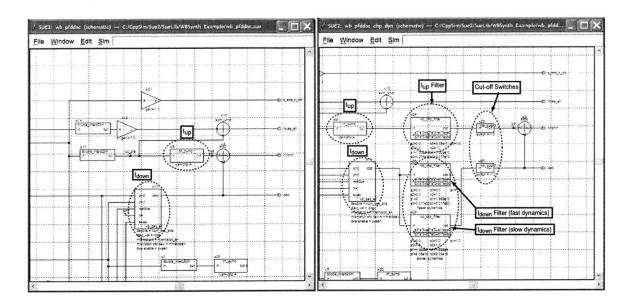

| 5-7  | Behavioral Model for PFD/DAC Synthesizer                                           | 111 |

| 5-8  | Lead-lag Loop Filter Configuration                                                 | 112 |

| 5-9  | Charge Pump With Noisy Currents                                                    | 114 |

| 5-10 | Detector Noise Inclusion in the PLL Design Assistant                               | 115 |

| 5-11 | VCO Noise Modeling                                                                       | 116 |

|------|------------------------------------------------------------------------------------------|-----|

| 5-12 | Baseline Behavioral Simulation Comparison With PLL Design Assis-                         |     |

|      | tant Calculations                                                                        | 117 |

| 5-13 | Separate CppSim Simulations of VCO, Detector and Quantization Noise,                     |     |

|      | and Only Quantization Noise Overlayed with PDA Calculations $\ldots$                     | 118 |

| 5-14 | Baseline Simulation for a $2^{nd}$ order $\Sigma\Delta$ Synthesizer                      | 119 |

| 5-15 | Baseline Improvement Using the PFD/DAC vs a $2^{nd}$ Order $\Sigma\Delta$ Syn-           |     |

|      | thesizer                                                                                 | 120 |

| 5-16 | Comparison of PDA and CppSim Step Responses for Baseline PFD/DAC                         |     |

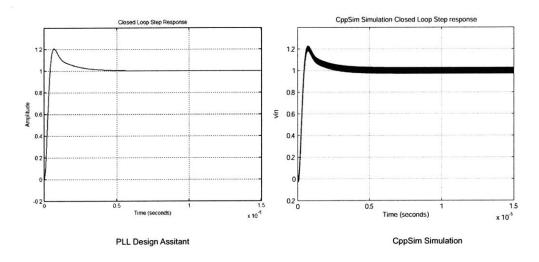

|      | Synthesizer                                                                              | 120 |

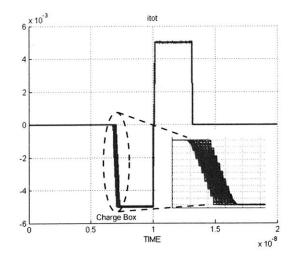

| 5-17 | PFD/DAC Output Current                                                                   | 121 |

| 5-18 | Simulation Showing the Impact of Unit Element Mismatch and Dy-                           |     |

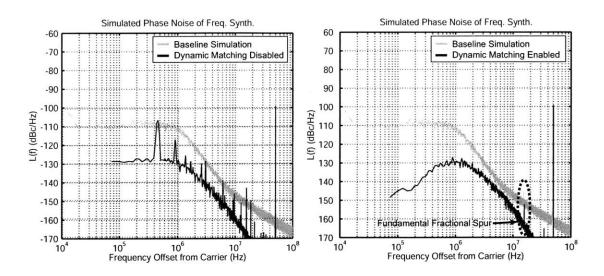

|      | namic Element Matching                                                                   | 122 |

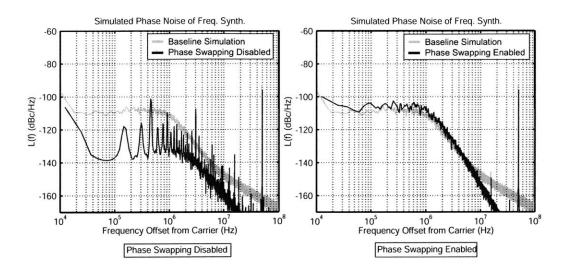

| 5-19 | Simulations Showing the Impact of Timing Mismatch and Phase Swap-                        |     |

|      | ping                                                                                     | 126 |

| 5-20 | Elimination of Shape Mismatch by Using a S/H                                             | 127 |

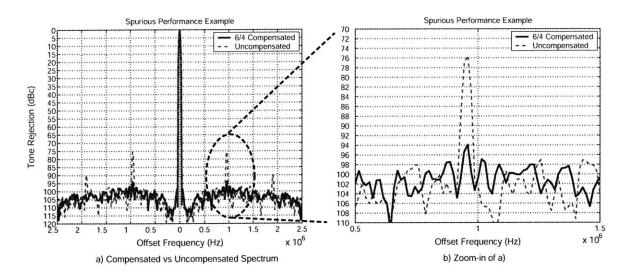

| 5-21 | Output Spectrum with and without Digital Compensation                                    | 129 |

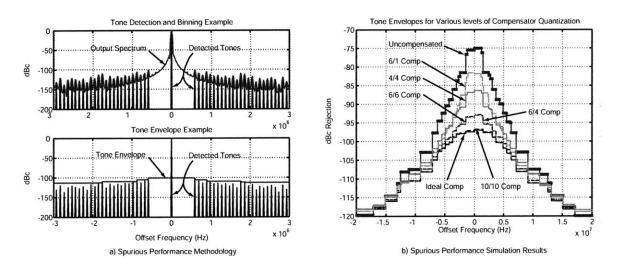

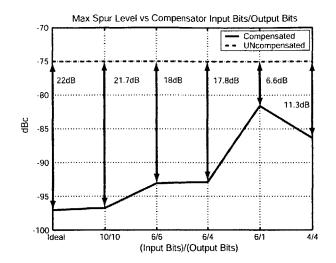

| 5-22 | Spurious Performance Methodology and Simulation Results                                  | 129 |

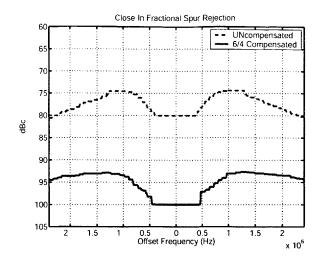

| 5-23 | Close-In Spur Performance                                                                | 130 |

| 5-24 | Maximum Spur Levels for Various Levels of Compensation                                   | 131 |

| 5-25 | PFD/DAC With and Without Finite Settling Added                                           | 132 |

| 5-26 | Finite Settling of the PFD/DAC Using Estimated Parasitics                                | 133 |

| 5-27 | Finite Settling of the PFD/DAC Using Extracted Layout Parasitics $% \mathcal{L}^{(1)}$ . | 134 |

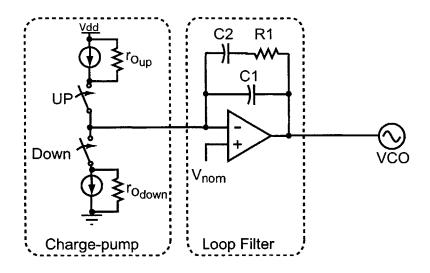

| 5-28 | Active Loop Filter Configuration                                                         | 135 |

| 5-29 | Simulation Results for Finite Output Impedance Current Source Model                      | 136 |

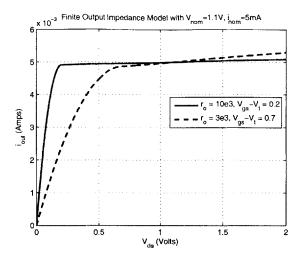

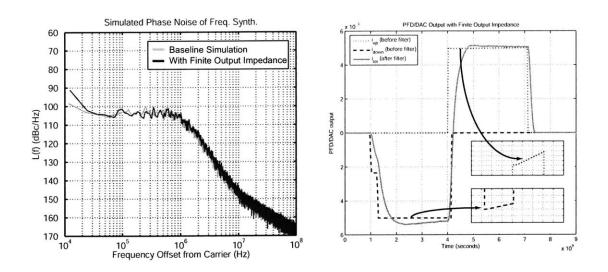

| 5-30 | Simulation Including Finite Unit Element Output Impedance                                | 137 |

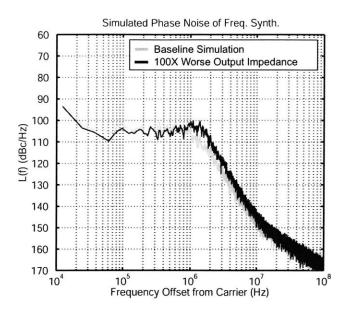

| 5-31 | Simulation with 100X Worse-than-expected Charge-pump Output Im-                          |     |

|      | pedance                                                                                  | 138 |

| 5-32 | Active Loop Filter With Unity Gain Inverting Buffer                                      | 139 |

| 5-33 | Inverting Buffer Amplifier Polynomial Approximation Model Response                       | 140 |

| 5-34 | Output Phase Noise Profile with Inverting Amplifier Model Included      | 141  |

|------|-------------------------------------------------------------------------|------|

| 5-35 | Classical Tri-State PFD Architecture                                    | 142  |

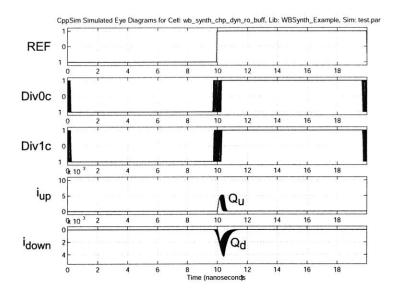

| 5-36 | Eye Diagram of Key Signals in a PFD/DAC Employing the Classic           |      |

|      | Tri-state PFD                                                           | 143  |

| 5-37 | Tri-state PFD and Charge-pump Transfer Curve for $i_{up} \neq i_{down}$ | 144  |

| 5-38 | Tri-State PFD Architecture With Current Overlap                         | 145  |

| 5-39 | Eye Diagram of Key Signals in a PFD/DAC Employing the Overlap-          |      |

|      | ping Tri-state PFD                                                      | 146  |

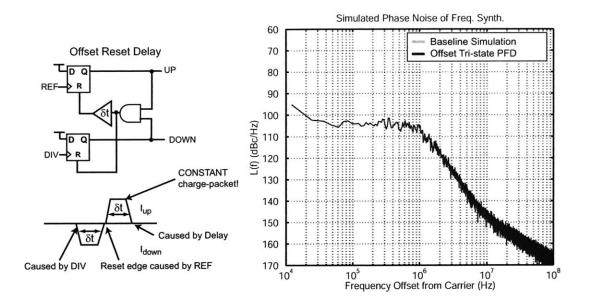

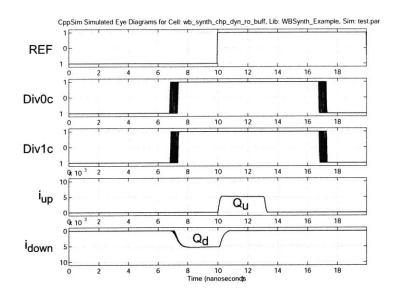

| 5-40 | Tri-State PFD Architecture With Offset Currents                         | 147  |

| 5-41 | Eye Diagram of Key Signals in a PFD/DAC Employing the Offset            |      |

|      | Tri-state PFD                                                           | 148  |

| 5-42 | Tri-State PFD Architecture With Both Overlapping and Offset Current     | s149 |

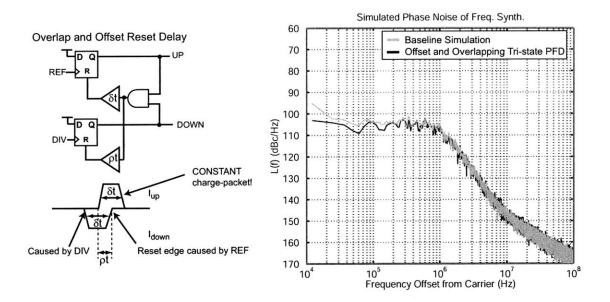

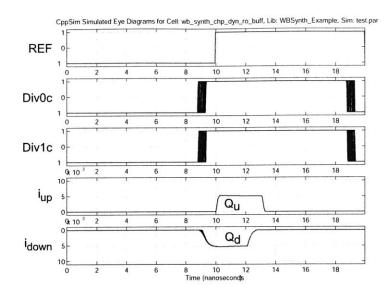

| 5-43 | Eye Diagram of Key Signals in a PFD/DAC Employing the Offset and        |      |

|      | Overlapping Tri-state PFD                                               | 150  |

| 5-44 | Dual Band GMSK Transmitter                                              | 151  |

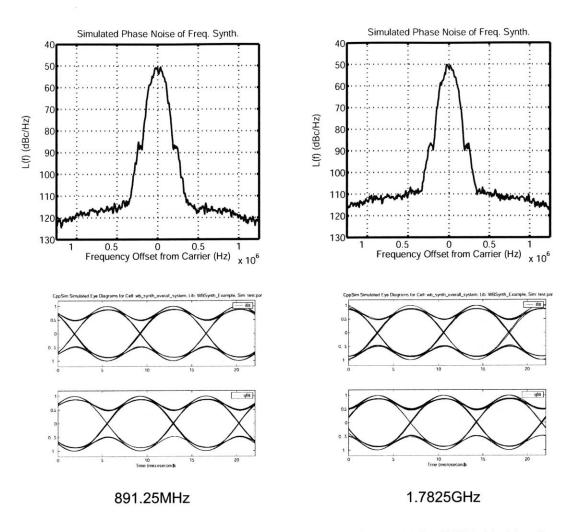

| 5-45 | Simulated Output Spectra and Eyes for 271kb/s GMSK Modulated            |      |

|      | PFD/DAC Synthesizer                                                     | 152  |

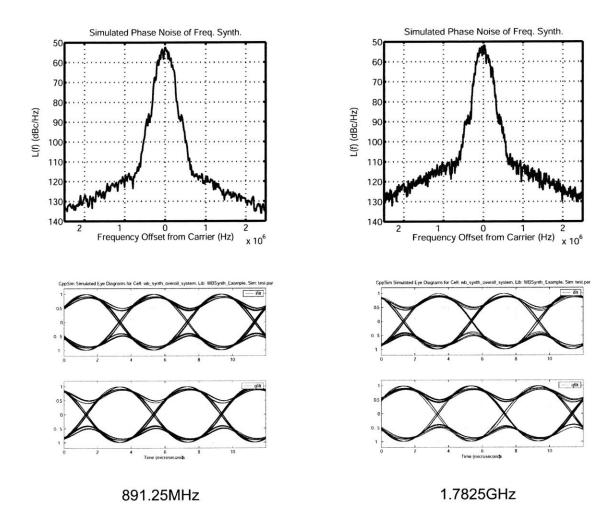

| 5-46 | Simulated Output Spectra and Eyes for 500kb/s GMSK Modulated            |      |

|      | PFD/DAC Synthesizer                                                     | 153  |

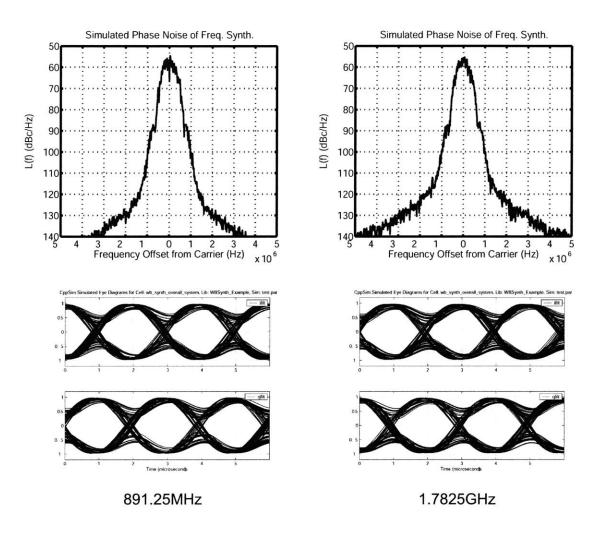

| 5-47 | Simulated Output Spectra and Eyes for 1Mb/s GMSK Modulated              |      |

|      | PFD/DAC Synthesizer                                                     | 154  |

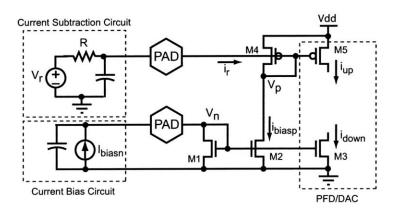

| 6-1  | Mismatch Compensated PFD/DAC Circuit Block                              | 156  |

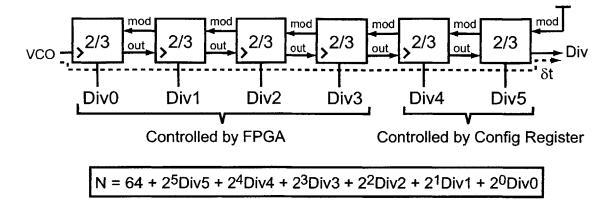

| 6-2  | High-Speed, Asynchronous, Multi-Modulus Divider                         | 157  |

| 6-3  | Synchronization in a Digital System                                     | 158  |

| 6-4  | Divider Retiming Circuitry                                              | 159  |

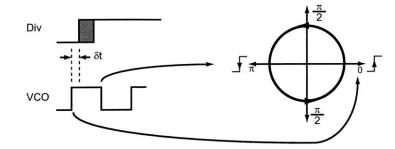

| 6-5  | Mapping the VCO Edges to Phase-space                                    | 160  |

| 6-6  | Mapping the Divider signal to Phase-space                               | 160  |

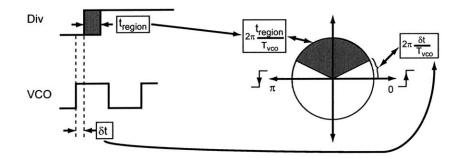

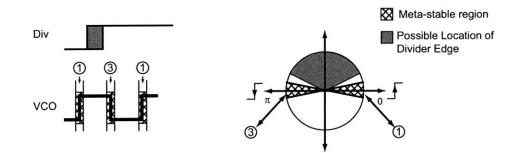

| 6-7  | Mapping the Meta-stable Timing Regions to Phase-space                   | 161  |

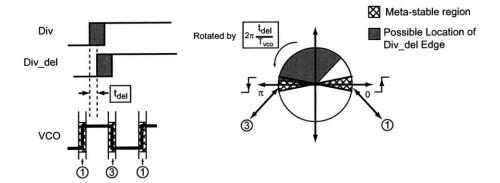

| 6-8  | Mapping the Delayed Divider Signal to Phase-space                       | 161  |

| 6-9  | Phase Space Explanation of the Divider Retimer Circuit                                  | 163 |

|------|-----------------------------------------------------------------------------------------|-----|

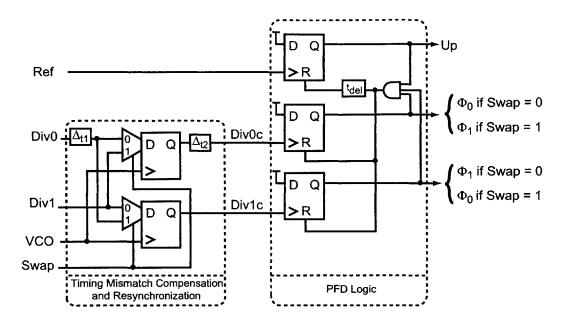

| 6-10 | Timing Compensation and Resynchronization Block and $\ensuremath{PFD}$ Logic .          | 165 |

| 6-11 | High Speed Differential Flip-Flop with Muxed Input Stage and State                      |     |

|      | Mismatch Compensation                                                                   | 166 |

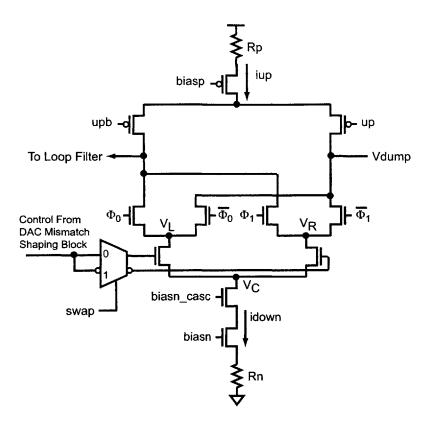

| 6-12 | PFD/DAC Unit Element                                                                    | 167 |

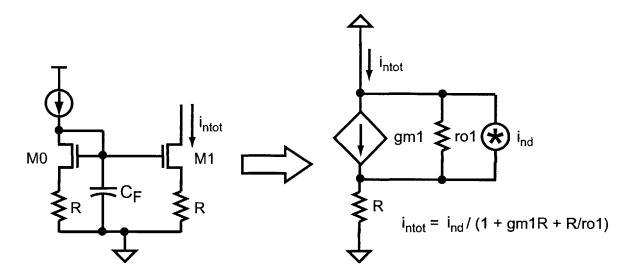

| 6-13 | Resistive Degeneration for Reduced Current Source Noise                                 | 168 |

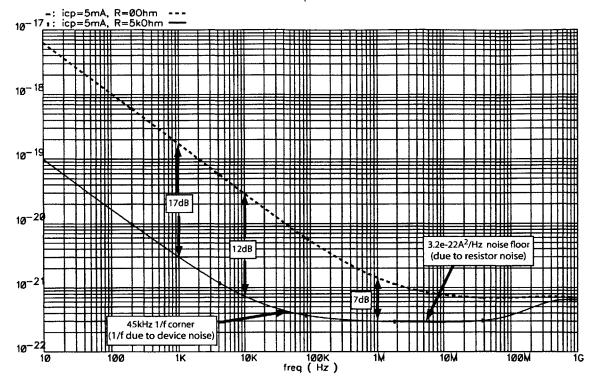

| 6-14 | Hspice Simulation of Charge-pump Noise With and Without Resistor                        |     |

|      | Degeneration                                                                            | 169 |

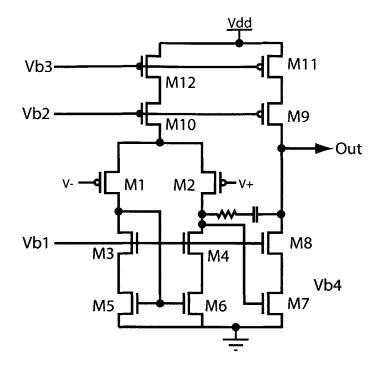

| 6-15 | Loop Filter Op-amp                                                                      | 172 |

| 6-16 | Unity Gain Inverting Amplifier                                                          | 174 |

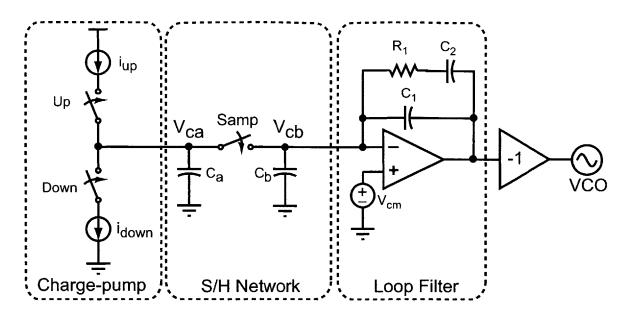

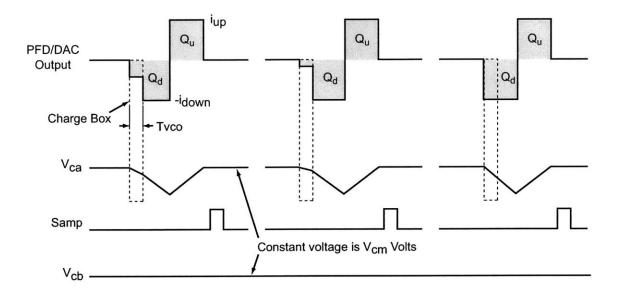

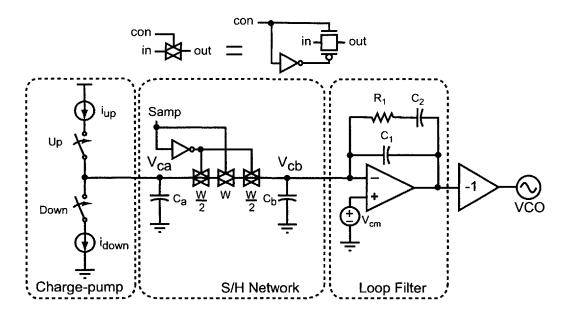

| 6-17 | Proposed Sample-and-hold Loop Filter                                                    | 176 |

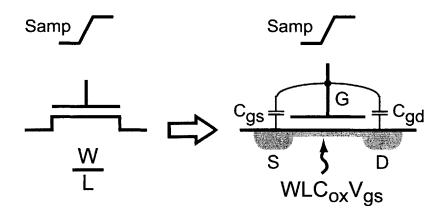

| 6-18 | Employing a Sample-and-hold to Eliminate Shape Mismatch                                 | 177 |

| 6-19 | Proposed Sample-and-hold Loop Filter                                                    | 179 |

| 6-20 | Charge Injection Mechanisms in the S/H Switches                                         | 179 |

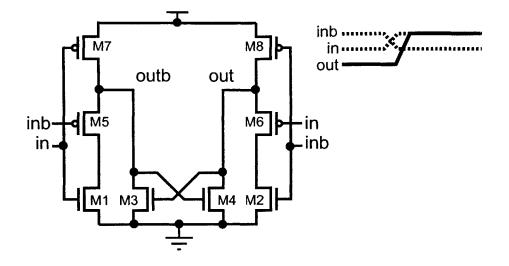

| 6-21 | Differential to Single-ended Converter                                                  | 181 |

| 6-22 | Hspice Simulation of Differential to Single Ended Converter                             | 182 |

| 6-23 | Input Buffer and Single-ended to Differential Converter used for VCO                    |     |

|      | and Reference Inputs                                                                    | 183 |

| 6-24 | Band Select Divider                                                                     | 184 |

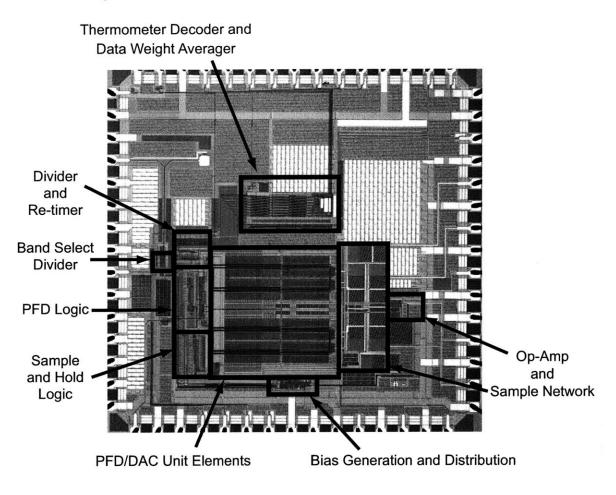

| 6-25 | $\label{eq:match} \mbox{Mismatch Compensated PFD/DAC Synthesizer Chip Microphotograph}$ | 185 |

| 7-1  | Prototype PFD/DAC Synthesizer                                                           | 188 |

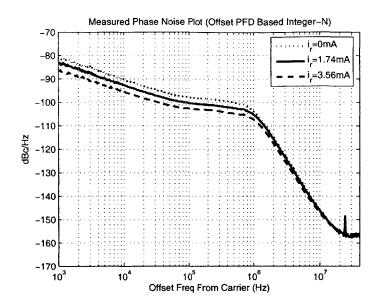

| 7-2  | Measured Phase Noise Plot for Integer-N Synthesizer                                     | 191 |

| 7-3  | Measured Vs. Calculated Performance                                                     | 192 |

| 7-4  | PFD Jitter Induced Noise Sources                                                        | 193 |

| 7-5  | Reference Buffer Jitter and Proposed Solution                                           | 194 |

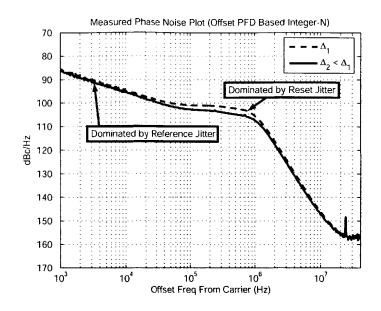

| 7-6  | Measured Phase Noise Plot for Integer-N Synthesizer                                     | 195 |

| 7-7  | Reducing Reset Jitter Induced Phase Noise in the Offset Tri-state PFD                   | 196 |

| 7-8  | Lowering $i_{up}$ to Reduce Reset Jitter Induced Phase Noise                            | 196 |

| 7-9  | Offset PFD Synthesizer Measured Phase Noise With Current Subtraction                    | 197 |

| 7-10 | Measured Phase Noise While Varying the Reset Pulse-width                   | 198 |

|------|----------------------------------------------------------------------------|-----|

| 7-11 | Analytical Model and Measured Performance for Extraction of Refer-         |     |

|      | ence Jitter                                                                | 199 |

| 7-12 | Measured Phase Noise: PFD/DAC Synthesizer Vs. Integer-N Synthe-            |     |

|      | sizer                                                                      | 200 |

| 7-13 | PFD/DAC Logic and Timing Block                                             | 201 |

| 7-14 | Extraction of Timing Mismatch in the PFD/DAC Using the Analytical          |     |

|      | Model                                                                      | 202 |

| 7-15 | PFD/DAC Synthesize Measured Vs. Calculated Step Response and               |     |

|      | Settling Time                                                              | 203 |

| 7-16 | Measured Performance: PFD/DAC Synthesizer Vs. $\Sigma\Delta$ Synthesizer . | 205 |

| 7-17 | Measured Performance: PFD/DAC Synthesizer Vs. $\Sigma\Delta$ Synthesizer   |     |

|      | With Phase Swapping Disabled                                               | 206 |

| 7-18 | S/H Loop Filter Attenuation of the Reference Spur                          | 207 |

| 7-19 | Measured Spurious Performance                                              | 209 |

| 7-20 | Comparison of Calculated Noise Performance for a 7-bit Vs. 5-bit           |     |

|      | PFD/DAC                                                                    | 212 |

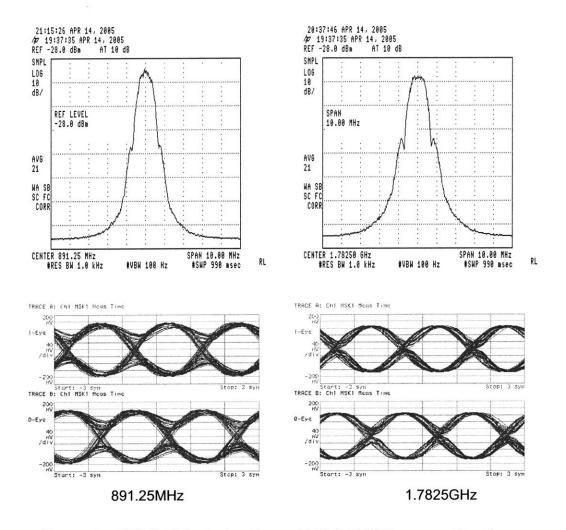

| 7-21 | PFD/DAC Synthesizer Measured 271kb/s GMSK Spectra and Eye Di-              |     |

|      | agrams                                                                     | 214 |

| 7-22 | PFD/DAC Synthesizer Measured 500kb/s GMSK Spectra and Eye Di-              |     |

|      | agrams                                                                     | 215 |

| 7-23 | PFD/DAC Synthesizer Measured 757kb/s GMSK Spectra and Eye Di-              |     |

|      | agrams                                                                     | 216 |

| 7-24 | PFD/DAC Synthesizer Measured 1Mb/s GMSK Spectra and Eye Di-                |     |

|      | agrams                                                                     | 217 |

| A-1  | Chip Bonding Diagram                                                       | 227 |

| B-1  | Configuration Register                                                     | 231 |

| B-2  | Functions Controlled by the general configuration bits of the configu-     |     |

|      | ration register                                                            | 233 |

| B-3 | Bias Circuitry                              | 235 |

|-----|---------------------------------------------|-----|

| B-4 | High-speed, Multi-modulus Divider           | 237 |

| B-5 | Simplified Divider Retimer Schematic        | 237 |

| B-6 | Simplified S/H Pulse Generation Schematic   | 239 |

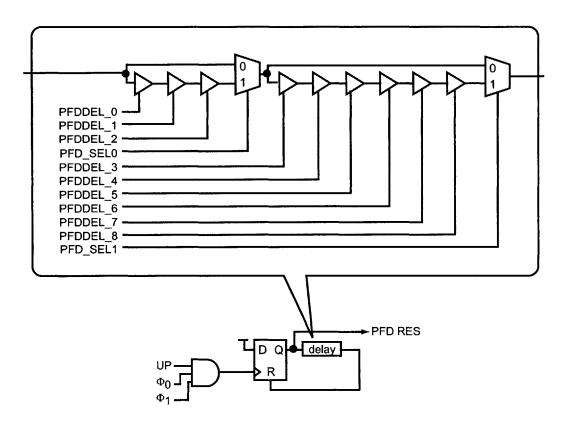

| B-7 | Simplified PFD Logic Reset Pulse Generation | 241 |

# List of Tables

| 5.1 | Nominal Parameter Values for Behavioral Simulations                 | 113 |

|-----|---------------------------------------------------------------------|-----|

| 5.2 | Nominal Noise Parameter Values for Behavioral Simulations           | 117 |

| 6.1 | Op-amp Simulation Results                                           | 173 |

| 7.1 | Prototype Synthesizer Design Parameters                             | 190 |

| 7.2 | Comparison of Synthesizers Employing Active Quantization Noise Can- |     |

|     | cellation (All are implemented in 0.18um CMOS)                      | 210 |

| 7.3 | Summary of PFD/DAC Synthesizer/Transmitter Performance              | 211 |

| A.1 | Chip Pinout                                                         | 226 |

| B.1 | Configuration Register General Function Control Bits                | 232 |

| B.2 | Configuration Register Bias Control Bits                            | 234 |

| B.3 | Configuration Register Divider Retimer Control Bits                 | 236 |

| B.4 | Configuration Register S/H Control Bits                             | 238 |

| B.5 | Configuration Register PFD Control Bits                             | 240 |

## Chapter 1

# Area of Focus: Fractional-N Synthesis

Frequency synthesis is an essential technique employed in RF systems to achieve local oscillator (LO) generation or direct modulation transmission [2]. Fractional-N synthesis offers the advantage over integer-N based systems of decoupling the choice of synthesizer resolution from its bandwidth. Fast settling, high resolution synthesis becomes possible, giving greater design flexibility at the system level. Fractional-N synthesis can be separated into two categories: classical fractional-N synthesis and  $\Sigma\Delta$  fractional-N synthesis.

In this chapter we will explore the tradeoffs associated with the different types of fractional-N synthesis. We will show that the key constraint limiting the bandwidth of modern synthesizers centers around management of fractional-N quantization noise. Quantization noise is introduced to the synthesizer as a by-product of the fractional-N dithering process, and so is unavoidable. After examining existing techniques aimed at lowering the magnitude of quantization noise, we propose a synthesizer architecture that overcomes the core limitation of this prior work, namely achieving a high quality gain match between the quantization noise and a cancellation signal.

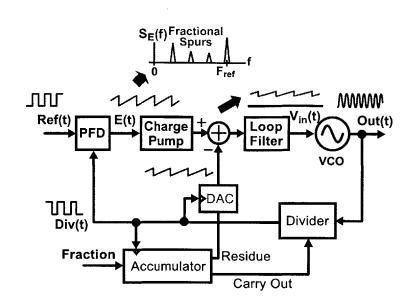

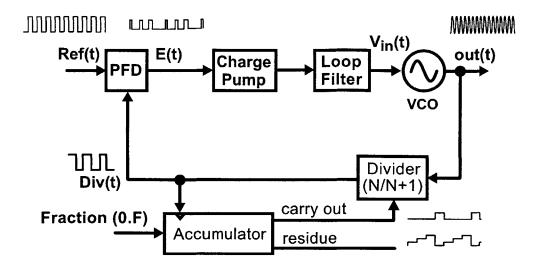

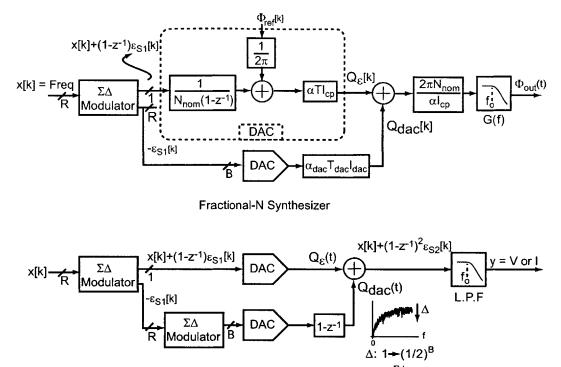

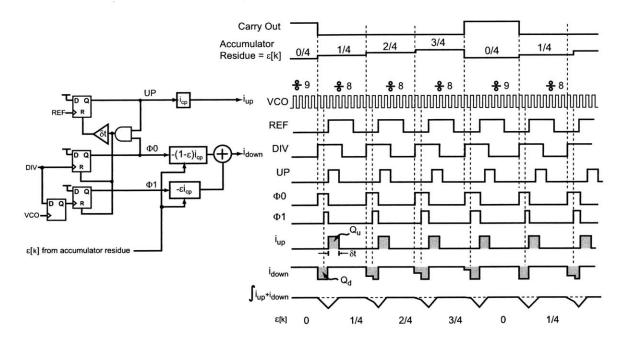

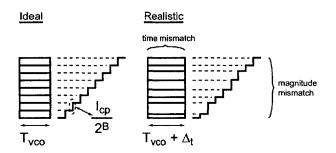

Figure 1-1 Classic Fractional-N Synthesis with Phase Interpolation

### 1.1 The Issue of Fractional-N Quantization Noise

The classical approach to fractional-N synthesizer design employs dithering and phase interpolation, as depicted in Figure 1-1. [3] An accumulator carry out signal is used to dither the control input to a multi-modulus divider such that a fractional average divide value is obtained from a divider that supports integer values. A digital to analog converter (DAC) is used in conjunction with a phase accumulation register to cancel out periodicities in the phase error signal, E(t). These periodicities represent quantization noise introduced by the fractional-N dithering process. The main performance limitation of this approach centers around the difficulty in creating a precise match between the noise cancellation DAC output and the phase error signal.

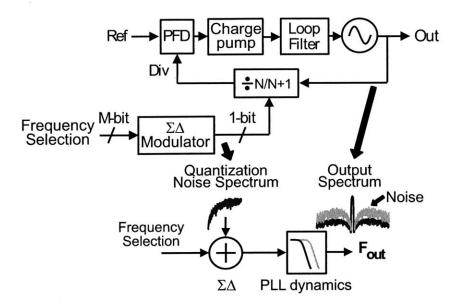

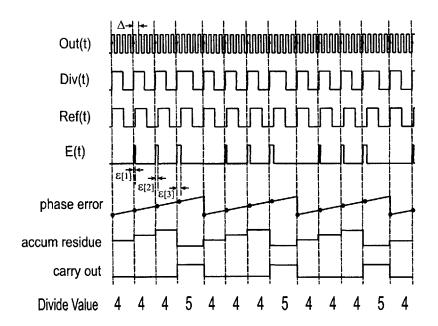

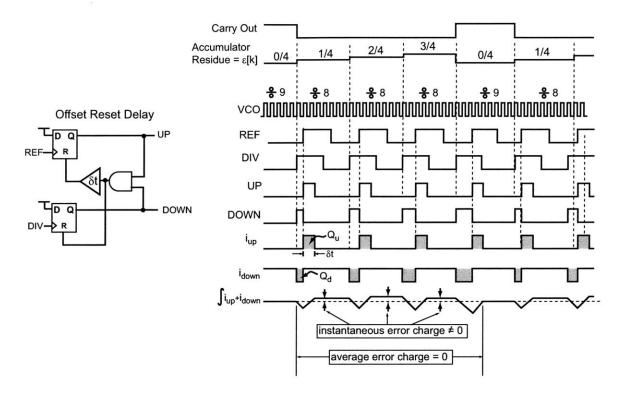

In  $\Sigma\Delta$  fractional-N synthesis, the most popular technique used today to generate fractional divide values [4–9], the spurious performance is improved through  $\Sigma\Delta$ modulation of the divider control. The quantization noise introduced by dithering the divide value is therefore whitened and shaped to high frequencies, such that it is substantially filtered by the synthesizer dynamics. In order to obtain sufficient randomization to reduce spurs to negligible levels,  $\Sigma\Delta$  modulators of order 3 or higher (often employing LSB dithering) are often employed, necessitating a higher order loop filter to counteract increased noise slope. The shaped quantization noise can easily

Figure 1-2  $\Sigma\Delta$  Fractional-N Synthesizer and Noise-Bandwidth Tradeoff

dominate at high offset frequencies, introducing a noise-bandwidth tradeoff which translates to low closed loop bandwidths for low phase-noise synthesizers. Depicted in Figure 1-2, this tradeoff is the bottleneck preventing high bandwidth fractional-N synthesis, and therefore presents an obstacle to achieving the central goal behind fractional-N synthesis, which is to increase synthesizer bandwidth. Bandwidths reported in the literature for  $\Sigma\Delta$  synthesizers are typically below 100kHz for high performance applications [8, 10–14].

## 1.2 Prior Work Aimed at Reducing Fractional-N Quantization Noise

Two approaches have emerged to improve the noise-bandwidth tradeoff. The first involves reducing the quantization step-size of the divide value dithering action through the use of multiple VCO (or divider) phases [15–17]. Introducing multiple VCO phases is the ideal means by which to reduce the quantization step-size. To explain, phase is the system parameter on which a PLL operates, so choosing one of a number of finely spaced VCO phases to clock the divider directly translates to a reduced quantization interval. In a similar manner, multiple divider output phases may be created, though it is still necessary to space these phases by some fraction of a VCO period, since the VCO period is the fundamental quantization step-size in the system.

In practice, the number of VCO or divider phases that can be accurately generated is limited. Phase resolution is often set by a gate delay which, for high frequency outputs, can be a significant fraction of the VCO period. Additionally, to generate multiple phases, either ring oscillators must be used, which have inherently poorer phase noise performance than LC oscillators, or a DLL with all of the associated overhead must be employed [17]. Mismatch between the phases occurs and must be carefully dealt with.

Very recently, a modification has been proposed to the selection logic used in the multi-phase approach of [15]. In this case, very high order  $\Sigma\Delta$  modulation is applied to the phase selection mux in order to make each tap equi-probable in a histogram sense [18]. For the simulated synthesizer proposed in [18], a 7<sup>th</sup> order  $\Sigma\Delta$ modulator was used to randomize the selection of output phase for a 16 phase divider. Noise shaping of this order requires large numbers of extra poles in the loop filter to counteract the increased noise slope of the high order modulator. Additionally, the multi-phase approach is ultimately limited in its ability to reduce broadband phase noise by limitations in creating the delay.

The second approach to reduce the noise-bandwidth tradeoff uses a DAC to cancel the error signal [19,20]. This method builds on the idea behind phase interpolation, but introduces  $\Sigma\Delta$  design techniques to reduce the impact of DAC nonlinearity. The main limitations with this architecture center around achieving a good match between the DAC output and phase error signal. Matching these signals is difficult because they are processed by separate circuits whose outputs are summed. An additional limitation of this technique is that a high resolution DAC is required to achieve high levels of noise cancellation. In [19], a 4 bit coarse DAC and 4 bit fine DAC were used, resulting in 16dB improvement in broadband phase noise and -45dBc fractional spur levels. A similar approach proposed in [20] results in 15dB noise suppression and -60dBc fractional spurs for a 5-bit cancellation DAC.

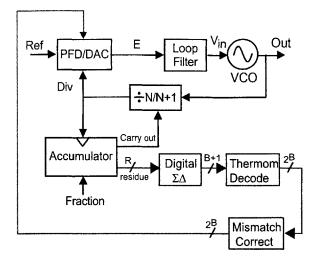

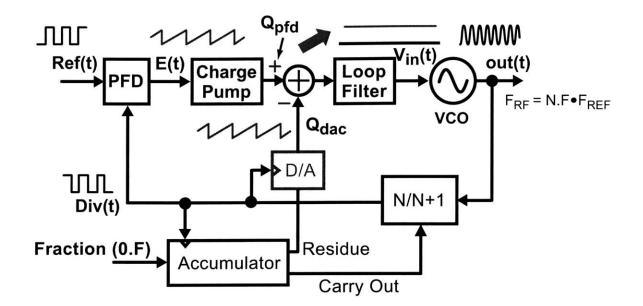

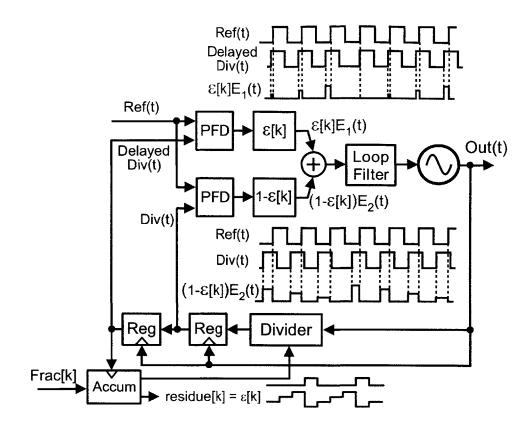

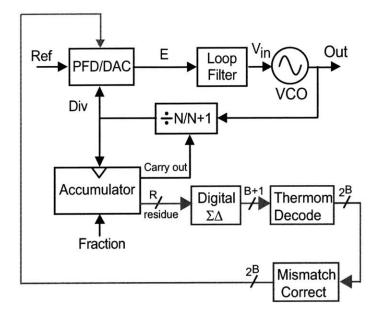

Figure 1-3 Proposed Synthesizer Architecture

An alternative approach that utilizes a DAC to reduce quantization-induced phase noise is proposed in [21]. The separate phase detector and DAC circuit elements are replaced by a hybrid structure, which we will refer to as a PFD/DAC. By embedding the two functions into one circuit, an intrinsically better gain match between the phase error and DAC cancellation signals is obtained. However, the architecture presented in [21] does not address the issue of mismatch between unit elements of the DAC, or between the timing signals in the phase detector, which will result in incomplete phase error signal cancellation and spurious feed-through.

While all of the proposed techniques described above succeed in reducing broadband phase noise levels by effectively reducing the phase quantization step-size, their performance is limited by mismatch between the quantization noise and the cancellation signal.

# 1.3 Proposed Quantization Noise Reduction Technique

To reduce fractional-N quantization noise, we propose the architecture shown in Figure 1-3. The proposed synthesizer leverages advances in noise-shaping DAC design to ease the requirements on the cancellation DAC used by the traditional fractional-N

Figure 1-4 Proposed Mismatch Compensated PFD/DAC

approach. It utilizes a PFD/DAC structure [21] to obtain a good intrinsic gain match between the phase error and DAC cancellation signal. However, this work makes the key contribution of introducing techniques to minimize the impact that PFD/DAC mismatch sources have on phase noise performance. Indeed, matching issues create the bottleneck in previous approaches since they result in error feed-through that is manifested in the phase noise spectrum as large spurs, or increased broadband phase noise. The proposed architecture incorporates several digital signal processing techniques to reduce the impact of non-idealities that occur in the PFD/DAC such as unit element mismatch, timing mismatch, and any residual gain mismatch occurring between the PFD/DAC output and phase error signal.

The key issue with prior fractional-N synthesizer implementations is that the cancellation DAC output and phase error signal are poorly matched. This error is a direct result of the fact that separate circuits have been used to implement the two required blocks. Figure 1-4 depicts the proposed PFD/DAC structure, which greatly reduces mismatch between the two signal paths. The proposed PFD/DAC differs from a prior implementation of a hybrid phase detector/cancellation DAC scheme [21] in that it compensates for mismatches within the PFD/DAC structure itself. As will be discussed, mismatch between magnitudes of the phase error and cancellation is phase information is

Figure 1-5 Calculated Phase Noise

a key consideration for achieving a high quality overall gain match.

## **1.4** Thesis Scope and Contributions

The mismatch compensated PFD/DAC synthesizer improves phase noise performance by reducing fractional-N quantization noise. If *quantization* noise can be lowered significantly, it is possible that it will not have a noticeable impact on overall phase noise performance, and that *intrinsic* noise sources should become the area of design focus for continued bandwidth extension. By intrinsic noise, we mean noise sources that are inherent to any PLL, such as charge-pump device noise, reference jitter, divider jitter, and VCO phase noise.

This thesis proposes techniques which allow low noise, high bandwidth, and fine resolution to be simultaneously achieved by a frequency synthesizer. Both intrinsic noise sources, as well as fractional-N quantization-induced phase noise are investigated. Our primary focus is reducing the quantization noise impact on output phase noise by using the proposed mismatch compensated PFD/DAC synthesizer architecture.

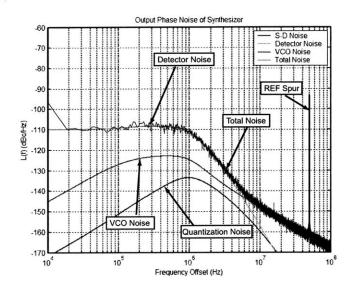

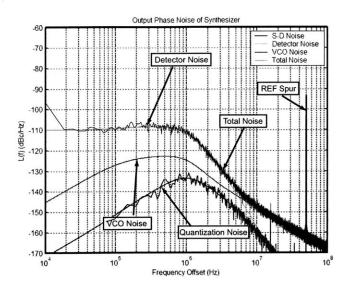

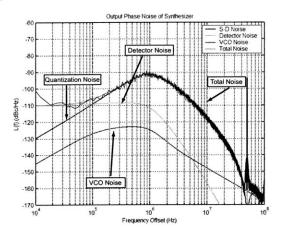

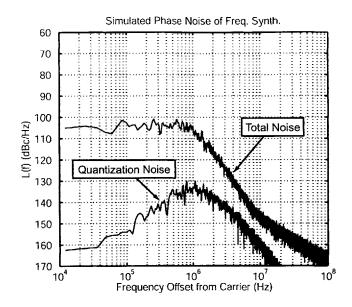

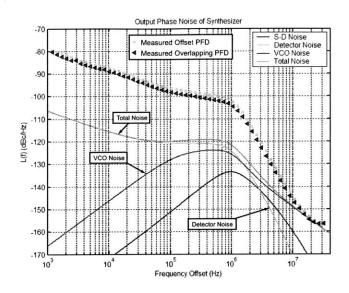

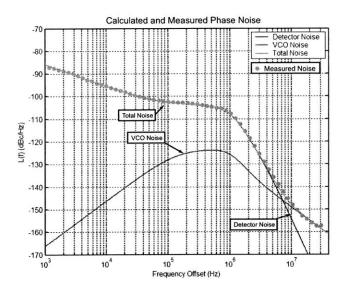

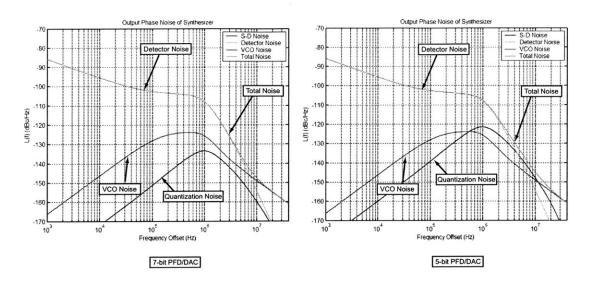

Figure 1-5 shows a calculation of output phase noise for a 1MHz bandwidth fractional-N synthesizer, with each noise source's contribution shown individually. The left plot in the figure clearly shows that, for the case of a  $2^{nd}$  order  $\Sigma\Delta$  synthe-

Figure 1-6 New Model View of Fractional-N Synthesizer as a MASH  $\Sigma\Delta$  DAC

Figure 1-7 PFD/DAC Synthesizer Model

sizer, quantization induced phase noise dominates over a broad frequency range. The right plot shows that, if quantization noise can be reduced by 40dB, the synthesizer noise profile is determined by the *intrinsic* noise sources. Because quantization noise is removed from consideration with respect to output phase noise, the fractional-N synthesizer looks, from a noise standpoint, like an integer-N synthesizer!

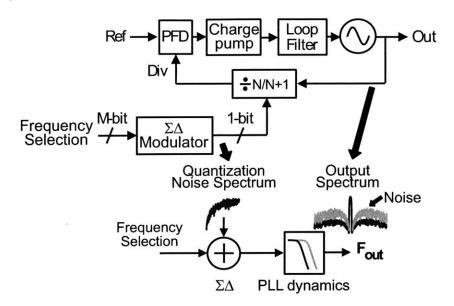

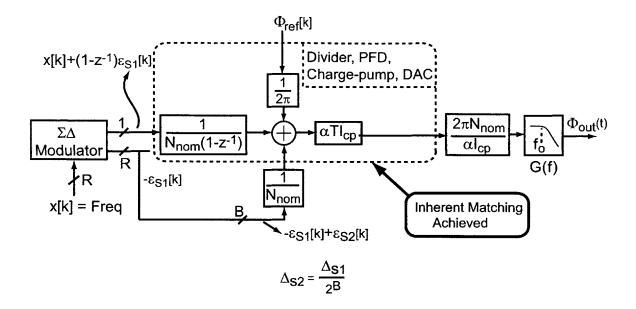

#### 1.4.1 System Analytical Noise Modeling

Our exploration into ways to reduce the impact of fractional-N quantization noise will begin with an examination of the model used for phase noise analysis proposed in [1]. In Chapter 3, we propose re-formatting this noise model to the form depicted in Figure 1-6. The new model view suggests that phase interpolation is both a general case of fractional-N synthesis that is a superset of the synthesizer architectures described in this thesis, as well as being directly analogous to a  $\Sigma\Delta$  DAC. The previously de-

Figure 1-8 Behavioral Model for PFD/DAC Synthesizer

scribed mismatch between the feed-forward cancellation path and the quantization error signal can been seen directly in the figure.

To eliminate the systematic mismatch problem associated with classical phase interpolation based synthesis, we propose the PFD/DAC synthesizer architecture, which can be represented by the model in Figure 1-7. Unlike the approach described in [21], the proposed mismatch compensated PFD/DAC synthesizer introduces dynamic element matching techniques to mitigate circuit mismatch internal to its structure. We will present details of the mismatch compensated PFD/DAC structure in Chapter 4.

#### 1.4.2 Behavioral Modeling and Simulation

Fractional-N synthesizers are difficult systems to simulate because the system dynamics have dominant poles typically on the order of kHz to MHz, while the synthesizer output frequency is usually in the GHz range. Simultaneously capturing transient effects occurring in a fraction of the VCO period and dynamic settling of the loop filter require prohibitively long simulations if performed at the transistor level [22–24].

Figure 1-9 PFD/DAC Technique Charge-box

For this reason, we use the C++ behavioral simulator CppSim described in [23] and freely available at http://www-mtl.mit.edu/researchgroups/perrottgroup/tools.html.

In Chapter 5 we propose behavioral modeling techniques used to capture non-ideal circuit characteristics from transistor level simulations and include them in behavioral simulations. Figure 1-8 depicts the behavioral model used for simulation. We will show good agreement between the results of behavioral simulation and the analytical model, motivating the use of behavioral simulation in complex mixed signal systems such as frequency synthesizers. Perhaps more importantly, we demonstrate that key internal system parameters that are not directly measurable can be back extracted using the analytical model, a powerful new analysis technique that the PLL designer can use for system characterization.

#### 1.4.3 Circuit Design

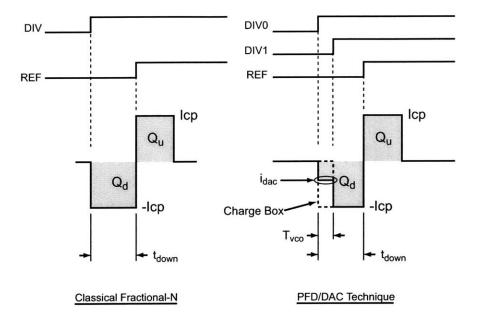

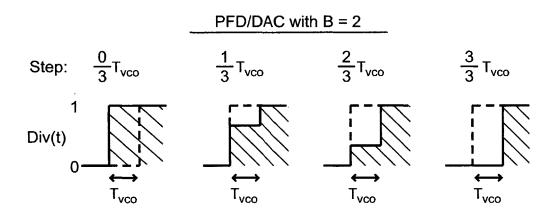

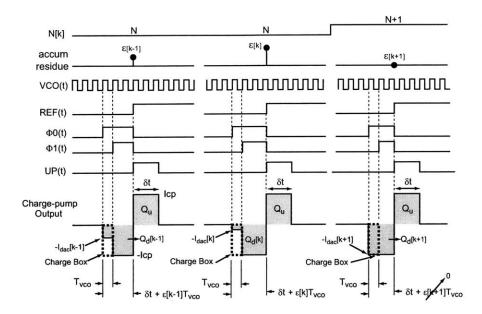

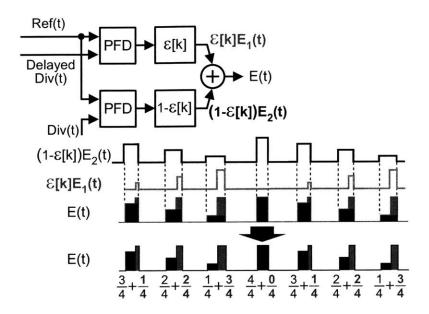

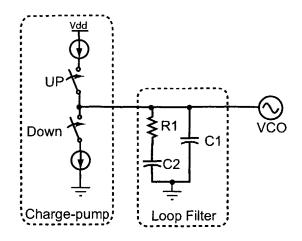

The PFD/DAC technique uses a one VCO period wide charge-box controlled by a DAC to achieve cancellation of the fractional-N quantization noise [25]. A snapshot of PFD/DAC operation is compared to classical fractional-N operation in Figure 1-9. As will be explained in detail in Chapter 4, the phase detector architecture chosen

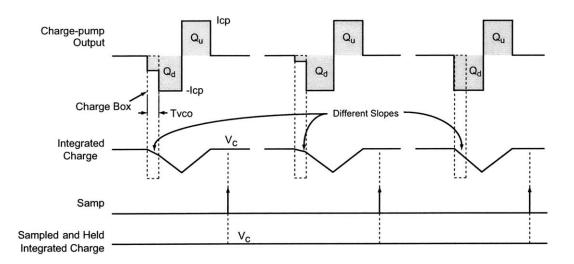

for the PFD/DAC results in steady-state operation where the reference signal, REF, always occurs after the divider, DIV, and produces a constant amount of positive charge  $Q_u$ .

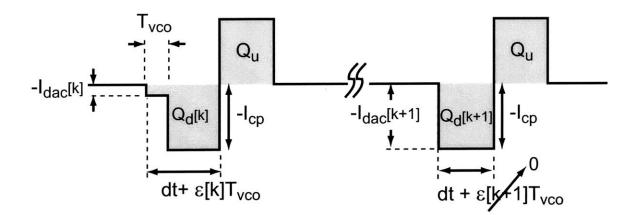

Because the reference operates at a constant frequency, its edge location, ignoring random jitter, will always occur at the same location in time. What is meant here is that the reference signal has a constant period. By contrast, the divider period, and therefore its edge location, will vary over time due to the fractional-N dithering process. The varying divider edge location causes the negative current pulse-width,  $t_{down}$ , to vary over time because  $t_{down}$  is determined by the difference between the divider edge and reference edge. In a classical fractional-N synthesizer, *all* of the charge-pump negative current is delivered at once, and so an instantaneous error charge equal to  $Q_u - Q_d$  is produced. It is important to note that the *average* error charge occurring over several periods will equal zero when the synthesizer is operating in steady-state, but the *instantaneous* error charge on a period-by-period basis will be non-zero. This error charge is due to the fractional-N dithering process and results in fractional spurs.

The PFD/DAC technique controls the value of current delivered in a one VCO period wide window to compensate for the instantaneous phase errors introduced by the fractional-N dithering process. The divider output and a one VCO period delayed version of the divider output create the timing window used to create the charge-box. As negative pulse-width,  $t_{down}$ , changes period-by-period due to dithering, the value of  $i_{dac}$  is changed to compensate such that  $Q_d = Q_u$  every period, and instantaneous charge errors do not occur. The DAC current is referenced to a single VCO period, and therefore changes  $t_{down}$  by some fraction of a VCO period. The fractional-N dithering accumulator contains information about the instantaneous phase error magnitude in its residue [26]. The residue is therefore used to control the DAC output level. A detailed explanation of PFD/DAC operation is given in Chapter 4.

A key merit of the PFD/DAC technique is that, as the VCO period changes with

Figure 1-10 Proposed Mismatch Compensated PFD/DAC

different divide values, the width of the charge-box changes in the same manner. The charge-box therefore tracks the instantaneous phase errors over time, resulting in a high-quality gain match between the quantization error signal (the changing divider edge location and value of  $t_{down}$ ) and the cancellation signal (the changing magnitude of  $i_{doc}$ ).

Accurate generation of the charge-box is key to achieving accurate cancellation of the quantization noise. In Chapter 6 we propose circuit design techniques that enable accurate generation and control of the charge-box.

The charge-box is a single VCO period wide, and since the prototype synthesizer is designed to operate with a 3.6GHz VCO, operation of PFD/DAC circuitry with fast edges is critical. Because the PFD/DAC approach effectively removes quantization noise from overall synthesizer noise performance, other noise sources within the system, such as charge-pump device noise, become dominant. Therefore, low noise circuit design techniques are also proposed in Chapter 6.

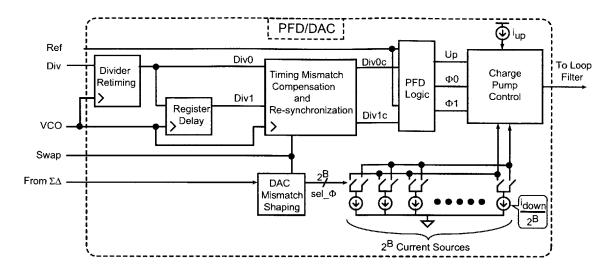

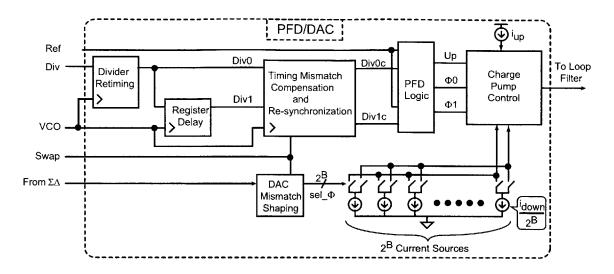

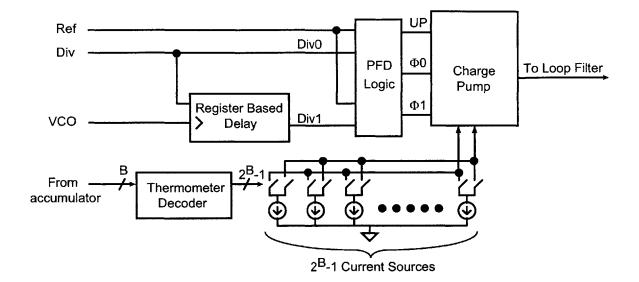

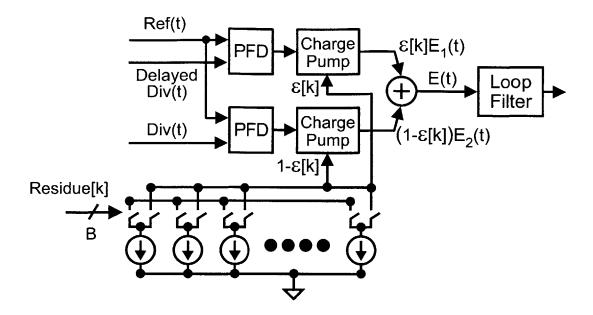

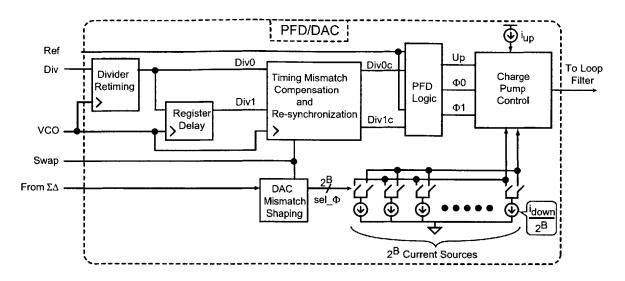

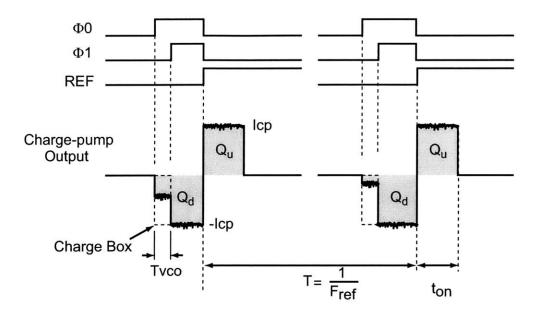

Figure 1-10 shows the proposed mismatch compensated PFD/DAC architecture. Three key circuit blocks are introduced to the basic PFD/DAC structure [21] to compensate for error sources. First, a divider retiming block is used to re-synchronize the divider to the VCO. This establishes the first timing edge, Div0, used to create the charge-box.

Figure 1-11 Proposed Divider Retiming Circuit

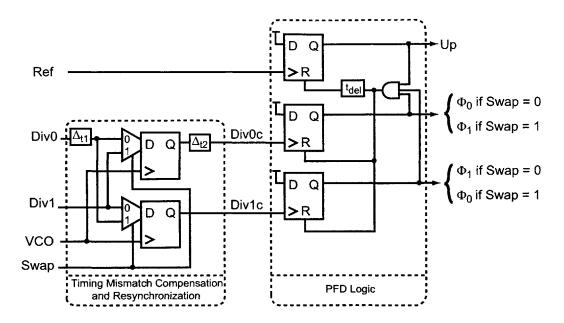

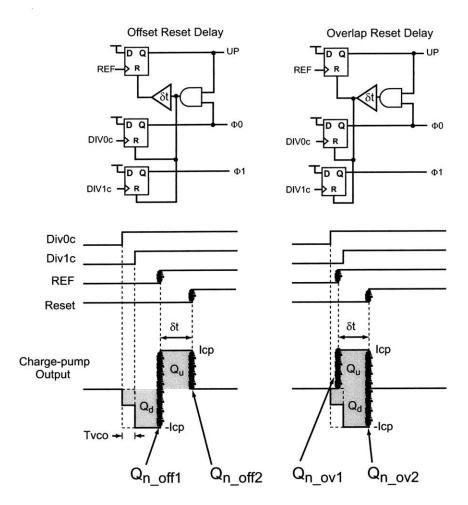

The second edge, Div1, used to create the charge-box is generated by a register delay. Mismatch between the paths seen by Div0 and Div1 is compensated by a timing mismatch block, which dynamically matches the paths, resulting in compensated signals, Div0c and Div1c that are, on average, exactly one VCO period apart. The PFD logic processes Div0c and Div1c and generates two output phase signals,  $\Phi_0$  and  $\Phi_1$ , which combine with the charge-pump circuitry to create the charge-box.

The DAC unit element current sources used to generate the charge-box will have some mismatch between them. This mismatch represents a gain error, and can severely limit noise cancellation. A DAC mismatch shaping block is introduced to dynamically match the unit elements, and improve overall noise performance.

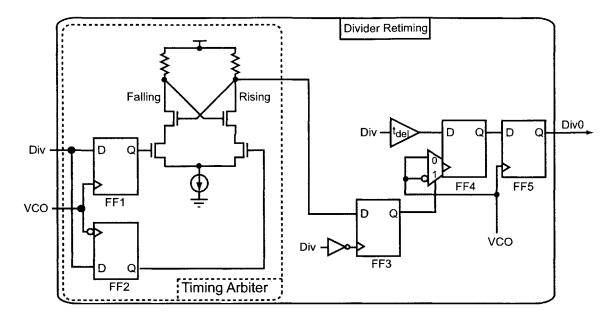

As a preview of the circuit details discussed in Chapter 6, we present our proposed divider retiming circuit in Figure 1-4. For proper operation and timing window duration, the divider output must be synchronized to the VCO. However, high speed multi-modulus dividers used in fractional-N synthesizers are typically asynchronous in nature due to speed and power considerations [27]. The divider output must therefore be synchronized to the VCO *before* the flip-flop delay used to create the PFD/DAC cancellation window.

The proposed approach differs from previous divider retiming techniques [19,28],

Figure 1-12 Measured Phase Noise Comparison of PFD/DAC Synthesizer Vs.  $2^{nd}$  Order  $\Sigma\Delta$  Synthesizer

in that meta-stability at the re-timing flip-flop is determined directly by a high speed arbiter circuit. A simple finite state machine then chooses whether to clock the synchronization flip-flop on the VCO rising or falling edge. A detailed explanation of operation of the re-timing circuit, as well as other high speed, low noise circuit techniques, is presented in Chapter 6.

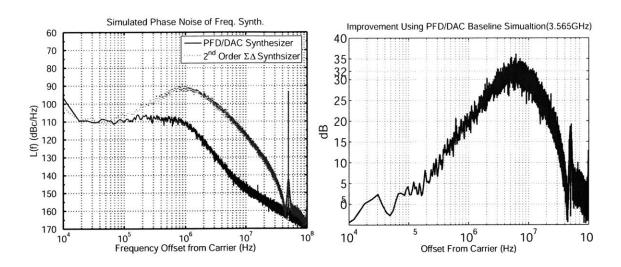

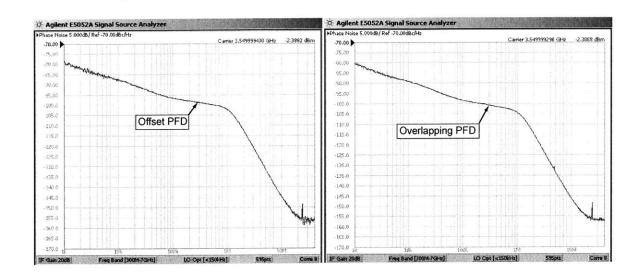

#### 1.4.4 Measured Results

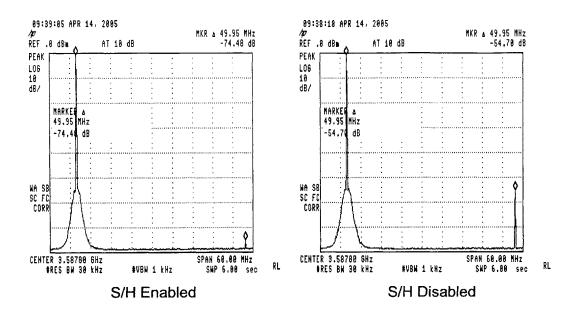

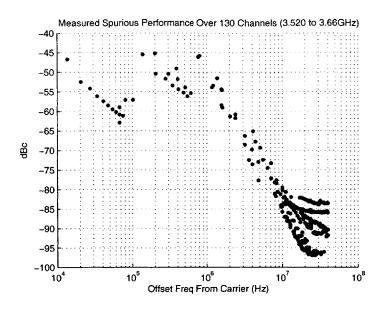

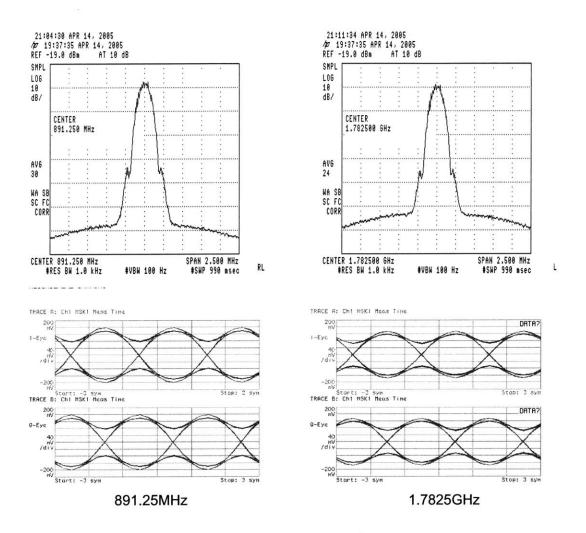

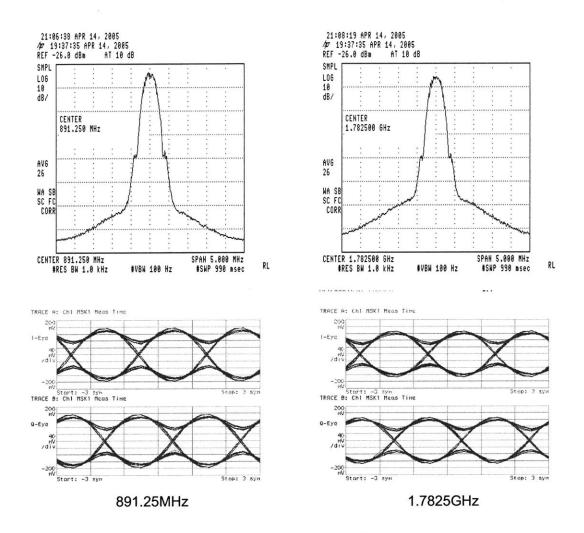

In chapter 7 we present measured results for a 0.18um CMOS IC that implements the proposed mismatch compensated PFD/DAC synthesizer architecture, and compare it with state-of-the-art  $\Sigma\Delta$  fractional-N frequency synthesis. Figure 1-12 shows measured results demonstrating 29dB broadband quantization noise suppression using the proposed mismatch compensated PFD/DAC synthesizer. This high level of noise suppression results in both excellent phase noise performance (-154dBc/Hz at 20MHz offset), and very high (1MHz) synthesizer bandwidth.

When configured as a dual band transmitter, the prototype synthesizer achieves data rates of up to 1Mb/s for a GMSK (Gaussian Minimum Shift Keying) data signal centered at either 1.8GHz or 900MHz.

#### 1.4.5 Thesis Outline

In summary, this thesis presents techniques to dramatically reduce quantization noise in fractional-N synthesizers using a proposed mismatch compensated PFD/DAC architecture. We will present the approach and supporting material in the seven remaining chapters. This thesis is divided into multiple chapters. Chapter 2 provides background for modern fractional-N synthesis techniques. In Chapter 3, a new view of the analytical noise model used for fractional-N synthesizer design is proposed. Chapter 4 builds on this model and presents the proposed architecture for reducing quantization noise. In Chapter 5, behavioral modeling techniques for fractional-N synthesis are presented. Emphasis is given to methods for incorporating circuit nonidealities determined from SPICE level simulations into the behavioral model. Chapter 6 focuses on proposed circuit design techniques for high speed and low noise that enable the PFD/DAC approach. Measured results for a prototype PFD/DAC synthesizer IC are presented and discussed in Chapter 7. Limitations of the prototype system are particularly emphasized. Finally, in Chapter 8 we draw conclusions about the effectiveness of the PFD/DAC technique, and propose areas of future work to further extend synthesizer bandwidth. Our focus will be interpreting the measured results presented in Chapter 7, and examining other recent techniques in the literature. Since quantization noise can be reduced by the PFD/DAC technique to the point where intrinsic noise sources dominate, we will see that reduction of intrinsic noise sources now becomes the focus of future work.

# Chapter 2

## **Frequency Synthesis Background**

In this chapter, we present some background into the history and evolution of frequency synthesizer design. Particular attention is paid to the performance tradeoffs that result from the choice of synthesizer architecture. To motivate the need for frequency synthesis, we begin with a discussion of possible applications.

### 2.1 Motivation for Fractional-N Synthesis

As the information age progresses, an increased emphasis is placed on data transmission and reception technologies. Of particular interest is the wireless application space [6,29–32]. As more personal communication devices (personal digital assistants (PDAs), cell phones, sensor networks, laptop computers, desktop computer local area networks (LANs)) become wireless, increased demands are placed on integrated circuit transceiver designs to achieve higher bandwidths, generate less noise, and be flexible enough to accommodate multiple transmission standards.

#### 2.1.1 Mixer-based Transceivers

One of the biggest challenges in the transceiver space is design of the programmable frequency source required for up-conversion and down conversion of data. Figure 2-1 depicts a typical transceiver architecture used in a cell phone. A transmit/receive

Figure 2-1 Typical RF Transceiver

(T/R) switch selects whether the transmitter is in transmit or receive mode by connecting either the transmit path circuitry or receive path circuitry to the antenna. The unused circuitry is typically shut down to save power.

In receive mode, the antenna output is amplified by a low noise amplifier (LNA), and then mixed with a local oscillator (LO). The mixing process translates the modulated high frequency signal to a low frequency. In the direct conversion transceiver architecture shown in Figure 2-1, the LO frequency is selected to be the same as the carrier frequency of the received signal,  $f_{RF}$ , and so the data is mixed down to DC [33]. The received signal is filtered and converted to a digital signal by analog-to-digital converters (ADCs), and then sent to the baseband processor, which further filters and decodes the data to be used by the system. Typically, the data is de-modulated in quadrature, so parallel I and Q channels are converted by the ADC circuitry.

In transmit mode, the process is reversed. The low frequency baseband data is converted from a digital to analog signal by digital-to-analog converters (DACs) and filtered. The analog data stream is mixed with the programmable LO signal to generate a modulated carrier centered at  $f_{RF}$ , as shown in Figure 2-2. A power amplifier amplifies the signal to a level appropriate for transmission, and is sent to the antenna via the T/R switch.

Figure 2-2 Mixer Up-conversion Operation

The key performance requirements on the LO are threefold. First, it must be programmable at a fine enough resolution to accommodate all channels inside the given band of interest. As an example, for a GSM cell-phone, the LO must span a range from 890MHz to 915MHz in 200kHz increments. Second, the LO has to be able to jump from one channel to another fast enough to accommodate a channel hopping specification. This requirement translates into a high LO bandwidth, and is particularly important in modulation schemes where the output signal is required to hop between channels as part of the modulation. Finally, the LO must satisfy a spectral phase noise mask. This requirement is to ensure that the LO does not corrupt the data, and that the transmitted signal does not act as an overpowering interferer on adjacent channels.

#### 2.1.2 Direct Modulation Transmission

A different approach to data transmission is to directly modulate the frequency synthesizer itself, as shown in Figure 2-3. In this case, the digital input to the frequency synthesizer consists of a constant component to set the channel, plus a varying component due to a filtered digital data signal. The output of the synthesizer is connected to the PA through a buffer. Direct modulation transmission therefore offers the possibility of eliminating the mixers and DAC circuitry shown in Figure 2-1.

The main limitation of direct modulated synthesizers is that the data path passes

Figure 2-3 Direct Modulation Transmitter

through the frequency synthesizer. The low-pass nature of the synthesizer dynamics will filter the data, requiring either a high synthesizer bandwidth, or some pre-filtering to overcome a low synthesizer bandwidth [7,34]. As with a mixer based system, we still require good noise performance and fine frequency resolution. Simultaneously achieving fine frequency resolution, high bandwidth, and low noise is an extremely challenging task, since these constraints often run in direct conflict with one another.

## 2.2 Frequency Synthesis

In this section, we discuss the various frequency synthesizer architectures available for use in a practical system. We also present the drawbacks of each approach, and propose a new technique which de-couples the primary performance tradeoff in modern frequency synthesizer design - namely, a noise-bandwidth tradeoff.

#### 2.2.1 Integer-N Synthesis

Figure 2-4 depicts the most basic synthesizer type, the integer-N frequency synthesizer [3]. To achieve lock, the PLL compares the divider phase (Div) to the reference phase (Ref) via the phase/frequency detector (PFD), produces an error signal, E(t), which is scaled by a charge-pump and filtered by the loop filter, and servos the VCO output with the filtered control signal. The output frequency is determined as:

$$F_{out} = N * F_{ref} \tag{2.1}$$

Figure 2-4 Integer-N Synthesizer

where N is the divider value and  $F_{ref}$  is the reference frequency. For reasons of stability, the closed loop bandwidth of the PLL is chosen to be at least ten times lower than the reference frequency [35]. Since the output resolution of the synthesizer is an integer multiple of  $F_{ref}$ , fine frequency resolution requires a low reference frequency and therefore low PLL bandwidth, and correspondingly slow dynamic response. This resolution-bandwidth tradeoff limits the use of integer-N synthesizers in high performance RF systems.

#### 2.2.2 Fractional-N Synthesis

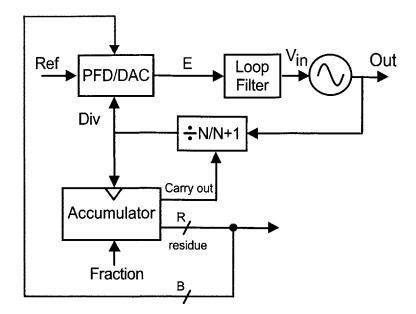

In order to break the resolution-bandwidth tradeoff that exists in integer-N synthesizers, fractional-N synthesis has been introduced [3]. Depicted in Figure 2-5, the fractional-N synthesizer uses a dithering modulator to dynamically vary the divide value. In classical fractional-N synthesis, the dithering modulator is a simple digital accumulator. The accumulator input represents the fractional portion of the divide value. Each reference period, the accumulator increments by a fraction of the fullscale accumulator range. This can be seen in Figure 2-5, where the accumulator residue (the value of its LSBs), increases each period. When the accumulator wraps, the carry out is used to increase the divide value from N to N+1. An *average* divide

Figure 2-5 Classical Fractional-N Synthesizer

value that is fractional is thereby obtained, with the result that

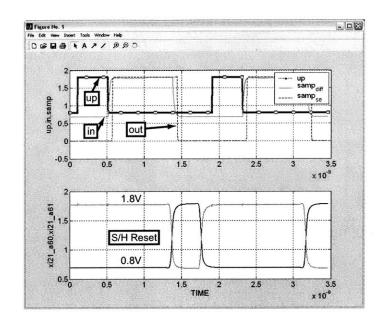

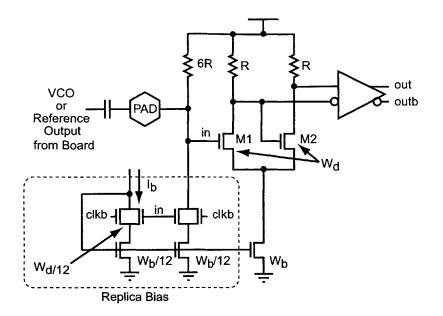

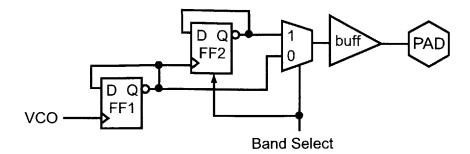

$$F_{out} = N.F * F_{ref} \tag{2.2}$$