# Efficient, Transparent, and Comprehensive Runtime Code Manipulation

by

## Derek L. Bruening

Bachelor of Science, Computer Science and Engineering Massachusetts Institute of Technology, 1998

Master of Engineering, Electrical Engineering and Computer Science Massachusetts Institute of Technology, 1999

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

September 2004

© Massachusetts Institute of Technology 2004. All rights reserved.

| Author       | Department of Electrical Engineering and Computer                                    | r Science            |

|--------------|--------------------------------------------------------------------------------------|----------------------|

|              | September                                                                            | 17, 2004             |

| Certified by |                                                                                      |                      |

|              | Saman Ama<br>Associate Professor of Electrical Engineering and Computer<br>Thesis Su | r Science            |

| Accepted by  |                                                                                      | G G 14               |

|              | Chairman, Departmental Committee on Graduate                                         | C. Smith<br>Students |

|              | MASSACHUSETTS INSTITU<br>OF TECHNOLOGY                                               | TE)                  |

|              | BARKER                                                                               | 1 1                  |

MAR 1 4 2005

\*\*\* **2**

# Efficient, Transparent, and Comprehensive Runtime Code Manipulation

by Derek L. Bruening

Submitted to the Department of Electrical Engineering and Computer Science on September 24, 2004 in partial fulfillment of the requirements for the degree of Doctor of Philosophy

#### **Abstract**

This thesis addresses the challenges of building a software system for general-purpose runtime code manipulation. Modern applications, with dynamically-loaded modules and dynamically-generated code, are assembled at runtime. While it was once feasible at compile time to observe and manipulate every instruction — which is critical for program analysis, instrumentation, trace gathering, optimization, and similar tools — it can now only be done at runtime. Existing runtime tools are successful at inserting instrumentation calls, but no general framework has been developed for fine-grained and comprehensive code observation and modification without high overheads.

This thesis demonstrates the feasibility of building such a system in software. We present *DynamoRIO*, a fully-implemented runtime code manipulation system that supports code transformations on any part of a program, *while it executes*. DynamoRIO uses code caching technology to provide efficient, transparent, and comprehensive manipulation of an unmodified application running on a stock operating system and commodity hardware. DynamoRIO executes large, complex, modern applications with dynamically-loaded, generated, or even modified code. Despite the formidable obstacles inherent in the IA-32 architecture, DynamoRIO provides these capabilities efficiently, with zero to thirty percent time and memory overhead on both Windows and Linux.

DynamoRIO exports an interface for building custom runtime code manipulation tools of all types. It has been used by many researchers, with several hundred downloads of our public release, and is being commercialized in a product for protection against remote security exploits, one of numerous applications of runtime code manipulation.

Thesis Supervisor: Saman Amarasinghe

Title: Associate Professor of Electrical Engineering and Computer Science

## Acknowledgments

I thank my advisor, Professor Saman Amarasinghe, for his boundless energy, immense time commitment to his students, accessibility, and advice. Thanks also go to my readers, Professors Martin Rinard, Frans Kaashoek, and Arvind, for their time and insightful feedback.

Several students at MIT contributed significantly to the DynamoRIO project. I would like to thank Vladimir Kiriansky for his fresh insights and competent approach. He was the primary inventor of program shepherding. He also came up with and implemented our open-address hashtable, and proposed our current method of performing arithmetic operations without modifying the condition codes. Thank-yous go also to Timothy Garnett for his contributions to our dynamic optimizations and to the interpreter project, as well as his help with the DynamoRIO release; to Iris Baron and Greg Sullivan, who spearheaded the interpreter project; and to Josh Jacobs, for implementing hardware performance counter profiling for DynamoRIO.

I would like to thank the researchers at Hewlett-Packard's former Cambridge laboratory. DynamoRIO's precursor was the Dynamo dynamic optimization system [Bala et al. 2000], developed at Hewlett-Packard. Vas Bala and Mike Smith built an initial dynamic optimization framework on IA-32, while Giuseppe Desoli gave valuable early advice on Windows details. I would like to especially thank Evelyn Duesterwald and Josh Fisher for facilitating the source code contract between MIT and Hewlett-Packard that made the DynamoRIO project possible. Evelyn gave support throughout and was instrumental in enabling us to release our work to the public as part of the Hewlett-Packard-MIT Alliance.

I also extend thanks to Sandy Wilbourn and Nand Mulchandani, for understanding and aiding my return to school to finish my thesis.

Last but not least, special thanks to my wife, Barb, for her innumerable suggestions, invaluable help, homemade fruit pies, and moral support.

This research was supported in part by Defense Advanced Research Projects Agency awards DABT63-96-C-0036, N66001-99-2-891702, and F29601-01-2-0166, and by a grant from LCS Project Oxygen.

# **Contents**

| 1 | Intr | troduction 2                                    |    |  |

|---|------|-------------------------------------------------|----|--|

|   | 1.1  | Goals                                           | 22 |  |

|   | 1.2  | DynamoRIO                                       | 24 |  |

|   | 1.3  | Contributions                                   | 26 |  |

| 2 | Cod  | e Cache                                         | 29 |  |

|   | 2.1  | Basic Blocks                                    | 31 |  |

|   | 2.2  | Linking                                         | 34 |  |

|   | 2.3  | Traces                                          | 37 |  |

|   |      | 2.3.1 Trace Shape                               | 39 |  |

|   |      | 2.3.2 Trace Implementation                      | 43 |  |

|   |      | 2.3.3 Alternative Trace Designs                 | 50 |  |

|   | 2.4  | Eliding Unconditional Control Transfers         | 53 |  |

|   |      | 2.4.1 Alternative Super-block Designs           | 57 |  |

|   | 2.5  | Chapter Summary                                 | 57 |  |

| 3 | Trar | nsparency                                       | 59 |  |

|   | 3.1  | Resource Usage Conflicts                        | 60 |  |

|   |      | 3.1.1 Library Transparency                      | 60 |  |

|   |      | 3.1.2 Heap Transparency                         | 62 |  |

|   |      | 3.1.3 Input/Output Transparency                 | 62 |  |

|   |      | 3.1.4 Synchronization Transparency              | 62 |  |

|   | 3.2  | Leaving The Application Unchanged When Possible | 63 |  |

|   |      | 3.2.1 Thread Transparency                       | 63 |  |

|   |      | 3.2.2    | Executable Transparency                             |

|---|------|----------|-----------------------------------------------------|

|   |      | 3.2.3    | Data Transparency                                   |

|   |      | 3.2.4    | Stack Transparency                                  |

|   | 3.3  | Preten   | ding The Application Is Unchanged When It Is Not    |

|   |      | 3.3.1    | Cache Consistency                                   |

|   |      | 3.3.2    | Address Space Transparency                          |

|   |      | 3.3.3    | Application Address Transparency                    |

|   |      | 3.3.4    | Context Translation                                 |

|   |      | 3.3.5    | Error Transparency                                  |

|   |      | 3.3.6    | Timing Transparency                                 |

|   |      | 3.3.7    | Debugging Transparency                              |

|   | 3.4  | Chapte   | r Summary                                           |

| 4 | Arcl | hitectur | al Challenges 71                                    |

|   | 4.1  | Compl    | ex Instruction Set                                  |

|   |      | 4.1.1    | Adaptive Level-of-Detail Instruction Representation |

|   |      | 4.1.2    | Segments                                            |

|   |      | 4.1.3    | Reachability                                        |

|   | 4.2  | Return   | Instruction Branch Prediction                       |

|   |      | 4.2.1    | Code Cache Return Addresses                         |

|   |      | 4.2.2    | Software Return Stack                               |

|   | 4.3  | Hashta   | ble Lookup                                          |

|   |      | 4.3.1    | Indirect Jump Branch Prediction                     |

|   |      | 4.3.2    | Lookup Routine Optimization                         |

|   |      | 4.3.3    | Data Cache Pressure                                 |

|   | 4.4  | Conditi  | ion Codes                                           |

|   | 4.5  | Instruc  | tion Cache Consistency                              |

|   |      | 4.5.1    | Proactive Linking                                   |

|   | 4.6  | Hardwa   | are Trace Cache                                     |

|   | 4.7  |          | t Switch                                            |

|   | 4.8 | Re-targetability                   |

|---|-----|------------------------------------|

|   | 4.9 | Chapter Summary                    |

| 5 | Ope | rating System Challenges 107       |

|   | 5.1 | Target Operating Systems           |

|   |     | 5.1.1 Windows                      |

|   |     | 5.1.2 Linux                        |

|   | 5.2 | Threads                            |

|   |     | 5.2.1 Scratch Space                |

|   |     | 5.2.2 Thread-Local State           |

|   |     | 5.2.3 Synchronization              |

|   | 5.3 | Kernel-Mediated Control Transfers  |

|   |     | 5.3.1 Callbacks                    |

|   |     | 5.3.2 Asynchronous Procedure Calls |

|   |     | 5.3.3 Exceptions                   |

|   |     | 5.3.4 Other Windows Transfers      |

|   |     | 5.3.5 Signals                      |

|   |     | 5.3.6 Thread and Process Creation  |

|   |     | 5.3.7 Inter-Process Communication  |

|   |     | 5.3.8 Systematic Code Discovery    |

|   | 5.4 | System Calls                       |

|   | 5.5 | Injection                          |

|   |     | 5.5.1 Windows                      |

|   |     | 5.5.2 Linux                        |

|   | 5.6 | Chapter Summary                    |

| 6 | Men | nory Management 143                |

|   | 6.1 | Storage Requirements               |

|   |     | 6.1.1 Cache Management Challenges  |

|   |     | 6.1.2 Thread-Private Versus Shared |

|   | 6.2 | Code Cache Consistency             |

|   |      | 6.2.1  | Memory Unmapping                    | 47 |

|---|------|--------|-------------------------------------|----|

|   |      | 6.2.2  | Memory Modification                 | 48 |

|   |      | 6.2.3  | Self-Modifying Code                 | 50 |

|   |      | 6.2.4  | Memory Regions                      | 53 |

|   |      | 6.2.5  | Mapping Regions to Fragments        | 54 |

|   |      | 6.2.6  | Invalidating Fragments              | 56 |

|   |      | 6.2.7  | Consistency Violations              | 57 |

|   |      | 6.2.8  | Non-Precise Flushing                | 58 |

|   |      | 6.2.9  | Impact on Cache Capacity            | 59 |

|   | 6.3  | Code C | Cache Capacity                      | 50 |

|   |      | 6.3.1  | Eviction Policy                     | 51 |

|   |      | 6.3.2  | Cache Size Effects                  | 54 |

|   |      | 6.3.3  | Adaptive Working-Set-Size Detection | 58 |

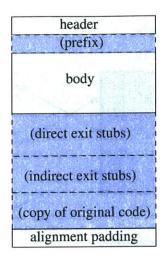

|   |      | 6.3.4  | Code Cache Layout                   | 74 |

|   |      | 6.3.5  | Compacting the Working Set          | 77 |

|   | 6.4  | Heap N | Management                          | 30 |

|   |      | 6.4.1  | Internal Allocation                 |    |

|   |      | 6.4.2  | Data Structures                     | 32 |

|   | 6.5  | Evalua | tion                                | 36 |

|   | 6.6  | Chapte | r Summary                           | 39 |

| 7 | Perf | ormanc | e 19                                | 12 |

| • | 7.1  |        | nark Suite                          |    |

|   | 7.1  | 7.1.1  |                                     |    |

|   | 7.2  |        | Measurement Methodology             |    |

|   | 1.2  |        | Paralidarya of Oracle 19            |    |

|   |      | 7.2.1  | Breakdown of Overheads              |    |

|   |      | 7.2.2  | Impact of System Components         |    |

|   | 7.3  |        | ng Tools                            |    |

|   |      | 7.3.1  | Program Counter Sampling            | )4 |

|   |      | 7.3.2  | Hardware Performance Counters       | )7 |

|   |             | 7.3.3     | Trace Profiling                             |

|---|-------------|-----------|---------------------------------------------|

|   | 7.4         | Chapte    | r Summary                                   |

| 8 | Inte        | rface for | Custom Code Manipulation 217                |

|   | 8.1         | Clients   |                                             |

|   |             | 8.1.1     | Application Control                         |

|   |             | 8.1.2     | Client Hooks                                |

|   | 8.2         | Runtin    | ne Code Manipulation API                    |

|   |             | 8.2.1     | Instruction Manipulation                    |

|   |             | 8.2.2     | General Code Transformations                |

|   |             | 8.2.3     | Inspecting and Modifying Existing Fragments |

|   |             | 8.2.4     | Custom Traces                               |

|   |             | 8.2.5     | Custom Exits and Entrances                  |

|   |             | 8.2.6     | Instrumentation Support                     |

|   |             | 8.2.7     | Sideline Interface                          |

|   |             | 8.2.8     | Thread Support                              |

|   |             | 8.2.9     | Transparency Support                        |

|   | 8.3         | Examp     | ole Clients                                 |

|   |             | 8.3.1     | Call Profiling                              |

|   |             | 8.3.2     | Inserting Counters                          |

|   |             | 8.3.3     | Basic Block Size Statistics                 |

|   | 8.4         | Client    | Limitations                                 |

|   | 8.5         | Chapte    | er Summary                                  |

| 9 | App         | lication  | Case Studies 239                            |

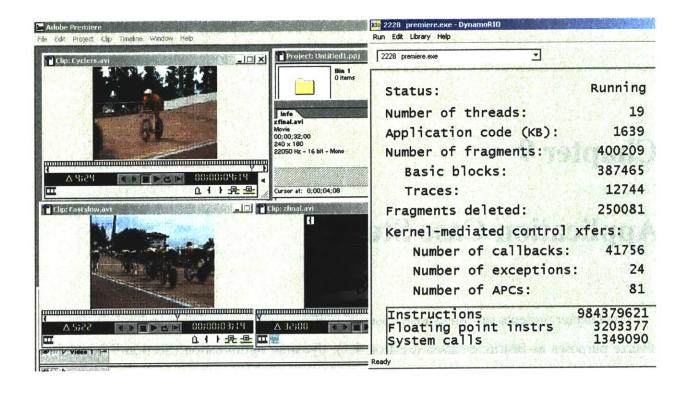

|   | 9.1         |           | nentation of Adobe Premiere                 |

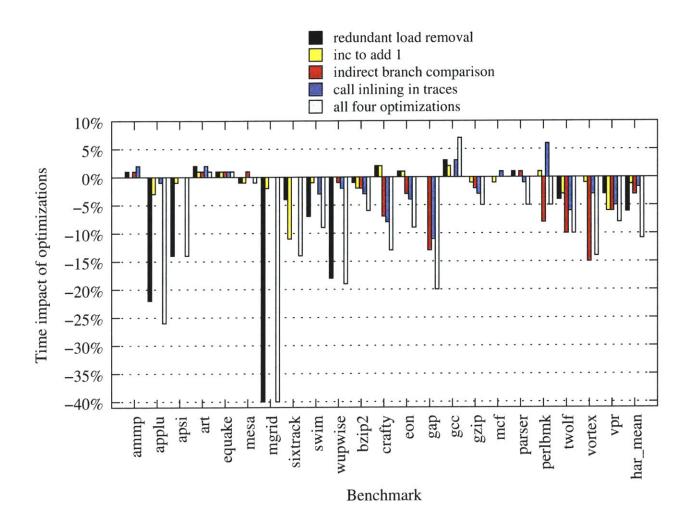

|   | 9.2         |           | nic Optimization                            |

|   | J. <b>2</b> | 9.2.1     | Redundant Load Removal                      |

|   |             | 9.2.2     | Strength Reduction                          |

|   |             | 9.2.3     | Indirect Branch Dispatch                    |

|   |             |           | Inlining Calls with Custom Traces           |

|    |       | 9.2.5    | Experimental Results              |

|----|-------|----------|-----------------------------------|

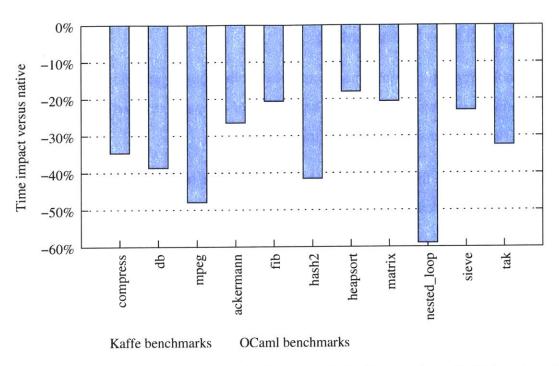

|    | 9.3   | Interpre | eter Optimization                 |

|    |       | 9.3.1    | The Logical Program Counter       |

|    |       | 9.3.2    | Instrumenting the Interpreter     |

|    |       | 9.3.3    | Logical Trace Optimization        |

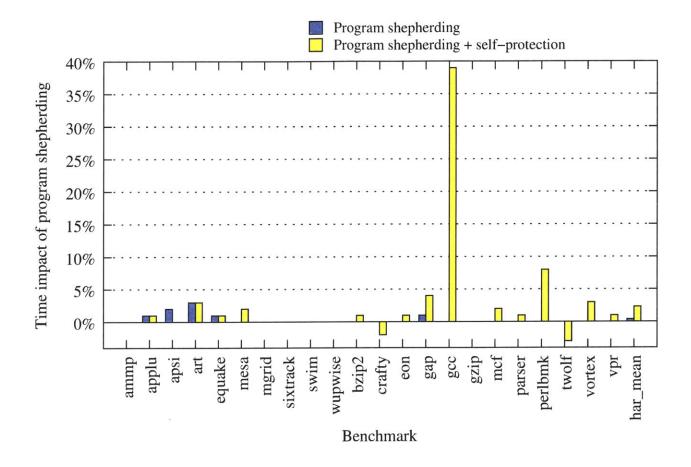

|    | 9.4   | Prograi  | m Shepherding                     |

|    |       | 9.4.1    | Execution Model                   |

|    |       | 9.4.2    | Program Shepherding Components    |

|    |       | 9.4.3    | Security Policies                 |

|    |       | 9.4.4    | Calling Convention Enforcement    |

|    |       | 9.4.5    | Protecting DynamoRIO Itself       |

|    | 9.5   | Chapte   | r Summary                         |

| 10 | Relat | ted Wor  | ·k 267                            |

|    | 10.1  | Related  | 1 Systems                         |

|    |       |          | Runtime Code Manipulation         |

|    |       |          | Binary Instrumentation            |

|    |       |          | Hardware Simulation and Emulation |

|    |       |          | Binary Translation                |

|    |       |          | Binary Optimization               |

|    |       |          | Dynamic Compilation               |

|    | 10.2  |          | Technology                        |

|    |       |          | Code Cache                        |

|    |       |          | Transparency                      |

|    |       |          | Architectural Challenges          |

|    |       |          | Operating System Challenges       |

|    |       |          | Code Cache Consistency            |

|    |       |          | Code Cache Capacity               |

|    |       |          | Tool Interfaces                   |

|    |       |          | Security                          |

|    |       |          |                                   |

|    | 10.3 Chapter Summary               | 285 |

|----|------------------------------------|-----|

| 11 | Conclusions and Future Work        | 287 |

|    | 11.1 Discussion                    | 287 |

|    | 11.2 Future Work                   | 288 |

|    | 11.2.1 Memory Reduction            | 288 |

|    | 11.2.2 Client Interface Extensions | 289 |

|    | 11.2.3 Sideline Operation          | 289 |

|    | 11.2.4 Dynamic Optimization        | 290 |

|    | 11.2.5 Hardware Support            | 290 |

|    | 11.2.6 Tools                       | 291 |

|    | 11.3 Summary                       | 291 |

# **List of Figures and Tables**

| 1.1  | The components of a modern web server                                        | 22 |

|------|------------------------------------------------------------------------------|----|

| 1.2  | The runtime code manipulation layer                                          | 23 |

| 1.3  | Operation of DynamoRIO                                                       | 25 |

| 2.1  | DynamoRIO flow chart                                                         | 30 |

| 2.2  | Performance summary of fundamental DynamoRIO components                      | 30 |

| 2.3  | Example application basic block                                              | 31 |

| 2.4  | Example basic block in code cache                                            | 32 |

| 2.6  | Performance of a basic block cache system                                    | 32 |

| 2.5  | Basic block size statistics                                                  | 33 |

| 2.7  | Linking of direct branches                                                   | 34 |

| 2.8  | Performance impact of linking direct control transfers                       | 35 |

| 2.9  | Performance impact of separating direct exit stubs                           | 37 |

| 2.10 | Performance impact of linking indirect control transfers                     | 38 |

| 2.11 | Performance impact of traces                                                 | 39 |

| 2.12 | Building traces from basic blocks                                            | 40 |

| 2.13 | Performance impact of using the NET trace building scheme                    | 41 |

| 2.14 | Trace cache size increase from DynamoRIO's changes to NET                    | 42 |

| 2.15 | Trace shape statistics                                                       | 44 |

| 2.16 | Trace coverage and completion statistics                                     | 45 |

| 2.17 | Methods of incrementing trace head counters                                  | 46 |

| 2.19 | Performance impact of incrementing trace head counters inside the code cache | 47 |

| 2.18 | Code cache exit statistics                                                   | 48 |

| 2.20 | Reversing direction of a conditional branch in a trace                             | 50 |

|------|------------------------------------------------------------------------------------|----|

| 2.21 | Example supertraces                                                                | 51 |

| 2.23 | Cache size increase of eliding unconditionals                                      | 54 |

| 2.24 | Basic block size statistics for eliding                                            | 55 |

| 2.22 | Performance impact of eliding unconditionals                                       | 56 |

| 2.25 | Pathological basic block                                                           | 57 |

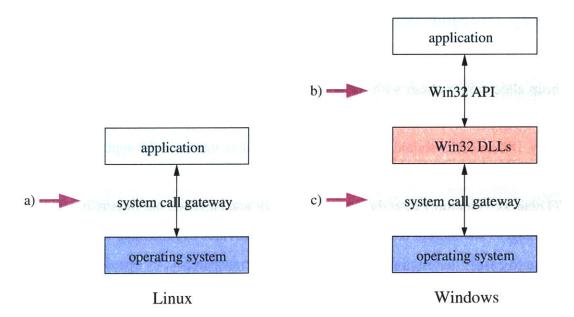

| 3.1  | Operating system interfaces                                                        | 61 |

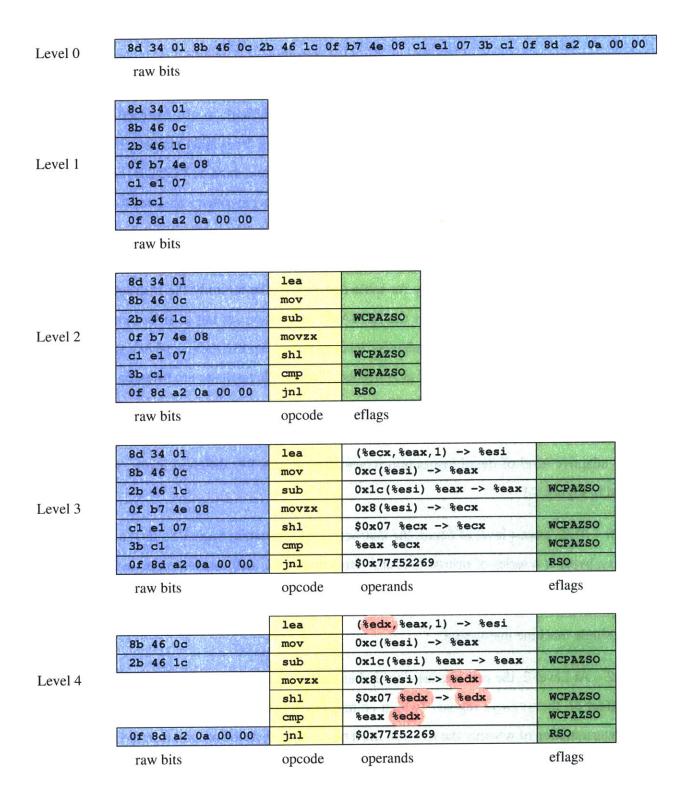

| 4.1  | Levels of instruction representation                                               | 74 |

| 4.2  | Performance of instruction levels                                                  | 77 |

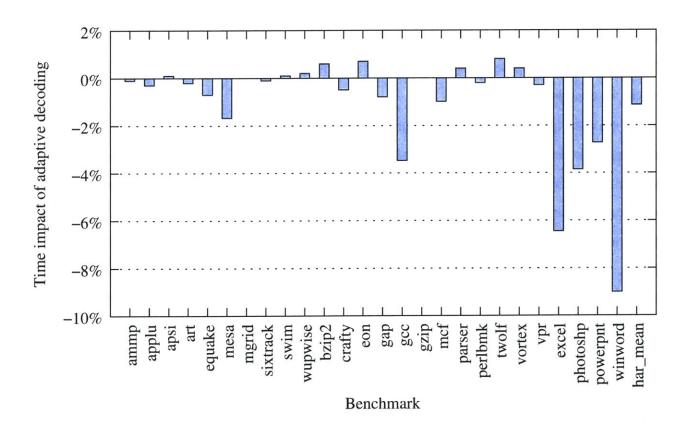

| 4.3  | Performance impact of decoding instructions as little as possible                  | 77 |

| 4.4  | Transformation of eight-bit branches that have no 32-bit counterpart               | 79 |

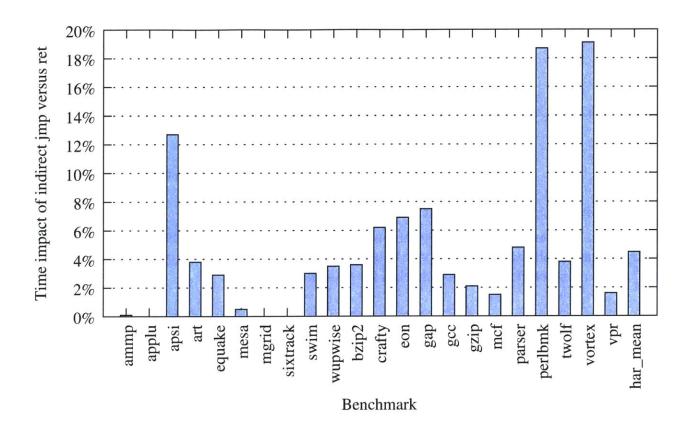

| 4.5  | Performance difference of indirect jumps versus returns                            | 81 |

| 4.6  | Call and return transformations to enable use of the return instruction            | 82 |

| 4.7  | Transparency problems with using non-application return addresses                  | 82 |

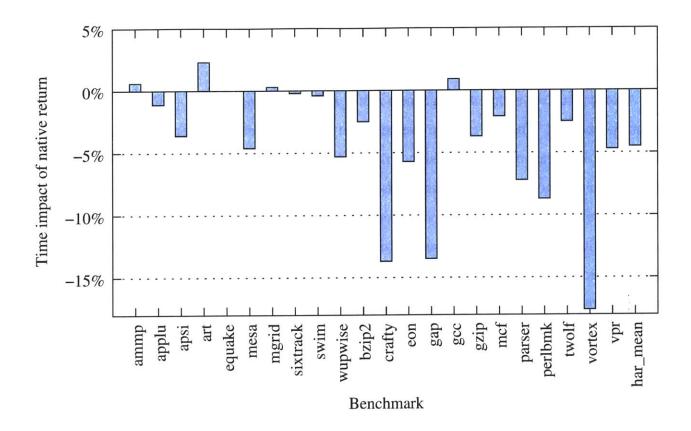

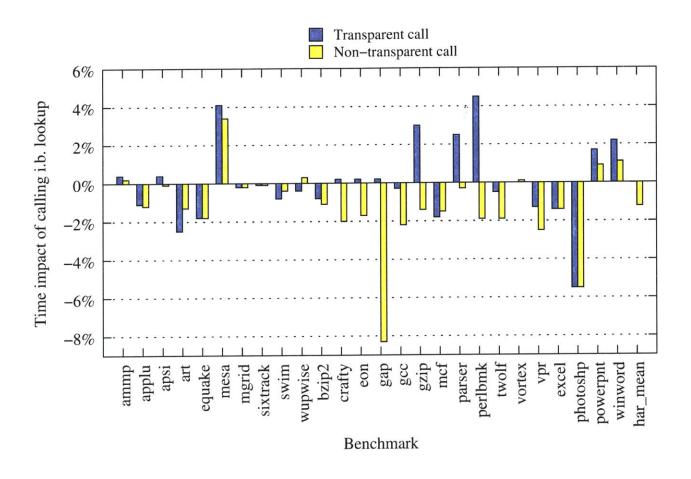

| 4.8  | Performance difference of using native return instructions                         | 84 |

| 4.9  | Instruction sequence for a call to make use of the RSB, when eliding               | 85 |

| 4.10 | Instruction sequence for a call to make use of the RSB, when not eliding           | 85 |

| 4.11 | Performance difference of using a software return stack                            | 86 |

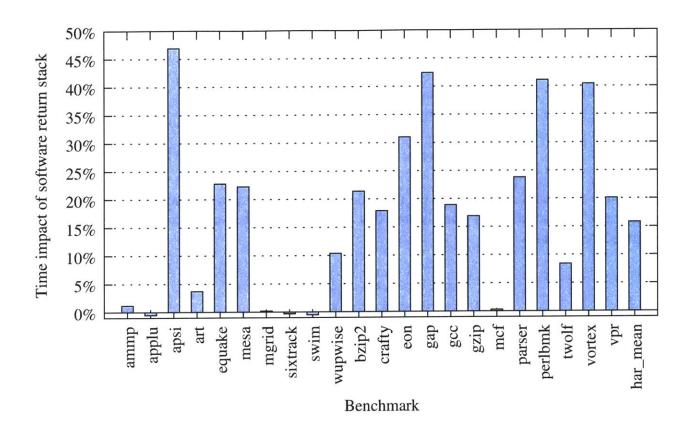

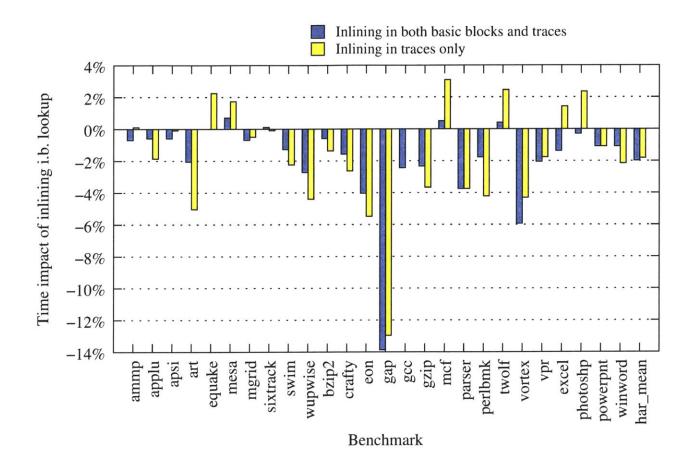

| 4.12 | Performance impact of calling the indirect branch lookup routine                   | 88 |

| 4.13 | Performance impact of inlining the indirect branch lookup routine                  | 89 |

| 4.14 | Cache size increase from inlining indirect branch lookup                           | 90 |

| 4.15 | Hashtable hit statistics                                                           | 91 |

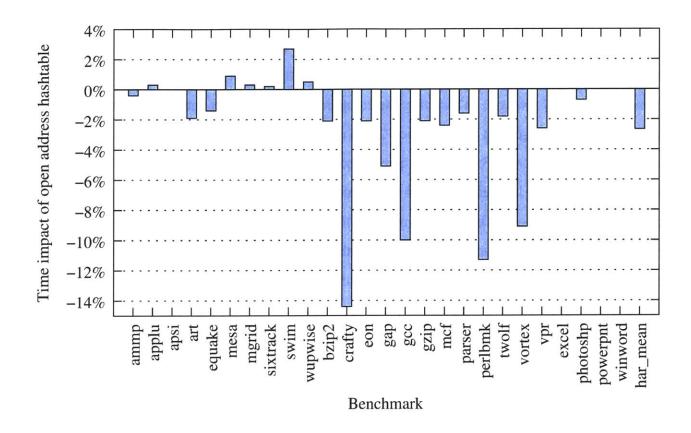

| 4.16 | Performance impact of using an open-address hashtable for indirect branches        | 93 |

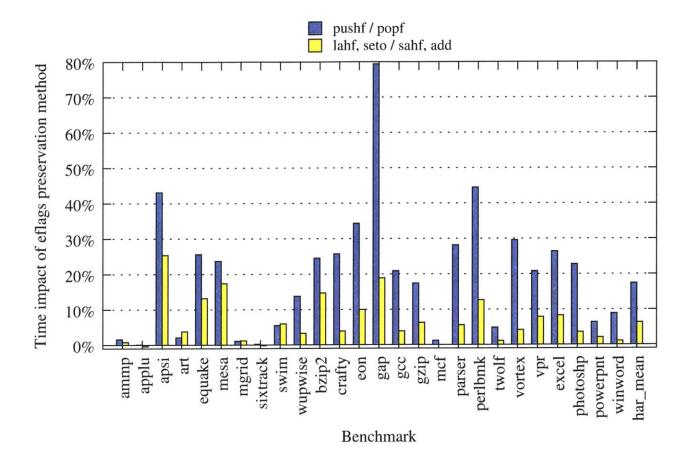

| 4.17 | Performance impact of using a full eflags save                                     | 95 |

| 4.18 | Instruction sequences for comparisons that do not modify the flags                 | 96 |

| 4.19 | Example indirect branch inlined into a trace                                       | 97 |

| 4.20 | Bitwise and instruction sequences that do not modify the flags                     | 98 |

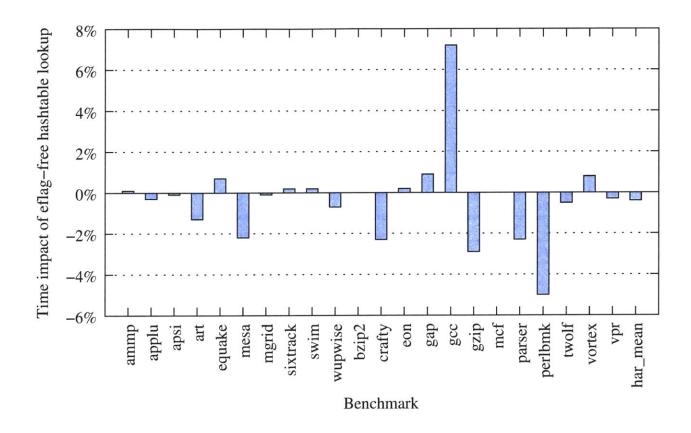

| 4.21 | Performance impact of an eflags-free hashtable lookup                              | 99 |

| 4.22 | Prefix that restores both arithmetic flags and scratch registers only if necessary | 99 |

| 4.23 | Frequency of trace prefixes that require restoration of eflags             |

|------|----------------------------------------------------------------------------|

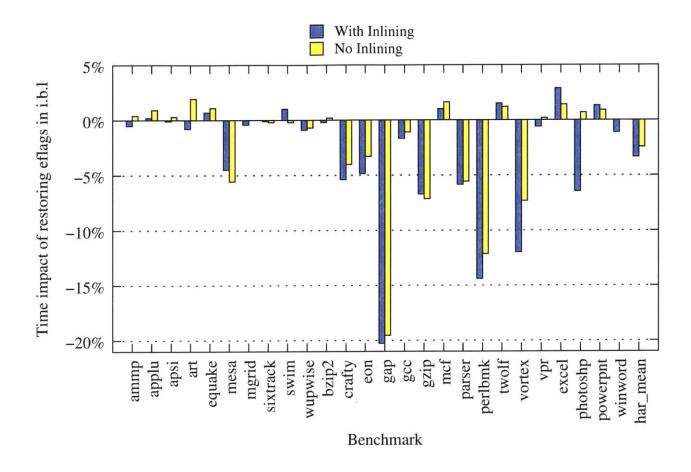

| 4.24 | Performance impact of shifting the eflags restore to fragment prefixes 101 |

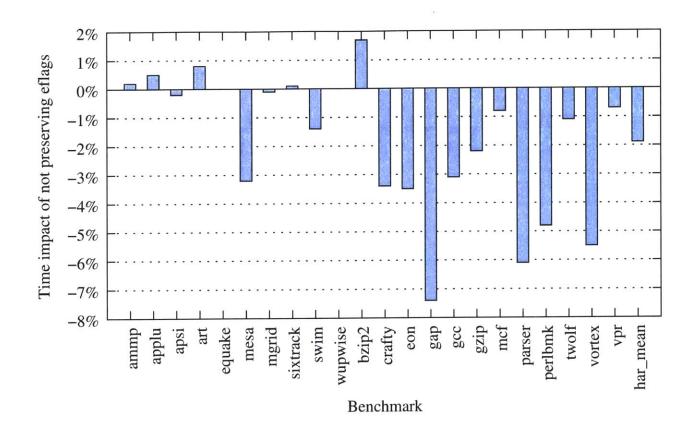

| 4.25 | Performance impact of not preserving eflags across indirect branches 102   |

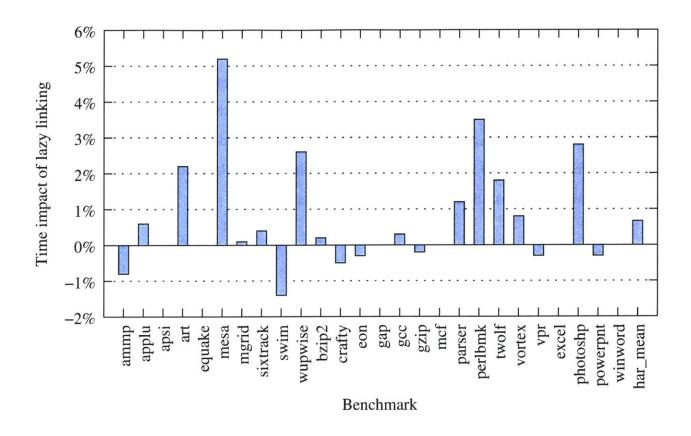

| 4.26 | Performance impact of lazy linking                                         |

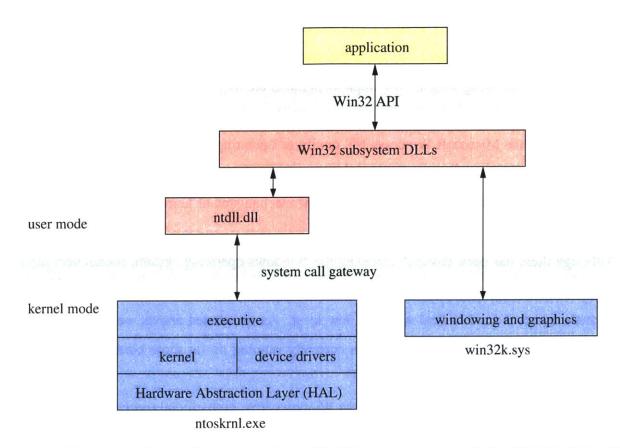

| 5.1  | Windows system components                                                  |

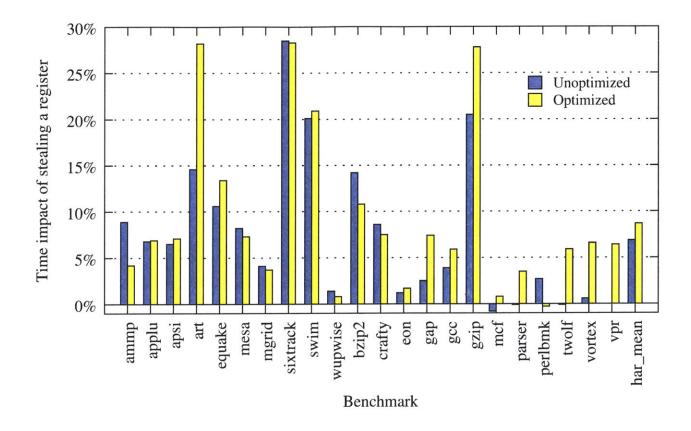

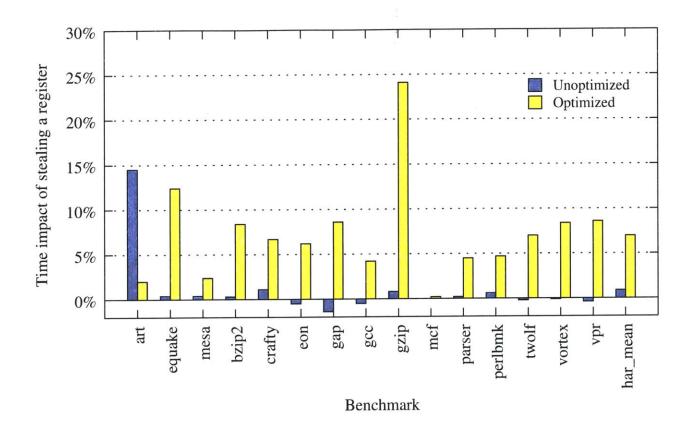

| 5.2  | Performance of register stealing on Linux                                  |

| 5.3  | Performance of register stealing on Windows                                |

| 5.4  | Thread suspension handling pseudo-code                                     |

| 5.5  | Summary of kernel-mediated control transfer types                          |

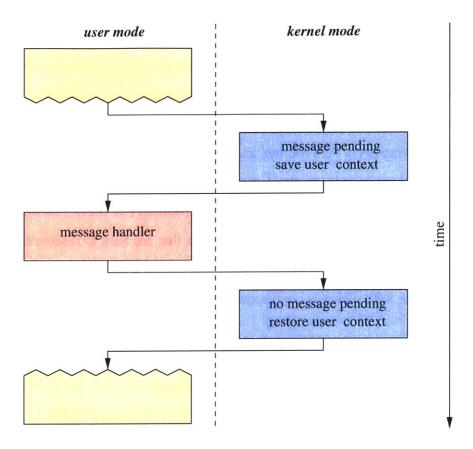

| 5.6  | Control flow of Windows message delivery                                   |

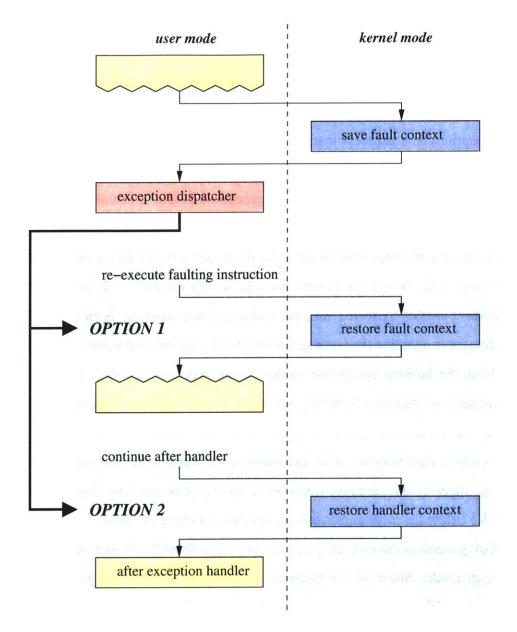

| 5.7  | Control flow of a Windows exception                                        |

| 5.8  | Windows kernel-mediated event counts                                       |

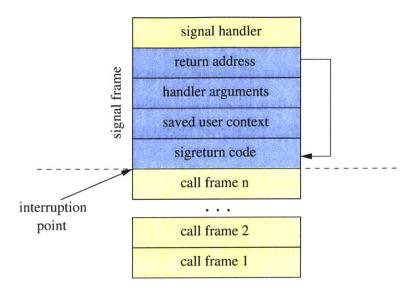

| 5.9  | Stack layout of a signal frame                                             |

| 5.10 | Handling clone in dynamically parametrizable system calls                  |

| 5.11 | Bounding signal delivery by avoiding system call execution                 |

| 6.1  | Fragment sharing across threads                                            |

| 6.2  | Memory unmapping statistics                                                |

| 6.3  | Code modification statistics                                               |

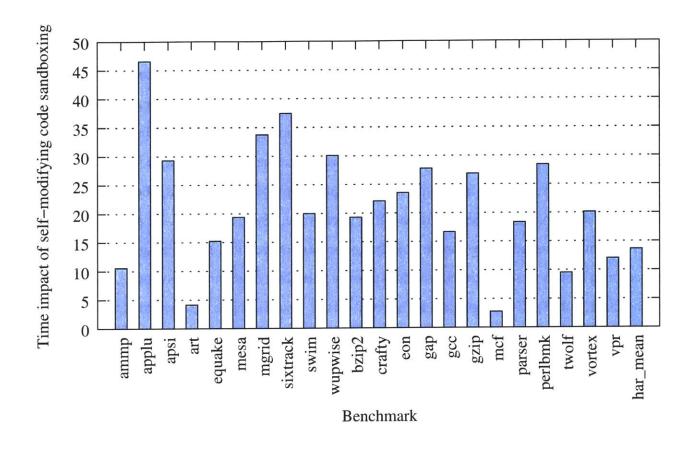

| 6.4  | Performance impact of self-modifying code sandboxing                       |

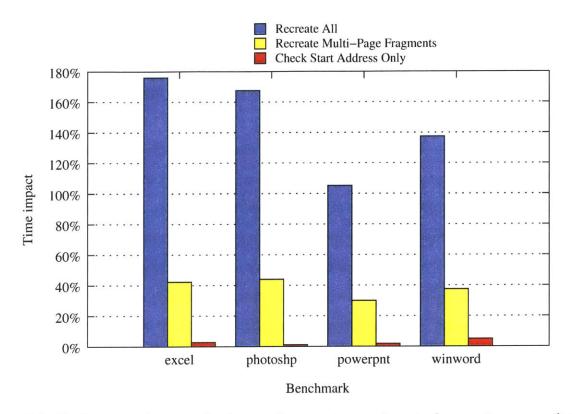

| 6.5  | Performance impact of schemes for mapping regions to fragments             |

| 6.6  | Fragment eviction policy                                                   |

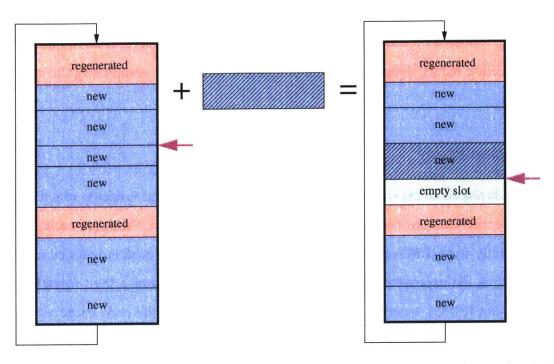

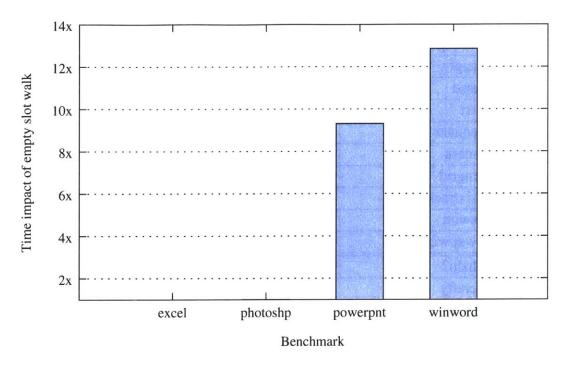

| 6.7  | Performance impact of walking the empty slot list                          |

| 6.8  | Cache space used with an unlimited cache size                              |

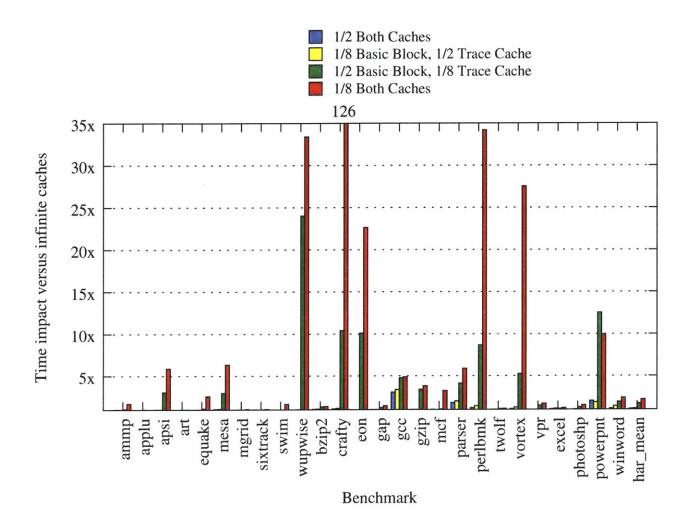

| 6.9  | Performance impact of shrinking the code cache                             |

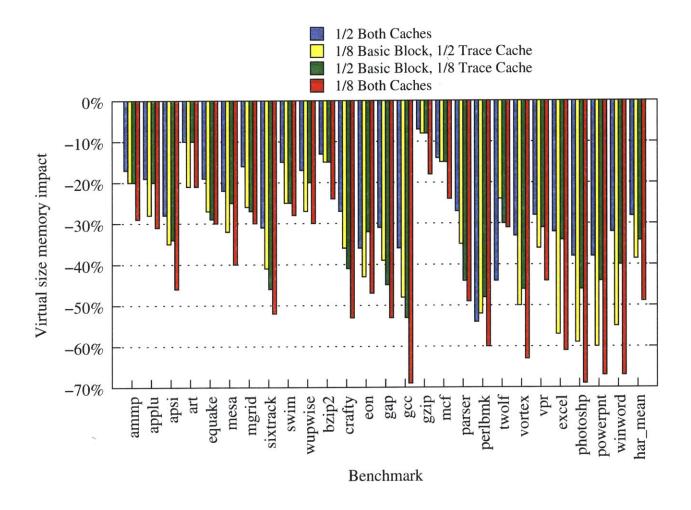

| 6.10 | Virtual size memory impact of shrinking the code cache                     |

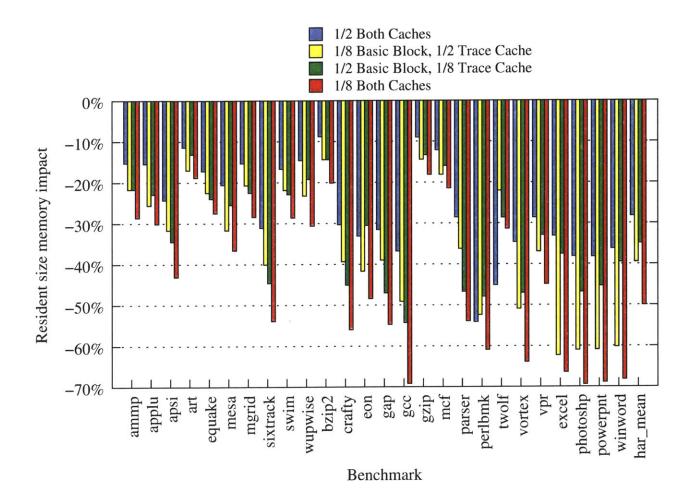

| 6.11 | Resident size memory impact of shrinking the code cache                    |

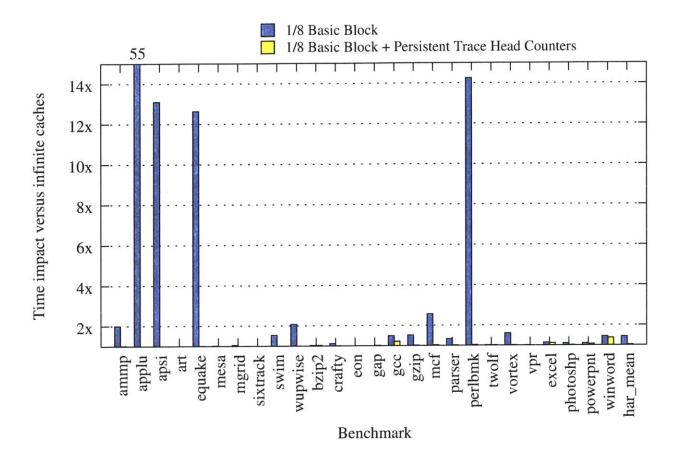

| 6.12 | Performance impact of persistent trace head counters                       |

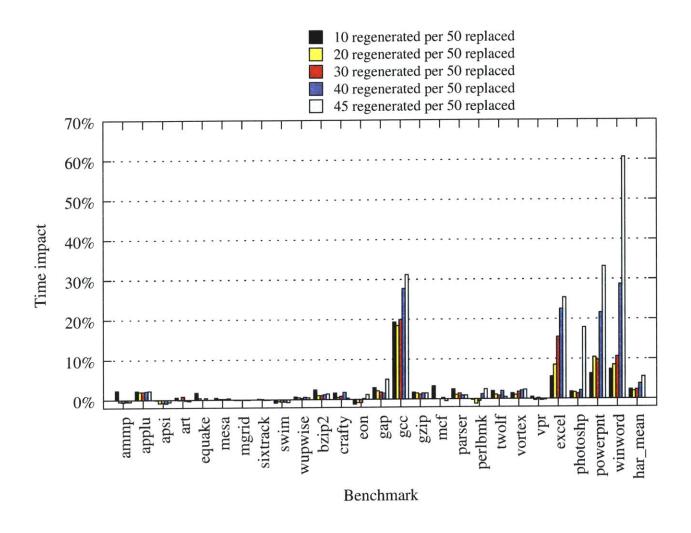

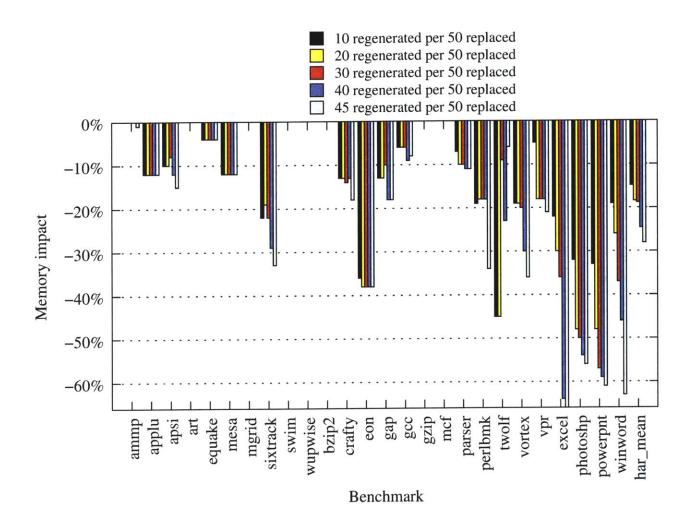

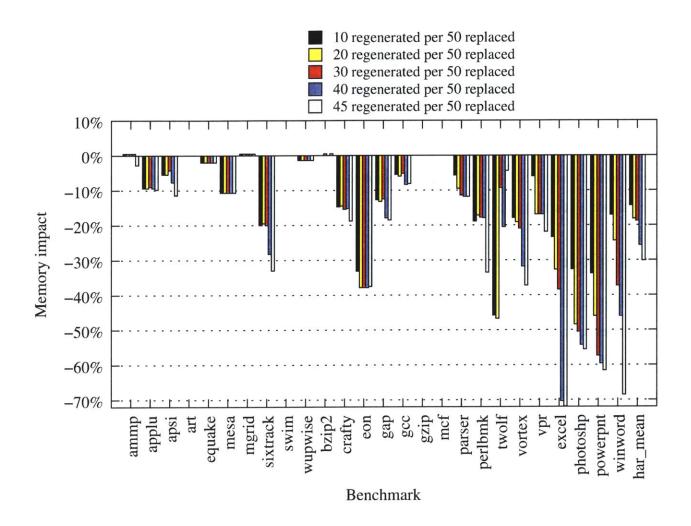

| 6.13 | Performance impact of adaptive working set with parameters 10*n/50 170     |

| 6.14 | Resulting cache sizes from the adaptive working set algorithm              |

| 6.15 | Virtual size memory impact of adaptive working set with parameters $10*n/50172$   |

|------|-----------------------------------------------------------------------------------|

| 6.16 | Resident size memory impact of adaptive working set with parameters $10*n/50$ 173 |

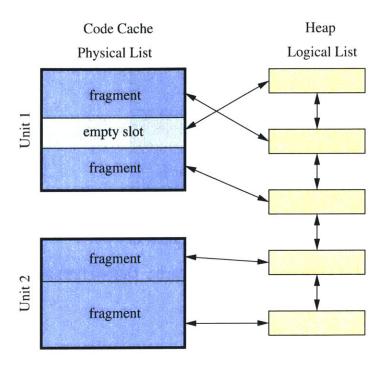

| 6.17 | Code cache logical list                                                           |

| 6.18 | Code cache layout                                                                 |

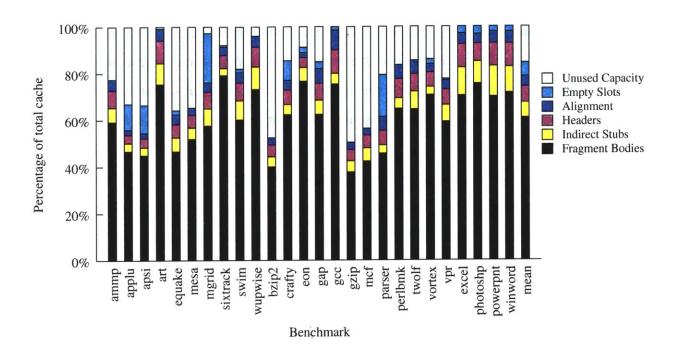

| 6.19 | Basic block code cache without direct stubs breakdown                             |

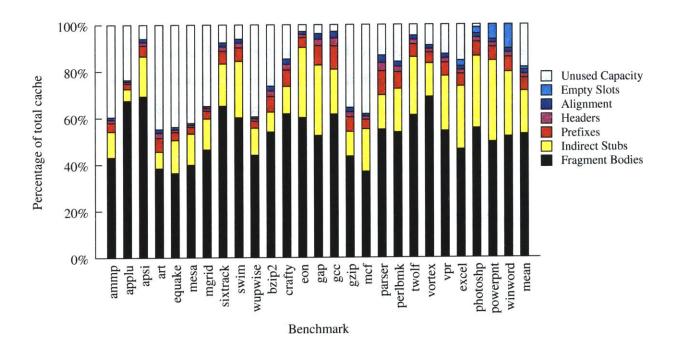

| 6.20 | Trace code cache without direct stubs breakdown                                   |

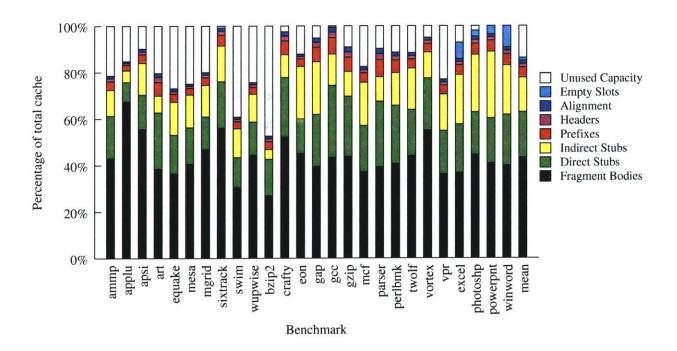

| 6.21 | Basic block code cache breakdown                                                  |

| 6.22 | Trace code cache breakdown                                                        |

| 6.23 | Memory reduction from separating direct exit stubs                                |

| 6.24 | Heap allocation statistics                                                        |

| 6.25 | Salient data structures                                                           |

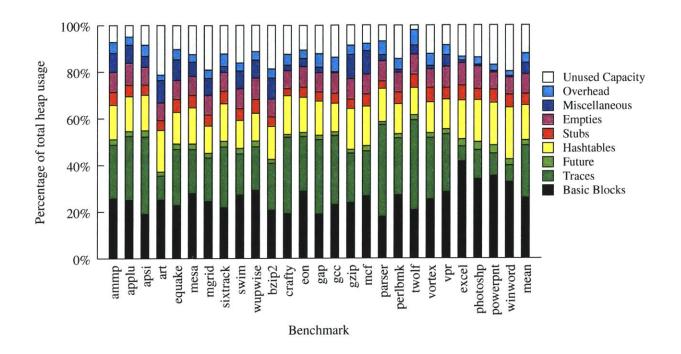

| 6.26 | Heap usage breakdown                                                              |

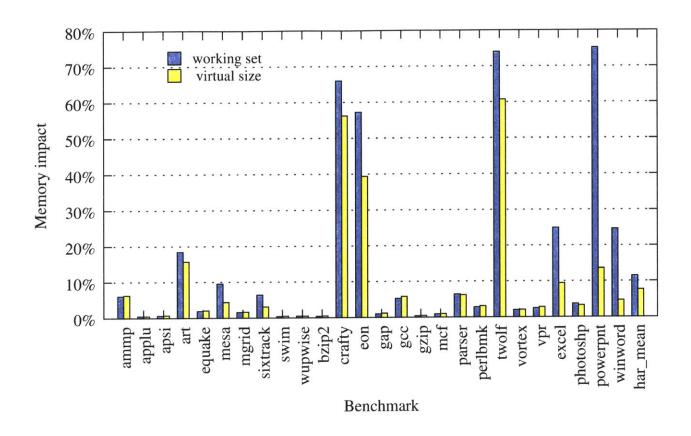

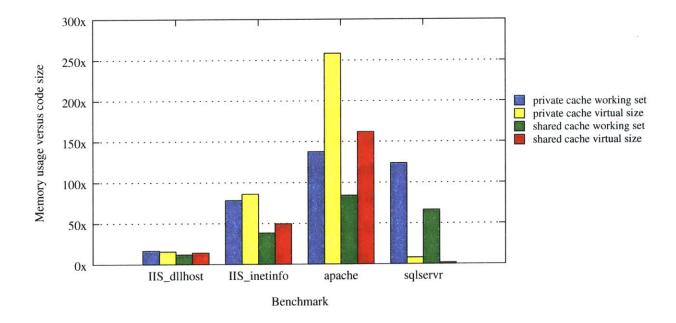

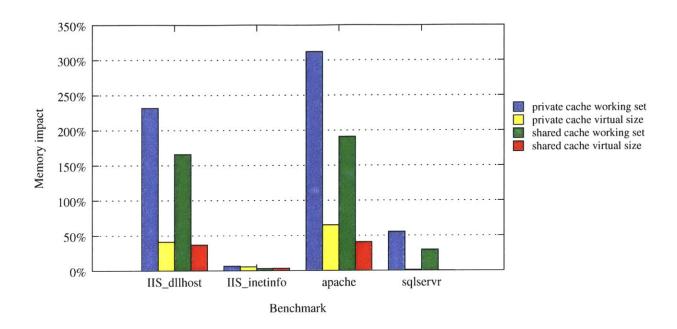

| 6.27 | Memory usage relative to native code size                                         |

| 6.28 | Combined memory usage relative to native                                          |

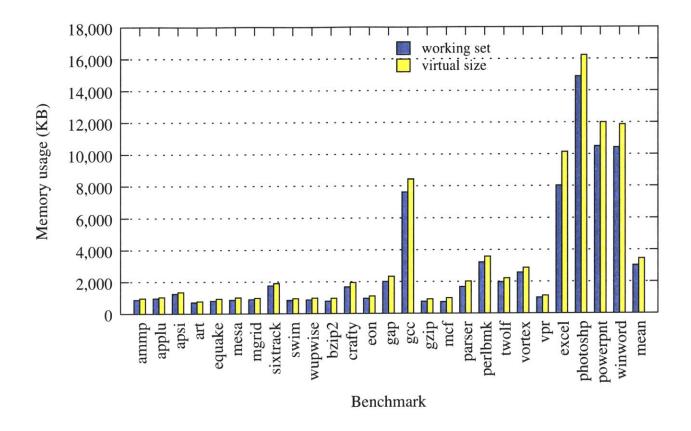

| 6.29 | Memory usage in KB                                                                |

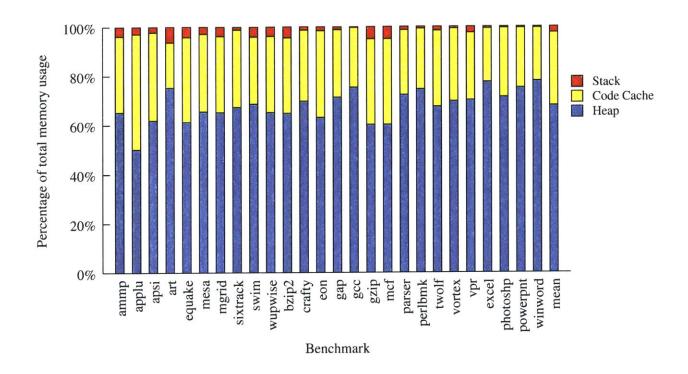

| 6.30 | Memory usage breakdown                                                            |

| 6.31 | Server memory usage relative to native code size                                  |

| 6.32 | Combined server memory usage relative to native                                   |

| 7.1  | Descriptions of our benchmarks                                                    |

| 7.2  | Descriptions of our server benchmarks                                             |

| 7.3  | Statistics of our benchmark suite                                                 |

| 7.4  | Indirect branch statistics                                                        |

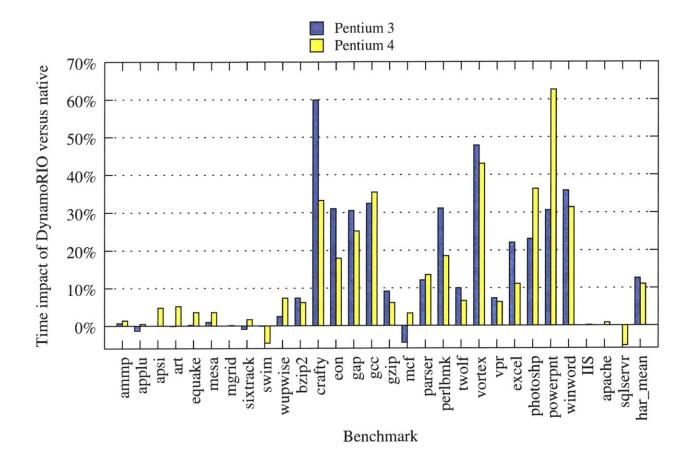

| 7.5  | Base performance of DynamoRIO                                                     |

| 7.6  | Average overhead on each benchmark suite                                          |

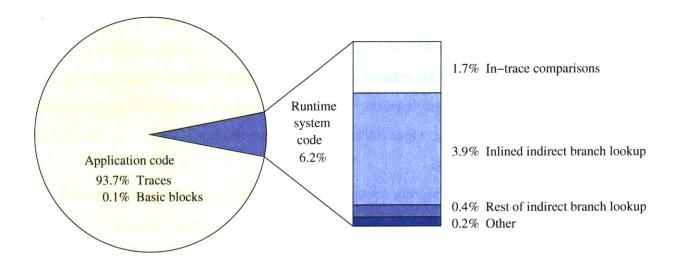

| 7.7  | Time spent in application code and DynamoRIO code                                 |

| 7.8  | System overhead breakdown via program counter profiling                           |

| 7.9  | Time spent in DynamoRIO breakdown via program counter profiling 204               |

| 7.10 | Performance summary of system design decisions                                    |

| 7.11 | Performance impact of program counter sampling                                    |

| 7.12 | Example program counter sampling output                           |

|------|-------------------------------------------------------------------|

| 7.13 | Hardware performance counter profiling data                       |

| 7.14 | Performance impact of exit counter profiling                      |

| 7.15 | Exit counter profiling code                                       |

| 7.16 | Percentage of direct exit stubs whose targets do not write eflags |

| 7.17 | Exit counter profiling output                                     |

| 8.1  | DynamoRIO client operation                                        |

| 8.2  | Explicit application control interface                            |

| 8.3  | Example use of the explicit control interface                     |

| 8.4  | Client hooks called by DynamoRIO                                  |

| 8.5  | Operand types                                                     |

| 8.6  | Decoding routines for each level of detail                        |

| 8.7  | Example use of clean calls                                        |

| 8.8  | Code for collecting branch statistics                             |

| 8.9  | Code for inserting counters into application code, part 1         |

| 8.10 | Code for inserting counters into application code, part 2         |

| 8.11 | Code for computing basic block statistics                         |

| 9.1  | Screenshot of a DynamoRIO client inspecting Adobe Premiere        |

| 9.2  | Code for example micro-architecture-specific optimization         |

| 9.3  | Code for indirect branch dispatch optimization                    |

| 9.4  | Performance impact of five dynamic optimizations                  |

| 9.5  | Interpreter instrumentation API                                   |

| 9.6  | Performance impact of logical trace optimizations                 |

| 9.7  | Performance impact of program shepherding                         |

| 9.8  | Un-circumventable sandboxing                                      |

| 9.9  | Capabilities of program shepherding                               |

| 9.10 | Return address sharing                                            |

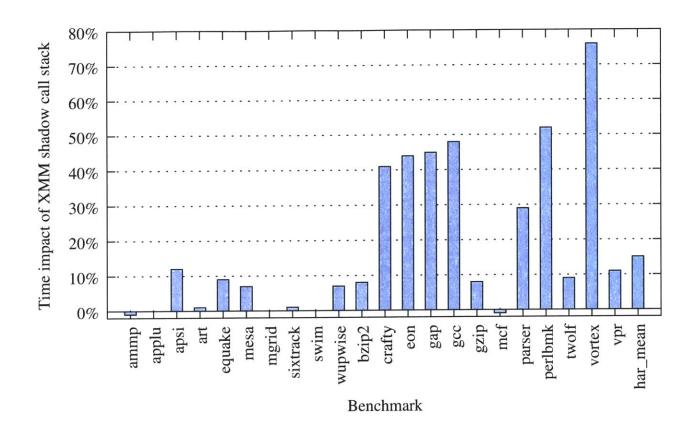

| 9.11 | Performance overhead of a complete call stack in XMM registers    |

| 9.12 | Memory protection privileges                                      |

| 10.1 | Related system comparison                  | 268 |

|------|--------------------------------------------|-----|

| 10.2 | Feature comparison of code caching systems | 277 |

# Chapter 1

# Introduction

As modern applications become larger, more complex, and more dynamic, building tools to manipulate these programs becomes increasingly difficult. At the same time the need for tools to manage application complexity grows. We need information-gathering tools for program analysis, introspection, instrumentation, and trace gathering, to aid in software development, testing, debugging, and simulation. We also need tools that modify programs for optimization, translation, compatibility, sandboxing, etc.

Modern applications are assembled and defined at runtime, making use of shared libraries, virtual functions, plugins, dynamically-generated code, and other dynamic mechanisms. The amount of program information available statically is shrinking. Static tools have necessarily turned to feedback from profiling runs, but these give only an estimate of program behavior. The complete picture of a program's runtime behavior is only available at runtime.

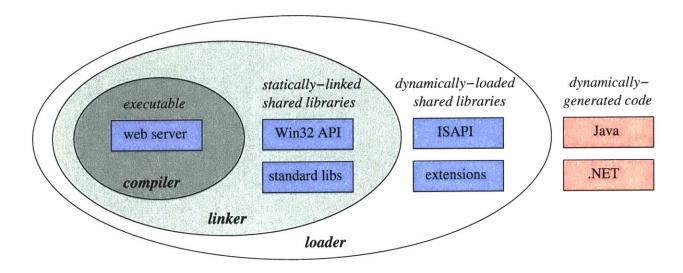

Consider an important modern application, the web server. Figure 1.1 shows the components of a running server, highlighting which parts can be seen by the compiler, linker, and loader. Today's web servers are built for extension by third-party code, in the form of dynamically-loaded modules (e.g., Internet Server Application Programming Interface (ISAPI) components used to provide dynamic data and capabilities for web sites). Even the designers of the web server program cannot anticipate all of the third-party code that will be executed when the web server is in actual use. Tools for operating on applications like this must have a runtime presence.

A runtime tool has many advantages beyond naturally handling dynamic program behavior. Operating at runtime allows the tool to focus on only the code that is executed, rather than wasting

Figure 1.1: The components of a modern web server, and which can be seen by the compiler, linker, and loader. The only components that are known statically, and thus viewable by the compiler or linker, are the executable itself and the shared libraries that it imports. Neither tool knows about custom extension libraries that are loaded in dynamically. The loader can see these, but even the loader has no knowledge of dynamically-generated code for languages like Java and .NET. In modern web servers, extension modules and generated code are prevalent. In addition to missing dynamic behavior, the linker and loader have difficulty seeing inside modules: code discovery and indirect branch target resolution are persistent problems.

analysis resources (which may not matter statically but do matter if operating at load time) on never-seen code. This natural focus on executed code also avoids the code discovery problems that plague link-time and load-time tools. With a runtime view of the program, module boundaries disappear and the entire application can be treated uniformly. Additionally, runtime tools need not require the target application's source code, re-compilation, or re-linking, although they can be coupled with static components to obtain extra information (from the compiler, for example).

## 1.1 Goals

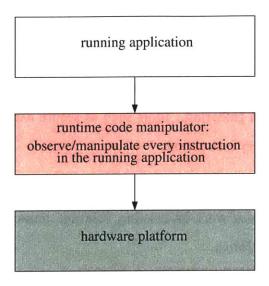

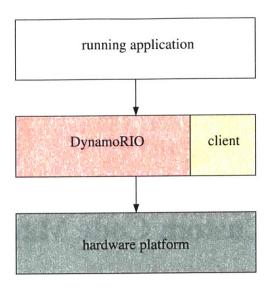

The goal of this thesis is to create a runtime tool platform for fine-grained code manipulation. We would like a *comprehensive* tool platform that systematically interposes itself between *every* instruction executed by a running application and the underlying hardware, as shown in Figure 1.2. Custom tools can then be embedded in this flexible software layer. In order for this layer to be

Figure 1.2: Our goal was to build a flexible software layer that comprehensively interposes itself between a running application and the underlying platform. The layer acts as a runtime control point, allowing custom tools to be embedded inside it.

maximally usable, it should be:

#### Deployable

The layer should be easily inserted underneath any particular application on a production system. Our target tools operate on and dynamically modify applications *in actual use*; they are not limited to studying emulated application behavior. Examples include secure execution environments, dynamic patching for security or compatibility, on-the-fly decompression, and dynamic optimization. This goal drives all of the other ones.

#### Efficient

The layer should amortize its overhead to avoid excessive slowdowns. Poor performance is always a deterrent to tool use, and near-native performance is required for deployment in production environments.

#### Transparent

The layer should operate on unmodified programs and should not inadvertently alter the behavior of any program. Transparency is critical when targeting and modifying applications in actual use, where unintended changes in behavior can have serious consequences. Even a seemingly innocuous imposition can cause incorrect behavior in applications with subtle

dependences.

#### Comprehensive

The layer must be able to observe and modify any and all executed instructions to do more than periodic information gathering. Tools such as secure execution environments require interposition between every instruction.

#### • Practical

To be useful, the layer must work on existing, relevant, unmodified, commodity hardware and operating system platforms.

#### • Universal

The layer should be robust, capable of operating on every application, including hand-crafted machine code and large, complex, multi-threaded, commercial products. Operating at runtime allows us to target applications for which source code is unavailable.

#### Customizable

The layer should be extensible for construction of custom runtime tools.

These goals shape the design of our code manipulation layer. Some are complementary: universal and transparent work together to operate on as many applications as possible. Other goals conflict, such as being comprehensive and practical while maintaining efficiency. This thesis is about optimally satisfying the combination of these goals.

## 1.2 DynamoRIO

We present *DynamoRIO*, a fully-implemented runtime code manipulation system that allows code transformations on any part of a program, *while it executes*. DynamoRIO extends existing code caching technology to allow efficient, transparent, and comprehensive manipulation of an individual, unmodified application, running on a stock operating system and commodity hardware.

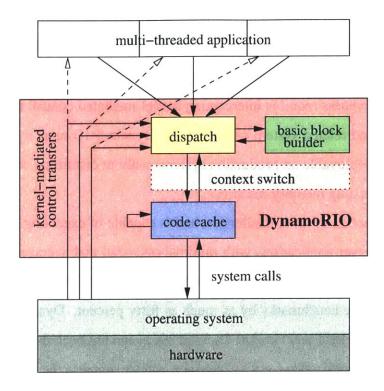

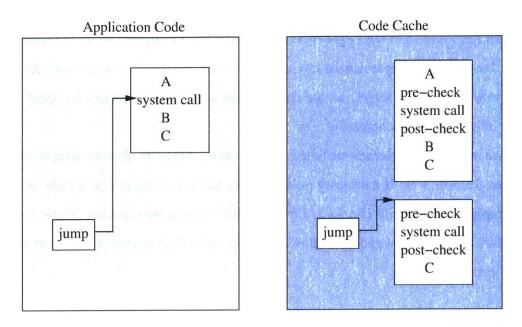

Figure 1.3 illustrates the high-level design of DynamoRIO. DynamoRIO executes a target application by copying the application code into a code cache, one basic block at a time. The code cache is entered via a context switch from DynamoRIO's dispatch state to that of the application.

Figure 1.3: The DynamoRIO runtime code manipulation layer. DynamoRIO interposes itself between an application and the underlying operating system and hardware. It executes a copy of the application's code out of a *code cache* to avoid emulation overhead. Key challenges include managing multiple threads, intercepting direct transfers of control from the kernel, monitoring code modification to maintain cache consistency, and bounding the size of the code cache.

The cached code can then be executed natively, avoiding emulation overhead. However, shifting execution into a cache that occupies the application's own address space complicates transparency. One of our most significant lessons is that DynamoRIO cannot run large, complex, modern applications unless it is fully transparent: it must take every precaution to avoid affecting the behavior of the program it is executing.

To reach the widest possible set of applications (to be universal and practical), DynamoRIO targets the most common architecture, IA-32 (a.k.a. x86), and the most popular operating systems on that architecture, Windows and Linux. The efficiency of a runtime code manipulation system depends on the characteristics of the underlying hardware, and the Complex Instruction Set Computer (CISC) design of IA-32 requires a significant effort to achieve efficiency. To be universal, DynamoRIO must handle dynamically-loaded, generated, and even modified code. Unfortunately, since any store to memory could legitimately modify code on IA-32, maintaining cache consistency

is challenging. Every write to application code must be detected, and system calls that load or unload shared libraries must be monitored. Further challenges arise because DynamoRIO resides on top of the operating system: multiple threads complicate its cache management and other operations, and comprehensiveness requires intercepting kernel-mediated control transfers (e.g., signal or callback delivery) and related system calls. Finally, DynamoRIO must dynamically bound its code cache size to be deployable on production systems without disturbing other programs on the same machine by exhausting memory resources.

DynamoRIO has met all of these challenges, and is capable of executing multi-threaded commercial desktop and server applications with minimal overhead that averages from zero to thirty percent. When aggressive optimizations are performed DynamoRIO is capable of surpassing native performance on some benchmarks by as much as forty percent. DynamoRIO is available to the public in binary form [MIT and Hewlett-Packard 2002] and has been used by many researchers for customized runtime applications via its interface, which supports the development of a wide range of custom runtime tools. Furthermore, DynamoRIO is being commercialized in a security product.

### 1.3 Contributions

Runtime code manipulation and code caching are mature fields of research. Many systems with different goals and designs have utilized these technologies, including emulators, simulators, virtual machines, dynamic optimizers, and dynamic translators. Chapter 10 compares and contrasts the differences in the goals and technologies of these systems with DynamoRIO. We extend runtime interposition technology in a number of different directions, the combination of which is required to comprehensively execute inside the process of a modern application:

#### • **Transparency** (Chapter 3)

We show how to achieve transparency when executing from a code cache inside of the application's own process, and we classify the types of transparency that are required.

#### • Architectural challenges (Chapter 4)

We contribute several novel schemes for coping with the CISC IA-32 architecture: an adap-

tive level-of-detail instruction representation to reduce decoding and encoding costs, efficient condition code preservation, and reduction of indirect branch performance bottlenecks.

#### • Operating system challenges (Chapter 5)

We show how to handle thread complications in everything from application synchronization to cache management to obtaining scratch space. Another contribution is handling kernel transfers whose suspended context is kept in kernel mode, invisible to a user-mode runtime system, and causing havoc on cache management and continuation. These problematic transfers are ubiquitous in Windows applications. We also give a systematic treatment of state-handling options across kernel transfers, show how to operate at the system-call level on Windows, and enumerate the system calls that must be monitored to retain control.

#### • Code cache management (Chapter 6)

We present a novel algorithm for efficient cache consistency in the face of multiple threads and self-modifying code, and extend the prior art with an incremental, runtime algorithm for adapting the cache size to match the application's working set size.

### • Validation and evaluation on real-world programs (Chapter 7)

We show that it is possible to build a runtime interposition point in software that can achieve zero to thirty percent overhead while executing large, complex, real-world programs with dynamic behavior and multiple threads.

#### • Runtime client interface (Chapter 8)

We present our interface for building custom runtime code manipulation tools, which abstracts away the details of the underlying system and allows a tool designer to focus on manipulating the application's runtime code stream. Our interface provides support to the tool builder for maintaining transparency and allows efficient self-replacement of code in our code cache, facilitating adaptive tools.

Case studies of several applications of DynamoRIO are presented in Chapter 9. Related work is described in Chapter 10, and conclusions and future work are discussed in Chapter 11. To provide background for the subsequent chapters, the next chapter (Chapter 2) describes how DynamoRIO

incorporates the standard code caching techniques of linking and trace building, including novel twists on trace starting conditions and basic block building across unconditional control transfers.

# Chapter 2

# **Code Cache**

DynamoRIO is able to observe and manipulate every application instruction prior to its execution by building upon known techniques of code caching, linking, and trace building. This chapter describes our implementation of these techniques, but delays discussing a number of important and novel aspects of DynamoRIO to subsequent chapters: transparency (Chapter 3), architectural challenges such as instruction representation and branch prediction problems (Chapter 4), challenges of interacting with the operating system (Chapter 5), and code cache management and consistency (Chapter 6).

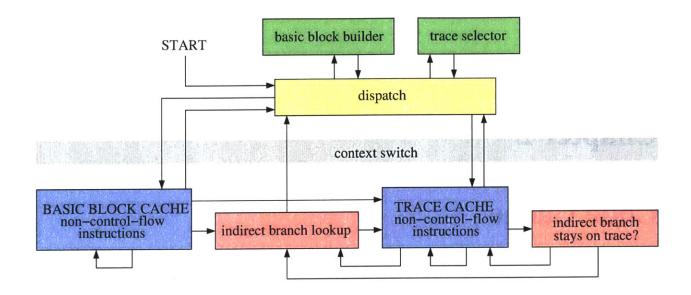

Figure 2.1 shows the components of DynamoRIO and the flow of operation between them. The figure concentrates on the flow of control in and out of the *code cache*, which is the bottom portion of the figure. The cached application code looks just like the original code with the exception of its control transfer instructions, which are shown with arrows in the figure, and which must be modified to ensure that DynamoRIO retains control. This chapter describes each component in the figure: how we populate our code cache one *basic block* at a time (Section 2.1) and then *link* the blocks together (Section 2.2). The code cache enables native execution to replace emulation, bringing performance down from a several hundred times slowdown for pure emulation to an order of magnitude (Table 2.2). Linking of direct branches reduces slowdown further, to around three times native performance. Adding in indirect branch linking, by using a fast lookup of the variable indirect branch target, pushes that performance further, down under two times. Our novel twist on linking is to separate the stubs of code required for the unlinked case from the code for the block itself. We achieve further performance gains by building *traces* (Section 2.3) in a slightly different

Figure 2.1: Flow chart of DynamoRIO. A context switch separates the code cache from DynamoRIO code (though it all executes in the same process and address space). Application code is copied into the two caches, with control transfers (shown by arrows in the figure) modified in order to retain control.

|                          | Average slowdown |         |  |

|--------------------------|------------------|---------|--|

| System Components        | SPECFP           | SPECINT |  |

| Emulation                | ~300x            | ~300x   |  |

| Basic block cache        | 3.54x            | 17.16x  |  |

| + Link direct branches   | 1.32x            | 3.04x   |  |

| + Link indirect branches | 1.05x            | 1.44x   |  |

| + Traces                 | 1.02x            | 1.17x   |  |

| + Optimizations          | 0.88x            | 1.13x   |  |

Table 2.2: Performance summary of the fundamental components of DynamoRIO described in this chapter: a basic block cache, linking of direct and indirect branches, and building traces. Average numbers for both the floating-point (SPECFP) and integer (SPECINT) benchmarks from the SPEC CPU2000 suite are given (our benchmarks are described in Section 7.1). We overcame numerous architectural challenges (Chapter 4) to bring each component to the performance level listed here. The final entry in the table shows the best performance we have achieved with DynamoRIO, using aggressive optimizations to surpass native performance for some benchmarks (see Section 9.2).

manner from other systems, and by our novel scheme of *eliding unconditional control transfers* when building basic blocks (Section 2.4).

original: add %eax, %ecx cmp \$4, %eax ile 0x40106f

Figure 2.3: An example basic block consisting of three IA-32 instructions: an add, a compare, and a conditional direct branch.

### 2.1 Basic Blocks

DynamoRIO copies application code into its code cache in units of *basic blocks*, sequences of instructions ending with a single control transfer instruction. Figure 2.3 shows an example basic block from an application. DynamoRIO's basic blocks are different from the traditional static analysis notion of basic blocks. DynamoRIO considers each entry point to begin a new basic block, and follows it until a control transfer is reached, even if it duplicates the tail of an existing basic block. This is for simplicity of code discovery. Unlike static analyzers, DynamoRIO does not have the luxury of examining an entire code unit such as a procedure. At runtime such information may not be available, nor is there time to spend analyzing it.

The application's code is executed by transferring control to corresponding basic blocks in the code cache. At the end of each block, the application's machine state is saved and control returned to DynamoRIO (a *context switch*) to copy the next basic block. Figure 2.4 shows what the example block looks like inside of DynamoRIO's code cache. Before the targets of its exits have materialized in the cache, they point to two *exit stubs*. Each stub records a pointer to a stub-specific data structure so DynamoRIO can determine which exit was taken. At first glance, putting the second stub first seems like an optimization to remove the jump targeting it, but as Section 2.2 will show, we use that jump for linking, and it is not worth optimizing for the rare unlinked case.

Table 2.5 shows statistics on the sizes of basic blocks in our benchmark suite. A typical basic block consists of six or seven instructions taking up twenty or thirty bytes, although some blocks can be quite large, in the thousands of bytes.

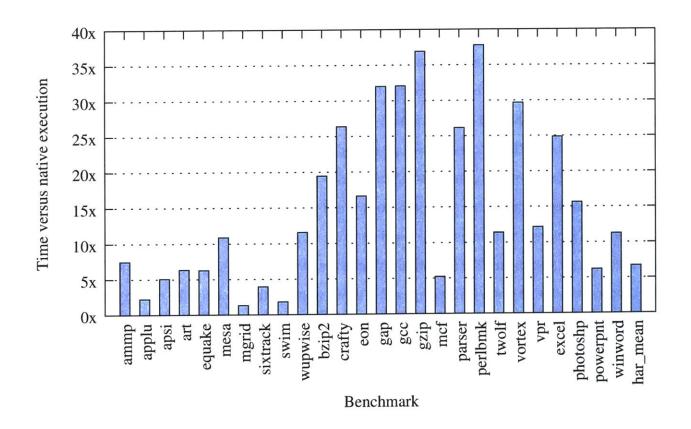

Figure 2.6 shows the performance of a basic block cache system. Pure emulation slows down execution by about 300 times compared to native; directly executing the non-control flow instructions in a basic block cache, and only emulating the branches, brings that slowdown down to about six times on average. Each successive addition of linking and trace building brings that perfor-

Figure 2.4: The example basic block from Figure 2.3 copied into DynamoRIO's code cache. Each exit stub records a pointer to its own data structure (*dstub0* or *dstub1*) before transferring control to the context switch, so that DynamoRIO can figure out which branch was taken. The pointer is stored in a register that first needs to be spilled because this two-instruction combination is more efficient than a ten-byte (slowly-decoded) store of the pointer directly to memory.

Figure 2.6: Performance of a basic block cache system versus native execution. This graph shows time, so smaller numbers are better.

| Benchmark | # blocks | Max bytes | Ave bytes | Max instrs | Ave instrs |

|-----------|----------|-----------|-----------|------------|------------|

| ammp      | 2351     | 2293      | 22.59     | 520        | 6.70       |

| applu     | 2687     | 33360     | 72.99     | 7570       | 16.84      |

| apsi      | 4470     | 3763      | 34.88     | 771        | 9.73       |

| art       | 1395     | 211       | 17.47     | 57         | 5.47       |

| equake    | 1940     | 372       | 21.22     | 118        | 6.04       |

| mesa      | 2884     | 1743      | 22.52     | 364        | 6.31       |

| mgrid     | 2321     | 3975      | 25.79     | 812        | 7.05       |

| sixtrack  | 9270     | 3039      | 29.62     | 908        | 7.58       |

| swim      | 2342     | 1332      | 18.32     | 310        | 5.50       |

| wupwise   | 2665     | 4805      | 22.30     | 1023       | 6.71       |

| bzip2     | 1693     | 193       | 19.20     | 35         | 5.61       |

| crafty    | 6306     | 834       | 23.60     | 163        | 6.55       |

| eon       | 6002     | 1247      | 40.33     | 206        | 8.65       |

| gap       | 8645     | 1002      | 16.03     | 103        | 5.19       |

| gcc       | 36494    | 748       | 13.97     | 102        | 4.51       |

| gzip      | 1600     | 193       | 17.33     | 29         | 5.20       |

| mcf       | 1661     | 313       | 15.84     | 87         | 5.01       |

| parser    | 6538     | 194       | 14.18     | 56         | 4.73       |

| perlbmk   | 14695    | 1673      | 15.07     | 583        | 4.80       |

| twolf     | 5781     | 280       | 19.31     | 68         | 5.86       |

| vortex    | 12461    | 532       | 17.85     | 81         | 5.96       |

| vpr       | 3799     | 298       | 17.52     | 68         | 5.52       |

| excel     | 92043    | 1129      | 13.04     | 458        | 4.39       |

| photoshp  | 206094   | 4023      | 16.35     | 834        | 5.13       |

| powerpnt  | 153984   | 1206      | 12.61     | 458        | 4.34       |

| winword   | 111570   | 2794      | 13.42     | 1009       | 4.52       |

| average   | 26988    | 2752      | 22.05     | 646        | 6.30       |

Table 2.5: Sizes of basic blocks measured in both bytes and instructions (since IA-32 instructions are variable-sized).

mance down still further (Table 2.2 summarizes the numbers).

Figure 2.7: The example basic block from Figure 2.4 with both the taken branch and the fall-through linked to other fragments in the code cache.

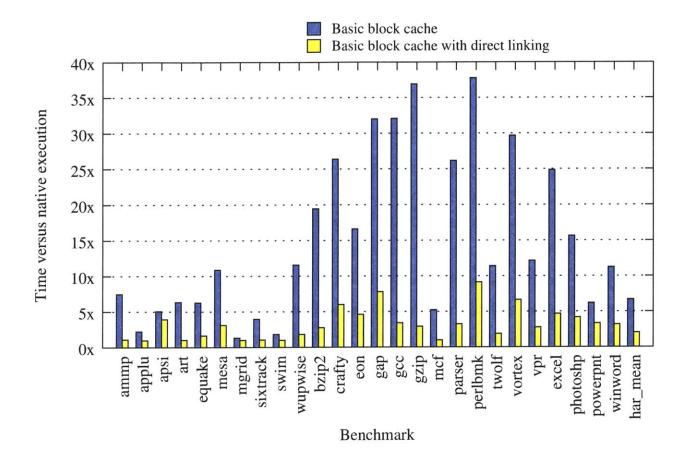

## 2.2 Linking

Copying each basic block into a code cache and executing it natively reduces the performance hit of interpretation enormously. However, we are still interpreting each control transfer by going back to DynamoRIO to find the target. If the target is already present in the code cache, and is targeted via a direct branch, DynamoRIO can *link* the two blocks together with a direct jump, avoiding the cost of a subsequent context switch. Figure 2.7 shows how the exit stubs of our example block are bypassed completely after linking. The performance improvement of linking direct control transfers is dramatic (Figure 2.8), as expensive context switches are replaced with single jumps.

Linking may be done either *proactively*, when a fragment is created, or *lazily*, when an exit is taken. Section 4.5.1 explains why proactive linking is a better choice for IA-32. In either case, data structures must be kept to record the outgoing links of each fragment. The incoming links must also be kept, in order to efficiently delete a single fragment: otherwise, all other fragments must be searched to make sure all links to the dead fragment are removed, or alternatively space must be wasted with a placeholder in the dead fragment's place. Single-fragment deletion is essential for cache consistency (see Section 6.2). Incoming link records are also required to quickly shift links from one fragment to another for things like trace head status changes (Section 2.3.2) or replacing a fragment with a new version of itself (Section 8.2.3). Incoming links to non-existent fragments must be stored as well, for which we use a *future fragment* data structure as a placeholder. Once an actual fragment at that target is built, it replaces the future fragment and takes over its incoming link list. Future fragments can also be used to keep persistent state across fragment deletions and

Figure 2.8: Performance impact of linking direct control transfers, compared to the performance of a basic block cache with no linking, versus native execution time.

re-creations, such as for cache capacity (Section 6.3.3) and trace head counters (Section 2.3.2).

We must be able to undo linking on demand, for building traces (Section 2.3), bounding time delay of delivering signals (Section 5.3.5), fragment replacement (Section 8.2.3), and when deleting a fragment. Unlinking requires either incoming link information or using a prefix on each fragment. DynamoRIO uses incoming link information, as it is already needed for proactive linking and other features.

The actual process of linking and unlinking boils down to modifying the exits of a fragment. Examining Figure 2.7 and its unlinked version Figure 2.4 shows that each branch exiting a fragment either points to its corresponding exit stub (the *unlinked* state) or points to its actual fragment target (the *linked* state). Switching from one state to the other takes a single 32-bit store, which, if the targets do not straddle cache lines or if the lock prefix is used, is atomic on all recent IA-32

processors [Intel Corporation 2001, vol. 3] and thus can be performed in the presence of multiple threads without synchronization.

Fortunately, on IA-32 we do not have reachability problems that systems on other architectures faced [Bala et al. 1999]. The variable-length instruction set allows for full 32-bit addresses as immediate operands, allowing a single branch to target any location in memory. A few specific branch types take only eight-bit immediates, but we are able to transform these to equivalent 32-bit-immediate branches (see Section 4.1.3).

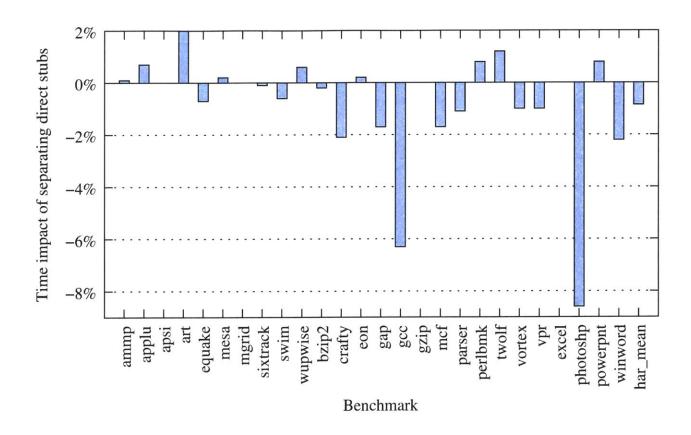

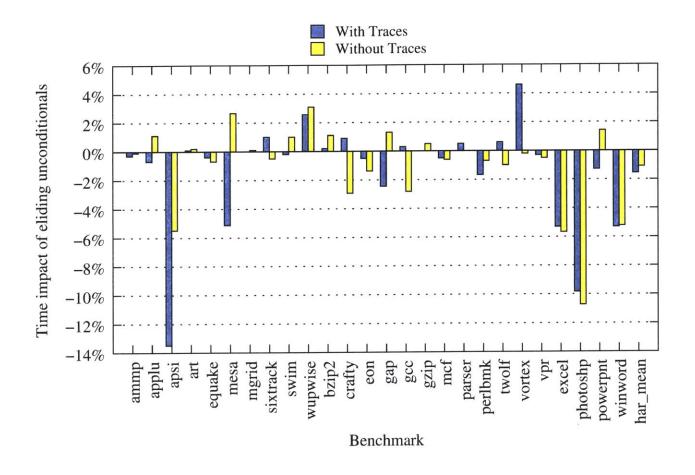

Once an exit from a basic block is linked, the corresponding exit stub is not needed again unless the exit is later unlinked. By locating the exit stubs in a separate cache from the basic block body, we can delete and re-create exit stubs on demand as they are needed. This both compacts the cache, reducing the working set size of the program, and reduces overall memory usage by deleting stubs no longer needed. The performance impact of separating direct exit stubs is shown in Figure 2.9. The resulting reduced instruction cache pressure helps benchmarks with larger code sizes, such as photoshp and gcc in our suite. Memory savings are given in Section 6.3.5. About one-half of all stubs are not needed at any given time (when not using them for profiling as in Section 7.3.3). The other half are mainly exits whose targets have not yet been reached during execution (and may never be reached).

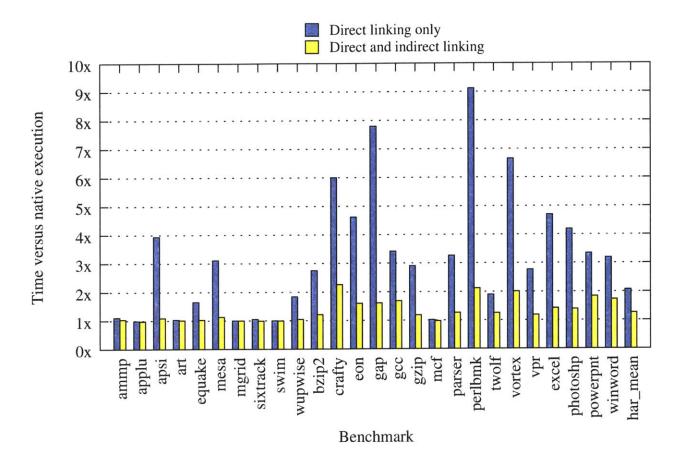

Indirect branches cannot be linked in the same way as direct branches because their targets may vary. To maintain transparency, original program addresses must be used wherever the application stores indirect branch targets (for example, return addresses for function calls — see Section 3.3.3). These addresses must be translated to their corresponding code cache addresses in order to jump to the target code. This translation is performed as a fast hashtable lookup inside the code cache (avoiding a context switch back to DynamoRIO). Figure 2.10 shows the performance improvement of linking indirect control transfers. Benchmarks with more indirect branches, such as perlbmk and gap, are more affected by optimizing indirect branch performance than applications with few indirect branches, like swim (see Table 7.4 for the indirect branch statistics of our benchmark suite).

The translation of indirect branches is the single largest source of overhead in DynamoRIO. Why this is so, and our attempts to reduce the cost by both optimizing our hashtable lookup and eliminating the translation altogether, are discussed in Section 4.2 and Section 4.3.

Figure 2.9: Performance impact of separating direct exit stubs. Relative time impact is shown compared to base DynamoRIO performance, so smaller numbers are better. As in all of our performance measurements, noise produces an impact of up to one or even two percent (see Section 7.1.1).

## 2.3 Traces

To improve the efficiency of indirect branches, and to achieve better code layout, basic blocks that are frequently executed in sequence are stitched together into a unit called a *trace*. The superior code layout and inter-block branch elimination in traces provide a significant performance boost, as shown in Figure 2.11. Benchmarks whose hot loops consist of single basic blocks, such as mgrid and swim, are not improved by traces; fortunately, such benchmarks already perform well under DynamoRIO. One of the biggest benefits of traces is in avoiding indirect branch lookups by inlining a popular target of an indirect branch into a trace (with a check to ensure that the actual target stays on the trace, falling back on the full lookup when the check fails). This explains why their biggest impact is often on benchmarks with many indirect branches.

Figure 2.10: Performance impact of linking indirect control transfers, compared to only linking direct control transfers, versus native execution time.

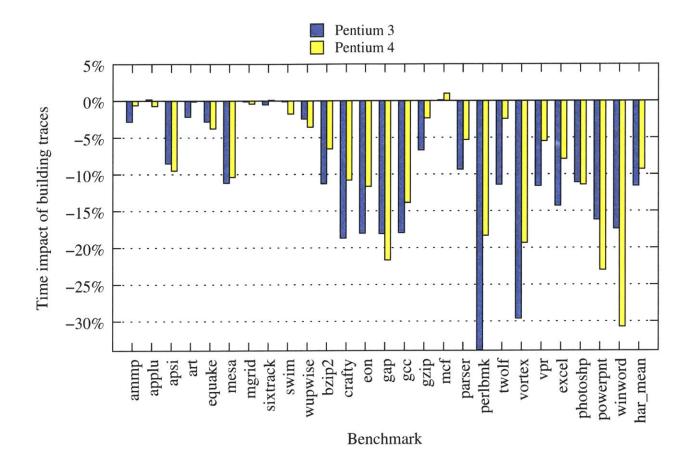

Trace building is also used as a hardware instruction fetch optimization [Rotenberg et al. 1996], and the Pentium 4 contains a hardware trace cache. Although the Pentium 4 hardware trace cache stitches together IA-32 micro-operations, it is targeting branch removal just like a software trace cache, and there is some competition between the two. The hardware cache has a smaller window of operation, but its effects are noticeable. In Figure 2.11 the average overall speedup is 11% on the Pentium 3 as opposed to just over 7% for the Pentium 4. The differences for individual benchmarks are sometimes reversed (e.g., powerpnt and winword) for reasons we have not tracked down, perhaps due to other differences in the underlying machines.

Figure 2.11: Performance impact of traces on both a Pentium 3 and a Pentium 4, versus DynamoRIO performance without traces.

## 2.3.1 Trace Shape

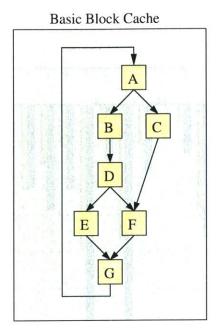

DynamoRIO's traces are based on the Next Executing Tail (NET) scheme [Duesterwald and Bala 2000]. Figure 2.12 shows two example traces created from sequences of basic blocks. As Duesterwald and Bala [2000] show, a runtime system has very different profiling needs than a static system. For static or offline processing, path profiling [Ball and Larus 1996] works well. However, its overheads are too high to be used online, especially in terms of missed opportunities while determining hot paths. Another problem with many path profiling algorithms is a preparatory static analysis phase that requires access to complete source code. These algorithms can only be used in a runtime system by coordinating with a compiler [Feigin 1999]. General runtime profiling must be done incrementally, as code is discovered — all the code to be profiled is not known beforehand. Some path profiling algorithms can operate online, such as bit tracing [Duesterwald and Bala 2000], but

Figure 2.12: Building traces from basic blocks. Block A, as a target of a backward branch, is a *trace head* with an associated execution counter. Once its counter exceeds a threshold, the *next executing tail* is used to build the trace headed by A. In this example, the tail is BDEG. Block C, as an exit from a (newly created) trace, becomes a *secondary trace head*. If it becomes hot, the secondary trace shown will be created.

none identify hot paths quickly enough.

The NET trace creation scheme is specifically designed for low-overhead, incremental use. Despite its simplicity, it has been shown to identify traces with comparable quality to more sophisticated schemes [Duesterwald and Bala 2000]. NET operates by associating a counter with each trace head. A trace head is either the target of a backward branch (targeting loops) or an exit from an existing trace (called a secondary trace head). The counter is incremented on each execution of the trace head. Once the counter exceeds a threshold (usually a small number such as fifty), trace creation mode is entered. The next executing tail (NET) is taken to be the hot path. This means that the next sequence of basic blocks that is executed after the trace head becomes hot is concatenated together to become a new trace. The trace is terminated when it reaches a backward branch or another trace or trace head.

DynamoRIO modifies NET to not consider a backward *indirect* branch target to be a trace head. Consequently, where NET would stop trace creation at a backward indirect branch, we continue. This has both an advantage and a disadvantage. The advantage is that more indirect branches

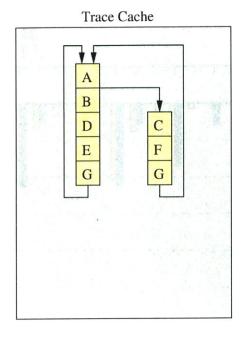

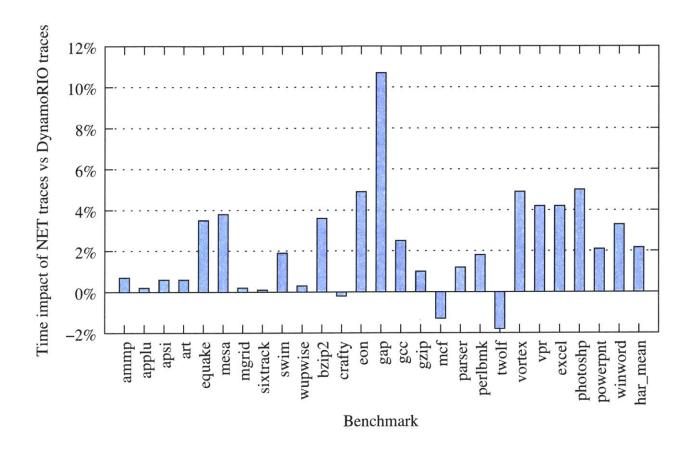

Figure 2.13: Performance impact of using the NET trace building scheme versus DynamoRIO's trace building scheme. NET treats indirect and direct branches the same for trace head purposes, while DynamoRIO does *not* treat a backward indirect branch target as a trace head. NET traces perform worse than DynamoRIO's traces on nearly all of our benchmarks.

will be inlined into traces, where with the NET scheme, half of the time a trace will stop at an indirect branch. The disadvantage is that in pathological situations (e.g., a recursive loop where the recursive call is indirect) unlimited loop unrolling can occur. We feel that the advantage is worth the extra unrolling, and use a maximum trace size to limit code bloat. Figure 2.13, showing performance, and Table 2.14, showing size, back up our choice: the average size increase is under eight percent, while the performance improvement is as much as ten percent. We have not tracked down the exact indirect branches in gap and the other benchmarks that are responsible for the difference in trace performance.

The key insight is that more trace heads do not result in better traces. Since trace creation stops upon reaching a trace head (to avoid code duplication), more trace heads can result in many tiny

| Trace cache |

|-------------|

| 7.2%        |

| 2.1%        |

| 5.8%        |

| 7.1%        |

| 11.8%       |

| 5.9%        |

| 8.0%        |

| 7.1%        |

| 7.1%        |

| 1.0%        |

| 0.0%        |

| 5.4%        |

| 17.3%       |

| 8.2%        |

| 6.1%        |

| 4.6%        |

| 14.3%       |

| 3.4%        |

| 4.5%        |

| 22.9%       |

| 4.0%        |

| 14.3%       |

| 9.5%        |

| 8.0%        |

| 13.4%       |

| 5.8%        |

| 7.9%        |

|             |

Table 2.14: Trace cache size increase from DynamoRIO's changes to the NET trace building scheme. The average size increase is under eight percent, which is a reasonable cost for achieving performance improvements as high as ten percent (Figure 2.13).

traces. By selectively eliminating trace heads that are targets of indirect branches, we try to build traces across those branches.

However, DynamoRIO's trace building scheme does do poorly in some extreme cases. An example is a threaded interpreter, such as Objective Caml [Leroy 2003], where indirect branches are used almost exclusively, causing DynamoRIO to build no traces. This is not a catastrophic situation; we will simply not get the performance boost of traces.

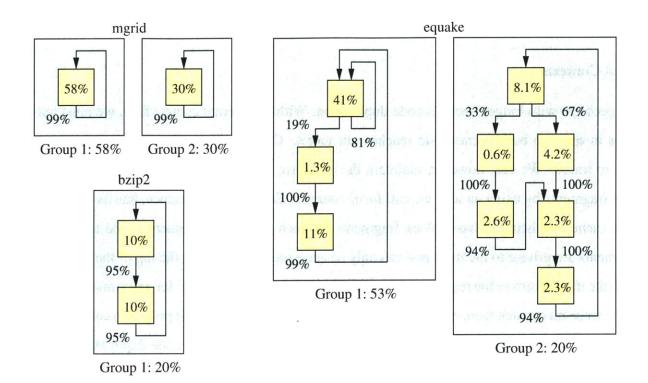

To understand the shape of our traces, see Table 2.15. An average trace consists of four basic blocks, about 29 instructions. More than one in two traces contains an inlined indirect branch, one of the goals of trace building. Traces reduce DynamoRIO's indirect branch translation overhead significantly.

Table 2.16 shows the coverage and completion rates of our traces. We gathered these using our *exit counter profiling*, which is discussed in Section 7.3.3. On average, only five traces are needed to cover a full one-half of a benchmark's execution time. Ten traces cover nearly two-thirds, and fifty approaches seven-eighths. For completion, on average a trace is only executed all the way to the end one-third of the time. However, execution reaches at least the half-way point in a trace 90% of the time.

## 2.3.2 Trace Implementation

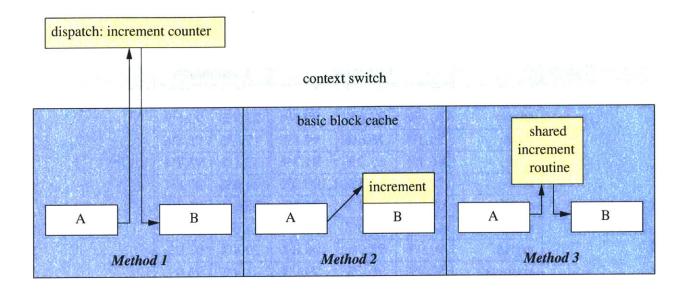

To increment the counter associated with each trace head, the simplest solution is to never link any fragment to a trace head, and perform the increment inside DynamoRIO (the first method in Figure 2.17). As there will never be more than a small number of increments before the head is turned into a trace, this is not much of a performance hit. We tried two different strategies for incrementing without the context switch back to DynamoRIO. One strategy is to place the increment inside the trace head fragment itself (the second method in Figure 2.17). However, this requires replacing the old fragment code once the fragment is discovered to be a trace head (which often happens after the fragment is already in the code cache, when a later backward branch is found to target it). The cost of replacing the fragment overwhelms the performance improvement from having the increment inlined (remember, the increment only occurs a small number of times — DynamoRIO's default is fifty).

A different strategy is to use a shared routine inside the cache to perform the increment (the

|           | Basic | blocks | Instructions |     | Bytes |     | Inlined ind. br. |     |

|-----------|-------|--------|--------------|-----|-------|-----|------------------|-----|

| Benchmark | Max   | Ave    | Max          | Ave | Max   | Ave | Max              | Ave |

| ammp      | 50    | 4.3    | 531          | 32  | 2355  | 108 | 12               | 0.5 |

| applu     | 40    | 3.3    | 4096         | 63  | 18068 | 278 | 13               | 0.3 |

| apsi      | 41    | 4.6    | 774          | 44  | 3778  | 152 | 13               | 0.6 |

| art       | 34    | 3.6    | 200          | 21  | 924   | 69  | 12               | 0.4 |

| equake    | 38    | 4.4    | 198          | 25  | 824   | 92  | 14               | 0.6 |

| mesa      | 45    | 5.4    | 669          | 39  | 2270  | 136 | 16               | 0.8 |

| mgrid     | 40    | 4.3    | 815          | 37  | 3984  | 137 | 13               | 0.7 |

| sixtrack  | 53    | 4.3    | 926          | 31  | 3113  | 111 | 17               | 0.5 |

| swim      | 40    | 4.3    | 313          | 27  | 1341  | 92  | 13               | 0.7 |

| wupwise   | 36    | 5.4    | 1034         | 45  | 4827  | 146 | 12               | 0.6 |

| bzip2     | 54    | 3.0    | 303          | 20  | 936   | 71  | 5                | 0.2 |

| crafty    | 69    | 3.4    | 530          | 23  | 2006  | 83  | 14               | 0.3 |

| eon       | 49    | 5.5    | 570          | 40  | 2271  | 130 | 13               | 1.1 |

| gap       | 66    | 3.7    | 292          | 19  | 752   | 53  | 22               | 0.6 |

| gcc       | 48    | 3.7    | 190          | 18  | 750   | 55  | 13               | 0.3 |

| gzip      | 26    | 3.2    | 149          | 18  | 612   | 63  | 9                | 0.3 |

| mcf       | 35    | 4.7    | 215          | 23  | 732   | 73  | 11               | 0.7 |

| parser    | 48    | 2.9    | 210          | 15  | 601   | 45  | 15               | 0.2 |

| perlbmk   | 57    | 4.0    | 604          | 21  | 1712  | 63  | 13               | 0.4 |

| twolf     | 52    | 5.0    | 270          | 27  | 853   | 93  | 14               | 0.7 |

| vortex    | 82    | 5.8    | 402          | 47  | 1244  | 137 | 16               | 0.5 |

| vpr       | 38    | 4.6    | 211          | 26  | 699   | 78  | 12               | 0.6 |

| excel     | 121   | 4.6    | 438          | 22  | 1262  | 67  | 23               | 0.8 |

| photoshp  | 62    | 4.1    | 394          | 37  | 1210  | 109 | 24               | 0.8 |

| powerpnt  | 21    | 4.3    | 95           | 20  | 303   | 59  | 6                | 0.8 |

| winword   | 321   | 4.4    | 1994         | 22  | 5880  | 66  | 99               | 0.7 |

| average   | 60    | 4.3    | 632          | 29  | 2435  | 98  | 17               | 0.6 |

Table 2.15: Trace shape statistics. The numbers for each benchmark are an average over all of that benchmark's traces. (See Table 7.3 for trace counts for each benchmark.) The maximum and the arithmetic mean are shown for each of four categories: number of basic blocks composing each trace, number of application instructions in each trace, number of bytes in those instructions (i.e., the sizes given are for the original application basic blocks that are stitched together, not the resulting trace size in the code cache, which would include exit stubs, prefixes, and indirect branch comparison code), and number of indirect branches inlined into each trace.

|           | Coverage |        |        | Completion |       |

|-----------|----------|--------|--------|------------|-------|

| Benchmark | Top 5    | Top 10 | Top 50 | End        | Half  |

| ammp      | 80.4%    | 92.6%  | 99.5%  | 23.7%      | 93.6% |

| applu     | 58.3%    | 76.6%  | 99.4%  | 17.7%      | 96.8% |

| apsi      | 46.1%    | 63.2%  | 94.3%  | 33.1%      | 93.7% |

| art       | 71.6%    | 84.5%  | 100.0% | 24.6%      | 90.8% |

| equake    | 69.8%    | 85.4%  | 99.3%  | 25.8%      | 91.3% |

| mesa      | 44.9%    | 65.3%  | 98.9%  | 34.6%      | 92.5% |

| mgrid     | 94.9%    | 98.9%  | 100.0% | 29.4%      | 93.9% |

| sixtrack  | 82.7%    | 98.7%  | 99.9%  | 41.4%      | 94.0% |

| swim      | 99.9%    | 99.9%  | 100.0% | 36.4%      | 95.9% |

| wupwise   | 72.2%    | 83.6%  | 94.7%  | 24.6%      | 92.4% |

| bzip2     | 36.7%    | 50.6%  | 90.6%  | 25.6%      | 90.0% |

| crafty    | 15.9%    | 24.5%  | 53.5%  | 33.8%      | 85.4% |

| eon       | 22.8%    | 35.7%  | 76.2%  | 30.4%      | 87.5% |

| gap       | 31.3%    | 47.5%  | 81.5%  | 44.7%      | 89.5% |

| gcc       | 27.0%    | 33.2%  | 47.7%  | 41.9%      | 90.3% |

| gzip      | 36.2%    | 58.3%  | 97.5%  | 26.8%      | 88.5% |

| mcf       | 54.2%    | 78.9%  | 97.6%  | 31.9%      | 89.8% |

| parser    | 16.3%    | 24.0%  | 54.5%  | 36.4%      | 89.8% |

| perlbmk   | 65.9%    | 76.0%  | 91.6%  | 38.2%      | 89.0% |

| twolf     | 24.3%    | 40.7%  | 81.4%  | 27.1%      | 91.0% |

| vortex    | 42.6%    | 56.2%  | 81.9%  | 48.0%      | 92.5% |

| vpr       | 33.5%    | 53.9%  | 96.8%  | 34.9%      | 86.8% |

| excel     | 60.2%    | 86.5%  | 98.0%  | 55.3%      | 84.7% |

| photoshp  | 29.0%    | 36.9%  | 57.7%  | 23.0%      | 90.7% |

| powerpnt  | 66.9%    | 87.1%  | 99.8%  | 40.2%      | 88.2% |

| winword   | 17.8%    | 27.1%  | 49.9%  | 62.1%      | 86.5% |

| average   | 50.1%    | 64.1%  | 86.2%  | 34.3%      | 90.6% |

Table 2.16: Trace coverage and completion statistics. The numbers for each benchmark are an average over all of that benchmark's traces. For coverage, the percentages of total trace execution time spent in the top five, ten, and fifty traces are shown in the first three columns, respectively. (Trace execution time is very close to total execution time for nearly all of our benchmarks, as shown in Table 7.8.) The fourth column shows how frequently execution makes it to the end of the trace (without exiting early). The final column shows the percentage of the time that execution makes it to the second half (defined in terms of exits) of the trace.

Figure 2.17: Three methods of incrementing trace head counters: exiting the cache to perform the increment in DynamoRIO code, re-writing the trace head to increment its counter inline, and using a shared increment routine inside the code cache.

third method in Figure 2.17). When discovering that a fragment is a trace head, all fragments pointing to it can be changed to instead link to the increment routine. This link change is most easily done when incoming links are recorded (see Section 2.2). The increment routine increments the counter for the target trace head and then performs an indirect branch to the trace head's code cache entry point. Since a register must be spilled to transfer information between the calling fragment and the increment routine, the routine needs to restore that register, while keeping the indirect branch target available. Only two options allow both: storing the indirect branch target in memory, or adding a prefix to all potential trace heads (all basic blocks, unless blocks are replaced once they are marked as trace heads, which as mentioned earlier is expensive) that will restore the register containing the target to its application value. We chose to store the target in memory, though this has ramifications for self-protection (see Section 9.4.5).

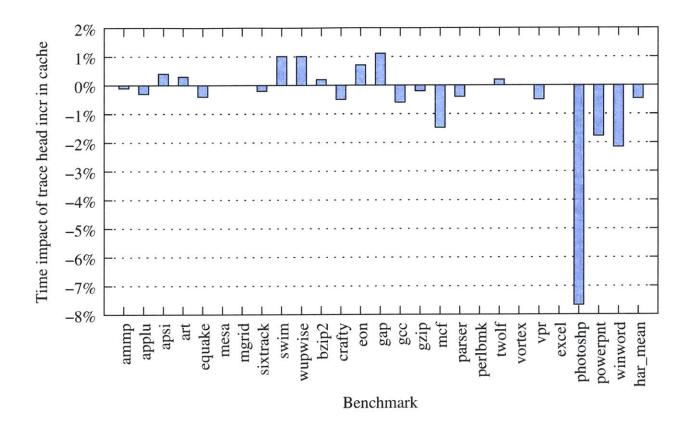

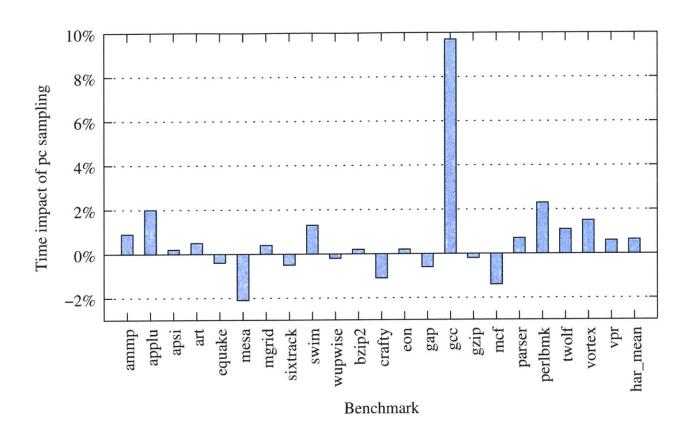

Incrementing the counter without leaving the code cache drastically reduces the number of exits from the cache (Table 2.18). Surprisingly, the performance difference (Figure 2.19) is no more than noise for nearly all of our benchmarks. The explanation is that code cache exits are not a major source of overhead because the number of them is already small. The benchmarks that it does make a difference on are those that execute large amounts of code with little re-use, our

Figure 2.19: Performance impact of incrementing trace head counters inside the code cache, versus exiting the cache to perform increments inside DynamoRIO.

desktop benchmarks, and are spending noticeable time entering and exiting the cache.