### Characterization and Modeling of Pattern Dependencies in Copper Interconnects for Integrated Circuits

by

Tae Hong Park

S.B., Electrical Engineering and Computer Science, MIT, 1998 M.Eng., Electrical Engineering and Computer Science, MIT, 1998

Submitted to the

Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

at the

### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

May 2002

© Massachusetts Institute of Technology, 2002. All Rights Reserved.

Certified by ..... Duane S. Boning Associate Professor of Electrical Engineering and Computer Science Thesis Supervisor

Accepted by .....

Arthur C. Smith Chairman, Department Committee on Graduate Theses Department of Electrical Engineering and Computer Science

`

#### BARKER

|   | MASSACHUSETTS INSTITUTE<br>OF TECHNOLOGY |  |

|---|------------------------------------------|--|

| - | JUL 312002                               |  |

|   | LIBRARIES                                |  |

.

### Characterization and Modeling of Pattern Dependencies in Copper Interconnects for Integrated Circuits

by

Tae Hong Park

Submitted to the Department of Electrical Engineering and Computer Science on May 24, 2002, in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering and Computer Science

#### Abstract

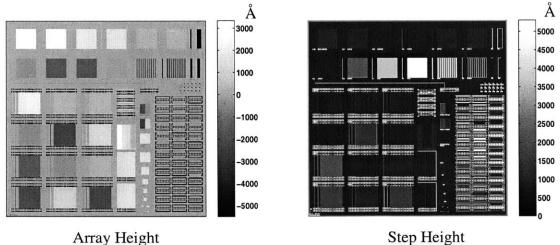

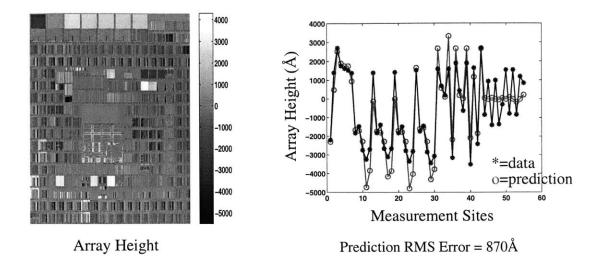

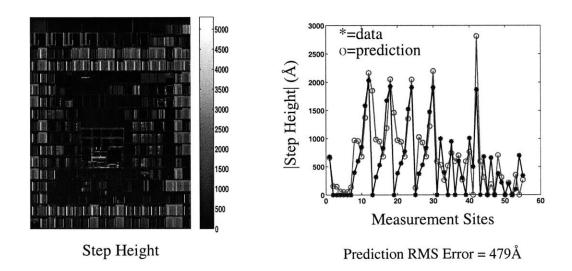

Copper metallization has emerged as the leading interconnect technology for deep sub-micron features, where electroplating and chemical mechanical polish (CMP) processes have a vital role in the fabrication of integrated circuits. The processes both suffer from a similar problem: the copper electroplated profiles and the polished surface exhibit pattern dependent topography. In this thesis, a methodology for the characterization and modeling of pattern dependent problems in copper interconnect topography is developed. For the electroplating process, the methodology consists of test structure and mask design to examine feature scale copper step height and the height of copper array regions as a function of underlying layout parameters. Semi-empirical response surface models are then generated with model parameters extracted from conventional and superfill plating processes. Once the models are calibrated, layout parameters including pattern density, line width distributions, and line length are extracted for each cell in a 40  $\mu$ m by 40  $\mu$ m discretization of any random chip layout. Then, a chip-scale prediction is achieved by simulating generalized average heights for each grid cell across the entire chip. The prediction result shows root mean square errors of less than 1000 Å for array height and around 500 Å for step height. This methodology provides the first known chip-scale prediction of electroplated topography.

For pattern dependencies in copper CMP, this thesis focuses on the development of test structures and masks (including multi-level structures) to identify key pattern effects in both single-level and multi-level polishing. Especially for the multi-level studies, electrical test structures and measurements in addition to surface profile scans are seen to be important in accurately determining thickness variations. The developed test vehicle and characterization of copper dishing and oxide erosion serve as a basis for further pattern dependent model development. Finally, integration of electroplating and CMP chip-scale models is illustrated; the simulated step and array heights as well as topography pattern density are used as an input for the initial starting topography for CMP simulation of subsequent polishing profile evolution.

Thesis Supervisor: Duane Boning

Title: Associate Professor of Electrical Engineering and Computer Science

### Acknowledgments

First of all, I would like to thank my research advisor, Professor Duane Boning, for his guidance and support throughout this research, and I am truly grateful for his advice and suggestions during my graduate studies here at MIT and on this thesis. I would also like to thank my thesis readers, Professor Jung-Hoon Chun and Professor Jesus del Alamo, for being on my thesis committee and providing valuable feedback on this research.

Various industrial collaborations have made this research possible. I would like to thank Chidi Chidambaram, Christopher Borst, Greg Shinn, and Dennis Buss at Texas Instruments for providing valuable experimental results. I also thank Steven Hymes and Paul Lefevre at International SEMATECH for help with test mask designs and various process experiments. I also want to express my sincere appreciation to Taber Smith at Praesagus Inc. and Soo-Young Oh at Ubi Tech for layout parameter extractions; I also thank SooKap Hahn at SKW Associates for providing software for profile scan extractions.

My life and this thesis are enriched by the research colleagues of the Statistical Metrology Group and MTL, and I want to thank the following people, including both past and current members: Tamba Tugbawa, Brian Lee, Xioalin Xie, Karen Gonzalez-Valentin, Joseph Panganiban, Nigel Drego, Vikas Mehrotra, Shiou Lin Sam, Dennis Ouma, Brian Stine, Rajesh Divecha, Huy Le, Jung Yoon, Abraham Kim, Jee-Hoon Krska, Taber Smith, David White, Aaron Gower-Hall, Hasan Nayfeh, and Arifur Rahman. I especially thank Tamba Tugbawa; it has been an exceptional experience working together with him on this and related research. I would also like to thank the members of MTL for their various support.

I also express my appreciation and gratitude to my friends at MIT, the Dahn Center and Munsu Temple, for their companionship and friendship. Their support and encouragement have always helped me to move forward with confidence and a smile. Finally, I am deeply grateful to my parents and family for their wisdom, encouragement, and support. Completing this research and my study at MIT would not have been possible without them, and I dedicate this thesis to my parents.

This work has been supported in part by DARPA, PDF Solutions Inc., Texas Instruments, Inc., and the NSF/SRC Engineering Research Center for Environmentally Benign Semiconductor Manufacturing.

# **Table of Contents**

| 1 Introduction                                                                   | 15  |

|----------------------------------------------------------------------------------|-----|

| 1.1 Introduction to Copper Metallization                                         | 16  |

| 1.2 Review of Electroplating and CMP: Principles and Mechanisms                  |     |

| 1.3 Key Problems in Electroplating and CMP                                       | 21  |

| 1.4 Thesis Goals                                                                 | 27  |

| 1.5 Thesis Organization                                                          | 28  |

| 2 Comprehensive Characterization and Modeling                                    |     |

| Methodology                                                                      |     |

| 2.1 Electroplating Characterization and Modeling                                 |     |

| 2.2 CMP Characterization and Modeling                                            |     |

| 2.3 Overview of Integration for Electroplating and CMP Chip-Scale Simulation     |     |

|                                                                                  |     |

| 3 Test Structure and Mask Design                                                 |     |

| 3.1 Structure Design Philosophy and Issues                                       |     |

| 3.1.1 Characteristic Length Scales in Electroplating and CMP                     |     |

| 3.1.2 Basic Test Structure Design: Line/Array                                    |     |

| 3.2 Single-Level Copper Test Mask V1.2                                           |     |

| 3.3 Measurements                                                                 |     |

| 3.4 Summary                                                                      |     |

| 4 Characterization and Modeling of Surface Topography in Electroplating          |     |

| 4.1 Surface Topography Definitions                                               |     |

| 4.2 Experimental Setup and Measurement                                           |     |

| 4.3 Characterization and Trends                                                  |     |

| 4.3.1 Surface Profile Trends for Various Patterns                                |     |

| 4.3.2 Step Height and Array Height Trends                                        |     |

| 4.3.3 Characteristic Length Scales in Electroplating                             |     |

| 4.3.4 Interaction of Line Width and Space                                        |     |

| 4.4 Pattern Dependent Model Development: Incorporating Physical Effect           |     |

| 4.4.1 Basic Governing Principles in Electroplating                               |     |

| 4.4.2 Superfill Electroplating Mechanisms                                        |     |

| 4.5 Semi-Empirical Pattern Dependent Model                                       |     |

| 4.6 Model Fit and Model Coefficient Extraction                                   | 80  |

| 5 Chip-Scale Simulation and Prediction of Surface Topography in Electroplating . | 87  |

| 5.1 Overview of Average Step and Array Height Calculation                        | 88  |

| 5.2 Layout Parameter Extraction                                                  | 91  |

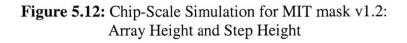

| 5.3 Chip-Scale Simulation of Array Height and Step Height                        | 97  |

| 5.4 Field Thickness Variation: Extraction and Simulation                         |     |

| 5.5 Chip-Scale Simulation and Prediction Results                                 | 108 |

| 5.5.1 Chip-Scale Simulation Calibration Results                                  | 108 |

| 5.5.2 Chip-Scale Prediction and Verification Result for Arbitrary Layout         |     |

| 5.6 Wafer to Wafer Variability of SH/AH and Field Thickness                      |     |

| 5.7 Summary                                                                      | 120 |

| 6 Pattern Dependencies in Chemical Mechanical Polishing    |     |

|------------------------------------------------------------|-----|

| 6.1 Single-Level Characterization                          | 121 |

| 6.1.1 Bulk Copper Polish Evolution                         | 122 |

| 6.1.2 Overpolish Evolution of Dishing and Erosion          | 130 |

| 6.1.3 Characterization of Dishing and Erosion              | 133 |

| 6.2 Multi-Level Pattern Effects and Propagation            | 145 |

| 6.2.1 Review of Multi-Level Structure and Mask Description | 146 |

| 6.2.2 Experimental Setting                                 | 148 |

| 6.2.3 Experimental Result And Discussion                   | 149 |

| 6.3 Modeling of Pattern Dependency in CMP Process          | 155 |

| 6.4 Integration of Plating and CMP Models                  | 161 |

| 7 Conclusion                                               | 167 |

| 7.1 Summary and Conclusion                                 | 167 |

| 7.2 Future Work – Applications of the Methodology          |     |

| 7.3 Future Work - Model Extensions                         |     |

| Bibliography                                               |     |

| Appendix A                                                 | 177 |

| Appendix A                                                 | 183 |

# **List of Figures**

| Figure 1.1: Copper Metallization: Damascene Process                                      | 17    |

|------------------------------------------------------------------------------------------|-------|

| Figure 1.2: Copper Interconnect (6 Levels, Source: IBM)                                  | 18    |

| Figure 1.3: Basic Mechanism of Copper Electroplating                                     | 19    |

| Figure 1.4: CMP Machine                                                                  |       |

| Figure 1.5: Non-Uniform Topography in Copper Electroplating (Superfill)                  | 22    |

| Figure 1.6: Initial Copper Profile and Influence on Copper Removal                       | 23    |

| Figure 1.7: Pattern Dependent Problems of Dishing and Erosion In Copper CMP              | 24    |

| Figure 1.8: Multi-Level Process Sequence                                                 | 26    |

| Figure 2.1: Overall Methodology for Characterization and Modeling of Thickness Patt      | ern   |

| Dependency in Copper Electroplating                                                      | 32    |

| Figure 2.2: Overall Methodology for Characterization and Modeling of Thickness Patt      | ern   |

| Dependency in Copper CMP                                                                 |       |

| Figure 2.3: Integration of Electroplating Model and CMP Model for Complete Chip-Le       | evel  |

| Simulation                                                                               | 36    |

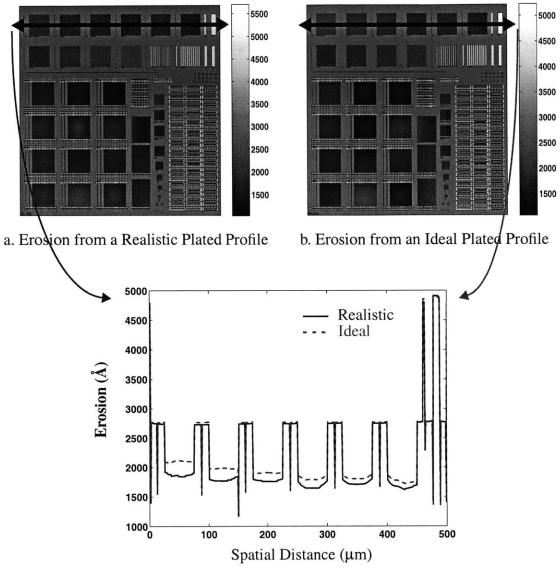

| Figure 3.1: Sample Erosion Profile Across an Array Region                                | 43    |

| Figure 3.2: Line and Array Test Structures                                               | 44    |

| Figure 3.3: Density Structure Circuit Representation                                     | 46    |

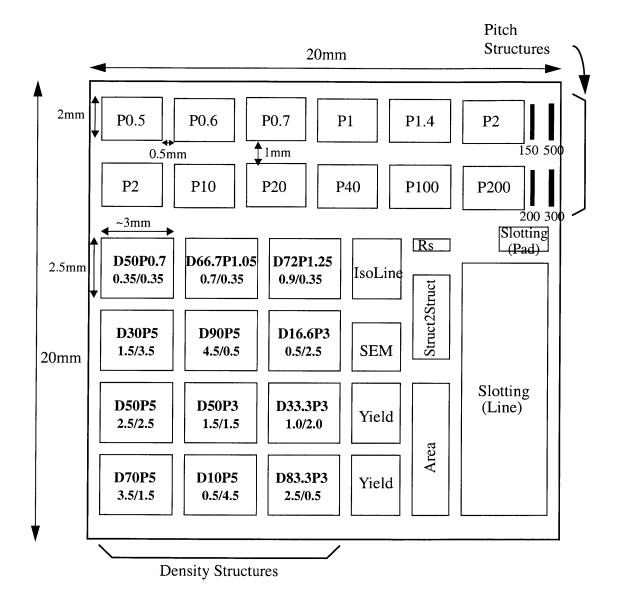

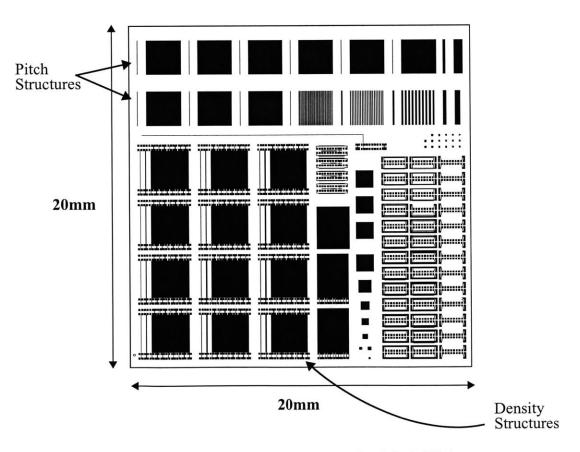

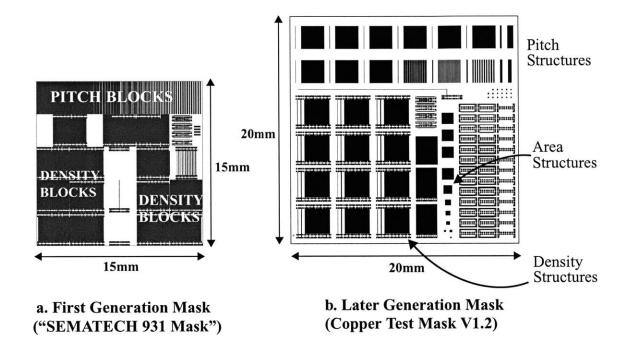

| Figure 3.4: Single-Level Mask Floorplan                                                  | 48    |

| Figure 3.5: Single-Level Copper Test Mask V1.2                                           | 49    |

| Figure 3.6: Sample Measurement Plan                                                      |       |

| Figure 4.1: Non-Uniform Topography in Copper Electroplating (Superfill)                  | 54    |

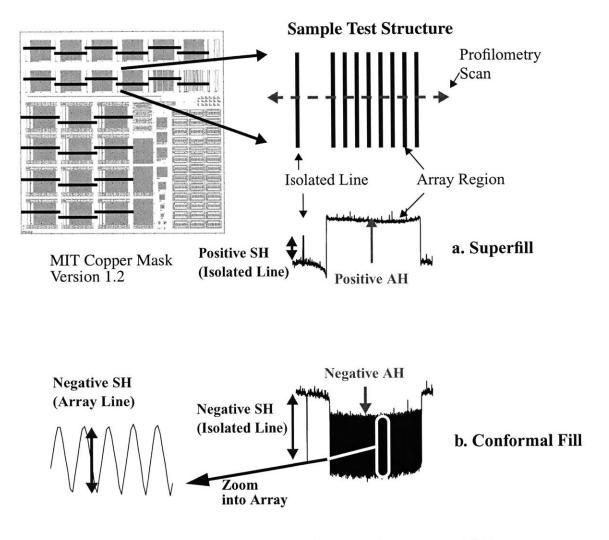

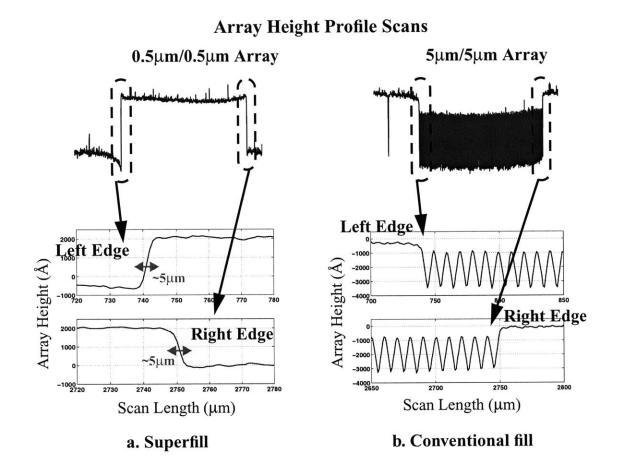

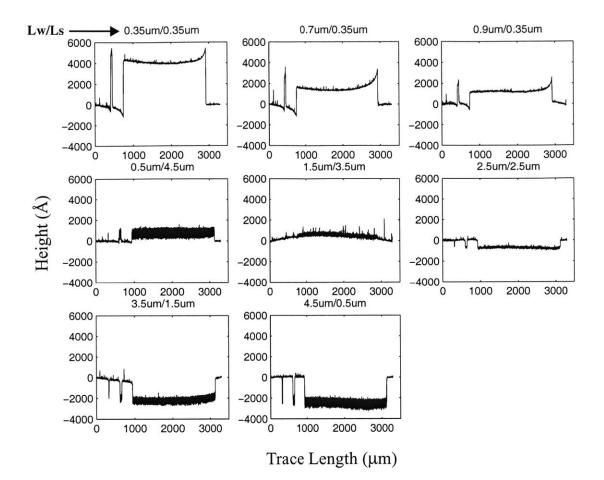

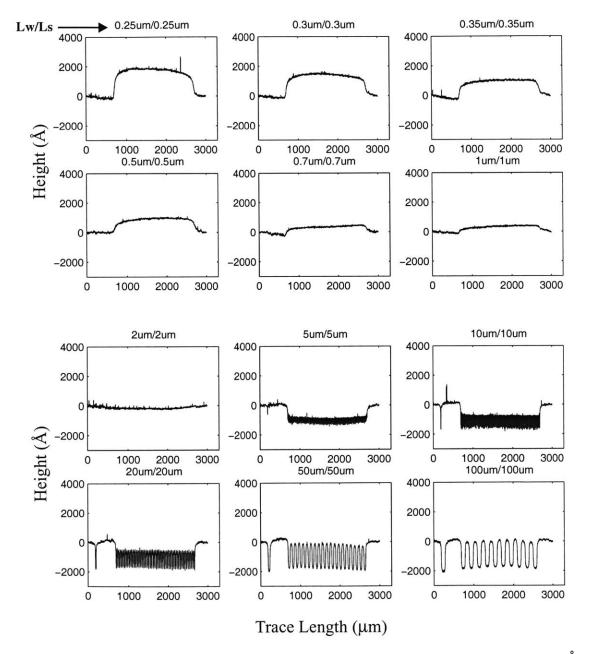

| Figure 4.2: Test Pattern and Sample Profile Scans for (a) Superfill Plating, and (b) Con |       |

| mal Fill                                                                                 |       |

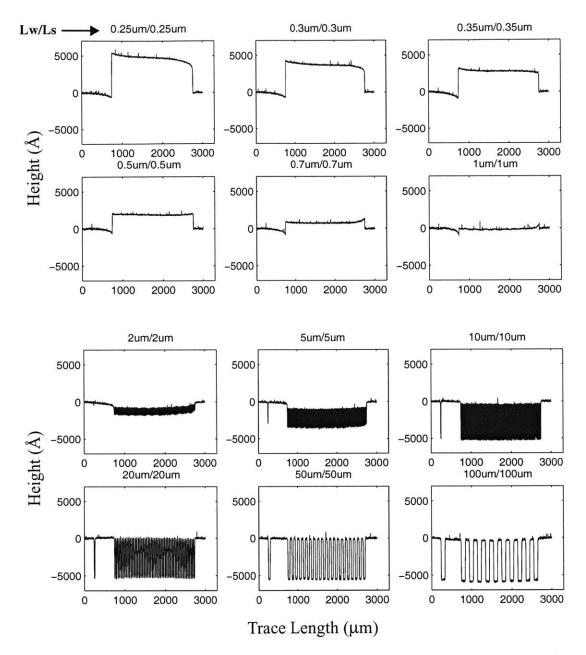

| Figure 4.3: Surface Topography Profiles for Pitch Structures (50% Pattern Density): P    | 'lat- |

| ing Experiment A                                                                         |       |

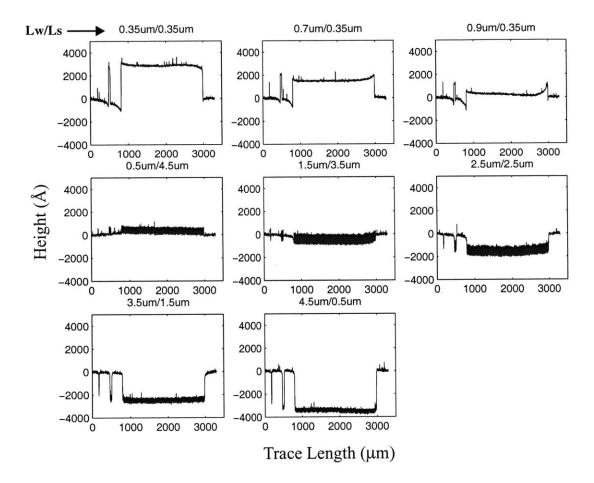

| Figure 4.4: Surface Topography Profiles for Density Structures (Varying Pitch): Platin   |       |

| Experiment A                                                                             |       |

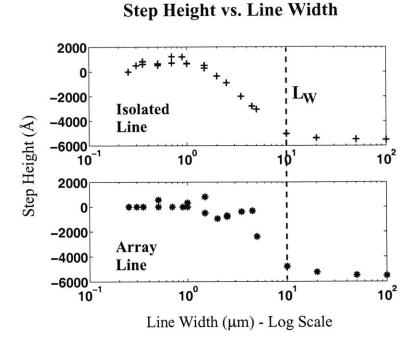

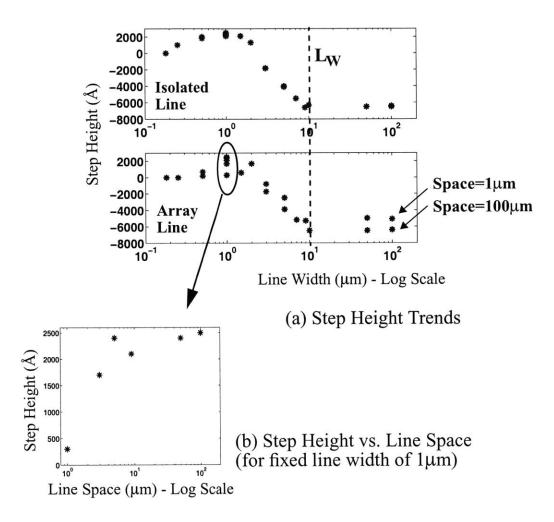

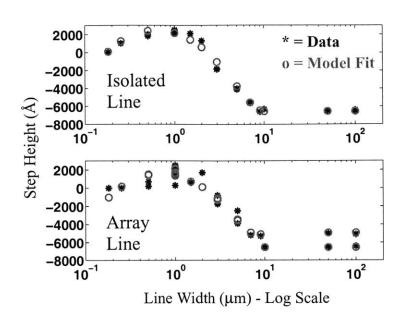

| Figure 4.5: Step Height vs. Line Width for Isolated Lines and Array Lines: Plating Ex    |       |

| iment A                                                                                  |       |

| Figure 4.6: Fill Characteristics for Different Trench Widths                             |       |

| Figure 4.7: Step Height vs. Line Space for Array Lines: Plating Experiment A             |       |

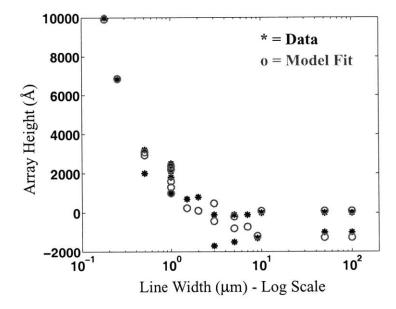

| Figure 4.8: Array Height vs. Line Width in Log Scale: Plating Experiment A               |       |

| Figure 4.9: Array Height: Bulge and Recess                                               |       |

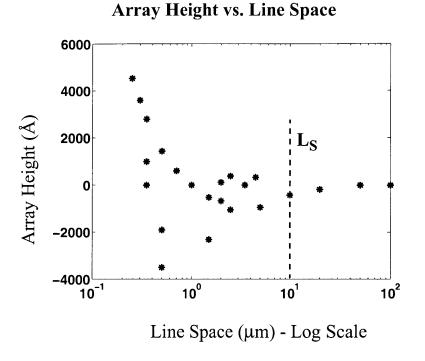

| Figure 4.10: Array Height vs. Line Space: Plating Experiment A                           |       |

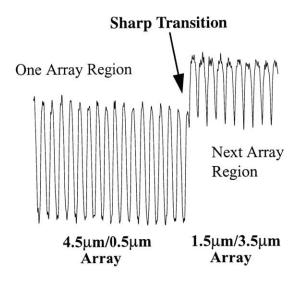

| Figure 4.11: Sharp Transition from Field to Array Region: Plating Experiment A           |       |

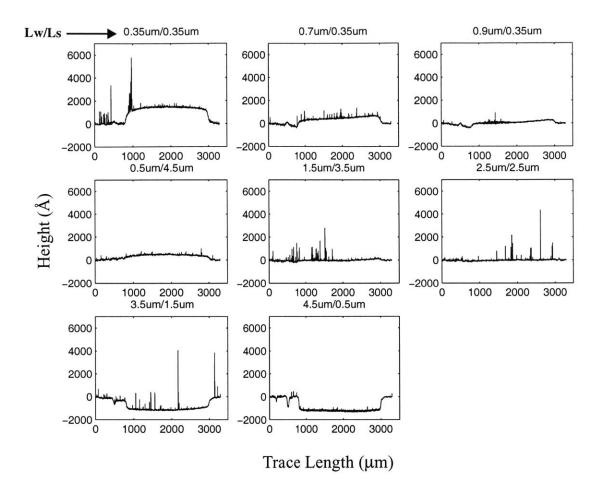

| Figure 4.12: Nearest Neighbor Effect in Electroplating: Plating Experiment A             | 66    |

| Figure 4.13: Line Space Effect and Interactions with Line Width:                         |       |

| Plating Experiment B                                                                     |       |

| Figure 4.14: Basic Mechanism for Blanket Wafer                                           |       |

| Figure 4.15: Basic Mechanism for Different Trench Width                                  |       |

| Figure 4.16: Basic Mechanism for Different Spacing Width                                 |       |

| Figure 4.17: Diffusion-Adsorption Based Model Proposed by IBM [4]                        |       |

| Figure 4.18: Illustration of Additive Adsorption-Accumulation Behavior During Elect      | ro-   |

| plating Fill                                                                          | 76   |

|---------------------------------------------------------------------------------------|------|

| Figure 4.19: Accelerator-Accumulation: Dependence on Aspect Ratio                     | 77   |

| Figure 4.20: Step Height Model Fit vs. Line Width: Plating Experiment A               | 81   |

| Figure 4.21: Array Height Model Fit vs. Line Width: Plating Experiment A              | 83   |

| Figure 4.22: Step Height Model Fit vs. Line Width: Plating Experiment B               | 85   |

| Figure 4.23: Array Height Model Fit vs. Line Width: Plating Experiment B              |      |

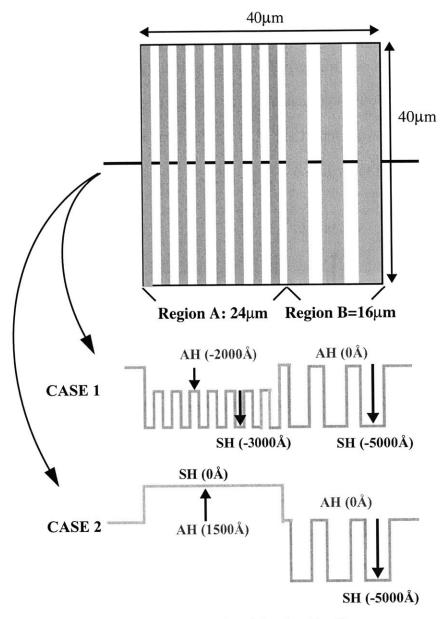

| Figure 5.1: Example Grid Cell and Cross Sectional View of Plated Profile              | 89   |

| Figure 5.2: Positive and Negative Step Height Cancellation Effect                     | 90   |

| Figure 5.3: Example "Random Layout" Grid Cell                                         |      |

| Figure 5.4: Definition of Line Width and Line Length                                  | 92   |

| Figure 5.5: Example Grid Cell for Binning Calculations                                | 95   |

| Figure 5.6: Step Height and Array Height vs. Line Width and Bin Cutoffs               | 96   |

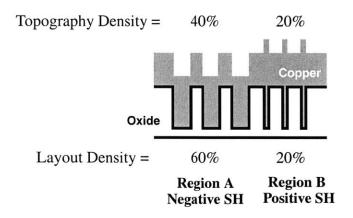

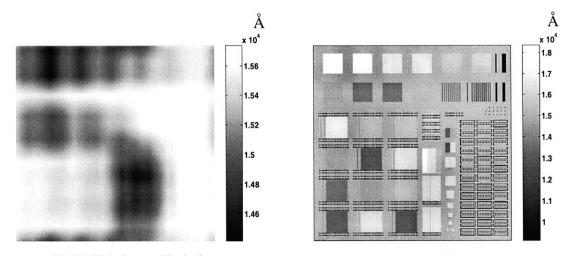

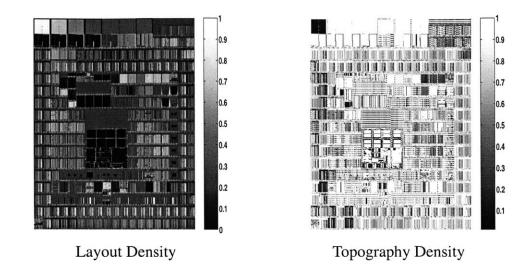

| Figure 5.7: Topography Density vs. Layout Density                                     | .101 |

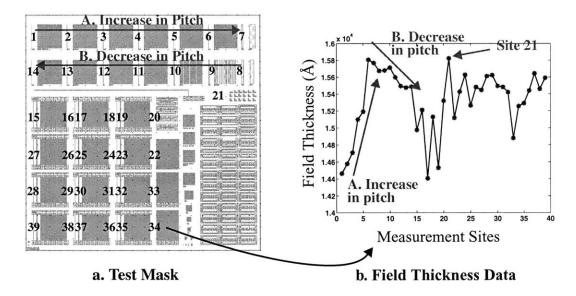

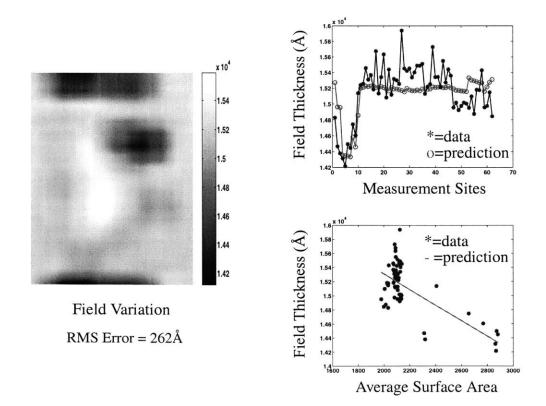

| Figure 5.8: Field Thickness Measurement and Data                                      | .102 |

| Figure 5.9: Initial Copper Profile and Influence on Copper Removal                    | .104 |

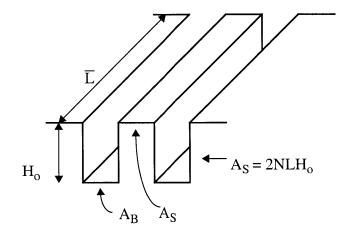

| Figure 5.10: Surface Area Calculation                                                 | .105 |

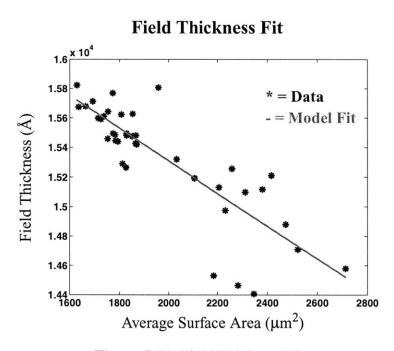

| Figure 5.11: Field Thickness Fit                                                      | .107 |

| Figure 5.12: Chip-Scale Simulation for MIT mask v1.2:                                 |      |

| Array Height and Step Height                                                          | .109 |

| Figure 5.13: Chip-Scale Simulation for MIT mask v1.2:                                 |      |

| Field Thickness Variation and Total Thickness Maps                                    | .110 |

| Figure 5.14: Chip-Scale Simulation for MIT mask v1.2:                                 |      |

| Layout Density and Topography Density                                                 |      |

| Figure 5.15: Prediction and Verification of Chip-Scale Simulation                     | .112 |

| Figure 5.16: Sample Profile Scan of Verification Data                                 |      |

| Figure 5.17: Chip-Scale Prediction and Verification: Array Height                     |      |

| Figure 5.18: Chip-Scale Prediction and Verification: Step Height                      |      |

| Figure 5.19: Chip-Scale Prediction and Verification: Field Thickness                  |      |

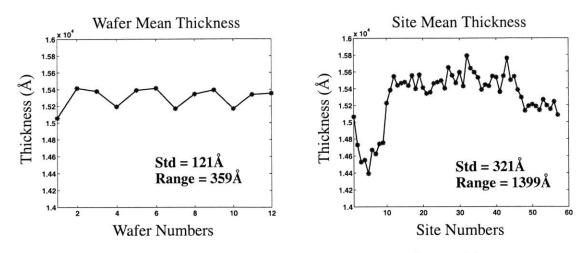

| Figure 5.20: Chip-Scale Prediction: Final Thickness                                   | .116 |

| Figure 5.21: Chip-Scale Prediction:                                                   |      |

| Layout Density and Topography Density                                                 |      |

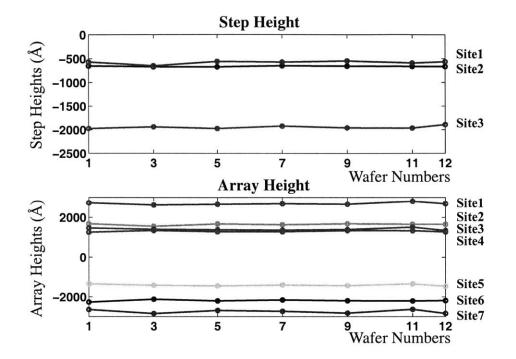

| Figure 5.22: Step Height & Array Height Variability from Wafer to Wafer               |      |

| Figure 5.23: Field Thickness Variability from Wafer to Wafer                          |      |

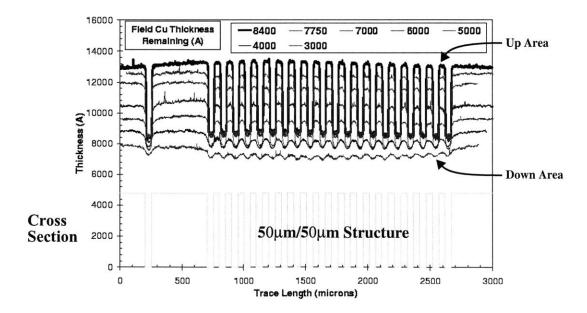

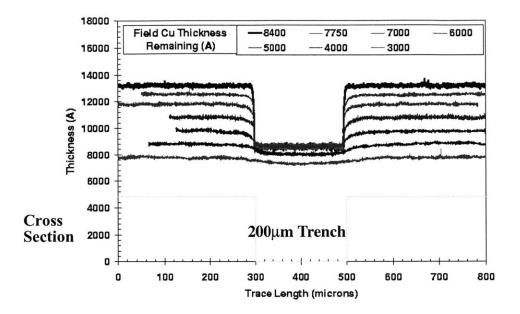

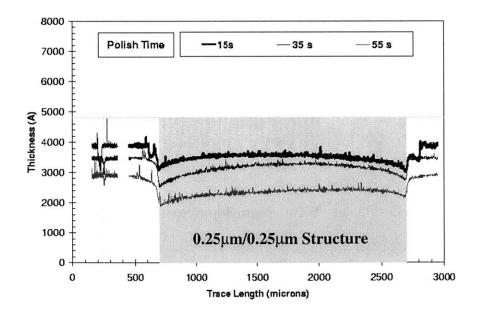

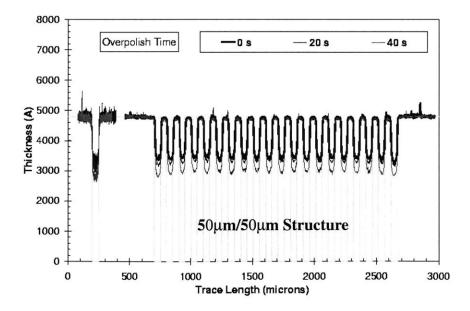

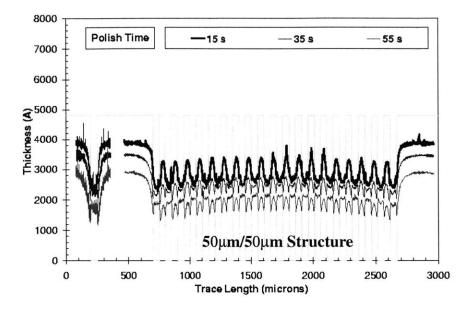

| Figure 6.1: Bulk Copper Polishing: Fine Feature                                       |      |

| Figure 6.2: Bulk Copper Polishing: Large Feature                                      |      |

| Figure 6.3: Bulk Copper Polishing: Large Trench                                       |      |

| Figure 6.4: Initial Surface Heights for Pitch Structures                              |      |

| Figure 6.5: Initial Surface Heights for Density Structures                            |      |

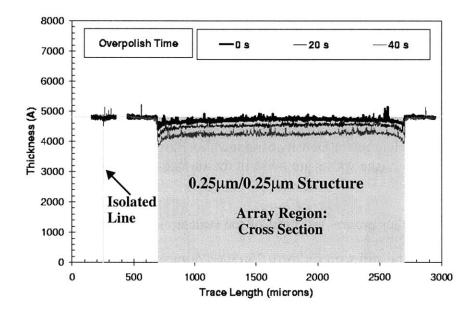

| Figure 6.6: Surface Heights for Pitch Structures for Target Field Thickness of 5000Å  |      |

| Figure 6.7: Surface Heights for Density Structures for Target Field Thickness of 5000 |      |

| (the spikes are noise in the surface trace)                                           |      |

| Figure 6.8: Copper Clearing and Overpolish: Fine Feature                              |      |

| Figure 6.9: Copper Overpolish: Fine Feature                                           |      |

| Figure 6.10: Copper Clearing and Overpolish: Large Feature                            |      |

| Figure 6.11: Copper Overpolish: Large Feature                                         |      |

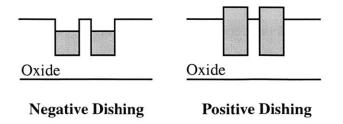

| Figure 6.12: Positive and Negative Dishing                                            | .134 |

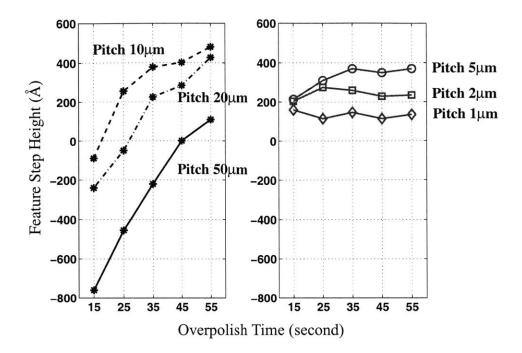

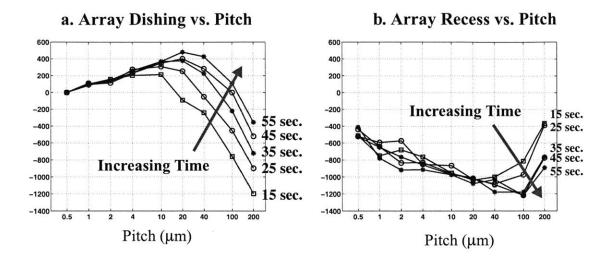

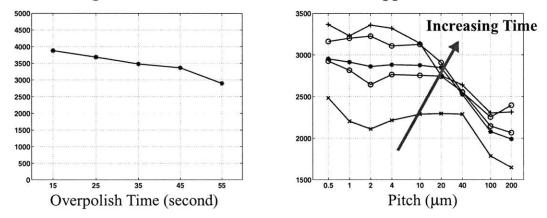

| Figure 6.13: Array Dishing vs. Overpolish Time135                                         | 5 |

|-------------------------------------------------------------------------------------------|---|

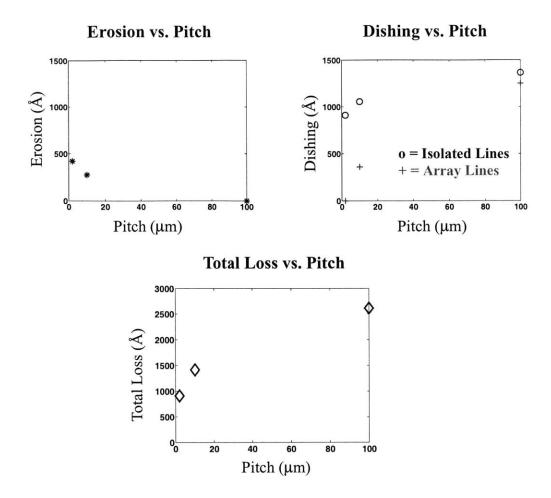

| Figure 6.14: Array Dishing vs. Pitch136                                                   | 5 |

| Figure 6.15: Surface Profiles Showing Dishing and Erosion Trends in the Line/Array Struc- | - |

| tures                                                                                     | 9 |

| Figure 6.16: Surface Topography and Copper Thickness Variation vs. Pitch140               | ) |

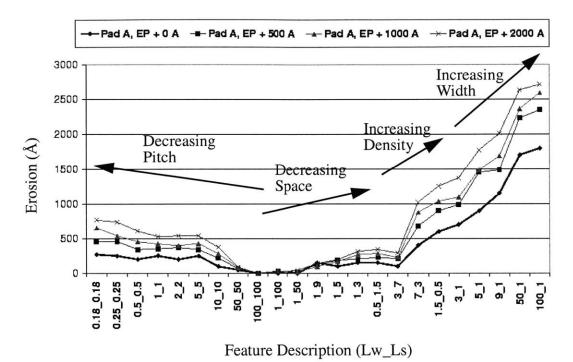

| Figure 6.17: Erosion for Pad A vs. Features141                                            | 1 |

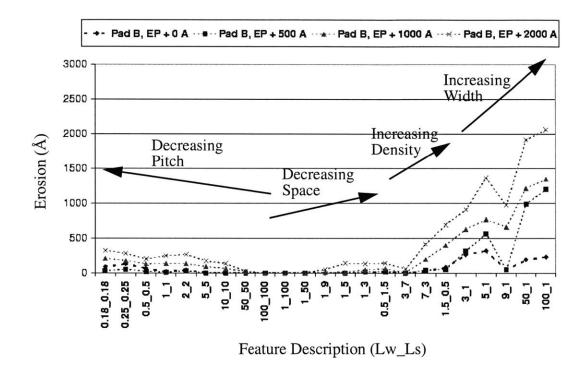

| Figure 6.18: Erosion for Pad B vs. Features142                                            | 2 |

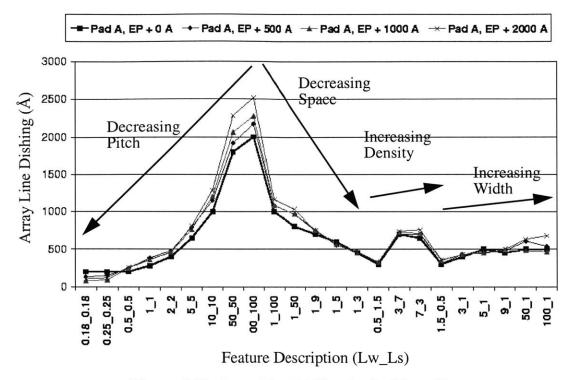

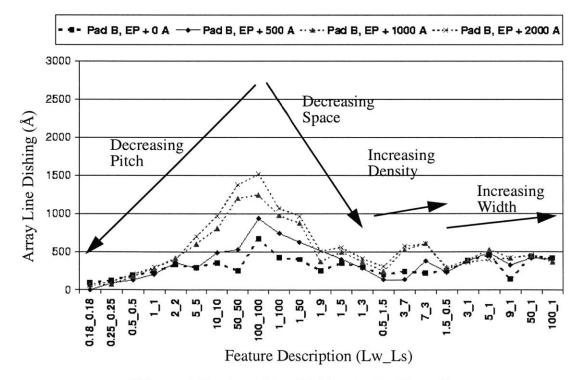

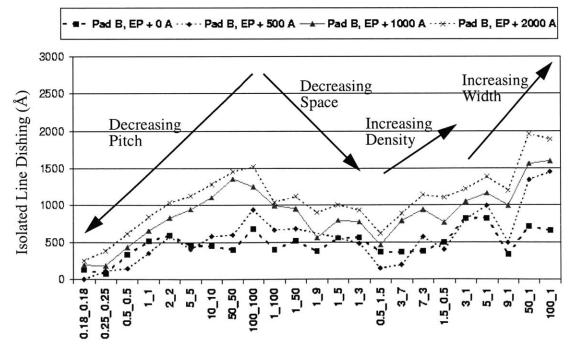

| Figure 6.19: Array Line Dishing for Pad A vs. Features                                    | 3 |

| Figure 6.20: Array Line Dishing for Pad B vs. Features143                                 | 3 |

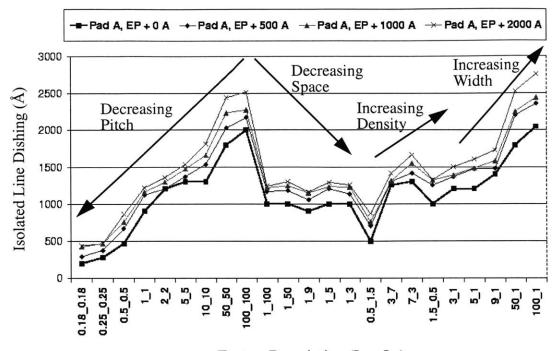

| Figure 6.21: Isolated Line Dishing for Pad A vs. Features144                              | 4 |

| Figure 6.22: Isolated Line Dishing for Pad B vs. Features144                              | 4 |

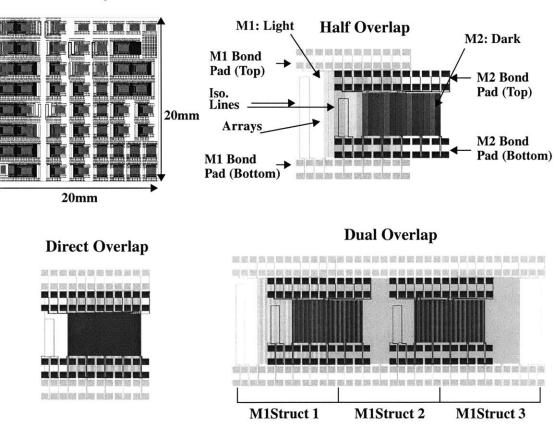

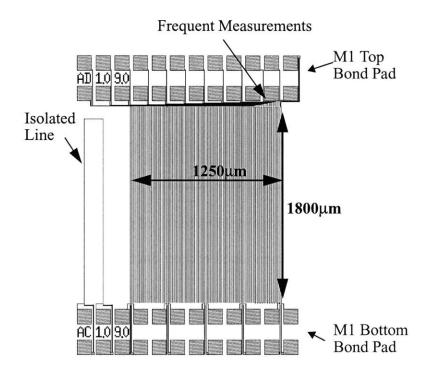

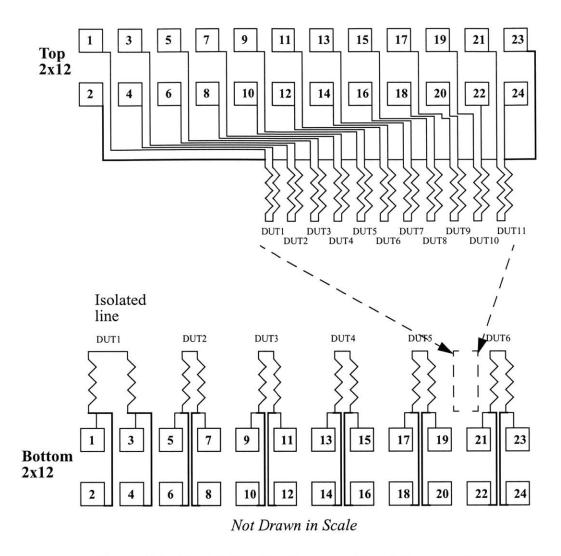

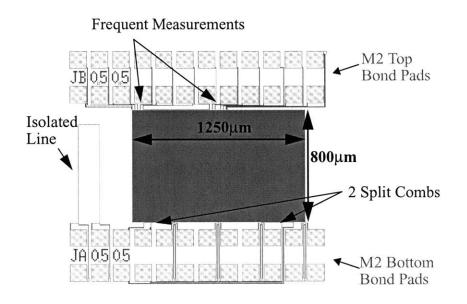

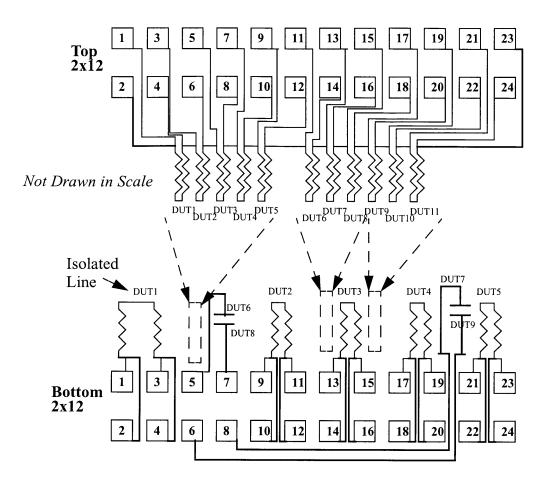

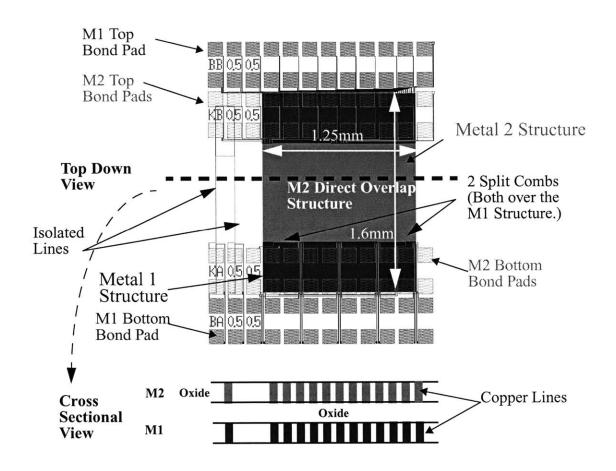

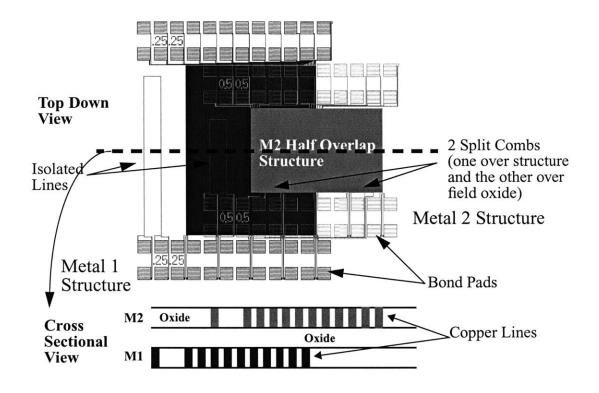

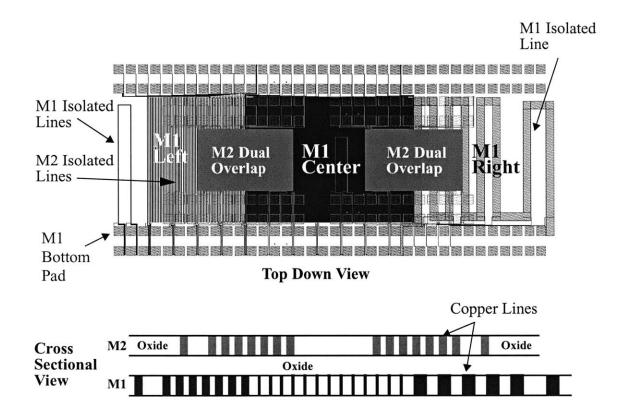

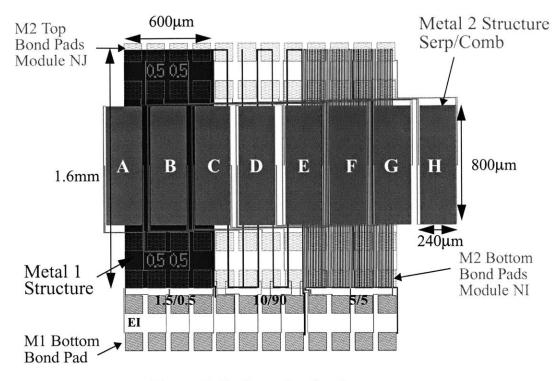

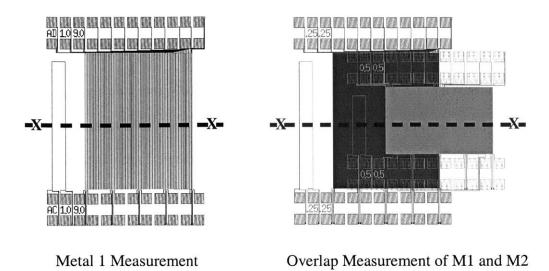

| Figure 6.23: Mask and Test Structure Layout146                                            | 6 |

| Figure 6.24: Multi-level Process Sequence                                                 | 9 |

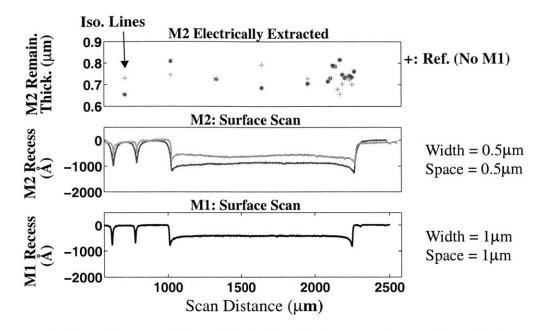

| Figure 6.25: Direct Overlap: M1 and M2 Surface Profile and Extracted Cu Thickness 150     | 0 |

| Figure 6.26: Half Overlap: M1 and M2 Surface Profile and Extracted Cu Thickness15         | 1 |

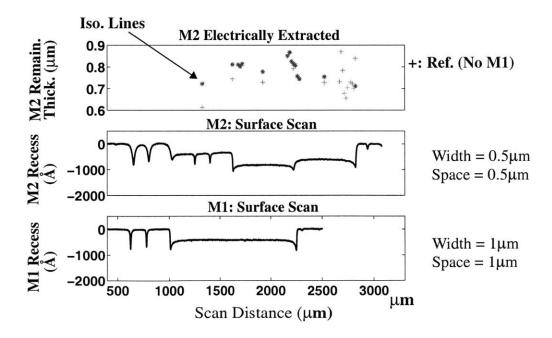

| Figure 6.27: Dual Overlap: M1 and M2 Surface Profile and Extracted Cu Thickness152        |   |

| Figure 6.28: Direct Overlap: M1 and M2 Surface Profile and Extracted Cu Thickness 15.     | 3 |

| Figure 6.29: Half Overlap: M1 and M2 Surface Profile and Extracted Cu Thickness15.        | 3 |

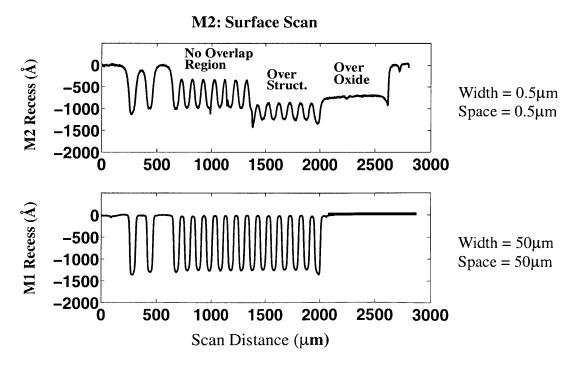

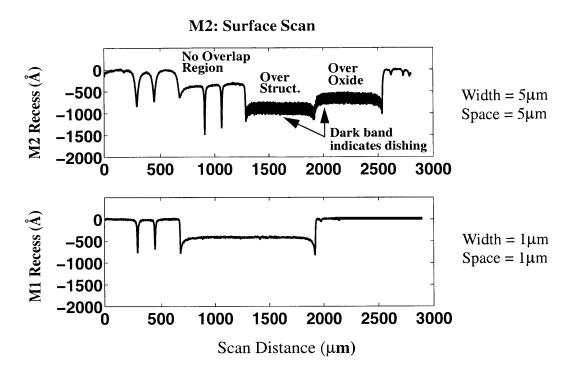

| Figure 6.30: Surface Profiles for Half Overlap: Propagation of M1 Dishing to              |   |

| M2 Profile154                                                                             | 4 |

| Figure 6.31: Surface Profiles for Half Overlap: Propagation of M1 Recess to M2 Recess     |   |

| and Dishing15                                                                             | 5 |

| Figure 6.32: Contact Mechanics from Yoshida [43]15                                        |   |

| Figure 6.33: Stage 1: Removal Rate Diagram15                                              |   |

| Figure 6.34: Stage 3: Removal Rate Diagram15                                              | 9 |

| Figure 6.35: Sample Electroplated Topography and the Associated "Envelope"                | 9 |

| Figure 6.36: Integrated Implementation of Contact Mechanics and Density-Step Height       |   |

| Model16                                                                                   |   |

| Figure 6.37: CMP Prediction Result of Dishing and Erosion for an Arbitrary Layout16       |   |

| Figure 6.38: Envelope (Array Height) in Discretized Cells16                               | 3 |

| Figure 6.39: Integration of Electroplating Model and CMP Model for Complete Chip-Leve     |   |

| Simulation16                                                                              |   |

| Figure 6.40: Impact of Plating Topography on CMP Erosion16                                | 6 |

## List of Tables

| Table 4.2: Step Height (SH) Fit81Table 4.3: Array Height (AH) Fit82Table 4.4: Array Height (AH) New Model Form (without 1/w term) Fit83Table 4.5: Process B: Step Height (SH) Fit84Table 4.6: Process B: Array Height (AH) Fit85Table 5.1: Example Layout Extraction97Table 5.2: Assigned Line Width for Each Distribution98Table 5.3: Field Model Fit107Table 5.4: Standard Deviations and Range for Wafer to Wafer118 | Table 4.1: Example of Line Width and Line Space Transformation | 80  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-----|

| Table 4.3: Array Height (AH) Fit82Table 4.4: Array Height (AH) New Model Form (without 1/w term) Fit83Table 4.5: Process B: Step Height (SH) Fit84Table 4.6: Process B: Array Height (AH) Fit85Table 5.1: Example Layout Extraction97Table 5.2: Assigned Line Width for Each Distribution98Table 5.3: Field Model Fit107                                                                                                | Table 4.2: Step Height (SH) Fit                                | 81  |

| Table 4.4: Array Height (AH) New Model Form (without 1/w term) Fit83Table 4.5: Process B: Step Height (SH) Fit84Table 4.6: Process B: Array Height (AH) Fit85Table 5.1: Example Layout Extraction97Table 5.2: Assigned Line Width for Each Distribution98Table 5.3: Field Model Fit107                                                                                                                                  |                                                                |     |

| Table 4.6: Process B: Array Height (AH) Fit85Table 5.1: Example Layout Extraction97Table 5.2: Assigned Line Width for Each Distribution98Table 5.3: Field Model Fit107                                                                                                                                                                                                                                                  |                                                                |     |

| Table 5.1: Example Layout Extraction                                                                                                                                                                                                                                                                                                                                                                                    | Table 4.5: Process B: Step Height (SH) Fit                     | 84  |

| Table 5.2: Assigned Line Width for Each Distribution98Table 5.3: Field Model Fit107                                                                                                                                                                                                                                                                                                                                     | Table 4.6: Process B: Array Height (AH) Fit                    | 85  |

| Table 5.3: Field Model Fit   107                                                                                                                                                                                                                                                                                                                                                                                        | Table 5.1: Example Layout Extraction                           | 97  |

|                                                                                                                                                                                                                                                                                                                                                                                                                         | Table 5.2: Assigned Line Width for Each Distribution           | 98  |

| Table 5.4: Standard Deviations and Range for Wafer to Wafer118                                                                                                                                                                                                                                                                                                                                                          | Table 5.3: Field Model Fit                                     | 107 |

|                                                                                                                                                                                                                                                                                                                                                                                                                         | Table 5.4: Standard Deviations and Range for Wafer to Wafer    | 118 |

### Chapter 1

### Introduction

With ever-decreasing dimensions and ever-increasing complexity of layout patterns in integrated circuits (IC), semiconductor manufacturing is continually faced with great challenges and difficulties. Over the years, tighter constraints have been imposed on process margins and specifications, and this kind of limitation on process window is projected to be even more severe for later generations of chips [1]. Furthermore, introduction of new materials such as copper and low dielectric constant films for back-end interconnects creates even greater challenges in terms of development of new processes and integration of different materials.

Copper metallization, which has replaced traditional aluminum technology for the state-of-the-art IC's, is expected to have ten levels of metal with as small as 50 Å of copper thickness loss for minimum feature arrays and less than 150 Å of wide copper line loss by year 2010. This is a challenging future requirement for the current chemical mechanical polish (CMP) process, especially when current planarization technology often exceeds 1000 Å of copper loss in dense regions. The constraint on copper planarization is made more difficult by the incoming topography variation from copper electroplating where large bulge or recess may be present depending on the size of feature arrays, as this incoming topography variation is known to impact CMP performance directly by causing varying removal rates of copper on different pattern regions [2].

The Semiconductor Industry Association (SIA) roadmap calls for a full CMP model in near future with 10% topography accuracy of specification limits. Thus, it is critical to have a systematic methodology for the characterization and modeling of pattern dependent issues and problems in both copper electroplating and subsequent CMP processes, and this is the focus of this thesis work. The research presented here enables rapid and effective development and optimization of each process, and the modeling work for chip-scale topography prediction capability also enables development of relevant layout design rules to limit topography variations.

This chapter is organized into five sections. An overview of copper metallization is given in Section 1.1 with a review of the damascene process used for copper metallization. In Section 1.2, the principles and mechanisms of the electroplating and CMP processes for copper metallization are described. Then, key pattern dependent problems and issues are examined in Section 1.3. Finally, the goal of this thesis is described in Section 1.4, and the thesis organization is given in Section 1.5.

#### **1.1 Introduction to Copper Metallization**

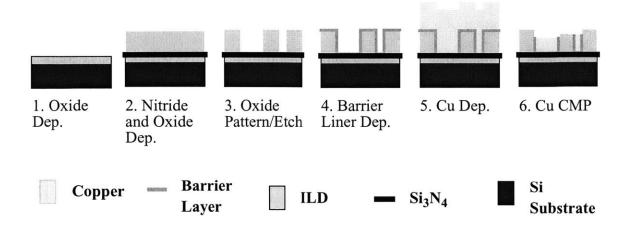

Aluminum has enjoyed over three decades usage as the preferred choice of interconnect in integrated circuits. However, due to performance and process limitations of aluminum metallization (e.g. inherent resistivity, electromigration limitations, and increasing challenge to etch very fine aluminum lines), copper metallization has emerged as the leading interconnect technology for deep sub-micron features. Unlike traditional metallization, where aluminum is deposited on top of inter-level dielectric (ILD), patterned, and etched, copper metallization uses a damascene process. In a damascene process as shown in Figure 1.1, ILD is first deposited and patterned to define "trenches" where the metal lines will lie. Then, a thin layer of barrier material (e.g. tantalum or tantalum nitride with thickness of around 200 Å) is deposited typically using a physical vapor deposition (PVD) process on the entire surface to act as a barrier since copper can readily diffuse into silicon and destroy devices. After the deposition of the barrier layer, a copper seed layer (around 1000 Å thick) is deposited, which serves as a base for the subsequent deposition of copper using electroplating. Once the patterned trenches and field regions are filled with copper as shown in step 5 in Figure 1.1, the CMP process is used to remove the excess metal outside the desired lines.

Figure 1.1: Copper Metallization: Damascene Process

As illustrated above, the copper metallization process involves many integrated processing steps, and two of the key enabling technologies are copper deposition by electroplating and copper removal/planarization by CMP. The underlying barrier material must have strong adhesion to the dielectric material and continuos step coverage across deep trenches with good electrical and electromigration performance. Furthermore, the copper seed layer, which is typically deposited by a PVD process, must be also continuous with high step coverage for adequate sidewall and bottom fills, especially for high aspect ratio trenches.

Once a wafer is coated with the copper seed layer, bulk copper is deposited by electroplating. Many techniques exist for the deposition of copper material on patterned wafers [3]; however, electroplating, which is the same technology used for printed circuit board (PCB) metallization, has become the widely accepted choice for copper deposition [4]. One of the key driving forces for the adoption of electroplating for copper deposition is that this technique enables void-free fills in narrow trenches which is a key requirement for sub-micron feature sizes and high aspect ratios. This void-free fill is often achieved with added chemistries in the copper plating solution so that a higher deposition rate occurs on the bottom of a trench, thus avoiding voids in trenches. Once copper is deposited, it must be removed so that copper only remains in the designed trenches. There is no viable solution for plasma etching of copper, and industry has adopted CMP for copper removal and planarization of the damascene structures.

CMP has emerged as the leading planarization technique in silicon integrated circuit fabrication processes and has been extensively applied for planarization requirements of back-end interlayer dielectrics (ILD) as well as for the front-end shallow trench isolation (STI) process. While other planarization techniques exist, such as spin-on-glass with etch back or other novel deposition and processing, CMP satisfies both the local and global planarity requirements, imposed by lithography depth-of-focus limitations and integration issues for current silicon technologies [5]. In addition, current CMP applications also include polishing of metals such as tungsten [6] and other novel materials which are currently under active research [7, 8]. Finally, CMP has been a key enabler for copper interconnects; one of the first commercial fabrication processes to use copper is pictured in Figure 1.2 [9].

Figure 1.2: Copper Interconnect (6 Levels, Source: IBM)

#### 1.2 Review of Electroplating and CMP: Principles and Mechanisms

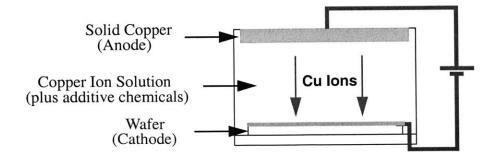

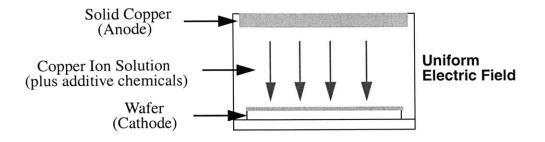

We begin with a brief review of the principles and mechanisms in copper electroplating and CMP. In Section 1.3, we then discuss in more detail a key challenge in the processes related to pattern dependencies. A schematic view of the electroplating tool is shown in Figure 1.3. A wafer surface coated with a thin electrically continuos layer of copper (the seed layer) is immersed in a solution containing copper ions, and the wafer surface is electrically connected to an external power source. Deposition of copper onto the wafer surface occurs by copper ions reacting with electrons to form copper at the wafer surface when current is passed through. The following equation describes the chemical reaction mechanism on the wafer surface which acts as a cathode where cupric ions are reduced to copper atoms.

$$Cu^{2+} + 2e^{-} \to Cu(O) \tag{1.1}$$

The depleted cupric ions in the solution are replenished by the anode which is another active electrical surface in the electroplating system that completes the electrical circuit. The anode, where an oxidation reaction occurs that balances the current flow in the system, is composed of a bulk copper material.

Figure 1.3: Basic Mechanism of Copper Electroplating

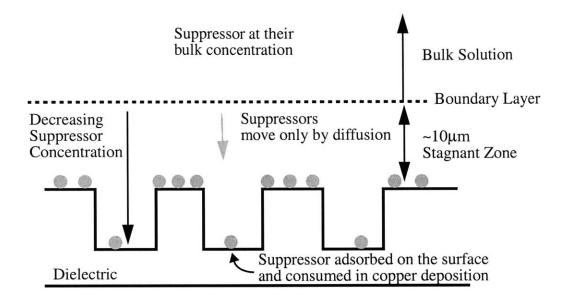

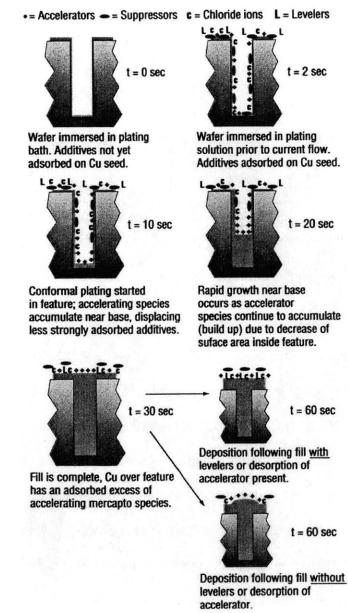

The basic governing principle of deposition is Faraday's law of electrolysis which relates the amount of copper deposited to current density [9]. However, this mechanism is complicated by added chemistry in the copper solution. Typically, these added chemicals are called suppressors and accelerators that are designed to suppress the deposition rate on raised regions while accelerating the deposition rate on the bottom of trenches to achieve void-free fills [10, 11, 12]; such electroplating processes are referred to as bottom-up fill or superfill.

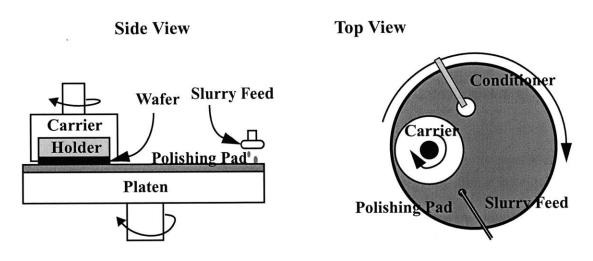

Figure 1.4: CMP Machine

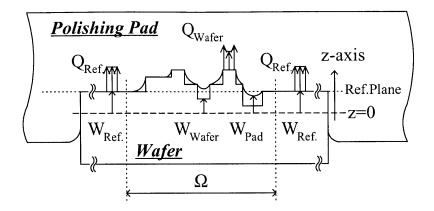

A schematic view of a CMP machine is shown in Figure 1.4. A wafer is held on a carrier typically with a back pressure with the surface to be polished facing down towards a polishing pad. A retainer ring on the outer edge of the carrier head prevents the wafer from slipping out of the carrier during polishing. The wafer is then pressed onto a porous polyurethane polishing pad that is attached to a platen. Both the wafer carrier and the platen are rotated, typically in the same direction with the carrier also having a lapping motion across the pad, and slurry composed of suspended particles in a chemical solution is delivered to the polishing platform. The removal mechanism has two parts. First, the slurry chemically reacts with the wafer surface film to enhance or inhibit removal of particular materials. Second, mechanical abrasion from the relative movements and pressure of pad and wafer with the slurry particles results in the removal of material [13]. Over time, the pad surface becomes glazed and the removal rate decreases resulting in poor polishing performance. In order to keep the integrity of the pad surface and maintain a reliable polish rate, a conditioning head typically with a diamond tip is used to refresh the surface of the pad to maintain the surface characteristics. Other variants of this rotating platform exist such as linear polishing machines, orbital machines, or machines in which the wafer is facing up with a small (smaller than the size of the wafer) polishing pad facing down on a wafer; in all of these tools the basic polishing mechanisms are similar [14].

#### **1.3 Key Problems in Electroplating and CMP**

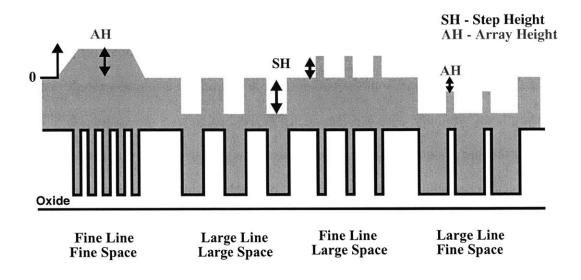

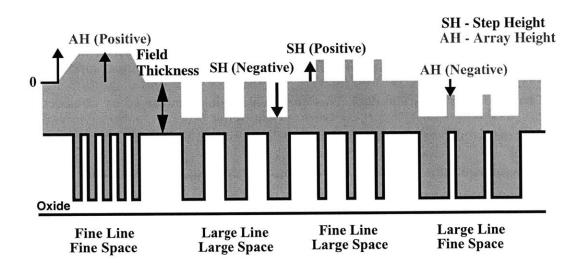

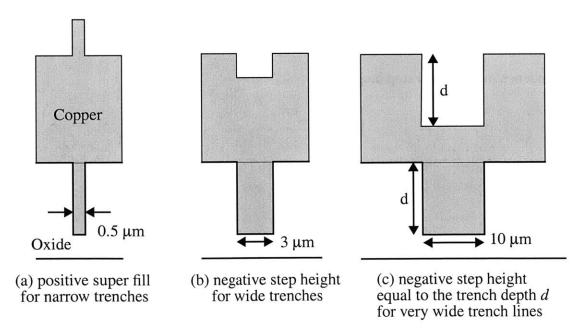

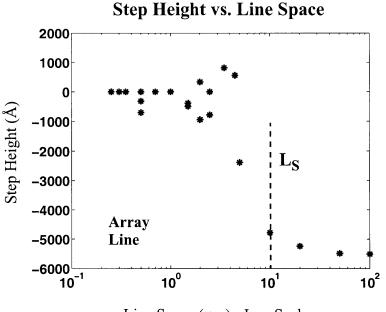

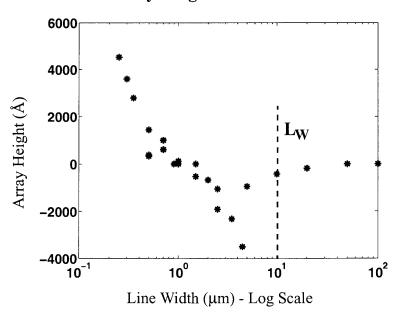

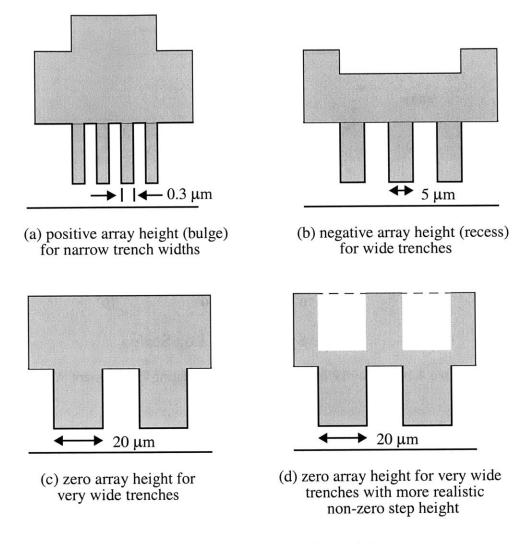

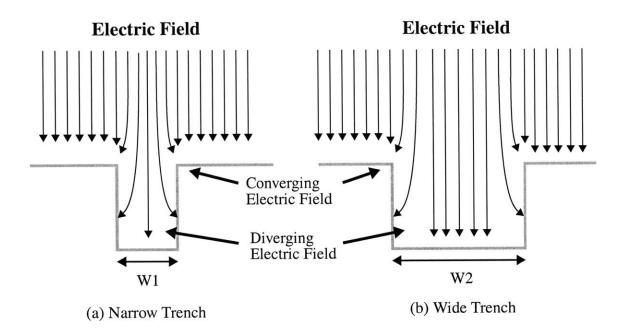

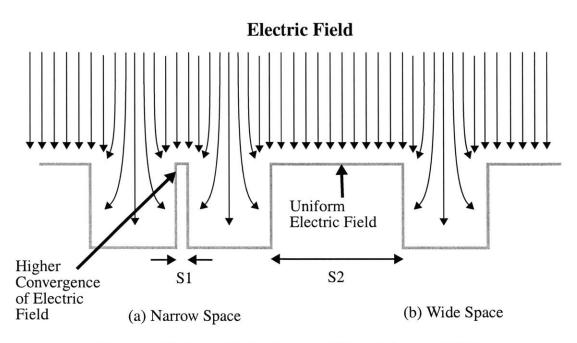

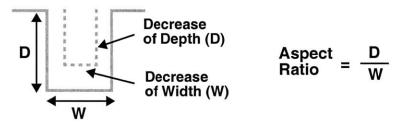

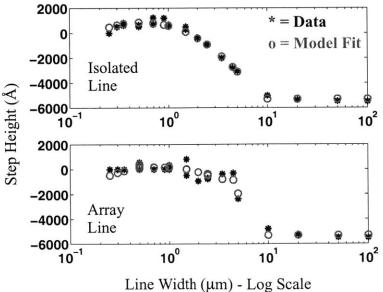

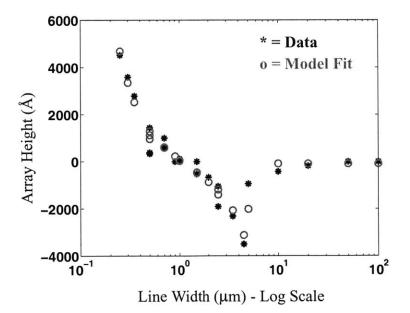

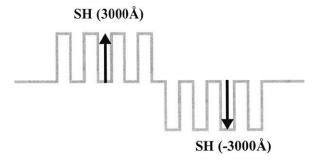

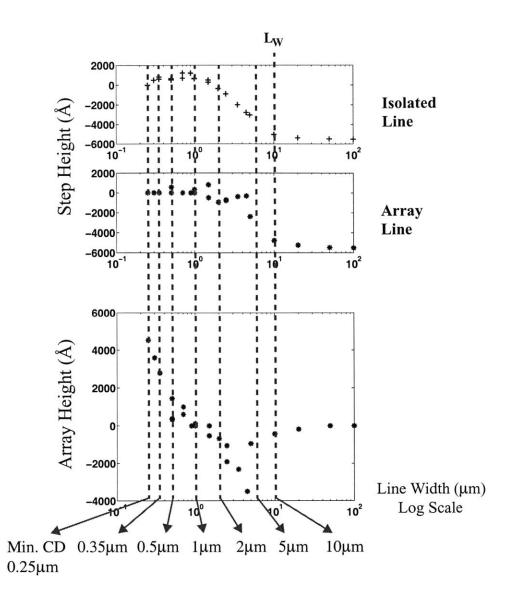

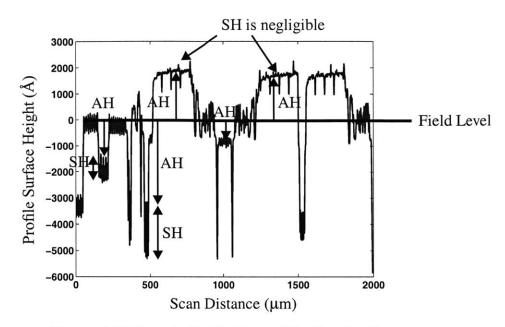

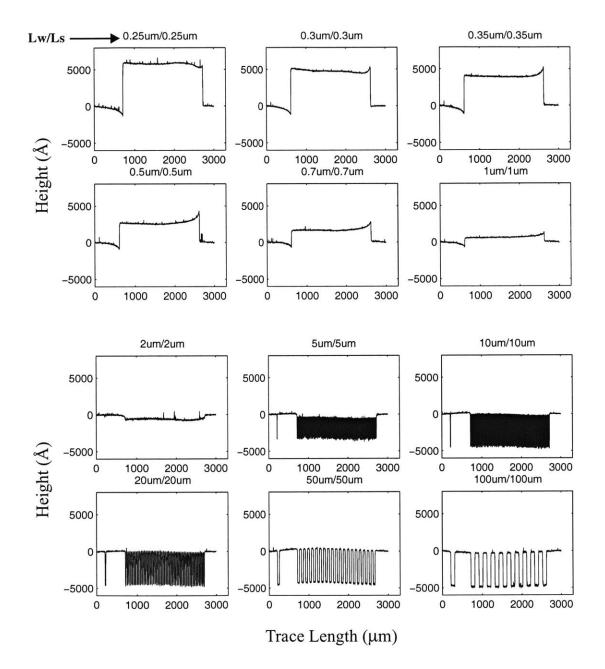

Due to the layout patterns of the underlying trenches to be filled, non-uniform topography exists after electroplating. The resulting topography can be characterized by two height parameters: a feature scale step height (SH) and an array height (AH) — either recess or bulge — as shown in Figure 1.5 for a superfill electroplating. SH is defined as the height associated with each copper line where copper may stick up or recess depending on the feature size, and the AH is measured from the top of the raised features in an array to the flat copper field region over wide oxide. The magnitude of bulge or recess and step heights are dependent on feature sizes including both line width and space. For large features, conformal plating is observed, indicating that there is no impact on large features from the added chemistries to cause superfill. However, for fine arrays of lines, copper is filled above the field level nearby, and for large lines with fine spaces, a recess may be present in the copper surface topography. Also, it is possible to have copper sticking up above a trench when the trenches are narrow and spaces are large. The step and array height trends will be thoroughly examined in Chapter 4.

Figure 1.5: Non-Uniform Topography in Copper Electroplating (Superfill)

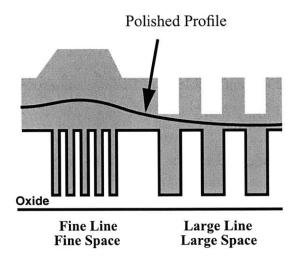

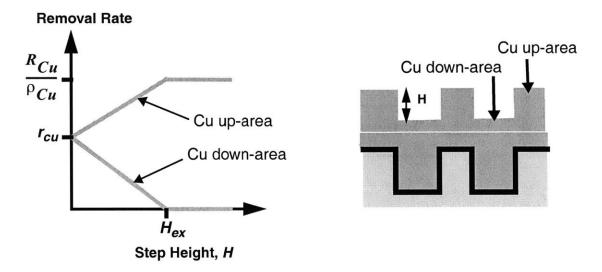

Once a wafer is deposited with copper which exhibits these non-uniform thickness variations, the next step is the CMP process. A copper CMP process is best viewed as having three intrinsic stages [15]. Stage 1 is the removal of bulk copper on top of a barrier layer, and stage 2 is the removal of the barrier layer. In stage 1, we have homogenous (single material) polishing where the copper removal rate on different parts of a die is influenced by the as-plated initial copper topography created by layout patterns and plating characteristics. For example, Figure 1.6 shows two sample regions: a fine array region and a large pitch region. The fine array region has a bulge and polishes roughly at a blanket copper polish rate. Thus, it achieves a relatively flat surface in that local region later than in the large pitch region where raised features with a 50% pattern density see an accelerated copper removal rate compared to the blanket rate. Due to the initial topography, there are differences in removal rates across a die, and thus different parts of a die complete the

removal of excess copper overburden and expose the underlying barrier layer at different polish times. Continued polish beyond barrier removal or overpolish phase is the third intrinsic stage, where additional differential polish rates occur to due material removal selectivity.

Figure 1.6: Initial Copper Profile and Influence on Copper Removal

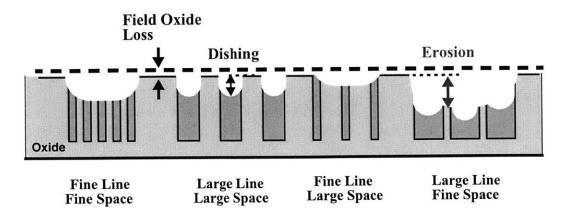

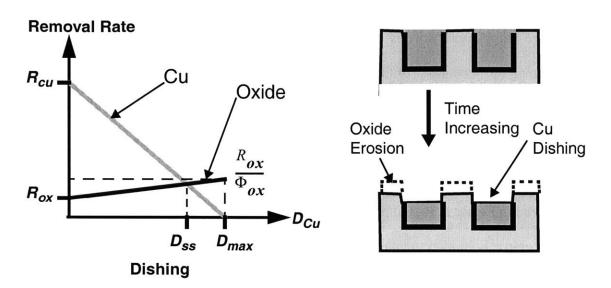

Ideally, the polished copper wafer surface should be perfectly flat; unfortunately, an important non-ideality is that copper lines suffer from dishing and erosion due to CMP. Figure 1.7 shows a cross sectional schematic view of a realistic case suffering from dishing and erosion. Dishing is defined as the recessed height of a copper line compared to the neighboring oxide, erosion is defined as the difference between the neighboring field region and the post-polish oxide height, and field oxide loss is defined as the difference between the original oxide thickness and the post-polish oxide thickness in wide field area as illustrated.

Figure 1.7: Pattern Dependent Problems of Dishing and Erosion In Copper CMP.

These problems of dishing and erosion come from the inherent overpolish stage in copper CMP, and the degree of overpolish depends on two components. First, due to the initial non-uniform topography, there are differences in bulk copper removal rates and thus different regions have different clearing times to the underlying barrier layer. Thus, using the example illustrated above, the region with fine arrays which starts out with a bulge would see a slower clearing time exposing the barrier layer later and thus receive less overpolish. This will result in decreased dishing and erosion for that structure. The second component that adds to the total degree of non-uniformity is the fact that during the barrier and overpolish, we are again polishing pattern regions created by copper trenches and oxide spacings. Thus, these regions will now again see differences in removal rates of copper and oxide and cause added dishing or erosion on top of what is already caused by the differences in clearing time due to the initial copper topography. Thus, the plated topography strongly affects CMP performance, and it is important that we develop an integrated methodology for understanding these pattern dependent issues of both electroplating and CMP.

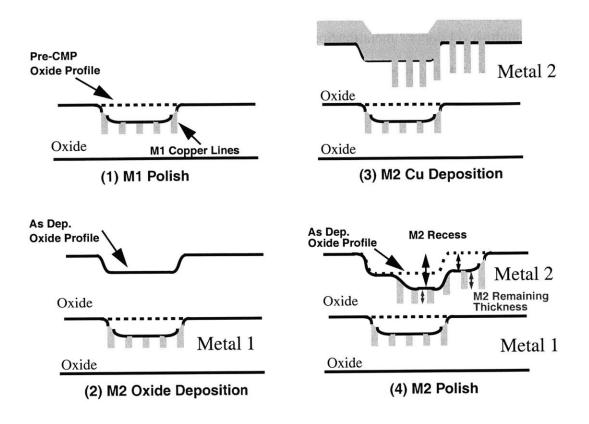

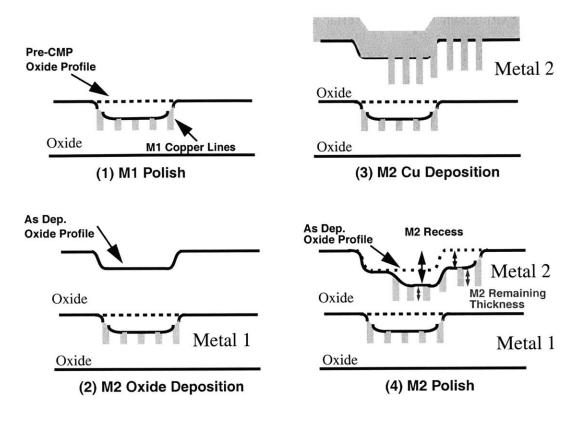

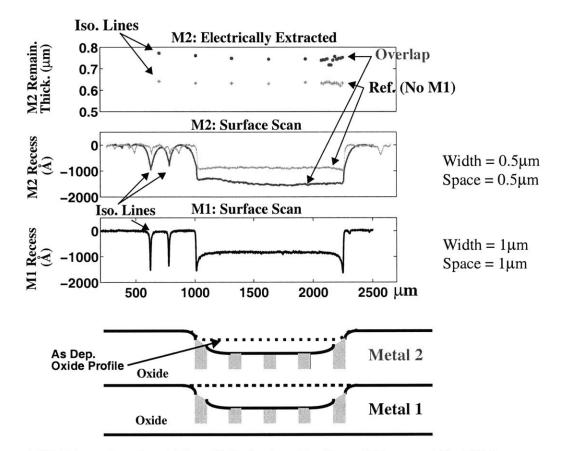

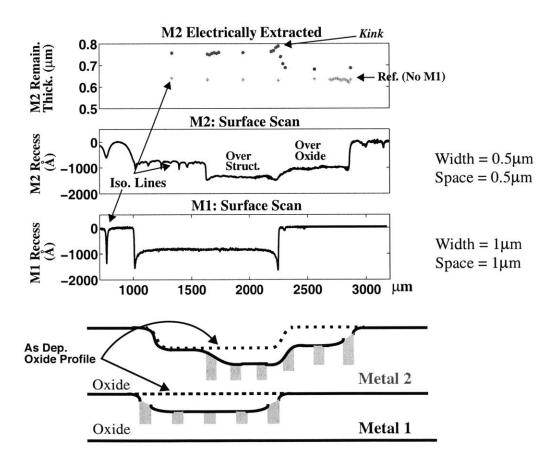

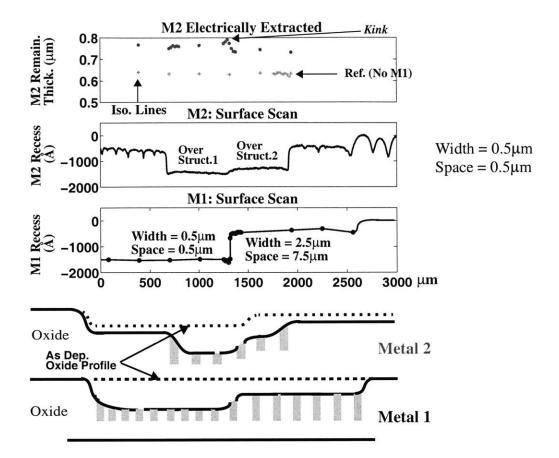

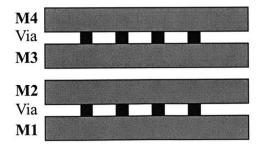

Beyond the non-uniformity problems in single-layer CMP processes, we must also consider multi-level copper metallization and its non-uniform topography and thickness variation. Figure 1.8 illustrates the processing sequence of multi-level copper metallization in a schematic format (excluding the via layer for the sake of simplicity). (1) After metal 1 polish, there is a certain amount of oxide recess across a structure region. (2) Because of this starting recess on the metal 1 layer, conformally deposited metal 2 oxide has a similar recess shape as the metal 1 recess. (3) The pattern and etch of the uneven oxide makes the bottom of the copper trenches uneven, and the copper deposition profile is also influenced by the uneven profile shape in addition to any non-uniform depositions from electroplating itself. (4) After copper deposition, the wafer is planarized by CMP.

What we are interested in are the metal 2 recess and the remaining line thickness in both an overlap region and non-overlap region, and understanding how these are affected by the propagation of non-uniform topography created in the lower level. The topography non-uniformity in the polished metal 2 surface exhibits the similar dishing and erosion problems seen in a single-level polish. However, different degrees of erosion, for example, exist for an uniform array of lines depending on whether a portion of it lies over alreadyrecessed metal 1 region since that region would see higher amounts of recess due to its recessed level even before metal 2 CMP. Another problem in multi-level polishing is that the topography map, often gathered using a surface profiler does not give a complete picture of thickness variation. We have found that electrical measurements of the copper thickness and surface scans are an effective complementary approach to fully characterize multi-level polish behaviors.

Figure 1.8: Multi-Level Process Sequence

These problems of copper thickness variation due to copper dishing, oxide erosion, and field loss are major challenges in advanced copper metallization processes. Such problems can affect chip performance by introducing variable differences in resistance and capacitance depending on line locations within a chip, and the different amount of dishing and erosion also leads to considerable surface non-planarity with consequent manufacturability and process integration difficulties. These problems are seen to largely depend on underlying layout patterns such as pattern density or pattern pitch. Understanding the initial as-plated topography pattern dependencies is a critical first step for modeling of integrated deposition and polish results.

#### **1.4 Thesis Goals**

Copper metallization is becoming a main stream process with tight constraints on thickness variations after CMP. The complexity of copper planarization is increased by the incoming topography variation from copper electroplating where large bulge or recess may be present depending on the underlying features. Thus, it is critical to have a systematic methodology for the characterization of pattern dependent issues and problems in both copper electroplating and CMP. This characterization methodology must also be coupled to a model that captures these pattern effects for prediction of plating and CMP results for arbitrary product patterns.

The basis of the methodology includes identifying key layout and process parameters that cause variations in electroplated step heights and CMP dishing/erosion. The identification of the key pattern dependent factor is possible by design of test structures that consist of various pattern factors combining a wide range of line widths and spaces. The design of the test structures is also closely tied with measurement and analysis techniques so that we can effectively capture these dependencies.

Using the same test mask as the vehicle of characterization for both electroplating and CMP, we can study and understand pattern dependent behaviors in each process and furthermore understand how the electroplated topography affects the CMP process. As described earlier, different array heights are possible for an electroplated die depending on the size of features and spacings, and thickness variations of dishing and erosion are present after CMP due to layout patterns. Based on the trends of these non-uniformities, a pattern dependent model can be formulated. With characterization and model formulation, one can understand the fundamental limitations of these thickness variations for a specific process. In addition to experimentally inducing and characterizing pattern dependent thickness variations, a model is needed capable of predicting thickness variations across an entire chip by relating layout parameters such as pattern density and line width with calibrated model coefficients. Thus, a layout parameter extraction algorithm needs to be developed so that an extracted layout result can be efficiently used with the model in predicting chip-level variations. Furthermore, when chip-scale prediction is possible based on layout parameters, relevant layout design rules can be generated to limit thickness variations after the copper electroplating and CMP process.

In summary, the main goals and objectives of this thesis are as follows:

- 1. Develop test structures and masks to explore key pattern effects in both electroplating and CMP processes.

- 2. Characterize pattern dependent problems in electroplating as a function of underlying pattern features and develop a model to capture the variation.

- 3. Develop layout parameter extraction procedures and apply the electroplating model in chip-scale simulation and prediction for arbitrary layouts.

- 4. Characterize both single level and multi-level CMP pattern dependent effects as a function of underlying pattern features.

- 5. Illustrate the integration of electroplating topography prediction and CMP modeling for predictive chip-scale simulation of final interconnect topography.

#### **1.5 Thesis Organization**

This thesis is organized into seven chapters. Chapter 2 outlines the overall methodology for both electroplating and CMP characterization and modeling and highlights different parts of the overall method with an emphasis on how they integrate to form a coherent methodology for characterizing and modeling interconnect topography.

Once the overall methodology is presented, the subsequent chapters discuss in detail each part of the methodology. Chapter 3 covers the test structure and mask design which is the key first step in experimentally exploring pattern dependencies in a process. Design issues and structure descriptions are presented for a single-level mask. Then, a multi-level mask description is given to study polishing effects in multi-level interconnect processes. In Chapter 4, electroplating characterization is presented and followed by modeling of electroplated non-uniform surface topography. Trends are observed and various proposed physical and superfill mechanisms are examined to formulate model variables. Then, Chapter 5 describes layout parameter extraction and chip-scale simulation using the developed model, and a chip-scale plating prediction result is presented.

Understanding of pattern dependent electroplating non-uniformity is essential for the subsequent CMP process since the initial topography directly impacts the planarization of the CMP process. In Chapter 6, CMP characterization is presented for both single-level and multi-level pattern dependencies. The use of electrical test structures and their analysis are also presented. The ability to gather electrical data, especially for fine lines which are often hard to measure with surface profile tools, is shown to complement surface height measurement. Then, an overview of the pattern dependent CMP model is described followed by the integration of the electroplated topography simulation result and a CMP chip-scale model. Finally, Chapter 7 summarizes the key results and contributions of this thesis and concludes with directions for future research in this area.

### **Chapter 2**

### **Comprehensive Characterization and Modeling Methodology**

Characterization of the pattern dependent non-uniformities in copper electroplating and CMP is needed to understand the fundamental limitations of each process and assist in new process development efforts. For the characterization work to be meaningful and valid, it must be carried out in a systematic and methodical way. This chapter first gives an overall methodology to characterize an electroplating process to understand the plated thickness variations such as step height and array height. The development and application of a pattern dependent electroplating model coupled to the characterization method is presented with an overall goal of chip-scale thickness simulations for any random layouts. Then, a similar methodology is illustrated for the characterization and modeling of the CMP process, with an emphasis on the integration of electroplating and CMP simulations. This chapter is intended to give an overall picture of all the pieces involved in the characterization and modeling work to illustrate how they are interrelated, and the subsequent chapters give details of each individual part of the methodology.

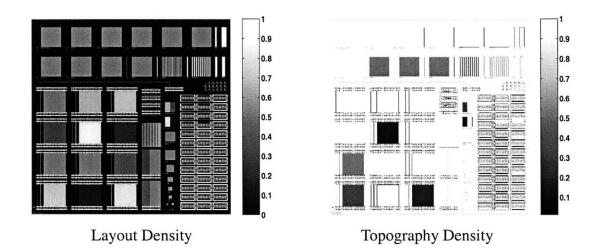

#### 2.1 Electroplating Characterization and Modeling

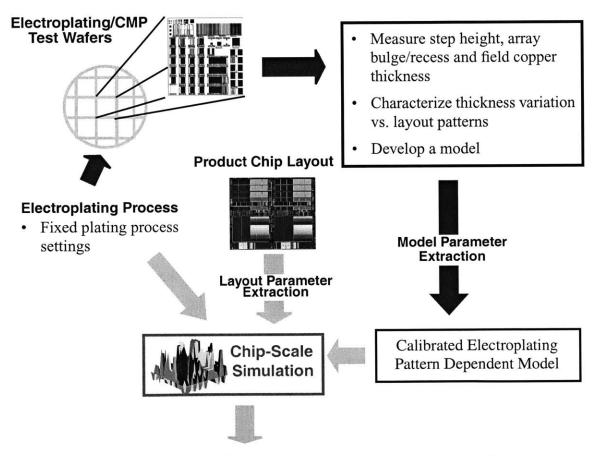

The overall methodology for electroplating characterization and modeling is summarized in Figure 2.1. To characterize as-plated copper topography variation for a particular electroplating process, a wafer patterned with a dedicated test mask is processed. The test mask consists of various combinations of line widths and line spaces to cover a wide range of pattern densities and features. The designed test patterns are used with measurement and analysis techniques to capture and identify key layout dependencies in the plating process. Once a wafer is electroplated, step height and array bulge or recess are measured across many test pattern arrays and isolated features using a surface profiler. Also, field areas (e.g. large region without any copper lines) are measured for the absolute copper thickness so that we can translate relative surface height measurements into absolute thickness throughout the chip. The direct measurement of copper film thickness has become possible due to emerging tools such as the Metapulse system by Rudolph Technologies, or the Impulse 300 system by Philips Analytical.

Prediction of Step Height and Array Height Across a Chip

Figure 2.1: Overall Methodology for Characterization and Modeling of Thickness Pattern Dependency in Copper Electroplating The measured data is analyzed to assess and identify key pattern dependencies, and their trends are examined as a function of specific layout features. This characterization serves as a powerful tool to understand the plating behavior and can help an engineer to identify and resolve any non-uniformity issues before they cause any difficulties in manufacturing or create yield problems. Once a process is fully characterized for its pattern induced thickness profiles, a semi-empirical model is developed incorporating the macrophysics of electroplating; this model captures the key pattern effects as a function of underlying layout patterns. The model can be calibrated for different electroplating recipes.

The model parameters are then extracted, and the calibrated electroplating pattern dependent model can be used to perform chip-scale simulations for the thickness variation for other chips fabricated using the calibrated electroplating process. The chip-scale simulation can be done for any arbitrary layout; to accomplish this, the relevant layout parameters must be extracted before the simulation can be performed. The result of the simulation is step height and array height across an entire chip for the given electroplating process. The simulation result can be used to determine overall non-uniformity as well as to check for any regions on the chip with excess copper bulge or recess. Furthermore, the modelbased simulation can be used to develop intelligent design rules for layout patterns: for example, once any possible trouble spots are determined, the layout can be modified to alleviate the problem by inserting dummy fills to equalize the pattern effects.

Detailed descriptions for each part of the methodology, including the test mask design, non-uniformity characterization and model development, chip-scale simulation and prediction, are presented in Chapters 3, 4, and 5, respectively.

33

#### 2.2 CMP Characterization and Modeling

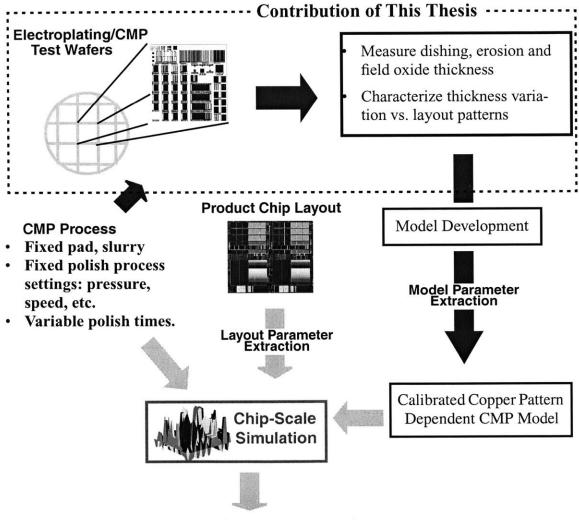

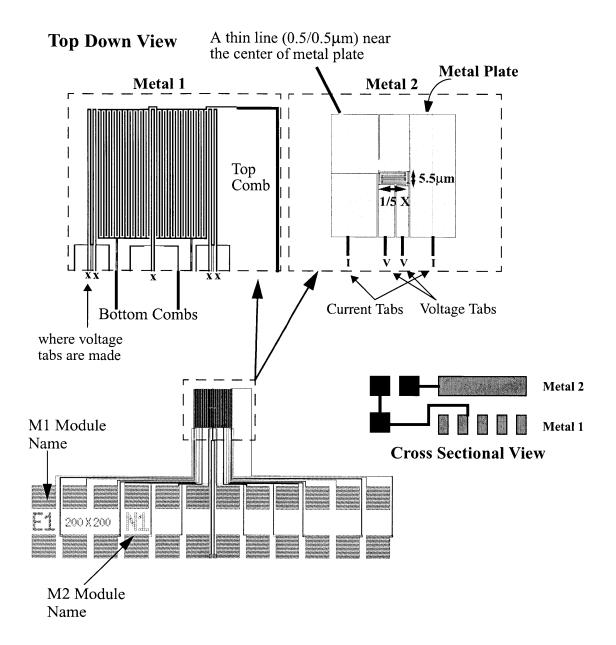

Characterization and modeling of pattern dependent variations of copper dishing and oxide erosion for CMP process is shown in Figure 2.2 and has similar flow as the method used for electroplating. A patterned wafer deposited with copper is polished using a particular process. Then, dishing of copper lines are measured for isolated lines and array lines, and erosion of oxide is measured for array lines using a surface profiler. In addition to these surface measurements, optical field area measurements of dielectric thickness are done to obtain the absolute remaining film thicknesses at various locations such as at either ends of each surface trace. Also, electrical measurements are performed to gather line resistance, which are later converted to copper thickness for comparisons with the surface profile data and optical dielectric film thickness. This electrical data analysis has been found to be particularly useful for multi-level CMP characterization where surface profile scan does not necessarily indicate the remaining copper thickness profile. It has been found that the use of both surface profiles and electrical measurements is necessary to get a complete picture of the polished thickness/surface variations. All of these measurements are done across various pattern regions to ensure that we have a data set that covers wide range of pattern features.

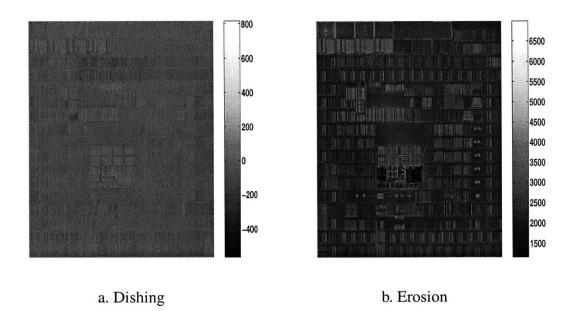

Based on the characterization of the pattern effects and incorporating polishing fundamentals such as blanket removal rates and material removal selectivities, a semi-empirical pattern dependent CMP model is developed. The calibrated copper CMP model can be used for chip-level simulation of any arbitrary layout (e.g. a product chip) using relevant layout parameters extracted from the layout. The chip-scale simulation gives prediction of dishing and erosion and can be used for layout design rules such as assessing the effectiveness of dummyfication. This thesis is not to cover all aspects of this methodology to understand and model CMP variations. Rather, this thesis focuses on the development of the test mask that serves as the foundation for all characterization and modeling work. Then, the thesis presents characterization methodology and result for single layer and multi-layer CMP thickness variations. The modeling and simulation aspects of the methodology are developed by a research colleague, Tamba Tugbawa. Please refer to his Ph.D thesis for the complete description of the modeling work for CMP [16].

Prediction of dishing and erosion

Figure 2.2: Overall Methodology for Characterization and Modeling of Thickness Pattern Dependency in Copper CMP

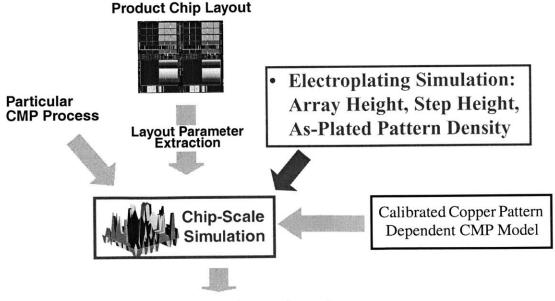

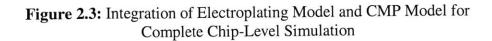

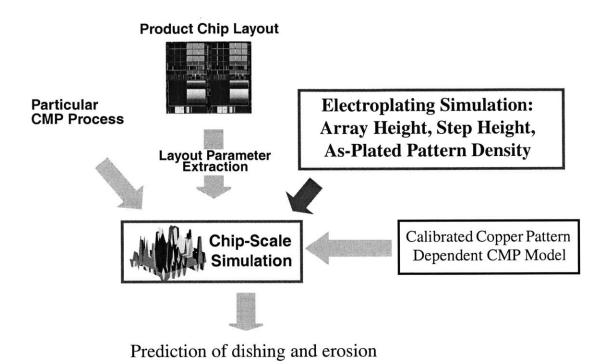

# 2.3 Overview of Integration for Electroplating and CMP Chip-Scale Simulations

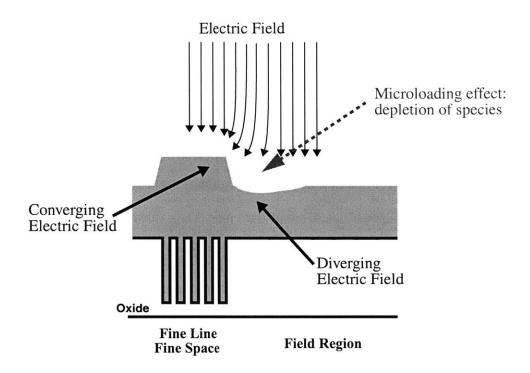

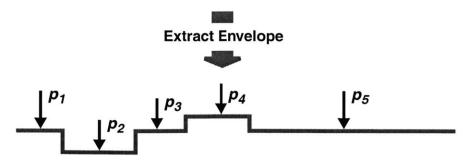

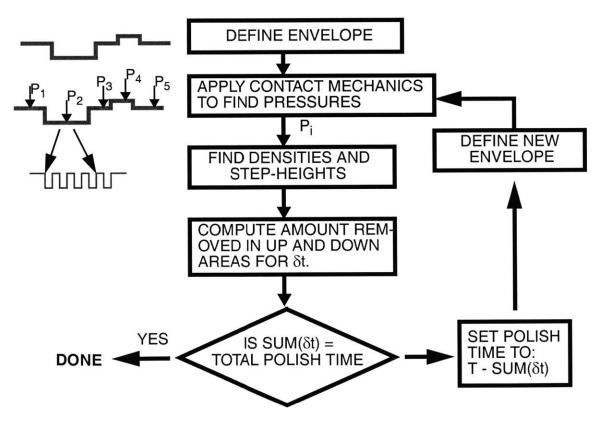

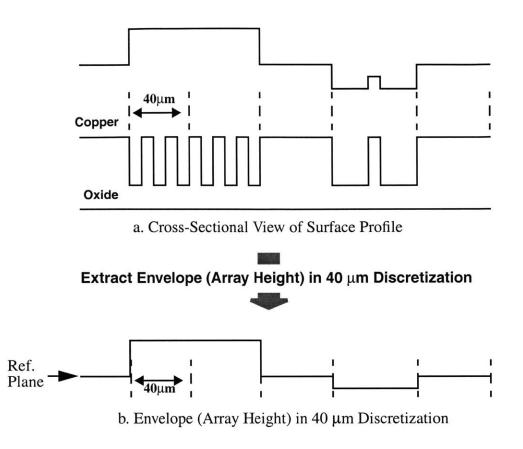

As discussed in Chapter 1, the initial non-uniform topography has a directly impact on the CMP polishing behavior and this topography is created by the pattern dependency in copper deposition in electroplating. Thus, we need to define what topography information is transferred to CMP model so that it can make an effective use of the plating information. The plating topography information needed by CMP is dictated by CMP simulation needs as the calibrated CMP model uses the electroplated topography as the initial condition of the die surface. Specifically, CMP uses the electroplated topography information of final thickness, step height, and as-plated pattern density to calculate removal rates at various locations across a whole chip in bulk copper removal stage. Subsequently, CMP model uses extracted layout parameters of a chip to predict copper dishing and erosion in the third stage of polishing. Figure 2.3 summarizes how the electroplated topography information is fed-forward to the CMP modeling methodology.

Prediction of dishing and erosion

How the electroplated topography is used in the CMP model is summarized in Chapter 6. As it can be seen, each characterization and modeling methodology for electroplating and CMP does not change for the purpose of the integrating the two models for chip level simulation. The integration is efficiently done through three electroplated topography information, array height, step height, final thickness, and pattern density, that are fed-forward to the CMP simulation. This information transfer is done for each discrete unit of grid cells where the grid cells are common in both electroplating and CMP simulations. Thus, all information from electroplating can serve as an input to the CMP model as it is without any alteration or manipulation of the data.

## **Chapter 3**

### **Test Structure and Mask Design**

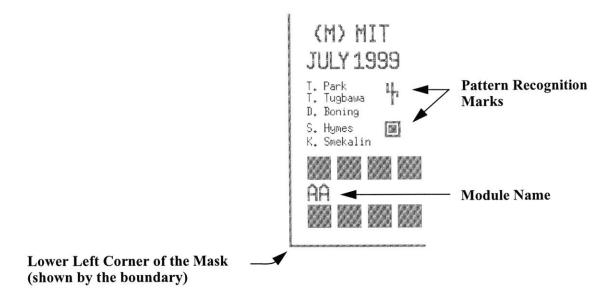

The key underlying vehicle that enables characterization and modeling of copper interconnect pattern dependency is a test mask. In this chapter, we present descriptions of test structures for a single level test mask. Measurement requirements and issues are also illustrated. The test mask described here has evolved from the original copper CMP test mask version 1.0 [17] through many experimental studies and subsequent enhancements of mask designs.

The test mask can be used for rapid characterization of electroplating and CMP characteristics such as consumable/tool comparisons, and process dependencies. Furthermore, these test masks can serve as a vehicle for calibrating and validating physical or semiempirical models. There exist many process and integration issues in copper metallization, some of which are void-free electroplating especially for high aspect ratio trenches, barrier reliability, and CMP endpoint controls. However, the test masks presented in this thesis, including the multi-level mask design presented in Appendix B, are specifically designed to target layout pattern dependent behavior and related studies for copper electroplating and subsequent CMP planarization.

This chapter is organized as follows. First, structure design issues and principles are described including the relevant characteristic length scales in electroplating and CMP processes. Then, a single level mask is described followed by measurement descriptions.

#### **3.1 Structure Design Philosophy and Issues**

The fundamental issue in designing a test mask is understanding what kinds of patterns do actually matter in causing non-uniform topography after processing. Having a

39

wide range of patterns does not necessarily mean that the key pattern problems can be identified. A test reticle should contain relevant pattern factors, such as pattern density, that a process of interest has dependency on. Identifying these pattern factors typically occurs through previous studies or results in similar processes; for example, studies of tungsten CMP process pattern effects can help in assessing the copper process since they are both in-laid processes. In addition to the types of patterns, it is also critical that the designed patterns have a structure size that accounts for a characteristic length of a process so that each structure or pattern does not get confounded pattern effects from neighboring structures.

For example, if a structure region is only 500  $\mu$ m wide when a characteristic length is 5 mm for a particular process, then the pattern effect from this particular structure has a significant amount of confounded influence from surrounding regions, complicating analysis especially when understanding of pattern interactions is not clear. Thus, each structure size should be big enough to attain a uniform local pattern environment. In addition, a structure design needs to remain simple, as complicated designs often cause measurement and analysis difficulties.

The placement of each pattern structure on the mask, also known as floorplanning, is the next critical factor in a test mask design. Floorplanning offers designers the flexibility of being able to place structures in strategic locations to either minimize or to cause possible structure to structure interactions. For instance, we have found that a field area of at least 100-200  $\mu$ m is needed between structures for each structure to be considered "isolated" from other structures in the overpolish phase of the copper CMP process [18]. The designed structures and their placements must also offer strategic and easy measurement plans for efficient and effective data gathering. For example, if a structure size is too big or if two structures are side by side, then a surface profile scan would contain excess noise from leveling by the profiler or distortions from wafer warp that would make it hard to distinguish what is noise and what is actual behavior. We encountered this measurement difficulty due to having structures side by side in an early test mask design (version 1.0), and all the subsequent designs have eliminated the problem by inserting field area separations between structures.

All of the issues described above – pattern factors, structure size, and placement – are critical in a test mask design to capture key pattern effects in a process. These design issues are described in detail in test structure designs in the following sections.

#### **3.1.1** Characteristic Length Scales in Electroplating and CMP

As discussed in the previous section, structure design must take into account characteristic length scales in a process. This section thus summarizes key length scales observed in the electroplating and CMP processes so that structure design principles are better understood. Since we want to use the same test mask to characterize both electroplating and CMP, the design must meet the characteristic length scales for both processes. This section first summarizes the relevant length scales in electroplating. Design of test structures is a iterative process where findings from experiments enable improvements in design. Thus, in discussing electroplating and CMP length considerations, we refer to early studies and experimental results; in may cases these results are presented later in more detail for electroplating in Chapter 4, and for CMP in Chapter 6.

In the electroplating process, our studies have found that the plated profile depends primarily on the details of the local feature itself. To first order, electroplating is a localized process where the plating depends on the line and its surroundings including the spacing and the nearest neighbors [19]. Thus, the characteristic length scale is equal to the feature size including the nearest neighbors within 2-5  $\mu$ m of the feature. Thus, if there are

41

more than several lines in a test structure, a uniform and self-contained local pattern environment is formed. Also, it is observed that if a line is positioned away from other lines by more than 5-10  $\mu$ m, then the line can be considered as an isolated line where it is not influenced by other lines.

The test mask design described later has a line/array structure with an isolated line that is hundreds of microns away from other structures, and this is far greater than the 3-5  $\mu$ m transition region length scale seen in electroplating. Thus the line structure can be effectively treated as an isolated line. For an array region consisting of sequences of lines and spaces, the test structure size is on the order or millimeters containing regular arrays of many lines. Thus the array size of the array region is large enough for use of the structures in studies of pattern effects in electroplating. We find that the constraining characteristic length scale governing the test mask design is imposed by the CMP process, rather than by the electroplating process. Thus, the designed test structures can be used effectively for an integrated studies of pattern effects in both processes if they satisfy the more difficult CMP imposed design challenges.

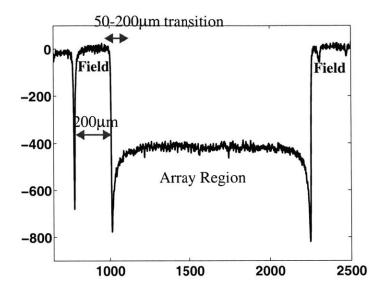

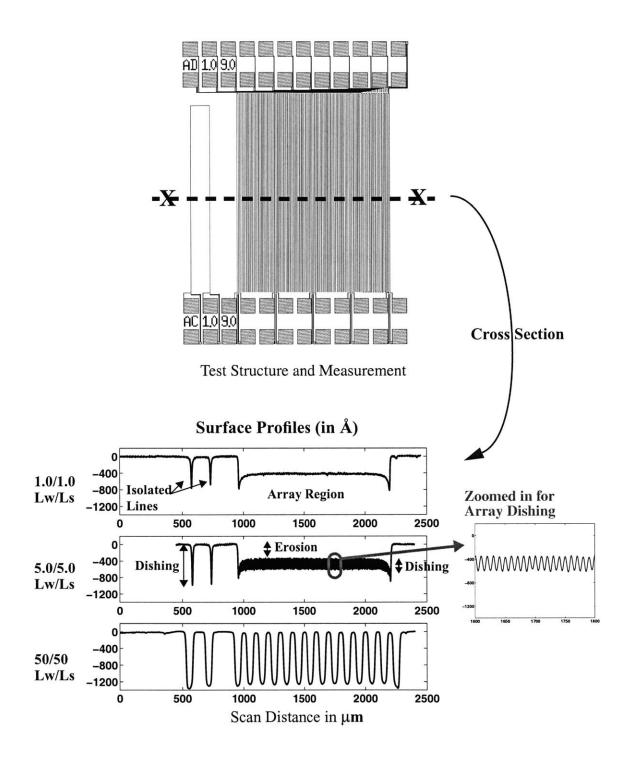

In oxide CMP, one length scale has been found to dominate: a "planarization length" on the order of 3-7 mm effectively averages the density of raised topography within that range, determining the relative rates of polish [20]. In copper polishing, on the other hand, three different length scales appear to be at work. First, an analogous long-range (e.g. 6 mm in [21]) pattern density dependence appears to be important during the initial planarization of the bulk copper. Second, a relatively sharp and short range transition of approximately 50-200  $\mu$ m is observed between a field oxide region and the dishing/erosion profile in an array region as shown in Figure 3.1, or between two different density/ pitch array regions [18, 22]. We have also found that field area of at least 100-200  $\mu$ m is needed between structures for each structure to be considered "isolated" from other struc-

tures in the overpolish phase of copper CMP process [18]. Finally, very short range dependencies on the order of the individual line width or space (feature length scale) can substantially accelerate or limit dishing and erosion [22].

Figure 3.1: Sample Erosion Profile Across an Array Region

The variety of these length scales and their influences must be accounted for in the design and layout of test structures for copper interconnect pattern dependency characterization, as well as in the measurement and analysis of topography data.

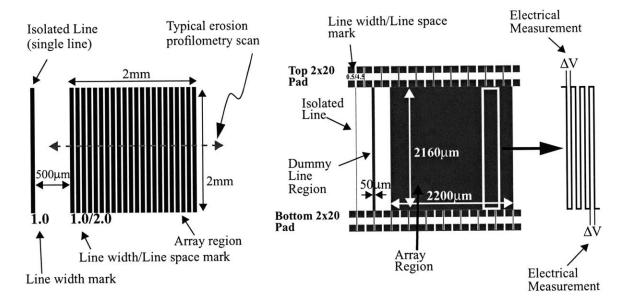

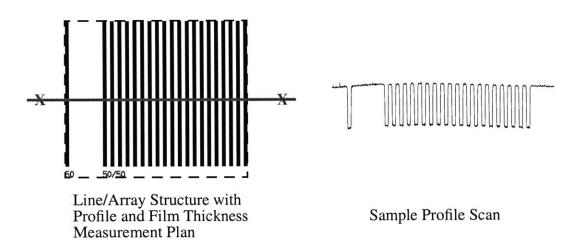

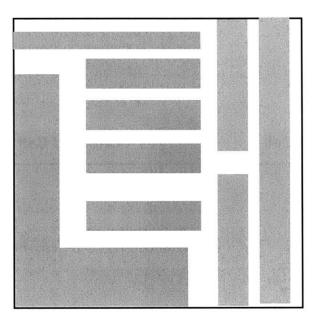

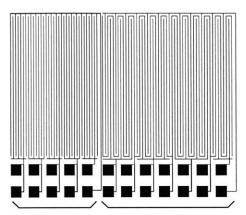

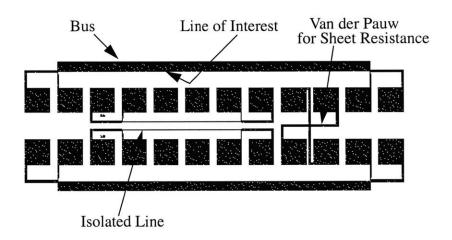

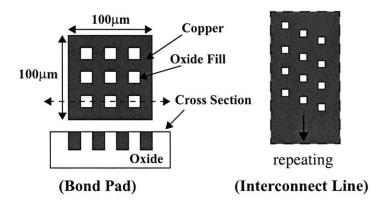

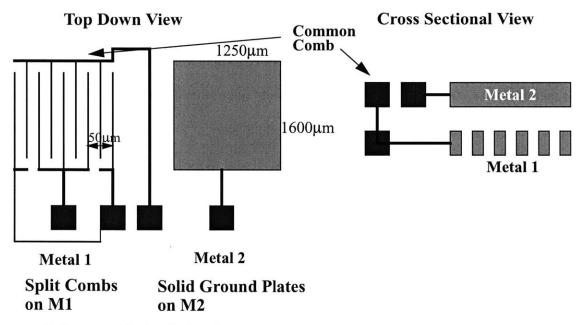

#### **3.1.2 Basic Test Structure Design: Line/Array**

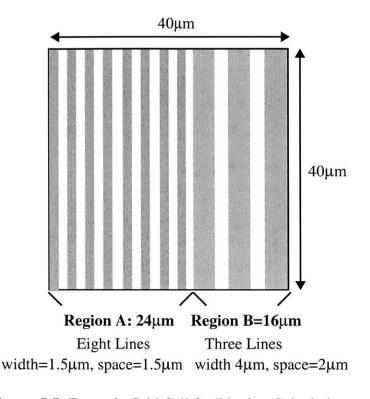

In this section we first describe the basic line/array structure used to explore array and step height in electroplating fill, and dishing and erosion in the CMP process. We then discuss the key principles and guidelines for structure design and layout to address the length scales discussed above, as well as how these structures support physical and electrical measurement of key pattern dependencies. As discussed earlier, the pattern dependent problems in plating and CMP have been found to depend on both line width and line space. To mimic interconnect, arrays of lines and spaces form the fundamental test structure for the study of pattern dependencies. Shown in Figure 3.2a is a test structure that incorporates two regions or elements. The "isolated line" on the left gives pattern effect due to an isolated line with minimal surrounding influence, and this is used to obtain isolated feature plating step height and CMP dishing information. The "array" region gives information about array bulge or recess in electroplating and array erosion in CMP across a series of lines, as well as feature step height and dishing within array lines.

#### **b. Electrical Test Structure**

Figure 3.2: Line and Array Test Structures

For a line to be considered "isolated" its electroplating and polishing behavior should not be influenced by nearby array region. For CMP, we have seen that oxide spaces greater than 200  $\mu$ m or so erode relatively little [18, 22, 23], so that separation of 300 to 500  $\mu$ m between the isolated line and the associated array region should minimize the impact of erosion on the isolated line. Also, this separation distance is large enough for the isolated line to be electroplated without array region influence.

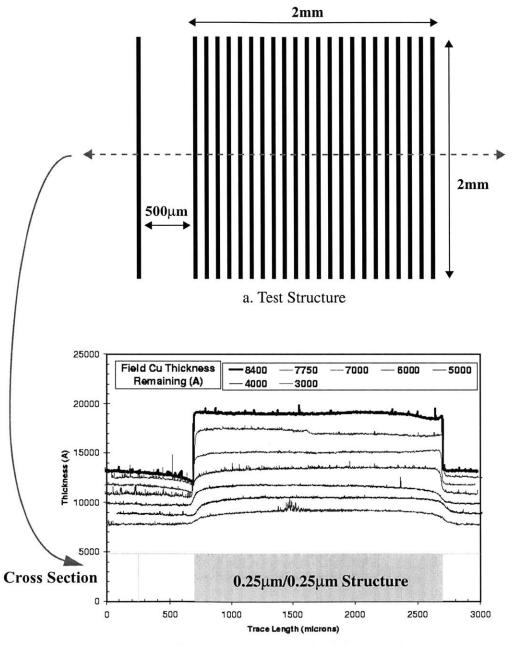

The entire array structure is relatively large in size (~2000 x 2000  $\mu$ m or more), and is separated from neighboring structures (including the associated isolated line) by substantial oxide spacing of 500  $\mu$ m to decouple interactions among structures to give a large field area to serve as measured surface profile reference points. The array region size of 2-3 mm is selected to be an appreciable fraction of the bulk copper planarization length and significantly more than the transition length in CMP erosion profile (50-200  $\mu$ m), so that a relatively constant effective pattern region is established within the structure. Furthermore, this choice of array size is large enough for an electroplating process as well since only an array size of tens of micron is required to maintain a uniform local pattern environment.

It should be remembered, however, that in CMP the bulk copper polish interacts over several mm; by keeping the isolated line relatively near to the corresponding array structure, both should experience similar long range averaged pattern densities. Considering the other extreme, dishing within the array will depend on both line width and line space. Typically, the dishing of a line in this case 'sits' on top of the erosion profile where the array erosion profile has a rather sharp transition from the field oxide region to the structure region. This length is on the order of 100  $\mu$ m, and thus we want the structure size to be several times larger than this so that a series of lines across the array can be examined without any influence from the transition region.

This basic structure is also extended with electrical bond pads for electrical testing as shown in Figure 3.2b. Such electrical testing is only applicable in post-CMP characterization after the copper and barrier have been sufficiently cleared to produce electrically welldefined copper lines and structures. Each structure consists of an isolated line, a dummy

45

line region, and a pattern region with electrical bond pads on both the top and bottom of the structure. The "isolated line" consists of two line segments with a bend so that the measurement can be taken from the same set of bottom pads. Second, a dummy line region is added for electrical test structure design and consists of a line surrounded by a small region (50  $\mu$ m wide) containing similar lines. The dummy line region is away from the isolated line and the array region by 200-300  $\mu$ m so that structure influence is minimized.

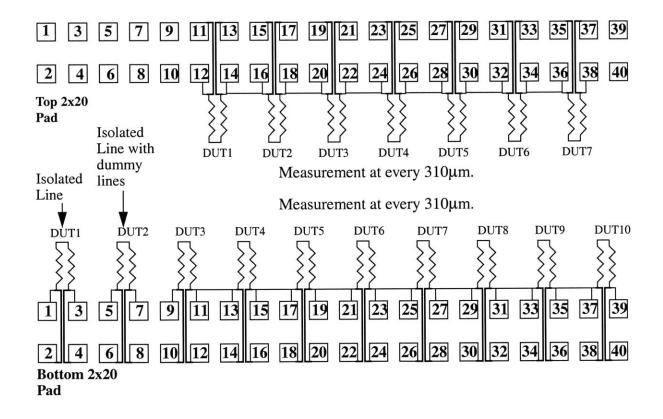

Note: Although not explicitly shown, the lines connected to the bottom 2x20 pad and the lines connected to the top 2x20 pad are all connected since all lines are designed in a serpentine fashion.

The array region is made up of serpentine lines providing resistance measurements based on a 4-point Kelvin structure. The use of both top and bottom pads is to increase the number of measurements that can be made on each structure: a spatial sampling along the array is thus possible. As the circuit representation shown in Figure 3.3 indicates, the electrical line resistance measurements are sampled evenly across the whole array region at every 155  $\mu$ m. This is done by interleaving top and bottom measurement taken at every 310  $\mu$ m. Serpentine lines also allow simultaneous resistance measurement on one loop of a line or an array for thickness extraction and continuity test of lines in the density structures. The spatial electrical measurement can also be used with the surface profile measurement as a complementary analysis.

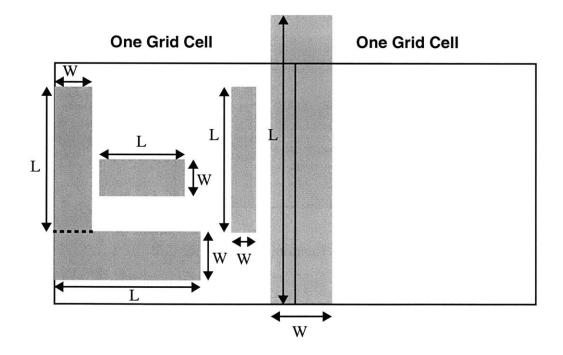

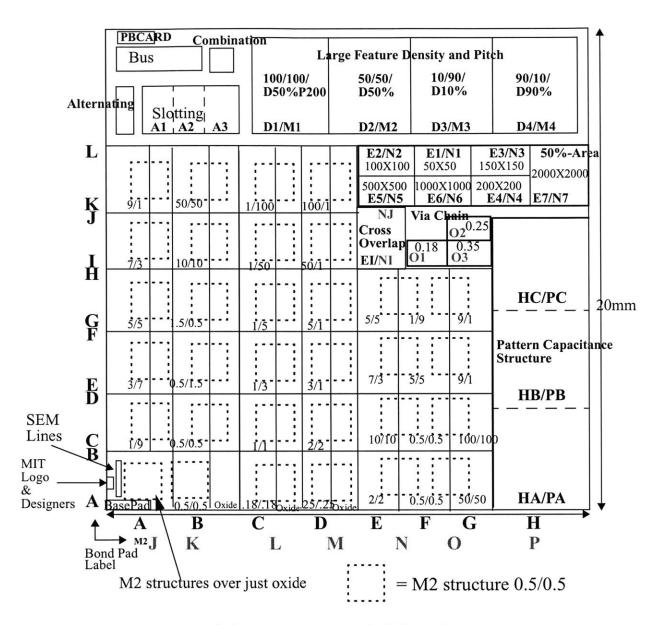

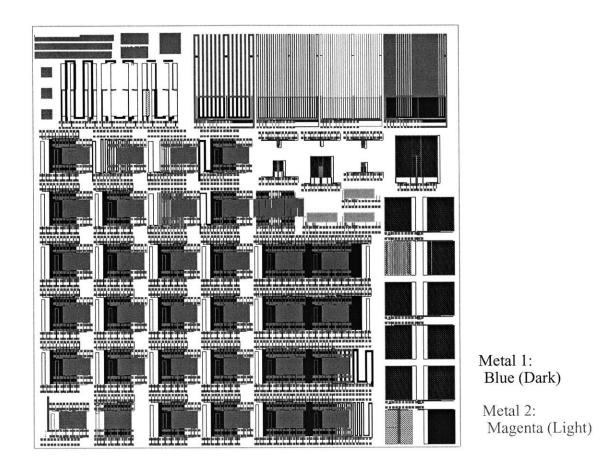

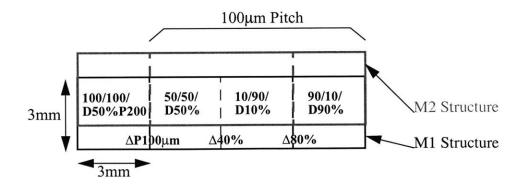

#### 3.2 Single-Level Copper Test Mask V1.2

Using the basic test pattern, a broad range of feature sizes, spanning typical IC designs from lower to upper metal layers, is used to form pattern structures for a test mask. This section contains the description for the single-level copper test mask version 1.2 evolved from the original test mask version 1.0. This mask is designed to understand and characterize pattern dependent variation of dishing and erosion on a wide range of density and pitch structures (thus, different line width and line space combinations), and further to model them for better process optimization and integration. As discussed previously, the test mask also provides the range of features and pattern environments needed for characterization of copper electroplating process pattern dependencies. This mask consists of the basic line/array test pattern with a wide range of pattern features such as pattern density and pitch (thus, different line width and line space combinations). The mask is a single level mask of die size 20 mm x 20 mm with a minimum geometry of 0.25  $\mu$ m for line width and 0.25  $\mu$ m for line space, and a maximum geometry of 500  $\mu$ m lines. The floorplan of the test mask is shown in Figure 3.4.

Figure 3.4: Single-Level Mask Floorplan

In the floorplan, pitch structures (top two rows) are marked with "Pxx" where xx is the associated pitch value in microns. Pitch is defined as the sum of line width and line space. If no density is indicated, the default density of 50% is used (e.g. same line width and line

space). For example, a structure designated with "P0.5" has a pitch of 0.5  $\mu$ m, or a line width and space of 0.25  $\mu$ m, respectively. To the right of the pitch structures are some wide lines having line widths of 150, 200, 300, and 500  $\mu$ m without associated array regions. The density structures are marked with "DyyPxx" where yy is the associated percentage density of copper lines for the given pitch of xx microns. The density is defined as the ratio of line width to pitch, and the range of density for these structures are from 10% to 90% for fixed pitch of 5  $\mu$ m, and from 16.6% to 83.3% for fixed pitch of 3  $\mu$ m. For example, "D90P5" indicates 90% density for pitch of 5  $\mu$ m, and this structure has 4.5  $\mu$ m lines and 0.5  $\mu$ m spaces. Likewise, 100% pattern density is solid copper and 0% pattern density is just oxide.

Figure 3.5: Single-Level Copper Test Mask V1.2