massachusetts institute of technology — artificial intelligence laboratory

# ADAM: A Decentralized Parallel Computer Architecture Featuring Fast Thread and Data Migration and a Uniform Hardware Abstraction

Andrew "bunnie" Huang

Al Technical Report 2002-006

June 2002

# ADAM: A Decentralized Parallel Computer Architecture Featuring Fast Thread and Data Migration and a Uniform Hardware Abstraction

by

## Andrew "bunnie" Huang

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

June 2002

© Massachusetts Institute of Technology 2002. All rights reserved.

Certified by: Thomas F. Knight, Jr. Senior Research Scientist Thesis Supervisor

Accepted by: Arthur C. Smith Chairman, Department Committee on Graduate Students

# ADAM: A Decentralized Parallel Computer Architecture Featuring Fast Thread and Data Migration and a Uniform Hardware Abstraction

by

Andrew "bunnie" Huang

Submitted to the Department of Electrical Engineering and Computer Science on May 24, 2002, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

#### **Abstract**

The furious pace of Moore's Law is driving computer architecture into a realm where the the speed of light is the dominant factor in system latencies. The number of clock cycles to span a chip are increasing, while the number of bits that can be accessed within a clock cycle is decreasing. Hence, it is becoming more difficult to hide latency. One alternative solution is to reduce latency by migrating threads and data, but the overhead of existing implementations has previously made migration an unserviceable solution so far.

I present an architecture, implementation, and mechanisms that reduces the overhead of migration to the point where migration is a viable supplement to other latency hiding mechanisms, such as multithreading. The architecture is abstract, and presents programmers with a simple, uniform fine-grained multithreaded parallel programming model with implicit memory management. In other words, the spatial nature and implementation details (such as the number of processors) of a parallel machine are entirely hidden from the programmer. Compiler writers are encouraged to devise programming languages for the machine that guide a programmer to express their ideas in terms of objects, since objects exhibit an inherent physical locality of data and code. The machine implementation can then leverage this locality to automatically distribute data and threads across the physical machine by using a set of high performance migration mechanisms.

An implementation of this architecture could migrate a null thread in 66 cycles – over a factor of 1000 improvement over previous work. Performance also scales well; the time required to move a typical thread is only 4 to 5 times that of a null thread. Data migration performance is similar, and scales linearly with data block size. Since the performance of the migration

mechanism is on par with that of an L2 cache, the implementation simulated in my work has no data caches and relies instead on multithreading and the migration mechanism to hide and reduce access latencies.

Thesis Supervisor: Thomas F. Knight, Jr.

Title: Senior Research Scientist

## Acknowledgments

I would like to thank my parents for all their love and support over the years, and for their unwaxing encouragement and faith in my ability to finish the degree program.

I would also like to thank my wonderful, loving, caring girlfriend Nikki Justis for all her support, motivation, patience, editing, soldering, discussion and idea refinement, cooking, cleaning, laundry doing, driving me to campus, wrist massages, knowing when I need to tool and when I need to take a break, tolerance of my 7 AM sleep schedule, and for letting me make a mess in her room and take over her couch with my whole computer setup.

I would like to thank all my friends for their support over the years, and for making the past decade at MIT-and my first step into the real world-an exciting, fun and rewarding experience. Let the rush begin...and may it never end.

This thesis would never happened if it were not for the Aries Research Group (in order of seniority): Tom Knight, Norm Margolus, Jeremy Brown, J.P. Grossman, Josie Ammer, Mike Phillips, Peggy Chen, Bobby Woods-Corwin, Ben Vandiver, Tom Cleary, Dominic Rizzo, and Brian Ginsburg. Tom Knight, in particular, has been a role model for me since I came to the lab; he is an endless source of inspiration and knowledge, and has provided invaluable guidance, counsel and encouragement. He is brilliant and visionary, yet humble and very accessible, and always willing to answer my questions, no matter how silly or stupid. I also really enjoy his *laissez-faire* policies with respect to running the group; I truly treasure the intellectual freedom Tom brought to the group, and his immense faith in all of our abilities to manage and organize ourselves, and to "go forth and think great thoughts." Jeremy Brown and J.P. Grossman were also invaluable for their good ideas, lively

conversation, and idea refinement. Jeremy invented the idempotent network protocol used in this thesis, and his excellent thesis work in novel parallel programming methods and scalable parallel garbage collection fills in many crucial gaps in my thesis. J.P. and Jeremy also developed the capability representation with SQUIDS that is central to my thesis. I also relied on J.P.'s excellent work in researching and characterizing various network topologies and schemes; I used many of his results in my implementation. Bobby Woods-Corwin, Peggy Chen, Brian Ginsburg and Dominic Rizzo were invaluable in working out the implementation of the network. Without them, I would have nothing to show for this thesis except for a pile of Java code. Two generations of M.Eng theses and two UROPs is a lot of work! Norm Margolus also helped lay down the foundations of the architecture with his work in spatial cellular automata machines and embedded DRAM processors. Finally, André DeHon, although not officially a part of the group, was very much instrumental to my work in many ways. This work relies very heavily upon his earlier work at MIT on the METRO network. André also provided invaluable advice and feedback during his visits from Caltech.

I would also like to give a special thanks to Ben Vandiver. Since the inception of the ADAM and the Q-Machine, Ben has furnished invaluable insight and feedback. The thesis would not be complete without his synergism as a compiler writer, programmer, and high-caliber software hacker. I also thank him for his enthusiasm and faith in the architecture; his positive energy was essential in keeping me from getting discouraged. He not only helped hash out the programming model for the machine, he also wrote two compilers for the machine along the way. He also was instrumental in coding and debugging the benchmarks used in the results section of my thesis.

Krste Asanović and Larry Rudolph were also very important influences on this thesis. Krste is a wellspring of knowledge and uncannily sharp insight into the even the finest architectural details. Larry opened my mind to the field of competitive analysis and on-line algorithms, something I would never have considered otherwise. I also appreciate the critical review provided by both Krste and Larry.

I would also like to thank my friends at the Mobilian Corporation—in particular, Rob Gilmore, MaryJo Nettles, Todd Sutton, and Rob Wentworth—for their understanding, patience, and support for me finishing my degree.

I thank the Xilinx Corporation for generously donating the many highend FPGAs and design tools to the project, which were used to implement prototype network and processor nodes. I would also like to thank the Intel Corporation and Silicon Spice for providing fellowships and equipment that enabled me to finish my work. Sun Corporation and Borland also provided me Java and JBuilder for free, but the value of these tools cannot be underestimated. This work was also funded by the Air Force Research Laboratory, agreement number F30602-98-1-0172, "Active Database Technology".

I could go on, but unfortunately there is not enough space to name everyone who has helped with my thesis. This is to everyone who provided invaluable input and guidance into my thesis—thank you all. I am indebted to the world, and I can only hope to someday make a contribution that is worthy.

Finally, all mistakes in this thesis are mine.

# **Contents**

| 1 | Intr | oductio  | n                                                   | 17 |

|---|------|----------|-----------------------------------------------------|----|

|   | 1.1  | Contri   | butions                                             | 18 |

|   | 1.2  | Organ    | ization of This Work                                | 19 |

| 2 | Bac  | kgroun   | d                                                   | 22 |

|   | 2.1  | Latence  | cy Management Techniques                            | 22 |

|   |      | 2.1.1    | Latency Reduction                                   | 23 |

|   |      | 2.1.2    | Latency Hiding                                      | 25 |

|   | 2.2  | Migra    | tion Mechanisms                                     | 28 |

|   |      | 2.2.1    | Discussion                                          | 30 |

|   | 2.3  | Archit   | ectural Pedigree                                    | 31 |

|   |      | 2.3.1    | Dataflow                                            | 32 |

|   |      | 2.3.2    | Decoupled-Access/Execute                            | 35 |

|   |      | 2.3.3    | Processor-In-Memory (PIM) and Chip Multi-Processors | s  |

|   |      |          | (CMP)                                               | 37 |

|   |      | 2.3.4    | Cache Only Memory Architectures                     | 39 |

| 3 | Arie | es Decer | ntralized Abstract Machine                          | 40 |

|   | 3.1  | Introd   | uction to ADAM by Code Example                      | 41 |

|   |      | 3.1.1    | Basics                                              | 41 |

|   |     | 3.1.2    | Calling Convention                              | 42 |

|---|-----|----------|-------------------------------------------------|----|

|   |     | 3.1.3    | Memory Allocation and Access                    | 44 |

|   | 3.2 | Progra   | nmming Model                                    | 46 |

|   |     | 3.2.1    | Threads                                         | 47 |

|   |     | 3.2.2    | Queues and Queue Mappings                       | 49 |

|   |     | 3.2.3    | Memory Model                                    | 50 |

|   |     | 3.2.4    | Interacting with Memory                         | 52 |

| 4 | Mig | ration 1 | Mechanism in a Decentralized Computing Environ- | -  |

|   | men | t        |                                                 | 54 |

|   | 4.1 | Introdu  | uction                                          | 54 |

|   | 4.2 | Backg    | round                                           | 55 |

|   |     | 4.2.1    | Architectures that Directly Address Migration   | 56 |

|   |     | 4.2.2    | Soft Migration Mechanisms                       | 58 |

|   |     | 4.2.3    | Programming Environments and On-Line Migration  |    |

|   |     |          | Algorithms                                      | 62 |

|   | 4.3 | Migrat   | tion Mechanism Implementation                   | 66 |

|   |     | 4.3.1    | Remote Memory Access Mechanism                  | 67 |

|   |     | 4.3.2    | Migration Mechanism                             | 71 |

|   |     | 4.3.3    | Data Migration                                  | 71 |

|   |     | 4.3.4    | Thread Migration                                | 75 |

|   | 4.4 | Migrat   | tion Mechanism Issues and Observations          | 81 |

|   |     | 4.4.1    | General Observations                            | 81 |

|   |     | 4.4.2    | Performance Issues                              | 84 |

| 5 | Imp | lementa  | ation of the ADAM: Hardware and Simulation      | 87 |

|   | 5.1 | Introdu  | uction                                          | 88 |

|   | 5.2 | High-I   | Level Organization                              | 89 |

|   | 5.3 | Leaf N   | Node                                            | 89 |

|   |      | 5.3.1    | Processor Node                                      | 91  |

|---|------|----------|-----------------------------------------------------|-----|

|   |      | 5.3.2    | Memory Node                                         | 97  |

|   | 5.4  | Physic   | al Design                                           | 100 |

|   |      | 5.4.1    | Technology Assumptions                              | 100 |

|   |      | 5.4.2    | Design Description                                  | 103 |

| 6 | Mac  | hine an  | d Migration Characterization                        | 107 |

|   | 6.1  | Basic    | Q-Machine Performance Results                       | 107 |

|   |      | 6.1.1    | Memory Performance                                  | 109 |

|   |      | 6.1.2    | Basic Network Operations Performance                | 110 |

|   | 6.2  | Migrat   | ion Performance and Migration Control: Simple Cases | 111 |

|   |      | 6.2.1    | Two Threads Benchmark                               | 112 |

|   |      | 6.2.2    | Thread and Memory Benchmark                         | 119 |

|   | 6.3  | Applic   | ration Cases                                        | 124 |

|   |      | 6.3.1    | In-Place Quicksort Application                      | 125 |

|   |      | 6.3.2    | Matrix Multiplication Benchmark                     | 130 |

|   |      | 6.3.3    | N-Body Benchmark                                    | 133 |

| 7 | Con  | clusions | s and Future Work                                   | 140 |

|   | 7.1  | Conclu   | isions                                              | 140 |

|   | 7.2  | Future   | Work                                                | 142 |

|   |      | 7.2.1    | Improved Migration Control Algorithms               | 142 |

|   |      | 7.2.2    | Languages and Compilers                             | 143 |

|   |      | 7.2.3    | Hardware Implementation                             | 144 |

|   |      | 7.2.4    | Transactions                                        | 145 |

|   | 7.3  | Final F  | Remarks                                             | 146 |

| A | Acro | onyms    |                                                     | 147 |

| B | ADA | AM Details                          | 150 |

|---|-----|-------------------------------------|-----|

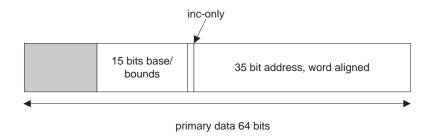

|   | B.1 | Data Types                          | 150 |

|   | B.2 | Instruction Formats                 | 154 |

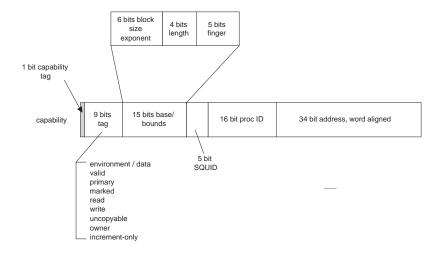

|   | B.3 | Capability Format                   | 157 |

|   | B.4 | Über-Capability and Multitasking    | 161 |

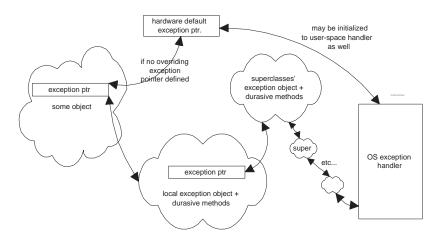

|   | B.5 | Exception Handling                  | 162 |

| C | Q-M | Iachine Details                     | 164 |

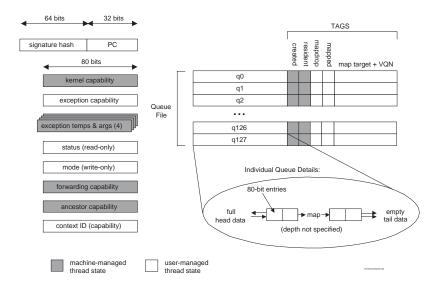

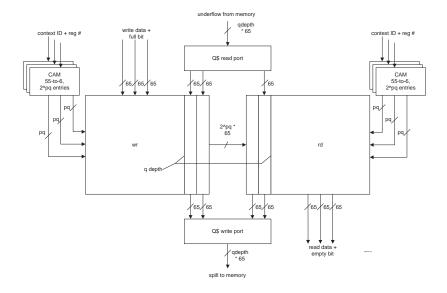

|   | C.1 | Queue File Implementation Details   | 165 |

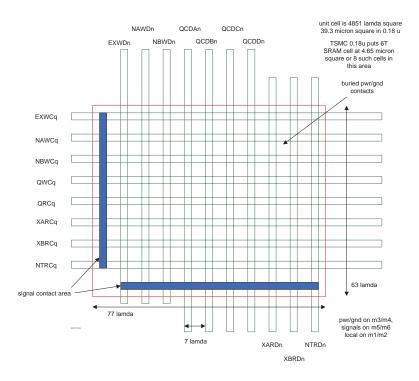

|   |     | C.1.1 Physical Design               | 165 |

|   |     | C.1.2 State Machine                 | 170 |

|   | C.2 | Network Interface                   | 174 |

|   | C.3 | Network Topology and Implementation | 179 |

| D | Opc | odes                                | 185 |

|   | D.1 | General Notes                       | 185 |

|   | D.2 | Lazy Instructions                   | 186 |

|   | D 3 | Instruction Summary                 | 187 |

# **List of Figures**

| 1.1 | Overview of the abstraction layers in this thesis. Couatl and |    |

|-----|---------------------------------------------------------------|----|

|     | People are compilers written by Ben Vandiver                  | 21 |

| 2.1 | Reachable chip area in top level metal, where area is mea-    |    |

|     | sured in six-transistor SRAM cells. Directly from [AHKB00]    | 26 |

| 2.2 | Illustration of the false sharing problem                     | 32 |

| 3.1 | Demonstration of the copy/clobber (@) modifier                | 42 |

| 3.2 | Simple code example demonstrating procedure linkage, thread   |    |

|     | spawning, memory allocation, and memory access                | 43 |

| 3.3 | Thread states after thread spawn and procedure linkage        | 45 |

| 3.4 | Thread states after memory allocation and access              | 47 |

| 3.5 | Programming model of ADAM                                     | 48 |

| 3.6 | Structure of an ADAM thread                                   | 49 |

| 3.7 | High-level breakdown of the ADAM capability format. De-       |    |

|     | tailed bit-level breakdowns of each field can be found in ap- |    |

|     | pendix B                                                      | 51 |

| 4.1 | Format of a remote memory capability's shadow space in lo-    |    |

|     | cal virtual memory space                                      | 69 |

| 4.2 | System level view of resolving remote memory requests.        | 69 |

| 4.3 | Details of handling remote and local EXCH requests               | 70  |

|-----|------------------------------------------------------------------|-----|

| 4.4 | Mechanism for temporarily freezing memory requests               | 74  |

| 4.5 | Handling of a migrated EXCH request with temporally bi-          |     |

|     | directional pointers                                             | 76  |

| 4.6 | Transmission line protocol for handling forwarding pointer       |     |

|     | updates on thread-mapped communications                          | 82  |

| 4.7 | Overview of a demand-driven data propagation scheme              | 86  |

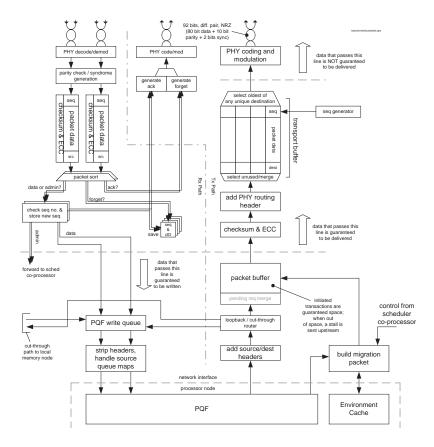

| 5.1 | Pieces of a Q-Machine implementation. Node ID tags are           |     |

|     | uniform across the machine, so network-attached custom hard-     |     |

|     | ware is addressable like any processor or memory node            | 90  |

| 5.2 | High level block diagram of a leaf node                          | 92  |

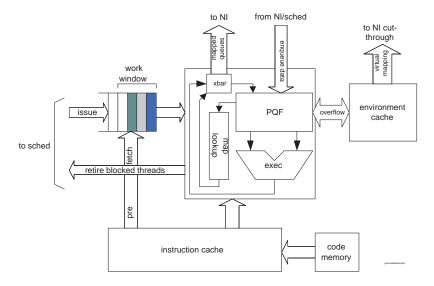

| 5.3 | Detail of a processor node                                       | 93  |

| 5.4 | Hybrid scheduler list/I-cache structure. In this diagram, c42    |     |

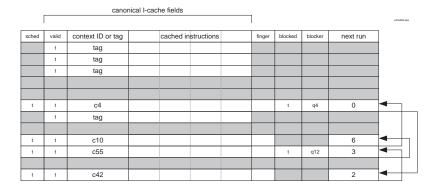

|     | and c10 are runnable and up for forwarding to the work-          |     |

|     | queue; as values for c55:q12 and c4:q4 arrive via the NI, they   |     |

|     | will be promoted to runnable status                              | 97  |

| 5.5 | High level block diagram of a memory node                        | 98  |

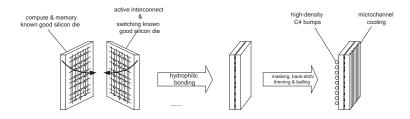

| 5.6 | Packaging and integration for a two-layer silicon high-performa  | nce |

|     | chip multiprocessor                                              | 102 |

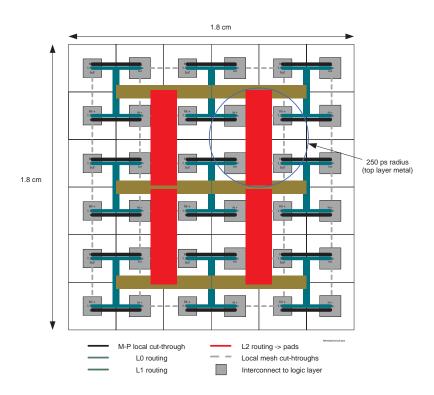

| 5.7 | Cartoon of the network layer layout                              | 104 |

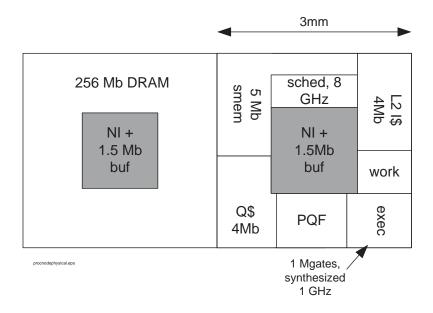

| 5.8 | Hypothetical layout of a single processor node                   | 105 |

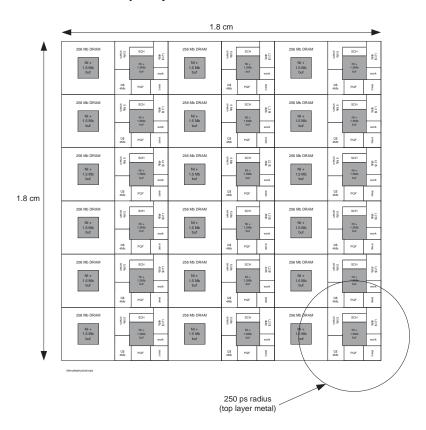

| 5.9 | Hypothetical layout of the tile processor chip                   | 106 |

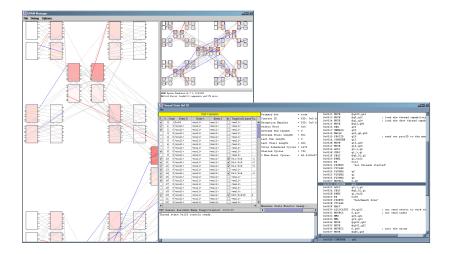

| 6.1 | Screenshot of the ASS running a 64-node vector reverse re-       |     |

|     | gression test. On the left is the machine overview; to the right |     |

|     | is the thread debugger window                                    | 109 |

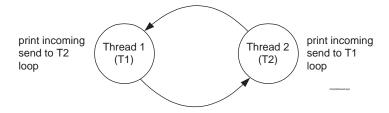

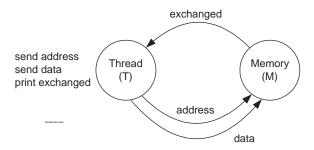

| 6.2  | The two threads synthetic benchmark. Communication hap-                    |     |

|------|----------------------------------------------------------------------------|-----|

|      | pens along the arcs; a data dependency is forced by printing               |     |

|      | the incoming data                                                          | 112 |

| 6.3  | Code used for the two thread benchmark                                     | 113 |

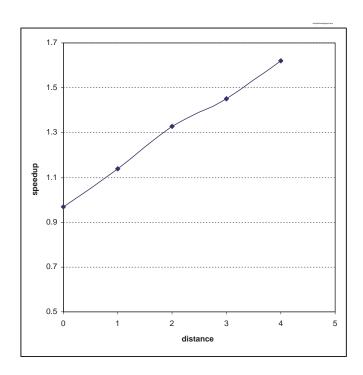

| 6.4  | Measured speedup versus migration distance for the Two Thread              | ls  |

|      | benchmark                                                                  | 115 |

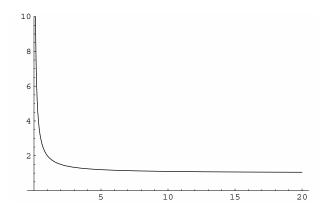

| 6.5  | Shape of the curve $\frac{x+c}{x}$                                         | 118 |

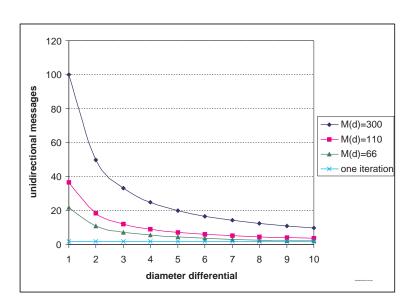

| 6.6  | Length of message sequence required to amortize various mi-                |     |

|      | gration overheads ( $M\left(d\right)$ ). The baseline two messages per it- |     |

|      | eration for the Two Thread benchmark is also marked on the                 |     |

|      | graph                                                                      | 120 |

| 6.7  | The thread and memory synthetic benchmark. Communica-                      |     |

|      | tion happens along the arcs; a data dependency is forced by                |     |

|      | printing the incoming data                                                 | 121 |

| 6.8  | Code used for the thread-memory benchmark                                  | 122 |

| 6.9  | Migration speedup versus migration decision time and mem-                  |     |

|      | ory capability size in the thread and memory benchmark. $\ . \ .$          | 123 |

| 6.10 | Cycles per iteration for Thread-Memory benchmark. $d=4$                    |     |

|      | in both cases.                                                             | 124 |

| 6.11 | Object method for the Quicksort benchmark written in People.               | 126 |

| 6.12 | Distribution of migration times used in the Quicksort bench-               |     |

|      | mark                                                                       | 127 |

| 6.13 | Plot of the load metric $T_{\it w}$ versus time for the Quicksort bench-   |     |

|      | mark with and without load balancing                                       | 128 |

| 6.14 | Plot of the load balanced Quicksort benchmark with migra-                  |     |

|      | tion events overlayed                                                      | 130 |

| 6.15 | Portion of the streaming matrix multiply benchmark written                 |     |

|      | in People                                                                  | 132 |

| 6.16 | Plot of the time required per iteration of a 100x100 matrix      |      |

|------|------------------------------------------------------------------|------|

|      | multiply over various migration conditions and coding styles.    | 134  |

| 6.17 | Plot of the time required per iteration of a 15x15 matrix mul-   |      |

|      | tiply over various migration conditions and coding styles        | 135  |

| 6.18 | Plot of the first few time steps of the N-Body benchmark output  | t136 |

| 6.19 | Inner-loop of N-Body benchmark code                              | 138  |

| 6.20 | Plot of the time required per timestep of a 12-body N-body       |      |

|      | simulation run on a 64-node Q-Machine                            | 139  |

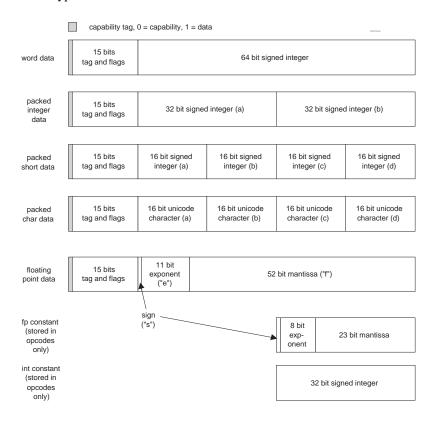

| B.1  | Data formats supported by ADAM                                   | 151  |

| D.1  | ••                                                               | 131  |

| B.2  | Tag and Flag field details                                       | 152  |

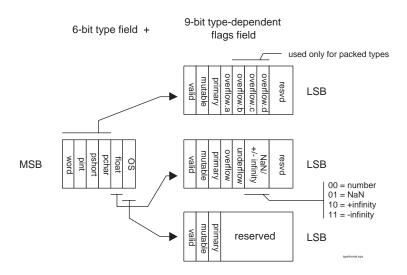

| B.3  | Format of ADAM opcodes                                           | 155  |

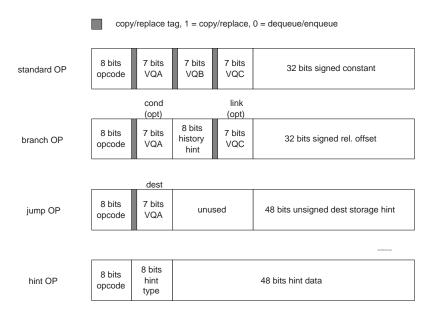

| B.4  | ADAM capability format                                           | 158  |

| B.5  | Exception handling overview                                      | 163  |

| C.1  | A 3-write, 3-read port VQF implementation. $pq = log_2(\#$       |      |

|      | physical registers). Q-cache details omitted for clarity         | 166  |

| C.2  | PQF unit cell                                                    | 167  |

| C.3  | PQF read request response flowchart                              | 171  |

| C.4  | PQF write request response flowchart                             | 173  |

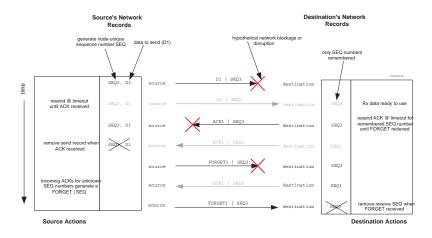

| C.5  | Details of the network interface                                 | 175  |

| C.6  | Idempotence and reliable data delivery protocol in detail for    |      |

|      | a single transaction. Lines in gray are "retry" lines that would |      |

|      | not happen in an ideal setting.                                  | 178  |

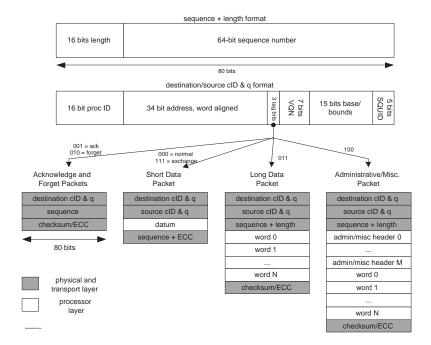

| C.7 | Details of packet formats. Note that in the destination/source |     |

|-----|----------------------------------------------------------------|-----|

|     | cID and queue headers, it is very important that the processor |     |

|     | ID be in the MSB and co-located with the address field, since  |     |

|     | implementations may push bits between the address and PID      |     |

|     | fields to increase the number of routable processor nodes or   |     |

|     | to increase the amount of memory per node                      | 180 |

| D 1 | ab format for the DARCEL instruction                           | 278 |

# **List of Tables**

| 5.1 | Extrapolated Technology Parameters for 2010. All values |     |

|-----|---------------------------------------------------------|-----|

|     | from [CI00a] unless otherwise noted                     | 10  |

| A.1 | Table of Acronyms                                       | 148 |

| A.2 | Table of Acronyms, continued                            | 149 |

# **Chapter 1**

# Introduction

You can't fake memory bandwidth that isn't there.

-Seymour Cray on why the Cray-1 had no caches

Most data and thread migration mechanisms to date are slow when compared to other latency management techniques. This thesis introduces an architecture, ADAM, that enables a simple hardware implementation of data and thread migration. This implementation reduces the overhead of migration to the point where it is comparable to other hardware-assisted latency management techniques, such as caching.

Data migration is useful to reduce access latencies in situations where the working set is larger than cache. It is also useful in reducing or redistributing network traffic in situations where hotspots are caused by contention for multiple data objects. Data migration can also be used to emulate the function of caches in systems that feature no data caches.

Thread migration is useful to reduce access latencies in situations where multiple threads are contending for a single piece of data. Like data migra-

tion, it is also useful in situations where hotspots can be alleviated by redistributing the sources and destinations of network traffic. Thread migration is also useful for load-balancing, particularly in situations where memory contention is low.

Data and thread migration can be used together to help manage access latencies in situations where many threads are sharing information in an unpredictable fashion among many pieces of data, as might be the case in an enterprise database application. Data and thread migration can also be used to enhance system reliability as well, if faults can be predicted far enough in advance so that the failing node can be flushed of its contents.

### 1.1 Contributions

The primary contribution of my thesis is a **fast, low-overhead data and thread migration mechanism.** In terms of processor cycles, the mechanism outlined in my thesis represents greater than a 1000-fold increase in performance over previous software-based migration mechanisms. As a result, data and thread migration overheads are similar to L2 cache fills on a conventional uni-processor system.

The key architectural features that enable my data and thread migration mechanisms are a **unified thread and data representation using capabilities** and **interthread communication and memory access through architecturally explicit queues**. Threads and data in my architecture, ADAM, are accessed using a capability representation with tags that encode base and bounds information. In other words, every pointer has associated with it the region of data it can access, and this information trivializes figuring out what to move during migration. Architecturally explicit queues, on the other hand, simplify many of the ancillary tasks associated with migrating threads and

data, such as the movement of stacks, the migration and placement of communication structures, concurrent access to migrating structures, and pointer updates after migration.

My thesis also describes an **implementation outline of ADAM** dubbed the "Q-Machine". The implementation technology is presumed to be 35 nm CMOS silicon, available in volume around 2010, and features no data caches; instead, it relies on the migration mechanism and multithreading to maintain good performance and high processor utilization. The proposed implementation is simulated with the ADAM System Simulator (ASS); it is this simulator that provides the results upon which the ADAM architecture is evaluated. Note that there is no requirement for advanced technology to implement the ADAM; one could make an ADAM implementation today, if so desired. The 2010 technology point was chosen to evaluate the ADAM architecture because it would match a likely tape-out time frame of the architecture's implementation.

## 1.2 Organization of This Work

Chapter 2, "Background", discusses some of the advantages and disadvantages of a migration scheme over more conventional latency management schemes. It also reviews, at a high level, some of the problems encountered in previous migration schemes; a more detailed review of migration mechanisms is presented in Chapter 4. Chapter 2 closes with a differentiation of this work from its predecessors in a brief discussion of the architectural pedigree of the ADAM and its Q-Machine implementation.

Chapter 3, "Aries Decentralized Abstract Machine", describes the ADAM in detail. This chapter lays the foundation for the programming model of the ADAM through a simple code example, followed up with a discussion of

the architectural details relevant to a migration implementation. A detailed discussion of other architectural features can be found in Appendix B.

Chapter 4, "Migration Mechanism in a Decentralized Computing Environment", presents the implementation of the migration mechanisms. The chapter begins with a survey of previous work involving data and thread migration; this survey includes both mechanisms and migration control algorithms, since their implementation details are intimately associated. I then describe the migration mechanism in detail.

Chapter 5, "Implementation of the ADAM: Hardware and Simulation", describes an implementation of ADAM. This implementation is known as the Q-Machine. This chapter summarizes the machine organization and implementation technology assumptions of the simulator used to evaluate my migration mechanisms.

In the next chapter, "Machine and Migration Characterization" (Chapter 6), I characterize the performance of the implementation. The chapter starts with two simple micro-kernel benchmarks and some formal analysis of the migration mechanism. Then, I present results for some more comprehensive benchmarks, Quicksort, Matrix Multiply and N-Body, with simple migration control heuristics driving the migration mechanisms.

The thesis concludes in chapter 7 with a discussion of further developments for the ADAM architecture, areas for improvement and further research, and programming languages for the machine. Note that while a detailed discussion of programming languages for the ADAM is outside the scope of this thesis, I did not work in a programming language vacuum. A strong point of using an abstract machine model is that compiler writers can begin their work on day one, and in fact, that is the case. Benjamin Vandiver, an M.Eng student in my research group, has developed two languages, *Couatl* and *People*, and compilers for these languages to the ADAM architecture.

Couatl is a basic object-oriented language that we used in the early stages of architecture development to hammer out the abstract machine model and to determine the unique strengths and weaknesses of a queue based architecture. The follow-on language, People, is a more sophisticated language supporting streaming constructs that leverages the availability of architectural queues at the language level. I refer interested readers to his M.Eng thesis [Van02].

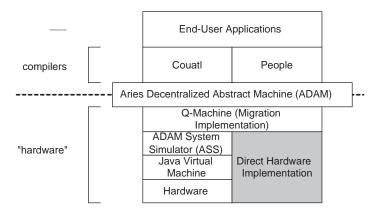

A summary of the abstraction layers employed by this thesis can be found in figure 1.1. ADAM is a pure abstraction, a boundary between compilers and hardware. Q-Machine is the implementation of ADAM that realizes the fast data and thread migration mechanisms made possible by ADAM. The ADAM System Simulator (ASS) is my software simulation of the Q-Machine, written in Java. The Q-Machine could also be implemented directly in hardware, but that is not within the scope of this thesis.

Figure 1.1: Overview of the abstraction layers in this thesis. Couatl and People are compilers written by Ben Vandiver.

I also provide a set of appendices that describe various technical nits of the architecture, including the bit-level details of the ADAM architecture, physical queue file (PQF) implementation, the network interface implementation, network protocols, and opcodes of the ADAM.

# Chapter 2

# **Background**

TSMC sees no insurmountable challenges in the path to scaling [silicon CMOS technology] to the 9 nm node. The question is, will the market be ready for it?

-Calvin Chenming Hu, CTO of TSMC at a talk at MIT

This chapter starts by characterizing the ADAM architecture in terms of its use of latency management techniques. This chapter then discusses in greater detail a comparison of various migration techniques. Finally, this chapter closes with a discussion of ADAM's architectural pedigree.

## 2.1 Latency Management Techniques

Numerous latency management techniques are available to computer architects looking to design large parallel machines. Latency management techniques can be divided into two broad categories, latency reduction, and latency hiding.

### 2.1.1 Latency Reduction

Latency reduction techniques include architectural trade-offs to optimize local memory access latency, such as non-uniform memory access (NUMA) and cache-only memory architecture (COMA). NUMA architectures cope with the spatial reality of large machines explicitly; thus, local memory references are faster than remote memory references. This is in contrast with busbased architectures that have uniform memory access times. NUMAs typically employ spatial interconnection networks that are inherently more scalable than bus-based architectures. While NUMAs enable better scalability, they are confronted with the issue of how to arrange data so that optimal performance is achieved. One popular method of addressing the data placement issue is to use a directory-based cache coherence mechanism. Examples of cache-coherent NUMAs (ccNUMAs) include Stanford's DASH [LLG+92], and MIT's Alewife [ABC+95]. COMAs, on the other hand, feature automatic data migration through the use of "attraction memories". COMAs also employ spatial interconnection networks that feature non-uniform memory access times, but in a COMA, memory has no home location. Data migrates in a cache-coherent fashion throughout the machine to their points of access. COMAs have the disadvantage of extra hardware complexity, but have an advantage over NUMA machines when the working set of data is larger than the NUMA's cache size. The ADAM architecture is similar to a COMA architecture, except that ADAM also features thread migration, and that there are no caches-in other words, there can be only one valid copy of a piece data in the machine. Removing cache semantics from memory reduces the hardware requirements, but causes ADAM to lose the benefit of automatic data replication. ADAM attempts to compensate for this loss by providing a hardware-recognized immutable data type that is write-once and can be freely copied throughout the machine. Thread migration also helps compensate for

this loss by allowing threads that contend heavily for a single piece of memory to migrate toward the contested memory location.

Latency reduction can also be applied at a lower level, through migration, replication, scheduling, placement and caching. Replication is a property inherent in cache-coherent memory systems where memory can be marked as exclusive or read-only, and several copies can exist throughout the machine to reduce the perceived access latency at multiple nodes. As mentioned previously, ADAM provides only limited support for data replication. Scheduling and placement are predictive techniques that attempt to reduce latency and balance loads by allocating memory and scheduling threads to be near each other. Scheduling and placement can be either directed explicitly by a programmer, inferred and statically linked in by a compiler, or directed by an intelligent runtime system. Scheduling and placement are important latency reduction techniques in any architecture, but are outside the scope of my thesis. A thorough discussion and comparison of migration techniques is reserved for later in this chapter and in chapter 4.

Caches reduce memory latency by keeping the most recently accessed values in a fast memory close to the processor. Caches rely on the statistically good spatial and temporal locality characteristics of data accesses found in most programs. Caches also rely on exclusive ownership of data; since a copy is made of data in main memory, a coherence mechanism is required for correct program execution in an environment where concurrent modification is a possibility. This coherence mechanism can present a challenge when scaling up to very large multiprocessor machines. In particular, simple directory-based or snoopy coherence mechanisms show poor scalability. Snoopy coherence mechanisms are used in bus-based multiprocessors, and suffer from bandwidth limitations due to excess coherence traffic as systems

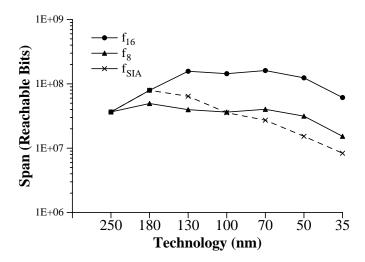

scale in size. Directory-based protocols are more scalable, but they also have their limits. With a 64-byte block size, a simple directory-based cache coherence protocol has a memory overhead of over 200% for a 1024-processor system [CS99], p.565. Techniques such as limited-pointer schemes [ASHH88], extended pointer schemes [ALKK91], and sparse directories [GWM90] can all be used to mitigate the overhead of cache coherence in large parallel systems, but at the cost of more complex protocols or the need for special mechanisms to handle corner cases where the protocol breaks down. The other problem with caches is that technology scaling is not ideal; buffered wire delays have been rising slightly faster than expected, and the expected capacity of caches per access time is anticipated to decrease as process technologies progress [AHKB00] [McF97]. Figure 2.1 illustrates the fallout of non-ideal wire delay scaling. Since the ADAM architecture already features data migration for latency reduction and can tolerate more access latency due to its use of multithreading and decoupling, no data caches are used in the ADAM implementation outlined in this thesis. The elimination of data caches alleviate the scaling concerns of data caches, and it also helps relieve some of the access time pressure resulting from technology constraints. The down-sides of this decision include slower single-threaded code execution and the loss of automatic data replication inherent in cache coherence schemes. Note that the ADAM implementation, as previously mentioned, compensates for this loss of data replication in part by providing an immutable data type, and in part by migrating threads toward heavily contested memory locations.

#### 2.1.2 Latency Hiding

Latency hiding techniques include prefetching, decoupling, multithreading, relaxing memory consistency, and producer-initiated communication.

Prefetching is the use of predictive mechanisms, either automatic or ex-

Figure 2.1: Reachable chip area in top level metal, where area is measured in six-transistor SRAM cells. Directly from [AHKB00]

plicit, to access data before a computation requires the data. The efficacy of prefetching is proportional to the accuracy of the predictive mechanism. When the predictive mechanism is wrong, the system can potentially pay a high cost, because improperly prefetched data could displace useful data while consuming bandwidth that could be used for other useful work. Prefetching can be applied in the ADAM architecture, but its implementation is beyond the scope of this thesis.

Decoupling is the use of explicit queues to hide access or compute latencies. Decoupling is featured in decoupled access-execute (DAE) machines, such as the ZS-1 [SDV<sup>+</sup>87], the WM architecture [Wul92] and the MT-DCAE [SKA01]. Decoupled architectures can be thought of as a type of programmed prefetch architecture, although the decoupling mechanism can also be used to decouple control flow events as well. In a simple DAE architecture, processors are divided into access and execute units, coupled by a set of queues. The access unit is allowed to "slip" ahead of the execute unit, ef-

fectively prefetching data for the execute unit. Since the ADAM uses explicit queues to communicate with threads and to access memory, ADAM shares many of the benefits and problems of DAE architectures.

Multithreading is the use of multiple thread contexts and a fast context switching mechanism to hide memory access latencies. When one thread context stalls on a dependency that requires a lengthy memory access, another thread context is swapped in, thus maintaining a high level of processor utilization. However, multithreading can only effectively hide memory latency if there are enough runnable contexts. As latencies increase, more parallelism is required. The HEP [Smi82a] and TERA [AKK+95] architectures apply multithreading to hide access latencies; the ADAM architecture uses this technique as well.

Relaxed memory consistency models and producer-initiated communication are architectural and programmer-level methods for hiding latency. Relaxing memory consistency models hides latency by allowing systems greater flexibility in hiding write latencies [LW95]. The choice of memory consistency model has a great impact on how a machine is programmed (or compiled to). The ADAM uses a weak ordering model [DS90] similar to that employed in the Alpha [CS99]. Of course, each thread is guaranteed that writes and reads complete in program order on the ADAM as well. Producerinitiated communication reduces latency by cutting out one half of a round trip when the producer and consumer relationships are well-defined. Instead of a consumer sending a message to request data and waiting for the response, producer-initiated communication pushes data into a consumer's cache or queue. In a cache-coherent system, this can lead to higher coherence traffic because all shared copies have to be updated on every write [LW95]. In ADAM, producer-initiated communication is the only mode of communication when using mapped queues. There is no coherence overhead for this

style of communication in ADAM because the queue namespace is separate from memory namespace, and all queue mappings are exclusive by definition.

## 2.2 Migration Mechanisms

Migration mechanisms tend to be tailor-made to a particular architecture, operating system, or application. As a result, the features of migration schemes are equally diverse. For example, in a network-of-workstations (NOW), migration mechanisms tend to operate on coarse-grained processes and objects. Migration on NOWs tend to be under dynamic run-time control, and migration times are on the order of tens to hundreds of milliseconds. [RC96] On the other hand, computation migration on Alewife [HWW93] implements structured activation frame movement throughout the machine using statically compiled migration directives, yielding migration times on the order of several hundreds of processor cycles.

At the least common denominator, every migration mechanism must do the following things: figure out what to move, prepare the receiver, send the data, and then handle any forwarded requests or pointer updates. Thread or process migration schemes also have to handle task scheduling issues as well. Process migration in NOWs is incredibly inefficient and slow because the abstraction boundary for processes is too high; for example, moving a process entails creating a virtual address space and moving file handles. [RC96] introduces a faster, more streamlined version of process migration that removes the restriction that communication producers be frozen during consumer migration (*i.e.*, enables concurrent communication during migration), but even then process migration takes 14 ms. [CM97] also introduces faster techniques for dealing with pointer updates after migration using explicitly managed pointer registries. The problem with explicitly managed pointer registries, however,

is that incorrect program execution results if the programmer forgets to register a pointer. DEMOS/MP [PM83], interestingly, is a multi-processor operating system introduced over a decade before either [RC96] or [CM97], and it features automatic pointer updating and concurrent communication during process migration. DEMOS/MP features explicit OS-managed communication queues for inter-process communication; this helps enable concurrent communication during process migration and simplifies pointer updates because the migration manager does not have to make guesses or conservative assumptions about the process communication mechanism. Unfortunately, the DEMOS/MP paper contains little performance information on its process migration mechanism, so it is more difficult to compare DEMOS/MP against other works. The ADAM thread migration mechanism implements many features of the DEMOS/MP migration mechanism, except at a finer grain and with hardware support.

On SMP-type machines, migration times are shorter, thanks to the tighter integration of network interfaces and processors, generally faster interconnection networks, finer granularity of objects, and globally shared system resources. Page migration in DASH, for example, takes 2 ms (about 66,000 memory cycles) [CDV+94]. This does not include the time spent waiting for locks in the kernel's virtual memory system; the paper indicates that the response time for workloads were not improved because of this overhead. Even if one could migrate threads in DASH by simply throwing a program counter over the fence to another processor, the overhead of migrating the thread's associated process state—the stack and heap—would be fairly large, since at least two memory structures have to be moved, perhaps at the page level of granularity. Thus, the thread scheduler should be aware of a task's memory footprint, and use cache affinity scheduling to achieve good performance. [CDV+94]

Active Threads [WGQH98] introduces user-space thread migration, so as to bypass the overhead of migrating kernel threads. In addition, Active Threads uses simple user-space messaging protocols for communication, to cut the overhead of copying messages and buffers in OS space. User-space thread migration reduces thread migration latencies down to about 150  $\mu$ s (about 16,000 processor cycles). Computation Migration [HWW93] also performs users-space thread migration, but in a more restrictive fashion. In Computation Migration, static annotations in user code cause a thread to spawn new procedures on remote nodes; also, [HWW93] makes no indication that inter-thread communication resources are migrated. A single thread thus snakes its way through the machine, with a trajectory that tracks the location of the working set of data. Computation Migration is fast, as it requires only 651 cycles to start a new thread on a remote processor. Even so, a breakdown of the costs of Computation Migration indicate that a large amount of time is spent in procedure linkage, thread creation, and marshaling thread state. As a side note, Computation Migration is not used as the comparative benchmark for ADAM's migration mechanism because Computation Migration implements a restricted version of thread migration that does not accommodate the level of dynamism or concurrency found in the next fastest migration implementation, Active Threads. Hence, Active Threads is used as the comparison point for ADAM's migration mechanism.

Note that this brief review of migration mechanisms is expanded upon in the background section of chapter 4.

#### 2.2.1 Discussion

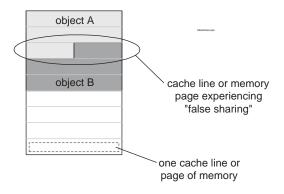

The ADAM architecture structures threads, data, and their communication mechanisms in such a way as to eliminate or drastically reduce the overheads experienced by the migration mechanisms outlined above. For example, almost all migration mechanisms have to deal with pointer updates and message forwarding. The issue is that interthread communications almost always use memory resources, so that any thread migration requires movement of stacks, OS structures, or heap-allocated communication structures. The ADAM architecture condenses communication structures into explicitly named resources through the use of explicit queues. As a result, communication state is stored as part of thread state, and migration of a thread typically involves a single copy operation. The use of bounded capabilities to represent a thread's state in memory, as well as all heap data structures, also simplifies migration, because the region of memory to be copied during migration can be directly computed given a pointer to a thread or data object. The use of bounded capabilities also offers more flexibility in the choice of migration granularity when compared to schemes that require page-level migration, such as that used in DASH [CDV+94]. Another benefit of bounded capabilities is that false data sharing is not possible. For example, in a conventional system two objects can, by random chance, share a cache line or a page of memory (see figure 2.2). If the two memory objects are concurrently accessed by threads on different nodes, the cache line or page of memory will either end up ping-ponging between the nodes, or one thread will have to suffer unfair access times. On the downside, bounded capabilities does not help when a programmer writes code that that explicitly shares objects among many scattered threads. In this case, thread migration should be used to minimize access latencies.

## 2.3 Architectural Pedigree

The genesis of the ADAM architecture lies in the Dataflow architectures, Decoupled-Access/Execute (DAE) architectures, Processor-In-Memory (PIM)

Figure 2.2: Illustration of the false sharing problem.

and Chip Multi-Processor (CMP) architectures, and Cache Only Memory Architectures (COMA).

#### 2.3.1 Dataflow

ADAM is perhaps most closely related to the dataflow family of architectures, in particular, \*T. Hence, a careful examination of the dataflow machines is important at this time.

Dataflow machines are a direct realization of dataflow graphs into computational hardware. Arcs on a dataflow graph are decomposed into tokens. Each token is a continuation; it contains a set of instructions and its evaluation context. The length of the instruction run and evaluation context method encapsulated within a token can characterize the spectrum of dataflow architectures. In the MIT Tagged-Token Dataflow Architecture (TTDA), each token represents roughly one instruction and its immediate dependencies and results, and token storage is managed implicitly. TTDA evolved into the Monsoon architecture, which has explicit evaluation context management and single-instruction tokens. With Monsoon, tokens contained a value; pointers to an instruction, and pointers to evaluation contexts that are compiler-

generated frame allocations in a linearly addressed structure. Monsoon evolved into the P-RISC and \*T architectures, which are machines with tokens that effectively refer to instruction traces and relatively large "stack-frame" style explicitly allocated frames. The tokens in P-RISC and \*T carried only an instruction pointer and a frame pointer, as opposed to any actual data [AB93] [NA89]. One could take this one step further and claim that a Simultaneous Multithreading (SMT) architecture is a dataflow machine with as many tokens as there are thread contexts, and that a conventional Von Neumann architecture is a single-token dataflow machine. [LH94] provides an excellent overview of dataflow machines and an analysis of their shortcomings.

Dataflow machines, while elegant, have a few fatal flaws. Their evolution from the TTDA into near-RISC architectures provides a clue into what these flaws are. The rather abstract TTDA decomposed dataflow graphs to a near-atomic instruction level. Thousands of tokens are created in the course of even a simple program execution, because tokens can be formed and dispatched before dependencies are resolved. [AB93] states that "these tokens represent data local to inactive functions which are awaiting the return of values undergoing computation in other functions invoked from within their bodies". The execution of any token required an associative search across the space of all tokens for the tokens that held the results that satisfied the current token's data dependencies. The multi-thousand element associative structure required to do this search is not implementable even after twenty years of process scaling.

Another flaw of the early Dataflow machines is that every token represents a high-overhead synchronization event. [Ian88] points out that von Neumann architectures also perform a synchronization event between each instruction, but the method of synchronization is very light-weight: IP = IP + 1 or IP = branch target. This allows von Neumann architectures to grind

through straight-line code very quickly. Fortunately for the von Neumann crowd, most code written to date can be straightened out sufficiently with either branch prediction or trace scheduling to get good performance out of such a system. P-RISC and \*T leveraged this strength of von Neumann architectures somewhat by allowing a token to represent what are essentially an execution trace and a stack frame. \*T actually has a very similar single-node architecture to the ADAM: it divides a single node into a synchronization coprocessor and a data processor. The synchronization processor is responsible for scheduling threads and dealing with synchronization issues, while the data processor's exclusive job is to execute straight-line code efficiently. However, the similarity ends there, as the \*T architecture focuses primarily on latency hiding through rapid and efficient thread scheduling, starting, and context switching. While latency hiding through multithreading is an important part of the ADAM architecture, it is also very important to reduce latency by providing mechanisms for the efficient migration of data and threads between processor nodes. The ADAM's overall organization reflects this attention to migration mechanisms. Also, a careful examination of the implementation strategy outlined in [PBB93] reveals a number of important differences (and similarities) between the ADAM and \*T. One significant difference is ADAM's use of a queue-based interface between threads, with implicit synchronization through empty/full bits, similar to the scheme used in the M-Machine [FKD<sup>+</sup>95]. \*T uses a register-based interface with a microthread cache to enable efficient context switching, and explicit, program-level handling of messages that could not be injected into the network. The use of self-synchronizing queues of an opaque depth in ADAM helps cushion network congestion and scheduling hiccoughs.

## 2.3.2 Decoupled-Access/Execute

Decoupled-access/execute (DAE) machines are single-node processors with separate execute and access engines. These engines are coupled with architecturally visible queues that are used to hide memory access latencies. Code for these machines are typically broken down by hand or compiler into an access and execute thread; latencies are hidden because the access thread, which handles memory requests, can "slip" ahead of the execute thread. Relatively few machines have been built that explicitly feature DAE. The architecture was first proposed in [Smi82b] and later implemented as the Astronautics ZS-1 [SDV<sup>+</sup>87]. [MSAD90] characterizes the latency-hiding performance of the ZS-1 in detail, and [MSAD91] compares the performance of the ZS-1 to the IBM RS/6000. A comparison of DAE versus superscalar architectures can be found at [FNN93], and a comparison of DAE versus VLIW architectures can be found at [LJ90]. Another proposed DAE architecture is the WM Architecture [Wul92], and a novel twist on DAE architectures where the access unit is actually co-located with the memory is proposed in [VG98]. The architecture described in this work parallels many of the ideas in [VG98].

The basic message contained in all the previously cited papers is that by judiciously dividing a processor into two spatially distributed processors, greater than 2x performance gains can be realized. This super-linear speedup results from latency that was architecturally bypassed by either allowing the memory subsystem to effectively slip ahead and prefetch data to the execution unit, or by physically co-locating the access unit with the memory. DAE ideas can actually be applied generically to any machine with a large amount of explicit parallelism by simply dividing every program into two threads, an access thread and an execute thread. The advantage of explicit DAE machines is that the synchronization between the access and execute threads is very fast because they are coupled via hardware queues, as opposed to software emu-

lated queues. Some conventional out of order execution machines also provide a certain amount of implicit access/execute decoupling via deep, speculative store and load buffers. However, in general, conventional architectures that emulate these queues in software pay a high price for synchronization overhead. Software implementations that use polling to check empty bits pay the overhead of polling plus any time lost between the actual data availability event and the poll event. Interrupt-driven implementations are also expensive because typical interrupt mechanisms require kernel intervention.

Another important message is that queues are like bypass capacitors for computer architectures. Queues low-pass filter the uneven access patterns of high-performance code and help decouple the demand side of a computation from the supply side of a computation. Like bypass capacitors, the time constant of the queue (*i.e.*, the size of the queue) has to be sufficiently large to filter out the average spike, but not so large as to reduce the available signal bandwidth and hamper important tasks such as context switching. The overhead of the queue structure must also be small so that the benefits of queuing can be realized.

Unfortunately, simple DAE machines as a whole suffer from a few problems. There are no compilers that generate explicit access and execute code streams; most benchmarks and simulations in the cited papers were with hand-coded access and execute loops. Also, the effectiveness of DAE is questionable on complicated loops and programs with complicated and/or dynamic dataflow graphs. Simple DAE is targeted at hiding memory latencies, and not much else. However, the basic idea of decoupling access and execute units is a powerful one; especially if the physical access and execute units are allowed to be assigned dynamically to a single virtual control thread, as is the case in ADAM. Creating these "virtual" DAE machines allows access and execute units to migrate throughout the machine and optimize latency on a

thread by thread basis. A sufficiently flexible infrastructure would also allow several execute units to be chained together, thus providing a kind of loop unrolling and a facility for streaming computations without any modification to the code. Because this chaining is dynamic, such a machine could be upgraded to have more processors and a greater performance would be realized without recompiling the code. This idea of a virtual DAE architecture is an important part of the ADAM architecture.

# 2.3.3 Processor-In-Memory (PIM) and Chip Multi-Processors (CMP)

Recent advances in process technology have made it possible to integrate a sufficient amount of SRAM on-chip to make a single-chip stand-alone processor node. Also, the availability of DRAM embedded on the same die as a processor opens the door to even higher levels of memory integration [Corb] [Mac00] [Cora]. This integration of processors and memory on a single die is referred to as Processor-In-Memory (PIM). The fact that the memory is included on the same die as the processor implies a power and performance advantage due to the elimination of chip-chip wiring capacitances and wire run lengths. It also offers a performance advantage because more wires can be run between the memory bank and the processor than in a discrete processormemory solution. As process technology continues to improve, it will be possible to put several processor cores plus memory on a single silicon die. This style of implementation is known as a Chip Multi-Processor (CMP). A paper that summarizes some of the key arguments for CMP architectures can be found in [ONH+96]. Some architectures that have been proposed which take advantage of some combination of embedded memory technology and chip multiprocessor technology include RAW [LBF<sup>+</sup>98], I-RAM [KPP<sup>+</sup>97], Active Pages [OCS98], Decoupled Access DRAM [VG98], Terasys [GHI94],

SPACERAM [Mar00], and Hamal [Gro01].

The level of performance available to users of embedded DRAM is remarkable. Traditionally, DRAM is thought of as the sluggish tanker of memory, while SRAM is the speed king. A recent DRAM core introduced by MoSys (the so-called 1-T SRAM), available on the TSMC process, has proven that DRAM has a place in high performance architectures [Cora]. The 1-T SRAM is based on a DRAM technology, but has a refreshless interface like a SSRAM (synchronous SRAM). The performance of this macro is also sufficiently high – 2-3 cycle access times at 450 MHz in a 0.13  $\mu$ m process – to entirely eliminate the need for data caches in the processor design. Note that the processor frequency targets for ADAM is on par with compiled "soft core" processor frequency targets, which is typically a factor of 2-4 below the level of the full-custom processors developed by Intel, AMD, and Compaq. The ADAM is assumed to be implemented using a portable RTL design flow, optimized for fast design cycles and portability to the latest process technology offered by foundries. The reduced implementation time and the CMP architecture of the ADAM helps compensate for the performance penalty of using a compiled design flow. Finally, because the 1-T SRAM has the memory cell structure of DRAM, the density of these macros is similar to the embedded DRAM macros offered in other processes (2.09 mm<sup>2</sup> per Mbit for a DRAM macro on IBM's Cu-11 process [Mac00] versus 1.9 mm<sup>2</sup> per Mbit for a MoSys macro on a TSMC 0.13  $\mu$ m logic process [Cora]).

The ADAM architecture leverages both the high level of logic integration available in future process technology and the availability of off-the-shelf, fast, dense memories to create a distributed massively parallel architecture with good single-threaded code performance.

#### 2.3.4 Cache Only Memory Architectures

While the architecture proposed in this thesis has no data caches, one could argue that the speed of the memories used in the processor nodes qualifies them as program-managed caches. Hence, it is important to look at the class of machines known as Cache Only Memory Architectures (COMA). The most relevant machine in this class in the Data Diffusion Machine (DDM) [MSW93]. The DDM relies on data migration through the implicit semantics of caches. Because this work is so closely tied to data migration and its control, a thorough discussion of how ADAM relates to the DDM is deferred until section 4.

# **Chapter 3**

## **Aries Decentralized**

### **Abstract Machine**

While Newton is to have said (sarcastically, in truth, but that's another story) that he saw farther by standing on the shoulders of giants, most of us squat on the kneecaps of pygmies. But that is meant in the nicest possible way.

—Thomas H. Lee, ISSCC 2002 Panelist Statement

The Aries Decentralized Abstract Machine (ADAM) is an abstract parallel computer architecture optimized for, among other things, fast data and thread migration. This chapter presents an overview of the architecture, highlighting the salient features that enable the implementation of high performance migration. A simple code example is presented first, to acquaint readers with basic ADAM communication and memory abstractions. The example is followed by a more formal, in-depth discussion of various features of the ADAM.

#### 3.1 Introduction to ADAM by Code Example

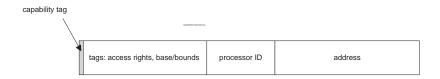

ADAM has a fine-grained multithreaded programming model. Inter-thread communication and memory access is accomplished via explicit queue resources. Also, memory is abstract; pointers are represented as capabilities with base and bound tags. Programmers cannot create capabilities; they must request one from the machine via an ALLOCATE opcode.

#### **3.1.1 Basics**

A simple program example that illustrates the salient features of the architecture can be seen in figure 3.2. This code illustrates procedure linkage, capability allocation, and memory mappings. The basic format of assembly opcodes is OP qa, qb, qc, where OP is the operation, qa and qb are the arguments, and qc is the result. Every operation may have zero, one or two arguments, and one of the arguments may be a constant. There are also some important opcodes that do not follow this format, such as MAPQC, that will be discussed soon. Also note that every queue specifier can be modified with an @ (copy/clobber) modifier. Figure 3.1 demonstrates the operation of the @ modifier. On reads, an @ specifies that the instruction should copy the value from an argument queue, instead of dequeuing it. On writes, an @ specifies that the instruction should overwrite ("clobber") the newest value in a queue, if there is one, instead of enqueuing a value. If the destination queue is empty, the @ operator has no effect. The @ operator is handy when dealing with temporaries that are reused frequently; without it, any time a result is used more than once, the programmer or compiler would have to include a special instruction to duplicate values.

```

MOVEC 2, q0 ; initialize q0 with the number 2 MOVEC 1, q1 MOVEC 4, q1 ; initialize q1 with the numbers 1 and 4 ADD @q0, q1, q2 ; at this point, q2 has 3, q0 has 2, q1 has 4 ADD q0, q1, @q2 ; at this point, q0 is empty, q1 is empty, and q2 has 6

```

Figure 3.1: Demonstration of the copy/clobber (@) modifier.

#### 3.1.2 Calling Convention

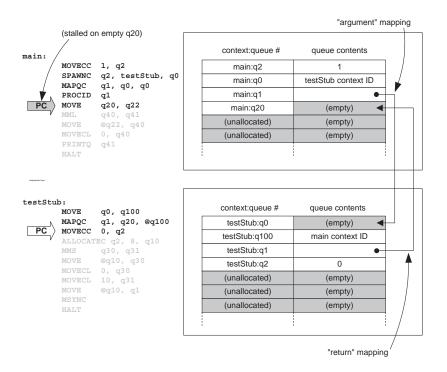

In ADAM, the calling convention is that every procedure is a new thread. Arguments and return values are passed via queue mappings. The code in figure 3.2 demonstrates this calling convention. The caller, main, calls test—Stub by executing a SPAWNC q2, testStub, q0 instruction. This instruction starts a new thread with its program counter set to the label test—Stub and returns the new thread's context ID in q0. The argument q2 is the *spawn metric*; this lets the programmer control the placement of new threads. In this case, the spawn metric was initialized to 1, which causes the new thread to be started on some node one network hop away.

After creating the new thread, the caller maps a queue into the callee's queue space to initiate argument passing. *Mapping a queue* causes values written into the mapped queue to appear eventually in the map target. The storage location of data written into a mapped queue is the map target. Also, communication via queue maps is push-only; one cannot read from a mapped queue. Hence, once a queue is mapped, it is write-only; a read from a mapped queue results in undefined behavior. In this example, the new thread expects all of its arguments in q0, so the caller maps to the new thread using the instruction MAPQC q1, q0, @q0. Note that the MAPQC instruction has unusual semantics. The first two arguments are actually immediate constants; in

```

main:

MOVECC 1, q2

; set spawn metric to 1

SPAWNC q2,testStub,q0 ; spawn remote thread

MAPQC q1, q0, @q0 ; map to my child

PROCID q1

; send my procID to child

q20, q22 ; wait for return val from child q40, q41 ; declare q40, q41 as load queues @q22, q40 ; initialize q40 w/capability 0, q40 ; retrieve data from offset 0 q41 : print (sim apposition)

MOVE

MML

MOVE

MOVECL 0, q40

PRINTQ q41

; print (sim specific instruction)

HALT

testStub:

MOVE

q0, q100

; store caller in q100

MAPQC q1, q20, @q100; my q1 -> q20 of my caller

MOVECC 0, q2

; set allocate metric to 0

ALLOCATEC q2, 8, q10 ; allocate 8-word local capability

MMS

q30, q31 ; declare q30, q31 as store queues

MOVE

@q10, q30

; init q30 w/capability

MOVECL 0, q30

; store data 10 at offset 0

MOVECL 10, q31

MSYNC

; ensure that store has committed

@q10, q1

MOVE

; send the capability to my caller

HALT

```

Figure 3.2: Simple code example demonstrating procedure linkage, thread spawning, memory allocation, and memory access.

other words, they are interpreted as simply queue numbers, and not as sources for operands. The first value, q1, specifies the local queue to be mapped. The second value, q0, specifies the queue number of the map target. The final argument, @q0, specifies the queue from which to read the map target's context ID. I chose the first two values to be constant values because programmers or compilers typically know exactly what the source and destination queue numbers of a mapping should be.

Now that the caller has mapped the argument queue to the callee, the caller first passes its context ID to the callee. Upon receiving the caller's context ID, the callee maps a return queue back to the caller. In this example, the caller and callee agree by convention that q20 is the return value queue. Figure 3.3 illustrates the state of the caller and callee after setting up the argument and return queues.

#### 3.1.3 Memory Allocation and Access

The next set of instructions in our code example demonstrate memory allocation and access. Memory allocation in ADAM is accomplished with the ALLOCATE instruction, and memory access is accomplished through queue mappings.

In this particular example, the instruction ALLOCATEC q2,8,q10 is used to create a new capability. q2 is an allocation metric similar to the spawn metric used by the SPAWNC opcode. In this case, q2 is initialized to 0, so this instruction is requesting the allocation of local memory.

The next instruction, MMS q30, q31, declares q30 and q31 to be store queues. The arguments to MMS are immediate constants, similar to the MAPQC instruction. Subsequent to the MMS instruction, q30 is a *store address* queue, and q31 is a *store data* queue. Data can be stored to memory using this pair of queue mappings by enqueuing address and data pairs into their re-

Figure 3.3: Thread states after thread spawn and procedure linkage.

spective queues. Before storing data using these queues, the store address queue must be initialized with a store capability. This is accomplished by the MOVE @q10, q30 instruction; it copies the allocated capability in q10 into the store address queue q30. Subsequent writes into the store address queue should be constant offsets to the initial capability; the memory subsystem is responsible for adding this offset and checking for bounds violations. Writing another capability into the store address queue causes the store address queue to be re-initialized with the new capability.

In our code example, a single value, 10, is stored at offset 0. The thread testStub then performs an MSYNC to ensure that the store has committed, and sends the memory capability to the calling thread and halts. The caller, main, then establishes load address and load data queues using the MML q40, q41 instruction. main then accesses the returned data capability by sending a copy of the capability into the load address queue, q40. main then prints the return value from memory and halts. The PRINTQ instruction is a convenience instruction only used in the simulator implementation for debugging purposes. The final state of our machine at the end of our code example run is illustrated in figure 3.4.

#### 3.2 Programming Model

This section fleshes out some of the basic architectural features of ADAM presented in the simple code example. For a discussion of architectural features and implementation details not directly relevant to migration, please see appendix B. Things discussed in appendix B include the instruction formats, detailed breakdowns of the capability format bitfields, exception handling, and kernel/OS interactions. For a comprehensive review of the opcodes provided in ADAM, please refer to appendix D.

Figure 3.4: Thread states after memory allocation and access.

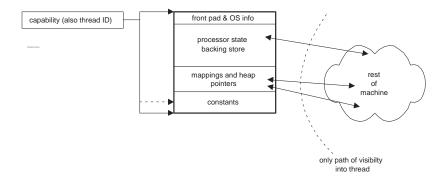

#### 3.2.1 Threads

The fundamental unit of computation in ADAM is a thread. Threads are very lightweight under ADAM, and they are opaque, monolithic memory structures. They could almost be called continuations except that they carry an activation frame's worth of data in addition to a program counter and an environment pointer. Every thread's state has a one-to-one mapping with a region of memory, as seen before in the named state register file [ND91]. The address and bounds of this region of memory is identified by a capability; this capability is referred to as a thread's *context ID*. Thus, any thread can be globally uniquely identified by its context ID, because the context ID is just a pointer into memory. Also, the number of threads per processor is limited only by the amount of memory available. The correlation of every thread state to a region of memory allows thread and data migration implementations to share the same basic mechanism. A summary of the state associated with a single ADAM thread can be seen in figure 3.5.

Figure 3.5: Programming model of ADAM

In place of registers in a typical machine, ADAM supplies queues of an unspecified depth. The output of any queue can be remapped onto the input of another queue in another thread context for inter-thread communications. This technique is referred to as *queue mapping*.

Arguments and return values are passed between threads via queue mappings; there is no stack in ADAM. Also, communication to memory is implemented using queue mappings. Hence, all visibility into and out of a thread occurs via a set of queue mappings. This idea is illustrated in figure 3.6. The use of queue mappings simplifies an implementation of thread migration first by isolating all thread state, including communication state, within a single contiguous region of memory, and second by enabling simple mechanisms for managing the forwarding of communications concurrently with migration. These migration mechanisms will be described in chapter 4.

Figure 3.6: Structure of an ADAM thread

#### 3.2.2 Queues and Queue Mappings

To a first approximation, the queues supplied by ADAM are of infinite depth. However, in a realistic implementation, the performance of the queues diminishes as more data is shoveled into them. Hence, while the programming abstraction allows programmers to store large amounts of data in queues, this should be avoided for performance reasons. If a programmer obeys this restriction, the queues should perform comparably to a register in a standard RISC machine (see appendix C for implementation details). Also, when the queues are used as a communication element between streaming threads, flow control is accomplished by applying back-pressure (*i.e.* enqueue stalling) proportional to their fullness. This allows programmers to chain together streaming threads that compute at different rates without having to deal with flow control explicitly.

Queue mapping is the recommended method for inter-thread communication. Data from any given source is guaranteed to arrive in-order in the destination context's queue; however, when more than one sender is mapped to a single receiver, there is no guarantee as to the ordering of the received values between the two senders. A node can request that the source ID of incoming data be enqueued in a secondary queue in lock-step with the primary destination queue, so that ambiguity created by such a situation can be resolved by user code. While a programmer can communicate data between threads by passing around heap-allocated data structures, it is not recommended because ADAM's memory model uses weak ordering [LW95], and makes no guarantees on the relative ordering of memory requests between threads. Using heap-allocated data structures for inter-thread communication can also be less efficient than direct queue mappings in the presence of thread migration, because heap-allocated communication structures do not automatically migrate with threads.

ADAM queues can assume register semantics when necessary via a copy/ clobber modifier, as described in the code example at the beginning of this chapter.

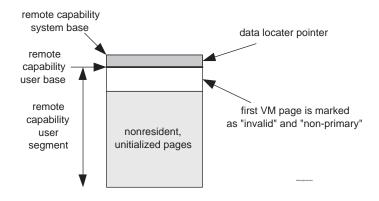

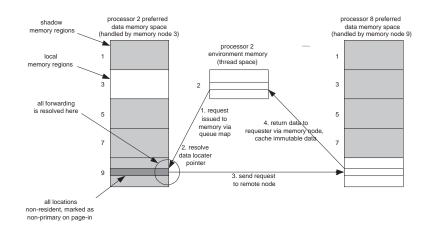

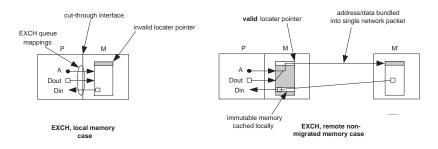

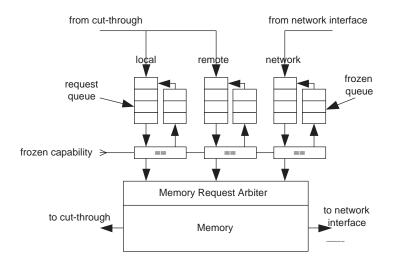

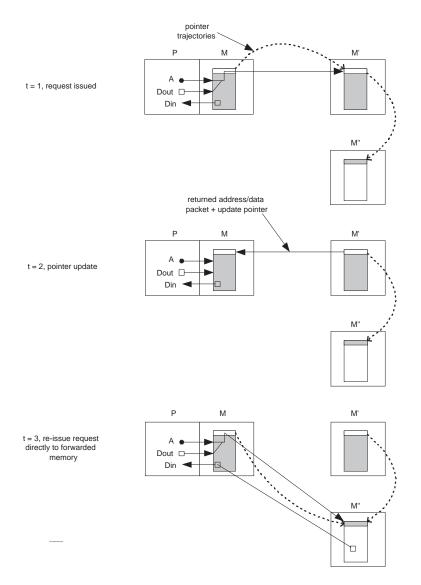

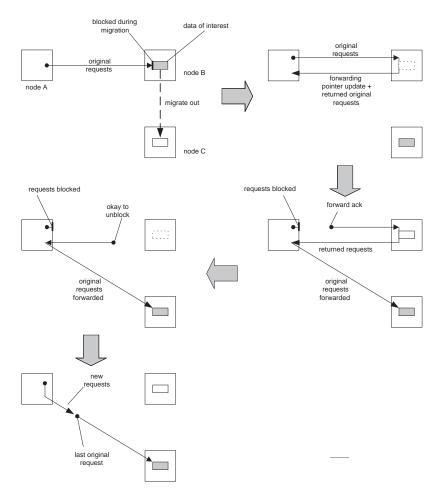

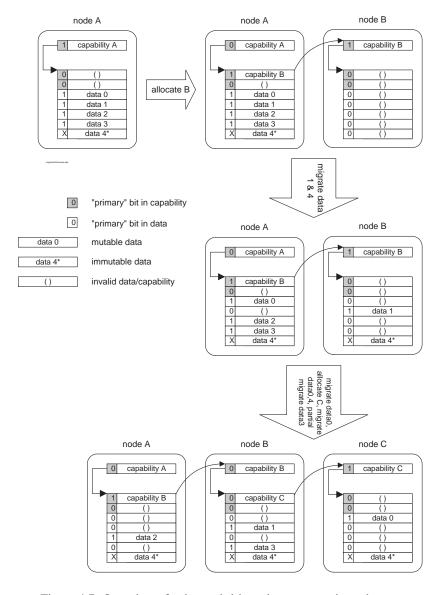

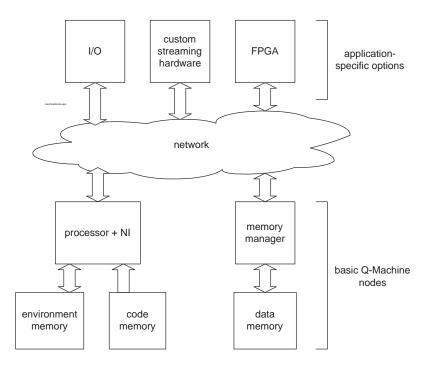

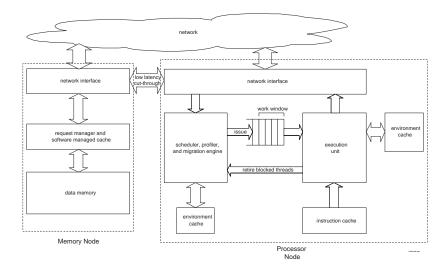

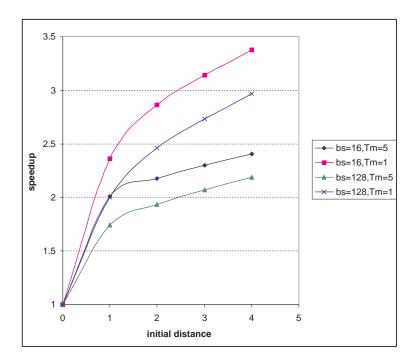

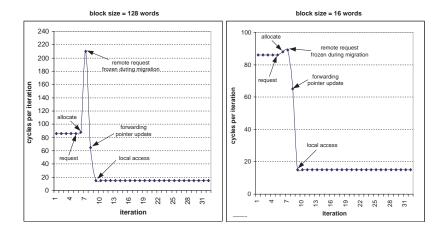

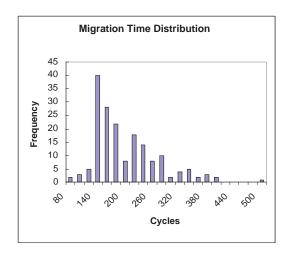

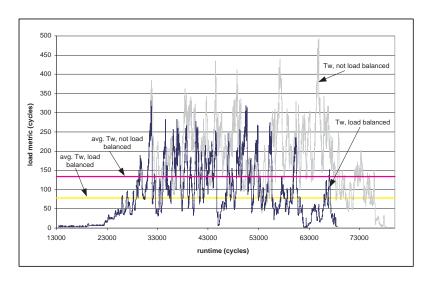

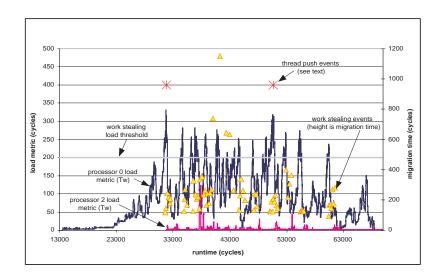

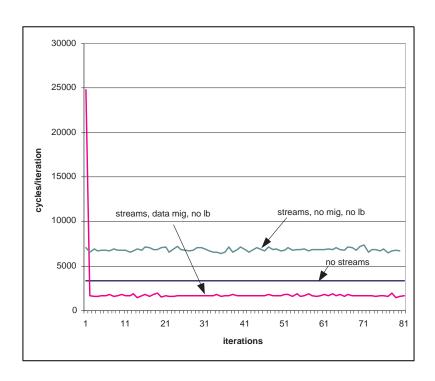

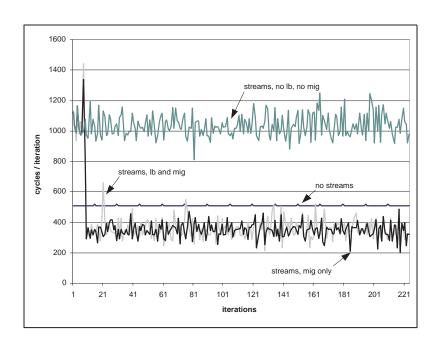

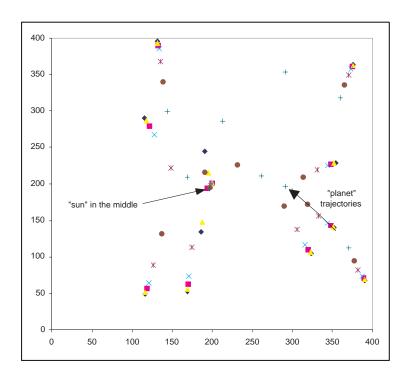

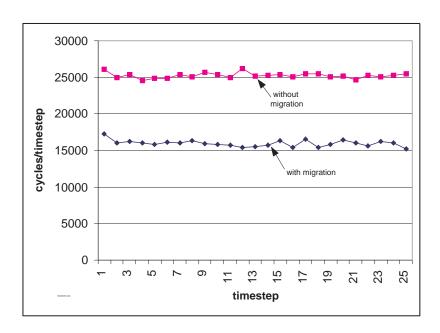

#### 3.2.3 Memory Model