# **Self-adaptivity of Applications on Network on Chip Multiprocessors**

#### The Case of Fault-tolerant Kahn Process Networks

Doctoral Dissertation submitted to the

Faculty of Informatics of the Università della Svizzera Italiana

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

presented by

### **Onur Derin**

under the supervision of Prof. Mariagiovanna Sami

May 2015

### **Dissertation Committee**

| Prof. Matthias Hauswirth | Università della Svizzera italiana, Lugano, Switzerland |

|--------------------------|---------------------------------------------------------|

| Prof. Dr. Miroslaw Malek | Università della Svizzera italiana, Lugano, Switzerland |

| Prof. Fernando Pedone    | Università della Svizzera italiana, Lugano, Switzerland |

| Prof. Dr. Peter Marwedel | Technische Universität Dortmund, Dortmund, Germany      |

|                          |                                                         |

Dissertation accepted on 19 May 2015

Research Advisor PhD Program Director

Prof. Mariagiovanna Sami Prof. Igor Pivkin

I certify that except where due acknowledgement has been given, the work presented in this thesis is that of the author alone; the work has not been submitted previously, in whole or in part, to qualify for any other academic award; and the content of the thesis is the result of work which has been carried out since the official commencement date of the approved research program.

Onur Derin Lugano, 19 May 2015

To my family

The way to succeed is to double your failure rate.

Thomas J. Watson

### **Abstract**

Technology scaling accompanied with higher operating frequencies and the ability to integrate more functionality in the same chip has been the driving force behind delivering higher performance computing systems at lower costs. Embedded computing systems, which have been riding the same wave of success, have evolved into complex architectures encompassing a high number of cores interconnected by an on-chip network (usually identified as Multiprocessor Systemon-Chip). However these trends are hindered by issues that arise as technology scaling continues towards deep submicron scales. Firstly, growing complexity of these systems and the variability introduced by process technologies make it ever harder to perform a thorough optimization of the system at design time. Secondly, designers are faced with a reliability wall that emerges as age-related degradation reduces the lifetime of transistors, and as the probability of defects escaping post-manufacturing testing is increased.

In this thesis, we take on these challenges within the context of streaming applications running in network-on-chip based parallel (not necessarily homogeneous) systems-on-chip that adopt the no-remote memory access model. In particular, this thesis tackles two main problems: (1) fault-aware online task remapping, (2) application-level self-adaptation for quality management. For the former, by viewing fault tolerance as a self-adaptation aspect, we adopt a cross-layer approach that aims at graceful performance degradation by addressing permanent faults in processing elements mostly at system-level, in particular by exploiting redundancy available in multi-core platforms. We propose an optimal solution based on an integer linear programming formulation (suitable for design time adoption) as well as heuristic-based solutions to be used at run-time. We assess the impact of our approach on the lifetime reliability. We propose two recovery schemes based on a checkpoint-and-rollback and a rollforward technique. For the latter, we propose two variants of a monitor-controller-adapter loop that adapts application-level parameters to meet performance goals. We demonstrate not only that fault tolerance and self-adaptivity can be achieved in embedded platforms, but also that it can be done without incurring large overheads. In addressing these problems, we present techniques which have been realized (depending on their characteristics) in the form of a design tool, a runtime library or a hardware core to be added to the basic architecture.

### **Acknowledgements**

I am indebted to numerous people for their support in the creation of this thesis. First and foremost, this work would not be possible if it was not for the hospitable environment offered by ALaRI and University of Lugano. For that I am forever grateful to the administration, in particular, to Prof. Mariagiovanna Sami, Prof. Miroslaw Malek, Umberto Bondi and the late Prof. Luigi Dadda. Mariagiovanna, as my research advisor, has provided me with continuous support, guidance and patience. Not only as a scientist but as a person, her example sets a high standard to follow for the rest of my life.

I feel privileged to have taken part in the MADNESS Project and I would like to thank all of its members, in particular Prof. Luigi Raffo, Paolo Meloni, Giuseppe Tuveri and Sebastiano Pomata (University of Cagliari) for providing the baseline platform upon which our implementation is built; Prof. Todor Stefanov and Emanuele Cannella (University of Leiden) for hosting me during my research visit and HiPEAC Network of Excellence for providing me a collaboration grant. I would also like to thank the members of my dissertation committee whose insightful comments helped me to improve this work.

While carrying out the work presented in this thesis, I had the opportunity to tutor some master of science students enabling me to investigate a variety of research problems and to offload some of the required engineering effort. Throughout the years our relationships have evolved into dear friendships. I hope I have been as impactful in their lives as they have been in mine. In particular, I would like to thank Deniz Kabakcı for the implementation of remapping heuristics in C; Karim M. A. Ali for coding of the TMH in VHDL; Poorna C. S. Alamanda for helping with tedious roll-forward recovery experiments; Prasanth K. Ramankutty for the implementation of the fuzzy controller and carrying out extensive experiments; Mariano Perna and Enea Affini for suffering the bugs of the platform and helping in their identification; Erkan Diken for exploring self-adaptation with the SACRE-Noxim integration; Katarina Balać and Aleksandra Jovanović for exploring self-adaptation in the GStreamer framework; and lastly Erick Amador, Amrit Panda, Yücel Şahin and Sherif El-Wafa for helping me ex-

plore other research areas towards the beginning of my studies.

I am also thankful to all of my colleagues at ALaRI, in no particular order, Leandro, Jelena, Antonio, Alberto, Giovanni, Francesco, Daniela, Katarina, Slobodan, Igor, Rami, Yum, Elisa, Janine, Carola, Luca and Marco for their support, availability and friendship. Life in Lugano has been even sunnier for me thanks to some of my friends, of whom I can list only a few: Cumhur, Ali, Korman, Gamze, Sertuğ, Burcu, Seda, Oktay and Caner. Without their moral support, these years would have been more difficult and less joyful.

Finally, the process leading to the completion of this thesis was as hard for my wife, Rana, as it was for me. I cannot thank her enough for being by my side. My deepest gratitude is to my parents who have lived through this world by making one not from zero but from minus one.

### **Contents**

| Co  | nten    | ts                                            | хi  |

|-----|---------|-----------------------------------------------|-----|

| Lis | st of l | Figures                                       | xv  |

| Lis | st of ' | Tables                                        | xix |

| Lis | st of   | Abbreviations                                 | xxi |

| 1   | Intr    | oduction                                      | 1   |

|     | 1.1     | Motivation                                    | 2   |

|     |         | 1.1.1 The need for self-adaptation            | 2   |

|     |         | 1.1.2 The need for fault tolerance            | 4   |

|     | 1.2     | Research framework                            | 7   |

|     |         | 1.2.1 KPN and PPN as the model of computation | 9   |

|     | 1.3     | Dissertation contributions                    | 11  |

|     | 1.4     | Organization of the dissertation              | 13  |

| 2   | Bacl    | kground and Related Work                      | 15  |

|     | 2.1     | Self-adaptive systems                         | 15  |

|     |         | 2.1.1 Adaptation coverage                     | 16  |

|     |         | 2.1.2 Separation of concerns                  | 18  |

|     |         | 2.1.3 Adaptation management                   | 18  |

|     |         | 2.1.4 Adaptation requirements specification   | 19  |

|     | 2.2     | MPSoC programming models                      | 19  |

|     | 2.3     | Kahn Process Networks                         | 22  |

|     | 2.4     | Polyhedral Process Networks                   | 24  |

|     | 2.5     | KPN for MPSoCs                                | 25  |

|     | 2.6     | Mapping applications to NoCs                  | 26  |

|     | 2.7     | Task migration                                | 28  |

|     | 2.8     | Fault tolerance                               | 29  |

xii Contents

|   |      | 2.8.1   | Fault detection                                          | 29 |

|---|------|---------|----------------------------------------------------------|----|

|   |      | 2.8.2   | Error recovery                                           | 30 |

|   |      | 2.8.3   | Related fault tolerance approaches in embedded systems . | 31 |

|   |      | 2.8.4   | The lifetime reliability aspect                          | 37 |

|   | 2.9  | Applic  | cation-level self-adaptation for quality management      | 37 |

|   |      | 2.9.1   | Adaptation of application-level parameters               | 38 |

|   |      | 2.9.2   | Quality management in multimedia systems                 | 39 |

| 3 | Refe | rence l | Platform                                                 | 41 |

|   | 3.1  | Archit  | ectural support                                          | 41 |

|   |      | 3.1.1   |                                                          | 43 |

|   |      | 3.1.2   | Inter-processor interrupt generation support             | 44 |

|   | 3.2  | Softwa  | are/Middleware infrastructure                            | 45 |

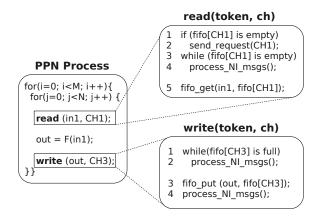

|   |      | 3.2.1   | Application model                                        | 46 |

|   |      | 3.2.2   | PPN middleware                                           | 47 |

|   | 3.3  | Fault-t | tolerance support                                        | 50 |

|   |      | 3.3.1   | Fault model                                              | 51 |

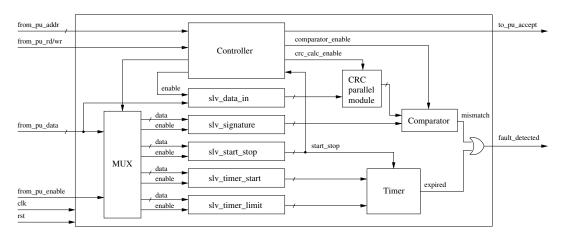

|   |      | 3.3.2   | Online self-testing support                              | 56 |

| 4 | Faul | t-awar  | e Online Task Remapping                                  | 59 |

| - | 4.1  |         | ibutions with respect to the state of the art            | 59 |

|   | 4.2  |         | rmulation of the mapping problem                         | 64 |

|   | •    | 4.2.1   | Minimization of the communication cost                   | 65 |

|   |      | 4.2.2   | Minimization of the total execution time                 | 67 |

|   |      | 4.2.3   | Multi-objective optimization with ILP                    | 68 |

|   | 4.3  |         | Online task remapping                                    | 69 |

|   |      | 4.3.1   | Optimal task remapping                                   | 69 |

|   |      | 4.3.2   | Center of Gravity heuristic (CoG)                        | 70 |

|   |      | 4.3.3   | Nonidentical Multiprocessor Scheduling (NMS)             | 72 |

|   |      | 4.3.4   | Localized NMS Heuristic (LNMS)                           | 73 |

|   | 4.4  |         | eliability aspect                                        | 74 |

|   |      | 4.4.1   | Reliability estimation for online task remapping         | 74 |

|   |      | 4.4.2   | Reliability estimation for N-modular redundancy          | 76 |

|   | 4.5  | Experi  | imental results                                          | 81 |

|   |      | 4.5.1   | Case study: the MPEG-2 decoder                           | 82 |

|   |      | 4.5.2   | A synthetic task graph                                   | 85 |

|   |      | 4.5.3   | Case studies on the platform                             | 89 |

|   |      | 4.5.4   | Evaluation of the remapping strategies on the platform   | 90 |

|   |      | 4.5.5   | Reliability evaluation                                   | 92 |

xiii Contents

|   | 4.6  | Summ    | nary                                                       | . 96  |

|---|------|---------|------------------------------------------------------------|-------|

| 5 | Reco | overy S | Support in the Fault-aware Run-time Environment            | 99    |

|   | 5.1  | Contri  | ibutions with respect to the state of the art              | . 99  |

|   | 5.2  |         | Fine-grained checkpointing and rollback based fault recove |       |

|   |      | 5.2.1   | Modifications to the PPN processes                         |       |

|   |      | 5.2.2   | Fault-aware remapping support                              | . 104 |

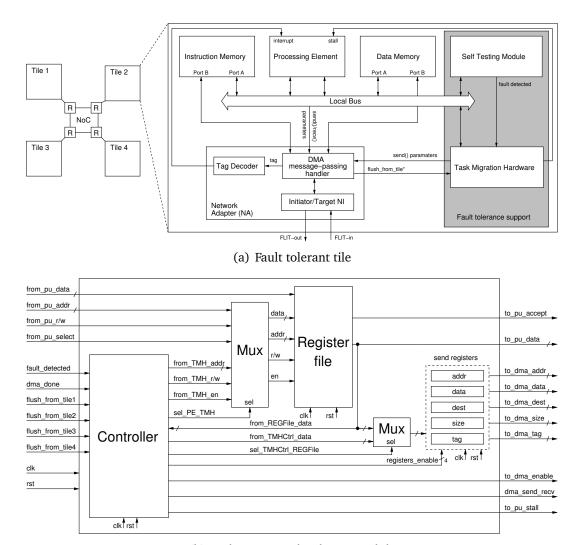

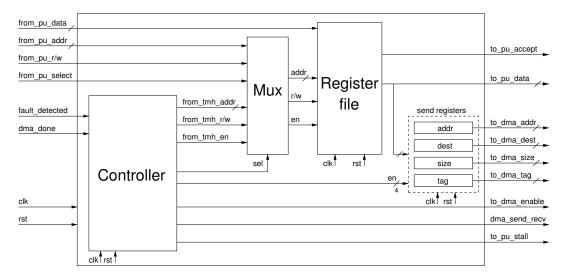

|   |      | 5.2.3   | Task migration hardware module                             | . 106 |

|   | 5.3  | RFR: I  | Roll-forward fault recovery                                |       |

|   |      | 5.3.1   | Task migration hardware module                             | . 109 |

|   |      | 5.3.2   | Fault-aware remapping support                              |       |

|   |      | 5.3.3   | Modifications to the PPN processes                         |       |

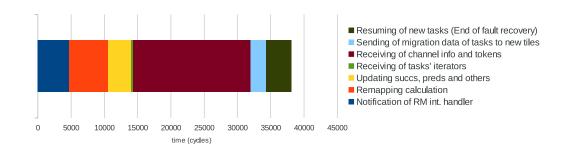

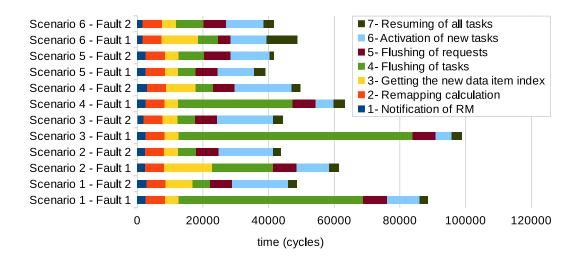

|   | 5.4  | Exper   | imental results for CRR                                    |       |

|   |      | 5.4.1   | Fault recovery time overhead                               |       |

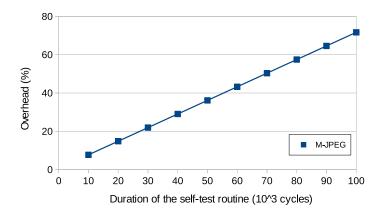

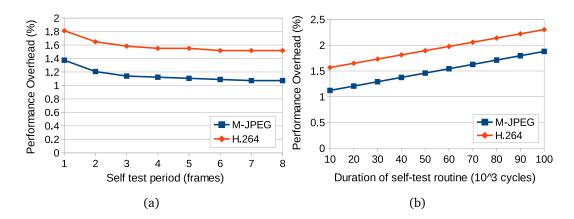

|   |      | 5.4.2   | Steady-state performance overhead                          |       |

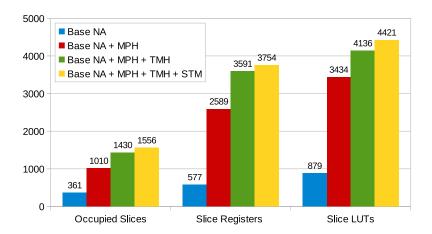

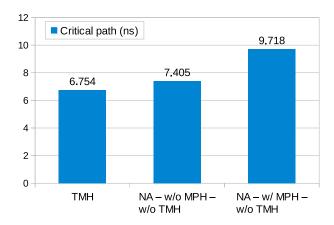

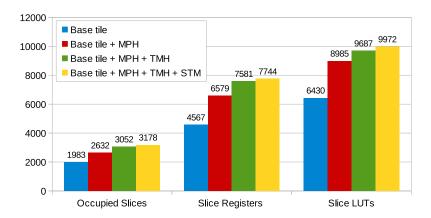

|   |      | 5.4.3   | Architectural support hardware overhead                    |       |

|   | 5.5  | Exper   | imental results for RFR                                    | . 119 |

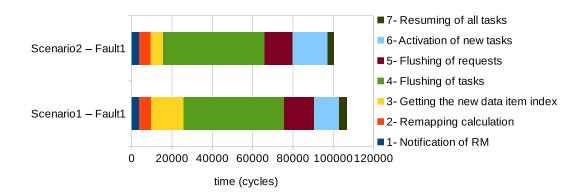

|   |      | 5.5.1   | Fault recovery time overhead                               | . 119 |

|   |      | 5.5.2   | Steady-state performance overhead                          | . 121 |

|   |      | 5.5.3   | Architectural support hardware overhead                    | . 123 |

|   | 5.6  | Summ    | nary                                                       | . 123 |

| 6 | App  | licatio | n-level Self-adaptation for Quality Management             | 125   |

|   | 6.1  |         | ibutions with respect to the state of the art              |       |

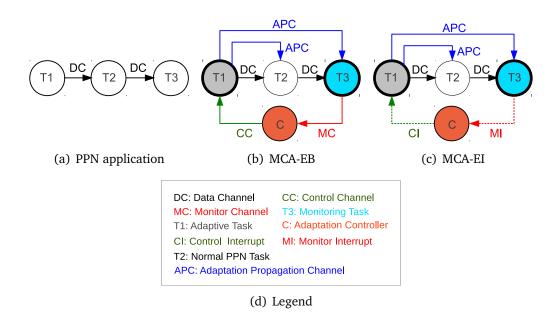

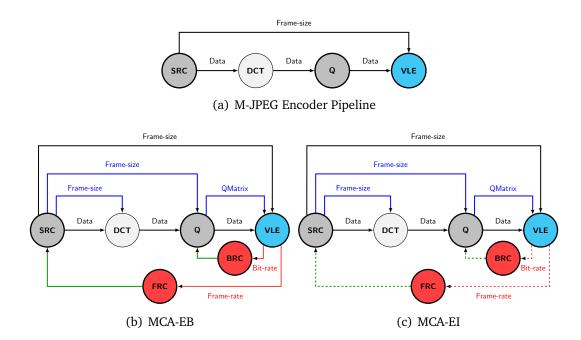

|   | 6.2  |         | EB: Self-adaptation with blocking channels                 |       |

|   |      | 6.2.1   | Adaptive task                                              |       |

|   |      | 6.2.2   | Monitoring task                                            |       |

|   |      | 6.2.3   |                                                            |       |

|   | 6.3  | MCA-l   | EI: Self-adaptation using inter-processor interrupts       |       |

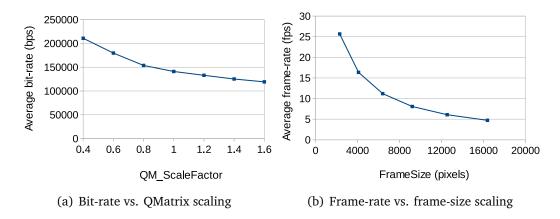

|   | 6.4  |         | study: Motion JPEG                                         |       |

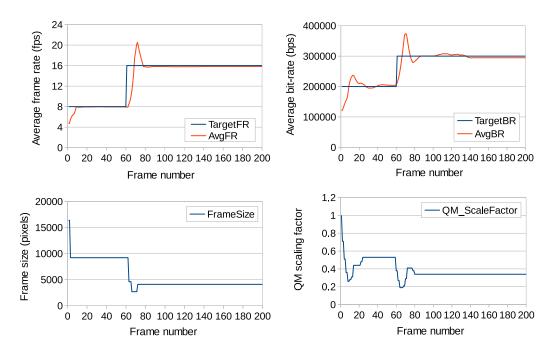

|   |      | 6.4.1   | Self-adaptive M-JPEG with MCA-EB                           |       |

|   |      | 6.4.2   | Self-adaptive M-JPEG with MCA-EI                           |       |

|   | 6.5  | Result  | s for MCA-EB                                               |       |

|   |      | 6.5.1   | Bit-rate and frame-rate adaptation tests                   | . 147 |

|   |      | 6.5.2   | Fast video vs. slow video                                  |       |

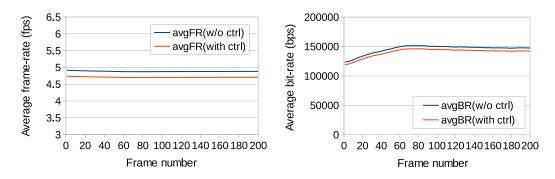

|   |      | 6.5.3   | Cost of adaptation                                         |       |

|   | 6.6  |         | arison of MCA-EB and MCA-EI                                |       |

|   |      | 6.6.1   | Adaptation overhead                                        |       |

|   |      | 6.6.2   | Control quality                                            |       |

| xiv |  | Contents |

|-----|--|----------|

|     |  | -        |

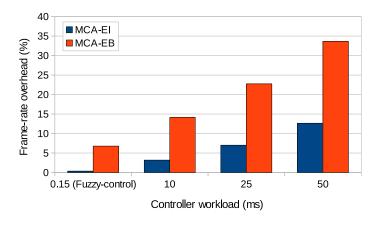

|     | 6.7   |         | Adaptation overhead vs. Controller workload ary |     |

|-----|-------|---------|-------------------------------------------------|-----|

| 7   | Con   | clusion | and Future Work                                 | 155 |

| Bil | bliog | raphy   |                                                 | 161 |

## **Figures**

| 1.1 | Model of a self-adaptive system                                                                                                              | 8  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Overview of the proposed self-adaptive and fault-tolerant system                                                                             | 12 |

| 2.1 | A KPN process with single input and output channels                                                                                          | 22 |

| 2.2 | Example of a PPN (a) and structure of process $P2$ (b)                                                                                       | 24 |

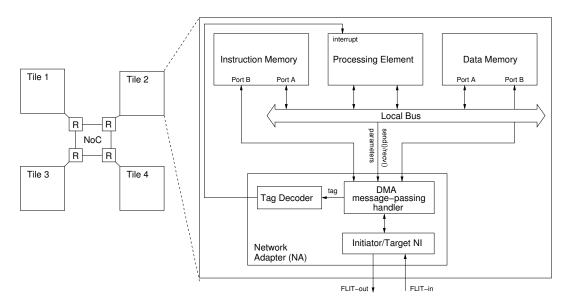

| 3.1 | A general overview of the baseline tile architecture                                                                                         | 42 |

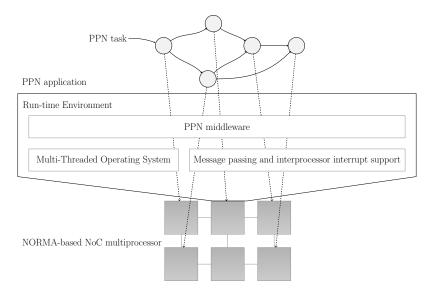

| 3.2 | Software stack in the reference platform                                                                                                     | 45 |

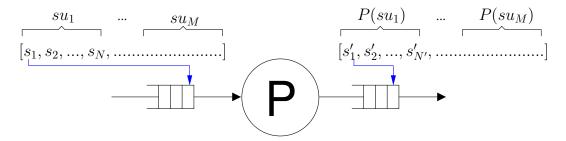

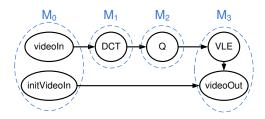

| 3.3 | Example of a streaming application                                                                                                           | 46 |

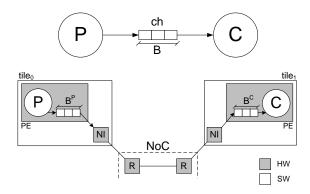

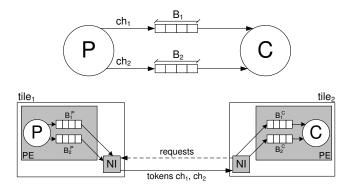

| 3.4 | Producer-consumer pair with FIFO buffer split over two tiles                                                                                 | 47 |

| 3.5 | Request-driven inter-tile communication implementation                                                                                       | 49 |

| 3.6 | Pseudocode of the R approach                                                                                                                 | 49 |

| 3.7 | Overview of the STM architecture                                                                                                             | 57 |

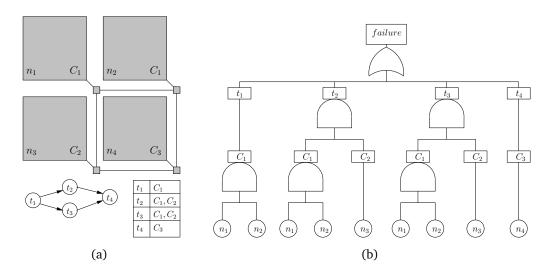

| 4.1 | A $2 \times 2$ NoC, a simple task graph and a table listing tasks and the core types capable of executing the tasks (a), and the correspond- |    |

|     | ing fault tree (b)                                                                                                                           | 76 |

| 4.2 | Example of a KPN application composed of three software tasks (a), and a mapping of the example application using the TMR                    |    |

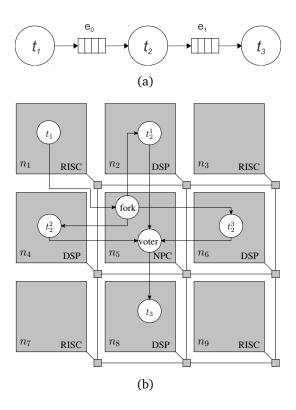

|     | pattern onto a 3 × 3 NoC (b)                                                                                                                 | 77 |

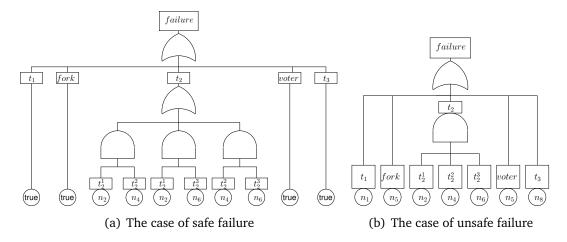

| 4.3 | The fault trees corresponding to the mapping in figure 4.2(b)                                                                                | 78 |

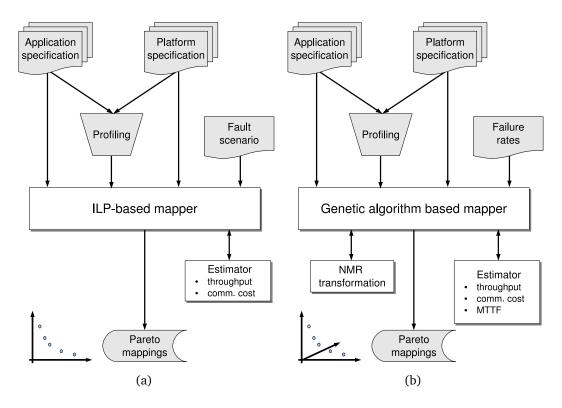

| 4.4 | Tool flow for evaluating the fault-aware online task remapping with the ILP-based mapper (a) and the reliability estimation with             |    |

|     | the genetic algorithm based mapper (b)                                                                                                       | 81 |

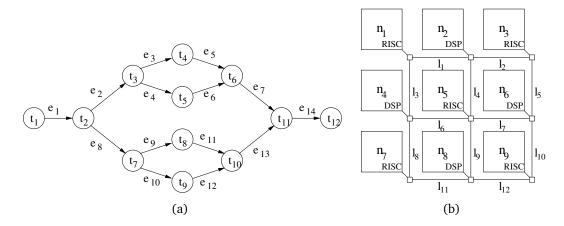

| 4.5 | An MPEG-2 encoder task graph with 12 tasks (a), and a $3 \times 3$                                                                           |    |

|     | mesh-based NoC with RISC and DSP processors (b)                                                                                              | 83 |

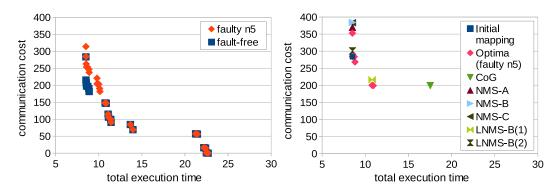

| 4.6 | Remapping results for the MPEG2 decoder case study on a $3 \times 3$                                                                         |    |

|     | heterogeneous platform with a faulty node $(n_5)$                                                                                            | 84 |

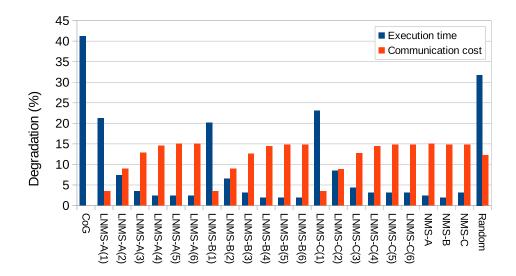

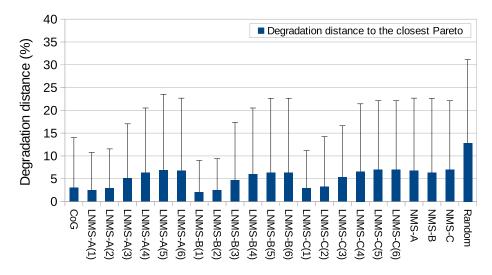

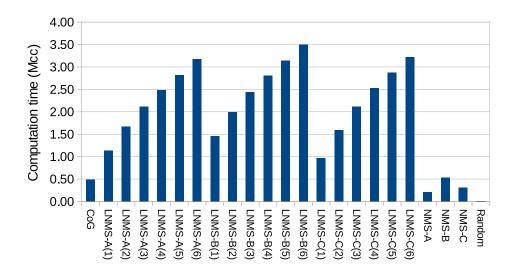

| 4.7 | Remapping results for 30 tasks on a 4 × 4 homogeneous platform                                                                               |    |

|     | averaged over 13 initial mappings and 16 single fault scenarios .                                                                            | 86 |

xvi Figures

| 4.8  | Computation times of the heuristics on the Microblaze processor .       | 88  |

|------|-------------------------------------------------------------------------|-----|

| 4.9  | PPN specification of the M-JPEG encoder                                 | 89  |

| 4.10 | Simplified PPN specification of the H.264 decoder                       | 90  |

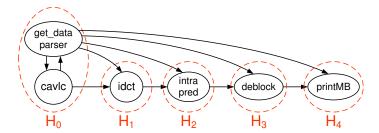

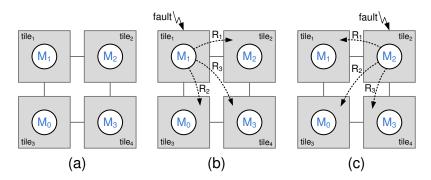

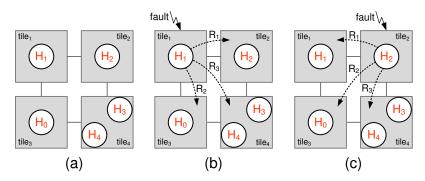

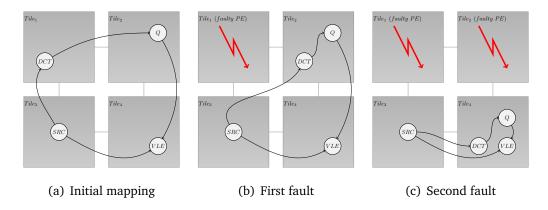

|      | Initial mapping and the two single fault scenarios showing all pos-     |     |

|      | sible remappings                                                        | 91  |

| 4.12 | Comparison of measured and calculated performance degradation           |     |

|      | of all possible remappings when $n_1$ is faulty (a) and when $n_2$ is   |     |

|      | faulty (b) as shown in figures 4.11(b) and 4.11(c), respectively.       | 92  |

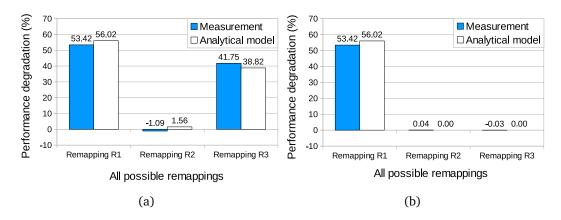

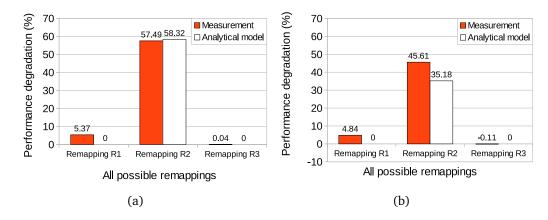

| 4.13 | Initial mapping and the two single fault scenarios showing all pos-     |     |

|      | sible remappings                                                        | 93  |

| 4.14 | Comparison of measured and calculated performance degradation           |     |

|      | of all possible remappings when $n_1$ is faulty (a) and $n_2$ is faulty |     |

|      | (b) as shown in figures 4.13(b) and 4.13(c)                             | 93  |

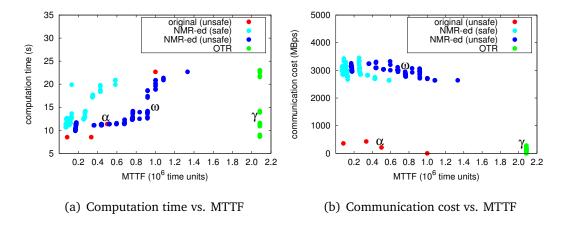

| 4.15 | Comparison of the Pareto points of original and NMR-ed task graphs      |     |

|      | as well as the OTR design points                                        | 95  |

|      |                                                                         |     |

| 5.1  | e e e e e e e e e e e e e e e e e e e                                   | 107 |

| 5.2  | č č                                                                     | 109 |

| 5.3  | · · · · · · · · · · · · · · · · · · ·                                   | 114 |

| 5.4  | * * *                                                                   | 114 |

| 5.5  | <u>.</u>                                                                | 115 |

| 5.6  | •                                                                       | 115 |

| 5.7  | Performance overhead with respect to the duration of the self-          |     |

|      |                                                                         | 116 |

| 5.8  | Area occupation overhead in comparison to the baseline network          |     |

|      | adapter due to the support for system adaptivity and fault-tolerance?   | 117 |

| 5.9  | Critical path length overhead related with support for system adap-     |     |

|      | •                                                                       | 118 |

| 5.10 | Area occupation overhead in comparison to the baseline tile archi-      |     |

|      | tecture due to the support for system adaptivity and fault-tolerance    |     |

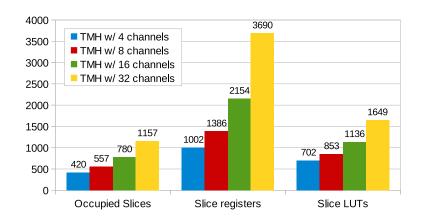

| 5.11 | TMH area for varying number of supported channels                       | 119 |

|      | ·                                                                       | 121 |

|      | •                                                                       | 122 |

| 5.14 | Performance overhead with respect to the period of the self-testing     |     |

|      | routine (a) and the duration of the self-testing routine (b) 1          | 122 |

| 6.1  | Self-adaptation approaches for PPN applications on NoC                  | 129 |

| 6.2  |                                                                         | 130 |

| 6.3  | A monitoring task                                                       |     |

| 0.5  | momonity ask                                                            | rof |

xvii Figures

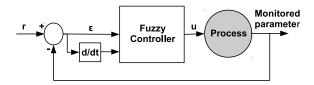

| 6.4  | A simple fuzzy control based system                                        | 133 |

|------|----------------------------------------------------------------------------|-----|

| 6.5  | A monitoring task in MCA-EI scheme                                         | 138 |

| 6.6  | Adaptation interrupt handler in MCA-EI scheme                              | 139 |

| 6.7  | An adaptive task in MCA-EI scheme                                          | 140 |

| 6.8  | Self-adaptive M-JPEG encoders in MCA-EB and MCA-EI (refer to               |     |

|      | the legend of figure 6.1(d))                                               | 141 |

| 6.9  | Impact of adaptation parameters on goal metrics                            | 144 |

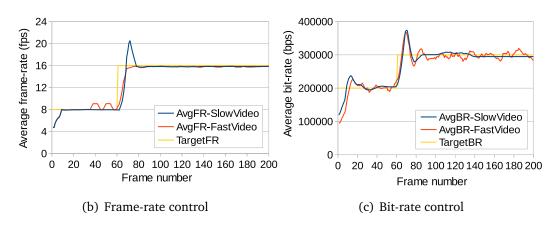

| 6.10 | Results for initial $FR = 8$ fps, initial $BR = 200000$ bps and final $FR$ |     |

|      | = 16 fps, final BR = 300000 bps                                            | 147 |

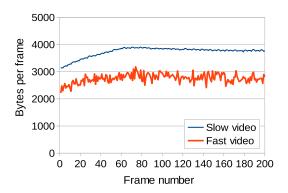

| 6.11 | Results for bit-rate and frame-rate control of slow and fast videos        | 149 |

| 6.12 | Cost of adaptation in terms of reduction in FR (left) and BR (right)       | 150 |

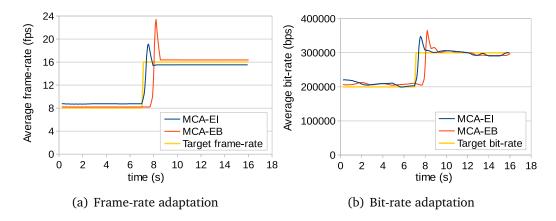

| 6.13 | Results for initial $FR = 8$ fps, initial $BR = 200000$ bps and final $FR$ |     |

|      | = 16 fps, final BR = 300000 bps                                            | 151 |

| 6.14 | Effect of controller workload on adaptation overhead                       | 152 |

xviii Figures

### **Tables**

| 1.1 | Addressed self-adaptation problems                                    | 11  |

|-----|-----------------------------------------------------------------------|-----|

| 4.1 | Table of notations                                                    | 63  |

| 4.2 | Execution times (in seconds) of tasks on the available core types     |     |

|     | $(T_{cap}^{CT})$                                                      | 83  |

| 4.3 | Bandwidth demands (in MBps) of edges $(d)$                            | 84  |

| 4.4 | Degradation achieved by Pareto-optimal limited remappings for         |     |

|     | faulty $n_5$ scenario                                                 | 85  |

| 4.5 | Degradation achieved by proposed heuristics for faulty $n_5$ scenario | 85  |

| 4.6 | Execution times of M-JPEG processes                                   | 89  |

| 4.7 | Execution times of H.264 processes                                    | 90  |

| 4.8 | Computation times of remapping heuristics                             | 93  |

| 5.1 | M-JPEG fault scenarios                                                | 120 |

| 5.2 | H-264 fault scenarios                                                 | 120 |

| 5.3 | Area synthesis results of the TMH and STM modules as well as the      |     |

|     | base tile architecture                                                | 123 |

| 6.1 | Error ranges for the fuzzy controller                                 | 134 |

| 6.2 | Delta-error ranges for the fuzzy controller                           | 134 |

| 6.3 | Control levels and their meanings                                     | 135 |

| 6.4 | Adaptation control algorithm                                          | 136 |

| 6.5 | Settling widths and error thresholds for controllers (Fraction pa-    |     |

|     | rameters shown in italic)                                             | 142 |

| 6.6 | Two step DSE for adaptation control. Selected controller configu-     |     |

|     | ration is shown in the last column                                    | 146 |

| 6.7 | Comparison of adaptation quality for fast and slow videos             | 148 |

| 6.8 | 1                                                                     | 150 |

| 6.9 | Comparison of control quality for MCA-EI and MCA-EB                   | 152 |

xx Tables

### **List of Abbreviations**

API application programming interface.

**ASIP** Application Specific Instruction Processor.

BDD binary decision diagram.

BER backward error recovery.

**BIST** built-in self-test.

BR bit-rate.

**CMOS** complementary metal-oxide-semiconductor.

**CoG** Center of Gravity.

**CPU** central processing unit.

CRC cyclic redundancy check.

**CRR** checkpointing-and-rollback recovery.

DMA direct memory access.

DMR double modular redundancy.

DSE design space exploration.

**DSP** digital signal processor.

**EM** electro-migration.

FER forward error recovery.

**FIFO** first-in first-out.

FPGA Field-Programmable Gate Array.

FR frame-rate.

GPU graphics processing unit.

HCI hot carrier injection.

HW hardware.

ILP integer linear programming.

IP intellectual property.

JPEG Joint Photographic Experts Group.

KPN Kahn Process Networks.

LNMS Localized NMS.

M-JPEG Motion JPEG.

MCA monitor-controller-adapter.

MCA-EB event-based MCA using blocking channels.

MCA-EI event-based MCA using interrupts.

MoC model of computation.

MPEG Moving Picture Experts Group.

MPH DMA message-passing handler.

MPI Message Passing Interface.

MPSoC Multiprocessor System-on-Chip.

MTOS multi-threaded operating system.

MTTF mean-time-to-failure.

**NA** Network Adapter.

NBTI negative bias temperature instability.

NI network interface.

NMR N-modular redundancy.

NMS nonidentical multiprocessor scheduling.

**NoC** Network-on-Chip.

NORMA no-remote memory access.

NUMA non-uniform memory access.

**OS** operating system.

**OTR** fault-aware online task remapping.

**PE** processing element.

PPN Polyhedral Process Networks.

**QoS** quality of service.

RFR roll-forward recovery.

**RISC** Reduced Instruction Set Computing.

RM run-time manager.

RTE run-time environment.

**SDC** silent data corruption.

SDF Synchronous Data Flow.

**SM** stress migration.

**SoC** System-on-Chip.

**STM** Self-testing Module.

SW software.

$\ensuremath{\textbf{TDDB}}$  time dependent dielectric breakdown.

TMH task migration hardware.

TMR triple modular redundancy.

### Chapter 1

### Introduction

Guided by Moore's Law, technology scaling accompanied with higher operating frequencies has been the driving force behind delivering higher performance computing systems at lower costs. However the past decade has witnessed the rise of some barriers, namely the power wall, the memory wall and the reliability wall, which threaten the rule of Moore's Law in the semiconductor industry [Borkar et al., 2007]. High performance embedded systems are also affected by these barriers as power consumption and reliability are even more important concerns for such systems. Power and memory wall have been regarded as more imminent threats and new architectural design trends have emerged in an effort to avert them.

Thanks to the advances in micro- and nano-electronic technologies, enabling the integration of billions of transistors in the same on-chip die, the next generation of embedded platforms will be composed of a high number of heterogeneous processing and storage elements; performances are increased by task-level parallelism, distributing the tasks on a multiplicity of (relatively simple) processors rather than by going for single, highly complex units running at very high frequency.

The initial trend was designing multi-core chips, usually in the form of a symmetric Multiprocessor System-on-Chip (MPSoC), with a limited number of nodes consisting of CPU and L1 cache interconnected by simple bus connections and capable in turn of becoming nodes in larger multiprocessors. However, as the number of components in these systems increases, communication becomes a bottleneck and it hinders the predictability of the metrics of the final system.

Networks-on-Chip (NoCs) [Dally and Towles, 2001] appeared as a design paradigm allowing to overcome the efficiency and technology problems related to traditional solutions for inter-core communication. NoCs, among the other

advantages, improve scalability, available bandwidth, and power efficiency of complex MPSoCs, usually by implementing a packet-switched communication among the cores [Benini and De Micheli, 2002]. The 48-core *Single Cloud Computer* [Howard et al., 2011] and the 80-core *Teraflops Research Chip* [Vangal et al., 2008] processors from Intel; the 64-core *Tile64* processor [Wentzlaff et al., 2007] from Tilera; and the 64-core *Epiphany* [Adapteva Inc., 2014] processor are few of the commercial NoC-based platforms exemplifying these trends.

Memory organization is also an important design choice. Shared memory architectures are less scalable than distributed-memory solutions. Although NoC-based platforms can support shared memory access, memory coherence protocols induce an overhead in the communication network rendering the gain from additional cores useless. There are two design paradigms for non-symmetric memory organization in NoCs: non-uniform memory access (NUMA) and no-remote memory access (NORMA). In NUMA, all cores share one logical address space, but this address space is physically partitioned so that each node has a local segment of the memory space; communication takes place simply by accessing shared memory locations. In NORMA, each core has its private local memory: this solution is suited for programming models based on message-passing [Carara et al., 2007].

This thesis takes on the challenges described in the next section in accordance with the aforementioned trends.

#### 1.1 Motivation

#### 1.1.1 The need for self-adaptation

Embedded systems are often subject to stringent non-functional goals such as high computational performance, low power consumption, restrictions on memory dimensions, low chip area and high dependability. Goals are specified by programmers or users by stating that a certain metric should be above or below a threshold value, or that it should be minimized or maximized. In classical design space exploration (DSE), systems are designed by evaluating the design alternatives in terms of the relevant metrics and by picking one that satisfies the goals, possibly with a trade-off between conflicting objectives.

Satisfying the non-functional requirements imposed by the application designer on systems with increasing complexity of the underlying architectures is a fundamental challenge. Design activities are mainly hindered by the difficulty in analyzing and estimating the performance metrics of the system. Design time

choices may be less than satisfactory when confronted with run-time processing, due to the complexity of the design space. Moreover, some run-time factors, which are only known during operation, may cause a performance that is different than the expected one. Variability issues of transistors at deep-submicron scale due to both manufacturing and aging effects show major performance and power consumption variability in the final system and thus they can no longer be overlooked [Borkar et al., 2007]. In order to deal with this problem, designers more and more often resort to self-adaptation based techniques [Kramer and Magee, 2007; Józwiak, 2006]. Self-adaptivity is the ability of the system to adapt itself dynamically to achieve its goals. As the complexity of the components increases and their integration becomes difficult, some of the decisions that are taken at design time are deferred to run-time. From that perspective, one can view self-adaptation as the ability of the system to switch at run-time from one design point to another in the design space with the help of a run-time design space exploration logic.

Self-adaptive systems are able to react when the actual operating conditions of the system differ from the design-time assumptions such as the workload, the internal and external conditions and the non-functional goals. For example, a portable device may be frequently moved from an office environment (where power and network plugs are available) to an external environment (where the device can only be battery operated and the network may be available in different wired or wireless forms). In this case the behavior of the system needs to be adapted to the new conditions (e.g., to reduce power consumption). Again, a video encoding application running on such a device may be required to work at higher resolution (i.e. different workload), at higher frame rate (i.e. different goal) and alongside a new application launched on the system (i.e. different internal condition).

There are certain challenges to be tackled when designing self-adaptive systems. A general concern when making the system monitorable and adaptable is the overhead introduced in the metrics of interest such as time, area and power. The benefits of adaptation can easily be offset by a large overhead. There are two types of overhead. The first type, which can be called *steady state overhead*, is the overhead experienced simply due to the additional hardware or software for enabling monitoring and adaptation capabilities. It is present even when there are no ongoing adaptations. This overhead should be minimized because it is afforded at all times. The second type, which can be called *transient overhead*, is the overhead experienced while an adaptation is taking place. The major sources of this overhead are the adaptation algorithm of the controller and the execution of an adaptation. If the system is expected to have frequent adaptations, then

care must be taken to minimize this type of overhead.

Separation of concerns is a key feature for self-adaptive systems. However the realization of this principle is quite challenging for several reasons. It emphasizes that the application programmer should be involved as little as possible in making the system self-adaptive. Although it may be possible to realize this for adaptations at the run-time environment and hardware levels because of the clear interface between the application and the execution platform, it is a more difficult task for application level adaptations. Intrinsic application knowledge by the application programmer is required in order to expose the feasible adaptations in the application. Automatic inference of such adaptations would be very difficult, if possible at all. Depending on the adaptation goal, another difficulty is in the inference of what to monitor and how to monitor it without involving the programmer. There is a semantic gap to be bridged between the given goal and the application. Monitoring involves choosing the correct program variables and operating on them in order to calculate the actual metric that corresponds to the goal. Another issue with the separation of concerns principle is that it is likely to conflict with the low overhead goal mentioned previously. Decreasing the amount of load on the programmer would lead to increasing the amount of work that the self-adaptation logic has to do, thus leading to greater overhead due its complexity. Last but not least, the behaviour of the adaptation controller is application-dependent. Machine learning algorithms can be used to obtain the application knowledge, particularly the relation between the goal and the adaptations, but this would result in a complex control logic with a larger overhead. Alternatively, the required application knowledge can be provided to the controller by the application programmer.

Another fundamental challenge for system-wide self-adaptivity is presented by the management of the adaptations. The systems are usually faced with multiple goals to be satisfied at run-time such as a desired throughput, low power consumption, high dependability. Satisfying all the goals by controlling various possible adaptation options is a difficult task. Changing the set of goal types would require a complete or partial re-design of the controller. Possible solutions to solve this problem are automated controller synthesis or designing generic controllers.

#### 1.1.2 The need for fault tolerance

Over the years semiconductor industry has benefited greatly from the improvements in process technologies that enabled scaling down of CMOS transistors. Smaller transistors led to better circuit performance due to higher frequencies.

As the area of the chip got smaller, fabrication costs per chip were also reduced. Moreover, the ability to pack more transistors in a smaller area enabled the integration of many more functions in a chip, leading also to performance improvements. These trends, referred to as Moore's Law, are threatened by power and reliability concerns in the deep sub-micron scale. As highlighted by the International Technology Roadmap for Semiconductors [ITRS, 2009], these concerns have to be addressed to continue harvesting the benefits of *More-Moore*.

A hardware fault is caused by an underlying physical defect in hardware. An error is the external manifestation of a fault. Regarding their duration, hardware faults have been classified as permanent (hard), transient (soft) and intermittent [Koren and Krishna, 2007]. Permanent faults cause persistent component malfunction, while transient faults last only for some time. Intermittent faults are those that make a component oscillate permanently between malfunctioning and correct functioning. We limit the scope of this thesis to permanent faults as they determine the lifetime reliability of a system. For systems that are prone to radiation effects, which are the major cause of transient errors, techniques presented in this thesis should be accompanied with techniques that handle such errors.

Permanent faults can be extrinsic or intrinsic. The former are caused by manufacturing defects and can be mostly detected by post-manufacturing tests such as burn-in. The latter are caused by wear-out and manifest during operation. The failure rate of electronic systems usually adhere to the Weibull distribution, also known as the bathtub curve [Koren and Krishna, 2007]. Extrinsic faults exhibit as high infant mortality rate, while intrinsic faults account for the increasing failure rates in the wear-out phase. In between the two lies the useful lifetime phase with a lower constant failure rate.

Considering an individual transistor, the fundamental mechanisms leading to intrinsic permanent failures are electro-migration (EM), stress migration (SM), time dependent dielectric breakdown (TDDB), negative bias temperature instability (NBTI) and hot carrier injection (HCI) [Renesas, 2013]. EM is caused by the movement of metal atoms in the interconnect with the momenta of the electrons, leading eventually to an open or a short circuit. SM stems from the thermal stress due to different thermal expansion coefficients of the interconnect metal and the underlying film, leading possibly to a rupture in the interconnect. In TDDB, a conducting path gradually forms between the gate electrode and the silicon substrate due to the traps created inside the dielectric by the electric field between the gate and the substrate. NBTI is caused by the formation of positive charge inside the dielectric due to high negative bias at the gate (with respect to source and drain) and high temperature, leading to the degradation of PMOS transistor's threshold voltage and thus performance. Similarly, NMOS transis-

tors suffer PBTI. HCI is caused by high electric field around the drain due to high supply voltage, leading to the injection of carriers (electrons or holes) inside the dielectric, thus degrading transistor's performance.

These failure mechanisms are affected strongly by the feature sizes of the transistor and in particular by the electric field at the gate, the temperature and the supply voltage. Although ideal scaling rules of transistors aim at keeping the electric field constant, in practice the supply voltage has been kept above ideally scaled values for performance concerns. This has two implications, firstly, the power densities have been increasing, and secondly, the ratio of leakage power with respect to switching power has been increasing with each technology node. As a result, chip temperatures have also increased, deteriorating the lifetime reliability of transistors [Borkar, 2005].

Moving from transistor to chip level, as the probabilty of failure in individual transistors increases, the probabilty of a failing transistor in a chip with billions of them becomes a more threatening issue for the lifetime of the system. While memories are often protected with error detecting and correcting codes, components consisting majorly of logic such as the processing elements (PEs) are more vulnerable to hard failures. Srinivasan [2006] estimates a five-fold decrease in a processor's lifetime as it is scaled from 180nm to 65 nm technology and expects this decrease to occur at higher rates with further scaling.

Another concern calling for fault tolerance against operational faults is due to the limitations of post-manufacturing tests to catch early defects. In particular, the effectiveness of the burn-in process, which subjects the final product to testing at higher voltages and higher temperatures to accelarate aging, is hampered by device scaling due to the prohibitive (exponential) increases in the gate leakage [Borkar et al., 2007] and by decreases in supply voltages (resulting in exponentially longer burn-in times) [ITRS, 2009].

As a result, designers are faced with the challenge of handling faults at runtime by detection, isolation and recovery without introducing prohibitive performance and cost overheads. Although reliability improvements in process technologies are continuously sought, a permanent solution to this problem requires new design techniques to be developed. Constraints presented by embedded systems design (e.g., low cost and low power consumption) make traditional approaches involving massive redundancy hardly adoptable. Moreover assessing the reliability of the system, consisting of the application and the platform it runs on, only after the platform is available puts the product development at risk with regard to time-to-market requirements. Design flows that encompass a loop in order to incorporate a posteriori measures for meeting reliability constraints are rendered obsolete. Therefore design techniques embracing con-

tinued availability in the presence of faults must be embedded into the normal design flow. This brings in a new challenge on the part of the designers of these techniques. In order to develop such techniques, low level fault models strongly tied to the technology should be abstracted in the form of functional-level error models. Since the exploitation of knowledge at higher levels of abstraction (e.g., regarding the application, the error or the system) creates a potential for developing fault tolerance techniques with lower performance and area costs; there has been a trend to move from physical and logical to micro-architectural, architectural and software-based solutions. In fact, these techniques employed at several levels should work hand in hand to guarantee reliable computation from unreliable components. This design paradigm which distributes the responsibility for tolerating errors, device variation and aging across the system stack is known as cross-layer resilient design [Mitra et al., 2010; Carter et al., 2010; DeHon et al., 2010]. By viewing fault tolerance as a self-adaptation aspect, in this thesis we adopt a cross-layer approach that aims at graceful performance degradation by addressing fault tolerance mostly at system-level, in particular by exploiting redundancy available in multi-core platforms. By system-level, we refer to techniques implemented in software both at application and run-time environment levels and not purely in hardware.

#### 1.2 Research framework

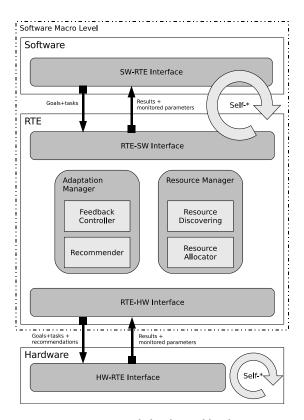

The work presented in this thesis has been carried out within two European projects. Initially it benefited from our partial involvement in the AETHER EU FP6 Project (No. IST-027611) - Self-Adaptive Embedded Technologies for Pervasive Computing Architectures. As it will be mentioned in section 2.1, the common design pattern for self-adaptivity is the monitor-controller-adapter (MCA) loop. Self-adaptive systems can be characterized with respect to what can be monitored, controlled and adapted. As a part of our work within the AETHER Project on modeling system-wide self-adaptivity in embedded systems, we proposed a generic model consisting of three levels, which are application, run-time environment (RTE) and hardware as shown in figure 1.1 [Derin et al., 2009]. In each of these levels, there are parameters to be monitored and adapted. To exemplify each level, at the application level, some application parameters or variant implementations of some functions can be adapted; some performance goals such as throughput and delay can be monitored. At the RTE level, the mapping of tasks onto the resources as well as the scheduling policy of tasks on a given resource can be adapted; resource utilization, goal achievements per application

Figure 1.1. Model of a self-adaptive system

can be monitored. At the hardware level, the clock frequency and voltage levels can be adapted; power consumption and temperature can be monitored. A goal is an expression containing boolean and arithmetic operators, which evaluates to true or false to denote whether the goal is satisfied or not. The variables in a goal expression come from the monitors. Controllers provide commands to the adaptors to change the system configuration. A goal is assigned to a controller at a specific level. For example, a performance goal for an application is associated with the application level, whereas a power consumption goal can be assigned to the RTE or hardware levels. Assigning the goals to the level where there are a relevant adaptor and monitor is a wise choice; otherwise, some overhead to monitor and/or adapt parameters of another level would be involved. Moreover, this is likely to violate the seperation of concerns principle.

Our AETHER work has also produced some ideas for enabling applicationlevel self-adaptation capabilities for process networks [Derin and Ferrante, 2009] and middleware support for Kahn Process Networks (KPN) on NoC-based platforms [Derin and Diken, 2010] with consideration of adaptability and fault-tolerance [Derin, Diken and Fiorin, 2011]. However, it is the MADNESS Project that allowed us to move from simulated systems to prototyped solutions.

Most of the work presented in this thesis has been done within the MAD-NESS EU FP7 Project (No. ICT-248424) – Methods for predictAble Design of heterogeneous Embedded Systems with adaptivity and reliability Support – in coordination with the project partners. Both reference architecture and benchmark application(s) were chosen in agreement with the whole collaboration.

The project aims at the definition of innovative system-level design methodologies for embedded MPSoCs, extending the classic concept of design space exploration in multi-application domains to cope with high heterogeneity, technology scaling and system reliability. The main goal of the project is to provide a framework able to guide designers and researchers to the optimal composition of embedded MPSoC architectures, according to the requirements and the features of a given target application field. The proposed strategies tackle the new challenges, related to both architecture and design methodologies, arising with the technology scaling, the system reliability and the ever-growing computational needs of modern applications.

#### 1.2.1 KPN and PPN as the model of computation

The design of embedded systems, unlike general computing systems, involve not only functional goals but also non-functional ones that dictate performance and/or resource usage goals. As a consequence, design flows entail the adoption of a model of computation (MoC). The behavioral specification of the system can be expressed with the given MoC. But, most importantly, the MoC enables the analyzability of the system with regard to the given non-functional goals. Depending on the target application domain, system-level synthesis approaches adopt a variety of MoCs based on finite state machines or process networks [Gerstlauer et al., 2009].

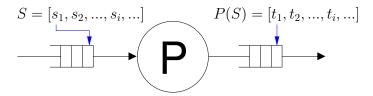

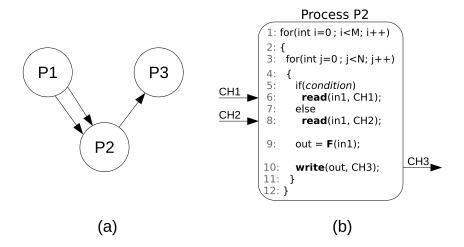

A fundamental design decision taken at the beginning of the MADNESS Project by the partners was the adoption of a streaming application model based on KPN [Kahn, 1974], in particular its variant named Polyhedral Process Networks (PPN). Although KPN was introduced by Kahn in 1974, it was only after year 2000 that it re-gained attention with the emergence of the increasingly parallel platforms needed by high performance embedded applications, which constitute a target domain for the MADNESS Project. KPN and PPN models are based on the idea of organizing an application into streams (*channels*) and computational blocks (interchangeably referred to as *tasks* or *processes*); channels represent the

flow of data, while tasks represent operations on a stream of data. Further background on KPN and PPN is provided in sections 2.3 and 2.4, respectively.

KPN and PPN present themselves as an acceptable trade-off point between abstraction level and efficiency versus flexibility and generality. The favorable features of KPN and PPN, which enable the work presented in this thesis, are discussed in the following.

*Generality:* It is capable of representing many signal and media processing applications, which occupy a large percentage of the consumer electronics in the market. Some KPN application examples that can be found in the literature are image/video processing (JPEG [de Kock, 2002], M-JPEG [Lieverse et al., 2001], MPEG-2 [van der Wolf et al., 1999], H.264 [Zrida et al., 2008; Nikolov et al., 2009; Vrba et al., 2009], Sobel edge detection, 2D-DWT [Verdoolaege et al., 2007]), sound processing (ADPCM [Ceng et al., 2008]), telecommunication (GSM [Castrillon et al., 2010], software-defined radio [Castrillon et al., 2011]), security (AES [Vrba et al., 2009]) and scientific computation (QR decomposition [Stefanov et al., 2002]). It should further be noted that, a recent work by Thies and Amarasinghe [2010] has shown that most of the streaming applications can be specified using the Synchronous Data Flow (SDF) model [Lee and Messerschmitt, 1987a]. KPN and PPN models are more expressive than SDF, thus it can as well be used effectively to model all streaming applications that can be specified via SDF. Moreover, KPN can be used to express applications from other domains, thanks to its Turing-completeness, albeit they are likely to be less efficient.

Abstraction level: Being untimed MoCs based on asynchronous message passing, KPN and PPN guarantee functional correctness independent of timing. The programmer is not directly involved with concurrency management. KPN and PPN tasks can be implemented in any programming language. The only restriction imposed on the tasks is the communication interface consisting of the read and write operations. Most importantly, the performance of the system given the mapping of a KPN application on a platform is estimable with an analytical model. Moreover, in case of PPN, as the FIFOs are bounded, the memory requirement of the system is also estimable.

Efficiency: KPN and PPN enable the exploitation of the parallel processing power available on the NoC-based multiprocessor platforms. Organizing the computation as parallel tasks and overlaping the computation with communication using FIFOs allows an efficient implementation when combined also with a mapping exploration design phase. Since the communication between the tasks is exposed explicitly, it makes KPN and PPN very suitable for message-passing platforms such as the NoC-based multi-processor platforms with no remote mem-

ory access. This enables estimating the amount of communication in the system.

Flexibility: The techniques to be developed in order to address self-adaptation and fault-tolerance challenges depends on the adopted MoC. KPN/PPN makes it possible to adapt the application without excessive effort and overhead. A fundamental property which facilitates this is that KPN/PPN tasks do not require a global scheduler and can synchronize simply by blocking read operations. Such a flexibility enables remapping of tasks at run-time. Secondly PPN tasks have a special execution point (i.e., the beginning of their outmost loop bodies) where they posses a small state, thus enabling efficient remapping of the tasks onto new processing nodes.

## 1.3 Dissertation contributions

In the view of the aforementioned challenges, this thesis presents novel contributions for achieving fault-tolerant and self-adaptive applications which are modelled as process networks and run on top of NORMA-based NoC platforms.

The self-adaptation model provides a comprehensive basis for the work presented in this dissertation. The two concrete self-adaptation problems shown in table 1.1 are derived based on this model. Firstly, the fault tolerance goal at the RTE level is addressed by viewing the problem of fault tolerant execution of KPNs on NoCs as a self-adaptation problem. Fault detection corresponds to monitoring; the remapping decision (chapter 4) corresponds to the adaptation control; and the fault recovery via task migration (chapter 5) corresponds to the adapter. Secondly, quality goals at the application level are addressed by viewing the adaptation of the parameters of KPN tasks as a self-adaptation problem as described in chapter 6. The quality attributes that are defined in [Derin et al., 2009], namely control quality, steady-state overhead and separation of concerns, have been used as the assessment criteria for the presented solutions to these two self-adaptation problems.

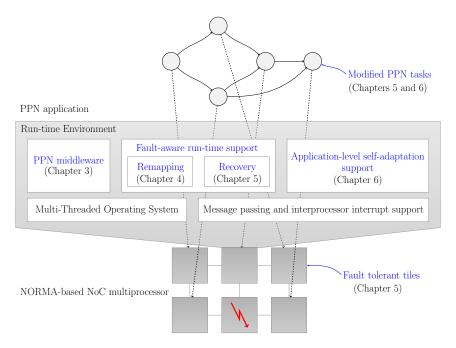

Figure 1.2 shows a pictorial view of the concrete self-adaptive and fault-tolerant system that has been realized in this thesis where the contributions are marked with their corresponding chapter numbers.

The main contributions of the dissertation are as follows:

• Fault-aware online task remapping (OTR): Firstly, we propose an integer linear programming (ILP) based method for finding the Pareto-optimal mappings and remappings of KPN applications onto NoC-based platforms with consideration of computation and communication objectives. Although optimal remappings can be computed offline for a given application and

| Problem           | Fault-aware              | Application-level self-adaptation |

|-------------------|--------------------------|-----------------------------------|

|                   | online remapping         | for quality management            |

| Goal space        | fault tolerance          | performance                       |

| Monitorable space | permanent faults in PEs  | throughput                        |

| Adaptation space  | task mapping             | task parameters                   |

| Controller        | remapping algorithms     | quality controller                |

| Control quality   | performance degradation, | mean absolute error,              |

|                   | fault recovery time      | rise/fall time                    |

| Other quality     | steady-state overhead,   | steady-state overhead,            |

| criteria          | separation of concerns   | separation of concerns            |

Table 1.1. Addressed self-adaptation problems

stored in system's memory to be used when a fault is encountered, it becomes inapplicable with increasing number of tasks and processing nodes, which often have limited memory resources. For this reason, we adopt an online approach and propose heuristics for the problem of remapping tasks when run-time faults are encountered. We assess the quality of the heuristics by comparing them with the optimal solutions found by the ILP-based method. We also evaluate the computation times of the heuristics on the actual platform.

We also present an analytical model for the calculation of the mean-time-to-failure (MTTF) as a reliability metric when running KPN applications on NoC-based platforms. We operate on an abstract, high-level model rather than on detailed lower-level solutions, thus achieving a model that remains valid for multiple underlying implementations. We investigate transformations of the KPN task graph that make it more reliable and allow fault detection and/or fault masking. We provide a comparison between the fault-aware online remapping technique and application-level N-modular redundancy in terms of their reliability and performance overhead.

• Recovery support in the fault-aware run-time environment (CRR and RFR): We realize the fault-aware online task remapping concept on a NoC-based platform in the form of a self-adaptive run-time environment consisting of a task-aware middleware, fault recovery support via task migration and a run-time manager. We propose roll-forward recovery (RFR) and checkpointing-and-rollback recovery (CRR) schemes. For each scheme, the recovery support involves modifications to the process template, run-time support in the form of interrupt handlers and addition of a task migration

Figure 1.2. Overview of the proposed self-adaptive and fault-tolerant system

hardware module to the tile architectural template. Both recovery schemes have been implemented and compared in terms of their overheads.

Application-level self-adaptation for quality management (MCA-EB and MCA-EI): We realize quality management support as a part of the selfadaptive run-time environment consisting of monitoring tasks, adaptable tasks and controller tasks based on fuzzy logic. Two schemes are proposed based on an MCA loop that interacts with the application, firstly, via blocking channel semantics, and secondly, via interrupting messages. The two schemes have been implemented and compared in terms of their overheads.

## 1.4 Organization of the dissertation

The remainder of this thesis is organized as follows:

Chapter 2 presents some background topics, in particular, regarding self-adaptive systems, MPSoC programming models, Kahn Process Networks and Polyhedral Process Networks. Then, an overview of the related work on each of the individual parts addressed in the dissertation is provided, in particular, regarding KPN frameworks in MPSoCs, mapping of applications onto NoCs, fault

tolerance in embedded systems with a focus on system-level approaches and finally application-level self-adaptation.

Chapter 3 presents firstly the preliminaries of this thesis by describing the baseline platform which forms the starting point of the implementation work. Then we present the developed middleware which enables the fault tolerance and self-adaptivity techniques that have been implemented in the following chapters. Lastly, the adopted fault tolerance approach is described at large.

Chapter 4 presents the fault-aware online task remapping approach. Firstly, the ILP formulation for the optimal solution of the mapping problem is described based on an analytical model for throughput and communication cost. Then it is extended for the remapping problem and a set of heuristics for online task remapping are explained. After that, we propose an analytical model for estimating the lifetime reliability of a system that adopts the fault-aware online task remapping technique. N-modular redundancy technique is also considered for comparison purposes. The chapter concludes with several case studies and results obtained both analytically and experimentally on the actual platform.

Chapter 5 presents the two techniques proposed for fault recovery based on fine-grained checkpointing-and-rollback and roll-forward. Each section details the required changes at the application, RTE and hardware layers. We present results obtained experimentally on the platform and compare the two techniques in terms of their overhead in time and area.

Chapter 6 presents the two proposed approaches for a self-adaptive framework with implementation details of monitoring, controlling and adaptive tasks. We give details on how a self-adaptive M-JPEG encoder case study is built using the two frameworks. Then we provide the results of the case study with a comparison of the two approaches in terms of the steady-state performance overhead and quality of the control.

Finally, chapter 7 concludes with a summary of achieved results and discusses possible extension points for future work.

# Chapter 2

# **Background and Related Work**

In the following sections, firstly, we provide general background on self-adaptive systems in section 2.1. Then, some background information about MPSoC programming models is given in section 2.2. The two models of computation of interest to us, namely KPN and PPN, are described in section 2.3 and 2.4, respectively. Previous work on KPN realizations in MPSoCs is discussed in section 2.5. Mapping of applications onto NoC platforms is overviewed in section 2.6 followed by task migration in section 2.7. Then, background information on fault tolerance is given together with the related work on fault tolerance and lifetime reliability approaches in embedded systems in section 2.8. The chapter ends with the related work on application-level self-adaptation for quality management in section 2.9.

## 2.1 Self-adaptive systems

As the most prevalent technique for self-adaptation, we see the use of the monitor-control-adapt paradigm, also referred to as the autonomic control loop, the monitor-analyze-plan-execute loop or the monitor-analyze-decide-act loop [Dobson et al., 2010]. The main idea is monitoring internal and/or external conditions and adapting the system according to a control logic in order to satisfy the goals. In an effort to classify the existing solutions, we identify four main design decisions:

- *Adaptation coverage* is defined by the parts of the system affected by adaptations. It may consist of hardware, software, part of a distributed system (through adaptive middleware) or any combination of them.

- *Separation of concerns* is a design principle that decouples the functionality of the system from the implementation of its self-adaptation capability.

- Adaptation management is the decision making process on the evolution of the system, in other words, the adaptation control logic.

- Adaptation requirements specification is the form of describing the non-functional requirements of the system.

In the remaining part of this section we provide some examples of related work on self-adaptivity, classified according to their most prominent characteristics in the view of the above-listed criteria. A more complete list of related work on self-adaptive systems can be found in [Salehie and Tahvildari, 2009; Cheng et al., 2009; Lemos et al., 2013]. Similar concepts has been studied also under other research areas such as autonomic computing [Huebscher and McCann, 2008] or organic computing (a term coined by the German Organic Computing Initiative) [Schmeck, 2005].

## 2.1.1 Adaptation coverage

A number of earlier studies address self-adaptivity in software; the simplest approach adopted is to manage adaptation in the application code. Although this approach enables the development of ad hoc solutions for specific adaptation problems, it is clearly not flexible enough to support a wide range of adaptations. The use of an architecture-based approach eases self-adaptivity: the system is viewed as a composition of concurrent components interconnected by connectors. A comprehensive adaptation methodology is presented in [Oreizy et al., 1999]. The authors propose an evolution and adaptation management infrastructure. The evolution management process adapts the architecture and the topology of the components and of the system; the adaptation management process gathers information from the operating environment, evaluates the observations with respect to the system requirements, plans and deploys adaptation changes. Moreover the need of composable components is emphasized. Another work describing a component-based architectural approach is presented in [Garlan et al., 2004]. The authors propose a framework that is both reusable, to cope with a large set of systems, and that supports mechanisms to specialize the infrastructure for specific cases. To achieve such objectives, the framework is divided into two logical parts: an adaptation infrastructure and a system specific adaptation model. The former provides common functionality that is reusable across different self-adaptive systems; the latter is specific to a certain system and it is used to tailor the entire framework for it. Similarly, Geihs et al. [2009] propose a comprehensive solution for the development and operation of contextaware, self-adaptive applications. The main contributions of this work are (a) a sophisticated middleware that supports the dynamic adaptation of component-based applications, and (b) an innovative model-driven development methodology based on abstract adaptation models and corresponding model-to-code transformations. In [Balasubramaniam et al., 2004] an architecture description language named ArchWare is modified to support self-adaptation. Feedback obtained by means of software probes is used to control software self-adaptations.

A formal approach to the design of adaptive software is introduced in [Zhang and Cheng, 2006]. In particular, the adaptation is conceived as a state transition from a source program to a target program inside a suitable set of adaptation states. Each adaptive software is represented by a state machine, where each state exhibits a different behavior and operates in a certain domain. To guarantee system integrity and consistency, local and global properties (requirements, constraints, and invariants) that should be satisfied by an adaptive program for every state change are introduced.

In [Gjørven et al., 2006] a *mirror-based reflection* approach for self-adaptivity is proposed. By definition, a reflective system is able to perform computations about itself; moreover, it provides introspection and control through a reflective interface. By applying this reflective mechanism to software components, the middleware can perform self-adaptation by using the reflective interface of each component. Adaptation behavior, architecture and implementation of a component can be specialized to fit a specific context by annotating each implementation with quality of service metrics. Therefore, the middleware uses such quality of service metrics to trigger the adaptation of components.

Some studies related to hardware self-adaptation have also been proposed. Self-adaptation at the hardware level improves some quality metrics of the system without requiring any changes in the software, that is, the hardware is adapted in conformance to the HW-SW interface (e.g., instruction-set architecture). In [Casas et al., 2007] a self-adaptive hardware architecture is presented; this architecture provides self-configuration, self-repair and/or fault tolerance capabilities by means of self-placement and self-routing. In [Bauer et al., 2007] a self-adaptive embedded processor is described. This processor is able to deploy different special instructions at run-time; the decision on which special instructions to deploy and when, is based on their monitored usage. A compile-time analysis of the applications is performed to reduce run-time overhead: the information extracted from this analysis is used to forecast the kind of instructions that will be used by the applications in the immediate future. Thus, self-adaptation can happen without introducing delays in the computation.

## 2.1.2 Separation of concerns

Separation of concerns between the regular system functionality and the adaptation processes is about putting different concerns into different components that will address them independently; this approach, even though not essential for self-adaptivity, is very important as it offers benefits in terms of generality, level of abstraction, integrated approach, and scalability. In [Kramer and Magee, 2007] a vision of architecture-based self-adaptation is provided and a reference software architecture is proposed.

In [Karsai et al., 2001] another architecture for software self-adaptivity is presented; one of its main goals is separation of concerns. Thus, a ground-level that includes baseline processing and a supervisory-level that is responsible for adaptation and reconfiguration are considered. The former provides components that are highly optimized for specific situations; the latter select the optimal components for the different situations. The adoption of the supervisory-level enables the system to provide flexibility and robustness. [Schantz et al., 2006] implements a quality of service (QoS) management framework in a distributed system where adaptation strategies are separated from the core functionality by means of aspect languages and an encapsulation model for packaging adaptive behaviors. A standardized way to manage self-adaptivity at application level is provided in [David and Ledoux, 2003], which proposes separation of concerns between adaptation management and system functionalities. Self-adaptivity is obtained by applying a set of adaptation policies on software components, while these policies are triggered by certain configurable system events. Possible adaptations for component behavior and application parameters are also discussed. Unfortunately, the authors do not discuss if and how a general goal is achieved.

## 2.1.3 Adaptation management

Most approaches proposed in the literature use a centralized controller for self-adaptation. For example, [Neema and Lédeczi, 2001] proposes a centralized controller based on constraint-guided DSE. The proposed approach is to use models to represent the different points in the design space of the application. The design space is composed of different software component alternatives. The basic idea is to create multiple-aspect models of the design points at design time. These models, along with system constraints, are then embedded into the run-time system and used for self-adaptivity decisions. Each constraint can be associated with one or more values that are continuously measured at run-time. Whenever one of these values crosses the threshold associated with it, the controller is triggered

and the constrained DSE starts.

A different approach is to use decentralized controllers instead of a centralized one. This idea is mentioned in [Vaughan and Munro, 2000]; its main goal is to propose a software architecture that enables applications to be self-tuning and persistent. The work relies on strictly defined and controlled layering of policies and mechanisms, and on the complete control of all layers. Layer coordination is also utilized to obtain a stable behavior of the software. In [Derin et al., 2009], we adopted a similar approach for designing adaptation controllers for multiple goals. We showed (by means of a high level simulation of a self-adaptive system in SystemC) that two independent controllers that are assigned different types of goals may lead to non-converging adaptations. The system is prone to such situations especially when the control decisions affect the monitored parameters of other controllers. We proposed a recommender module that coordinates the two controllers such that both goals are achieved. In our solution, the controller at the higher level recommends to the lower level controller to take a non-greedy decision. [Schantz et al., 2006] uses a mix of centralized and localized QoS management in a distributed real-time system setting. Central control drives the QoS management via policies throughout the network whereas local control is guided by the contract attached to the network component.

## 2.1.4 Adaptation requirements specification

Adaptation requirements have been specified differently in various early work. In [Neema and Lédeczi, 2001] they are specified as constraints by Object Constraint Language (OCL); in [Schantz et al., 2006] they are expressed as policies via rule-based contracts. In [Hawthorne and Perry, 2004] adaptation requirements are defined as constraints in a custom requirement description language (RDL). In [Brown et al., 2006] the authors introduce a method to specify adaptation requirements by means of goals. Goals are represented by using a graphical language named KAOS; by using this language a full goal-oriented specification of an adaptive system can be drawn.

## 2.2 MPSoC programming models

An MPSoC-based system is fundamentally composed of a hardware architecture consisting of a set of processing, storage, communication elements which are put together on the same chip, and of the software running on such architecture so as to carry out a function at the same time satisfying some stringent design goals