## **COPYRIGHT AND CITATION CONSIDERATIONS FOR THIS THESIS/ DISSERTATION**

- Attribution You must give appropriate credit, provide a link to the license, and indicate if changes were made. You may do so in any reasonable manner, but not in any way that suggests the licensor endorses you or your use.

- NonCommercial You may not use the material for commercial purposes.

- ShareAlike If you remix, transform, or build upon the material, you must distribute your contributions under the same license as the original.

#### How to cite this thesis

Surname, Initial(s). (2012) Title of the thesis or dissertation. PhD. (Chemistry)/ M.Sc. (Physics)/ M.A. (Philosophy)/M.Com. (Finance) etc. [Unpublished]: <u>University of Johannesburg.</u> Retrieved from: <u>https://ujdigispace.uj.ac.za</u> (Accessed: Date).

## ELECTROMAGNETIC INTERFERENCE IN BALANCED CONVERTERS

By

## **STEVEN TREFOR BURFORD**

## DISSERTATION

submitted in fulfilment of the requirements for the degree

## **MAGISTER INGENERIAE**

# IN ELECTRICAL AND ELECTRONIC ENGINEERING SCIENCE

in the

**Faculty of Engineering**

at the

**UNIVERSITY OF JOHANNESBURG**

STUDY SUPERVISOR: Dr. D.C. Pentz

**CO-STUDY SUPERVISOR: Dr. A.S. de Beer**

2014

# **Anti-Plagiarism Declaration**

Full Name: Steven Trefor Burford

Student Number: 920309498

- I understand fully what plagiarism is and am aware of the department and universities policy in regard to this.

- I understand that plagiarism is wrong.

- Where the work of other people has been used, the work's author has been acknowledged and referenced.

- I declare that the content of this document is my own original work.

- No other person has copied this document (to my knowledge) with the intention of passing it off as his own work.

Signature

Date

## ABSTRACT

In this dissertation, an investigation into reducing Electromagnetic Interference (EMI) through design is presented. Root generation mechanisms of Electromagnetic Interference are often neglected during the design process and later treated symptomatically. Mitigation of Electromagnetic Interference at source often reduces cost and physical size of electronics. This dissertation demonstrates the process and results by which schematic balance mitigates EMI. In addition, the introduction of Geometric Balance and physically designing circuits to be Geometrically Symmetrical are presented and tested to determine whether the design produces mitigating EMI results. Multiple Printed Circuit Boards (PCB's) were developed and tested against each other to demonstrate schematic balance and other EMI generation mechanisms. The final PCB was designed to be Geometrically Symmetrical and the test results compared. The results illustrate the varying performance of each PCB due to their differing design. The Geometrically Symmetrical PCB presented the best results due to various improvements which include physical layout size and semiconductor placement. An additional important phenomenon discovered was the amount of EMI generated during MOSFET Driver operation. This contributed to a significant amount of EMI during the noload phase of testing.

# **TABLE OF CONTENTS**

| 1 IN | NTR | ROD  | UCTION AND PROBLEM STATEMENT1-                                        | 1  |

|------|-----|------|-----------------------------------------------------------------------|----|

| 1    | .1  | Inte | RODUCTION1-                                                           | -1 |

| 1    | .2  | Sco  | РЕ1-                                                                  | -2 |

| 1    | .3  | Doc  | CUMENT OVERVIEW1-                                                     | -2 |

| 1    | .4  | Ехр  | erimental Overview1-                                                  | .3 |

| 2 E  | LE  | CTR  | OMAGNETIC INTERFERENCE (EMI)2-                                        | 1  |

| 2    | .1  | Inti | RODUCTION2-                                                           | -1 |

| 2    | .2  | Ele  | CTROMAGNETIC INTERFERENCE CATEGORIES2-                                | -1 |

|      | 2.2 | 2.1  | Radiated EMI2-                                                        | ·1 |

|      | 2.2 | 2.2  | Conducted EMI2-                                                       | -2 |

| 2    | .3  | CON  | DUCTED EMI2-                                                          | ·2 |

|      | 2.3 | 8.1  | Scope (Specifications 150 kHz-30MHz) of Conducted EMI                 | -2 |

|      | 2.3 | 8.2  | Differential Mode (DM) EMI2-                                          | -2 |

|      | 2.3 | 8.3  | Common Mode (CM) EMI                                                  | .3 |

|      | 2.3 | 8.4  | Relationship Between Common Mode (CM) and Differential Mode (DM) EMI2 | -6 |

| 2    | .4  | MEA  | ASURING EMI                                                           | .7 |

|      | 2.4 | 1.1  | Theory                                                                | -7 |

|      | 2.4 | 4.2  | Measurement Equipment                                                 | 0  |

|      | 2.4 | 1.3  | Terminology                                                           | 2  |

|      | 2.4 | 1.4  | Standards                                                             | 2  |

| 2    | .5  | CON  | ICLUSION2-1                                                           | 4  |

| 3 B. | AL  | ANC  | ED CONVERTERS AND ELECTROMAGNETIC INTERFERENCE3-                      | 1  |

| 3    | .1  | Inti | RODUCTION                                                             | -1 |

| 3    | .2  | BAL  | ANCED CONVERTER THEORY                                                | -1 |

|      | 3.2 | 2.1  | Principles of Operation of an Unbalanced Converter                    | ·1 |

| 3.2.2                                                                                                                                                               | Balancing a Converter                                                                                                                                                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.3 BA                                                                                                                                                              | LANCED CONVERTER EXAMPLES                                                                                                                                                                                                                                                   |

| 3.3.1                                                                                                                                                               | Boost Converter                                                                                                                                                                                                                                                             |

| 3.3.2                                                                                                                                                               | Buck-Boost Converter                                                                                                                                                                                                                                                        |

| 3.3.3                                                                                                                                                               | Naturally Balanced Converters (Schematically)                                                                                                                                                                                                                               |

| 3.4 Рн                                                                                                                                                              | YSICAL LAYOUT BALANCE (GEOMETRIC SYMMETRY)                                                                                                                                                                                                                                  |

| 3.4.1                                                                                                                                                               | Hypothesis                                                                                                                                                                                                                                                                  |

| 3.4.2                                                                                                                                                               | Electromagnetic Perspective                                                                                                                                                                                                                                                 |

| 3.5 Pro                                                                                                                                                             | DPOSED DESIGN                                                                                                                                                                                                                                                               |

| 3.5.1                                                                                                                                                               | H-Bridge Converter and Full Bridge Rectifier Circuit                                                                                                                                                                                                                        |

| 3.5.2                                                                                                                                                               | Physical Layout                                                                                                                                                                                                                                                             |

| 3.6 Co                                                                                                                                                              | NCLUSION                                                                                                                                                                                                                                                                    |

| 4 DESIGN                                                                                                                                                            | AND IMPLEMENTATION                                                                                                                                                                                                                                                          |

|                                                                                                                                                                     |                                                                                                                                                                                                                                                                             |

| 4.1 INT                                                                                                                                                             | RODUCTION                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                     | RODUCTION                                                                                                                                                                                                                                                                   |

| 4.2 Ge                                                                                                                                                              |                                                                                                                                                                                                                                                                             |

| <ul><li>4.2 GE</li><li>4.3 MC</li></ul>                                                                                                                             | NERAL DESIGN SPECIFICATIONS                                                                                                                                                                                                                                                 |

| <ul><li>4.2 GE</li><li>4.3 MC</li></ul>                                                                                                                             | NERAL DESIGN SPECIFICATIONS                                                                                                                                                                                                                                                 |

| <ul> <li>4.2 GE</li> <li>4.3 Mo</li> <li>4.3.1</li> </ul>                                                                                                           | NERAL DESIGN SPECIFICATIONS                                                                                                                                                                                                                                                 |

| <ul> <li>4.2 GE</li> <li>4.3 MC</li> <li>4.3.1</li> <li>4.3.2</li> <li>4.3.3</li> </ul>                                                                             | NERAL DESIGN SPECIFICATIONS       4-1         DESFET DRIVER CIRCUITS       4-2         Rationale       4-2         Optical Drive with Isolated Supplies       4-3                                                                                                           |

| <ul> <li>4.2 GE</li> <li>4.3 MC</li> <li>4.3.1</li> <li>4.3.2</li> <li>4.3.3</li> </ul>                                                                             | NERAL DESIGN SPECIFICATIONS4-1OSFET DRIVER CIRCUITS4-2Rationale4-2Optical Drive with Isolated Supplies4-3Non-Isolated Drive (IR2113 Drivers)4-5                                                                                                                             |

| <ul> <li>4.2 GE</li> <li>4.3 Mo</li> <li>4.3.1</li> <li>4.3.2</li> <li>4.3.3</li> <li>4.4 Co</li> </ul>                                                             | NERAL DESIGN SPECIFICATIONS       4-1         DESFET DRIVER CIRCUITS       4-2         Rationale       4-2         Optical Drive with Isolated Supplies       4-3         Non-Isolated Drive (IR2113 Drivers)       4-5         MPLETE BALANCED CIRCUIT SCHEMATIC       4-6 |

| <ul> <li>4.2 GE</li> <li>4.3 MC</li> <li>4.3.1</li> <li>4.3.2</li> <li>4.3.3</li> <li>4.4 Co</li> <li>4.4.1</li> </ul>                                              | NERAL DESIGN SPECIFICATIONS4-1DESFET DRIVER CIRCUITS4-2Rationale4-2Optical Drive with Isolated Supplies4-3Non-Isolated Drive (IR2113 Drivers)4-5MPLETE BALANCED CIRCUIT SCHEMATIC4-6H-Bridge Circuit4-6                                                                     |

| <ul> <li>4.2 GE</li> <li>4.3 Mo</li> <li>4.3.1</li> <li>4.3.2</li> <li>4.3.3</li> <li>4.4 Co</li> <li>4.4.1</li> <li>4.4.2</li> </ul>                               | NERAL DESIGN SPECIFICATIONS4-1OSFET DRIVER CIRCUITS4-2Rationale4-2Optical Drive with Isolated Supplies4-3Non-Isolated Drive (IR2113 Drivers)4-5MPLETE BALANCED CIRCUIT SCHEMATIC4-6H-Bridge Circuit4-6Full Bridge Rectifier4-6                                              |

| <ul> <li>4.2 GE</li> <li>4.3 Mo</li> <li>4.3.1</li> <li>4.3.2</li> <li>4.3.3</li> <li>4.4 Co</li> <li>4.4.1</li> <li>4.4.2</li> <li>4.4.3</li> <li>4.4.4</li> </ul> | NERAL DESIGN SPECIFICATIONS4-1DSFET DRIVER CIRCUITS4-2Rationale4-2Optical Drive with Isolated Supplies4-3Non-Isolated Drive (IR2113 Drivers)4-5MPLETE BALANCED CIRCUIT SCHEMATIC4-6H-Bridge Circuit4-6Full Bridge Rectifier4-6Entire Circuit4-7                             |

| 4.5.2     | Optical Signal Generator                               |

|-----------|--------------------------------------------------------|

| 4.5.3     | IR2113 Driver Board                                    |

| 4.5.4     | PCB1 – Baseline                                        |

| 4.5.5     | PCB 2 – Second Baseline                                |

| 4.5.6     | PCB 3 – 3 Dimensional Layout                           |

| 4.5.7     | PCB4 – Physically Balanced Layout                      |

| 4.6 Imp   | LEMENTATION (REALISATION)4-13                          |

| 4.6.1     | MOSFET Driver Boards                                   |

| 4.6.2     | Devices Under Test                                     |

| 4.7 Cor   | NCLUSION                                               |

| 5 EXPERIM | MENTAL SETUP                                           |

| 5.1 INT   | RODUCTION                                              |

| 5.2 Equ   | JIPMENT SETUP                                          |

| 5.2.1     | <i>Equipment</i>                                       |

| 5.2.2     | Equipment Setup Overview                               |

| 5.3 Exe   | PERIMENTAL OVERVIEW                                    |

| 5.3.1     | Test 1: No Load with Zero Elevation, DM Measurement5-7 |

| 5.3.2     | Test 2: No Load with Zero Elevation, CM Measurement5-7 |

| 5.3.3     | Test 3: Loaded with Zero Elevation, DM Measurement     |

| 5.3.4     | Test 4: Loaded with Zero Elevation, CM Measurement     |

| 5.3.5     | Test 5: No Load with Elevation, DM Measurement         |

| 5.3.6     | Test 6: No Load with Elevation, CM Measurement5-8      |

| 5.3.7     | Test 7: Loaded with Elevation, DM Measurement          |

| 5.3.8     | Test 8: Loaded with Elevation, CM Measurement5-8       |

| 5.4 Cor   | NCLUSION                                               |

| 6 RESULT  | S AND ANALYSIS6-1                                      |

| 6.1 PC  | B1 (VEROBOARD) RESULTS                       |

|---------|----------------------------------------------|

| 6.1.1   | DM Results                                   |

| 6.1.2   | CM Results                                   |

| 6.2 PC  | B2 (BASELINE) RESULTS                        |

| 6.2.1   | DM Results                                   |

| 6.2.2   | CM Results                                   |

| 6.3 PC  | B3 (3 DIMENSIONAL) RESULTS                   |

| 6.3.1   | DM Results                                   |

| 6.3.2   | CM Results                                   |

| 6.4 PC  | B4 (GEOMETRICALLY SYMMETRICAL) RESULTS       |

| 6.4.1   | DM Results                                   |

| 6.4.2   | CM Results                                   |

| 6.5 PC  | B1 vs. PCB2 vs. PCB3 vs. PCB4 DM Results6-18 |

| 6.5.1   | No Load with Zero Elevation                  |

| 6.5.2   | No Load with 200mm Elevation                 |

| 6.5.3   | Loaded with Zero Elevation                   |

| 6.5.4   | Loaded with 200mm Elevation                  |

| 6.6 PC  | B1 vs. PCB2 vs. PCB3 vs. PCB4 CM Results     |

| 6.6.1   | No Load with Zero Elevation                  |

| 6.6.2   | No Load with 200mm Elevation                 |

| 6.6.3   | Loaded with Zero Elevation                   |

| 6.6.4   | Loaded with 200mm Elevation                  |

| 6.7 MC  | OSFET DRIVER NOISE                           |

| 6.8 Co  | NCLUSION                                     |

| 7 CONCL | USION AND FUTURE WORK                        |

| 7.1 Co  | NCLUSION7-1                                  |

| 7.2   | FUI  | TURE WORK                                                              |

|-------|------|------------------------------------------------------------------------|

| 7.    | 2.1  | Investigate MOSFET Driver Noise                                        |

| 7.    | 2.2  | Development of a Schematically Balanced Boost Converter                |

| 7.    | 2.3  | Geometrically Balancing an Unnaturally Schematically Balanced Circuit  |

| 7.    | 2.4  | Root Cause of Geometric Symmetry Reducing EMI Generation Mechanisms7-4 |

| 7.    | 2.5  | Mutual Inductance7-4                                                   |

| 8 APP | END  | ICES                                                                   |

| 8.1   | App  | PENDIX A                                                               |

| 8.2   | App  | PENDIX B                                                               |

| 8.3   | App  | PENDIX C                                                               |

| 9 REF | FERE | NCES                                                                   |

# LIST OF FIGURES

| Figure 2-1 Propagation Methods [6]                                         | 2-1  |

|----------------------------------------------------------------------------|------|

| Figure 2-2 Differential Mode (DM) EMI Conduction Path [4]                  | 2-2  |

| Figure 2-3 Common Mode (CM) EMI Conduction Path [4]                        | 2-4  |

| Figure 2-4 MOSFET Parasitic Capacitance [8]                                | 2-4  |

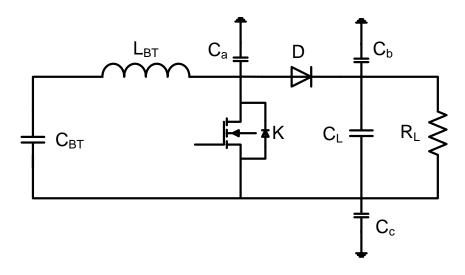

| Figure 2-5 Boost Converter illustrating parasitic $C_S$ [9]                | 2-5  |

| Figure 2-6 Boost Converter with associated parasitic components [9]        | 2-5  |

| Figure 2-7 CM EMI generation through DM Unbalance [2]                      | 2-6  |

| Figure 2-8 CM generation through imbalance in the CM and DM impedances [2] | 2-7  |

| Figure 2-9 Power and noise propagation directions [2]                      | 2-7  |

| Figure 2-10 Differential Mode (DM) Currents Flowing into Noise Loads [2]   | 2-8  |

| Figure 2-11 Common Mode (CM) Currents Flowing into Noise Loads [2]         | 2-8  |

| Figure 2-12 DM and CM as Conducted EMI [4]                                 | 2-9  |

| Figure 2-13 EMCO 3825/2 Circuit Diagram [4] [12]                           | 2-11 |

| Figure 2-14 FCC Part 15 Subpart A [15]                                     | 2-13 |

| Figure 2-15 FCC Part 15 Subpart B [15]                                     | 2-13 |

| Figure 3-1 Boost Converter Illustration CM EMI Generation [9]              | 3-2  |

| Figure 3-2 Simplified Boost Converter CM Path [9]                          | 3-3  |

| Figure 3-3 Unbalanced Boost Converter [9]                                  | 3-3  |

| Figure 3-4 Balanced Boost Converter [9]                                    | 3-4  |

| Figure 3-5 Simplified Balanced Boost Converter CM Path [9]                 | 3-4  |

| Figure 3-6 Conventional Boost Converter [9]                                | 3-5  |

| Figure 3-7 Balanced Boost Converter [9]                                    | 3-6  |

| Figure 3-8 Conventional Buck-Boost Converter (Two Windings) [9]            | 3-6  |

| Figure 3-9 Balanced Buck-Boost Converter (Two Windings) [9]                | 3-7  |

| Figure 3-10 H-Bridge Converter and Full-Bridge Rectifier                                              |

|-------------------------------------------------------------------------------------------------------|

| Figure 3-11 H-Bridge Converter and Full-Bridge rectifier with output filter                           |

| Figure 3-12 Half -Cycle analysis of Full-Bridge converter and Full-Bridge rectifier 3-10              |

| Figure 3-13 Output Filter Unbalanced Component                                                        |

| Figure 3-14 Schematically Balanced Full-Bridge Converter with Full-Bridge Rectifier and output filter |

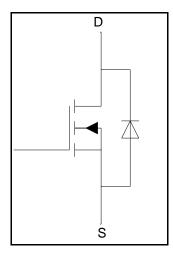

| Figure 4-1 MOSFET [16]                                                                                |

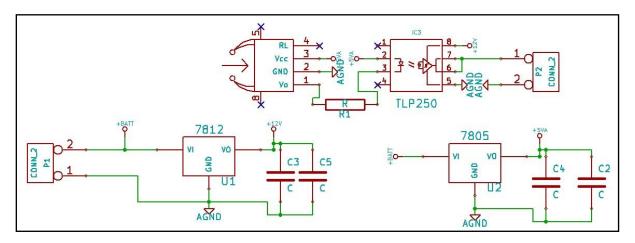

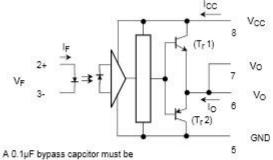

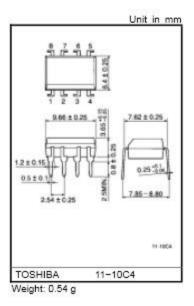

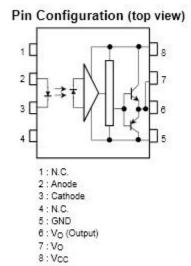

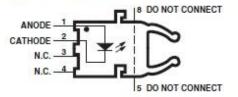

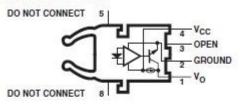

| Figure 4-2 TLP250 Drive Module                                                                        |

| Figure 4-3 Optical Signal Generator Board                                                             |

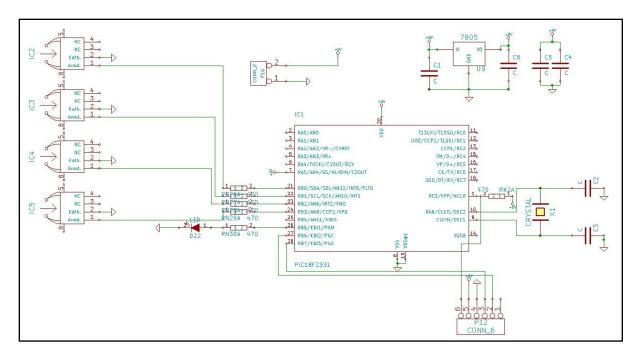

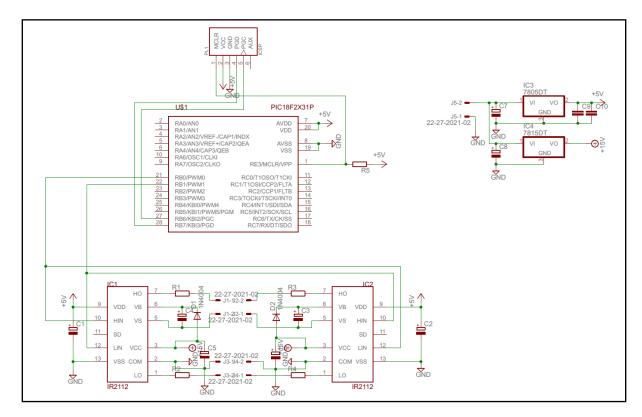

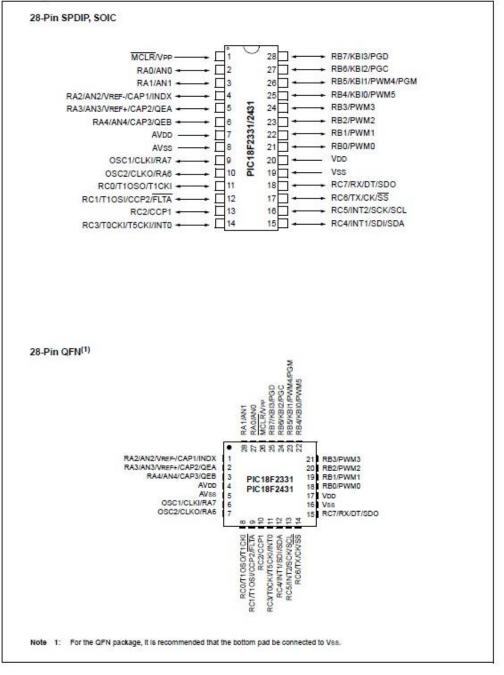

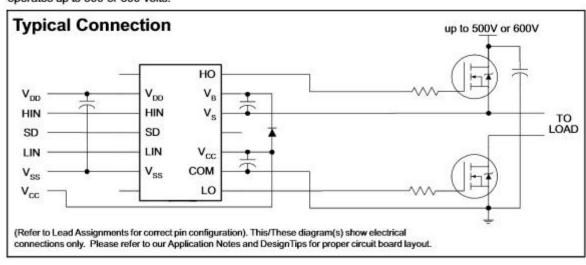

| Figure 4-4 IR2113 Driver Board                                                                        |

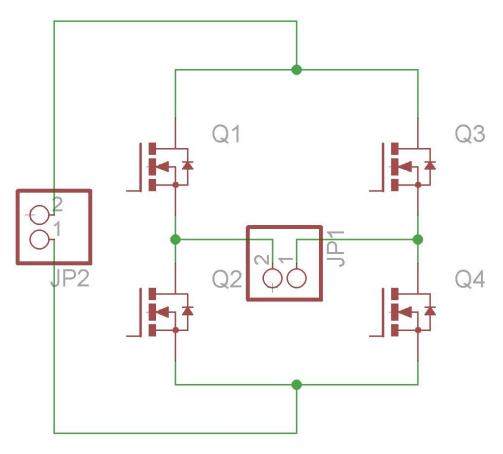

| Figure 4-5 H-Bridge Schematic4-6                                                                      |

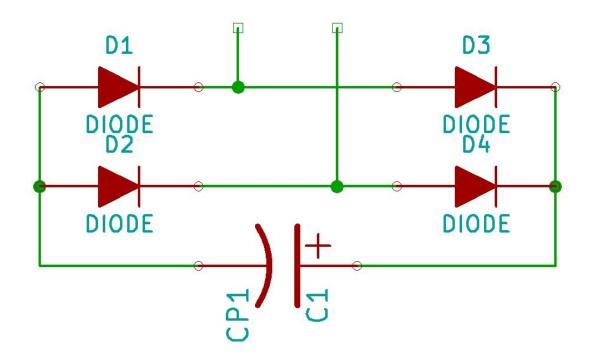

| Figure 4-6 Full-Bridge Rectifier Schematic4-7                                                         |

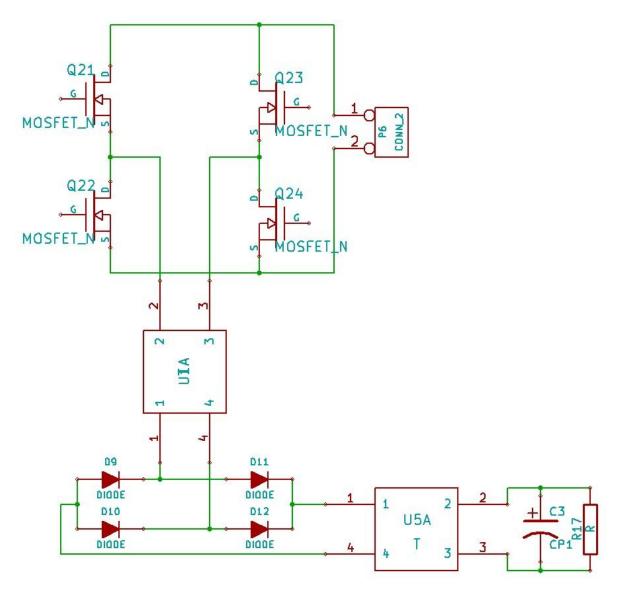

| Figure 4-7 Entire Circuit Schematic                                                                   |

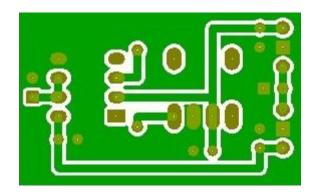

| Figure 4-8 TLP250 PCB artwork                                                                         |

| Figure 4-9 Optical Signal Generator PCB artwork                                                       |

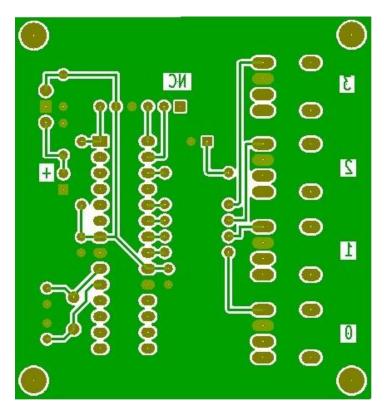

| Figure 4-10 IR2113 Driver Board PCB artwork4-10                                                       |

| Figure 4-11 PCB 2 (Second Baseline) artwork                                                           |

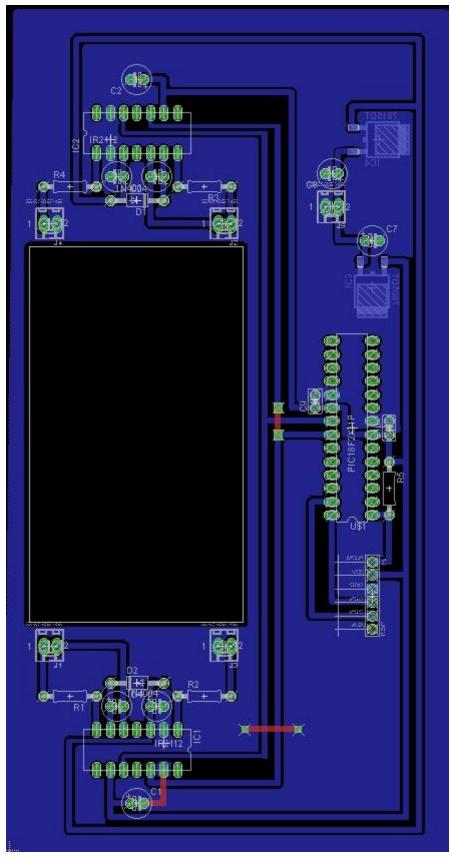

| Figure 4-12 PCB 3 (3 Dimensional Layout) artwork                                                      |

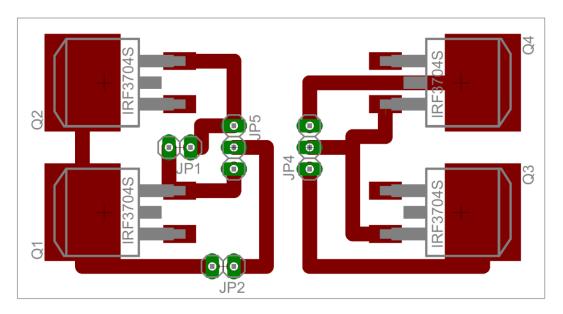

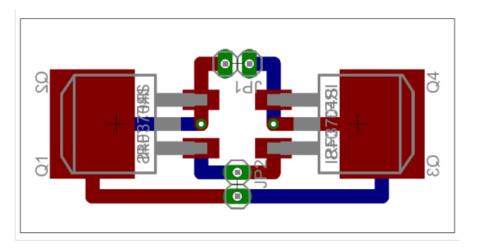

| Figure 4-13 PCB 4 Geometrically Balanced PCB artwork                                                  |

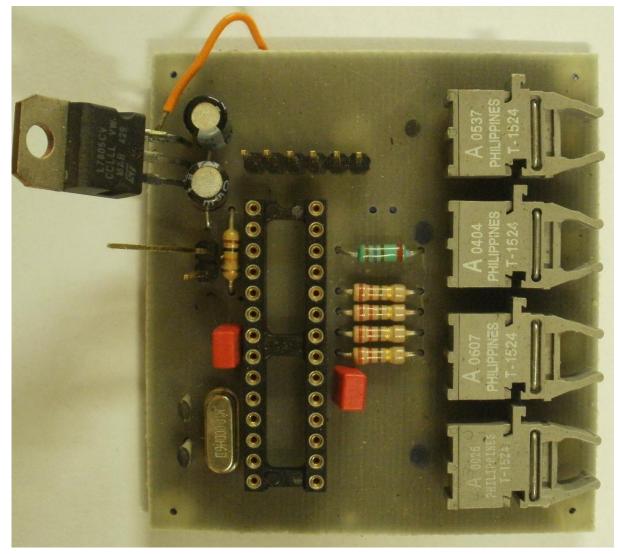

| Figure 4-14 Optical Signal PCB4-13                                                                    |

| Figure 4-15 TLP250 Driver PCB4-14                                                                     |

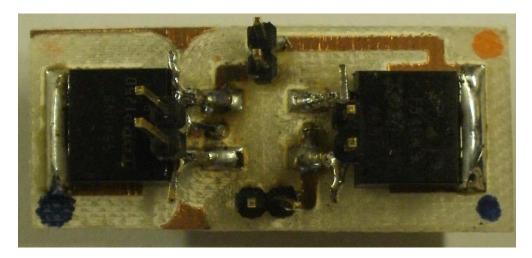

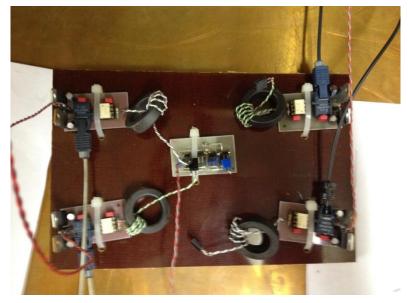

| Figure 4-16 IR2113 MOSFET Driver PCB4-14                                                              |

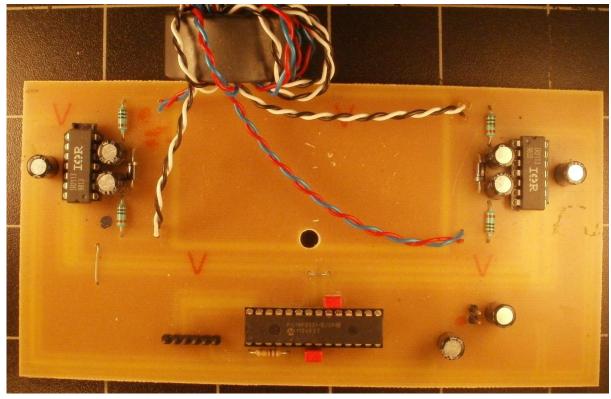

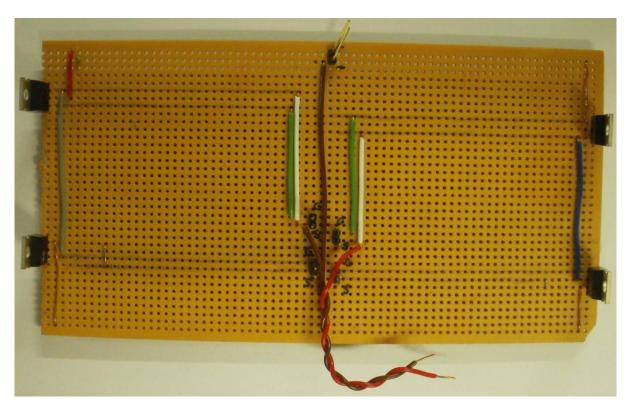

| Figure 4-17 Device Under Test 1 Veroboard (Baseline)                                                  |

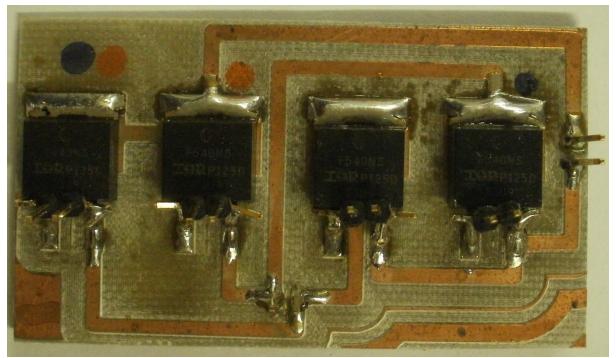

| Figure 4-18 Device Under Test 2 PCB (Second Baseline)                                                 |

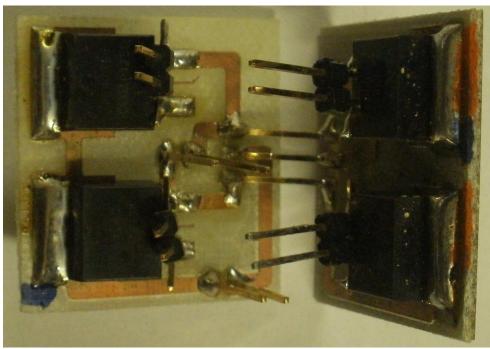

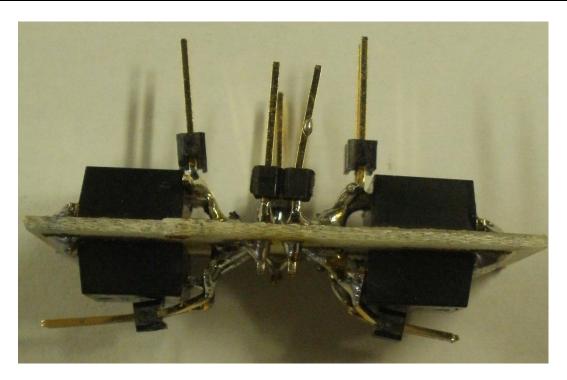

| Figure 4-19 Device Under Test 3 PCB (3 Dimensional)4-16                                               |

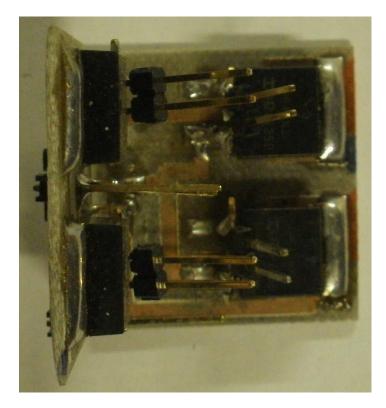

| Figure 4-20 Device Under Test 3 PCB (3 Dimensional – Alternate View)                                  |

| Figure 4-22 Side view of Device Under Test 4 PCB (Geometrically Symmetrical – Rotated View) |

|---------------------------------------------------------------------------------------------|

| Figure 5-1 Linear DC Power Supply5-2                                                        |

| Figure 5-2 EMI Filter5-2                                                                    |

| Figure 5-3 Line Impedance Stabilisation Network (LISN)                                      |

| Figure 5-4 CM + DM Splitter                                                                 |

| Figure 5-5 Spectrum Analyser                                                                |

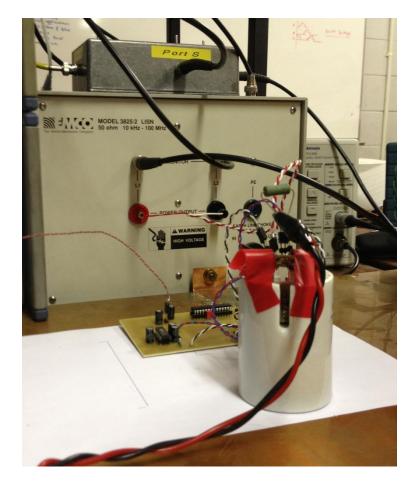

| Figure 5-6 Experimental Setup5-5                                                            |

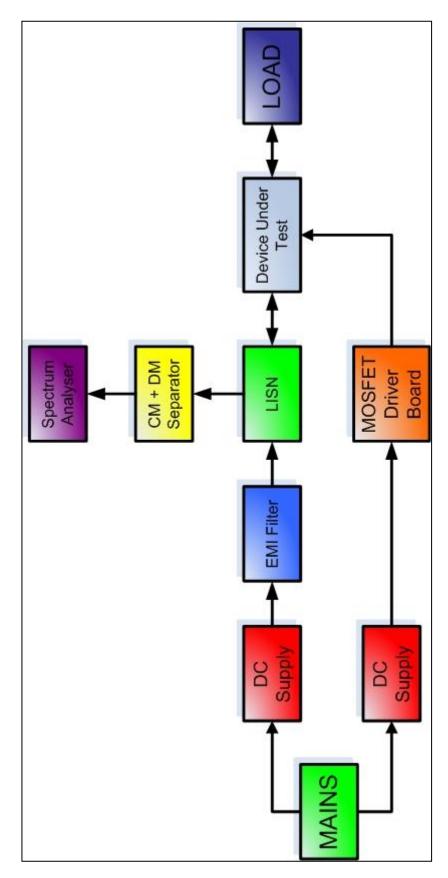

| Figure 5-7 Experiment Overview5-6                                                           |

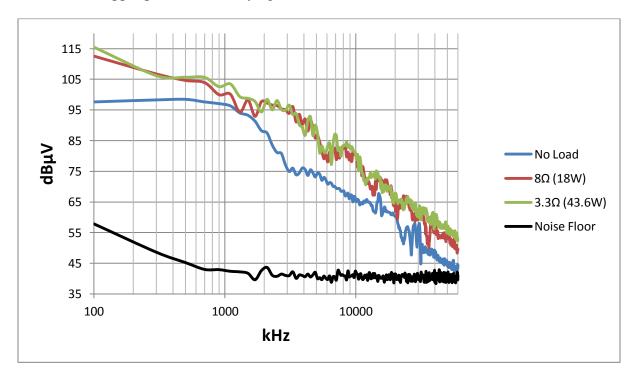

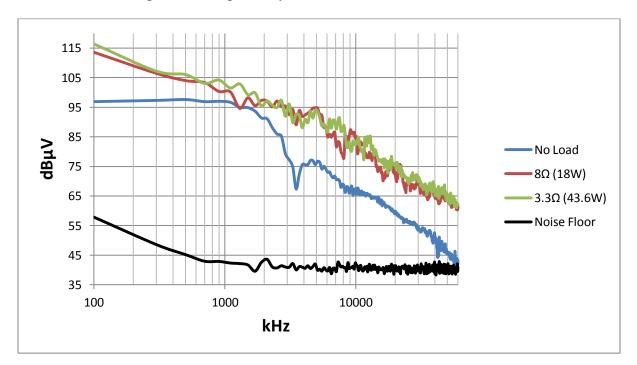

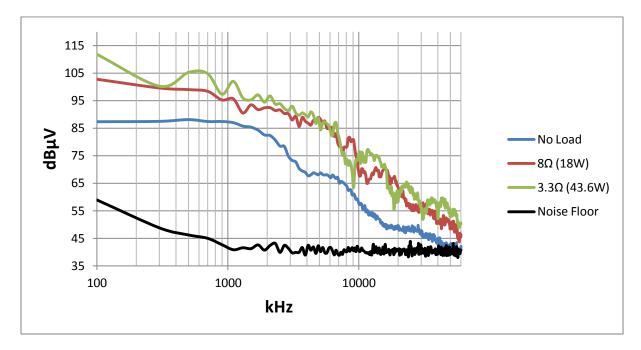

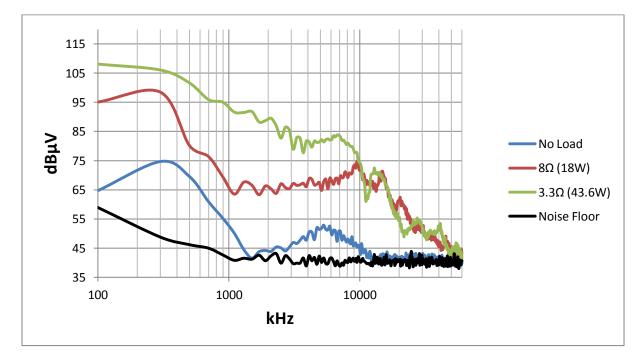

| Figure 6-1 PCB1 Zero Elevation DM Results                                                   |

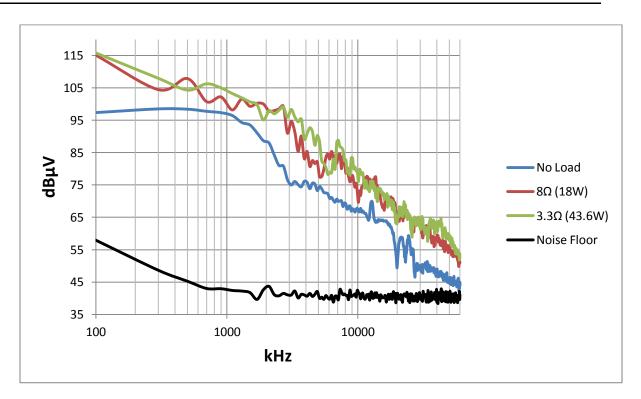

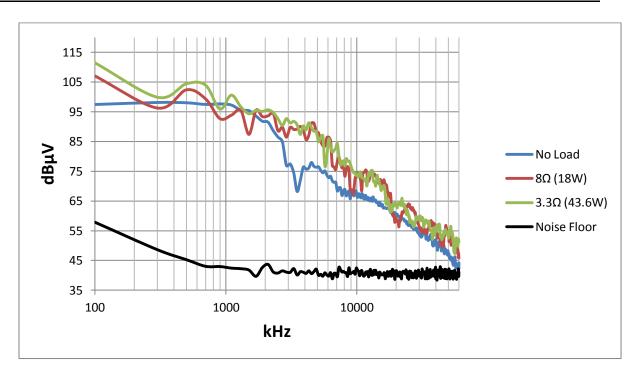

| Figure 6-2 PCB1 200mm Elevation DM Results                                                  |

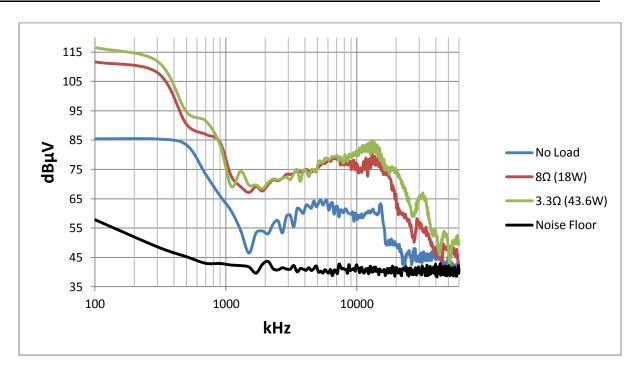

| Figure 6-3 PCB1 Zero Elevation CM Results                                                   |

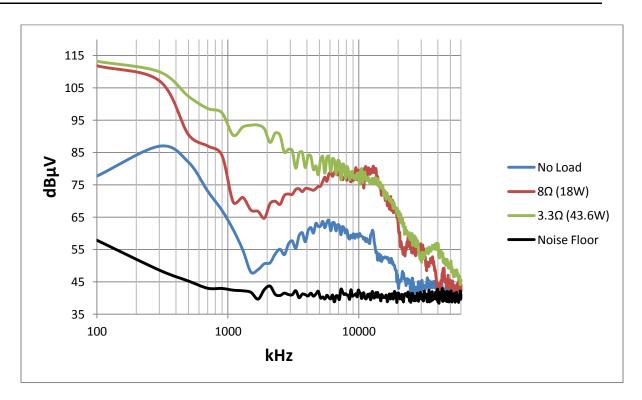

| Figure 6-4 PCB1 200mm Elevation CM Results                                                  |

| Figure 6-5 PCB2 Zero Elevation DM Results                                                   |

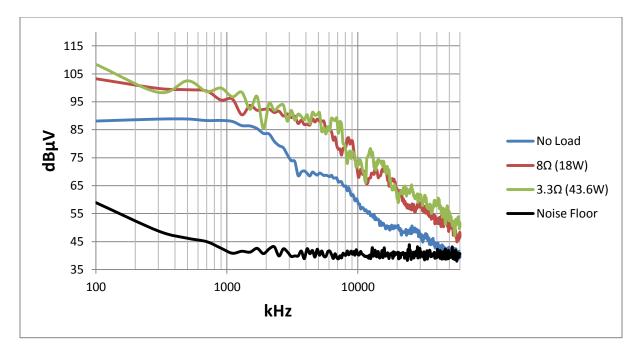

| Figure 6-6 PCB2 200mm Elevation DM Results                                                  |

| Figure 6-7 PCB2 Zero Elevation CM Results                                                   |

| Figure 6-8 PCB2 200mm Elevation CM Results                                                  |

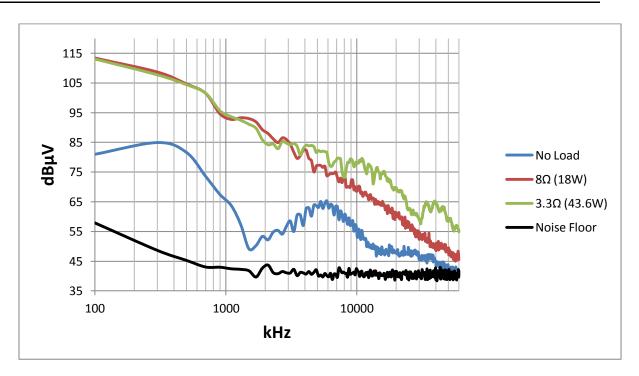

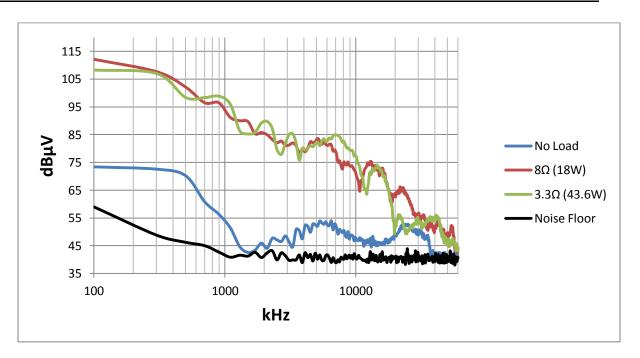

| Figure 6-9 PCB3 Zero Elevation DM Results                                                   |

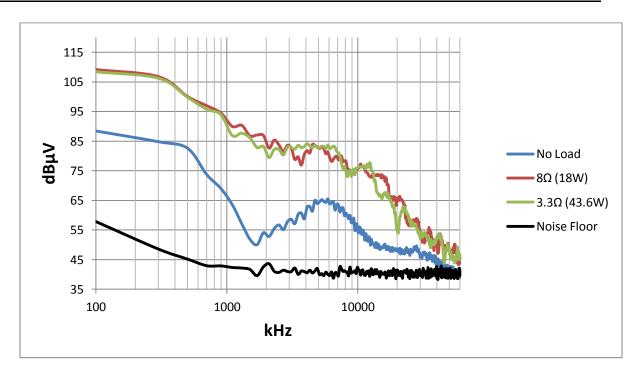

| Figure 6-10 PCB3 200mm Elevation DM Results                                                 |

| Figure 6-11 PCB3 Zero Elevation CM Results                                                  |

| Figure 6-12 PCB3 200mm Elevation CM Results                                                 |

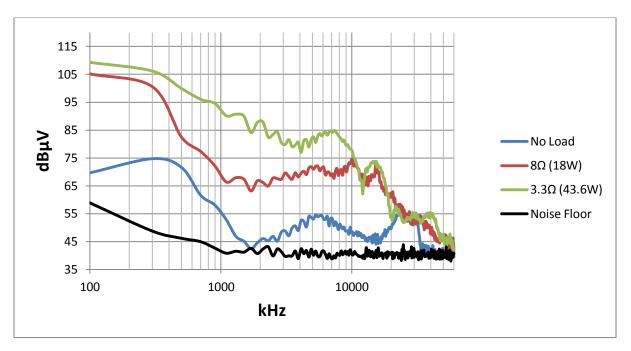

| Figure 6-13 PCB4 Zero Elevation DM Results                                                  |

| Figure 6-14 PCB4 200mm Elevation DM Results 6-16                                            |

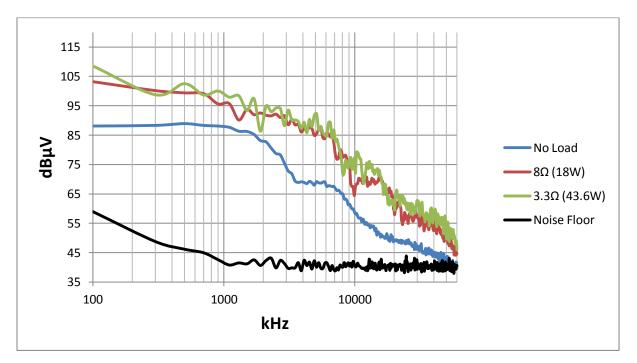

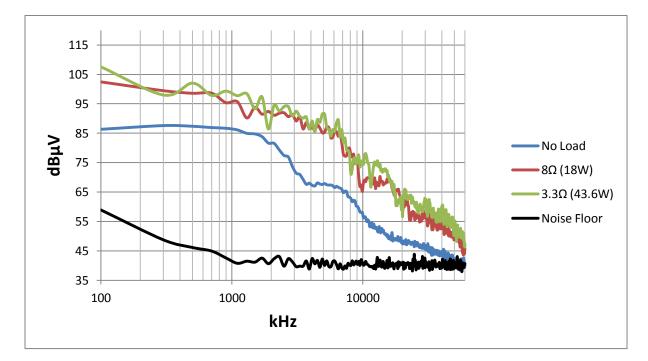

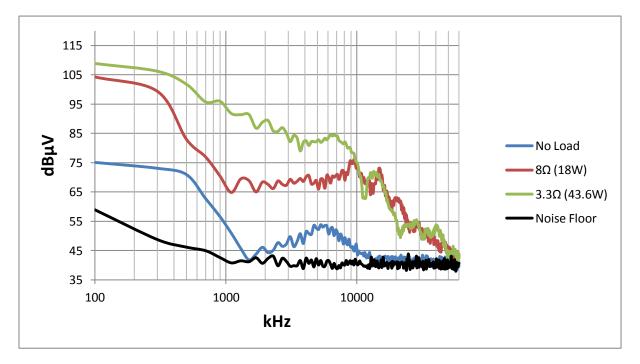

| Figure 6-15 PCB4 Zero Elevation CM Results                                                  |

| Figure 6-16 PCB4 200mm Elevation CM Results                                                 |

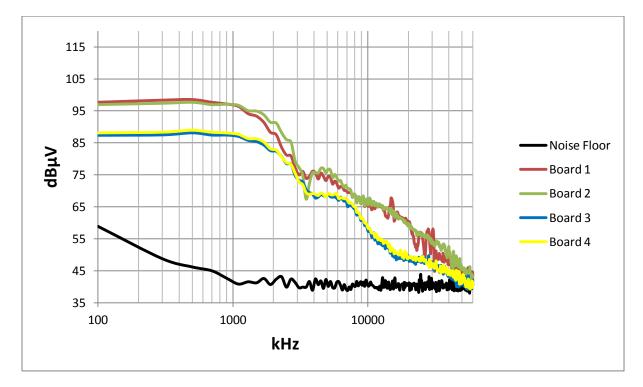

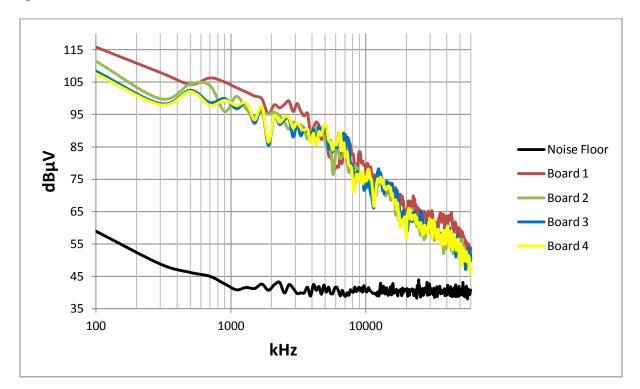

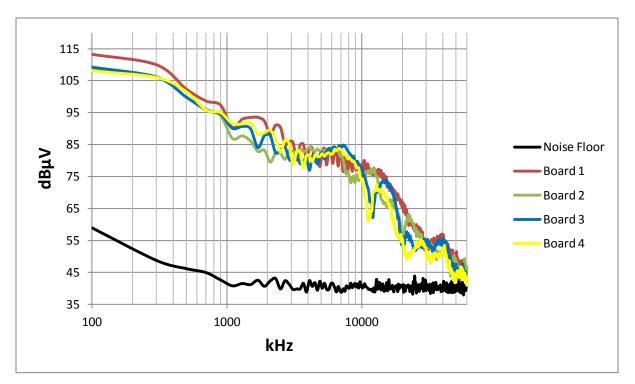

| Figure 6-17 Comparitive No Load Zero Elevation DM Results  |

|------------------------------------------------------------|

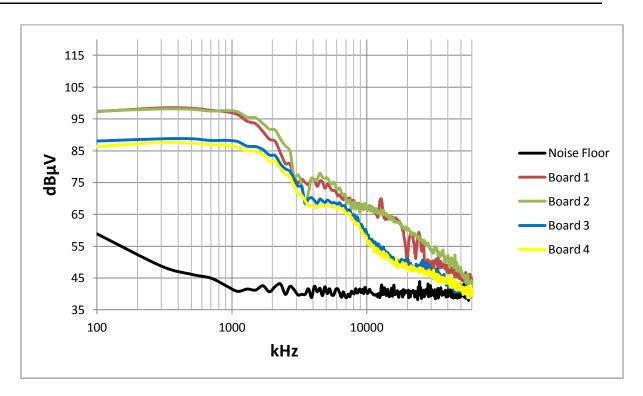

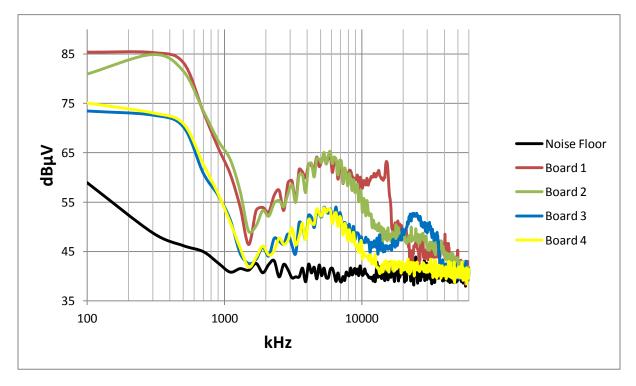

| Figure 6-18 Comparitive No Load 200mm Elevation DM Results |

| Figure 6-19 Comparitive Loaded Zero Elevation DM Results   |

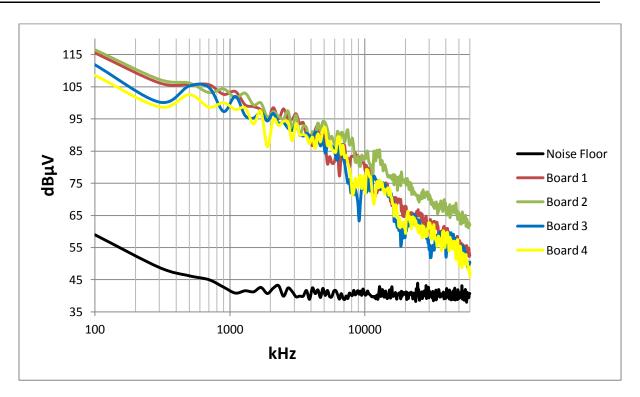

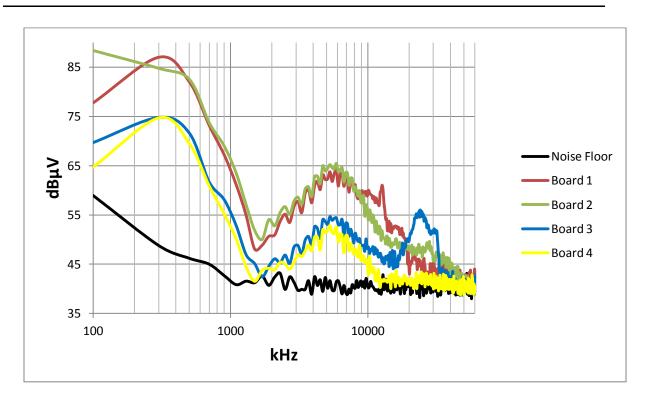

| Figure 6-20 Comparitive Loaded 200mm Elevation DM Results  |

| Figure 6-21 Comparitive No Load Zero Elevation CM Results  |

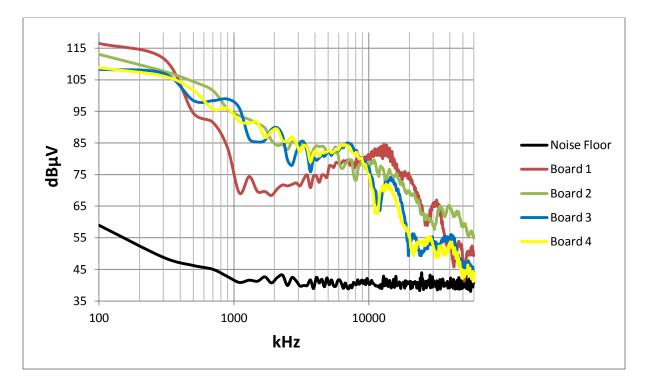

| Figure 6-22 Comparitive No Load 200mm Elevation CM Results |

| Figure 6-23 Comparitive Loaded Zero Elevation CM Results   |

| Figure 6-24 Comparitive Loaded 200mm Elevation CM Results  |

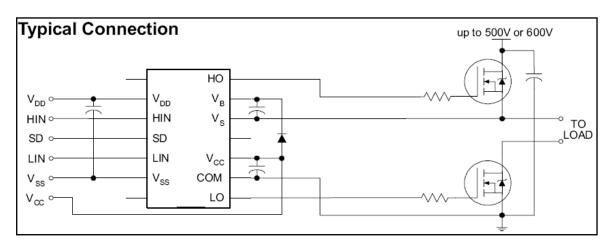

| Figure 6-25 Typical IR2113 Configuration [20]6-30          |

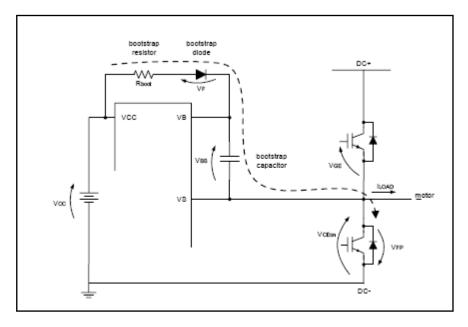

| Figure 6-26 IR2113 Bootstrap Current Path [21]6-30         |

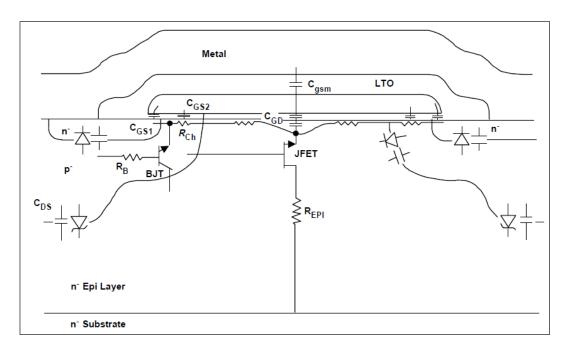

| Figure 6-27 MOSFET Parasitic Components [22]6-31           |

| Figure 7-1 Unbalanced to Balanced Boost Converter          |

| Figure 8-1 TLP250 MOSFET Driver Experimental Setup         |

| Figure 8-2 4 Isolated Power Supplies                       |

| Figure 8-3 Tektronix TDS 2024B Oscilloscope                |

# LIST OF ACRONYMS

- AC Alternating Current

- CM Common Mode

- DC Direct Current

- DM Differential Mode

- DUT Device Under Test

- EMC Electromagnetic Compatibility

- EMI Electromagnetic Interference

- EUT Equipment Under Test

- LISN Line Impedance Stabilisation Network

- NF Noise Floor

- PCB Printed Circuit Board

- PWM Pulse Width Modulation

- RF Radio Frequency

- SMPS Switched Mode Power Supply

- TCL Transverse Conversion Loss

# **1 INTRODUCTION AND PROBLEM STATEMENT**

## **1.1 INTRODUCTION**

The increasing drive for energy efficiency in today's world brings about new challenges and obstacles especially within the domain of Industrial Electronics. These increasing demands for increased efficiency, reduced size (through increased frequency operation) and the lower cost of devices brings about the need to focus on new or previously unimportant phenomenon as they become ever more dominant. One such phenomenon in the Industrial Electronics field is the phenomenon of Electromagnetic Interference (EMI).

The need to advance is fundamental to human progress and hence the ever increasing efforts within the Industrial Electronics fraternity. With reference to the general timeline of Electrical Engineering and electricity, Electronics and specifically Industrial Electronics is a relatively new arena [1] [2] [3]. The relative infancy of Industrial Electronics and now the ever increasing improvements within the field exposes the previous lack of study of the EMI phenomenon. One such reason for the previous lack of concern with EMI is the state of the art of electronics (i.e. operating frequencies and size of devices). Operating modes of electronics never produced appreciable amounts of EMI or the ability to measure EMI was not evident at such a time.

Electromagnetic Interference is the phenomenon by which the operation of a device or system emits Electromagnetic Radiation via a cacophony of methods. The emitted radiation through propagation can then result in an undesirable operating effect on other operational equipment so as to cause the equipment to fail or malfunction. The equipment which falls victim to such interference is not only limited to other equipment but may include the generating equipment itself (the source).

EMI has generally been considered a difficult phenomenon to understand within the Engineering community and has often been labelled as a "*Black Art*" due to the complexities and unknown or abstract generation mechanism of EMI.

As the generation mechanisms of EMI are generally not well understood, operational devices are not normally designed with EMI in mind [2] [3] [4]. During development of electronic devices, a device is designed and developed until functional against preliminary design specifications. Once operating within the design specifications, the device is then sent to EMI testing. Based on the EMI results, an appropriately large EMI filter is then fitted to the front and back of the device to fall with EMI standards. These filters then add both cost, physical size and weight to the device. If the device were to be designed and developed with the generation mechanisms of EMI in mind, the EMI issues would be solved on a root level and hence automatically reduce cost and the required filter size for the device.

Due to the difficulty of understanding the sometimes abstract generation mechanisms or more often than not the lack of knowledge in understanding EMI, devices are not normally designed with EMI in mind. Therefore the knowledge of EMI from the beginning of the design process will substantially aid in the reduction of EMI from root causes and automatically improve EMI results, a direct treatment of the issues on a root level and not just on a symptom level.

Gaining insight into the root generation mechanisms of EMI and discovering appropriate methods of reducing EMI through design, forms the foundation of the dissertation presented within.

## **1.2 SCOPE**

The scope of this dissertation pertains to the design and development of multiple Printed Circuit Boards (PCB's) to investigate methods used to firstly demonstrate EMI and secondly to mitigate Electromagnetic Interference on a root level. Varying parameters shall be applied to observe the effects of these altered parameters on EMI generation mechanisms.

## **1.3 DOCUMENT OVERVIEW**

Chapter 2:

- Defining Electromagnetic Interference

- Differentiating EMI Propagation Methods into subsequent modes

- Defining Conducted EMI

- Components of Conducted EMI and Generation mechanisms

- Measurement Methods and EMI

- Separation of Conducted EMI components into DM and CM

Chapter 3:

- Introduction of the Balanced Converter topology

- Unbalanced Converter theory and EMI generation mechanisms

- Conversion of an Unbalanced Converter to a Balanced Converter

- Balanced Converter Examples

- Investigation in Geometrically Balanced Converter

- Proposed Geometrically Balanced Converter

Chapter 4:

- Test Circuits design criteria

- Required circuit

- Dividing circuit into sub-circuits

- MOSFET Driver Circuit Design

- Varying PCB's Design

- Physical Implementation of Designed Circuits

#### Chapter 5:

- Equipment Required and Setup

- Experimental Setup

#### Chapter 6:

- Individual PCB results

- Comparative results

- Analysis of results

### Chapter 7:

- Conclusion

- Future work

## **1.4 EXPERIMENTAL OVERVIEW**

A brief outline of the Experimental setup is outlined below:

- 1. No load DM results: Non-Elevated and Elevated case

- 2. Loaded DM results: Non-Elevated and Elevated case

- 3. No load CM results: Non-Elevated and Elevated case

- 4. Loaded CM results: Non-Elevated and Elevated case

# 2 ELECTROMAGNETIC INTERFERENCE (EMI)

## 2.1 INTRODUCTION

Electromagnetic Interference (EMI) can be described as the undesirable effect due to an electromagnetic emission or disturbance from a source due to its operation regardless whether intentional or not upon another piece of operating equipment. The emissions may produce an undesirable or unwanted operating effect on the affected piece of equipment. Such effects in turn may cause the affected equipment to malfunction or cease to function entirely. The victim is not limited to other operational devices but may include the source itself.

Multiple categories of EMI exist based upon the method of propagation, which are discussed in Section 2.2.

#### 2.2 ELECTROMAGNETIC INTERFERENCE CATEGORIES

Due to the multiple coupling methods of EMI (inductive, capacitive, conductive, radiated) [5], multiple standards have been developed to help classify the type of EMI experienced. These standards mainly dictate frequency ranges and noise thresholds.

Figure 2-1 Propagation Methods [6]

## 2.2.1 Radiated EMI

Referring to Figure 2-1, Radiated EMI is propagated through free space in the form of electromagnetic waves similar to radio waves. Any equipment in the path or vicinity of the radiated energy may be susceptible to interference from the radiated energy.

The official Radiated EMI frequency spectrum begins at 30 MHz and continues up to 10 GHz. At frequencies above 30 MHz circuit wire/track length becomes considerately small enough as to behave as an antenna and hence radiate energy, thus 30 MHz being the beginning of the Radiated EMI Standard.

#### 2.2.2 Conducted EMI

Referring to Figure 2-1, Conducted EMI is propagated through inductive, capacitive and conductive means. Conducted EMI therefore propagates through a physical means such as conductors being wire or traces from the source to the victim, including capacitive and inductively through a path such as ground between the source and victim.

Conducted EMI not only affects the source supply or other equipment directly connected, but can propagate through the power system upon which it's connected to, and affect other sensitive equipment.

Conducted EMI will be the category of focus within this dissertation, upon which the further subcategories within Conducted EMI will be discussed in section 2.3.

### 2.3 CONDUCTED EMI

The details pertaining to Conducted EMI, its standards and modes are discussed in section 2.3.

#### 2.3.1 Scope (Specifications 150 kHz-30MHz) of Conducted EMI

The conducted EMI spectrum is regulated from 150 kHz to 30 MHz [4].

Frequency measurements will be done from 100 kHz to 60 MHz as to ensure measurements are within the conducted EMI standards spectrum. Both modes of EMI will be measured and compared relative to a control circuit in order to determine efficacy. Frequency measurements are conducted from 100 kHz due to measurement equipment abilities.

Conducted EMI is broken down into two categories or modes being:

- Differential Mode (DM) EMI

- Common Mode (CM) EMI

These modes are subsequently discussed in detail respectively in Sections 2.3.2 and 2.3.3.

#### 2.3.2 Differential Mode (DM) EMI

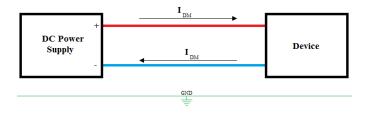

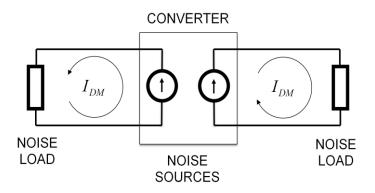

Differential Mode (DM) EMI as its name implies is the component of the Conducted EMI spectrum in which the EMI currents flow in a differential manner (opposite in direction to each other) between the source and the victim, typically through planned conductors as illustrated in Figure 2-2. By definition they are equal in magnitude but opposite in direction and the return path is in absence of the use of "ground" [4].

Figure 2-2 Differential Mode (DM) EMI Conduction Path [4]

### 2.3.2.1 Theory of DM

Differential Mode (DM) EMI is a function of the Differential Mode Current within the conductors of an operating circuit [1] [2] [4]. DM current is due to the fundamental operation of the source equipment which in many cases is a switch-mode converter [1] [2] [4], the switching function of which draws a non-DC current component regardless whether the source (and also the victim) is pure DC. There are thus frequency components within the DM current and thus DM EMI is present.

## 2.3.2.2 Generation Mechanisms of DM

The operational current drawn from the source by the switch-mode converter is not DC in which case differential alternating current is drawn and hence DM EMI is generated.

The generation mechanisms of DM EMI are, but not limited to:

- Switching Creation of frequency content (AC)

- Inductance Stray and leakage

- Absence of bus capacitance

The physical switching of a perfect source converter in theory would have perfect rise and fall times where  $t_r$  and  $t_f$  are infinitely small. The resultant current within the system produces a frequency spectrum with a fundamental switching frequency and related harmonics with a decreasing magnitude. The resulting spectrum is due to a perfect square wave being an infinite sum of sinusoids with decreasing amplitude according to Fourier Transform Theory [7]. The frequency content which results due to the switching action of a switch-mode converter therefore constitutes to DM EMI. It can be noted that a decrease or increase in  $t_r$  and  $t_f$  will change the outline of the frequency spectrum and hence influence the magnitude of the DM EMI [4].

Inductance and capacitance also have a secondary effect on DM EMI. Parasitics have the ability to form resonant circuits within a system or converter. The ringing constitutes to the generation of higher or additional frequency components which in turn generates additional DM EMI. Inductance and capacitance can also aid in coupling, thus spreading the generated EMI.

Sources of parasitic inductance can be physical layout inductance (self inductance) and leakage inductance caused by magnetic components (i.e. transformers) [4]. Parasitic capacitance can be in the form of inter-winding capacitance in magnetic sources (i.e. transformers) [4] and the capacitance's found within switching components such as semiconductor devices [4].

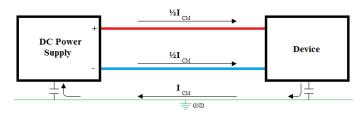

## 2.3.3 Common Mode (CM) EMI

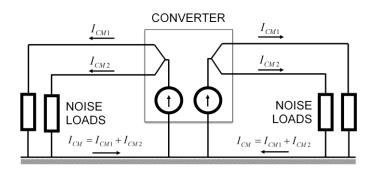

In contrast to DM EMI, where the EMI is conducted in a loop between the supply positive and negative rail (or live and neutral in AC systems) as in conventional current, CM EMI current is conducted down the positive and negative rails in the same direction with equal magnitude normally with a capacitive return path to the supply through physical ground. Figure 2-3 illustrates the basic process of the CM EMI conduction path.

Figure 2-3 Common Mode (CM) EMI Conduction Path [4]

#### 2.3.3.1 Theory of CM

By definition CM EMI is the conducted component of EMI whereby the current flows from the source to the victim normally through a capacitive means to a plane normally called "ground" [4]. In most cases the ground reference is the Earth wire in a power supply system which is usually connected to the chassis of the supply and converter.

Parasitic components within a converter or circuit are the predominant cause of CM EMI in conjunction with high frequency DM Noise. The parasitic components provide a short circuit path to ground for the already present high frequency DM components and thus are allowed to travel through a ground plane. These parasitic components are often not considered or even aware of during circuit analysis.

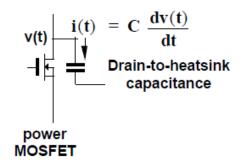

Figure 2-4 MOSFET Parasitic Capacitance [8]

Figure 2-4 illustrates the Drain to heat-sink capacitance normally found within an active switch such as a typical MOSFET and illustrates the current path used to sink current to ground as the heat-sink in a converter is usually connected to ground for safety reasons. The contact area of such a device is required to be large for cooling purposes, which in turn increases parasitic capacitance (parallel-plate area).

## 2.3.3.2 Generation of CM

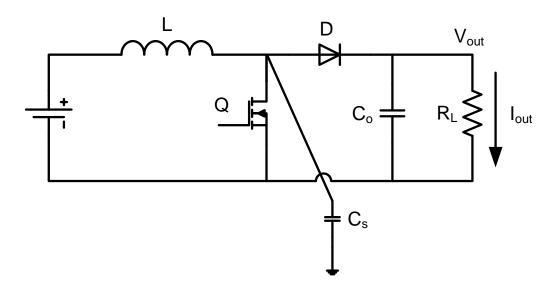

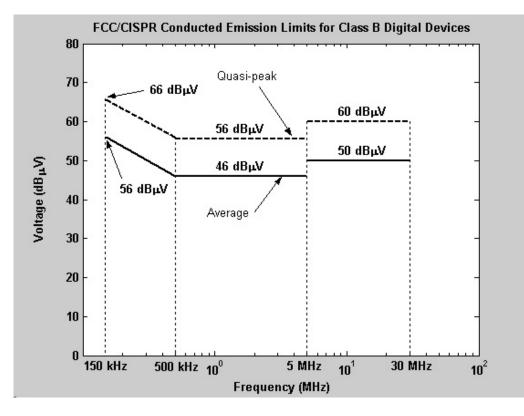

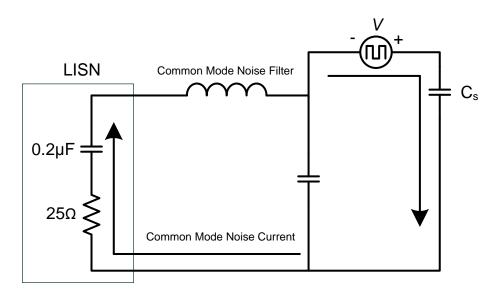

Generally, CM EMI cannot be present without the presence of DM currents or DM EMI [1] [2]. As no circuit or converter is ideal, parasitics exist. Figure 2-5 illustrates a simple boost converter with only a single parasitic present, the drain to heat-sink capacitance ( $C_s$ ).

During normal operation of the circuit in Figure 2-5, the active switch Q will switch with a specific frequency f, which will draw a current through inductor L. As inductor L is not perfect and is a complex impedance and has a resistive component at frequency, a voltage drop will appear across inductor L and in turn will present an AC voltage at the node where the drain of the MOSFET is connected to the diode and  $C_S$ .

Figure 2-5 Boost Converter illustrating parasitic  $C_S$  [9]

A high frequency voltage present across  $C_s$  will conduct current to ground hence causing current to flow from the source to the victim or supply ground. CM EMI is thus generated through the abovementioned mechanism.

CM EMI is not only limited to being generated from a single capacitive component. Figure 2-6 illustrates the other parasitics present in a boost converter, which all influence CM EMI to some extent.

Figure 2-6 Boost Converter with associated parasitic components [9]

#### 2.3.4 Relationship Between Common Mode (CM) and Differential Mode (DM) EMI

According to [1] [2], a relationship exists between CM and DM EMI. [2] Further states CM EMI is a proportional function of the DM EMI and therefore a direct theoretical correlation exists.

#### 2.3.4.1 DM to CM conversion

According to [1], using the Transverse Conversion Loss (TCL) theory, there is a predictable relationship between DM and CM.

The TCL definition in [1] simplifies the TCL into the following equation:

Where  $U_1$  represents a DM quantity and  $U_{TCL}$  represents a CM quantity. Equation (1) implies the CM EMI can be modelled as a proportional function of the DM EMI.

If there is either an increase or a decrease in the DM EMI (in magnitude or frequency), the CM EMI will either increase or decrease proportionally (in magnitude or frequency) as a result of the proportional relationship.

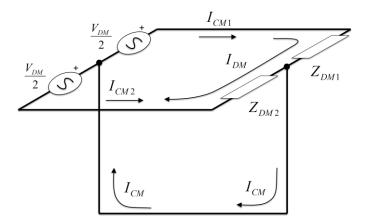

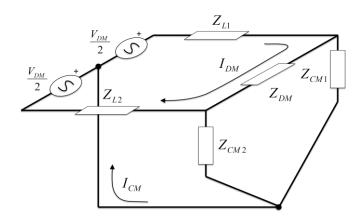

A second source of conversion illustrated in [1] is the conversion of a DM signal into CM current and hence CM EMI through DM unbalance.

Figure 2-7 CM EMI generation through DM Unbalance [2]

In Figure 2-7  $I_{CM}$  would be zero only when  $Z_{DM1}=Z_{DM2}$ , however this seldom occurs even in special cases.

When there is an imbalance between  $Z_{DM1}$  and  $Z_{DM2}$  (they are not equal), a voltage divider is present in Figure 2-7 and  $I_{CM} \neq 0$  thus creating CM currents and hence CM EMI.

An additional example of DM to CM conversion can be found in Figure 2-8.

Figure 2-8 CM generation through imbalance in the CM and DM impedances [2]

An extensive explanation regarding the DM to CM conversion process is documented within [2] for Figure 2-8 which discusses the various mechanisms by which DM to CM conversion takes place, including the possibility of CM generation mechanisms through CM components solely. In essence an imbalance between either  $Z_{L1}$  and  $Z_{L2}$  or  $Z_{CM1}$  and  $Z_{CM2}$  results in the generation of CM currents which is generally the case within real-world circuits due to circuits being imperfect.

### 2.4 MEASURING EMI

Measurement theory, techniques and the associated equipment are discussed here within Section 2.4.

#### 2.4.1 Theory

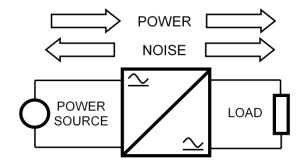

When a converter operates, by the means discussed in previous sections, EMI is generated by the converter. Power drawn from the source as either DC or low frequency AC (50-60Hz) is converted normally through switching within the converter to a different level as required by the application, often where a DC output is required.

However, regardless of whether the input or output is DC, the high frequency activity of the converter presents high frequency components (harmonics, voltage and current components) to both the load and power source as illustrated in Figure 2-9.

Figure 2-9 Power and noise propagation directions [2]

In order for the generated noise to propagate, by definition as either a current source or voltage source [2], an impedance (and current path) for the noise needs to be present in order for the noise currents to flow into. The noise load is discussed further in section 2.4.1.1.

### 2.4.1.1 Noise Source and Load Impedances

The Noise Load is defined as the impedance seen by the noise source when looking into either the *Load* or *Supply*. Similarly the noise source is the noise (EMI) generated by the converter through operation. The *Supply* and *Load* provide an impedance for the noise to enter into.

To illustrate the propagation of EMI emanating from the converter, a convention is presented such that the converter is the noise source, from where the noise propagates from to both the supply and load impedances as illustrated in Figure 2-10 and Figure 2-11.

Figure 2-10 Differential Mode (DM) Currents Flowing into Noise Loads [2]

In Figure 2-10, conventional DM noise currents flow from the noise source (converter) to the noise load (*Supply, Load*) through conventional means. The DM noise propagates through the physical conductors from the source towards the load as for conventional current, through known and easily identifiable paths.

As can be seen in Figure 2-10 and Figure 2-2, DM current flow within a cable or circuit path is equal but opposite in direction.

Figure 2-11 Common Mode (CM) Currents Flowing into Noise Loads [2]

CM noise in contrast to DM noise does not flow like conventional current convention but rather through other coupling mechanisms. The noise source and loads are similar to DM source and loads but not identical.

Figure 2-11 and Figure 2-3 illustrate that CM currents flow in the same direction along both conductors, to return via ground. The ground is connected via capacitive coupling effects whereby high frequency harmonics of the converter will couple to a heat-sink, ground-plane, ground-wire and etc to obtain a return path back to the converter. The capacitive coupling methods are mainly due to parasitic components.

#### 2.4.1.2 CM and DM separation

Mentioned earlier, DM and CM EMI Sources and Loads have been discussed and their relevant propagation methods have been discussed.

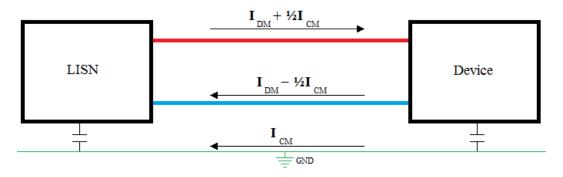

From Figure 2-2 and Figure 2-3 we can derive Figure 2-12 as the result of summing both DM and CM to produce the total Conducted EMI presented to the noise load.

Figure 2-12 also illustrates when measuring EMI, CM and DM EMI are present together within the measurement. In order to measure DM and CM individually, DM and CM EMI need to be separated by an appropriate measurement technique in order to evaluate each individually.

Figure 2-12 DM and CM as Conducted EMI [4]

In order to separate CM and DM the following equations can be formed based on Figure 2-12 and Figure 2-13. The voltages with reference to ground can be derived in terms of the DM and CM currents:

$$V_{LE} = 50 * (I_{DM} + \frac{1}{2}I_{CM})$$

Similarly

$$V_{NE} = 50 * (\frac{1}{2}I_{CM} - I_{DM})$$

Letting  $V_{DM} = 50 \times I_{DM}$  and  $V_{CM} = 25 \times I_{CM}$  and substituting:

$$V_{LE} + V_{NE} = 2 \times V_{CM}$$

$$V_{LE} - V_{NE} = 2 \times V_{DM}$$

Hence the Differential Mode (DM) voltage

$$V_{DM} = \frac{V_{LE} - V_{NE}}{2}$$

And the Common Mode (CM) voltage:

$$V_{CM} = \frac{V_{LE} + V_{NE}}{2}$$

Multiple methods are outlined in [4], [10] and [11] in order to separate DM and CM in order to measure them individually.

#### 2.4.2 Measurement Equipment

The following section outlines and describes the equipment and terminology relevant in the use of EMI measurements.

#### 2.4.2.1 LISN

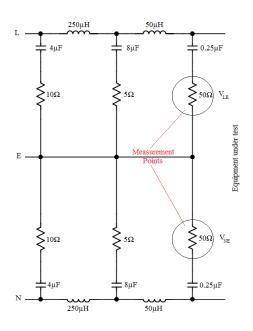

A Line Impedance Stabilisation Network (LISN) is a piece of measuring equipment used in EMI measurements to provide a standardised noise source impedance as illustrated in Figure 2-13.

A LISN is comprised of inductors, capacitors and resistors to form a multi-line low pass filter network [4] which provides a stabilised line impedance of  $50\Omega$  in order to measure conducted EMI.

In addition to providing a stabilised impedance, a LISN isolates the Equipment Under Test (EUT) from the source supply and vice versa, inhibiting noise emanating from the EUT to penetrate the supply network and to inhibit noise from the supply network entering the measurement setup.

For the purpose of this dissertation, an EMCO 3825/2 LISN was made available. According to [4] and [12] the LISN has a network inductance, impedance of 50  $\mu$ H/250  $\mu$ H, 50  $\Omega$ . The guaranteed frequency range at which the 50  $\Omega$  impedance is presented to the EUT is 10 kHz to 100 MHz for the EMCO 3825/2. Figure 2-13 below illustrates the circuit diagram of the available LISN and the location of the mentioned components.

Figure 2-13 EMCO 3825/2 Circuit Diagram [4] [12]

The 50  $\Omega$  measurement points as indicated in Figure 2-13 are used to measure the total conducted EMI from the EUT. Using the combination of both measurement points, CM and DM EMI can be separated as per discussion in Section 2.4.1.2.

A LISN will usually provide an Earth point by which a ground-plane can be connected directly to the LISN, facilitating in a good coupling plane for CM EMI and a known return path for the measurement of CM EMI.

#### 2.4.2.2 Spectrum Analyser

A spectrum analyser is a specialised piece of measuring equipment, as the name suggests capable of measuring the frequency spectrum of a signal or input. A spectrum analyser measures the power or magnitude of an electrical input signal and plots it with reference to the frequency at which the individual frequency intensities are measured.

A spectrum analyser differs from an oscilloscope as it presents its results in the frequency domain and a major difference being its bandwidth and minimum measurement threshold.

An oscilloscopes minimum measurement threshold is typically in mV whereas a spectrum analyser is capable of measuring in the  $\mu V$  range. Conducted EMI values are typically in the  $\mu V$  range and hence the use of a spectrum analyser as a necessity.

For the purpose of the dissertation, a Rohde & Schwarz FSH3 spectrum analyser was available. The FSH3 has a frequency spectrum range of 100 kHz to 3 GHz and hence is adequate for measuring EMI in the Conducted EMI spectrum.

#### 2.4.2.3 Measurement Units

Due to the extremely low measurement values, typically in the  $\mu V$  or  $\mu A$  range, Conducted EMI measurements are measured in a logarithmic scale represented as either dB $\mu V$  or dB $\mu A$  whether a voltage or current is measured.

Measuring in the  $dB\mu V$  range allows very small values to be easily interpreted and related against larger values that would seemingly be un-relatable. Another advantage in measuring with a dB scale in EMI is the ease in which it relates when applying EMI filters to a device as filters often give dB/decade roll-off values.

The  $dB\mu V$  scale is a relative voltage measurement value. It is relative to 1  $\mu$ V, thus 0  $dB\mu V = 1 \mu V$  (whereas 60  $dB\mu V = 0 dBmV$ ). [13]

### 2.4.3 Terminology

The following section covers terminology commonly found in Conducted EMI Theory which has not been previously covered.

## 2.4.3.1 Ground

Ground, sometimes referred to as "Earth" is a return path for the CM portion of the Conducted EMI spectrum [14].

The ground is usually comprised of a conductive material normally within the vicinity of the EUT. Examples of which are heat sinks and equipment enclosures.

Ground is usually connected to the Earth wire within an electrical supply system for safety reasons and hence usually forms part of the noise source return path for an Earth-Leakage system.

## 2.4.4 Standards

The Federal Communications Commission (FCC) of the USA and the Comité International Spécial des Perturbations Radioélectriques (CISPR - English: Special international committee on radio interference) provide many standards relating to EMI. These standards include measuring equipment, techniques and emission standards to mention a few.

Examples of the major standards relevant to the dissertation but not limited to are:

- CISPR 16-1

- CISPR 16-2

- FCC Part 15 Subpart A

- FCC Part 15 Subpart B

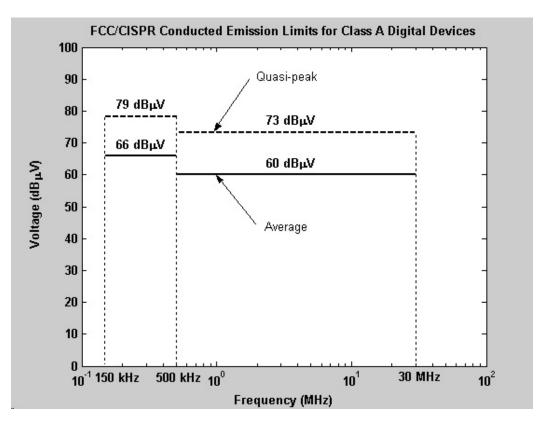

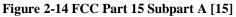

Figure 2-14 and Figure 2-15 below illustrate the FCC Part 15 A & B Conducted Noise Emission Limits. These emission limits illustrate the allowable spectrum for products that wish to go on sale to the public. These levels serve as a useful reference when comparing measured results within this dissertation.

Figure 2-15 FCC Part 15 Subpart B [15]

## 2.5 CONCLUSION

Electromagnetic Interference and mechanisms by which EMI is generated have been introduced and discussed. The categories of EMI have been highlighted and the pertinent major category of Conducted EMI has been discussed. The two conduction modes (Differential-Mode and Common-Mode) within the Conducted EMI spectrum have been discussed and the mechanisms behind their generation highlighted. The measurement techniques of Conducted EMI have been presented including some of the essential measurement equipment required to perform the measurements. The relevant standards and terminology pertaining to measuring Conducted EMI have also been discussed. Methods pertaining to the mitigation of EMI through good design practices are subsequently presented in Chapter 3.

# **3 BALANCED CONVERTERS AND ELECTROMAGNETIC INTERFERENCE**

## 3.1 INTRODUCTION

As discussed in Section 2, EMI is generated through the operation of electronic equipment. Multiple ways are available to mitigate the EMI produced by such equipment which includes the standard method of adding EMI filters to the entry-point (front-end) and exit (back-end) of the devices.

The alternate method of EMI mitigation is to employ good design techniques in order to reduce the production of EMI in the first place. This firstly includes addressing the generation mechanisms of DM and CM EMI as discussed in Section 2.3.2.2 and 2.3.3.2, which primarily addresses the physical contributors including methods to reduce EMI in terms of layout.

Secondly, the method to be investigated within this dissertation is the so called balancing of a converter, which incorporates the knowledge of how CM EMI is generated with reference to circuit parasitics unbalance. It incorporates the schematic balance of a circuit in order to reduce CM EMI. Schematic Balance as referred to henceforth describes the method by which a normally unbalanced circuit is then balanced on paper or on a circuit level to achieve in theory, identical parasitic components across active semiconductor components. The method by which schematic balance reduces EMI is documented in Section 3.2.

In addition to schematic balancing through circuit symmetry, an investigation into the physical circuit orientation and physical circuit symmetry shall be investigation to determine the efficacy on EMI mitigation. The investigation into physical orientation and achieving physical layout symmetry shall be noted as Geometric Symmetry henceforth.

## 3.2 BALANCED CONVERTER THEORY

The theory and methods to schematically balance a converter and the subsequent mitigating effects on EMI are discussed in this Section.

The theory covered within Section 3.2 covers schematic balance and the application to converters where schematic balance pertains only to balancing parasitic components by certain methods and disregards the physical construction or 3D layout of the circuit. Geometric balance in contrast, pertains to achieving Geometric Symmetry of the physical converter and is discussed further within Section 3.4. No reference to physical circuit balance (also called Geometric Symmetry or Geometric Balance) is presented within [9], nor the construction of a physically balanced circuit.

#### 3.2.1 Principles of Operation of an Unbalanced Converter

The processes by which an unbalanced converter generates EMI are discussed here.

#### 3.2.1.1 Unbalanced Circuits and CM

To illustrate the method by which a foundation for predominantly CM EMI generation through unbalance is illustrated in Figure 3-1. Taking the example of a classic converter, the boost converter, which illustrates a single parasitic capacitance present (the Drain to ground capacitance), which is typically not considered or known of during normal design procedures.

Figure 3-1 Boost Converter Illustration CM EMI Generation [9]

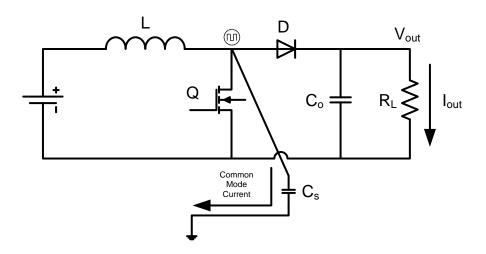

The presence of such parasitic components during the operation of a converter provides a conduction path for high frequency currents between the drain of the switch Q and ground as discussed in section 2.3.3. As is typical with boost converters, the Source of the switch is connected only to the negative of the supply. No parasitic component with reference to ground and the Source of switch Q are present.

The circuit within Figure 3-1 is said to be Unbalanced due to the absence of an identical parasitic capacitance between the Source of switch Q and ground, which would make the circuit schematically balanced.

#### 3.2.1.2 Foundation for Common Mode EMI Generation process through Unbalance

As is present in Figure 3-1 and discussed within Section 3.2.1.1, an unbalance in voltage is present across switch Q.

The voltage present at the node (Drain) is due to the presence of the inductor L within the boost converter. The inductor naturally has a high frequency impedance and through the high frequency switching of the switch Q, a high frequency current is drawn through Q and hence through L. Due to the impedance of L and the high frequency current drawn through L a high frequency voltage across L is present.

As the Drain of Q is at the same node as the inductor L, a high frequency voltage is thus present at the drain of Q. The presence of the parasitic capacitance  $C_s$  thus provides a path to ground and hence a Common Mode Current can flow through a ground return path to the supply.

Figure 3-2 illustrates a simplified representation of a boost converter circuit to highlight the CM Current path when connected to a LISN in order to measure CM currents.

Figure 3-2 Simplified Boost Converter CM Path [9]

#### 3.2.2 Balancing a Converter

The process by which a converter is schematically balanced and the resulting reduction primarily in CM EMI is discussed. The method to achieve schematic balance is illustrated.

#### 3.2.2.1 Schematically Balancing a Converter

As discussed, Figure 3-1 was said to be schematically unbalanced. Figure 3-3 illustrates the conduction path available in Figure 3-1 provided by the parasitic components as discussed in section 3.2.1.

Figure 3-3 Unbalanced Boost Converter [9]

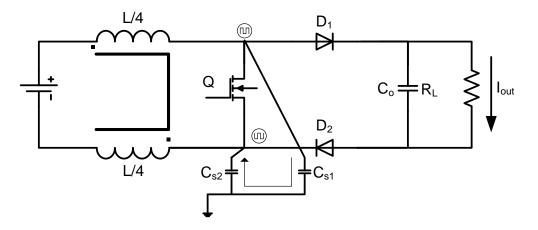

In order to mitigate the common mode EMI generated within the circuit illustrated in Figure 3-3, the method of schematically balancing a circuit is presented in Figure 3-4.

Figure 3-4 Balanced Boost Converter [9]

Figure 3-4 is said to be Schematically Balanced according to [1] and [9]. The balance of the boost converter is achieved by maintaining "symmetry" about an imaginary horizontal dividing line in the case of a boost converter. By maintaining said symmetry the converter becomes balanced. The reasoning behind how the process achieves said balance is discussed in section 3.2.2.2.

In the example of a boost converter, balance is achieved by the addition of D2 to provide a mirroring diode to D1. The inductor for the boost converter is then split into two but kept on the same core. The total inductance however remains identical to the inductance in Figure 3-3 to maintain identical converter operation.

#### 3.2.2.2 Process by which balancing has a mitigating effect on EMI

In Figure 3-4, the process by which schematic balance is achieved has been shown, and in Section 3.2.1.2, the process by which EMI is generated through unbalance.

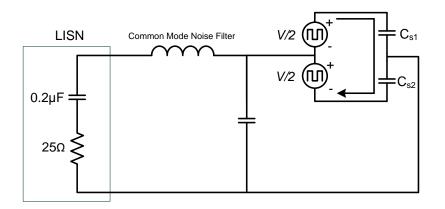

Figure 3-5 illustrates a simplified version of Figure 3-4 where the EUT (Equipment Under Test) is connected to a LISN.

Figure 3-5 Simplified Balanced Boost Converter CM Path [9]

By creating a mirrored or symmetric circuit in Figure 3-4 there is now present an additional diode D2 and inductor within the circuit. The converter operation as normal generates the voltages at the upper node to cause common mode currents to flow. The addition of the inductor on the negative rail introduces an inductance identical to the inductance of the positive rail.

Due to high frequency currents and impedances within the inductor, during normal operation of the converter, equal but opposite voltages across the inductors will be present as discussed in section 3.2.1.2. The addition of the diode D2 within Figure 3-4 gives rise to the additional parasitic component  $C_{s2}$ .

The equal but opposite voltage waveforms present at the Drain of Q and Source of Q in conjunction with the addition of parasitic impedance  $C_{s2}$  provides a conduction path for the common mode current in such a manner that the currents circulate within the converter circuit as illustrated, thus being short circuited within the converter and not allowed to circulate through a ground-path.

The process of containing the Common Mode currents within the converter reduces the Common Mode EMI generated by the converter through the action of prohibiting the Common Mode EMI from being emanating from the converter. Through the process of preventing Common Mode EMI emanation, Common Mode EMI is mitigated as conducted EMI is reduced which can lead to a reduction in Radiated EMI.

#### **3.3 BALANCED CONVERTER EXAMPLES**

The section within discusses other conventional converters and their schematically balanced counterpart circuits and how to modify such circuits to achieve schematic balance.

#### 3.3.1 Boost Converter

Figure 3-6 illustrates a conventional unbalanced boost converter.

Figure 3-6 Conventional Boost Converter [9]

Figure 3-7 illustrates a schematically balanced boost converter.

Figure 3-7 Balanced Boost Converter [9]

The schematic balance of a boost converter is achieved by the addition of an additional diode in the opposite direction to the original and by splitting up the boost inductor into two inductors on the same core, with orientation as illustrated to maintain normal operation of the original converter.

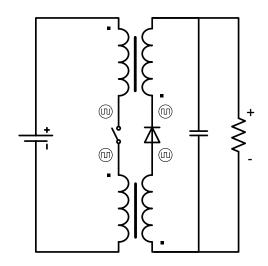

#### 3.3.2 Buck-Boost Converter

Figure 3-8 illustrates a conventional schematically unbalanced two winding buck-boost converter. In comparison to Figure 3-6 there are similarities in the circuit structure and hence the unbalance mechanisms which Common Mode EMI arises from, which includes a single switch and diode.

Figure 3-8 Conventional Buck-Boost Converter (Two Windings) [9]

Figure 3-9 illustrates the schematically balanced counterpart circuit to Figure 3-8, the balanced two – windings buck-boost converter.

Figure 3-9 Balanced Buck-Boost Converter (Two Windings) [9]

Similarly with the conventional boost converter, the balance on the primary side of a buckboost converter is achieved by the splitting of the primary side of the inductor into two separate inductors on the same core with the orientation as illustrated in Figure 3-9. The splitting of the inductor into two thus provides a complimentary voltage across the switch which in turn leads to the circulation of Common Mode currents within the parasitic components within the circuit and thus no Common Mode currents flow through the groundpath.

To achieve balance on the secondary side and to maintain identical converter operation, the inductor once again is split into two separate inductors on the same core oriented in a fashion as illustrated in Figure 3-9. Similarly with the secondary side of the buck-boost converter, the separation of the secondary inductor into two causes a complimentary voltage across the diode and hence allows the generated Common Mode currents to circulate within the secondary side rather than flowing through the ground return path.

In the case of a buck-boost converter, schematic balance is achieved without the addition of components but rather the winding scheme of the coupled inductor.

## 3.3.3 Naturally Balanced Converters (Schematically)

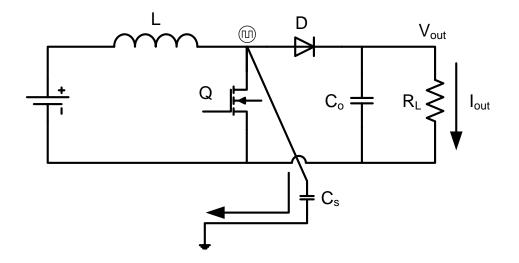

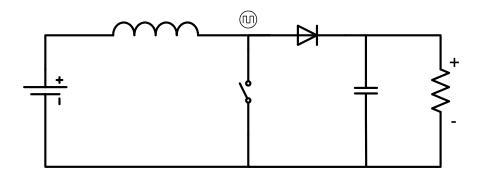

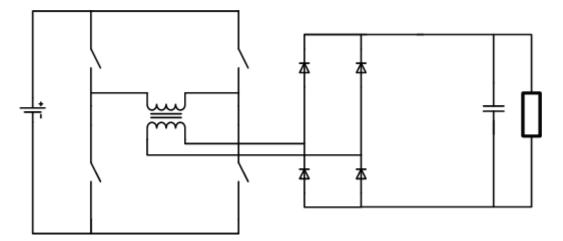

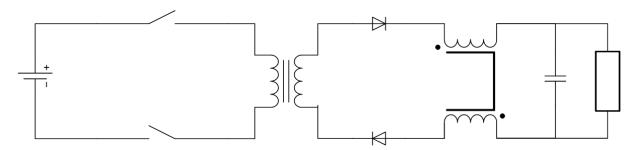

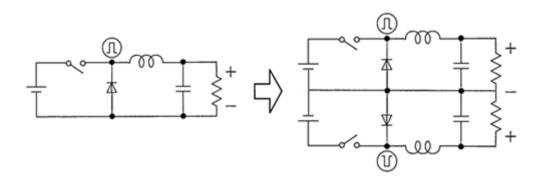

Figure 3-10 illustrates a full bridge converter and a full bridge rectifier circuit.

Figure 3-10 H-Bridge Converter and Full-Bridge Rectifier

A full-bridge (H-bridge) converter and a full-bridge rectifier circuit are naturally balanced such as they need zero additional components or modified inductor or transformer winding strategies to achieve schematic balance. The need for no additional components or winding strategies makes the circuits desirable candidates for circuits with naturally mitigated Common Mode EMI. Therefore this H-bridge topology will be used for experimental purposes in this study.

Section 3.5.1 thus discusses the details behind the natural circuit balance and the halfcycle analysis of an H-bridge converter and shows how it is naturally schematically balanced.

# 3.4 PHYSICAL LAYOUT BALANCE (GEOMETRIC SYMMETRY)

The following section discusses Geometric Balance or Geometric Symmetry, the physical layout symmetry and the application thereof to the converters and the possibility of EMI mitigation.

## 3.4.1 Hypothesis

The evidence of Schematically Balancing a circuit shows theoretical promise to mitigate Common Mode EMI to some extent [9], however no reference is presented where the physical construction of a Geometrically Symmetrical implementation of any converter or the mitigating effects if any are discussed.

An investigation into balancing a circuit or converter physically by means of orientation of components within the layout is speculated to aid in the mitigating effect primarily of Common Mode but also Differential Mode EMI.

The physical layout balance shall be denoted as Geometric Symmetry henceforth.

#### 3.4.1.1 Physical Layout Symmetry

Firstly in order to achieve Geometric Symmetry, the use of a Schematically Balanced circuit is to be used.

The physical placement of components within the physical circuit (circuit layout), shall be in such an orientation as to form a mirror image of the circuit if an imaginary mirror line is to be drawn through the circuit.

The symmetry is not limited to a single plane only as the circuit may be symmetrical in a vertical and horizontal plane.

## 3.4.2 Electromagnetic Perspective

Through circuit Geometric Symmetry, it is speculated that through orientation of components, electromagnetically there is a possibility of electromagnetic cancellation through correct placement of components.

Switch pairs within a phase arm placed back to back on different sides of a Printed Circuit Board (PCB) are speculated to have a mitigating EMI effect, as this is speculated to reduce the effective coupling area presented to the ground plane.

In EMI, wires or traces are not just conductors and need to be considered holistically as they are a combination of inductance, capacitance and resistance [14].

# 3.5 **PROPOSED DESIGN**

The following section discusses the proposed design of multiple circuit layouts to evaluate the hypothesis of Geometric Symmetry and the mitigating effect on EMI.

## 3.5.1 H-Bridge Converter and Full Bridge Rectifier Circuit

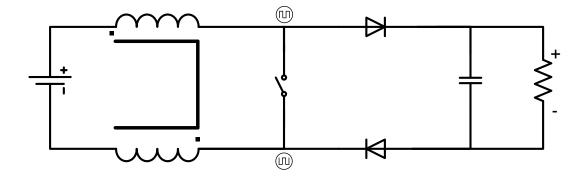

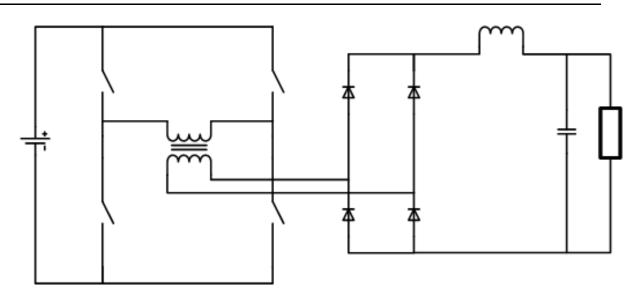

Figure 3-11 represents a Full-Bridge converter and Full-Bridge rectifier circuit with output filter and load.

The circuit in Figure 3-11 during operation is nearly naturally Schematically Balanced and therefore a good candidate for testing the hypothesis of Geometric Symmetry as minimal circuital change is required.

Figure 3-11 H-Bridge Converter and Full-Bridge rectifier with output filter

Section 3.5.1.1 discusses half cycle analysis to illustrate the inherent balance of the converter.

#### 3.5.1.1 Naturally Balanced Circuit

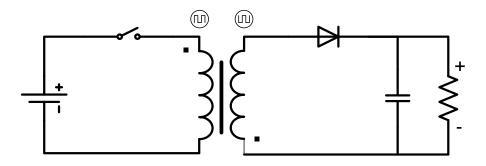

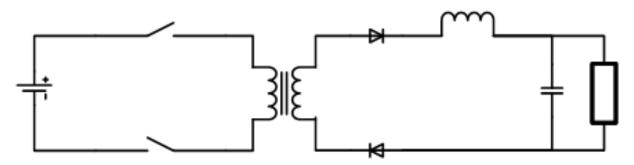

Figure 3-12 represents the half cycle analysis of the circuit in Figure 3-11.

Figure 3-12 Half -Cycle analysis of Full-Bridge converter and Full-Bridge rectifier

During normal circuit operation, only a single diagonal phase arm operates and only two rectification diodes conduct to form the circuit as illustrated in Figure 3-12.

The circuit in Figure 3-12 is almost a Schematically Balanced circuit with the exception of the output filter inductor as highlighted in Figure 3-13.

Figure 3-13 Output Filter Unbalanced Component

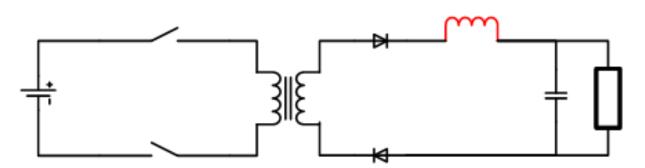

In order for Figure 3-13 to be Schematically Balanced, the output filter inductor needs to be changed in a manner to aid schematic balance.

Similarly as in section 3.3.1, the output inductor needs to be split into two but remain on the same core as to facilitate schematic balance. Figure 3-14 illustrates the half-cycle analysis with the split output filter inductor to achieve said schematic balance.

Figure 3-14 Schematically Balanced Full-Bridge Converter with Full-Bridge Rectifier and output filter

If the circuit in Figure 3-11 is absent of the output filter inductor as in Figure 3-10, the circuit is naturally Schematically Balanced and hence no further circuit modification is required to achieve said balance.

#### 3.5.1.2 Symmetrical Physical Layout Potential

The natural Schematic Balance of the circuit in Figure 3-10 aids itself in the requirement of testing the hypothesis in section 3.4.1. The natural Schematic Balance means there are no complicated components added or the need for complicated trace layouts.

Due to there being even multiples of components where more than a single component is present in the circuit facilitates Geometric Symmetry and the testing thereof as the ability to form a physically mirrored circuit is much more easily obtainable.

#### 3.5.2 Physical Layout

To test the hypothesis discussed in section 3.4.1, a selection of differing physical circuit implementation layouts of the circuit in Figure 3-10 are developed and discussed here.

#### 3.5.2.1 Circuit 1

Circuit 1 forms the baseline circuit upon where no knowledge or consideration for circuit layout shall be demonstrated. Circuit 1 shall be constructed on Veroboard to demonstrate lack of layout consideration with particularly large track loops and MOSFET spacing.

Through-hole components are to be utilised.

#### 3.5.2.2 Circuit 2

Circuit 2 forms the second baseline circuit where there is no major particular attention paid to layout symmetry, but rather a typical layout where the switching components in the circuit are laid out adjacent to each other on the same plane.

Circuit 2 is to be absent of a ground-plane or top copper pour layer. Surface mount semiconductors are to be used.

#### 3.5.2.3 Circuit 3

Circuit 3 forms a test platform where the circuit is split into two circuit boards where a phase arm is present on one PCB and the other on a different PCB.

The PCBs are to be joined in such a way as to be perpendicular to each other. One PCB shall have a ground pour on the bottom plane and the second PCB to be absent of the ground pour. Both PCBs are to be absent of a top copper pour.

Circuit 3 is designed to illustrate more than just symmetry and the effects on EMI but to illustrate the phenomena of coupling and Common Mode EMI. Surface mount semiconductor devices are to be used for Circuit 3.

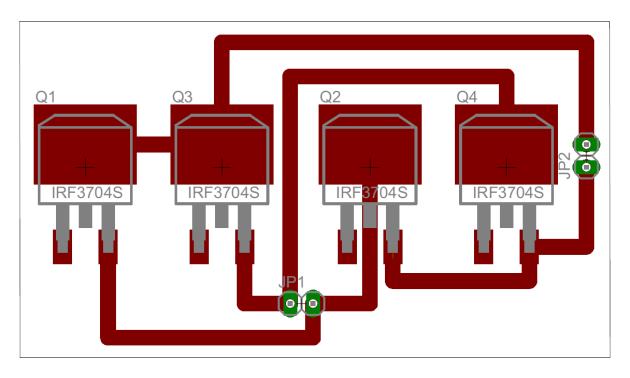

## 3.5.2.4 Circuit 4

Circuit 4 is the circuit with a Geometrically Symmetrical layout.

The circuit is to be designed such that the circuit is physically symmetrical in context of component locality and trace layout.

Circuit 4 shall be void of any ground pours or top copper pours. Circuit 4 shall use surface mount semiconductor devices.

# **3.6** CONCLUSION

The concept and introduction of balanced converters have been introduced. The theory pertaining to Schematically Balancing a converter and why a converter is termed schematically unbalanced from an EMI perspective. The process of Schematically Balancing a converter is presented and the mitigating effect which Schematic Balance has on EMI is presented. Examples of Schematically Balancing a converter have been presented, which includes naturally balanced examples. The concept of Geometric Symmetry has been introduced through physical layout symmetry of a circuit or PCB. The proposed design for the dissertation has been documented where four separate PCB's are to be designed and implemented to demonstrate various EMI mitigating or aggravating techniques. One of the said designs includes a Geometrically Symmetrical layout. The relevant design and implementation process is documented within Chapter 4.

# **4 DESIGN AND IMPLEMENTATION**

# 4.1 INTRODUCTION

Section 4 entails the design and implementation of the Printed Circuit Boards as discussed in section 3.5.2. Design specifics pertaining to achieving a repeatable test setup and relevant supporting circuit specifications and their appropriate design are also detailed within this section.