# Analysis of bias stress on thin-film transistors obtained by Hot-Wire Chemical Vapour Deposition

D.K. Dosev\*<sup>1,2</sup>, J. Puigdollers <sup>1</sup>, A. Orpella<sup>1</sup>, C. Voz<sup>1</sup>, M. Fonrodona<sup>3</sup>, D. Soler<sup>3</sup>, L.F. Marsal<sup>2</sup>, J. Pallarès<sup>2</sup>, J. Bertomeu<sup>3</sup>, J. Andreu<sup>3</sup> and R. Alcubilla<sup>1</sup>

#### Abstract

The stability under gate bias stress of unpassivated thin-film transistors was studied by measuring the transfer and output characteristics at different temperatures. The active layer of the devices consisted on nano-crystalline silicon deposited at 125°C by Hot-Wire Chemical Vapour Deposition. The dependence of the sub-threshold activation energy on gate bias for different gate bias stress is quite different from that reported for hydrogenated amorphous silicon. This behaviour has been related to the charge trapped in the active layer of the thin-film transistor.

Keywords: TFT, nano-crystalline silicon, HWCVD, Stability.

## 1. Introduction

Hot-Wire Chemical Vapour Deposition (HWCVD) is one of the most promising techniques to obtain hydrogenated amorphous silicon (a-Si:H) and hydrogenated nanocrystalline silicon (nc-Si:H) at low substrate temperatures (<300°C) over large areas and high deposition rates (>1nm/s)[1-3].

Hydrogenated nanocrystalline silicon obtained by HWCVD is composed of small silicon crystallites, with an average grain size of a few nanometers embedded in an amorphous silicon matrix. As a result, nc-Si:H properties lay between those of a-Si:H and polysilicon (with grain sizes of few micrometers).

Hydrogenated amorphous silicon thin-film transistors (TFT) are widely used in liquid crystal displays and matrix image sensors. However a-Si:H TFTs present electrical instability, mainly consisting of a threshold voltage ( $V_t$ ) shift, when a gate voltage is applied for a prolonged period of time. Two mechanisms contribute to threshold voltage instability: charge trapping in the gate insulator and defect creation in the band-gap of a-Si:H [4].

In this paper, the stability of TFTs with nc-Si:H active layers deposited at 125°C by HWCVD is studied. The stability was investigated by examining the gate transfer characteristics and the dependence of the subthreshold current activation energy on gate bias for as-deposited samples and after negative and positive bias stress.

<sup>&</sup>lt;sup>1</sup> Departament d'Enginyeria Electrònica, Universitat Politècnica de Catalunya, Jordi Girona 1–3 Mòdul C4, 08034-Barcelona, Spain.

<sup>&</sup>lt;sup>2</sup> Departament d'Enginyeria Electrònica, Universitat Rovira i Virgili, Tarragona, Spain <sup>3</sup> Departament de Física Aplicada i Electrònica, Universitat de Barcelona, Barcelona, Spain.

<sup>\*</sup> Corresponding author: tel. +34 977 558236; fax: +34 977 559605; e-mail: ddosev@etse.urv.es

# 2. Experimental

Nano-crystalline TFT's were deposited by HWCVD by using an ultra-high-vacuum multichamber set-up described elsewhere [5]. Processing gases [silane-hydrogen mixture (4/76 sccm)] were catalytically dissociated by a tungsten wire heated at 1700°C. Substrate temperature was around 125°C (measured by a thermocouple attached to the heater) and the process pressure was  $1\times10^{-2}$  mbar. Under these conditions the deposition rate was 0.6 nm/s. Thin-film transistors used in this work are inverted staggered structures without top passivation layer. A thermally oxidised n-type (100) silicon wafer with a resistivity of 1-10  $\Omega$ ·cm was used as substrate. Thicknesses were 250 nm for the active layer and 250 nm for the silicon dioxide. An n<sup>+</sup>-doped layer (50 nm) between the drain and source contacts and the intrinsic layer was also deposited by HWCVD.

Finally a chromium layer was thermally evaporated and the metallic contacts (drain and source) were delimited by photolithographic techniques. The channel width was 137  $\mu$ m and the length 55  $\mu$ m, giving an aspect ratio for the device (i.e. W/L) of 2.5. Details on the fabrication process have been reported in a previous work [6].

Different TFTs were electrically characterised by measuring the transfer and output characteristics. We also studied the dependence of the subthreshold current activation energies  $(E_{ACT}=E_C-E_F)$  on gate bias. After the initial characterisation of the samples, stressing processes at different gate voltages  $(\Box 40, \ \Box 20 \ \text{and} + 40 \ \text{V})$  were performed at room temperature (298 K) for 1000 s. All the measurements were performed under dark conditions by using a Hewlett  $\Box$  Packard HP4145B semiconductor parameter analyser and a temperature controlled chuck.

## 3. Results and discussion.

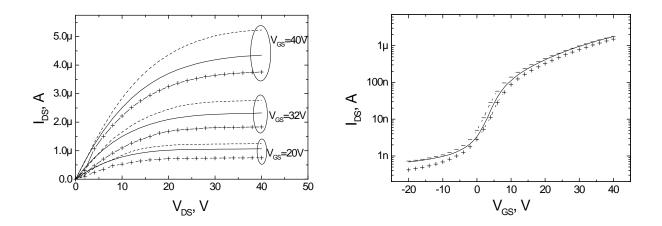

The output and transfer characteristics of the transistors as deposited and after positive and negative gate bias stress are shown in Fig. 1a. From the output characteristics  $I_{DS}$  vs.  $V_{DS}$  it can be seen that there is not a current crowding and as a consequence we conclude that the influence of the source and drain contact resistance is not important in our devices. The absence of the Kink effect (a rapid rise of  $I_{DS}$  at high  $V_{DS}$ ) indicates that the electron injection at the contacts is very small. The transfer characteristics in saturation regime were measured to determine the threshold voltage and the field effect mobility of the transistors. A threshold voltage of 6.9 V and field effect mobility of

$0.3~\text{cm}^2/\text{V}\cdot\text{s}$  were obtained. After gate bias stress, a positive shift of threshold voltage ( $\Delta V_t \approx +1~\text{V}$ ) for positive gate bias stress and a negative shift ( $\Delta V_t \approx -1~\text{V}$ ) for negative gate bias stress were obtained.

The application of a gate voltage in field effect structures shifts the Fermi level inside the gap. This displacement allows us to study the electronic properties of the material. The rate at which EF moves towards the conduction band (in n-channel devices) depends on the density of states located in the band gap and on the distribution of tail states close to the conduction band. For small values of  $V_{GS}$  the Fermi level is located in deep states. Increasing  $V_{GS}$  shifts the Fermi level to the conduction band, and the tail band states become important. Besides, for high positive  $V_{GS}$  applied an influence of the amorphous phase in the nucleation region of the crystallites could not be discarded.

It has been reported (experimentally as well as through simulation results) [7,8] that for hydrogenated amorphous silicon, the application of a negative gate bias create additional states in the upper half part of the bandgap. This additional peak on the density of states leads to a reduction

of the slope of  $E_{ACT}(V_{GS})$  for  $V_{GS}$ <10 V, indicating the presence of defect states created by degradation.

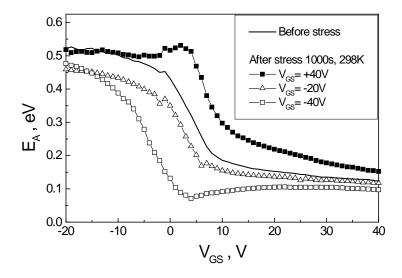

In Fig. 2 the dependence of  $E_{ACT}$  on  $V_{GS}$  for TFTs before and after bias stress degradation is shown. For the as-deposited sample we observe that the Fermi level moves from around midgap ( $E_{ACT}$  =0.45 eV for  $V_{GS}$ =0 V) to the conduction band, remaining nearly constant at approximately 0.15 eV, where the Fermi level is pinned by the band tail states.

Fig. 1. Output and transfer characteristics of nano-crystalline TFT measured as-deposited (solid lines) and after different gate bias stress:  $V_{GS} = +40 \text{ V}$  (- symbols),  $V_{GS} = -40 \text{ V}$  (+ symbols).

In Fig. 2 it is observed that the application of positive (negative) bias stress to the gate leads to a positive (negative) displacement of the  $[E_{ACT}(V_{GS})]$  characteristics. The shift obtained after the application of negative gate bias stress is in opposite direction to the one observed for a-Si:H TFTs after a similar degradation process [8].

Fig.2. Dependence of the activation energy ( $E_{ACT} = E_{C} - E_{F}$ ) of the sub-threshold transfer characteristics for TFT stressed at different gate biases.

We believe that the application of positive/negative bias stress to the gate causes redistributions in the trapped charge of the active layer in the TFT. Negative stress, for example, depletes the trapped charge between EF and the conduction band, causing the Fermi level to be slightly shifted towards the conduction band. Therefore, the application of small values of  $V_{GS}$  easily shifts the  $E_F$  to the conduction band, remaining fixed by the band-tail states. This charge trapped could be related to the impurities (oxygen, copper,...) incorporated in the layer during the deposition process [9].

The transistors were measured again 50 h after the stressing process. They showed the same characteristics as before the stressing process including threshold voltage and activation energy, these results also seem to confirm that charge trapping could be the main mechanism involved by the application of gate bias stress.

### 4. Conclusions

In this work we have presented the results of stress treatment of TFT's with nano-crystalline active layer fabricated at low temperature (125°C) by HWCVD process. The results indicate that changes in the electrical characteristics of the device could be due to temporarily trapped charge in the material. In our future work detailed analysis of the interface states in the transistors by capacitance measurements will be performed.

# Acknowledgements

The authors wish to thank Dr. L. Fonseca from Centre Nacional de Microelectrònica for growing the silicon dioxide. This work was supported by the CICYT of the Spanish Government under programme TIC1999-0842.

### References

- [1] H. Matsumura, Jpn. J. Appl. Phys. 30 (1991) L1522.

- [2] J. Cifre, J. Bertomeu, J. Puigdollers, M.C. Polo, J. Andreu, A. Lloret, Appl. Phys. A 59 (1994) 645.

- [3] H. Meiling, R.E.I. Schropp, Appl. Phys. Lett. 69(8) (1996) 1062.

- [4] M. J. Powell, Appl. Phys. Let. 53 (1983) 2753.

- [5] D. Peiró, PhD Thesis, University of Barcelona (1999).

- [6] J. Puigdollers, A. Orpella, D. Dosev, C. Voz, D. Peiró, J. Pallarès, L.F. Marsal, J. Bertomeu, J. Andreu, R. Alcubilla, J. Non-Cryst. Solids 266-269 (2000) 1304.

- [7] M.J. Powell, S.C. Deane and W.I. Milne, Appl. Phys. Lett. 60 (2) (1992) 207.

- [8] H. C. Slade and M.S. Shur, IEEE Trans on Elec. Dev., 45 (7) (1998) 1548-1553.

- [9] C. Voz, M. Fonrodona, D. Soler, D. Peiró, J.M. Asensi, J. Bertomeu, J. Andreu, Proceedings of 16th European Photovoltaic Solar Energy Conference, 2000 Glasgow, in print.