## Technical University of Denmark

## Low Power High Dynamic Range A/D Conversion Channel

Marker-Villumsen, Niels; Bruun, Erik; Rombach, Pirmin

Publication date: 2015

Document Version Publisher's PDF, also known as Version of record

Link back to DTU Orbit

*Citation (APA):* Marker-Villumsen, N., Bruun, E., & Rombach, P. (2015). Low Power High Dynamic Range A/D Conversion Channel. Technical University of Denmark, Department of Electrical Engineering.

#### DTU Library Technical Information Center of Denmark

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Niels Marker-Villumsen

# Low Power High Dynamic Range A/D Conversion Channel

PhD Thesis, August 2015

**DTU Electrical Engineering** Department of Electrical Engineering

Niels Marker-Villumsen

## Low Power High Dynamic Range A/D Conversion Channel

PhD Thesis, August 2015

Author:

Niels Marker-Villumsen

#### Supervisors:

Erik Bruun (*DTU Elektro*) Pirmin Rombach (*EPCOS AG*)

Department of Electrical Engineering Electronics Group Technical University of Denmark Elektrovej building 325 DK-2800 Kgs. Lyngby Denmark

www.ele.elektro.dtu.dk Tel: (+45) 45 25 38 00 Fax: (+45) 45 88 01 17 E-mail: hw@elektro.dtu.dk

| Release date: | 29 August 2015                                                                                                                                 |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Category:     | 1 (Public)                                                                                                                                     |

| Edition:      | First                                                                                                                                          |

| Comments:     | This thesis is submitted in partial fulfillment of the requirements<br>for obtaining the PhD degree at the Technical University of<br>Denmark. |

| Rights:       | © Niels Marker-Villumsen, 2015                                                                                                                 |

To Marianne, Karen and Viggo

This thesis is submitted in partial fulfillment of the requirements for obtaining the PhD degree from the Technical University of Denmark. The project has been carried out as an Industrial PhD project in collaboration with DTU Electrical Engineering and the SAW Design Center Denmark, part of the SAW Business Group of EPCOS AG. The project was supervised by Professor Erik Bruun and company supervisor Pirmin Rombach in the period from March 2012 to August 2015, including 26 weeks of leave from the project. The project was partially by EPCOS AG and partially by Innovation Fund Denmark through the Industrial PhD program.

Although the life as a PhD student is an example of pure self-management, the project could not have been completed without the help and support of several people. I would like to spent this opportunity to thank all of you.

- A very special thank you to Erik Bruun, for the support and assistance throughout the entire duration of the project. You have been an inspiration, a great mentor, and someone who I could always discuss my problems with, whether professional or private.

- A very special thank you to Pirmin Rombach and EPCOS AG, for allowing me to carry out this Industrial PhD project with EPCOS AG, for financing the tape-out of the test IC, and for all the support and help during the project.

- A thank you to Ivan H. H. Jørgensen for always being available for both technical and non-technical discussions. It has been a real pleasure.

- A thank you to Gino Rocca for the technical discussions along the way, and for handling the practical parts of the tape-out.

- A thank you to Johann Hauer from Fraunhofer IIS, Erlangen, Germany, for hosting my external research stay. It was an inspirational stay in Franconia.

- A thank you to Henriette D. Wolff for help with handling the bureaucracy at DTU, and for the hard work of keeping the ELE group running smoothly.

- A thank you to Allan Jørgensen for technical assistance with the development tools, both at DTU and at EPCOS.

- A special thank you to Tomasz Marczak for the tremendous effort in getting the layout ready for the tape-out of the test IC.

- A thank you to Rene Grundahl Pedersen for assistance with the design and production of the test PCB.

- A thank you to Sébastien Santurette for assistance with planning and preparing the listening tests.

- A thank you to my colleagues at the EPCOS SAW Design Center Denmark and Poland, for the assistance, support, and for keeping up the spirit.

- A thank you to all the PhD students and personnel in the ELE group, for all the help and for making my time in the group a memorable one.

- A big thank you to Pere Llimós Muntal and Dennis Øland Larsen for all the technical discussions, non-technical discussions, general discussions, all other discussions, for keeping the arrows pretty, and just doing it. BILF forever!

- A thank you to my family for the help, love and support during the project.

- A thank you to all my friends who throughout the project have shown interest, and also shown that there is more to life than just the PhD project.

- Finally, a very special thank you to my dear wife Marianne, and my children Viggo and Karen, for always being around; for supporting me through thick and thin, even when the going got tough. My life would not be the same without you, and I am forever in your debt.

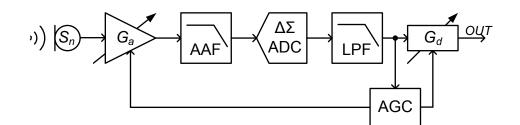

This work concerns the analysis of an adaptive analog-to-digital (A/D) conversion channel for use with a micro electromechanical system (MEMS) microphone for audio applications. The adaptive A/D conversion channel uses an automatic gain control (AGC) for adjusting the analog preamplifier gain in the conversion channel in order to avoid distortion for large input signals. In combination with a low resolution A/D converter (ADC) and a digital gain block, the adaptive A/D conversion channel achieves an extended dynamic range beyond that of the ADC. This in turn reduces the current consumption of the conversion channel in comparison to a static A/D conversion channel; this at the cost of a reduced peak signal-to-noise ratio (SNR).

The adaptive A/D conversion channel compensates for the change in analog gain by a digital gain, thus achieving a constant channel gain in the full dynamic range. However, this compensation results in the generation of audible transient errors in the conversion channel output. The adaptive conversion channel is modeled in order to analyze the factors that impact the performance of the conversion channel, including the generation of the transient error. To evaluate the audibility of the transient errors, an objective method based on the *Perceived Evaluation* of Audio Quality (PEAQ) method is investigated and compared with a subjective evaluation. The results of the evaluation provide key knowledge about the transient glitches from both a system and psychoacoustical point-of-view. Based on this knowledge, a new method is proposed for the reduction of the transient glitches, based on linear extrapolation of the channel output signal.

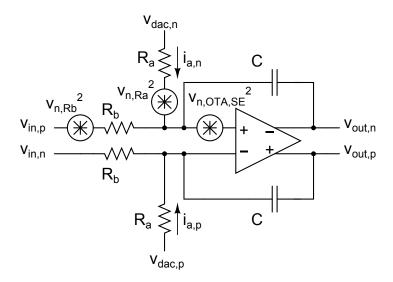

The design of a low power continuous-time (CT) Delta-Sigma ( $\Delta\Sigma$ ) ADC for use in the adaptive A/D conversion channel is also presented. When designing a CT  $\Delta\Sigma$  ADC, the choice of e.g. integrator topology, feedback waveform, feedback type, noise transfer function, and quantization levels, results in a large design space, both at the modulator and circuit level. A new optimization method is presented, that seeks to minimize the current consumption of the ADC. Based on an analysis of the modulator circuits and loopfilter, the optimization method determines a theoretical minimum current solution based on a set of performance requirements. Furthermore the use of current mode feedback in combination with active-RC integrators in the CT  $\Delta\Sigma$  ADC is investigated as a method for reducing the current consumption of the ADC, without sacrificing the noise performance of the ADC.

The main scientific contributions described in this thesis can be divided into two parts: contributions related to AGC audio systems, and contributions related to low power CT  $\Delta\Sigma$  ADC design. In the area of AGC audio systems, the main contributions are: an overview of the challenges in applying AGC to audio systems; a proposed objective method for evaluating the audibility of the transient glitches generated by the adaptive A/D conversion channel; and method for reducing the transient glitches generated by the adaptive A/D conversion channel.

In the area of low power CT  $\Delta\Sigma$  ADC design a substantial contribution is given. The presented optimization method and the use of current mode feedback identifies the possibilities of achieving a low power design by considering the modulator and circuit design as interdependent rather than two separate parts of the design. Denne afhandling vedrører analysen af en adaptiv analog-til-digital (A/D) konverteringskanal til anvendelse sammen med en mikro-elektromekanisk system (MEMS) mikrofon til audio brug. Med henblik på at undgå forvrængning af store indgangssignaler anvender den adaptive A/D konverteringskanal en automatisk forstærkningsstyring (AGC) til justering af forstærkningen af en analog forforstærker i konverteringskanalen. I kombination med en lav-opløsnings A/D konverter (ADC) og en digital forstærkerblok opnår den samlede adaptive A/D konverteringskanal et dynamikområde, som er større end ADC'ens eget dynamikområde.

Den adaptive A/D konverteringskanal kompenserer for ændringen i den analoge forstærkning via en digital forstærkning og opnår dermed en konstant kanalforstærkning i hele dynamik området. Imidlertid resulterer denne kompensering i generering af hørbare transiente fejl i udgangssignalet fra konverteringskanalen. Den adaptive konverteringskanal er blevet modelleret med henblik på at analysere de faktorer, der påvirker egenskaberne af konverteringskanalen, inklusiv genereringen af de transiente fejl. Til evaluering af hørbarheden af de transiente fejl er der udviklet en objektiv metode, baseret på *Perceived Evaluation of Audio Quality* (PEAQ) metoden. Metoden er blevet sammenlignet med en subjektiv evaluering baseret på lyttetests. Resultaterne heraf giver vigtig viden om de transiente fejl, både fra et systemperspektiv og fra et psykoakustisk perspektiv. På grundlag af denne viden foreslås en ny metode til reduktion af de transiente fejl. Metoden er baseret på lineær ekstrapolering af kanalens udgangssignal.

Afhandlingen omhandler også design af lav-effekt, kontinuert-tid (CT) Delta-Sigma ( $\Delta\Sigma$ ) ADC'er til anvendelse i den adaptive A/D konverteringskanal. Ved design af en CT  $\Delta\Sigma$  ADC fører valget af f.eks. integratortopologi, tilbagekoblingskurveform, støj-overføringsfunktion og antal kvantiseringsniveauer til et stort antal frihedsgrader, både på modulatorniveau og på kredsløbsniveau. Der præsenteres en ny optimeringsmetode til minimerering af strømforbruget af ADC'en. Baseret på en analyse af modulatorkredsløbene og sløjfefilteret bestemmer optimeringsmetoden en teoretisk løsning med et minimum af strømforbrug ud fra en række krav til øvrige specifikationer. Yderligere undersøges anvendelsen af strømbaseret tilbagekobling i kombination med *active-RC* integratorer til CT  $\Delta\Sigma$  ADC'en som en metode til reduktion af ADC'ens strømforbrug, uden at der gås på kompromis med ADC'ens egenstøj.

De væsentlige videnskabelig bidrag i dette ph.d. projekt kan opdeles i to dele: bidrag vedrørende AGC i audio systemer og bidrag vedrørende design af lav effekt CT  $\Delta\Sigma$  ADC'er.

Inden for AGC audio systemer er de primære bidrag følgende: (1) et overblik over udfordringerne ved anvendelse af AGC i audiosystemer; (2) en objektiv metode til evaluering af hørbarheden af de transiente fejl, der genereres i den adaptive A/D konverteringskanal; (3) en metode til reduktion af de transiente fejl i udgangen af den adaptive A/D konverteringskanal.

Inden for området omhandlende CT  $\Delta\Sigma$  ADC design er den udviklede optimeringsmetode et væsentligt bidrag. Denne metode samt anvendelsen af strømbaseret tilbagekobling viser, hvordan der er muligt at opnå et design med lavt strømforbrug ved at betragte design af modulator og kredsløb som indbyrdes afhængige opgaver fremfor som to separate dele af designet.

| 1        | Intr | oduction                       | n                                  | 1  |

|----------|------|--------------------------------|------------------------------------|----|

|          | 1.1  | Thesis C                       | Dutline                            | 3  |

| <b>2</b> | Ada  | ptive A                        | /D Conversion Channel              | 7  |

|          | 2.1  | Static A                       | /D Conversion Channel              | 7  |

|          | 2.2  | Adaptiv                        | e A/D Conversion Channel           | 9  |

|          | 2.3  | Constan                        | t Channel Gain                     | 11 |

|          | 2.4  | Automa                         | tic Gain Control                   | 13 |

|          |      | 2.4.1 A                        | AGC Loops                          | 14 |

|          |      | 2.4.2 F                        | Peak Detection                     | 15 |

|          |      | 2.4.3 A                        | Attack Level                       | 16 |

|          |      | 2.4.4 A                        | Attack Time                        | 19 |

|          |      | 2.4.5 F                        | Release Level                      | 19 |

|          |      | 2.4.6                          | Gain Levels and Steps              | 22 |

|          | 2.5  | Other S                        | ystem Blocks                       | 24 |

|          |      | 2.5.1 V                        | Variable Gain Amplifier            | 25 |

|          |      | 2.5.2 A                        | Analog-to-Digital Converter        | 26 |

|          |      | 2.5.3 H                        | Filters                            | 26 |

|          |      | 2.5.4 I                        | Digital Filters and Gain Block     | 27 |

|          | 2.6  | Summar                         | y                                  | 28 |

| 3        | Eva  | luation o                      | of Adaptive A/D Conversion Channel | 29 |

|          | 3.1  | Evaluati                       | ion of Audio Quality               | 29 |

|          | 3.2  | 3.2 Existing Objective Methods |                                    |    |

|          |      | 3.2.1 N                        | Mean Squared Error                 | 32 |

|          |      | 3.2.2 S                        | Structural Similarity Index        | 32 |

|          |      | 3.2.3 F                        | PEAQ MOVs                          | 33 |

|          | 3.3  | High-Le                        | vel Conversion Channel Model       | 35 |

|          | 3.4  | Test Sig                       | nals                               | 36 |

|   |                | 3.4.1             | Generation of Test Signals                    | 37 |

|---|----------------|-------------------|-----------------------------------------------|----|

|   |                | 3.4.2             | Scaling of Transient Glitch                   | 37 |

|   | 3.5            | Refere            | ence Listening Test                           | 40 |

|   |                | 3.5.1             | Alternative Forced Choice Test                | 40 |

|   |                | 3.5.2             | Up-Down Test Method                           | 41 |

|   |                | 3.5.3             | Conducting the Listening Tests                | 42 |

|   |                | 3.5.4             | Bias Errors                                   | 45 |

|   | 3.6            | Object            | tive Evaluation                               | 45 |

|   | 3.7            | Comp              | arison of Subjective and Objective Evaluation | 47 |

|   | 3.8            | Applic            | cability of Objective Method                  | 48 |

|   | 3.9            | Summ              | ary                                           | 49 |

| 4 | $\mathbf{Red}$ | luction           | n of Transient Glitches                       | 51 |

|   | 4.1            | Existi            | ng Methods                                    | 51 |

|   | 4.2            | Gain S            | Step Size                                     | 53 |

|   | 4.3            | Digita            | l Gain Adjustment                             | 54 |

|   | 4.4            | Zero (            | Crossing Gain Change                          | 55 |

|   | 4.5            | Glitch            | Reduction by Output Extrapolation             | 55 |

|   | 4.6            | Exten             | ded Conversion Channel Model                  | 57 |

|   | 4.7            | Evalua            | ation                                         | 59 |

|   |                | 4.7.1             | Constant Amplitude Sine Wave                  | 59 |

|   |                | 4.7.2             | Audio Signals                                 | 60 |

|   | 4.8            | Audib             | ility of Reduced Glitches                     | 66 |

|   | 4.9            | Summ              | ary                                           | 67 |

| 5 | Opt            | imum              | Design of Continuous-Time $\Delta \Sigma$ ADC | 69 |

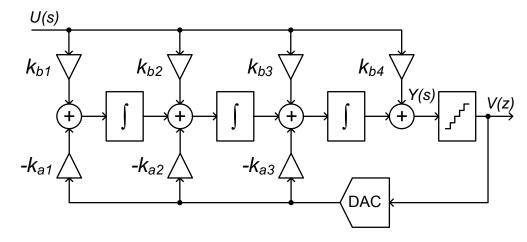

|   | 5.1            | $\Delta \Sigma$ M | lodulator Basics                              | 69 |

|   | 5.2            | Modul             | lator Design                                  | 72 |

|   |                | 5.2.1             | Oversampling Ratio                            | 72 |

|   |                | 5.2.2             | Loopfilter Order                              | 73 |

|   |                | 5.2.3             | NTF Corner Frequency                          | 73 |

|   |                | 5.2.4             | Quantization Levels                           | 74 |

|   |     | 5.2.5 Loopfilter Topology $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 74$ |  |  |

|---|-----|------------------------------------------------------------------------------------------------------|--|--|

|   |     | 5.2.6 Modulator Summary                                                                              |  |  |

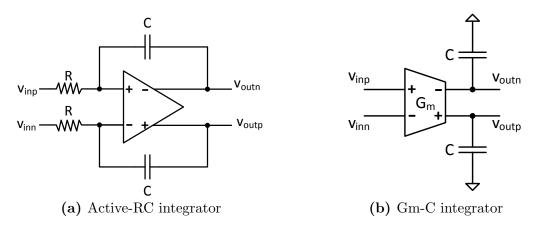

|   | 5.3 | Continuous-Time $\Delta\Sigma$ ADC                                                                   |  |  |

|   |     | 5.3.1 Integrator Topology                                                                            |  |  |

|   |     | 5.3.2 Feedback DAC                                                                                   |  |  |

|   | 5.4 | Optimum Design of Modulator and Circuits                                                             |  |  |

|   |     | 5.4.1 Loopfilter Coefficients                                                                        |  |  |

|   |     | 5.4.2 Noise of Integrator                                                                            |  |  |

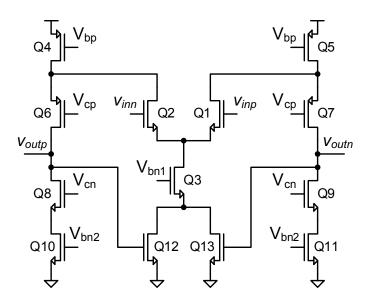

|   |     | 5.4.3 GBW and SR of Folded-Cascode OTA 87                                                            |  |  |

|   |     | 5.4.4 Noise of Folded-Cascode OTA                                                                    |  |  |

|   | 5.5 | Optimization Method                                                                                  |  |  |

|   |     | 5.5.1 Optimization Routine                                                                           |  |  |

|   | 5.6 | Design Example                                                                                       |  |  |

|   | 5.7 | Summary 96                                                                                           |  |  |

| 6 | Con | tinuous-Time $\Delta \Sigma$ ADC with Current Mode DAC 99                                            |  |  |

|   | 6.1 | Modulator Design                                                                                     |  |  |

|   | 6.2 | Current Mode DAC Noise 105                                                                           |  |  |

|   | 6.3 | Circuit Design                                                                                       |  |  |

|   |     | 6.3.1 Integrator                                                                                     |  |  |

|   |     | 6.3.2 Quantizer                                                                                      |  |  |

|   |     | 6.3.3 Current Mode DAC                                                                               |  |  |

|   | 6.4 | Tuning of STF 119                                                                                    |  |  |

|   | 6.5 | Other Circuit Considerations                                                                         |  |  |

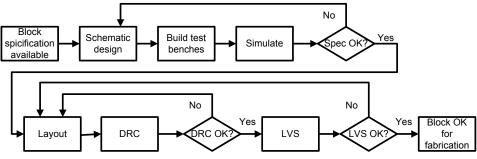

|   |     | 6.5.1 Layout Considerations                                                                          |  |  |

|   | 6.6 | Evaluation                                                                                           |  |  |

|   |     | 6.6.1 Simulation results                                                                             |  |  |

|   |     | 6.6.2 Measurements                                                                                   |  |  |

|   |     |                                                                                                      |  |  |

|   | 6.7 | Summary                                                                                              |  |  |

| 7 |     |                                                                                                      |  |  |

| 7 |     | Summary       138         aclusion       141         Future Work       143                           |  |  |

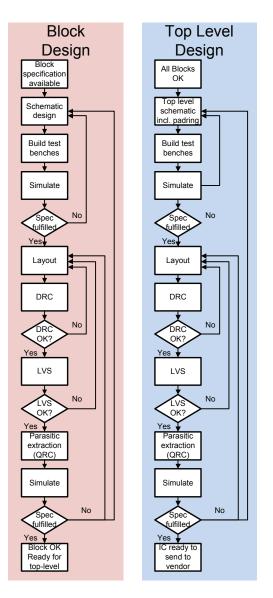

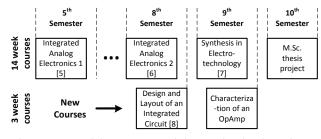

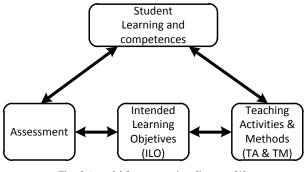

| 8  | Oth   | er Research Topics                                                                             | 145         |

|----|-------|------------------------------------------------------------------------------------------------|-------------|

|    | 8.1   | How To Implement an Experimental Course on Analog IC Design<br>in a Standard Semester Schedule | 145         |

|    | 8.2   | Increasing Generic Engineering Competences Using Coaching and<br>Personal Feedback             | 145         |

|    | 8.3   | Investigation of an AGC for Audio Applications                                                 | 146         |

| Bi | bliog | graphy                                                                                         | 147         |

| A  | ppen  | dix                                                                                            | 154         |

| A  | -     | ective Evaluation of the Audibility of Transient Errors in an aptive $A/D$ Conversion Channel  | ı<br>155    |

| в  | Cire  | cuit and Method of Operating a Circuit                                                         | 163         |

| С  | -     | imization of Modulator and Circuits for Low Power Continuo<br>ne Delta-Sigma ADC               | ous-<br>199 |

| D  |       | Power Continuous-Time Delta-Sigma ADC with Current<br>put DAC                                  | t<br>207    |

| Е  |       | v to Implement an Experimental Course on Analog IC Design<br>Standard Semester Schedule        | ı<br>213    |

| F  |       | reasing Generic Engineering Competences Using Coaching<br>Personal Feedback                    | g<br>221    |

| G  | Inve  | estigation of an AGC for Audio Applications                                                    | 233         |

## List of Abbreviations

| 3I2AFC | Three interval, Two Alternative Forced Choice   |

|--------|-------------------------------------------------|

| 3I3AFC | Three interval, Three Alternative Forced Choice |

| A/D    | Analog-to-Digital                               |

| AAF    | Anti Aliasing Filter                            |

| ADB    | Average Distorted Block                         |

| ADC    | Analog-to-Digital Converter                     |

| AGC    | Automatic Gain Control                          |

| AOP    | Acoustical Overload Point                       |

| CIFB   | Cascade of Integrators with Feedback            |

| CIFF   | Cascade of Integrators with Feedforward         |

| CMFB   | Common-Mode Feedback                            |

| CRFB   | Cascade of Resonators with Feedback             |

| СТ     | Continuous-Time                                 |

| DEM    | Dynamic Element Matching                        |

| DGB    | Digital Gain Block                              |

| DR     | Dynamic Range                                   |

| DT     | Discrete-Time                                   |

| ECM    | Electret Condenser Microphone                   |

| ENOB   | Effective number of bits                        |

| ESD    | Electrostatic Discharge                         |

| FIR    | Finite Impulse Response                         |

| FoM    | Figure-of-Merit                                 |

| GBW    | Gain-Bandwidth Product                          |

| IC     | Integrated Circuit                              |

| LPF    | Low-pass Filter                                 |

| MEMS   | Micro Electro Mechanical System                         |

|--------|---------------------------------------------------------|

| MFPD   | Mean Filtered Probability of Detection                  |

| MIM    | Metal-Insulator-Metal, in the context of MIM capacitors |

| MOSFET | Metal-Oxide-Semiconductor Field Effect Transistor       |

| MOV    | Model Output Variable                                   |

| MSA    | Maximum Stable Amplitude                                |

| MSE    | Mean Squared Error                                      |

| MUX    | Multiplexer                                             |

| NRZ    | Non-Return-to-Zero                                      |

| NTF    | Noise Transfer Function                                 |

| OpAmp  | Operational Amplifier                                   |

| OSR    | Oversampling Ratio                                      |

| OTA    | Operational Transconductance Amplifier                  |

| PCB    | Printed Circuit Board                                   |

| PDK    | Process Design Kit                                      |

| PDM    | Pulse Density Modulation                                |

| PEAQ   | Perceptual Evaluation of Audio Quality                  |

| PEX    | Parasitic Extracted                                     |

| PSD    | Power Spectral Density                                  |

| PVT    | Process, Voltage and Temperature                        |

| RZ     | Return-to-Zero                                          |

| SNDR   | Signal to Noise and Distortion Ratio                    |

| SNR    | Signal-to-Noise Ratio                                   |

| SPL    | Sound Pressure Level                                    |

| SR     | Slew Rate                                               |

| STF    | Signal Transfer Function                                |

| THD    | Total Harmonic Distortion                               |

| VGA    | Variable Gain Amplifier                                 |

|        |                                                         |

## List of Figures

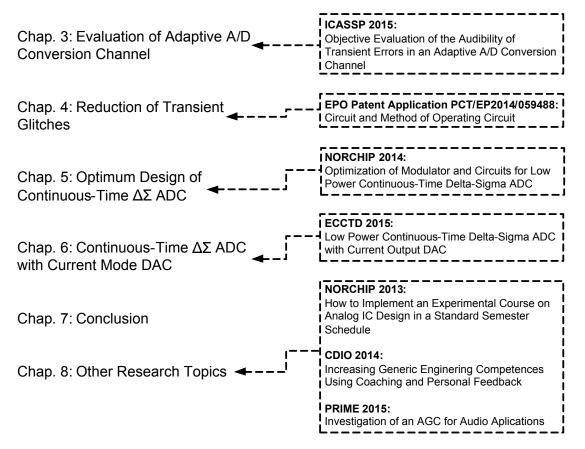

| 1.1  | Overview of thesis chapters and related publications                                                                                                                     | 5  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1  | Block diagram of static A/D conversion channel $\ . \ . \ . \ . \ .$                                                                                                     | 7  |

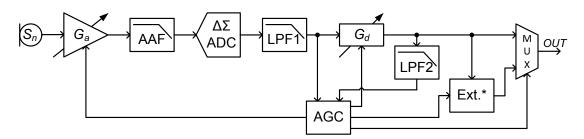

| 2.2  | Block diagram of adaptive A/D conversion channel $\ . \ . \ . \ .$                                                                                                       | 9  |

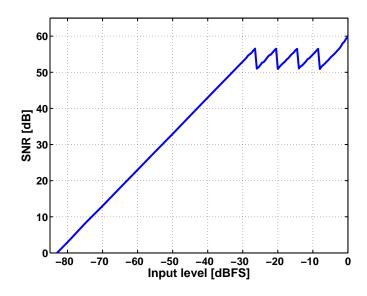

| 2.3  | Example of SNR as a function of the input level for the static and the adaptive A/D conversion channel                                                                   | 10 |

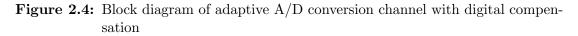

| 2.4  | Block diagram of adaptive A/D conversion channel with digital compensation                                                                                               | 11 |

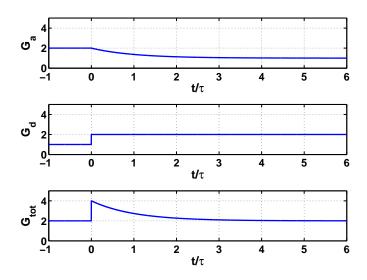

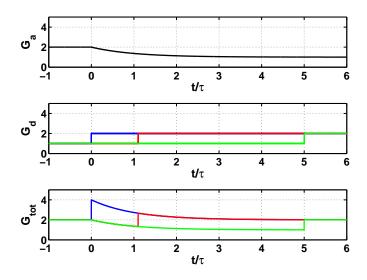

| 2.5  | Analog gain, digital gain and channel gain during adjustment event                                                                                                       | 12 |

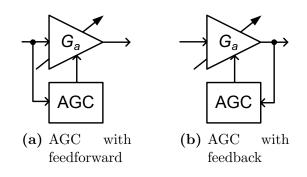

| 2.6  | Types of AGC loops                                                                                                                                                       | 14 |

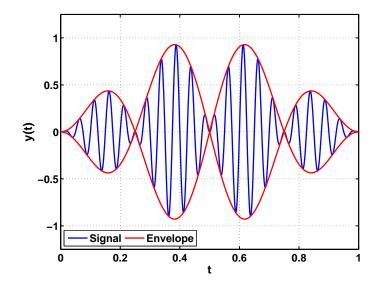

| 2.7  | Signal and the associated signal envelope                                                                                                                                | 15 |

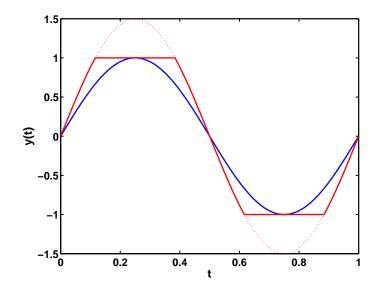

| 2.8  | Sine wave without clipping (blue) and with clipping at $y(t) = 1$ (red)                                                                                                  | 17 |

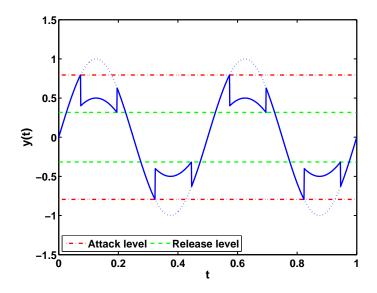

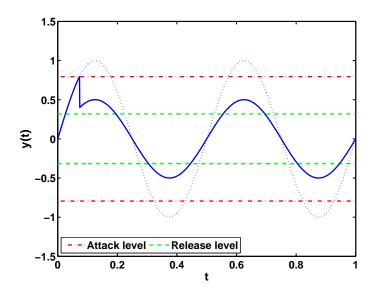

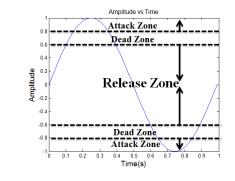

| 2.9  | Signal output from ideal VGA, showing the amplitude hysteresis window of the AGC. Dashed curve is the ideal output, and the full drawn curve is the gain adjusted output | 20 |

| 2.10 | Signal output from ideal VGA, for AGC with amplitude hysteresis window and non-zero release time                                                                         | 20 |

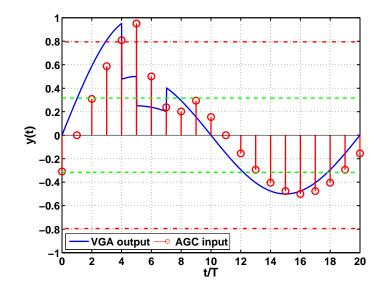

| 2.11 | Plot of VGA output and AGC input for a system where the AGC input is delayed one clock period, T, compared to the VGA output                                             | 21 |

| 2.12 | Example SNR vs input amplitude for adaptive A/D conversion channel                                                                                                       | 23 |

| 2.13 | Adaptive A/D conversion channel with channel filters                                                                                                                     | 24 |

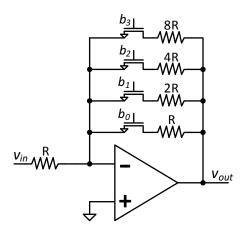

| 2.14 | Example of variable gain amplifier based on inverting amplifier configuration, with four gain levels and one-hot control                                                 | 25 |

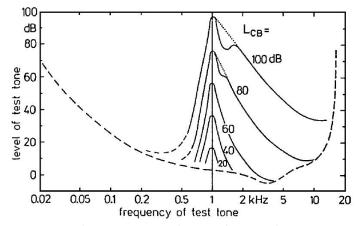

| 3.1  | Loudness contour plots of the binaural hearing threshold in free field                                                                                                   | 30 |

| 3.2  | Loudness contour plots with a masker present at 1 kHz $\hdots$                                                                                                           | 31 |

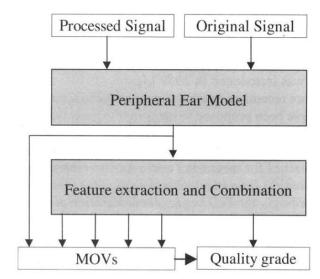

| 3.3  | High-Level block diagram of the PEAQ model                                                                                                                               | 33 |

| 3.4  | Block diagram of adaptive A/D conversion channel $\ . \ . \ . \ .$                                                                                                       | 36 |

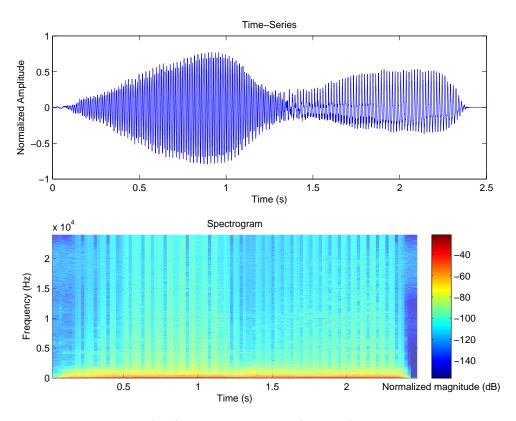

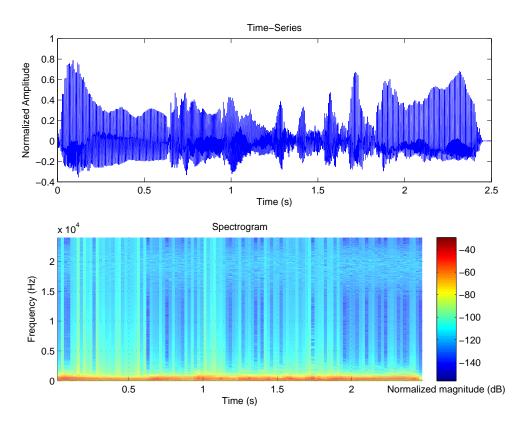

| 3.5  | Time-series (top) and spectrogram (bottom) plots of <i>Double-Bass</i> sound sample                                                                                      | 38 |

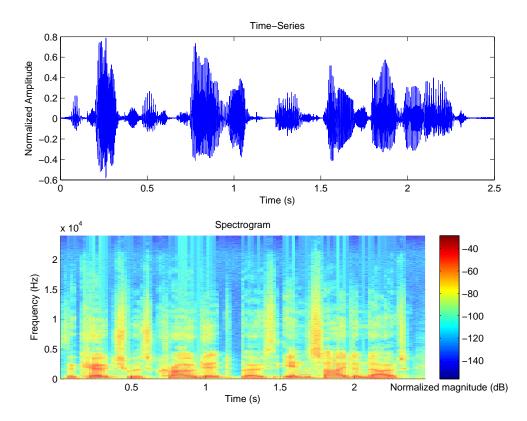

| 3.6  | Time-series (top) and spectrogram (bottom) plots of <i>Tuba</i> sound sample                                                                                                             | 38 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.7  | Time-series (top) and spectrogram (bottom) plots of <i>English Male</i><br>Speech sound sample                                                                                           | 39 |

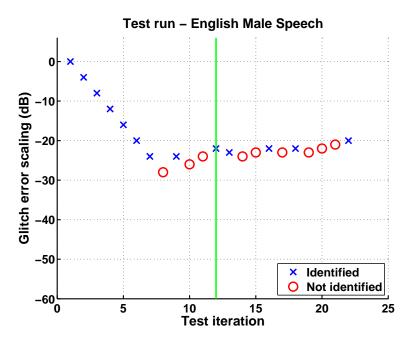

| 3.8  | Listening test run example. Search part of test to the left of the vertical green line; measurement part to the right                                                                    | 41 |

| 3.9  | Picture of the listening booth used for conducting listening tests .                                                                                                                     | 43 |

| 3.10 | Interface of the AFC MATLAB package used for the listening test                                                                                                                          | 43 |

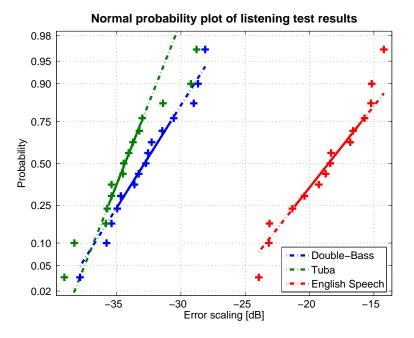

| 3.11 | Normal probability plot of listening test results                                                                                                                                        | 44 |

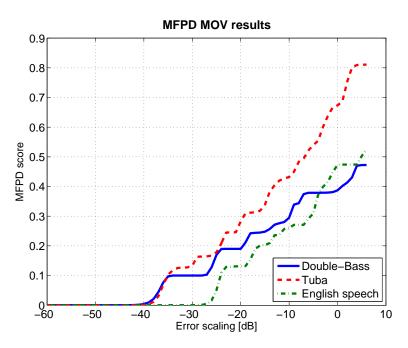

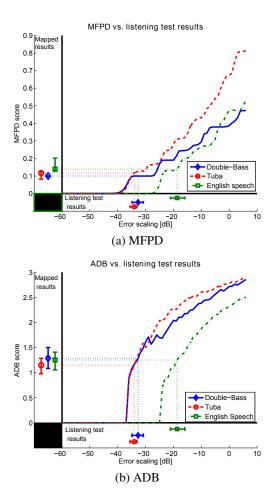

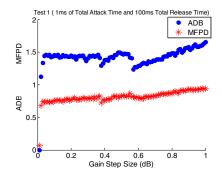

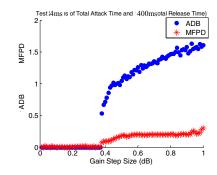

| 3.12 | Results from MFPD evaluation of the conversion channel                                                                                                                                   | 45 |

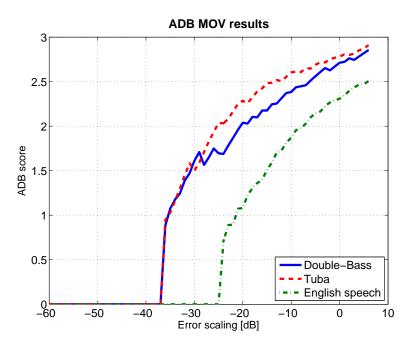

| 3.13 | Results from ADB evaluation of the conversion channel                                                                                                                                    | 46 |

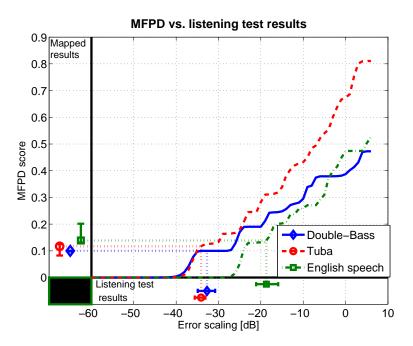

| 3.14 | Mapping of listening test results onto MFPD results                                                                                                                                      | 47 |

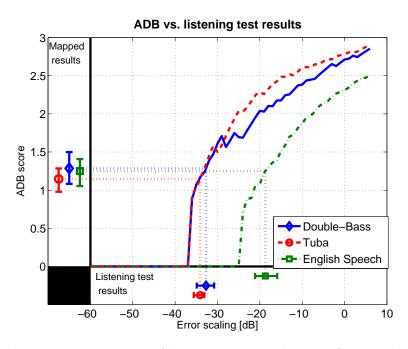

| 3.15 | Mapping of listening test results onto ADB results                                                                                                                                       | 47 |

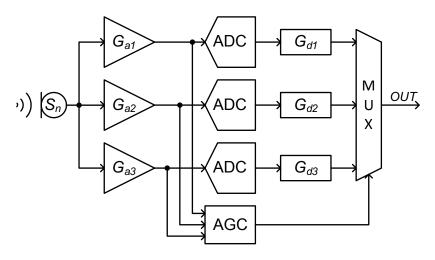

| 4.1  | Adaptive A/D conversion channel based on multiple static conversion channel                                                                                                              | 52 |

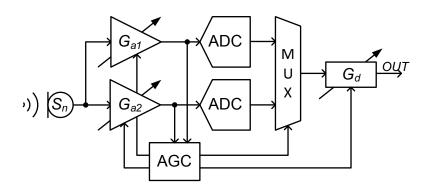

| 4.2  | Adaptive A/D conversion channel based on two adaptive conversion channels                                                                                                                | 52 |

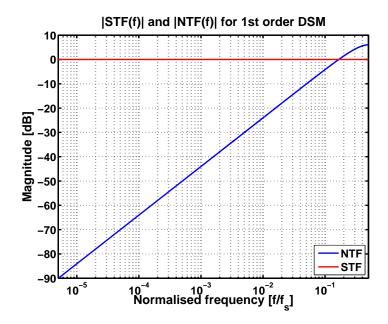

| 4.3  | Total channel gain, $G_{tot}$ , when delaying the change of $G_d$ by $0\tau$ (blue), $1.1\tau$ (red) or $5\tau$ (green) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 54 |

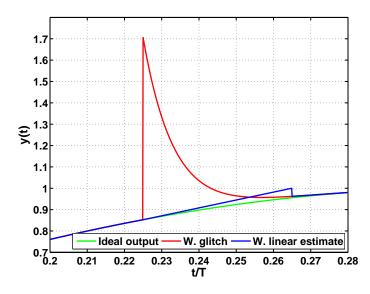

| 4.4  | Example of glitch removal by linear extrapolation of output signal                                                                                                                       | 57 |

| 4.5  | Block diagram of adaptive A/D conversion channel with glitch re-<br>moval                                                                                                                | 58 |

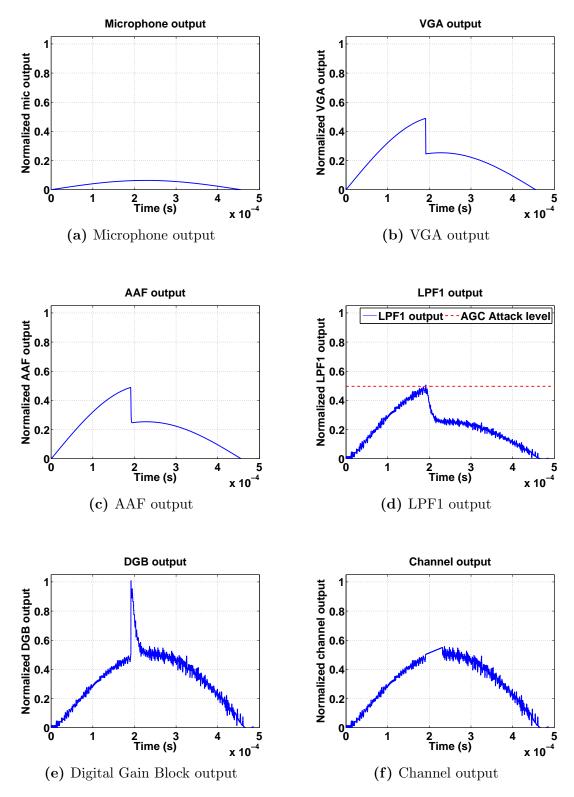

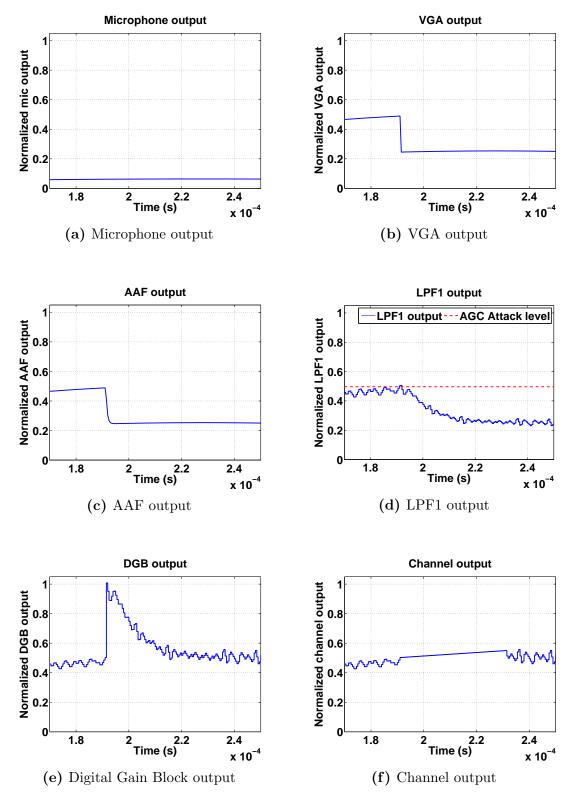

| 4.6  | Signal along conversion channel for sine-wave input at 1.1 kHz $$ .                                                                                                                      | 61 |

| 4.7  | Signal along conversion channel for sine-wave input at 1.1 kHz, zoom in around gain transition event                                                                                     | 62 |

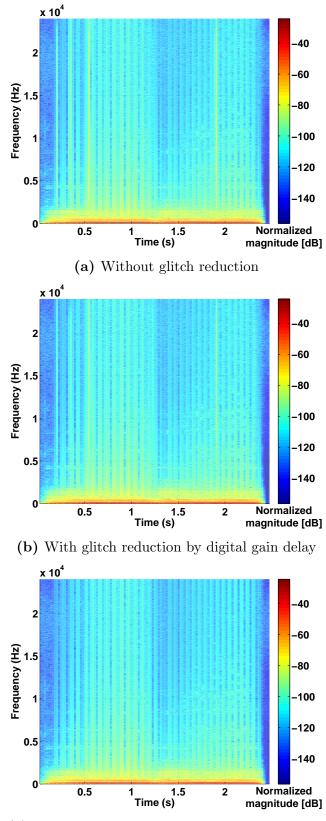

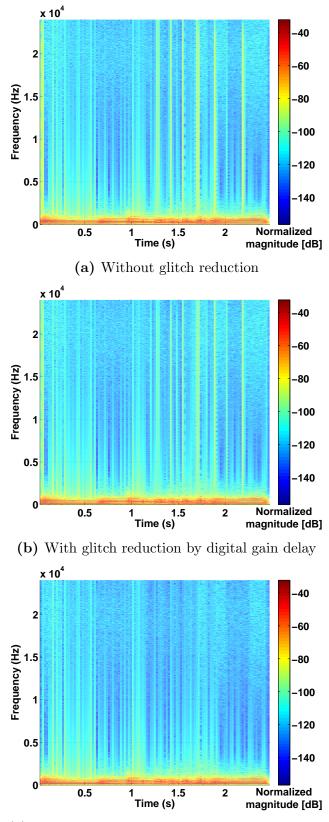

| 4.8  | Spectrogram of <i>Double-Bass</i> sound sample                                                                                                                                           | 63 |

| 4.9  | Spectrogram of <i>Tuba</i> sound sample                                                                                                                                                  | 64 |

| 4.10 | Spectrogram of English Male Speech sound sample                                                                                                                                          | 65 |

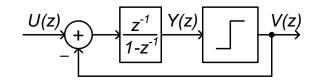

| 5.1  | 1st order discrete-time $\Delta\Sigma$ modulator                                                                                                                                         | 70 |

| 5.2  | Linearized model of 1st order $\Delta\Sigma$ modulator                                                                                                                                   | 70 |

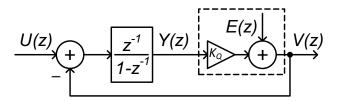

| 5.3  | Magnitude response of NTF and STF for 1st order $\Delta\Sigma$ modulator                                                                                                                 | 71 |

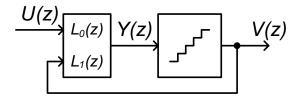

| 5.4  | Block diagram of generic $\Delta\Sigma$ modulator $\ldots \ldots \ldots \ldots \ldots$                                                                                                   | 72 |

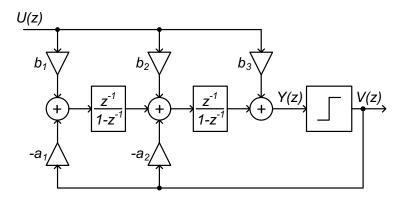

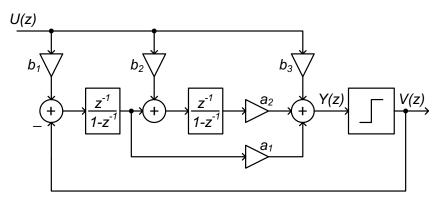

| 5.5  | CIFB topology for 2nd order modulator                                                                                                                                                    | 75 |

| 5.6  | CIFF topology for 2nd order modulator                                                                                                         | 75   |

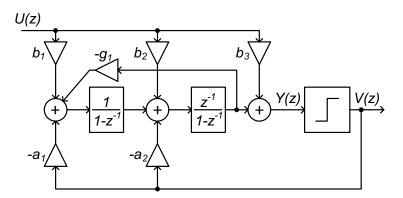

|------|-----------------------------------------------------------------------------------------------------------------------------------------------|------|

| 5.7  | CRFB topology for 2nd order modulator                                                                                                         | 76   |

| 5.8  | CT integrator topologies                                                                                                                      | 78   |

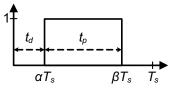

| 5.9  | Generic rectangular feedback DAC waveform                                                                                                     | 79   |

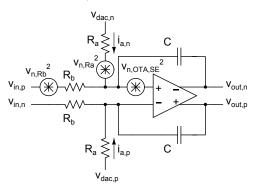

| 5.10 | Fully differential active-RC integrator with single-ended noise sources                                                                       | s 81 |

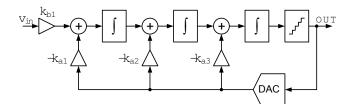

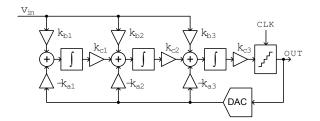

| 5.11 | Block diagram of 3rd order CT $\Delta\Sigma$ ADC with CIFB topology $~$                                                                       | 83   |

| 5.12 | Fully differential folded-cascode OTA                                                                                                         | 87   |

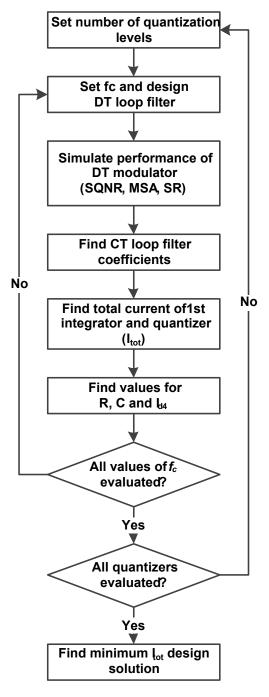

| 5.13 | Flowchart of optimization routine                                                                                                             | 93   |

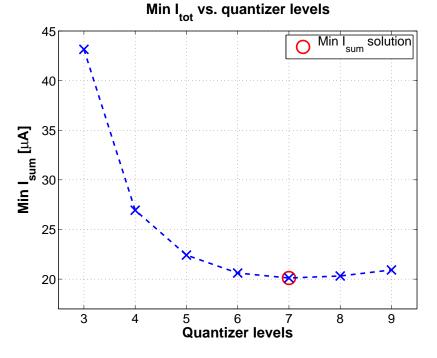

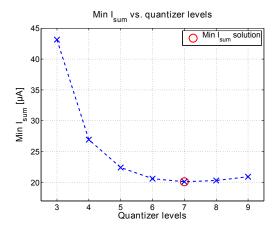

| 5.14 | Minimum $I_{\text{tot}}$ as a function of quantizer levels $\ldots \ldots \ldots \ldots$                                                      | 95   |

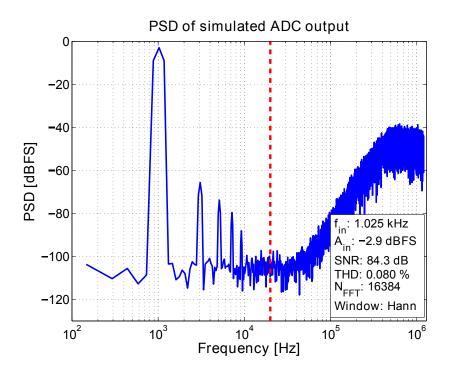

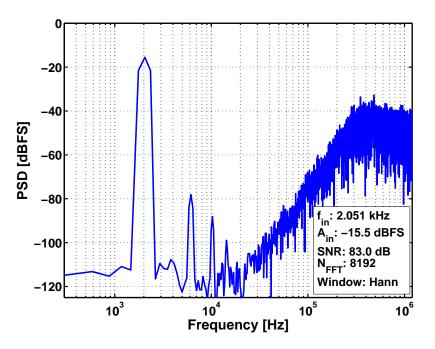

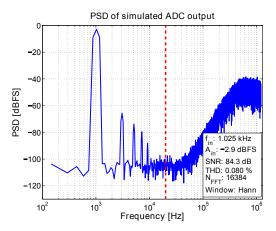

| 5.15 | PSD of simulated ADC output, with dashed line indicating the signal bandwidth                                                                 | 95   |

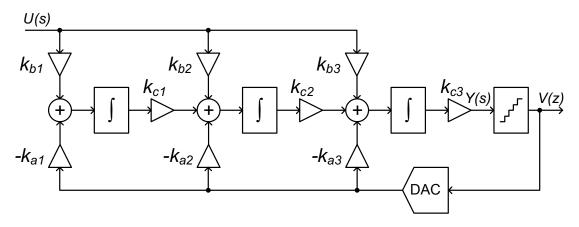

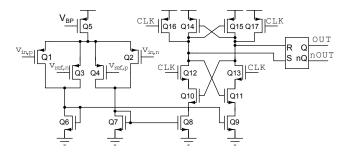

| 6.1  | Block diagram of the designed 3rd order CT $\Delta\Sigma$ modulator $~$                                                                       | 100  |

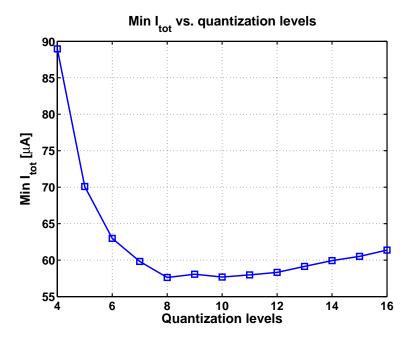

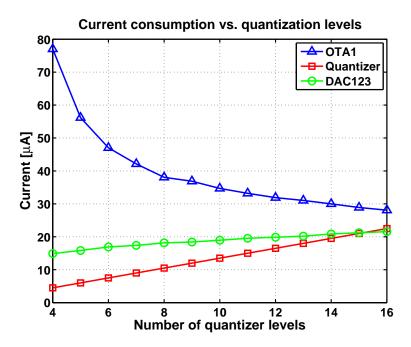

| 6.2  | Total current consumption for different quantization levels $\ldots$ .                                                                        | 101  |

| 6.3  | Current consumption of OTA1, DAC and Quantizer for different quantization levels                                                              | 102  |

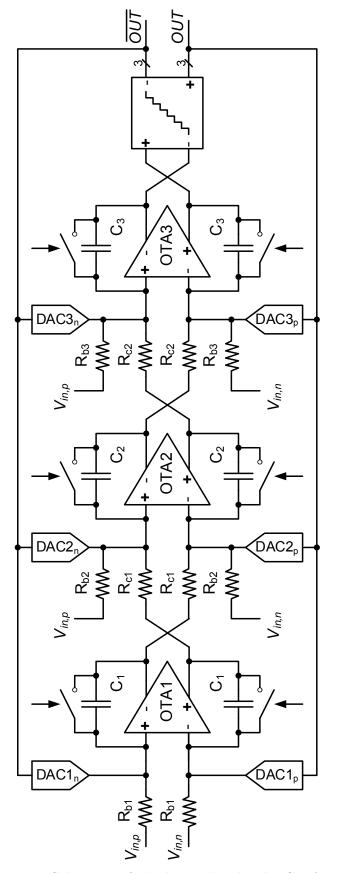

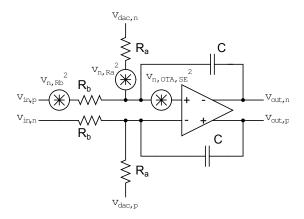

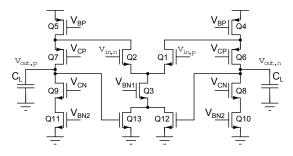

| 6.4  | Schematic of the designed 3rd order CT $\Delta\Sigma$ ADC                                                                                     | 103  |

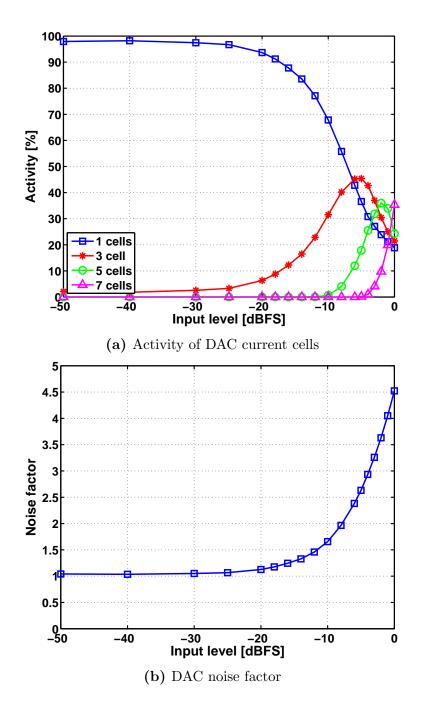

| 6.5  | Activity of current unit cells and current mode DAC noise factor<br>for 3rd order modulator, with an 8-level quantizer                        | 107  |

| 6.6  | Activity of current unit cells and current mode DAC noise factor<br>for 3rd order modulator, with a 7-level quantizer                         | 108  |

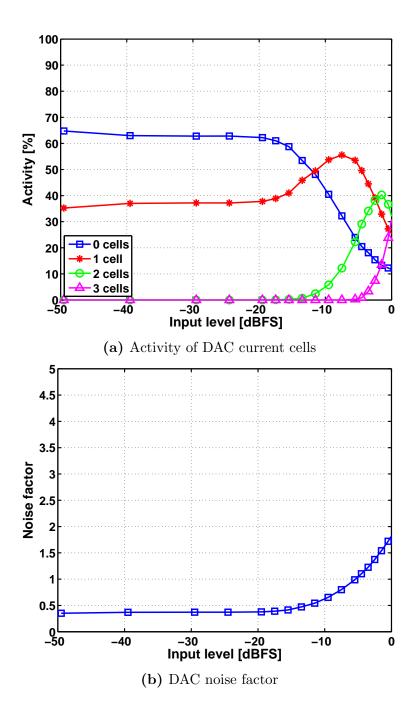

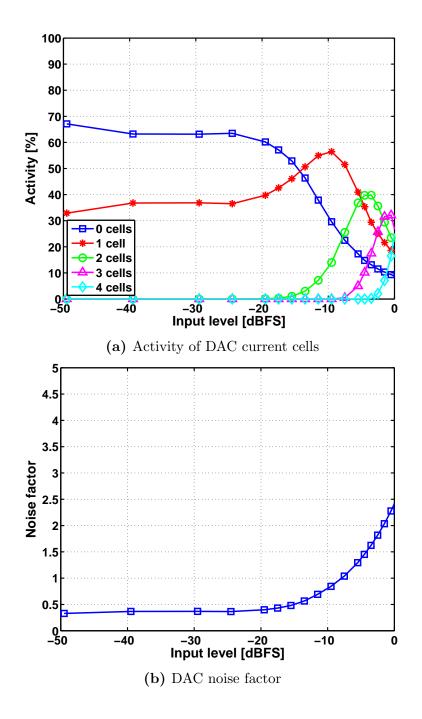

| 6.7  | Activity of current unit cells and current mode DAC noise factor<br>for 3rd order modulator, with a 9-level quantizer                         | 109  |

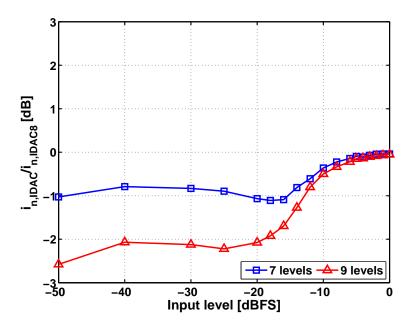

| 6.8  | 7-level and 9-level DAC noise normalized to noise of 8-level DAC, as a function of input level                                                | 110  |

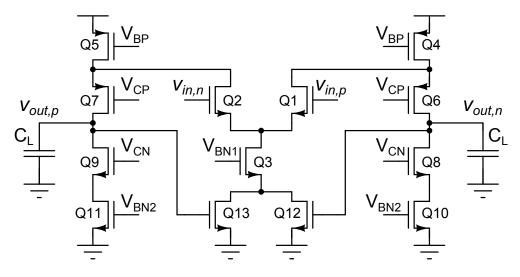

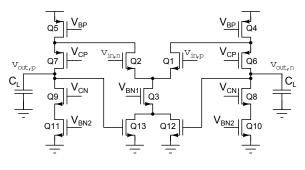

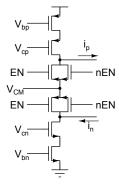

| 6.9  | Schematic of folded-cascode OTA                                                                                                               | 113  |

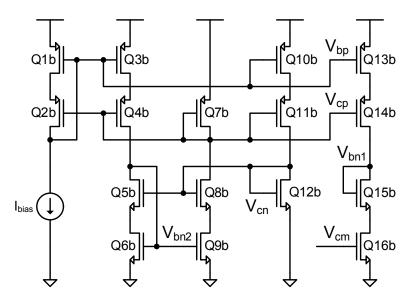

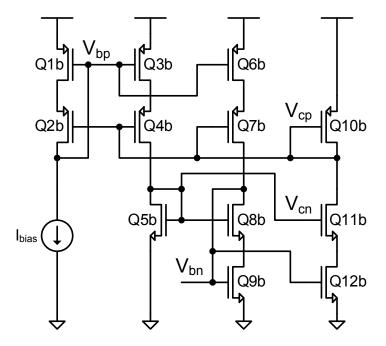

| 6.10 | Schematic of OTA biasing circuit                                                                                                              | 114  |

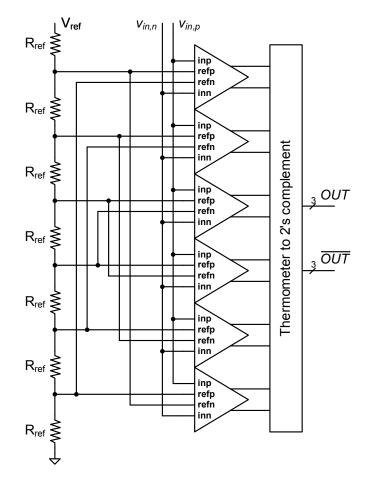

| 6.11 | Schematic of 7-level flash ADC                                                                                                                | 115  |

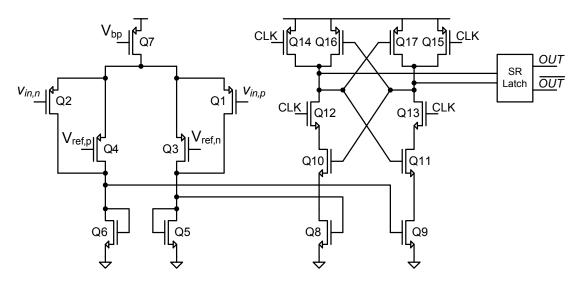

| 6.12 | Schematic of comparator                                                                                                                       | 115  |

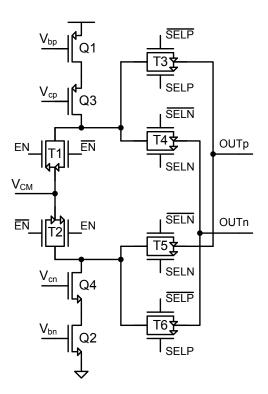

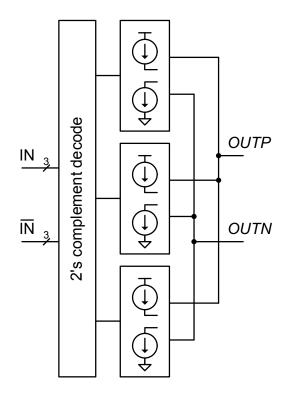

| 6.13 | Schematic of current unit cell of current mode DAC $\ldots$                                                                                   | 118  |

| 6.14 | Block diagram of current mode DAC                                                                                                             | 118  |

| 6.15 | Schematic of DAC biasing circuit                                                                                                              | 120  |

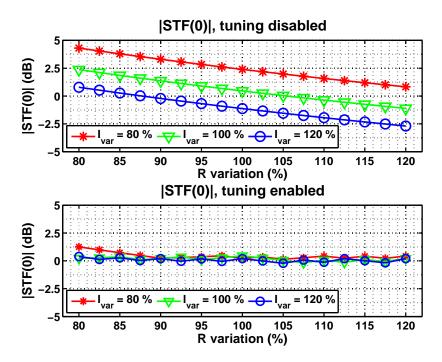

| 6.16 | Variation of $ STF(0) $ for variations of reference current $(I_{var})$ and resistor values, with tuning disabled (top) and enabled (bottom). | 121  |

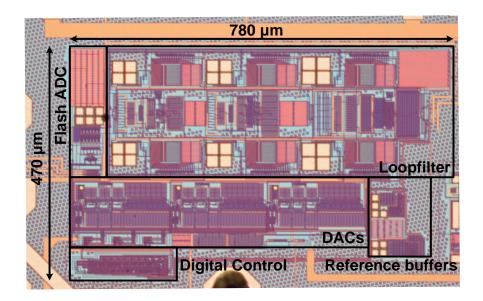

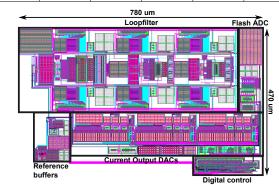

| 6.17 | Die-photo of the fabricated test IC, with modulator input on the right side and output on the left                                                                                        | 123 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

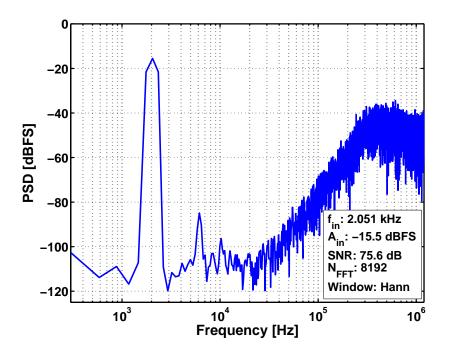

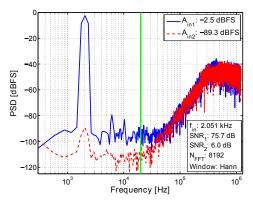

| 6.18 | PSD of simulated ADC output, using averaging of two simulations                                                                                                                           | 124 |

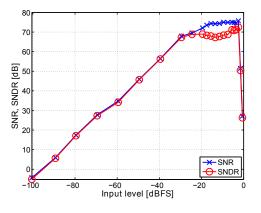

| 6.19 | Simulated SNR and SNDR as a function of the modulator input level                                                                                                                         | 126 |

| 6.20 | Simulated THD as a function of the modulator input level $\ldots$                                                                                                                         | 126 |

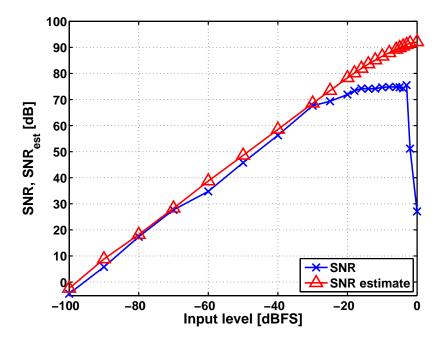

| 6.21 | Simulated SNR and estimated SNR based on noise of 1st integrator<br>and 1st feedback DAC                                                                                                  | 127 |

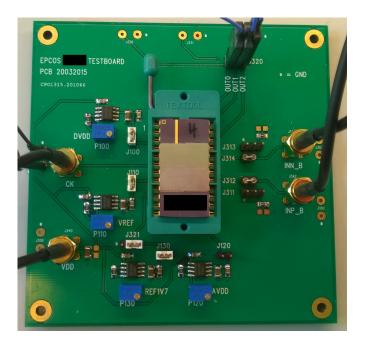

| 6.22 | Test PCB for evaluation of the test IC $\ldots \ldots \ldots \ldots \ldots$                                                                                                               | 132 |

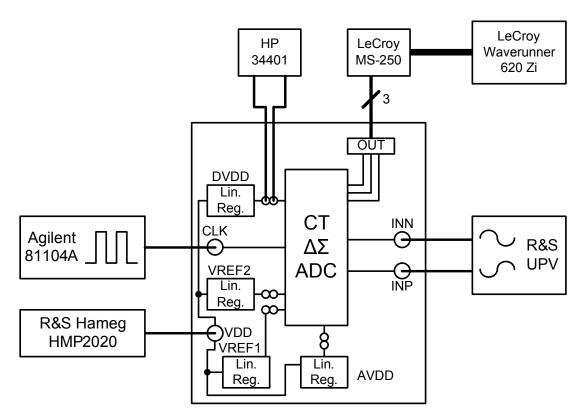

| 6.23 | Block diagram of measurement setup for evaluation of test IC $$                                                                                                                           | 133 |

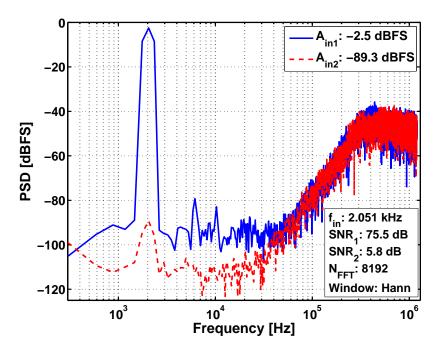

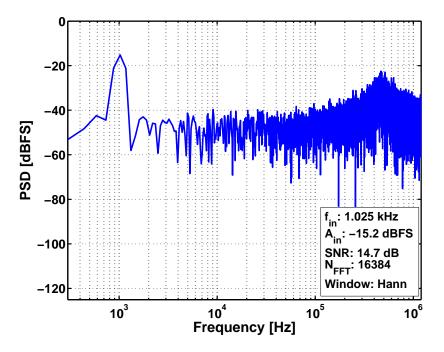

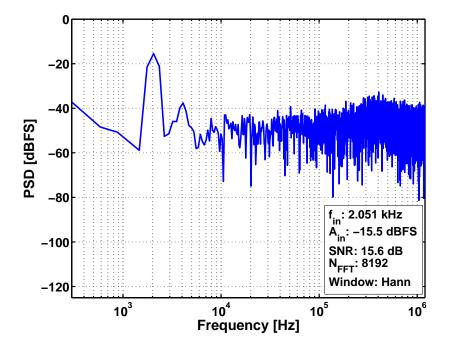

| 6.24 | PSD of measured output                                                                                                                                                                    | 134 |

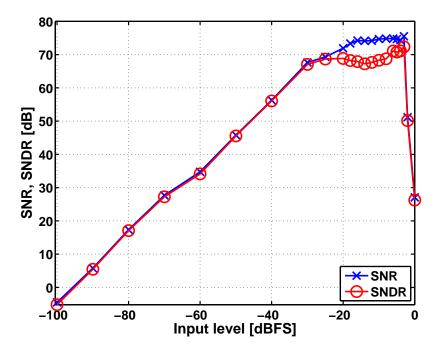

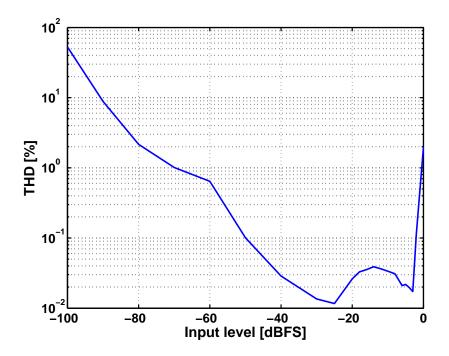

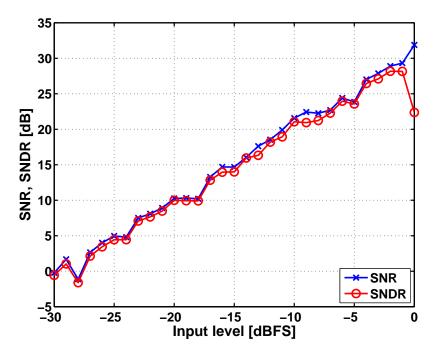

| 6.25 | Measured SNR and SNDR as a function of the modulator input level, for input sine wave at 1 kHz                                                                                            | 134 |

| 6.26 | PSD of simulated CT $\Delta\Sigma$ ADC output, with PEX model for the Flash ADC and without circuit noise $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                              | 135 |

| 6.27 | PSD of simulated CT $\Delta\Sigma$ ADC output, with PEX model for the Flash ADC, without circuit noise, and without flip-flops in output buffer $\ldots$                                  | 135 |

| 6.28 | PSD of simulated CT $\Delta\Sigma$ ADC output, with PEX model for<br>the Flash ADC, without circuit noise, without flip-flops in output<br>buffer, with doubled time delayed of DAC clock | 136 |

|      |                                                                                                                                                                                           |     |

| 1.1 | Performance overview of some of the commercially available high SPL MEMS microphones                                            | 2   |

|-----|---------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1 | Pros and cons of feedback and feedforward AGC loops                                                                             | 14  |

| 2.2 | Pros and cons of using small and large gain steps $\ldots \ldots \ldots$                                                        | 23  |

| 3.1 | Subjective grading scale used in ITU-R BS.1116                                                                                  | 31  |

| 3.2 | Properties of noiseless adaptive A/D conversion channel model used for generation of test signals                               | 36  |

| 3.3 | Properties of sound samples used for evaluation of the adaptive A/D conversion channel                                          | 37  |

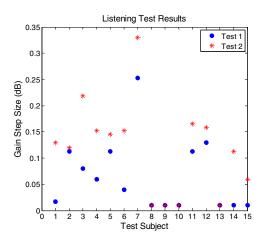

| 3.4 | Statistics for the transient error detection threshold levels from the results of the listening test, based on 15 test subjects | 44  |

| 4.1 | Properties of noiseless adaptive A/D conversion channel model used for evaluation of glitch reduction method                    | 59  |

| 4.2 | Summary of results from evaluation of audibility of transient glitches, when applying glitch reduction methods                  | 67  |

| 5.1 | Overview of advantages of CT and DT implementations of $\Delta\Sigma$ ADCs                                                      | 77  |

| 5.2 | Overview of pros and cons of RZ and NRZ feedback DAC waveforms                                                                  | 80  |

| 5.3 | Design parameters used for the optimization of the 3rd order CT $\Delta\Sigma$ ADC                                              | 94  |

| 5.4 | Summary of results from optimization and simulation $\ldots$ $\ldots$ $\ldots$                                                  | 94  |

| 6.1 | Summary modulator properties from optimization routine 1                                                                        | 104 |

| 6.2 | Summary of simulated circuit properties for OTA1, OTA2 and OTA31                                                                | 113 |

| 6.3 | Summary of simulated circuit properties of the OTA biasing circuit 1                                                            | 114 |

| 6.4 | Summary of quantizer circuit properties                                                                                         | 116 |

| 6.5 | Summary of the main circuit properties of the DAC current unit cell                                                             | 117 |

| 6.6 | Summary of DAC biasing circuit properties                                                                                       | 120 |

| 6.7 | Overview of modulator current consumption, total and for subblocks                                                              | 128 |

| 6.8  | Summary of simulated performance of the CT $\Delta\Sigma$ ADC in typical process corner at 27°C      | 128 |

|------|------------------------------------------------------------------------------------------------------|-----|

| 6.9  | Comparison of FoM with other audio CT $\Delta\Sigma$ ADCs                                            | 129 |

| 6.10 | Simulated performance of the designed CT $\Delta\Sigma$ ADC in PVT corners for -15 dBFS input signal | 131 |

| 6.11 | Measured modulator current consumption, based on 6 chips $\ldots$                                    | 137 |

# 1

## Introduction

This chapter provides an introduction to the PhD project documented by this thesis. The motivation for the project is given, and an overview of the sections of the thesis is provided.

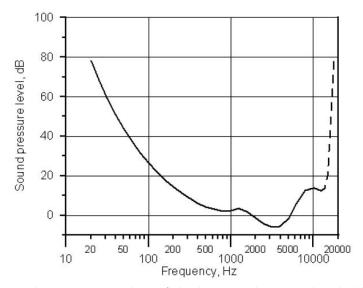

In the last 30 years the research in Micro Electro Mechanical Systems (MEMS) has been continuously growing. This has led to the commercialization of several products, including MEMS microphones. Compared to electret condenser microphones (ECM), MEMS microphones are smaller, thereby allowing for integration into smaller devices or having multiple microphones in e.g. a smartphone. The ECM microphones require a permanent charge on the backplate of the microphone, miking it sensitive to high temperature. The MEMS microphone is instead charged by a charge-pump circuit when operating; as a result, it is possible to reflow solder the MEMS microphone is silicon based and fabricated using standard fabrication methods developed by the semiconductor industry over the years. Batch processing is therefore possible, resulting in a low variation in the performance of the fabricated microphones.

The market for MEMS microphones has increased significantly in recent years [1], with the market revenue in 2010 at \$US 200 million and forecasted to increase to \$US 1400 million in 2017. About 40 % of this market revenue in 2017 is from very high performance microphones, characterized by a high signal-to-noise ratio (SNR) and a high dynamic range (DR). Having a larger dynamic range in the microphone reduces the risk of clipping of the audio signal due to very large sound pressure levels; high sound pressure levels may occur at a concert venue from the subwoofers or due to wind noise.

To characterize the performance of the microphones, the microphone SNR is specified for an acoustical input of 1 Pa, equal to 94 dB sound pressure level (SPL). The acoustical overload point (AOP) defines the maximum acoustical input of the microphone at which the microphone output signal has 10 % total harmonic distortion (THD). From the reference SNR and the AOP the dynamic range of the microphone may be calculated as:

$$DR_{mic} = SNR_{1Pa} + AOP - 94 dB$$

(1.1)

| Microphone      | $\mathrm{SNR}_{\mathrm{1Pa}}$ | AOP         | DR                 | $\mathbf{I_{tot}}$ | Interface |  |  |  |

|-----------------|-------------------------------|-------------|--------------------|--------------------|-----------|--|--|--|

| InvenSense      |                               |             |                    |                    |           |  |  |  |

| INMP411 [2]     | 62  dB(A)                     | 131  dB SPL | 99 dB              | 250 µA             | analog    |  |  |  |

| INMP510 [3]     | 65  dB(A)                     | 124  dB SPL | $95~\mathrm{dB}$   | 180 µA             | analog    |  |  |  |

| ICS-40300 [4]   | 63  dB(A)                     | 130  dB SPL | 99  dB             | 220 µA             | analog    |  |  |  |

| INMP621 [5]     | 65  dB(A)                     | 133  dB SPL | 104 dB             | 1200 µA            | digital   |  |  |  |

| Knowles         |                               |             |                    |                    |           |  |  |  |

| SPA2629LR5H [6] | 65  dB(A)                     | 123  dB SPL | 94 dB              | 120 µA             | analog    |  |  |  |

| SPH0641LM4H [7] | 64.3  dB(A)                   | 120  dB SPL | $90.3~\mathrm{dB}$ | 620 µA             | digital   |  |  |  |

| SPK1638LM4H [8] | 64.5  dB(A)                   | 122  dB SPL | $92.5~\mathrm{dB}$ | 460 µA             | digital   |  |  |  |

| EPCOS           |                               |             |                    |                    |           |  |  |  |

| C928 [9]        | 66  dB(A)                     | 135  dB SPL | 107  dB            | 140 µA             | analog    |  |  |  |

Table 1.1: Performance overview of some of the commercially available high SPL

MEMS microphones

In the current microphone market a range of microphones with a high dynamic range around 100 dB is available from different manufacturers. A list of analog and digital microphones is given in Table 1.1, stating the main performance parameters of the microphones. From the table it can be seen that for the same dynamic range, the current consumption of the digital microphones is significantly larger than for the analog microphones. Basically the analog microphone consists of a MEMS sensor and an analog amplifier circuit, while the digital microphone has an additional analog-to-digital converter (ADC). The ADC is thus the cause of the high current consumption of the digital MEMS microphones. As the market asks for digital MEMS microphones with dynamic ranges around 110 dB, the current consumption will increase further due to the increased dynamic range requirements of the ADC used in the microphone.

Designing an ADC with a dynamic range above 10 dB and with low current consumption is a difficult challenge, since all non-idealities need to be taken into account at this performance level. A state-of-the-art  $\Delta\Sigma$  ADC for audio applications is presented in [10] that achieves a dynamic range of 106 dB, but with a current consumption of 5.4 mA. It should be noted that this is including the decimation filter of the ADC. In digital MEMS microphones the output signal is typically pulse density modulated (PDM) and output as a 1-bit data stream at the sampling frequency of the ADC; thus, the decimation filter is not needed in the digital MEMS microphone. The INMP621 digital microphone from InvenSense [5] achieves a dynamic range of 104 but with a current consumption of 1200 mA. The results from [10] and the available digital microphones indicate, that for digital microphones with 110 dB dynamic range the current consumption will be in range of 1.5 mA to 2 mA.

The main problem of the digital microphone is the requirement of the ADC to have a dynamic range larger than that of the MEMS sensor. Thus, if this ADC requirement is relaxed, a lower current digital MEMS microphone may be created. The C928 analog microphone from EPCOS [9] has a dynamic range of 107 dB with a current consumption of 140  $\mu$ A. If a digital microphone could be designed with a similar dynamic range and with a current consumption below 1 mA, this would be a significant benefit for the company from a commercial point of view.

The project documented in this thesis concerns the investigation of an adaptive analog-to-digital (A/D) conversion channel for use in a digital MEMS microphone. The preamplifier and the ADC of the microphone may be viewed as an A/D conversion channel. Typically the gain of the preamplifier is fixed, but by adaptively adjusting the gain of the preamplifier based on the input signal level, the dynamic range of the conversion channel may be extended. This has the benefit of not requiring that the ADC has a dynamic range equal to that of the conversion channel; thus, a lower performing ADC may be used, thereby reducing the total current consumption of the microphone.

## 1.1 Thesis Outline

This thesis consists of eight chapters that can be split into three parts. The first part of the thesis, consisting of Chap. 2-4, covers the system level aspect of the high dynamic range A/D conversion channel.

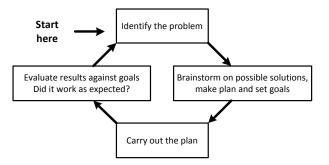

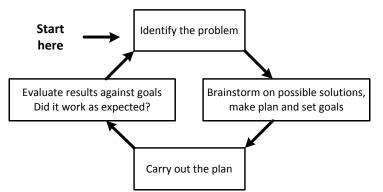

Chapter 2 provides an introduction to the topic of A/D conversion channels. A detailed description is given of the adaptive A/D conversion channel uses an automatic gain controller for adjusting the channel gain configuration, thereby extending the dynamic range of the channel. Important properties of the adaptive A/D conversion channel are described, with emphasis on the automatic gain controller. The non-idealities generated by the conversion channel and added to the channel output signal due to the gain adjustment in the channel, are discussed and possible solutions are described.

Chapter 3 presents an objective method for the evaluation of the audibility of the transient glitches generated by the adaptive A/D conversion channel. The objective evaluation is based on parts of the psychoacoustic model that is used in the objective *Perceptual Evaluation of Audio Quality* method. The proposed method is compared with the results of a subjective evaluation in the form of a listening test. The chapter is based on the ICASSP 2014 conference paper: *Objective Evaluation of the Audibility of Transient Errors in an Adaptive A/D Conversion Channel.*

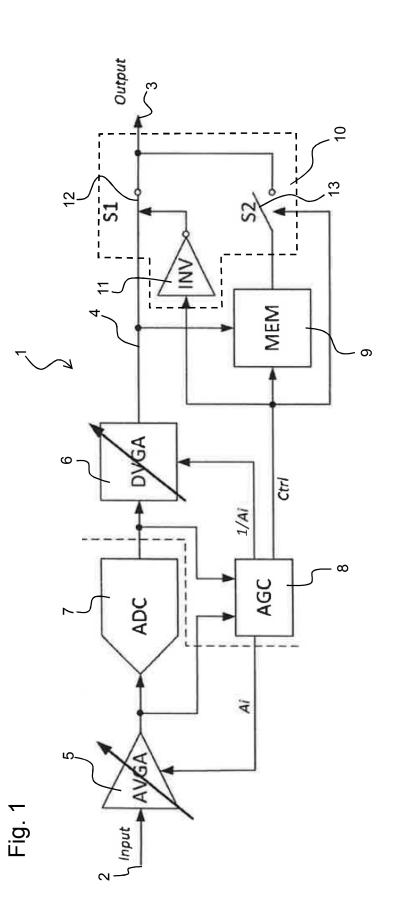

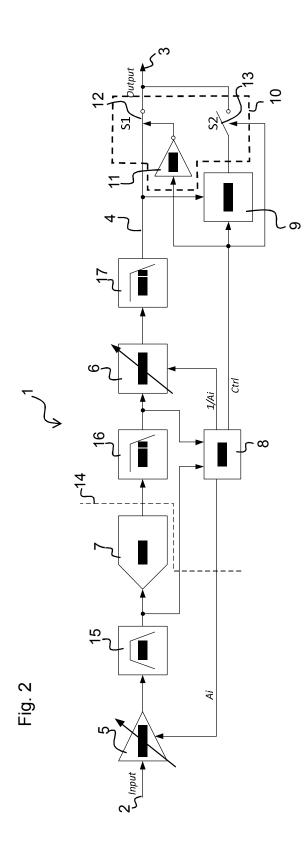

Chapter 4 presents a method for reducing the transient glitches of the adaptive A/D conversion channel. The method replaces the output signal of the channel by a linear estimate, while the conversion channel settles after a gain change. The chapter is based on a patent application submitted to the European Patent Office: PCT/EP2014/059488 - Circuit and Method of Operating Circuit.

The second part of the thesis covers the design of low power continuous-time  $\Delta\Sigma$  ADCs for application in the adaptive A/D conversion channel.

Chapter 5 presents a brief introduction to the topic of  $\Delta\Sigma$  modulation and

continuous-time  $\Delta\Sigma$  modulators. An optimization method is then presented for the design of low power continuous-time  $\Delta\Sigma$  ADC. The optimization is based on an analysis of the modulator and the circuit blocks of the ADC. By taking the circuit implementation into account when designing the modulator, the method tries to determine the minimum current design based on a set of performance requirements. The chapter is based on the NORCHIP 2014 conference paper: *Optimization of Modulator and Circuits for Low Power Continuous-Time Delta-Sigma ADC.*

Chapter 6 presents the design of a low power continuous-time  $\Delta\Sigma$  ADC, where a current mode DAC is used in combination with active-RC integrators. This combination relaxes the noise requirements of the 1st integrator of the ADC, resulting in a lower power solution in comparison to the use of voltage mode feedback. The designed ADC is described in detail, and the performance results are presented including suggestions on how further to improve the design. The chapter is based on the ECCTD 2015 conference paper: Low Power Continuous-Time Delta-Sigma ADC with Current Output DAC.

Chapter 7 summarizes the results of the thesis project, and the recommendations for future work.

Chapter 8 briefly describes the other research work that has been carried out during the PhD project. This includes the design of a new university course on practical IC design; a study on the use of coaching and personal feedback as a way of improving the generic engineering competences of students; and a study on the problems of using automatic gain control in audio applications. The chapter is based on three conference publications presented at the NORCHIP 2013 conference, the CDIO 2014 conference, and the PRIME 2015 conference.

A graphical overview of the thesis chapters and related publications is given in Fig. 1.1.

#### Chap. 1: Introduction

Chap. 2: Adaptive A/D Conversion Channel

Figure 1.1: Overview of thesis chapters and related publications

2

## Adaptive A/D Conversion Channel

This chapter introduces the adaptive A/D conversion channel for the purpose of achieving a high dynamic range conversion channel with a low power consumption. The chapter is intended as an overview to the topic, and provides a description of the different parts of the conversion channel, with the main emphasis being on the automatic gain controller that is at the core of the channel. The issues related to the application of the automatic gain control are discussed and possible solutions are presented.

## 2.1 Static A/D Conversion Channel

When considering an A/D conversion channel for a sensor, the dynamic range of the conversion channel should be larger than, or equal to, that of the sensor. The simplest A/D conversion channel consists of a preamplifier with a fixed gain and an analog-to-digital converter, as shown in Fig. 2.1. The dynamic range of the channel is limited by two factors: the supply voltage and the noise floor. The supply voltage sets an upper limited on the input signal that the channel is able to process without clipping the signal. Clipping is unwanted as it causes harmonic distortion in the output signal. The noise floor determines the minimum signal power that may be detected.

The noise of the static A/D conversion channel, when referred to the input of the channel, is given as:

$$v_{n,irn}^{2} = v_{n,mic}^{2} + \frac{1}{G_{a}^{2}} \left( v_{n,preamp}^{2} + v_{n,ADC}^{2} \right)$$

$$(2.1)$$

$$(2.1)$$

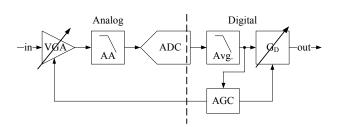

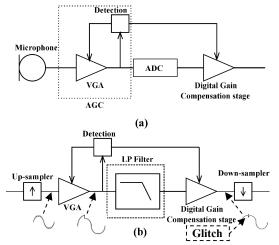

Figure 2.1: Block diagram of static A/D conversion channel

where  $v_{n,irn}^2$  is the input referred noise power of the channel,  $v_{n,mic}^2$  is the microphone noise power,  $v_{n,preamp}^2$  is the output noise power of the preamplifier,  $v_{n,ADC}^2$ the equivalent ADC noise power at the input of the ADC, and  $G_a$  is the analog preamplifier gain. Generally, the A/D conversion channel should be designed so that the microphone noise is the dominant noise source. Furthermore,  $v_{n,preamp}$ should be smaller than  $v_{n,ADC}$  in order to fully utilize the resolution and dynamic range of the ADC. From (2.1) it is seen, that the noise of the preamplifier and the ADC is reduced by the gain of the preamplifier.

Generally the circuit noise relates to the current consumption of the circuits: the gate referred thermal noise power of a MOSFET is given as [11]:

$$v_{g,therm}^2(f) = \frac{8}{3}kT\frac{1}{g_m}$$

(2.2)

where k is the Boltzmann constant, T the absolute temperature, and  $g_m$  the transistor transconductance. From the Schichmann-Hodges model of the MOSFET, the value of  $g_m$  relates to the biasing current as:

$$g_m = \frac{2I_d}{V_{ov}} \tag{2.3}$$

where  $I_d$  is the biasing current, and  $V_{ov}$  is the transistor overdrive voltage. Thus, the thermal noise power of the MOSFET is inversely proportional to the biasing current, resulting in a large current consumption for low noise operation. The gate referred 1/f noise power of the MOSFET is given as [11]:

$$v_{g,1/f}^2(f) = \frac{K}{WLC_{ox}f}$$

(2.4)

where K is a process dependent constant, W the MOSFET gate width, L the MOSFET gate length, and  $C_{ox}$  is the gate capacitance per unit area. A low 1/f noise requires large transistors, which in turn results in a large gate capacitance. This adds a capacitive load to the preceding stages, thus implicitly increasing the current consumption. Finally, the quantization noise of the ADC depends on the ADC topology used in the conversion channel. Generally speaking, the larger the resolution, the higher the current consumption due to the increased number of active components in the ADC or higher sampling frequency.

In order to achieve a low current conversion channel, it is thus preferable to have a large preamplifier gain. However, this may conflict with the goal of utilizing the dynamic range of the sensor. Consider the case where a given static conversion channel has been designed, but it lacks 6 dB in dynamic range to match the dynamic range of the sensor. One solution is to increase the internal supply voltage of the circuit by the use of e.g. a voltage doubler. Assuming a constant current consumption and MEMS sensor sensitivity, then by doubling the supply voltage, the maximum signal level that may be processed in the channel without clipping is increased by 6 dB. However, doubling the supply voltage also double the power consumption since the biasing currents are unchanged. An alternative solution is to keep the supply voltage constant and instead dampen the sensor

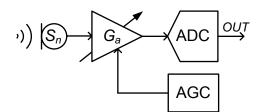

Figure 2.2: Block diagram of adaptive A/D conversion channel

signal by 6 dB. This also reduces the noise of the sensor by the same amount, thus requiring that the circuit noise of the conversion channel is reduced by 6 dB as well. Considering only thermal noise from the MOSFETs in the circuit, then from (2.2)-(2.3) a 6 dB improvement in noise would require quadrupling the biasing current; similarly, this increases the power consumption by a factor of four.

To obtain an increase of the dynamic range by 6 dB, the obvious solution appears to be applying a voltage doubler in the conversion channel. However, the voltage doubler circuit also requires current and area. Furthermore, the higher supply voltage may not be compatible with the process technology used for implementation of the circuits. Thus the

Overall the static A/D conversion channel is limited by the requirement that the circuits blocks need a dynamic range equal to that of the MEMS sensor. In applications where a very high dynamic range is required, but where the related increase in power consumption is not acceptable, the static A/D conversion channel is not a viable solution.

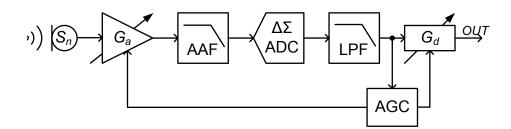

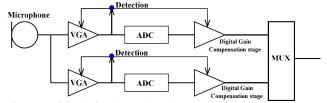

## 2.2 Adaptive A/D Conversion Channel

The alternative to the static A/D conversion channel is an adaptive A/D conversion channel, where the preamplifier is realized as a variable gain amplifier (VGA), as shown in Fig. 2.2. The gain of the VGA may then be adjusted based on the level of the input signal from the sensor. For small input levels, a large gain is used in the VGA, while a small gain is used for large input levels. The gain level of the VGA may then be controlled by an adaptive gain controller (AGC) that monitors the signal level and adjusts the VGA gain accordingly.

The input referred noise of the adaptive A/D conversion channel is similar to that of the static A/D conversion channel given in (2.1), except for the variable gain:

$$v_{n,irn}^2 = v_{n,mic}^2 + \frac{1}{G_{a,VGA}(t)^2} \left( v_{n,VGA}^2 + v_{n,ADC}^2 \right)$$

(2.5)

where  $G_{a,VGA}(t)$  is the gain time-dependent of the VGA, and  $v_{n,VGA}$  is the output noise of the VGA. From (2.5) it is given that for large  $G_{a,VGA}$  the circuit noise is low; this occurs for small input signal levels. For large input signal levels the value of  $G_{a,VGA}$ , is reduced, thus increasing the circuit noise. Due to the gain

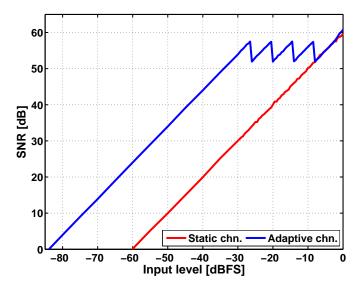

Figure 2.3: Example of SNR as a function of the input level for the static and the adaptive A/D conversion channel

adjustment, the dynamic range is in essence extended in comparison to the static gain conversion channel. This gain adjustment is handled by the AGC. In Fig. 2.3 is plotted the SNR as a function of the input signal level for both the static and the adaptive A/D conversion channel. As seen from the figure the dynamic range of the adaptive channel is extended beyond that of the static channel.

With AGC it is thus possible to design the VGA with a large gain for small input signals, which may relax the noise requirements of the VGA and the ADC. The peak SNR of the adaptive conversion channel is still limited by the noise of the VGA and the ADC. As the input signal increases, the SNR of the conversion channel stops to increase at the input level that triggers the first VGA gain reduction. As a result, dynamic range of the adaptive A/D conversion channel is not equal to the peak SNR of the channel. This behavior of the adaptive A/Dconversion channel is clearly seen from the plots shown in Fig. 2.3. Nevertheless, the dynamic range of the conversion channel is improved without increasing the supply voltage of the circuits or reducing the noise of the circuit. Thereby for the same dynamic range, the current consumption of the adaptive A/D conversion channel will ideally be smaller than that of the static A/D conversion channel. The power consumption of the AGC and support blocks needs to be taken into account, when evaluating the overall reduction in current consumption. Overall, the adaptive conversion channel can primarily be used in applications where high dynamic range combined with low current consumption is more important than the peak SNR of the channel.

Unfortunately the addition of the VGA and the AGC in the conversion channel adds complexity to the system. Some of the questions that arise are:

- How many gain levels should the VGA have?

- How should the AGC detect the level of the signal being processed by the

channel?

- How should the AGC be implemented: analog or digital?

- How should the AGC block adjust the VGA gain?

- How should the varying channel gain be handled?

- How to handle transient errors generated when adjusting the VGA gain?

In the following sections these questions will be discussed in more detail.

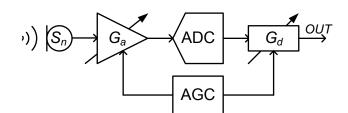

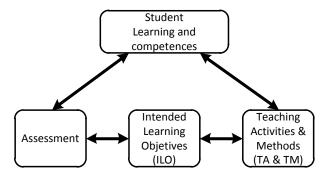

# 2.3 Constant Channel Gain

For a microphone it is a desired property that the sensitivity is a time-invariant parameter, so that a given sound pressure level results in a specific output signal. With the adaptive A/D conversion channel depicted in Fig. 2.2, the same output level may be generated from several different input levels, due to the change of the VGA gain depending on the signal level; thus, the constant sensitivity property of the microphone is violated. In order to achieve a constant channel gain it is necessary to compensate for the reduction of the VGA gain. With the output of the A/D conversion channel being digital, the change in analog gain may be compensated digitally, as shown in Fig. 2.4. A similar approach was used in [12] for an adaptive A/D conversion channel for a bio-sensor array.

Thus, the total conversion channel gain,  $G_{chn}$ , is given as:

$$G_{chn} = G_a \cdot G_d \tag{2.6}$$

where  $G_d$  is the digital gain. When  $G_a$  is reduced,  $G_d$  is increased by the same factor, and vice versa when the  $G_a$  is increased. From a digital point of view, it is preferable that the digital gain levels are different by a factor in powers of 2, as this can easily be implemented digitally by a bit shift operation. Other gain factors require dedicated multiplier blocks which increases the digital power consumption, thus increasing the complexity. This also limits the gain steps used by the conversion channel to factors of powers of 2, thus minimum 6 dB.

A problem related to compensating the change in analog gain by means of a digital gain is the introduction of transient errors or transient glitches. The glitch

Figure 2.5: Analog gain, digital gain and channel gain during adjustment event

occurs due to different transition times when changing the analog and the digital gain, thus resulting in a non-constant channel gain during the gain transition. This is shown in Fig. 2.5 for a 1st order analog system. While the digital gain can be changed almost instantly on a sample by sample basis, the settling time of the preamplifier output after a gain change depends on the bandwidth of the amplifier.

A change of gain for a constant input level is equal to the situation of having a step pulse on the input of the preamplifier. For a 1st order system, with a time-constant  $\tau$ , the time-constant is given as:

$$\tau = \frac{1}{f_{BW}} \tag{2.7}$$

where  $f_{BW}$  is the system frequency bandwidth. Applying the gain change at t = 0, then after  $t = \tau$  the preamplifier output has settled to 63.2% of the final value. At  $t = 5\tau$  the output is within 99.3% of the final value. Consider the case of an adaptive A/D conversion channel where the sampling frequency,  $f_s$ , is at the Nyquist rate of the signal bandwidth,  $f_s = 2f_{BW,sig}$ . For the output of the preamplifier to have settled to within 99.3% of the final value within a sampling period, requires that:

$$\tau = \frac{1}{5f_s} \Leftrightarrow f_{BW} = \frac{1}{\tau} = 5f_s = 10f_{BW,sig} \tag{2.8}$$

The result in (2.8) is only valid in case of the digital part of the conversion channel operating at the Nyquist rate. Thus in order to avoid any transient glitches in the channel output, the preamplifier needs to be significantly faster than dictated by the signal bandwidth. Higher bandwidth requires higher transconductance of the MOSFETs in the amplifier, which in turn requires higher biasing current. Avoiding transient glitches by increasing the bandwidth of the preamplifier is thus not an attractive solution for low power systems. The generation of transient glitches is practically unavoidable in the adaptive A/D conversion channel, when applying digital gain compensation. A relevant question is then how large a transient glitch that can be tolerated in the output of the conversion channel. The transient glitch error, e(t), may be analytically expressed as:

$$e(t) = \Delta G \cdot [h(t) - s(t)] \cdot x(t) \tag{2.9}$$

where  $\Delta G$  is the change in gain, h(t) is the Heaviside step function, s(t) is the step response of the signal path from the amplifier output to the digital gain block, and x(t) is the input signal to the digital gain block and the AGC detector. The peak glitch error thus depends on the gain step  $\Delta G$ , the value of x(t) at the moment of the gain change and the step response s(t). The minimum value of  $\Delta G$  is directly related to the step sizes used in the VGA, the value x(t) is dependent on the signal level at the moment of the gain change, and s(t) is dependent on the settling time of the VGA and conversion time of the ADC. By adjusting either one, the peak value of the glitch may be reduced. These parameters are discussed in more detail in Sec. 2.4.

The question of how large a glitch that may be tolerated is more difficult to answer. Since the conversion channel is for audio applications, sound recorded using a MEMS sensor in combination with the conversion channel, will be played back to a person. Since the hearing of each individual is different, so is the perception of how large a glitch that may be tolerated. Thus, the psychoacoustical performance needs to be taken into account. This topic is evaluated further in Chap. 3.

Finally follows the question of how best to reduce the glitch error in the output of the conversion channel. From (2.9) it seems obvious to adjust  $\Delta G$ , but this may not be the best solution. This is discussed further in Chap. 4.

# 2.4 Automatic Gain Control

The automatic gain control is a key part of the adaptive A/D conversion channel as it handles all changes of the VGA gain and the digital compensation. The topic of AGC systems has been thoroughly researched in the past, and are used in e.g. RF circuits for expanding the dynamic range of a receiver circuit. In [13] is presented a general overview of the topic for RF applications, including circuit examples. Some of the considerations for applying AGC to RF systems can also be applied to audio systems. A review of AGC theory is provided in [14], focusing on the theory for mainly analog AGC systems. In [15] is presented an analysis of AGC systems for audio applications, also with the focus on the theoretical analysis of the analog implementation. In [16] is given an analysis of distortion in AGC for audio systems, where the impact of the AGC loop delay on the signal distortion is discussed. However, in [13–16], the application of digital gain compensation is not investigated.

In this section an overview is given for the important properties and related

Figure 2.6: Types of AGC loops

Table 2.1: Pros and cons of feedback and feedforward AGC loops, adapted from [13]

|             | DR of input detector | Stability | Settling time |

|-------------|----------------------|-----------|---------------|

| Feedforward | -                    | +         | +             |

| Feedback    | +                    | -         | -             |

considerations when designing the AGC system for the adaptive A/D conversion channel with digital gain compensation and for audio signals.

# 2.4.1 AGC Loops

The purpose of the AGC system in the adaptive A/D conversion channel is to adjust the channel gain settings. This with the aim of avoiding clipping in the analog domain for large input signals. Ideally, the AGC loop is able to instantly adjust the gain of the preamplifier in order to avoid clipping. In reality such an AGC is not realizable, as the AGC loop inherently has a delay that depends on the type of loop.

The loop of the AGC can be either feedback or feedforward based, depending on whether the AGC input is taken from the signal path before or after the preamplifier. Both loop types are depicted in Fig. 2.6.

Using a feedback based AGC has the benefit that the dynamic range of the peak detector only has to be as good as the dynamic range of the output of the preamplifier. However, feedback systems may be unstable which is a concern when controlling the amplifier gain. Furthermore, a feedback loop inherently increases the delay time of the AGC. A feedforward system is inherently stable, since there is no loop. For the same reason, the delay time of the AGC is much lower, making it possible for the AGC to react almost instantly when a large input signal occurs. However, with the peak detector connected to the input of the conversion channel, the peak detector requires a dynamic range equal to that of the input signal. For large dynamic ranges, this may be a problem. A summary of the pros and cons of the two loop types is given in Table 2.1.

For the A/D conversion channel it is also necessary to consider whether the peak detector and the AGC controller should be implemented in the analog domain,

Figure 2.7: Signal and the associated signal envelope